High-performance semiconductor module

Auer , et al. July 16, 2

U.S. patent number D853,978 [Application Number D/615,038] was granted by the patent office on 2019-07-16 for high-performance semiconductor module. This patent grant is currently assigned to Infineon Technologies AG. The grantee listed for this patent is Infineon Technologies AG. Invention is credited to Thomas Auer, Andras Bertalan, Jens Krugmann, Christoph Messelke.

| United States Patent | D853,978 |

| Auer , et al. | July 16, 2019 |

High-performance semiconductor module

Claims

CLAIM The ornamental design for a high-performance semiconductor module, as shown and described.

| Inventors: | Auer; Thomas (Warstein, DE), Bertalan; Andras (Warstein-Allagen, DE), Krugmann; Jens (Paderborn, DE), Messelke; Christoph (Arnsberg, DE) | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Applicant: |

|

||||||||||

| Assignee: | Infineon Technologies AG

(Neubiberg, DE) |

||||||||||

| Appl. No.: | D/615,038 | ||||||||||

| Filed: | August 25, 2017 |

Foreign Application Priority Data

| Feb 28, 2017 [EM] | 003772235-0001 | |||

| Current U.S. Class: | D13/182 |

| Current International Class: | 1303 |

| Field of Search: | ;D13/182 ;257/678,684,690,691 ;361/679.01,713,728,736,760,761,772,775,783,820 ;174/250,253 ;438/15,25,26,51,55,63,64,106 |

References Cited [Referenced By]

U.S. Patent Documents

| 6774465 | August 2004 | Lee |

| D587662 | March 2009 | Soutome |

| D589012 | March 2009 | Soyano |

| D606951 | December 2009 | Soyano |

| D648290 | November 2011 | Mori |

| D653634 | February 2012 | Soyano |

| D712853 | September 2014 | Nakamura |

| D721048 | January 2015 | Nakamura |

| D721340 | January 2015 | Nakamura |

| D748595 | February 2016 | Bertalan |

| D754084 | April 2016 | Kawase |

| D762185 | July 2016 | Muehlensiep |

| D762597 | August 2016 | Bertalan |

| D766851 | September 2016 | Yoneyama |

| D767516 | September 2016 | Yoneyama |

| D772184 | November 2016 | Soyano |

| D773412 | December 2016 | Yoneyama |

| D774479 | December 2016 | Soyano |

| D775091 | December 2016 | Edenharter |

| D775593 | January 2017 | Edenharter |

| D776071 | January 2017 | Edenharter |

| D785577 | May 2017 | Kawase |

| D798832 | October 2017 | Hayashida |

| D799439 | October 2017 | Hayashiguchi |

| D814431 | April 2018 | Matsumoto |

| D814433 | April 2018 | Soyano |

| 2001/0038143 | November 2001 | Sonobe |

| 2011/0044012 | February 2011 | Matsumoto |

Attorney, Agent or Firm: Murphy, Bilak & Homiller, PLLC

Description

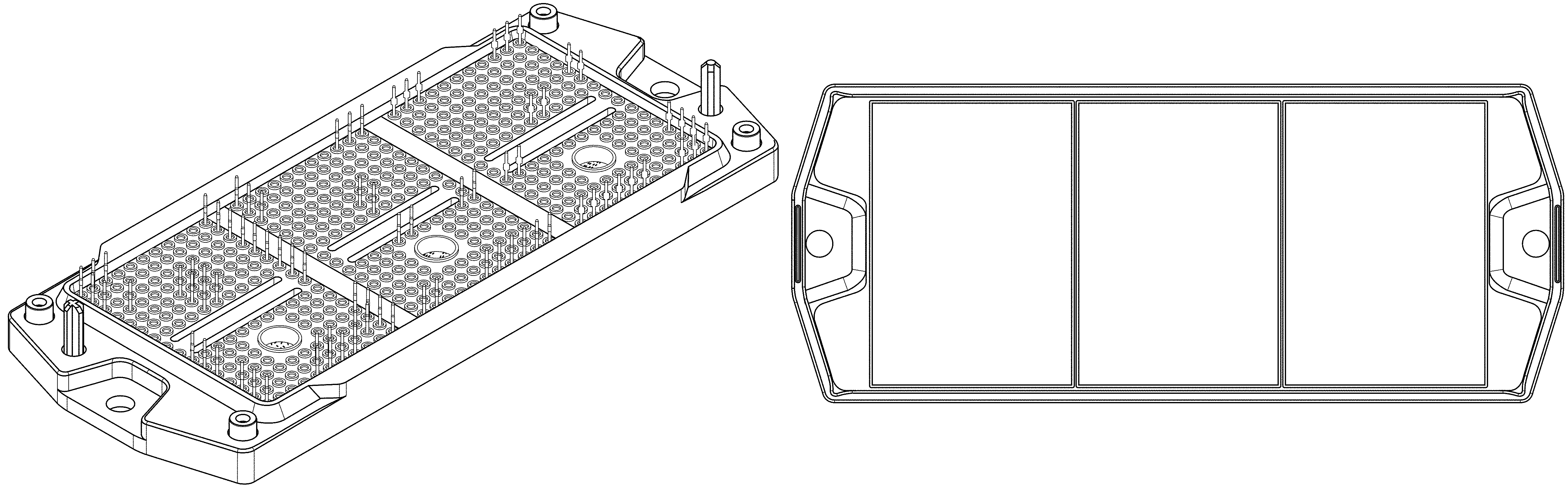

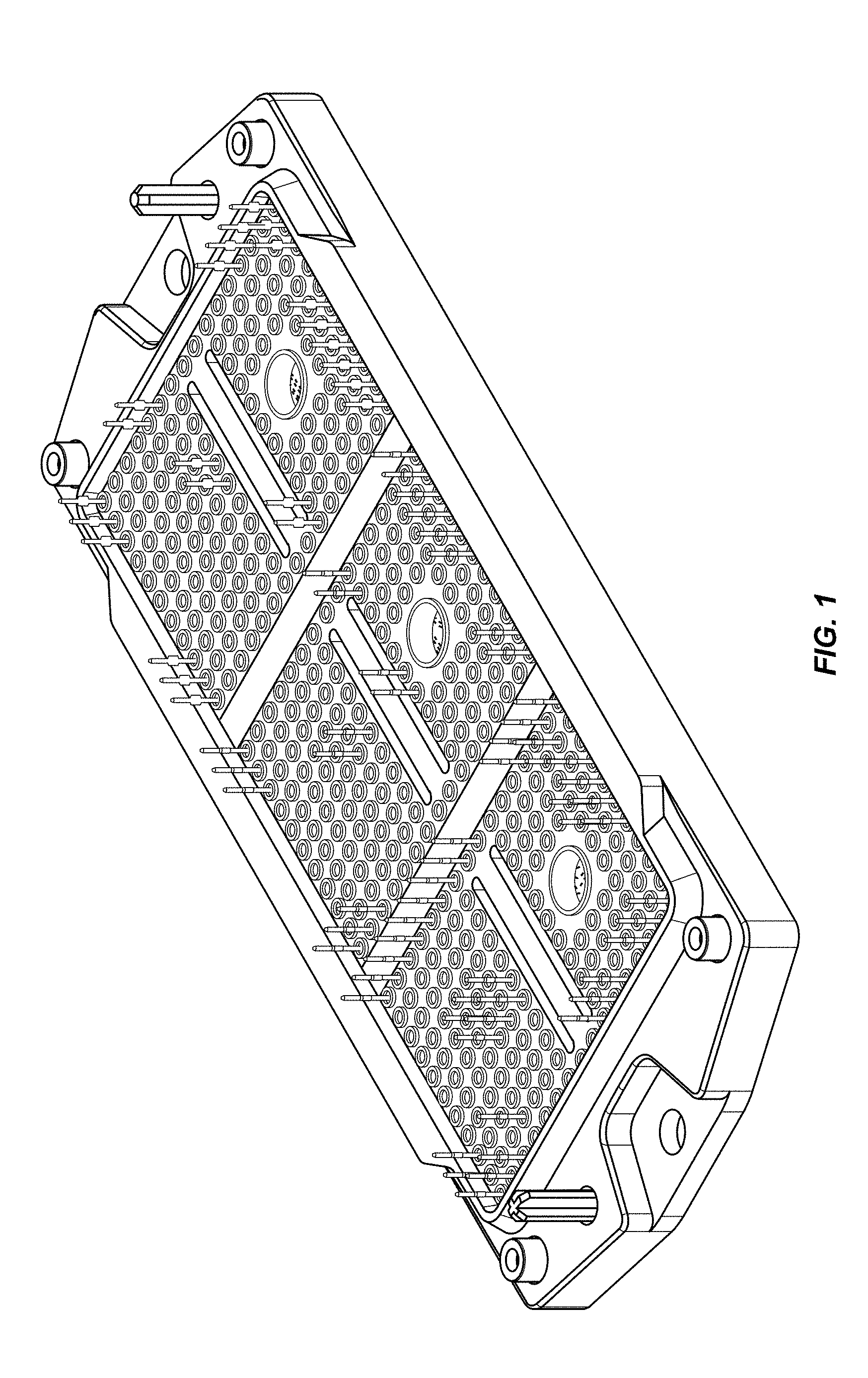

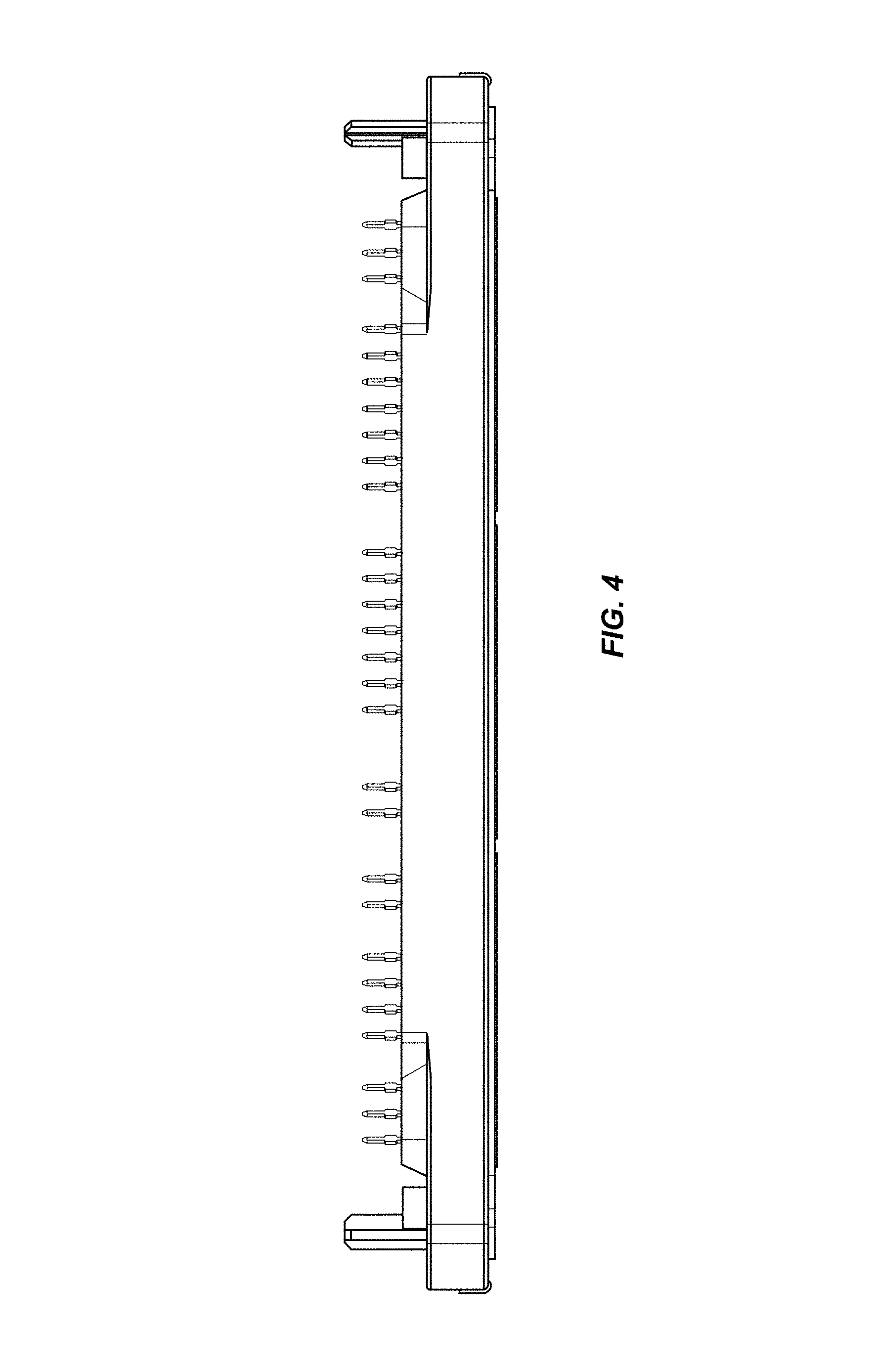

FIG. 1 is a top, front and right side perspective view of a high-performance semiconductor module showing our new design;

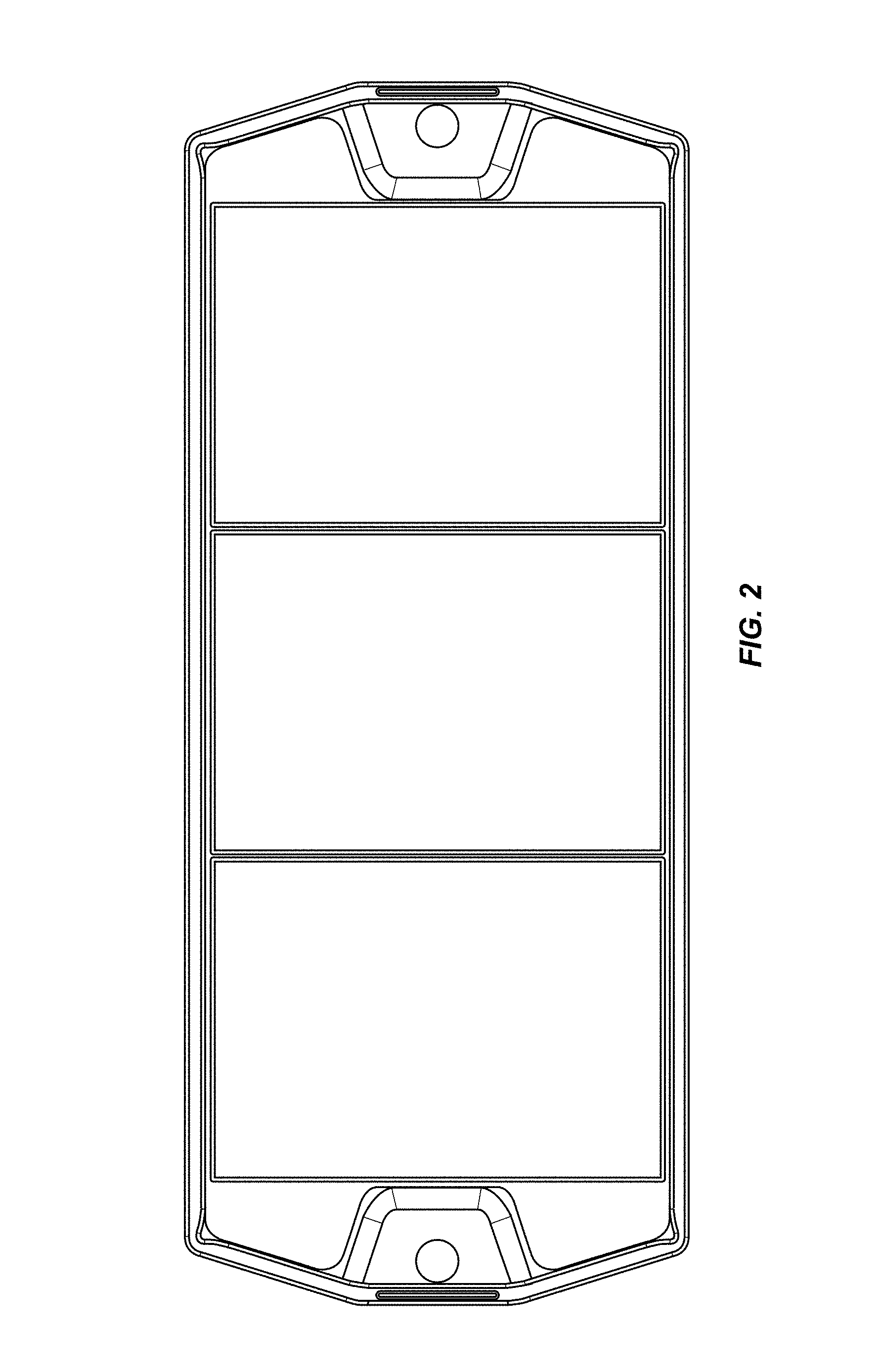

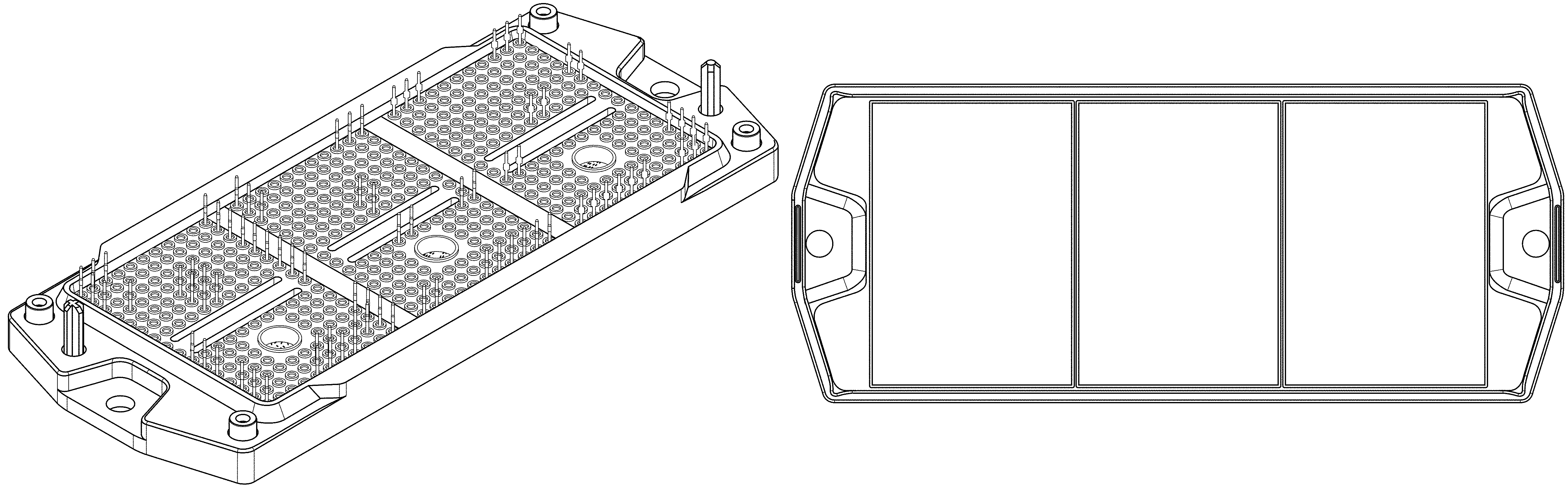

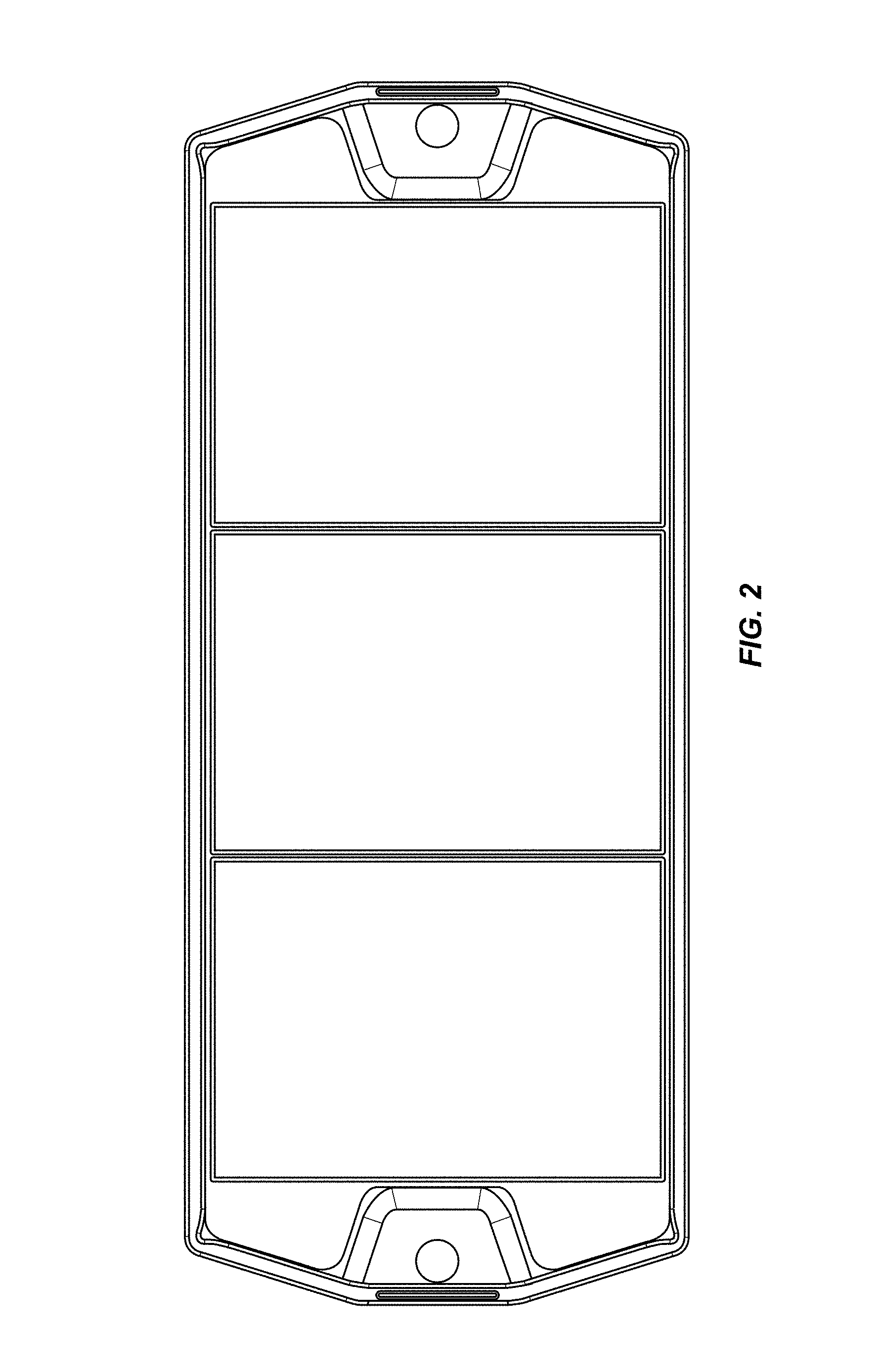

FIG. 2 is a bottom plan view thereof;

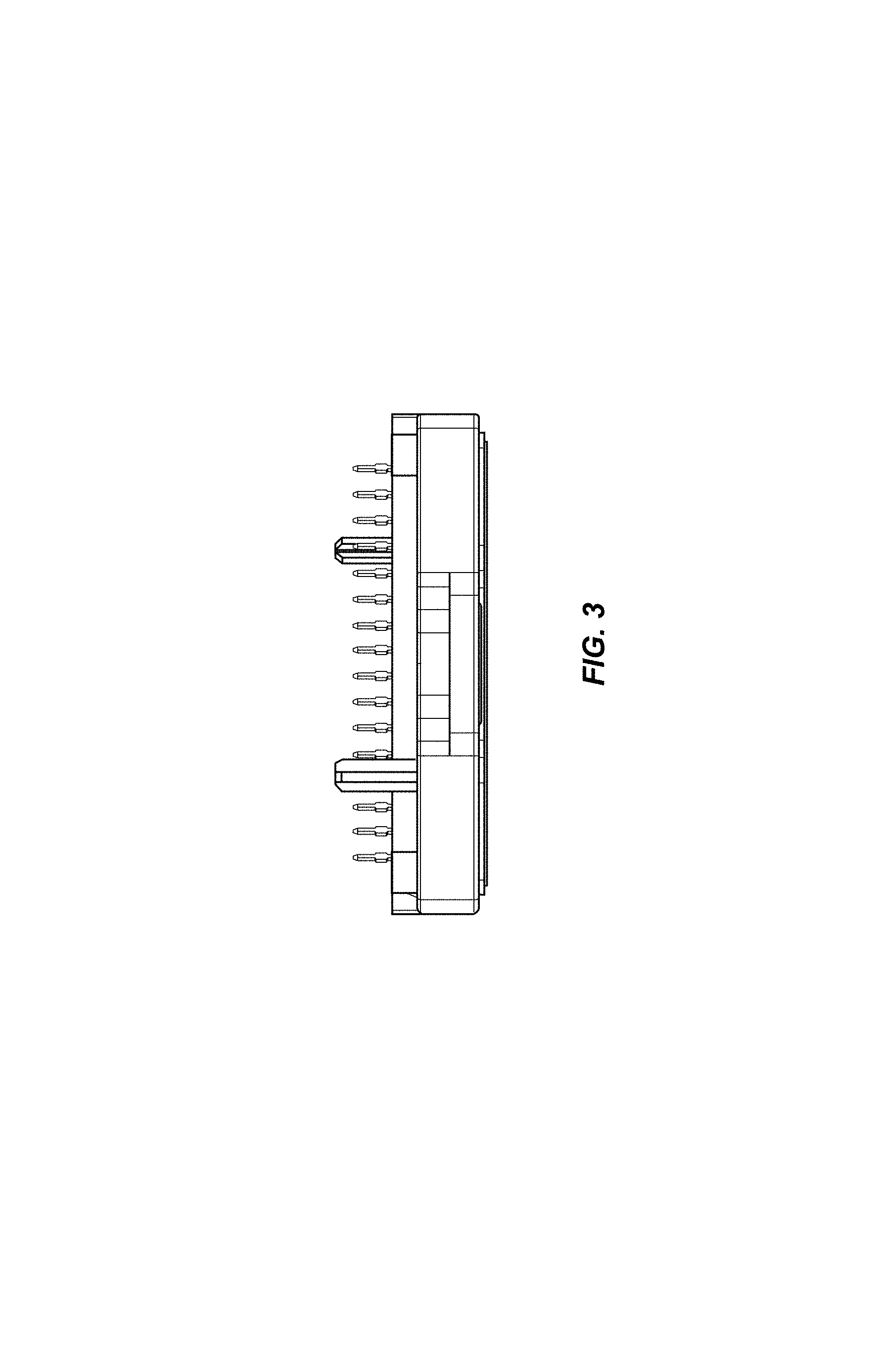

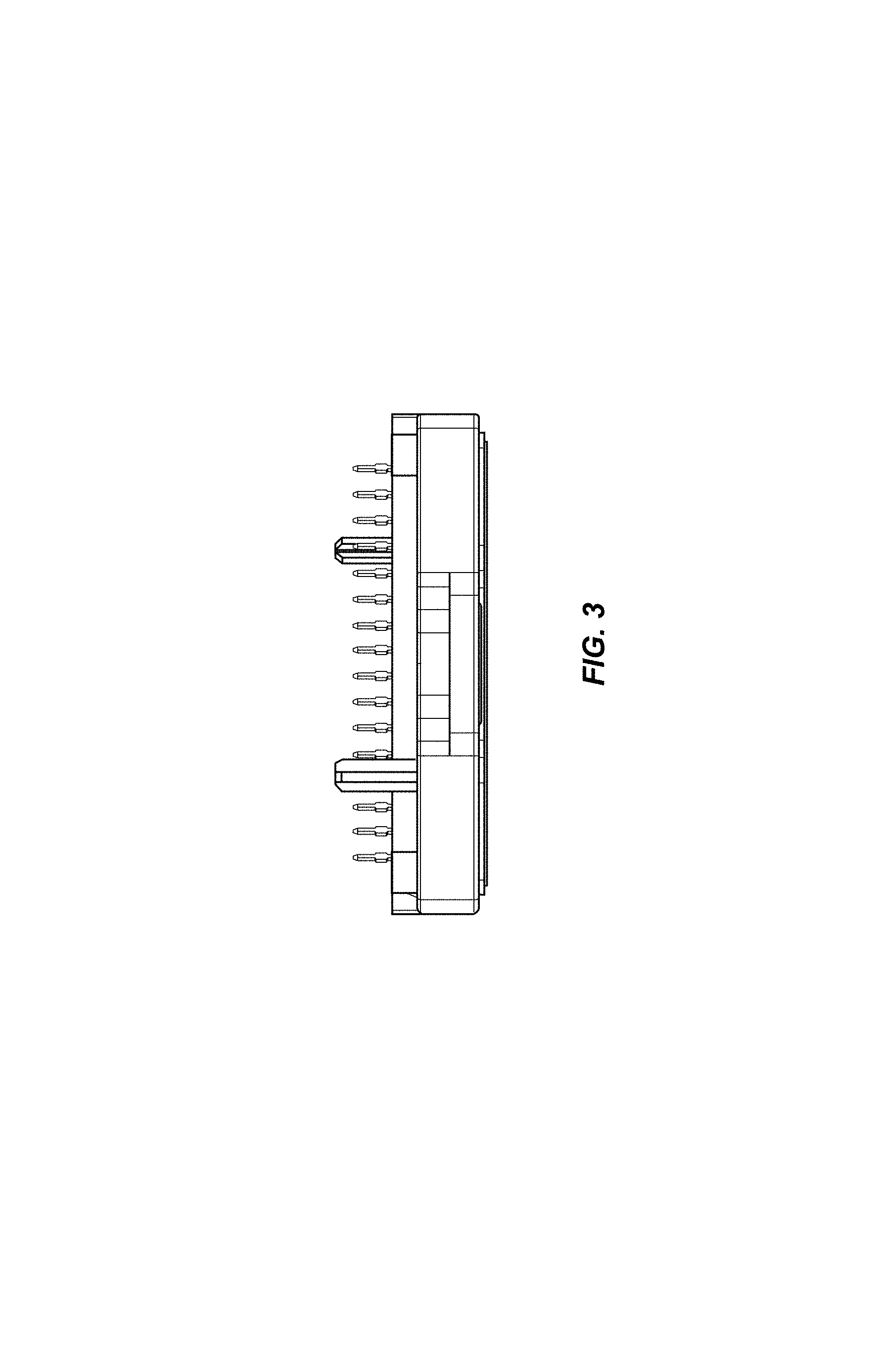

FIG. 3 is a front side elevational view thereof;

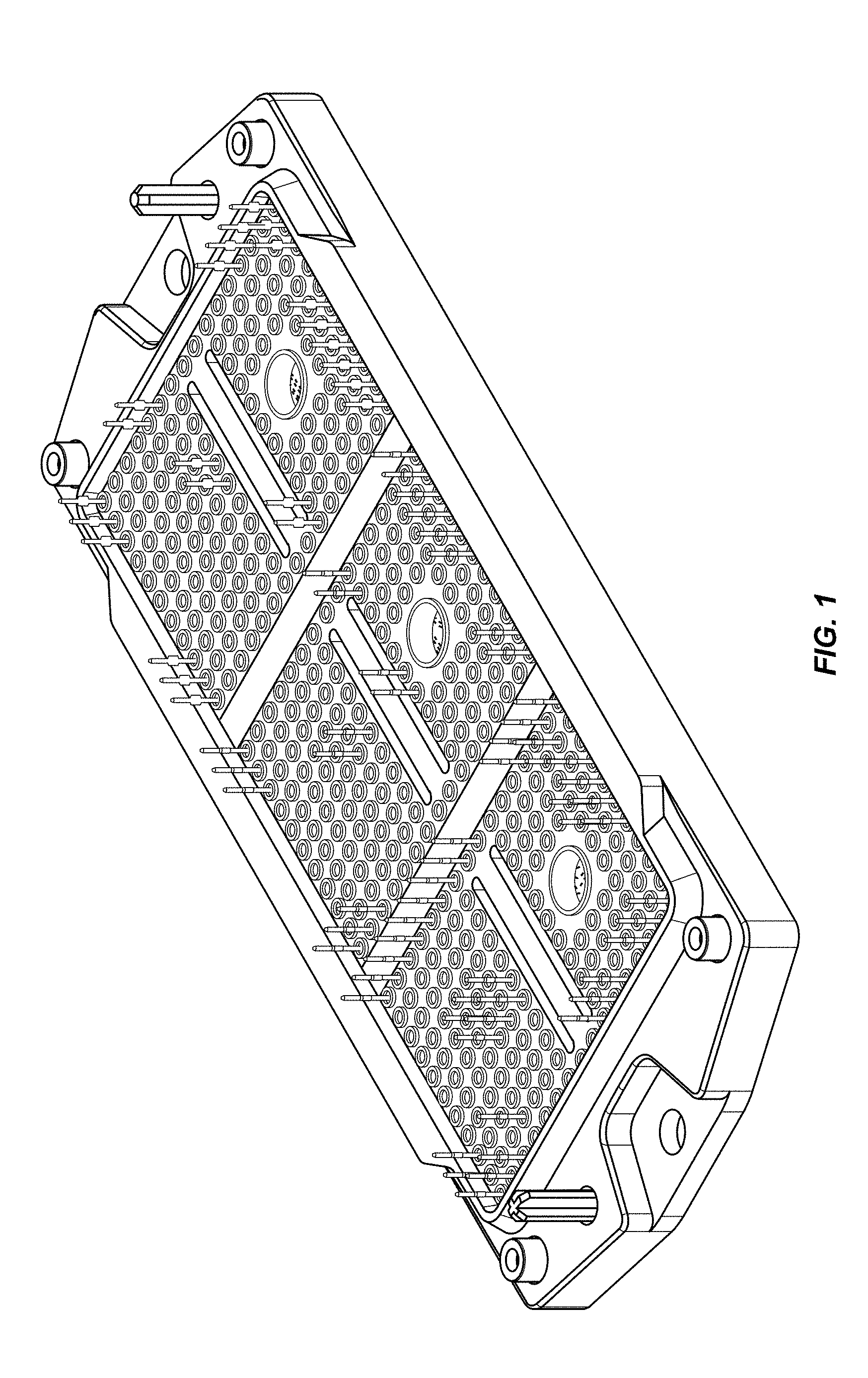

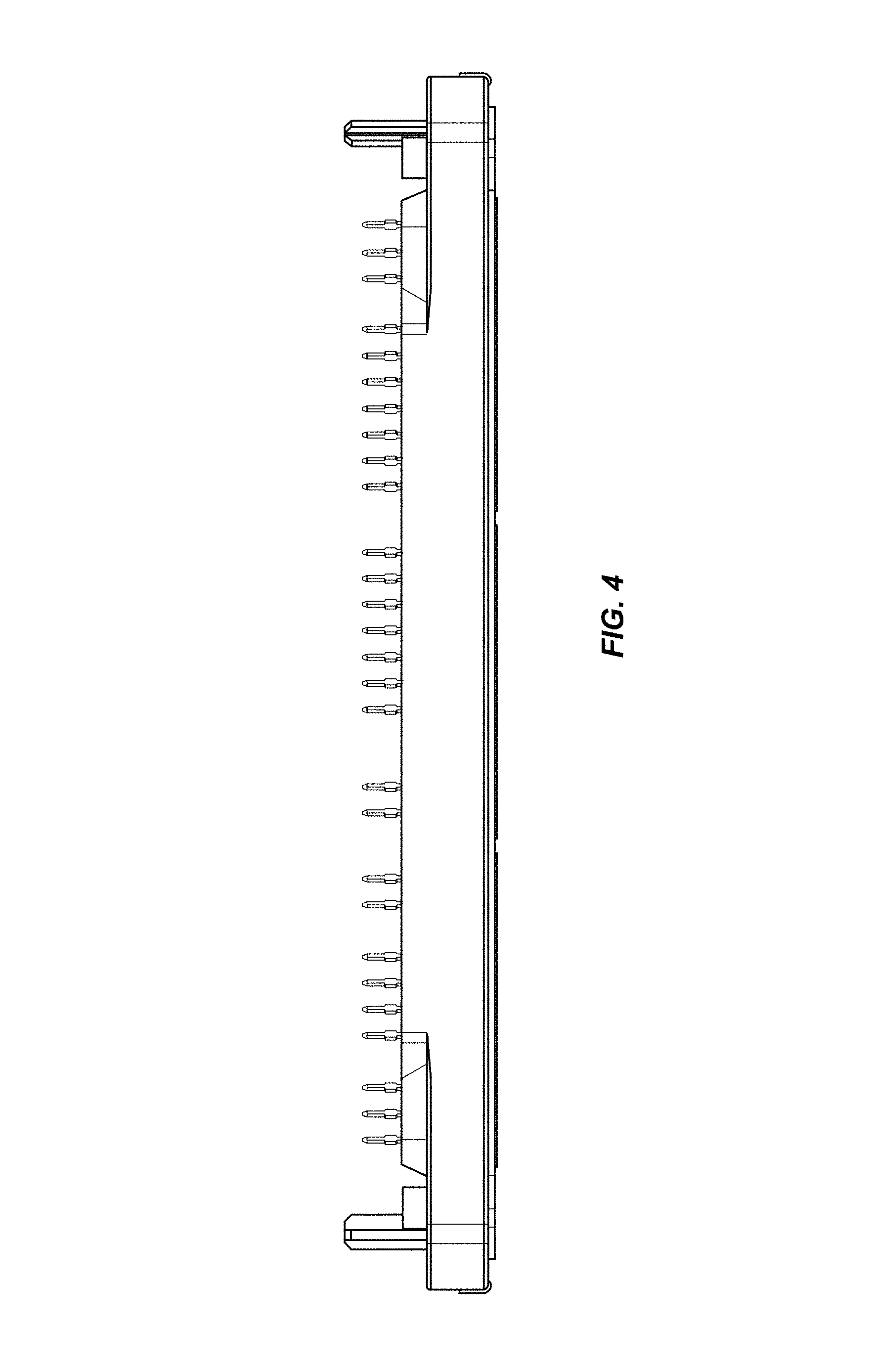

FIG. 4 is a right side elevational view thereof; and,

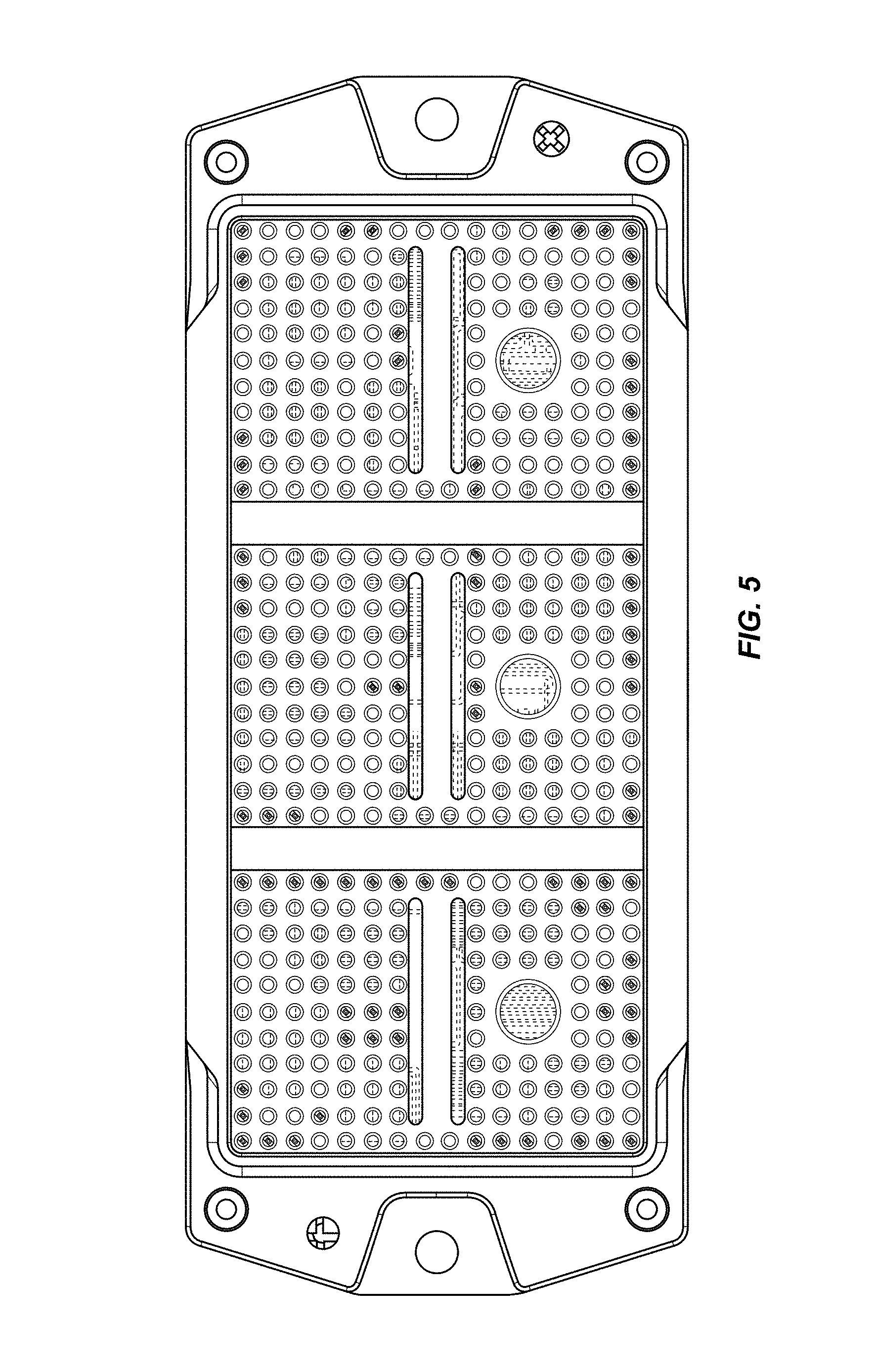

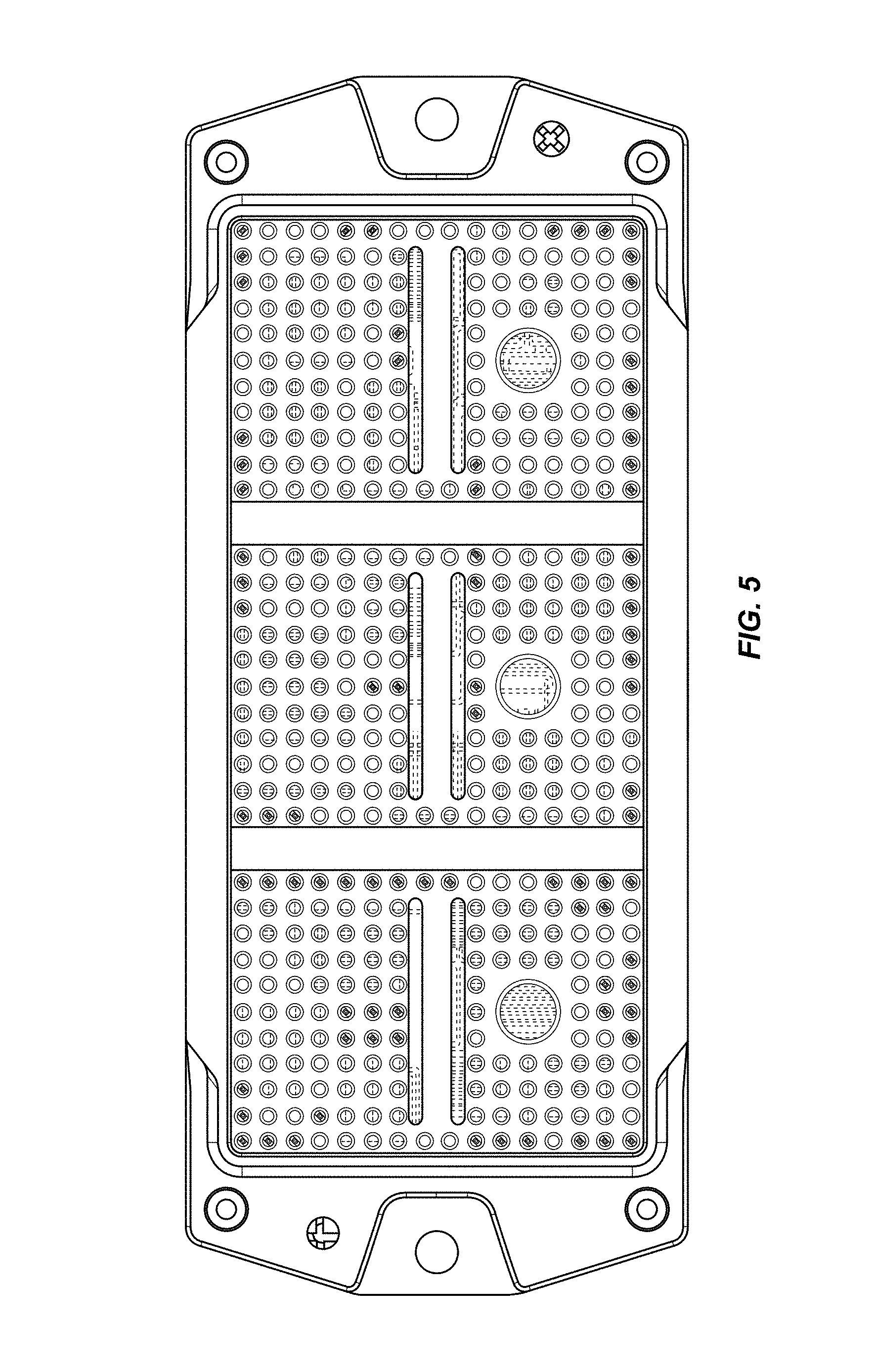

FIG. 5 is a top plan view thereof.

The broken line portions of the figure drawings are included to show portions of the article that form no part of the claimed design.

All surfaces not shown form no part of the claimed design.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.