Structure And Method For Providing Line End Extensions For Fin-type Active Regions

YU; Shao-Ming ; et al.

U.S. patent application number 16/726405 was filed with the patent office on 2020-07-02 for structure and method for providing line end extensions for fin-type active regions. The applicant listed for this patent is Taiwan Semiconductor Manufacturing Company, Ltd.. Invention is credited to Chang-Yun CHANG, Chih-Hao CHANG, Kai-Tai CHANG, Hsin-Chih CHEN, Yi-Tang LIN, Kuei-Liang LU, Ming-Feng SHIEH, Shao-Ming YU.

| Application Number | 20200212217 16/726405 |

| Document ID | / |

| Family ID | 59847816 |

| Filed Date | 2020-07-02 |

View All Diagrams

| United States Patent Application | 20200212217 |

| Kind Code | A1 |

| YU; Shao-Ming ; et al. | July 2, 2020 |

STRUCTURE AND METHOD FOR PROVIDING LINE END EXTENSIONS FOR FIN-TYPE ACTIVE REGIONS

Abstract

A semiconductor structure includes an isolation feature formed in the semiconductor substrate and a first fin-type active region. The first fin-type active region extends in a first direction. A dummy gate stack is disposed on an end region of the first fin-type active region. The dummy gate stack may overlie an isolation structure. In an embodiment, any recess such as formed for a source/drain region in the first fin-type active region will be displaced from the isolation region by the distance the dummy gate stack overlaps the first fin-type active region.

| Inventors: | YU; Shao-Ming; (Hsinchu County, TW) ; CHANG; Chang-Yun; (Taipei, TW) ; CHANG; Chih-Hao; (Hsin-Chu, TW) ; CHEN; Hsin-Chih; (Taipei County, TW) ; CHANG; Kai-Tai; (Kaohsiung City, TW) ; SHIEH; Ming-Feng; (Tainan County, TW) ; LU; Kuei-Liang; (Hsinchu City, TW) ; LIN; Yi-Tang; (Hsinchu City, TW) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 59847816 | ||||||||||

| Appl. No.: | 16/726405 | ||||||||||

| Filed: | December 24, 2019 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 15614439 | Jun 5, 2017 | 10573751 | ||

| 16726405 | ||||

| 14586602 | Dec 30, 2014 | 9673328 | ||

| 15614439 | ||||

| 13356235 | Jan 23, 2012 | 9324866 | ||

| 14586602 | ||||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 21/823418 20130101; H01L 29/66545 20130101; H01L 21/823437 20130101; H01L 21/823431 20130101; H01L 29/66795 20130101; H01L 29/7842 20130101; H01L 29/785 20130101; H01L 21/67248 20130101; H01L 27/0886 20130101; H01L 21/823412 20130101; H01L 29/7848 20130101 |

| International Class: | H01L 29/78 20060101 H01L029/78; H01L 29/66 20060101 H01L029/66; H01L 21/8234 20060101 H01L021/8234; H01L 21/67 20060101 H01L021/67; H01L 27/088 20060101 H01L027/088 |

Claims

1-20. (canceled)

21. A semiconductor structure, comprising: an isolation feature formed in a semiconductor substrate; a first fin formed in the semiconductor substrate, wherein the first fin extends in a first direction; a second fin formed on the semiconductor substrate, wherein the second fin is parallel to the first fin and a next adjacent fin to the first fin in a second direction; and a dummy gate disposed over the isolation feature and on an end region of the first fin and an end region of the second fin, wherein the dummy gate extends in the second direction, the second direction perpendicular to the first direction, and wherein the dummy gate includes spacers formed on sidewalls of a dummy electrode.

22. The semiconductor structure of claim 21, further comprising: another gate disposed on a first region of the first fin and a first region of the second fin, each of the first regions being spaced a distance from the respective end region.

23. The semiconductor structure of claim 22, wherein a source/drain region is disposed in the first fin between the another gate and the dummy gate.

24. The semiconductor structure of claim 21, wherein the spacers are formed on the end region of the first fin and the end region of the second fin.

25. The semiconductor structure of claim 21, wherein the isolation feature extends from physically interfacing the first fin region to the second fin.

26. The semiconductor structure of claim 21, further comprising: a third fin disposed a distance from and disposed parallel to the first fin, wherein the third fin is a next adjacent fin to the first fin, and wherein the first fin interposes the second and third fins.

27. The semiconductor structure of claim 26, wherein the dummy gate stack is disposed on an end region of the third fin.

28. The semiconductor substrate of claim 21, wherein the spacer element physically interfaces with a top surface of the first fin and a top surface of the second fin.

29. The semiconductor substrate of claim 21, wherein a gate dielectric layer of the dummy gate interfaces the isolation feature.

30. The semiconductor structure of claim 21, wherein the spacer element interfaces a top surface of the isolation feature.

31. A semiconductor device, comprising: a first plurality of fins oriented in a first direction, wherein each of the first plurality of fins are parallel and spaced a first distance in a second direction from one another, the second direction being perpendicular the first direction; a shallow trench isolation (STI) feature adjacent an end region of each of the first plurality of first fins; and a gate disposed on the STI feature, wherein the gate extends in a second direction to overlap with the end region of each of the first plurality of fins, wherein the gate includes spacers formed on sidewalls of a main gate.

32. The device of claim 31, further comprising: a second plurality of fins oriented in the first direction, wherein the STI feature interposes the first and second plurality of fins.

33. The device of claim 31, further comprising: a second gate disposed on each of the first plurality of fins.

34. The device of claim 31, wherein a first portion of a bottom surface of the spacers interface a top surface of each of the first plurality of fins.

35. The device of claim 34, wherein a second portion of a bottom surface of the spacers interface a top surface of the STI feature.

36. The device of claim 31, wherein at each end region, a surface of the spacers extending between the first portion and the second portion of the bottom surface of the spacers interfaces a sidewall of the end regions.

37. A device comprising: a gate structure including spacer elements disposed over a semiconductor substrate; a first plurality of fin active regions extending from the semiconductor substrate and each having a first end surface terminating directly under spacer elements of the gate structure; and a second plurality of fin active regions extending from the semiconductor substrate and each having a second end surface terminating directly under spacer elements of the gate structure; wherein the first plurality of fin active regions extend laterally away from the gate structure on a first side of the gate structure; and wherein the second plurality of fin active regions extend laterally away from the gate structure on a second side of the gate structure that is opposite the first side of the gate structure.

38. The device of claim 37, wherein the spacer elements include one or more dielectric materials.

39. The device of claim 37, wherein a source/drain region adjacent the gate structure is aligned with an edge of the spacer elements.

40. The device of claim 37, wherein the spacer elements are formed on a sidewall of a polysilicon gate electrode.

Description

CROSS-REFERENCE

[0001] This application is a continuation of U.S. application Ser. No. 15/614,439, filed Jun. 5, 2017, which is a divisional of U.S. application Ser. No. 14/586,602, filed Dec. 30, 2014, now U.S. Pat. No. 9,673,328, which is a continuation-in-part of U.S. patent application Ser. No. 13/356,235 filed on Jan. 23, 2012, now U.S. Pat. No. 9,324,866, the entire disclosures of which are incorporated herein by reference.

BACKGROUND

[0002] In advanced technologies of integrated circuit industry, strained semiconductor structures are used to increase the carrier mobility in the channel and enhance circuit performance. Epitaxy growth is a step implemented to form the strained structure. However, the epitaxy growth is sensitive to the structure of the active regions and the corresponding environment. In one example, faucet defects are formed and constrain further epitaxy growth. Therefore, a structure of an integrated circuit and a method making the same are needed to address the issues identified above.

BRIEF DESCRIPTION OF THE DRAWINGS

[0003] Aspects of the present disclosure are best understood from the following detailed description when read with the accompanying figures. It is emphasized that, in accordance with the standard practice in the industry, various features are not drawn to scale. In fact, the dimensions of the various features may be arbitrarily increased or reduced for clarity of discussion.

[0004] FIG. 1 is a top view of a semiconductor structure constructed according to aspects of the present disclosure in one embodiment.

[0005] FIG. 2 is a fragmental top view of the semiconductor structure of FIG. 1 constructed according to aspects of the present disclosure in one embodiment.

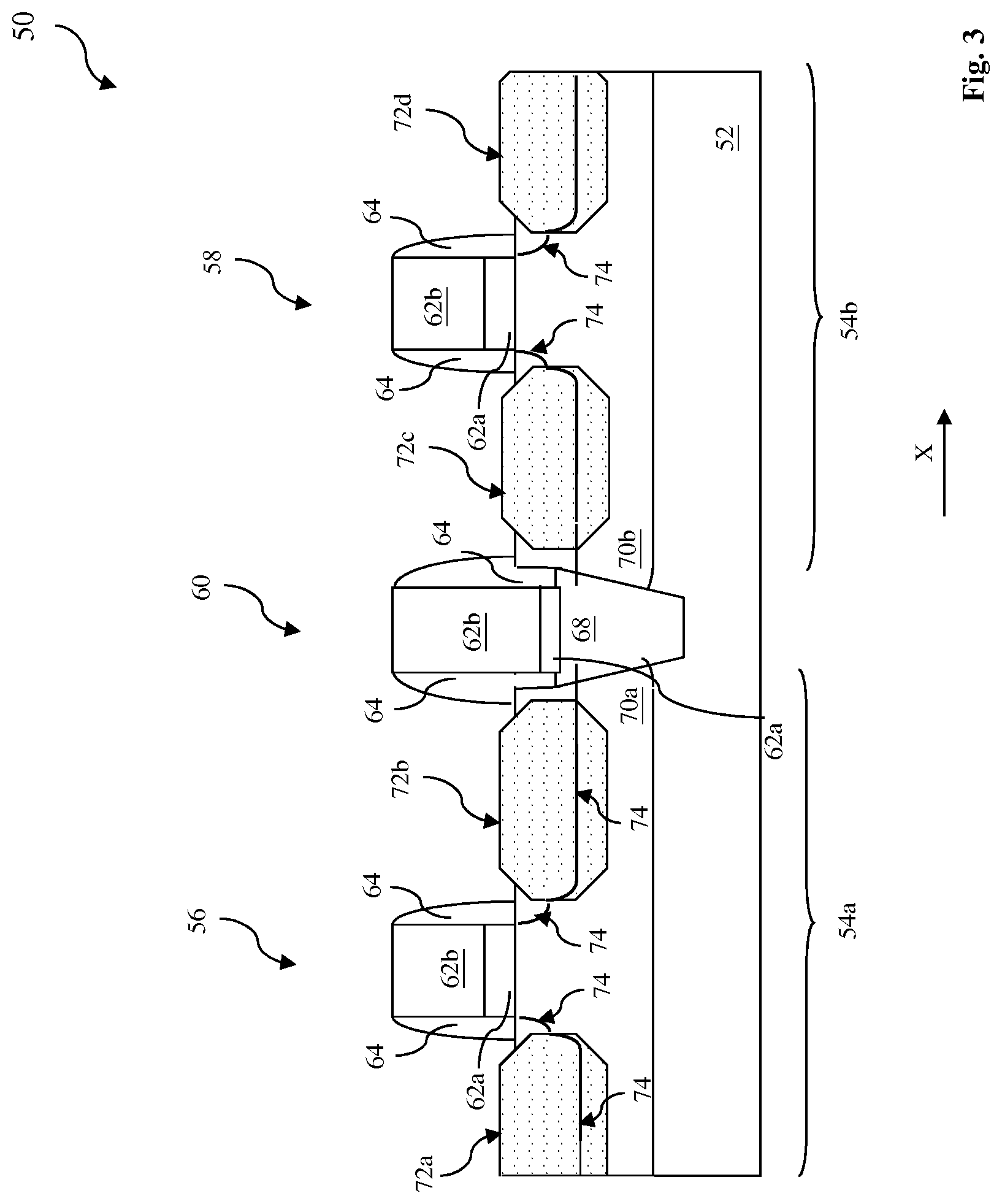

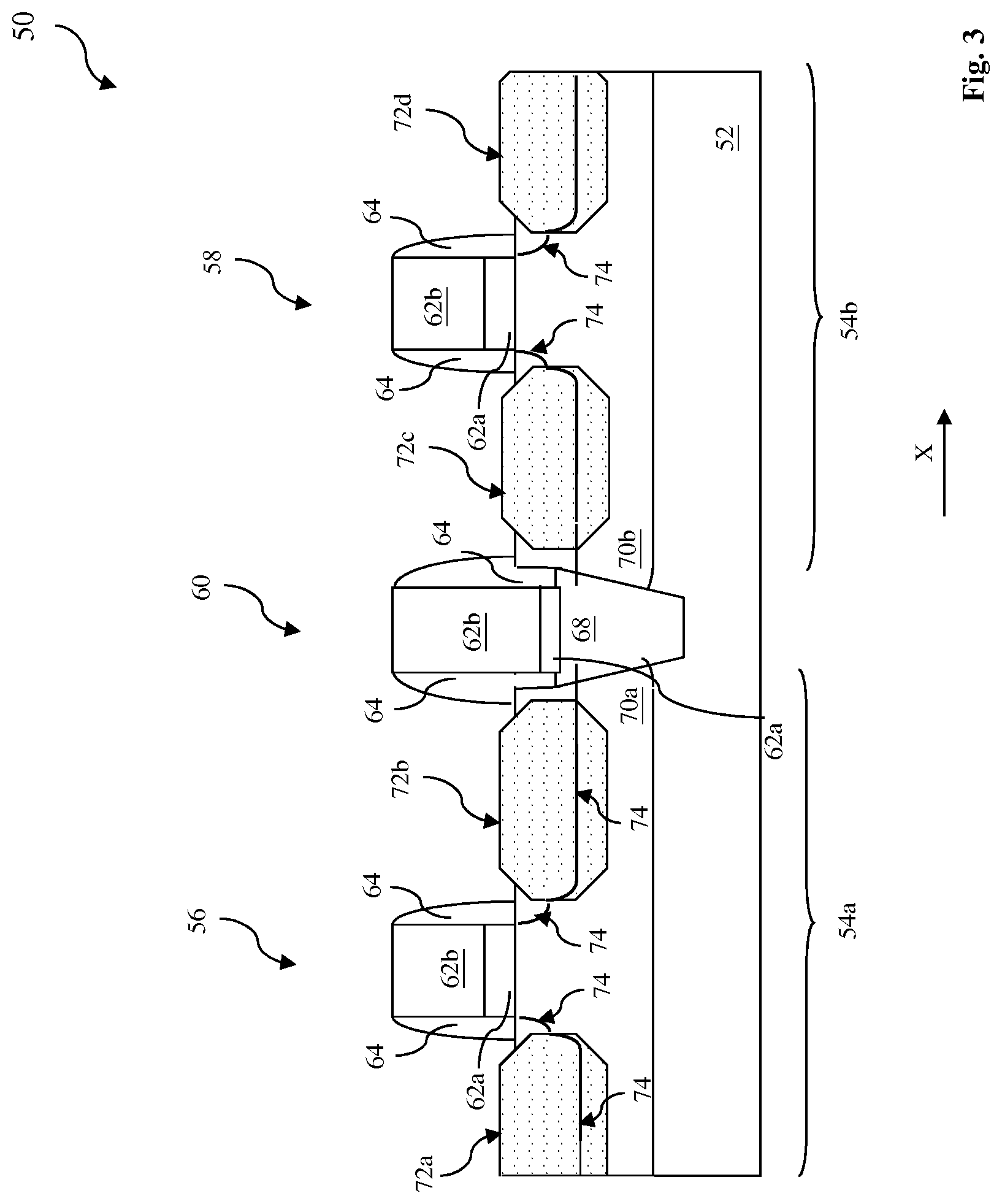

[0006] FIG. 3 is a sectional view of the semiconductor structure of FIG. 1 along line AA' constructed according to aspects of the present disclosure in one embodiment.

[0007] FIG. 4 is a flowchart of a method making the semiconductor structure of FIG. 1.

[0008] FIG. 5 is a flowchart of a method making a fin-like active regions in the semiconductor structure of FIG. 1.

[0009] FIG. 6 is a schematic diagram to illustrate patterning a hard mask for forming the fin-like active regions in the semiconductor structure of FIG. 1.

[0010] FIG. 7 is a sectional view of the semiconductor structure of FIG. 1 along line BB' constructed according to aspects of the present disclosure in one embodiment.

[0011] FIG. 8 is a fragmental top view of a semiconductor structure constructed according to aspects of the present disclosure in one embodiment.

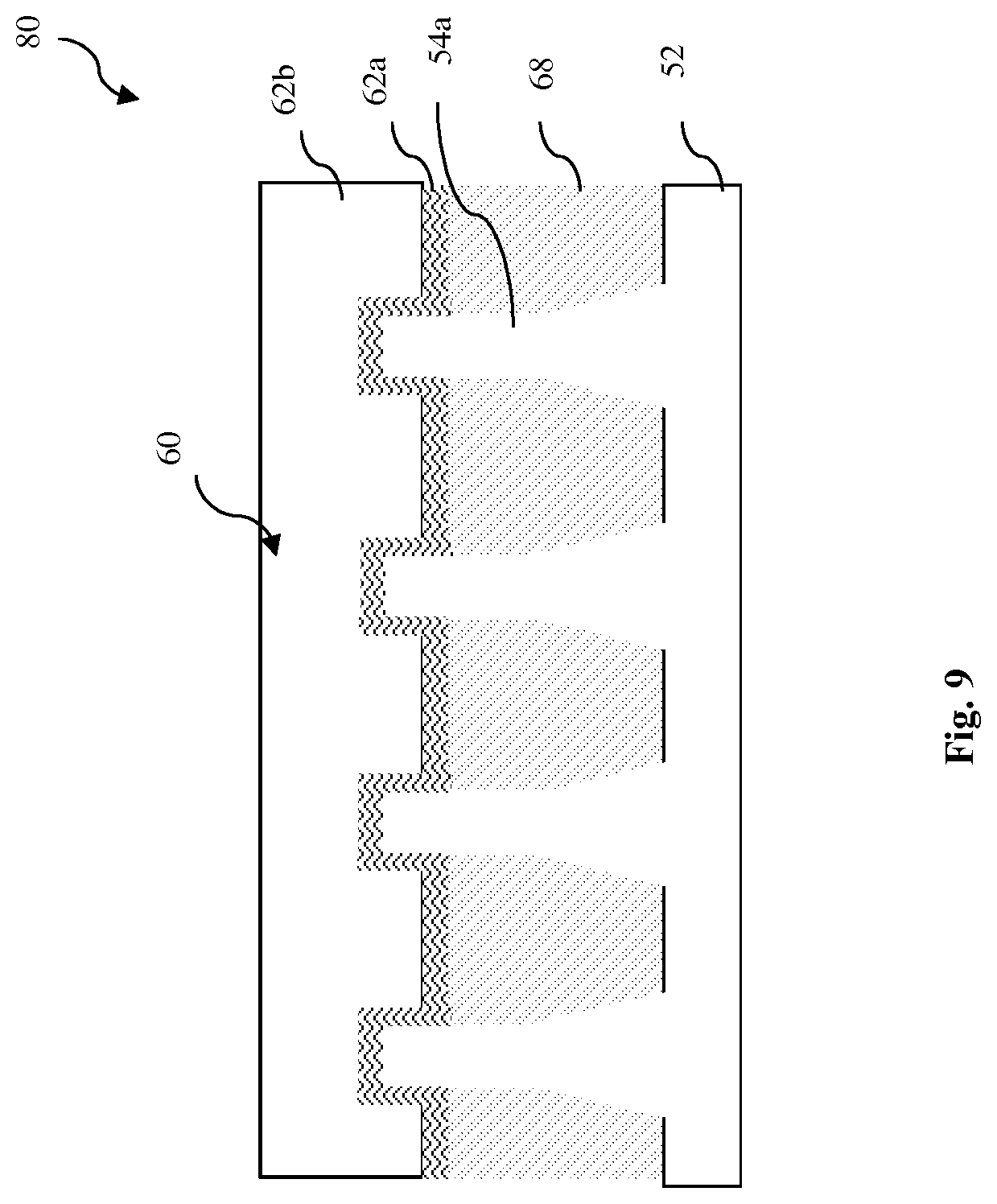

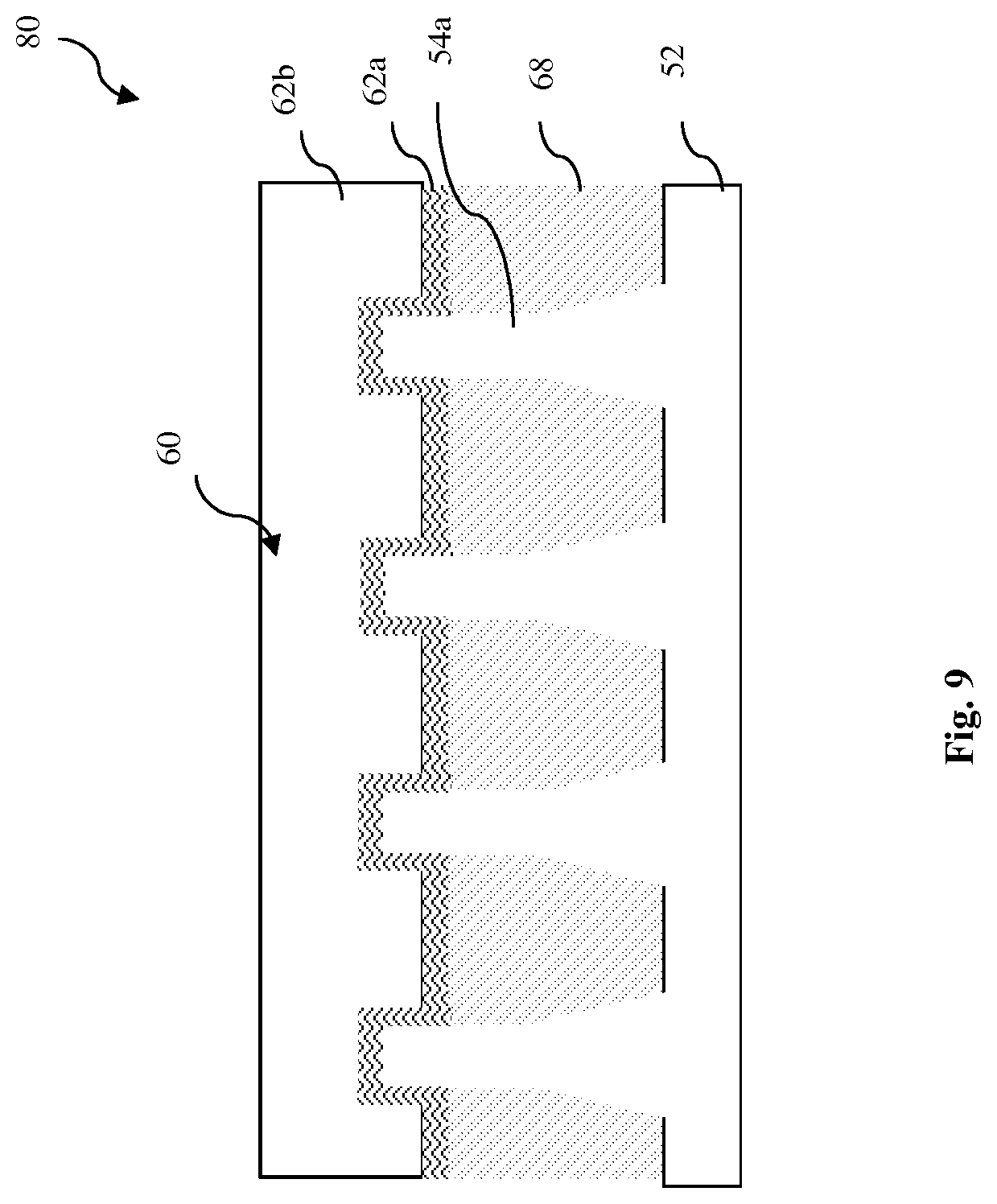

[0012] FIG. 9 is a sectional view of the semiconductor structure of FIG. 8 along line CC' constructed according to aspects of the present disclosure in one embodiment.

[0013] FIG. 10 is a fragmental top view of a semiconductor structure constructed according to aspects of the present disclosure in one embodiment.

[0014] FIGS. 11A and 11B are each a sectional view of the semiconductor structure of FIG. 8 along line DD' constructed according to aspects of the present disclosure in one embodiment.

DETAILED DESCRIPTION

[0015] It is to be understood that the following disclosure provides many different embodiments, or examples, for implementing different features of various embodiments. Specific examples of components and arrangements are described below to simplify the present disclosure. These are, of course, merely examples and are not intended to be limiting. In addition, the present disclosure may repeat reference numerals and/or letters in the various examples. This repetition is for the purpose of simplicity and clarity and does not in itself dictate a relationship between the various embodiments and/or configurations discussed. Moreover, the formation of a first feature over or on a second feature in the description that follows may include embodiments in which the first and second features are formed in direct contact, and may also include embodiments in which additional features may be formed interposing the first and second features, such that the first and second features may not be in direct contact.

[0016] FIG. 1 is a top view of a semiconductor structure 50 constructed according to aspects of the present disclosure in one embodiment. FIG. 2 is a fragmental top view of the semiconductor structure 50 constructed according to aspects of the present disclosure in one embodiment. The semiconductor structure 50 and the method making the same are collectively described with reference to FIGS. 1 and 2.

[0017] In one embodiment, the semiconductor structure 50 is a portion of a semiconductor wafer, or particularly a portion of a semiconductor dice (or a chip). The semiconductor structure 50 includes a semiconductor substrate 52. In one embodiment, the semiconductor substrate includes silicon. Alternatively, the substrate 52 includes germanium or silicon germanium. In other embodiments, the substrate 52 may use another semiconductor material, such as diamond, silicon carbide, gallium arsenic, GaAsP, AnnAs, AlGaAs, GaInP, or other proper combination thereof. Furthermore, the semiconductor substrate 52 may include a bulk semiconductor such as bulk silicon and an epitaxy silicon layer formed on he bulk silicon.

[0018] Referring to FIG. 1, the semiconductor structure 50 further includes various active regions 54, such as active regions 54a and 54b. In the present embodiment, the active regions 54 are fin-like structure designed to form fin-like field effect transistors (FinFETs). In a particular embodiment, the semiconductor structure 50 includes a plurality of fin-like active regions configured in parallel, such as a first plurality of fin-like active regions 54a and a second plurality of fin-like active regions 54b. The first plurality of fin-like active regions 54a and the second plurality of fin-like active regions 54b are separated by isolation features. In one example for illustration, the first plurality of fin-like active regions 54a are configured for n-type FinFETs (nFinFETs) and the second plurality of fin-like active regions 54b are configured for p-type FinFETs (pFinFETs). Various isolation features, such as shallow trench isolation (STI) features, are formed on the semiconductor substrate 52 in a procedure to form the fin-like active regions.

[0019] The fin-like active regions 54 are formed by a proper technique. In one example, the formation of the fin-like active regions includes forming STI features to define the areas for the active regions, etching the semiconductor material (e.g., silicon) in the active regions, and epitaxy growing a semiconductor material (e.g., silicon) in the active regions to form fin-like active regions 54. In another example, the formation of the fin-like active regions includes forming STI features to define the areas for the active regions, and etching to recess the STI features such that the active regions are extruded to form fin-like active regions 54.

[0020] Various gate stacks are formed on the fin-like active regions 54. The gate stacks include one or more functional gate stacks for field effect transistors and a dummy gate stack configured over the isolation features. In the present embodiment, the semiconductor structure 50 includes a first gate stack 56 disposed on the first plurality of fin-like active regions 54a and a second gate stack 58 disposed on the second plurality of fin-like active regions 54b. The first gate stack 56 and the second gate stack 58 are configured to form respective field effect transistors, such as nFinFETs and pFinFETs. Furthermore, the semiconductor structure 50 includes a dummy gate stack 60 disposed on the STI feature and extended to be partially over the active regions 54. Particularly, the dummy gate stack 60 is disposed on the STI features and covers the end portions of the active regions 54 as illustrated in FIG. 1. State differently, the fin-like active regions 54 are extended to the dummy gate 60 such that the end portions of fin-like active regions 54 are underlying the dummy gate stack. In furtherance of the present embodiment, the first plurality of fin-like active regions 54a are extended to the dummy gate stack 60 from one side, and the second plurality of fin-like active regions 54b are extended to the dummy gate stack 60 from another side such that the dummy gate stack 60 covers both the ends of the first plurality of fin-like active regions 54a and the ends of the second plurality of fin-like active regions 54b.

[0021] In one embodiment, each of the gate stacks 56, 58 and 60 includes a main gate 62 and a gate spacer 64 formed on the sidewalls of the corresponding main gate 62. Each main gate of the gate stacks 56, 58 and 60 includes a gate dielectric feature and a gate electrode disposed on the gate dielectric feature. The gate dielectric feature includes one or more dielectric material and the gate electrode includes one or more conductive material. The gate spacer includes one or more dielectric material.

[0022] Further referring to FIG. 2, the configuration of the dummy gate stack is described with details.

[0023] FIG. 2 is a top view of the semiconductor structure 50 of FIG. 1 in portion for simplicity. In the present embodiment, the fin-like active regions 54 are aligned in a first direction X and the gate stacks are aligned in a second direction Y perpendicular to the first direction. The dummy gate 60 includes the main gate 62 and the gate spacer 64 on the sidewalls. The main gate 62 includes a width X defined in the first direction. The gate spacer 64 includes a thickness T on each side illustrated in FIG. 2. The first fin-like active regions 54a have end portions embedded in (underlying) the dummy gate stack 60. Each embedded end portion of the first fin-like active regions 54a has a dimension ZL defined in the first direction. FIG. 7 illustrates a cross-sectional view of the semiconductor structure 50 of FIGS. 1 and 2 along line BB' of FIG. 2. The first fin-like active regions 54a are embedded in (or underlying) spacer elements 64. The spacer elements 64 are formed on the sidewall of a dummy gate stack (e.g., dummy gate stack 60). FIG. 7 depicts an end region of the first fin-line active regions 54a.

[0024] The second fin-like active regions 54b have end portions embedded in (underlying) the dummy gate stack 60. Each embedded end portion of the second fin-like active regions 54b has a dimension ZR in the second direction. The first fin-like active regions 54a and the second fin-like active regions 54b are spaced from each other in the first direction with a spacing dimension S. Various parameters defined above satisfies an equation as S1+ZL+ZR=X+2T. In one embodiment, the dimensions ZL and ZR of the embedded end portions of the fin-like active regions 54 range between about 5 nm and about 10 nm. In another embodiment, the dummy gate stack 60 has a different width than that of functional gate stack, such as the functional gate stack 56 or 58. The parameters ZL and ZR define the overlaps between the fin-like active regions (54a or 54b) and the dummy gate stack 60. The parameters ZL and ZR also define the offsets between the edges of the dummy gate stack 60 and the edges of the isolation feature underlying the dummy gate stack 60.

[0025] FIG. 3 is a sectional view of the semiconductor structure 50 taken along a dashed line AA' in FIG. 1 constructed according to one embodiment of the present disclosure. More features are illustrated in FIG. 3 with following descriptions. The semiconductor structure 50 includes functional gate stacks 56 and 58 and further includes a dummy gate stack 60 disposed between the functional gate stacks. The dummy gate 60 is formed on the isolation feature 68 and extended in the first direction X to the end portions of the fin-like active regions 54.

[0026] Various doped features are disposed in the semiconductor substrate 52 and are formed by proper technologies, such as ion implantation. For example, one or more doped wells 70 are formed in the active regions. In one embodiment, a first well 70a is formed in the first fin-like active regions 54a and a second well 70b is formed in the second fin-like active regions 54b. In furtherance of the embodiment, the first well 70a includes a p-type dopant for nFinFETs and the second well 70b includes a n-type dopant for pFinFETs.

[0027] The semiconductor structure 50 includes one or more epitaxy grown semiconductor features (epi features) 72 for strained effect to enhance the circuit performance. In one embodiment, the semiconductor structure 50 includes epi features 72a and 72b disposed on the both sides of the first functional gate 56. In another embodiment, the semiconductor structure 50 includes epi features 72c and 72d disposed on the both sides of the second functional gate 58. In the present embodiment, the epi features 72a, 72b, 72c and 72d are present. Particularly, the epi features 72a and 72b include epi grown silicon carbide with the strain effect tuned to enhance the performance of nFinFETs formed in the active regions 54a and the epi features 72c and 72d include epi grown silicon germanium with the strain effect tuned to enhance the performance of pFinFETs formed in the active regions 54b. The epi features are extended to the dummy gate stack 60 but are spaced away from the isolation feature 68, due the offset of the dummy gate 60 to the isolation feature 68.

[0028] The formation of the epi features includes etching the semiconductor substrate to form the recesses and epi growing to form the corresponding epi features, such as silicon germanium or silicon carbide. In one embodiment, epi features 72 may be grown to extrude above the surface of semiconductor substrate 52.

[0029] During the etching process to form the recesses, the recesses is offset from the isolation feature 68 by the dummy gate 60 such that the sidewalls of the isolation feature 68 are exposed, resulting in the recesses with surfaces of only semiconductor material (silicon in the present embodiment). Accordingly, the epi growth substantially occurs in the surfaces of the recesses and the faucet defect issue is eliminated.

[0030] In the existing method, the recesses expose the surfaces of the isolation feature (STI feature). The epi growth cannot grow on the surface of the isolation feature that is dielectric material, such as silicon oxide. Void defects are formed between the epi features and the isolation features. Those void defects are referred to as faucet defects. In contrast, the disclosed semiconductor structure 50 and the corresponding method eliminate the faucet defects.

[0031] The semiconductor structure 50 further includes source and drain features 74 formed in the active regions 54 (e.g., 54a and 54b) and respectively disposed on the sides of the corresponding functional gate stack (56 or 58). The source and drain features 74 include light doped drain (LDD) features substantially aligned with the corresponding main gate stack and the heavily doped source and drain (S/D) aligned with the corresponding gate spacer 64. The LDD features and the heavily doped S/D are collectively referred to as source and drain features 74. The source and drain features 74 are formed by various steps of ion implantation. In the present embodiment, the source and drain features 74 in the first active regions 54a have n-type dopant, such as phosphorous, configured to form nFinFETs. The source and drain features 74 in the second active regions 54b have p-type dopant, such as boron, configured to form pFinFETs.

[0032] The gate stacks (including the functional gate stacks 56 and 58 and the dummy gate stack 60) include the main gates 62 and the gate spacers 64. Each main gate stack 62 includes a gate dielectric feature 62a and a gate electrode 62b disposed on the gate dielectric feature 62a. The gate dielectric features 62a include one or more dielectric materials disposed on the semiconductor substrate 52. The gate electrodes 62b include one or more conductive materials. In one embodiment, the gate dielectric features 62a include silicon oxide and the gate electrodes 62b include polysilicon, formed by a procedure including deposition and patterning. The patterning includes lithography process and etch process.

[0033] In another embodiment, the gate dielectric features 62a include a high k dielectric material layer and the gate electrodes 62b include a metal layer, referred to as high k metal gates. The high k metal gates may be formed by proper procedure, such as gate-last procedure where polysilicon gate stacks are formed first and then replaced by etching, deposition and polishing. In this embodiment, the gate dielectric features 62a may additionally include an interfacial layer (IL) disposed between the semiconductor substrate and the high k dielectric material layer. The gate electrodes 62b may include a metal film of a proper work function to the respective transistors according to type (n-type or p-type) for tuned threshold voltage, therefore referred to as work function metal. In this case, the work function metal for nFinFETs are different from the work function metal for pFinFETs.

[0034] In yet another embodiment, the functional gate stacks 56 and 58 includes the high k dielectric material layer for gate dielectric and the metal layer for gate electrode but the dummy gate include silicon oxide for gate dielectric and polysilicon for gate electrode.

[0035] Referring now to FIG. 8, a configuration of an embodiment of a dummy gate stack with reference to fin-like active regions is described with details. In the present embodiment, the fin-like active regions 54 are aligned in a first direction X and the gate stacks are aligned in a second direction Y perpendicular to the first direction. The dummy gate 60 includes the main gate 62 and the gate spacer 64 on the sidewalls. The dummy gate 60 of FIG. 8 is illustrative of the embodiment discussed above providing for a width of the dummy gate 60 in the horizontal direction to be different, as illustrated greater, than the widths for active gate structures 56 and 58. In other embodiments of the device 80, the widths of the gate structures 56, 58 and/or 60 are the same, within fabrication tolerances.

[0036] The first fin-like active regions 54a have end portions embedded in (underlying) the dummy gate stack 60. In particular, the end portions of the first fin-like active regions 54a extend such that they are embedded under (or underlying) the main gate 62, and in particular under a gate electrode 62b disposed on the gate dielectric feature 62a. Each embedded end portion of the first fin-like active regions 54a has a dimension ZA defined in the first direction. FIG. 9 illustrates a cross-sectional view of the semiconductor structure 80 of FIG. 8 along line CC' of FIG. 8. The first fin-like active regions 54a are embedded (underlying) the gate feature 60 including underlying the gate dielectric 62a and the gate electrode 62b. FIG. 9 depicts an end region of the first fin-line active regions 54a.

[0037] FIGS. 11A and 11B each illustrates a cross-sectional view of the semiconductor structure 80 of FIG. 8 along line DD' of FIG. 8. FIGS. 11A and 11B are each substantially similar to as discussed above with reference to FIG. 3, with differences as noted herein. The device 80, including as represented in FIG. 11A/B, provides for a dummy gate 60 that is formed on the isolation feature 68 and extends in the first direction X to overlie end portions of the fin-like active regions 54. Specifically, the spacers 64 and gate dielectric layer 62a and gate electrode features 62b overlie the fin like active region 54. The isolation feature 68 is recessed. It is noted that using chemical mechanical polishing (CMP) processes in an embodiment, (FIG. 11B) the gate structures of devices 56, 58 and 60 have a coplanar top surface.

[0038] The second fin-like active regions 54b have end portions underlying the dummy gate stack 60. In particular, the regions 54b underlie the gate electrode 62b. Each embedded end portion of the second fin-like active regions 54b has a dimension ZB in the second direction. The first fin-like active regions 54a and the second fin-like active regions 54b are spaced from each other in the first direction with a spacing dimension S2. Various parameters defined above satisfies an equation as S2+ZA+ZB=X2+2(T2). In one embodiment, the dimensions ZA and/or ZB of the embedded end portions of the fin-like active regions 54 range between about 5 nm and about 10 nm. The dummy gate stack 60 has a different width X2 than that of functional gate stack, such as the functional gate stack 56 or 58. In other embodiments, the widths are substantially similar, within manufacturing process tolerances. The parameters ZA and ZB define the overlap between the fin-like active regions (54a or 54b respectively) and the dummy gate stack 60. The parameters ZA and ZB also define the offsets between the edges of the dummy gate stack 60 and the edges of the isolation feature underlying the dummy gate stack 60.

[0039] FIG. 4 is a flowchart of a method 100 forming the semiconductor structure 50 constructed according to aspects of the present disclosure according to one or more embodiments. The method 100 is described with reference to FIGS. 1 through 4.

[0040] The method 100 begins at step 102 by providing a semiconductor substrate 52. The semiconductor substrate 52 includes silicon or alternatively other suitable semiconductor material.

[0041] The method 100 proceeds to step 104 by forming fin-like active regions 54. In one embodiment, the fin-like active regions 54 are formed by a procedure including forming STI features to define the areas for the active regions, and etching back the STI features such that the active regions are extruded to form the fin-like active regions 54.

[0042] In furtherance of the embodiment, a more detailed procedure for the formation of the fin-like active regions 54 is provided below with reference to FIG. 5 as a flowchart of forming the fin-lie active regions according to various embodiments.

[0043] At step 112, a hard mask is formed on the semiconductor substrate. In one example, the hard mask includes a silicon oxide film (pad oxide) and a silicon nitride film on the pad oxide. The hard mask layer may be formed by a proper techniques. In one example, silicon oxide is formed by thermal oxidation and silicon nitride is formed by chemical vapor deposition (CVD).

[0044] At step 114, the hard mask layer is patterned to form various openings. The patterned hard mask layer define the areas for isolation features and areas for active regions. Particularly, the openings of the patterned hard mask layer define the areas for the isolation features. The hard mask layer is patterned by lithography process and etching process.

[0045] To reduce the line end shortening and corner rounding issues, two photomasks are used to pattern the hard mask layer. The first photomask defines fin lines and the second photomask defines line end cut patterns and creates end-to-end spacing. As illustrated in FIG. 6 as a top view of the hard mask layer, the first photomasks defines fin features 126 and the second photomask defines line end cut patterns 128 to form the fin-like active regions 54 of the semiconductor structure 50. In one example, the first photomask defines the fin features aligned in a first direction X and the second photomask defines the line end cut feature 128 aligned in a second direction Y perpendicular to the first direction X.

[0046] In one embodiment, the two photomasks are utilized in a double exposure procedure. A photoresist layer is coated on the hard mask layer. Two exposures are implemented sequentially with the first and second photomasks, respectively. Then the double exposed photoresist layer is developed to form a patterned photoresist layer with openings defined therein. An etching process follows to etch the hard mask layer through the openings of the patterned photoresist layer. The lithography process may include other steps, such as soft baking post-exposure baking and/or hard baking. The etching process may include two etch steps to respectively etch silicon nitride and silicon oxide.

[0047] In another embodiment, the two photomasks are utilized in a double exposure and double etching procedure. A first photoresist layer is patterned (coating, exposure and developing) using the first photomask. Then an etching process follows to etch the hard mask layer through the openings of the first photoresist layer. Similarly, a second photoresist layer is patterned using the second photomask. Then an etching process follows to etch the hard mask layer through the openings of the second photoresist layer.

[0048] At step 116, the semiconductor substrate is etched through the openings of the hard mask layer, forming trenches in the semiconductor trenches. The pattern of the hard mask layer is transferred to the semiconductor substrate.

[0049] At step 118, the trenches of the semiconductor substrate are filled with one or more dielectric materials to form shallow trench isolation (STI) features. In one embodiment, the shallow trench isolation features include silicon oxide. The silicon oxide can be filled in the trenches by a CVD process. In various examples, the silicon oxide can be formed by a high density plasma chemical vapor deposition (HDPCVD). The silicon oxide may be alternatively formed by a high aspect ratio process (HARP). In another embodiment, the trench isolation features may include a multi-layer structure. In furtherance of the embodiment, the STI features include other suitable materials, such as silicon nitride or silicon oxynitride.

[0050] In one embodiment, a polishing process, such as chemical mechanical polishing (CMP), is followed to remove the excessive dielectric material on the semiconductor substrate and planarize the surface.

[0051] At step 120, the STI features are etched back such that the STI features are recessed and the semiconductor portions (silicon portions) are extruded relative to the recessed STI features, resulting in fin-like active regions. Accordingly, the top surface of the STI features is lower than the top surface of the fin-like active regions.

[0052] Referring back to FIG. 4, after the formation of the fin-like active regions at step 104, the method 100 proceeds to step 106 by forming gate stacks, including the functional gate stacks (56 and 58) and the dummy gate stack 60. As illustrated in FIG. 3, the gate stacks (including the functional gate stacks 56 and 58 and the dummy gate stack 60) include the main gates 62 and the gate spacers 64. Each main gate stack 62 includes a gate dielectric feature 62a and a gate electrode 62b disposed on the gate dielectric feature 62a. In various embodiments, the gate stacks may include polysilicon or metal for gate electrode and may include silicon oxide and/or high k dielectric material for gate dielectric. When the gate stacks include high k dielectric and metal (referred to as high k metal gates), the formation of the high k metal gates may implement gate-first process where the high k dielectric material and metal directly deposited and patterned at this step. Alternatively, high k metal gates may be formed by other techniques, such as gate-last process or high-k-last process in various embodiments.

[0053] The method 100 proceeds to step 108 by forming source and drain features 74 in the active regions 54 (e.g., 54a and 54b). The source and drain features are respectively disposed on the sides of the corresponding functional gate stack (56 or 58). In one embodiment, the source and drain features 74 include light doped drain (LDD) features substantially aligned with the corresponding main gate stack and the heavily doped source and drain (S/D) aligned with the corresponding gate spacer 64. The source and drain features 74 are formed by proper technique (such as ion implantation) and are followed by thermal anneal for activation. In the present embodiment, the source and drain features 74 in the first active regions 54a include n-type dopant configured to form nFinFETs. The source and drain features 74 in the second active regions 54b include p-type dopant configured to form pFinFETs.

[0054] The formation of the gate stacks and the formation of the source and drain features are integrated in one procedure. For example, the heavily doped source and drain are formed after the formation of the gate spacer. One embodiment of the procedure to form gate stacks and the source/drain features is described below.

[0055] The gate material layers are formed on the substrate and patterned to form gate stacks. The gate material layers include an interfacial layer (such as silicon oxide) and a high k dielectric material disposed on the interfacial layer and a polysilicon layer on the high k dielectric material layer. The patterning technique includes lithography process and etching. A hard mask may be utilized as an etch mask to pattern the gate material layers.

[0056] The LDD features are then formed by ion implantation and may be followed by thermal anneal for activation. The gate spacers are formed on the sidewalls of the gate stacks by deposition and dry etch. Particularly, the dummy gate stack 60 (including gate spacer) is formed to land on the STI feature 68 and is extended to cover end portions of the fin-like active regions 54. In the present embodiment illustrated in FIGS. 1 and 2, the dummy gate 60 covers the end portions of the fin-like active regions 54a on one side and covers the end portions of the fin-like active regions 54b on another side. In the embodiment illustrated in FIG. 10, the ends of the fin-like active structures 54a are embedded under the dummy gate stack 60.

[0057] The semiconductor substrate is then etched to form recesses. In the present embodiment, silicon substrate is etched using a proper etchant. The recesses are formed in the silicon substrate and are separated from the STI feature 68 by silicon. The offsets between the edge of the STI feature 68 and the edge of the dummy gate stack 60 are ZL and ZR, respectively, as illustrated in FIG. 2. The offsets ZL and ZR are designed to be enough such that the recesses cannot reach and expose the STI feature 68. For example, using the examples of FIGS. 2, 8, and 10, the recesses are formed in the fin-like active regions 54a between the gate features.

[0058] Then the epitaxy growth (or epi growth) is implemented to form epi grown features of a semiconductor material different from the substrate to achieve proper strain effect for enhanced channel mobility. In one embodiment, the silicon germanium is epi grown in the recesses for pFinFETs. In another embodiment, the silicon carbide is epi grown in the recesses for nFinFETs.

[0059] The epi growth may grow the epi features substantially coplanar with the surface of the silicon surface or alternatively higher than the silicon surface such that the epi features are extruded out. Heavily doped source and drain are formed by ion implantation after the epitaxy growth.

[0060] In another embodiment, the gate spacer used for recess etching is removed and a second gate spacer is formed on the sidewalls of the gate stack. Thus, the second gate spacer is tuned to offset the heavily doped source and drain while the first gate spacer is tuned to offset the overlap of the fin end and the dummy gate stack.

[0061] In yet another embodiment, heavily doped source and drain are formed during the epi growth wherein the epi features are in situ doped during the epi growth. The precursor of the ep growth includes chemical to introduce the dopant simultaneously during the epi growth.

[0062] Other processing steps may be implemented before, during and/or after the method 100. In one embodiment, an interlayer dielectric (ILD) layer is formed on the substrate and the gate stack. The ILD layer is deposited by a proper technique, such as CVD. The ILD includes a dielectric material, such as silicon oxide, low k dielectric material or a combination. Then a chemical mechanical polishing (CMP) process may be applied thereafter to polarize the surface of the ILD. In one example, the gate stack is exposed by the CMP process for the subsequent processing steps. In the gate-last process to form high k metal gates, the polysilicon layer is replaced by one or more metals after the formation of the ILD layer. More specifically, the polysilicon layer in the gate stacks is removed by etching, resulting in gate trenches. Then the gate trenches are filled by one or more metal materials, forming metal gate stacks. In the present embodiment, a first metal having a proper work function is deposited in the gate trenches and a second metal is disposed on the first metal to fill the gate trenches. The first metal is also referred to as work function metal. The second metal may include aluminum or tungsten.

[0063] In the high-k-last process, both the gate dielectric and the polysilicon are removed by etching. Afterward, the high k dielectric material and metal are then filled in to form high k metal gate stacks.

[0064] In another example, an interconnect structure is further formed on the substrate and is designed to couple various transistors and other devices to form a functional circuit. The interconnect structure includes various conductive features, such as metal lines for horizontal connections and contacts/vias for vertical connections. The various interconnect features may implement various conductive materials including copper, tungsten and silicide. In one example, a damascene process is used to form copper-based multilayer interconnect structure. In another embodiment, tungsten is used to form tungsten plug in the contact holes.

[0065] Although not shown, other features and the processing steps making these features may present, including various device features such as silicide for contact, and multilayer interconnection (MLI). In one example, the silicide contact layer includes nickel silicide, cobalt silicide, tungsten silicide, tantalum silicide, titanium silicide, platinum silicide, erbium silicide, palladium silicide, or combinations thereof. The gate spacers may have a multilayer structure and may include silicon oxide, silicon nitride, silicon oxynitride, or other dielectric materials.

[0066] Although embodiments of the present disclosure have been described in detail, those skilled in the art should understand that they may make various changes, substitutions, and alterations herein without departing from the spirit and scope of the present disclosure. For example, the semiconductor structure 50 includes fin-like active regions. However, the present disclosure is also applicable to a two-dimensional circuit wherein the active regions and the STI features are substantially coplanar. The overlap between the dummy gate stack and the end portion of the active regions, as disclosed, can be implemented to reduce the faucet defects when the epi features are incorporated in the field effect transistors for strain effect. In another example, the dummy gate 60 has a width different from the functional gate stack such that the overlap between the dummy gate and the active regions is tuned to effectively prevent the faucet issue. In yet another example, the dummy gate may include different materials, such as silicon oxide and polysilicon while the functional gate stacks include high k dielectric material and metal. In yet another embodiment, only silicon germanium epi features are formed in the pFinFETs while the nFinFETs have source and drain features formed in the silicon substrate.

[0067] Thus, the present disclosure provides a semiconductor structure. The semiconductor structure includes a semiconductor substrate; an isolation feature formed in the semiconductor substrate; a first active region and a second active region formed in the semiconductor substrate, wherein the first and second active regions extend in a first direction and are separated from each other by the isolation feature; and a dummy gate disposed on the isolation feature, wherein the dummy gate extends in the first direction to the first active region from one side and to the second active region from another side.

[0068] In one embodiment, the semiconductor structure further includes a first functional gate disposed on the first active region and configured to form a first field effect transistor; and a second functional gate disposed on the second active region and configured to form a second field effect transistor.

[0069] In another embodiment, the semiconductor structure further includes first epitaxy features formed on the first active region and interposed by the first functional gate stack. In yet another embodiment, the semiconductor substrate includes silicon; the first epitaxy features include silicon germanium; and the first field transistor includes one of a p-type field effect transistor and a n-type field effect transistor, wherein the first epitaxy features are separated from the dummy gate by a portion of the semiconductor substrate.

[0070] In another embodiment, the semiconductor structure further includes second epitaxy features formed on the second active region and interposed by the second functional gate stack. In yet another embodiment, the second epitaxy features include silicon carbide; and the second field transistor includes another one of the p-type field effect transistor and n-type field effect transistor, wherein the second epitaxy features are separated from the dummy gate by another portion of the semiconductor substrate.

[0071] In yet another embodiment, the first and second functional gates each include a high k dielectric material layer and a metal layer on the high k dielectric material layer.

[0072] In yet another embodiment, the isolation feature is a shallow trench isolation (STI) feature extending a first dimension S1 in the first direction. In another embodiment, the first active region and the second active region are fin-like active regions aligned in the first direction; and the dummy gate aligned in a second direction perpendicular to the first direction and spanning a second dimension S2 in the first direction, wherein the second dimension is greater than the first dimension.

[0073] In yet another embodiment, the dummy gate extends to the first active region with a first overlap dimension Z1 in the first direction; and the dummy gate extends to the second active region with a second overlap dimension Z2 in the first direction, wherein the S1, S2, Z1 and Z2 are related in a formula S2=S1+Z1+Z2. In yet another embodiment, the dummy gate includes a main gate stack and a gate spacer disposed on both sides of the main gate stack; the main gate stack has a width W in the first direction and the gate spacer has a thickness T; and the second dimension S2 is equal to W+2T.

[0074] The present disclosure also provides another embodiment of a semiconductor structure. The semiconductor structure includes a silicon substrate; first plurality of fin-like active regions formed in the silicon substrate and oriented in a first direction; second plurality of fin-like active regions formed in the silicon substrate and oriented in the first direction; a shallow trench isolation (STI) feature formed in the silicon substrate and interposed between the first fin-like active regions and the second fin-like active regions; and a dummy gate disposed on the STI feature, wherein the dummy gate extends in the first direction to overlap with the first fin-like active regions from one side and to overlap with the second fin-like active regions from another side.

[0075] In one embodiment of the semiconductor structure, the first fin-like active regions each include a first end contacting the STI feature and the second fin-like active regions each include a second end contacting the STI feature.

[0076] In another embodiment, the STI feature spans a first dimension S1 in a first direction; the first ends and the second ends have a first distance in the first direction, wherein the first distance is equal to the first dimension S1; and the dummy gate spans a second dimension S2 in the first direction, S2 being greater than S1.

[0077] In yet another embodiment, the dummy gate overlaps with the first fin-like active regions of a first overlap dimension Z1 in the first direction; the dummy gate overlaps with the second fin-like active regions of a second overlap dimension Z2 in the first direction; and S1, S2, Z1 and Z2 are related in a formula S2=S1+Z1+Z2.

[0078] In yet another embodiment, the STI feature includes a top surface lower than top surfaces of the first and second fin-like active regions.

[0079] The present disclosure also provides an embodiment of a method that includes forming an isolation feature in a semiconductor substrate; forming a first fin-like active region and a second fin-like active region in the semiconductor substrate and interposed by the isolation feature; forming a dummy gate stack on the isolation feature, wherein the dummy gate extends to the first fin-like active region from one side and to the second fin-like active region from another side.

[0080] In one embodiment, the method further includes forming epitaxy grown source and drain features in the first fin-like active region. In another embodiment, the forming of the dummy gate stack includes forming a first gate having polysilicon and replacing the polysilicon with metal.

[0081] In yet another embodiment, the forming of the isolation feature and the forming of the first fin-like active region and the second fin-like active region include forming a hard mask using a first photomask defining an active region and a second photomask defining a cut feature, wherein the hard mask includes openings defining the first and second fin-like active regions.

[0082] In another of the broader embodiments, provided is a semiconductor structure. The structure includes an isolation feature formed in the semiconductor substrate. A first fin-type active region is formed in the semiconductor substrate. The first fin-type active region extends in a first direction. A dummy gate stack disposed on an end region of the first fin-type active region.

[0083] In another of the broader embodiments, a semiconductor device including a first plurality of fin-like active regions, an STI feature, and a dummy gate is provided. The first plurality of fin-like active regions is formed in the silicon substrate and oriented in a first direction. The shallow trench isolation (STI) feature is formed in the silicon substrate and interfaces with an end region of each of the first fin-like active regions. A dummy gate is disposed on the STI feature. The dummy gate extends in the second direction to overlap with the end region of each of the first fin-like active regions.

[0084] Also described is a method, including forming an isolation feature in a semiconductor substrate. A first fin-like active region is formed in the semiconductor substrate and contacts the isolation feature. A dummy gate stack is formed on an end region of the isolation feature. The dummy gate extends above the first fin-like active region. A functional gate stack is formed on a first region of the first fin-like active region.

[0085] The foregoing has outlined features of several embodiments so that those skilled in the art may better understand the aspects of the present disclosure. Those skilled in the art should appreciate that they may readily use the present disclosure as a basis for designing or modifying other processes and structures for carrying out the same purposes and/or achieving the same advantages of the embodiments introduced herein. Those skilled in the art should also realize that such equivalent constructions do not depart from the spirit and scope of the present disclosure, and that they may make various changes, substitutions and alterations herein without departing from the spirit and scope of the present disclosure.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

D00009

D00010

D00011

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.