Semiconductor Structure And Manufacturing Method Thereof

HO; POKUAN ; et al.

U.S. patent application number 16/254007 was filed with the patent office on 2020-01-30 for semiconductor structure and manufacturing method thereof. The applicant listed for this patent is TAIWAN SEMICONDUCTOR MANUFACTURING COMPANY LTD.. Invention is credited to CHENG-CHI CHUANG, POKUAN HO, CHIA-TIEN WU.

| Application Number | 20200035612 16/254007 |

| Document ID | / |

| Family ID | 69177478 |

| Filed Date | 2020-01-30 |

View All Diagrams

| United States Patent Application | 20200035612 |

| Kind Code | A1 |

| HO; POKUAN ; et al. | January 30, 2020 |

SEMICONDUCTOR STRUCTURE AND MANUFACTURING METHOD THEREOF

Abstract

A semiconductor structure includes a first dielectric layer; a first conductive member extended through and surrounded by the first dielectric layer; a first protective layer disposed over the first dielectric layer and the first conductive member; a second dielectric layer disposed over the first protective layer; a third dielectric layer disposed over the second dielectric layer; and a second conductive member disposed over the first dielectric layer and the first conductive member, and surrounded by the first protective layer, the second dielectric layer and the third dielectric layer, wherein the second conductive member includes a first portion and a second portion disposed over and coupled with the first portion, the first portion is extended through and surrounded by the first protective layer and the second dielectric layer, the second portion is surrounded by the third dielectric layer.

| Inventors: | HO; POKUAN; (TAIPEI CITY, TW) ; WU; CHIA-TIEN; (TAICHUNG CITY, TW) ; CHUANG; CHENG-CHI; (NEW TAIPEI CITY, TW) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 69177478 | ||||||||||

| Appl. No.: | 16/254007 | ||||||||||

| Filed: | January 22, 2019 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 62711098 | Jul 27, 2018 | |||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 21/76811 20130101; H01L 23/5226 20130101; H01L 21/76834 20130101; H01L 21/76879 20130101; H01L 21/76832 20130101; H01L 21/76847 20130101; H01L 21/76813 20130101; H01L 21/76804 20130101; H01L 21/76877 20130101; H01L 23/53295 20130101; H01L 21/76802 20130101 |

| International Class: | H01L 23/532 20060101 H01L023/532; H01L 21/768 20060101 H01L021/768; H01L 21/033 20060101 H01L021/033; H01L 23/528 20060101 H01L023/528 |

Claims

1. A semiconductor structure, comprising: a first dielectric layer; a first conductive member extended through and surrounded by the first dielectric layer; a first protective layer disposed over the first dielectric layer and the first conductive member; a second dielectric layer disposed over the first protective layer; a third dielectric layer disposed over the second dielectric layer; and a second conductive member disposed over the first dielectric layer and the first conductive member, and surrounded by the first protective layer, the second dielectric layer and the third dielectric layer, wherein the second conductive member includes a first portion and a second portion disposed over and coupled with the first portion, the first portion is extended through and surrounded by the first protective layer and the second dielectric layer, the second portion is surrounded by the third dielectric layer, at least a portion of the second dielectric layer is disposed between the first protective layer and the second portion of the second conductive member.

2. The semiconductor structure of claim 1, wherein a first width of the first portion of the second conductive member is substantially less than a second width of the second portion of the second conductive member.

3. The semiconductor structure of claim 1, wherein at least a portion of the second portion of the second conductive member is protruded from the first portion of the second conductive member.

4. The semiconductor structure of claim 1, wherein the second portion of the second conductive member is tapered towards the first portion of the second conductive member.

5. The semiconductor structure of claim 1, wherein the first portion of the second conductive member is tapered towards the first conductive member.

6. The semiconductor structure of claim 1, wherein the first portion of the second conductive member is disposed above the first conductive member.

7. The semiconductor structure of claim 1, wherein the first portion of the second conductive member is disposed above the first conductive member and the first dielectric layer.

8. The semiconductor structure of claim 1, further comprising a second protective layer disposed between the second dielectric layer and the third dielectric layer, wherein the second protective layer surrounds the second portion of the second conductive member.

9. The semiconductor structure of claim 8, wherein the first protective layer and the second protective layer include nitride.

10. The semiconductor structure of claim 1, wherein the second conductive member includes a third portion surrounded by the third dielectric layer, disposed over and coupled with the second portion of the second conductive member.

11. The semiconductor structure of claim 10, wherein a third width of the third portion of the second conductive member is substantially greater than a first width of the first portion of the second conductive member and a second width of the second portion of the second conductive member.

12. A semiconductor structure, comprising: a first dielectric layer; a first conductive member extended through and surrounded by the first dielectric layer; a first protective layer disposed over the first dielectric layer and the first conductive member; a second dielectric layer disposed over the first protective layer; a second protective layer disposed over the second dielectric layer; a third dielectric layer disposed over the second dielectric layer; a second conductive member disposed over the first dielectric layer and the first conductive member, and surrounded by the first protective layer, the second dielectric layer, the second protective layer and the third dielectric layer; and a third conductive member disposed over the second conductive member and surrounded by the third dielectric layer, wherein the second conductive member includes a first portion and a second portion disposed over and coupled with the first portion, the first portion is extended through and surrounded by the first protective layer and the second dielectric layer, the second portion is surrounded by the third dielectric layer, at least a portion of the second dielectric layer is disposed between the first protective layer and the second portion of the second conductive member.

13. The semiconductor structure of claim 12, wherein a curved interface is disposed between the second portion of the second conductive member and the third conductive member.

14. The semiconductor structure of claim 12, wherein the second portion of the second conductive member includes a convex surface curving towards the third conductive member.

15. The semiconductor structure of claim 12, wherein the third conductive member includes a concave surface curving away from the second conductive member.

16. The semiconductor structure of claim 12, wherein the second portion of the second conductive member is protruded from the first portion of the second conductive member in a length of about 3 .ANG. to about 150 .ANG..

17. The semiconductor structure of claim 12, further comprising a barrier layer surrounding the third conductive member, disposed over the second portion of the second conductive member and separating the third conductive member from the second conductive member.

18. A method of manufacturing a semiconductor structure, comprising: providing a first dielectric layer and a first conductive member surrounded by the first dielectric layer; disposing a first protective layer over the first dielectric layer and the first conductive member; disposing a second dielectric layer over the first protective layer; disposing a second protective layer over the second dielectric layer; disposing a third dielectric layer over the second protective layer; removing a first portion of the third dielectric layer to form a first opening; removing a first portion of the second protective layer exposed by the first opening; removing a second portion of the third dielectric layer to form a second opening; removing a first portion of the second dielectric layer exposed from the second protective layer to form a third opening; removing a portion of the first protective layer exposed by the third opening and a second portion of the second protective layer exposed by the second opening; and disposing a conductive material into the second opening and the third opening to form a second conductive member.

19. The method of claim 18, wherein a first width of the first opening is substantially less than a second width of the second opening, and the first width is substantially the same as a third width of the third opening.

20. The method of claim 18, wherein a second portion of the second dielectric layer is exposed by the second opening after the removal of the second portion of the second protective layer.

Description

PRIORITY CLAIM AND CROSS-REFERENCE

[0001] This application claims the benefit of a provisional application Ser. 62/711,098 filed on Jul. 27, 2018, entitled "SEMICONDUCTOR STRUCTURE AND MANUFACTURING METHOD THEREOF," the disclosure of which is hereby incorporated by reference in its entirety.

BACKGROUND

[0002] Electronic equipments using semiconductor devices are essential for many modern applications. With the advancement of electronic technology, the semiconductor devices are becoming small in size while having many complicated integrated circuitries. Due to the miniaturized scale of the semiconductor device, many semiconductor components are assembled on the semiconductor device. Furthermore, numerous manufacturing operations are implemented within such a small semiconductor device.

[0003] However, the manufacturing operations of the semiconductor device involve many steps and operations on such a small and thin semiconductor device. The manufacturing of the semiconductor device in a miniaturized scale becomes more complicated. An increase in a complexity of manufacturing the semiconductor device may cause deficiencies such as poor electrical interconnection, misalignment of components or other issues, resulting in a high yield loss of the semiconductor device. The semiconductor device is produced in an undesired configuration, which would further exacerbate materials wastage and thus increase the manufacturing cost.

[0004] Since more different small components are involved, a complexity of the manufacturing operations of the semiconductor device is increased. As such, there is a continuous need to modify a structure of the semiconductor devices and improve the manufacturing operations of the semiconductor devices.

BRIEF DESCRIPTION OF THE DRAWINGS

[0005] Aspects of the present disclosure are best understood from the following detailed description when read with the accompanying figures. It is emphasized that, in accordance with the standard practice in the industry, various features are not drawn to scale. In fact, the dimensions of the various features may be arbitrarily increased or reduced for clarity of discussion.

[0006] FIG. 1 is a schematic cross sectional view of a semiconductor structure in accordance with some embodiments of the present disclosure.

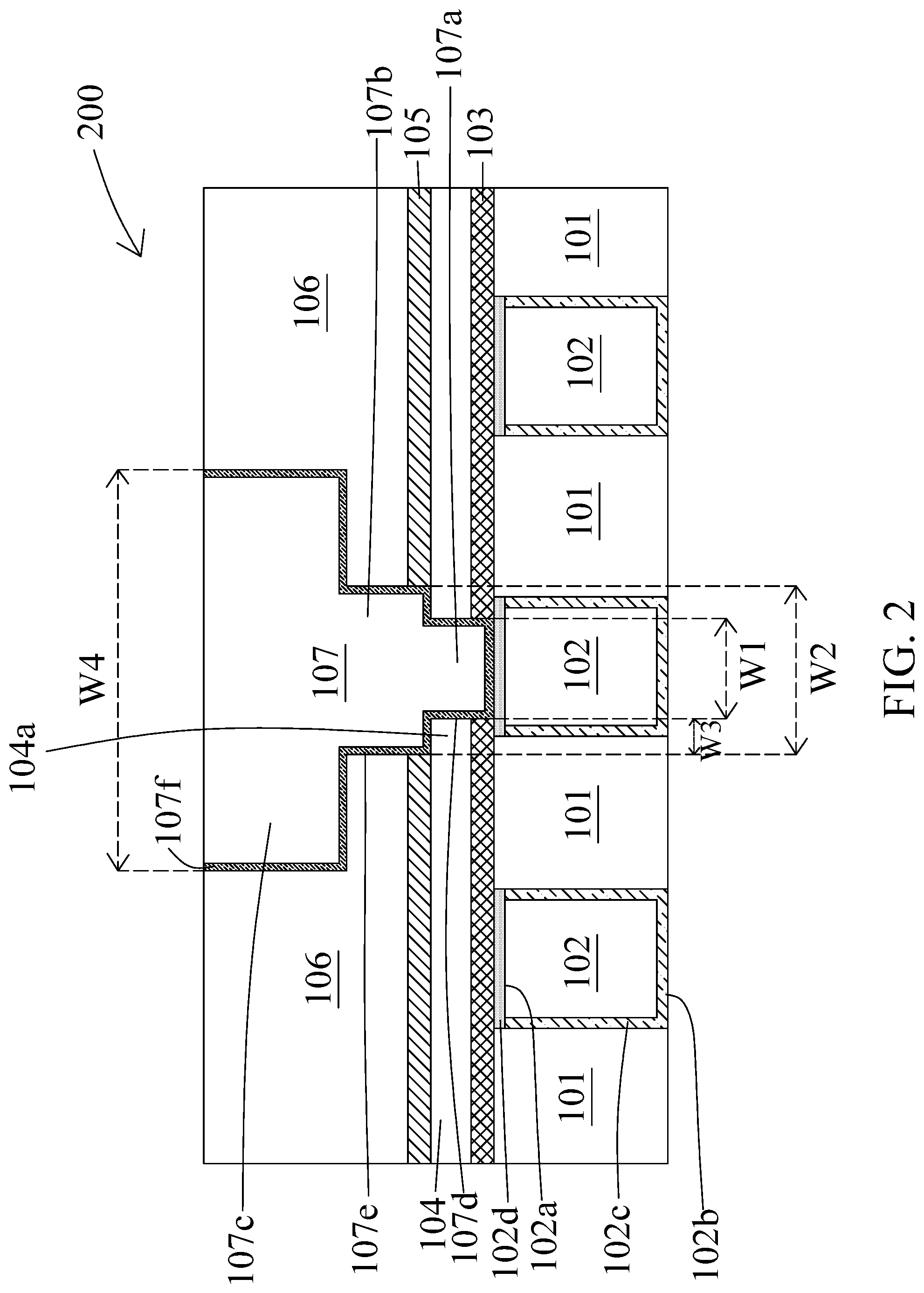

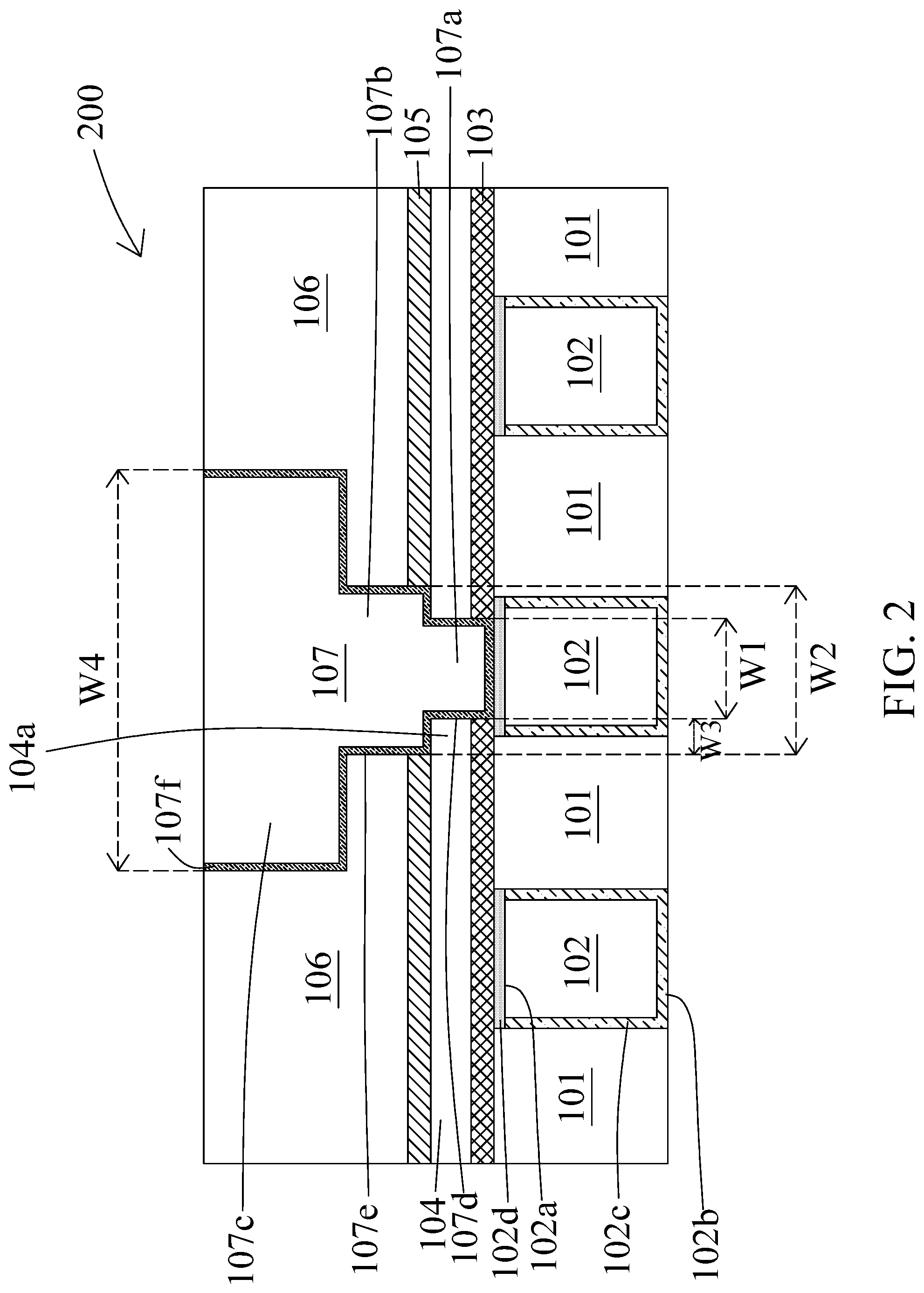

[0007] FIG. 2 is a schematic cross sectional view of a semiconductor structure in accordance with some embodiments of the present disclosure.

[0008] FIG. 3 is a schematic cross sectional view of a semiconductor structure in accordance with some embodiments of the present disclosure.

[0009] FIG. 4 is a schematic cross sectional view of a semiconductor structure in accordance with some embodiments of the present disclosure.

[0010] FIG. 5 is a flow diagram of a method of manufacturing a semiconductor structure in accordance with some embodiments of the present disclosure.

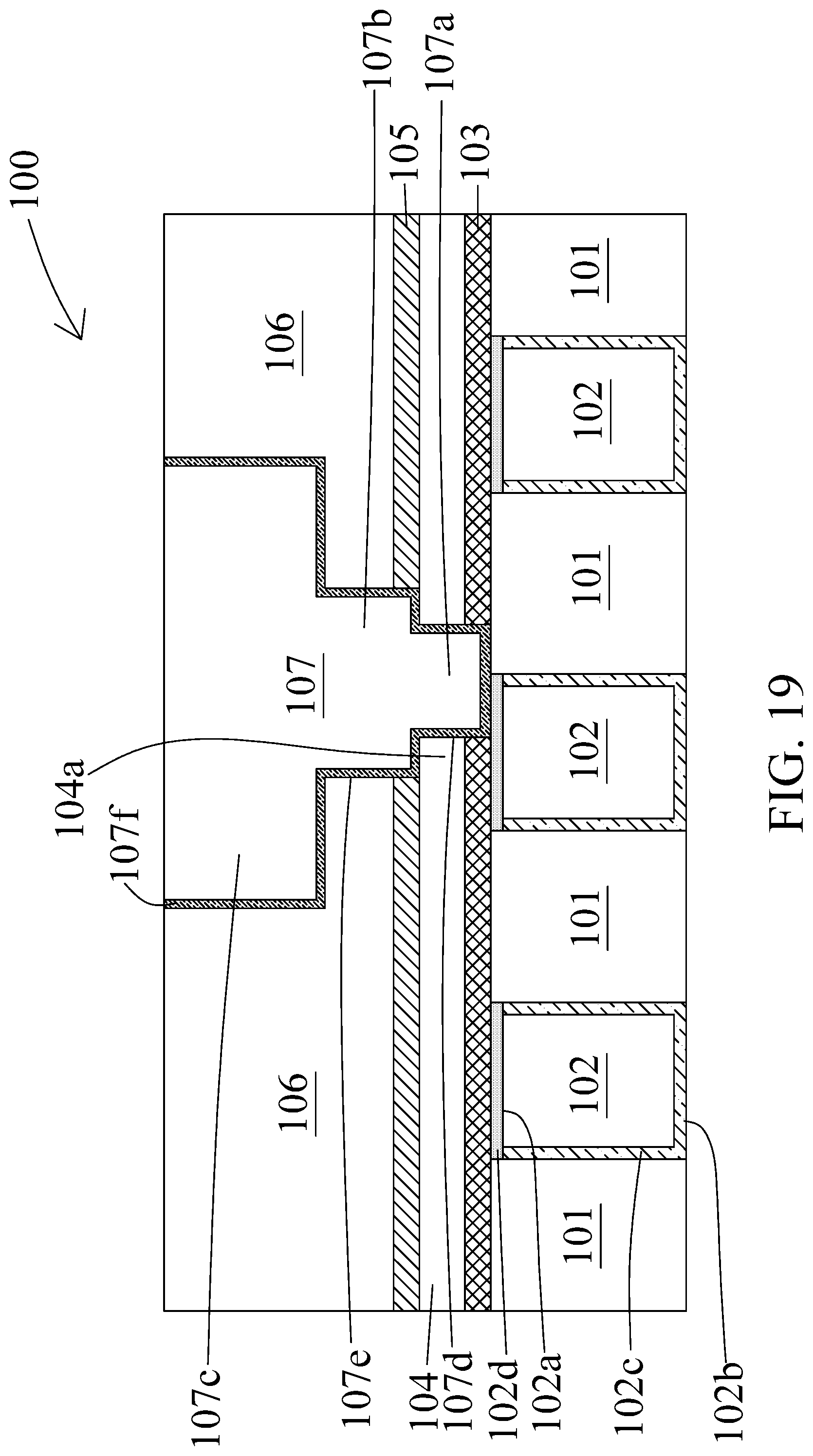

[0011] FIGS. 6-19 are schematic views of manufacturing a semiconductor structure by a method of FIG. 5 in accordance with some embodiments of the present disclosure.

[0012] FIG. 20 is a flow diagram of a method of manufacturing a semiconductor structure in accordance with some embodiments of the present disclosure.

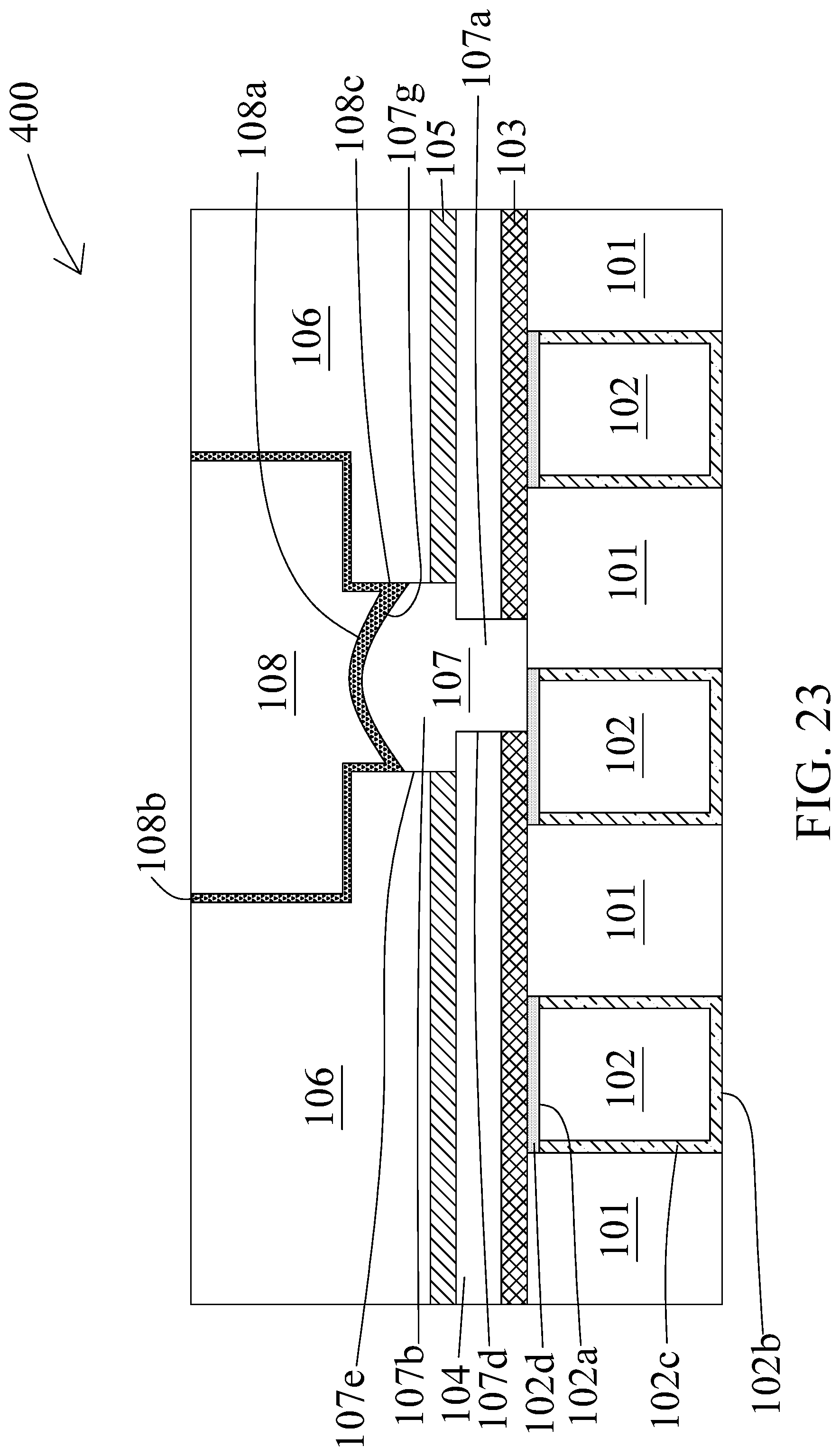

[0013] FIGS. 6-17 and 21-23 are schematic views of manufacturing a semiconductor structure by a method of FIG. 20 in accordance with some embodiments of the present disclosure.

DETAILED DESCRIPTION OF THE DISCLOSURE

[0014] The following disclosure provides many different embodiments, or examples, for implementing different features of the provided subject matter. Specific examples of components and arrangements are described below to simplify the present disclosure. These are, of course, merely examples and are not intended to be limiting. For example, the formation of a first feature over or on a second feature in the description that follows may include embodiments in which the first and second features are formed in direct contact, and may also include embodiments in which additional features may be formed between the first and second features, such that the first and second features may not be in direct contact. In addition, the present disclosure may repeat reference numerals and/or letters in the various examples. This repetition is for the purpose of simplicity and clarity and does not in itself dictate a relationship between the various embodiments and/or configurations discussed.

[0015] Further, spatially relative terms, such as "beneath," "below," "lower," "above," "upper" and the like, may be used herein for ease of description to describe one element or feature's relationship to another element(s) or feature(s) as illustrated in the figures. The spatially relative terms are intended to encompass different orientations of the device in use or operation in addition to the orientation depicted in the figures. The apparatus may be otherwise oriented (rotated 90 degrees or at other orientations) and the spatially relative descriptors used herein may likewise be interpreted accordingly.

[0016] An interconnect structure is involved in a semiconductor structure. The interconnect structure includes several conductive vias extended through one or more layers of the semiconductor structure and connected with conductive lines extended over one of layers of the semiconductor structure. The conductive vias extended through different layers and connects the conductive lines at different layers of the semiconductor structure. However, an overall size of the semiconductor structure becomes smaller and smaller. As such, an overlay issue may occur between two conductive vias disposed over each other. The conductive vias may not be disposed accurately and thus may not vertically align with each other. Further, a space between neighboring conductive vias also becomes smaller and smaller. Therefore, the neighboring conductive vias at the same layer may be easily bridged by the conductive via disposed at the above layer, which leads to failure of electrical connection. As a result, reliability of the semiconductor structure would be adversely affected.

[0017] In the present disclosure, a semiconductor structure is disclosed. The semiconductor structure includes a first conductive member surrounded by a first dielectric layer, and a second conductive member disposed over the first conductive member and surrounded by a second dielectric layer and a third dielectric layer. The second conductive member includes a first portion and a second portion disposed over and coupled with the first portion. The first portion is extended through and surrounded by the second dielectric layer, and the second portion is surrounded by the third dielectric layer.

[0018] A contour of the second conductive member with a step is formed by the first portion and the second portion of the second conductive member. A width of the first portion is substantially less than a width of the second portion. The second conductive member with the step contour can increase a clearance between the second conductive member and a conductive member neigbouring with the first conductive member. Therefore, undesirable contact with the conductive member neigbouring with the first conductive member can be prevented.

[0019] Further, a method of manufacturing a semiconductor structure is disclosed. The method includes providing a first dielectric layer and a first conductive member surrounded by the first dielectric layer; disposing a first protective layer over the first dielectric layer and the first conductive member; disposing a second dielectric layer over the first protective layer; disposing a second protective layer over the second dielectric layer; disposing a third dielectric layer over the second protective layer; removing a portion of the second dielectric layer; removing a portion of the third dielectric layer; and disposing a conductive material to form a second conductive member. The second conductive member includes a first portion surrounded by the second dielectric layer and a second portion surrounded by the third dielectric layer.

[0020] A width of the first portion is substantially less than a width of the second portion. As such, a step contour of the second dielectric layer and the third dielectric layer is formed by the removal of the portion of the second dielectric layer and the portion of the third dielectric layer. As a result, a clearance between the second conductive member and a conductive member neigbouring with the first conductive member can be increased.

[0021] FIG. 1 is a schematic cross sectional view of a semiconductor structure 100 in accordance with various embodiments of the present disclosure. In some embodiments, the semiconductor structure 100 includes a first dielectric layer 101, a first conductive member 102, a first protective layer 103, a second dielectric layer 104, a second protective layer 105, a third dielectric layer 106 and a second conductive member 107. In some embodiments, the semiconductor structure 100 is a part of a wafer, a die or a package. In some embodiments, the semiconductor structure 100 is configured to connect with another semiconductor structure such as a die, a package, a printed circuit board (PCB) or the like.

[0022] In some embodiments, the semiconductor structure 100 includes a substrate under the first dielectric layer 101 and the first conductive member 101. In some embodiments, the substrate includes semiconductive materials such as silicon or other suitable materials. In some embodiments, the substrate is a silicon substrate or silicon wafer.

[0023] In some embodiments, the first dielectric layer 101 surrounds the first conductive member 102. In some embodiments, the first dielectric layer 101 includes a low dielectric constant (k) material such as silicon oxide (SiO), porous organosilicate (SiOCH), borophosphosilicate glass (BPSG), phosphosilicate glass (PSG) or the like.

[0024] In some embodiments, the first conductive member 102 is extended through and surrounded by the first dielectric layer 101. In some embodiments, the first conductive member 102 includes a first surface 102a and a second surface 102b opposite to the first surface 102a. In some embodiments, the first conductive member 102 is extended between the first surface 102a and the second surface 102b. In some embodiments, the first conductive member 102 includes conductive material such as copper (Cu), aluminum (Al), cobalt (Co), titanium (Ti), tungsten (W), ruthenium (Ru), molybdenum (Mo), iridium (Ir), rhodium (Rh) or the like.

[0025] In some embodiments, the second surface 102b of the first conductive member 102 is exposed. In some embodiments, the second surface 102b is configured to receive a conductive line or a conductive structure to connect a circuitry of the semiconductor structure 100 with a circuitry of another semiconductor structure. In some embodiments, a height of the first conductive member 102 is substantially the same as a thickness of the first dielectric layer 101. In some embodiments, the height of the first conductive member 102 and the thickness of the first dielectric layer 101 are respectively about 50 .ANG. to about 500 .ANG..

[0026] In some embodiments, a first barrier layer 102c surrounds the first conductive member 102. In some embodiments, the first barrier layer 102c is a diffusion barrier layer. In some embodiments, the first barrier layer 102c is configured to prevent diffusion from the first conductive member 102 to the first dielectric layer 101 and provide adhesion between the first conductive member 102 and the first dielectric layer 101. In some embodiments, the first barrier layer 102c is disposed between the first conductive member 102 and the first dielectric layer 101. In some embodiments, the first barrier layer 102c includes tungsten (W), titanium (Ti), aluminum (Al), copper (Cu), tantalum (Ta) or the like.

[0027] In some embodiments, a capping layer 101d is disposed over the first conductive member 102. In some embodiments, the capping layer 101d is disposed over the first surface 102a of the first conductive member 102. In some embodiments, the capping layer 101d is surrounded by the first dielectric layer 101. In some embodiments, the capping layer 101d is disposed over the first barrier layer 102c. In some embodiments, the capping layer 102d includes cobalt (Co), tantalum (Ta), tungsten (W), platinum (Pt) or the like.

[0028] In some embodiments, the first protective layer 103 is disposed over the first dielectric layer 101 and the first conductive member 102. In some embodiments, the first protective layer 103 is in contact with the first dielectric layer 101. In some embodiments, the first protective layer 103 is disposed over and in contact with the capping layer 102d. In some embodiments, the first protective layer 103 is an etch stop layer configured to stop etching operations. In some embodiments, the first protective layer 103 includes nitride. In some embodiments, the first protective layer 103 includes dielectric material such as silicon nitride (SiN), silicon oxide (SiO), aluminum oxynitride (AlON), silicon carbon nitride (SiCN) or the like.

[0029] In some embodiments, the second dielectric layer 104 is disposed over the first protective layer 103. In some embodiments, the second dielectric layer 104 is disposed over the first dielectric layer 101 and the first conductive member 102. In some embodiments, the second dielectric layer 104 includes material same as or different from the first dielectric layer 101. In some embodiments, the first dielectric layer 101 includes a low dielectric constant (k) material such as silicon oxide (SiO), porous organosilicate (SiOCH), borophosphosilicate glass (BPSG), phosphosilicate glass (PSG) or the like.

[0030] In some embodiments, the second protective layer 105 is disposed over the second dielectric layer 104. In some embodiments, the second protective layer 105 is disposed over the first protective layer 103, the first conductive member 102 and the first dielectric layer 101. In some embodiments, the second protective layer 105 is an etch stop layer configured to stop etching operations. In some embodiments, the second protective layer 106 includes material same as or different from the first protective layer 103. In some embodiments, the second protective layer 105 includes nitride. In some embodiments, the second protective layer 105 includes dielectric material such as silicon nitride (SiN), silicon oxide (SiO), aluminum oxynitride (AlON), silicon carbon nitride (SiCN) or the like.

[0031] In some embodiments, the third dielectric layer 106 is disposed over the second dielectric layer 104. In some embodiments, the third dielectric layer 106 is disposed over the second protective layer 105, the first protective layer 103, the first conductive member 102 and the first dielectric layer 101. In some embodiments, the second protective layer 105 is disposed between the second dielectric layer 104 and the third dielectric layer 106. In some embodiments, the third dielectric layer 106 surrounds the second conductive member 107. In some embodiments, the third dielectric layer 106 includes material same as or different from the first dielectric layer 101 and the second dielectric layer 104. In some embodiments, the third dielectric layer 106 includes a low dielectric constant (k) material such as silicon oxide (SiO), porous organosilicate (SiOCH), borophosphosilicate glass (BPSG), phosphosilicate glass (PSG) or the like.

[0032] In some embodiments, the second conductive member 107 is disposed over the first dielectric layer 101 and the first conductive member 102. In some embodiments, the second conductive member 107 is extended through and surrounded by the third dielectric layer 106, the second protective layer 105, the second dielectric layer 104 and the first protective layer 103. In some embodiments, the second conductive member 107 includes conductive material such as copper (Cu), aluminum (Al), cobalt (Co), titanium (Ti), tungsten (W), ruthenium (Ru), molybdenum (Mo), iridium (Ir), rhodium (Rh) or the like.

[0033] In some embodiments, the second conductive member 107 includes a first portion 107a and a second portion 107b. In some embodiments, the first portion 107a is extended through and surrounded by the first protective layer 103 and the second dielectric layer 104. In some embodiments, the first portion 107 is disposed over the first conductive member 102 and the first dielectric layer 101. In some embodiments, the first portion 107a covers a portion of the first conductive member 102 and a portion of the first dielectric layer 101.

[0034] In some embodiments, the second portion 107b is disposed over and coupled with the first portion 107a. In some embodiments, the second portion 107b is surrounded by the third dielectric layer 106 and the second dielectric layer 105. In some embodiments, a first width W1 of the first portion 107a of the second conductive member 107 is substantially less than a second width W2 of the second portion 107b of the second conductive member 107. In some embodiments, the first width W1 is about 10 .ANG. to about 300 .ANG.. In some embodiments, the second width W2 is about 16 .ANG. to about 600 .ANG..

[0035] In some embodiments, at least a portion of the second portion 107b of the second conductive member 107 is protruded from the first portion 107a of the second conductive member 107. In some embodiments, the portion of the second portion 107b is protruded from the first portion 107a in a third width W3 of about 3 .ANG. to about 150 .ANG.. In some embodiments, at least a portion 104a of the second dielectric layer 104 is disposed between the first protective layer 103 and the second portion 107b of the second conductive member 107. In some embodiments, the portion 104a of the second dielectric layer 104 is protruded into the second conductive member 107. In some embodiments, an outer surface of the first portion 107a and the second portion 107b includes a step contour.

[0036] In some embodiments, the first portion 107a includes a third surface 107d interfacing with the first protective layer 103 and the second dielectric layer 104. In some embodiments, the second portion 107b includes a fourth surface 107e interfacing with the second protective layer 105 and the third dielectric layer 106. In some embodiments, the third surface 107d is substantially parallel to the fourth surface 107e. In some embodiments, the third surface 107d and the fourth surface 107e are substantially orthogonal to the first surface 102a of the first conductive member 102. In some embodiments, the third surface 107d and the fourth surface 107e are vertical surfaces. In some embodiments, the fourth surface 107e is protruded from the third surface 107d. In some embodiments, the fourth surface 107e is protruded from the third surface 107d in the third width W3.

[0037] In some embodiments, the second conductive member 107 includes a third portion 107c disposed above the second portion 107b and the first portion 107a. In some embodiments, the third portion 107c is coupled with the second portion 107b. In some embodiments, the third portion 107c is surrounded by the third dielectric layer 106. In some embodiments, a fourth width W4 of the third portion 107c is substantially greater than the first width W1 of the first portion 107a and the second width W2 of the second portion 107b.

[0038] In some embodiments, a second barrier layer 107f surrounds the second conductive member 107. In some embodiments, the second barrier layer 107f is a diffusion barrier layer. In some embodiments, the second barrier layer 107f is configured to prevent diffusion from the second conductive member 107 to the third dielectric layer 106 and the second dielectric layer 104, and provide adhesion between the second conductive member 107 and the third dielectric layer 106 and between the second conductive member 107 and the second dielectric layer 104. In some embodiments, the second barrier layer 107f is disposed between the second conductive member 107 and the third dielectric layer 106. In some embodiments, the second barrier layer 107f is disposed between the second conductive member 107 and the second dielectric layer 104. In some embodiments, the second barrier layer 107f is disposed between the second conductive member 107 and the first protective layer 103. In some embodiments, the second barrier layer 107f is disposed between the second conductive member 107 and the second protective layer 105. In some embodiments, the second barrier layer 107f includes tungsten (W), titanium (Ti), aluminum (Al), copper (Cu), tantalum (Ta) or the like.

[0039] In some embodiments, the first portion 107a of the second conductive member 107 is disposed above the first conductive member 102 and the first dielectric layer 101. In some embodiments as shown in FIG. 1, the second conductive member 107 is not vertically aligned with the first conductive member 102. In some embodiments, a central axis of the second conductive member 107 is deviated from a central axis of the first conductive member 102. In some embodiments, the first portion 107a of the second conductive member 107 is not vertically aligned with the first conductive member 102. In some embodiments, a central axis of the first portion 107a is deviated from the central axis of the first conductive member 102. In some embodiments, the first portion 107 is disposed above the first conductive member 102 and the first dielectric layer 101. In some embodiments, the first portion 107 covers or is in contact with a portion of the first dielectric layer 101.

[0040] In some embodiments, the first portion 107a of the second conductive member 107 is disposed above the first conductive member 102. In some embodiments as shown in FIG. 2, the second conductive member 107 is vertically aligned with the first conductive member 102. In some embodiments, the central axis of the second conductive member 107 is overlapped and common with the central axis of the first conductive member 102. In some embodiments, the first portion 107a of the second conductive member 107 is vertically aligned with the first conductive member 102. In some embodiments, the central axis of the first portion 107a is overlapped and common with the central axis of the first conductive member 102. In some embodiments, the first portion 107 is disposed above the first conductive member 102. In some embodiments, the first portion 107 does not cover and is not in contact with the first dielectric layer 101.

[0041] In some embodiments as shown in FIG. 3, the second portion 107b of the second conductive member 107 is tapered towards the first portion 107a of the second conductive member 107. In some embodiments, the first portion 107 of the second conductive member 107 is tapered towards the first conductive member 102. In some embodiments, a first angle .theta. of the third surface 107d relative to the first surface 102a of the first conductive member 102 is about 90.degree. to about 160.degree.. In some embodiments, a second angle .alpha. of the fourth surface 107e relative to the first surface 102a of the first conductive member 102 is about 90.degree. to about 160.degree.. In some embodiments, the first angle .theta. is substantially the same as the second angle .alpha.. In some embodiments, the third surface 107d of the first portion 107a and the fourth surface 107e of the second portion 107b are tilted surfaces. In some embodiments, the second angle .alpha. is substantially greater than the first angle .theta.. In some embodiments, the third surface 107d is a vertical surface and the fourth surface 107e is a tilted surface.

[0042] In some embodiments as shown in FIG. 4, a third conductive member 108 is disposed over the second conductive member 107. In some embodiments, the third conductive member 108 is surrounded by the third dielectric layer 106. In some embodiments, the second portion 107b of the second conductive member 107 is protruded into the third conductive member 108. In some embodiments, the second portion 107b includes a dome shaped contour. In some embodiments, the second portion 107b includes a convex surface 107g curving towards the third conductive member 108. In some embodiments, the convex surface 107g is surrounded by the third dielectric layer 106. In some embodiments, the third conductive member 108 includes a concave surface 108a curving away from the second conductive member 107. In some embodiments, a curved interface is disposed between the second portion 107b of the second conductive member 107 and the third conductive member 108.

[0043] In some embodiments, the third conductive member 108 includes a fifth width W5 and a sixth width W6. In some embodiments, the fifth width W5 is a shortest width of the third conductive member 108. In some embodiments, the sixth width W6 is a longest width of the third conductive member 108. In some embodiments, the fifth width W5 is substantially less than the sixth width W6. In some embodiments, the third conductive member 108 includes conductive material such as copper (Cu), aluminum (Al), cobalt (Co), titanium (Ti), tungsten (W), ruthenium (Ru) , molybdenum (Mo), iridium (Ir), rhodium (Rh) or the like.

[0044] In some embodiments, the second portion 107b of the second conductive member 107 is tapered towards the first portion 107a of the second conductive member 107. In some embodiments, the third conductive member 108 is tapered towards the second conductive member 107. In some embodiments, the third conductive member 108 includes a fifth surface 108c interfacing with the third dielectric layer 106. In some embodiments, the fourth surface 107 is substantially parallel to the fifth surface 108c. In some embodiments, the fourth surface 107e of the second portion 107b and the fifth surface 108c of the third conductive member 108 are tilted surfaces. In some embodiments, the fourth surface 107e and the fifth surface 108c have substantially the same gradient.

[0045] In some embodiments, a third barrier layer 108b surrounds the third conductive member 108. In some embodiments, the third barrier layer 108b is a diffusion barrier layer. In some embodiments, the third barrier layer 108b is configured to prevent diffusion from the third conductive member 108 to the third dielectric layer 106 and provide adhesion between the third conductive member 108 and the third dielectric layer 106. In some embodiments, the third barrier layer 108b is disposed over the second portion 107b of the second conductive member 107. In some embodiments, the second conductive member 107 is separated from the third conductive member 108 by the third barrier layer 108. In some embodiments, the third barrier layer 108b is disposed between the third conductive member 108 and the third dielectric layer 106. In some embodiments, the third barrier layer 108b is disposed between the third conductive member 108 and the second conductive member 107. In some embodiments, the third barrier layer 108b includes tungsten (W), titanium (Ti), aluminum (Al), copper (Cu), tantalum (Ta) or the like.

[0046] In the present disclosure, a method of manufacturing a semiconductor structure is also disclosed. In some embodiments, a semiconductor structure 100, 200 or 300 is formed by a method 500. The method 500 includes a number of operations and the description and illustration are not deemed as a limitation as the sequence of the operations. FIG. 5 is an embodiment of the method 500 of manufacturing the semiconductor structure 100, 200 or 300. The method 500 includes a number of operations (501, 502, 503, 504, 505, 506, 507, 508, 509, 510 and 511).

[0047] In operation 501, a first dielectric layer 101 and a first conductive member 102 are provided as shown in FIG. 6. In some embodiments, the first conductive member 102 is surrounded by the first dielectric layer 101. In some embodiments, the first conductive member 102 is extended through the first dielectric layer 101. In some embodiments, the first conductive member 102 includes a first surface 102a and a second surface 102b opposite to the first surface 102a.

[0048] In some embodiments, the first dielectric layer 101 is formed by spin coating, chemical vapor deposition (CVD), plasma enhanced CVD (PECVD) or any other suitable operations. In some embodiments, the first conductive member 102 is formed by removing a portion of the first dielectric layer 101 to form a hole and disposing a conductive material into the hole. In some embodiments, the removal of the portion of the first dielectric layer 101 includes photolithography, etching or any other suitable operations. In some embodiments, the disposing of the conductive material includes sputtering, electroplating or any other suitable operations.

[0049] In some embodiments, a substrate is provided before the disposing of the first dielectric layer 101 and the first conductive member 102. In some embodiments, the first dielectric layer 101 and the first conductive member 102 are disposed over the substrate. In some embodiments, the substrate is configured to support components of the semiconductor structure during the method 500. The components of the semiconductor structure are formed over the substrate during the method 500.

[0050] In some embodiments, a first barrier layer 102c is formed before the formation of the first conductive member 102. In some embodiments, the first barrier layer 102c surrounds the first conductive member 102. In some embodiments, the first barrier layer 102c is disposed conformal to the hole of the first dielectric layer 101, and then the first conductive member 102 is disposed over the first barrier layer 102c. In some embodiments, the first barrier layer 102c is disposed by deposition, electroless plating or any other suitable operations.

[0051] In some embodiments, a capping layer 102d is formed over the first conductive member 102 and the first barrier layer 102c. In some embodiments, the capping layer 102d is surrounded by the first dielectric layer 101. In some embodiments, the capping layer 102d is formed by CVD, sputtering or any other suitable operations. In some embodiments, the first dielectric layer 101, the first conductive member 102, the first barrier layer 102c and the capping layer 102d are in configurations as described above or shown in FIGS. 1-4.

[0052] In operation 502, a first protective layer 103 is disposed over the first dielectric layer 101 and the first conductive member 102 as shown in FIG. 7. In some embodiments, the first protective layer 103 is disposed over the capping layer 102d. In some embodiments, the first protective layer 103 is an etch stop layer configured to stop etching operations. In some embodiments, the first protective layer 103 is formed by CVD, PECVD or any other suitable operations. In some embodiments, the first protective layer 103 is in configuration as described above or shown in FIGS. 1-4.

[0053] In operation 503, a second dielectric layer 104 is disposed over the first protective layer 103 as shown in FIG. 8. In some embodiments, the second dielectric layer 104 is disposed conformal to the first protective layer 103. In some embodiments, the second dielectric layer 104 is formed by spin coating, CVD, PECVD or any other suitable operations. In some embodiments, the second dielectric layer 104 is in configuration as described above or shown in FIGS. 1-4.

[0054] In operation 504, a second protective layer 105 is disposed over the second dielectric layer 104 as shown in FIG. 9. In some embodiments, the second protective layer 105 is disposed conformal to the second dielectric layer 104. In some embodiments, the second protective layer 105 is an etch stop layer configured to stop etching operations. In some embodiments, the second protective layer 105 is formed by CVD, PECVD or any other suitable operations. In some embodiments, the second protective layer 105 is in configuration as described above or shown in FIGS. 1-4.

[0055] In operation 505, a third dielectric layer 106 is disposed over the second protective layer 105 as shown in FIG. 10. In some embodiments, the third dielectric layer 106 is formed by spin coating, CVD, PECVD or any other suitable operations. In some embodiments, the third dielectric layer 106 is in configuration as described above or shown in FIGS. 1-4.

[0056] In some embodiments, a dielectric mask 109 is disposed over the third dielectric layer 106, and a hard mask 110 is formed over the dielectric mask 109 as shown in FIG. 11. In some embodiments, the dielectric mask 109 is configured to protect the third dielectric layer 106 from removal. In some embodiments, the dielectric mask 109 includes silicon oxide or any other suitable materials. In some embodiments, the dielectric mask 109 is formed by CVD or any other suitable operations.

[0057] In some embodiments, a portion of the hard mask 110 is removed to pattern the hard mask 110. In some embodiments, the hard mask 110 is patterned by disposing a first photoresist over the hard mask 110, patterning the first photoresist and removing the portion of the hard mask 110 exposed from the patterned first photoresist. In some embodiments, the first photoresist is disposed by spin coating or any other suitable operations. In some embodiments, the first photoresist is patterned by exposing a portion of the first photoresist from a photomask, projecting a predetermined electromagnetic radiation towards the photomask and the exposed portion of the first photoresist, and removing the exposed portion of the first photoresist. In some embodiments, the patterned hard mask 110 is formed as shown in FIG. 11. In some embodiments, the dielectric mask 109 covers the third dielectric layer 106 after the patterning of the hard mask 110. In some embodiments, the first photoresist is removed after the patterning of the hard mask 110. In some embodiments, the first photoresist is removed by wet etching, stripping or any other suitable operations.

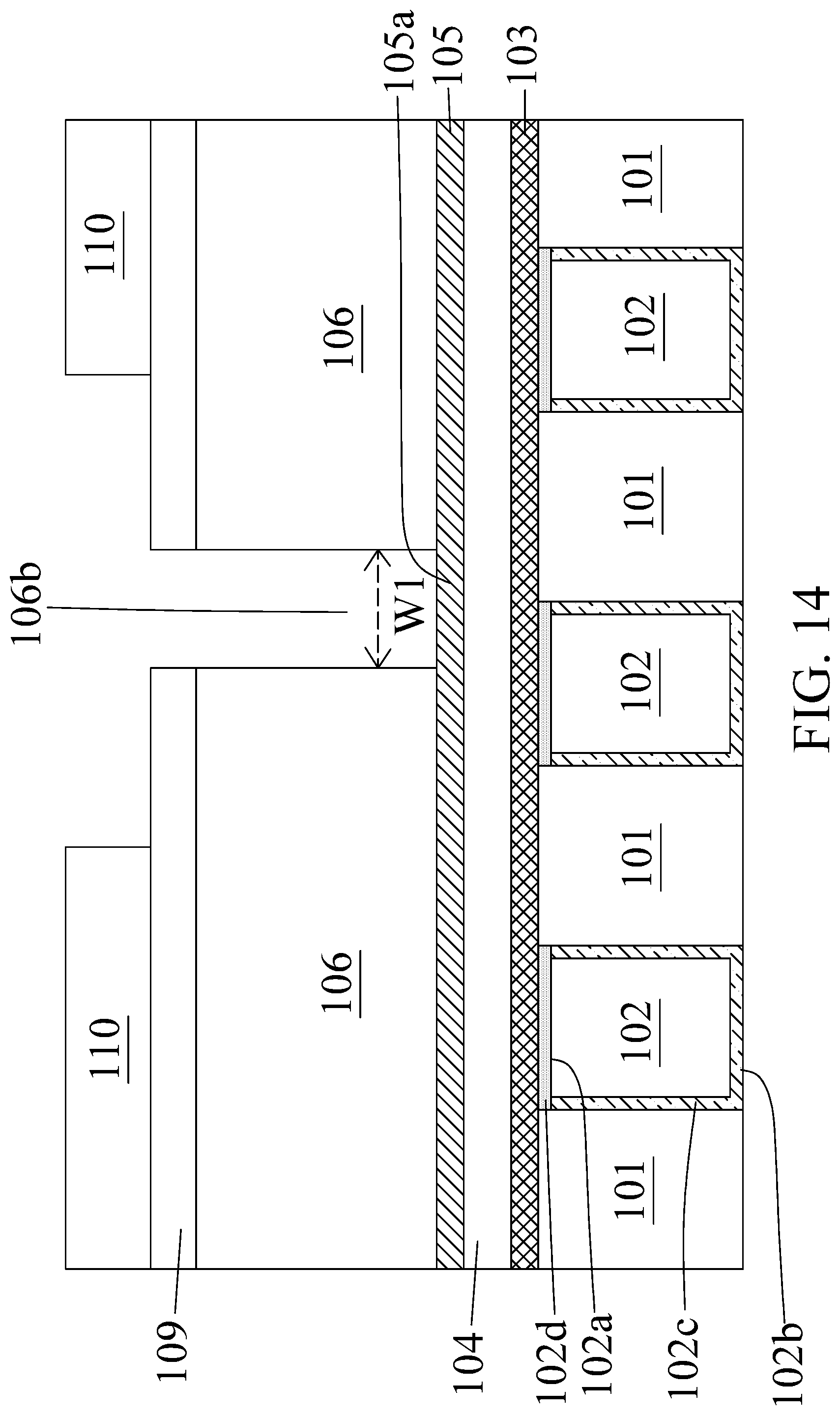

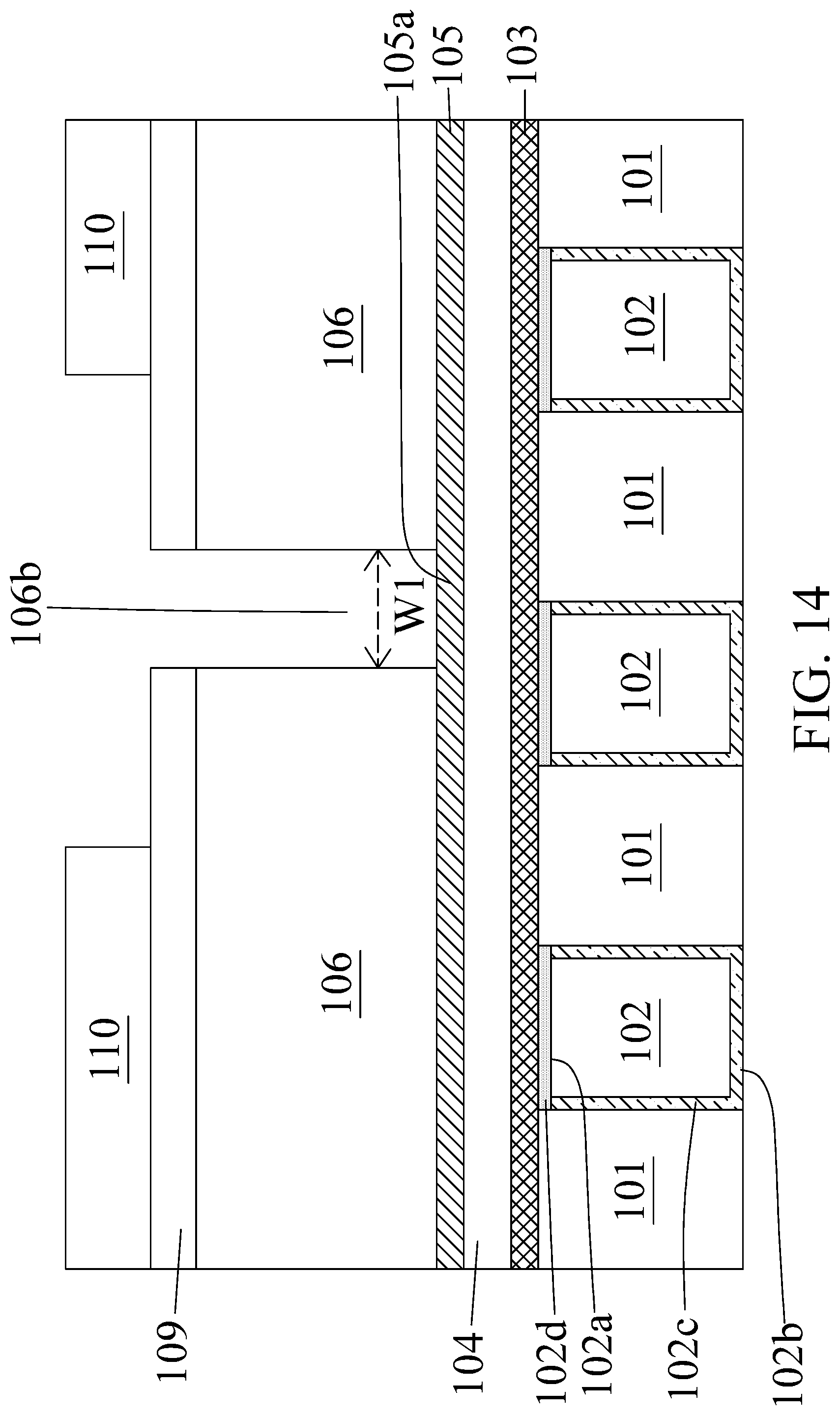

[0058] In operation 506, a first portion 106a of the third dielectric layer 106 is removed to form a first opening 106b as shown in FIGS. 12-14. In some embodiments, a second photoresist 111 is disposed over the hard mask 110 and the dielectric mask 109. In some embodiments, the second photoresist 111 is disposed by spin coating or any other suitable operations. In some embodiments, the second photoresist 111 is patterned by exposing a portion of the second photoresist 111 from a photomask, projecting a predetermined electromagnetic radiation towards the photomask and the exposed portion of the second photoresist 111, and removing the exposed portion of the second photoresist 111. In some embodiments, a patterned second photoresist 111 is formed as shown in FIG. 12.

[0059] In some embodiments, a portion of the dielectric mask 109 is exposed from the patterned second photoresist 111. In some embodiments, the exposed portion of the dielectric mask 109 and the first portion 106a of the third dielectric layer 106 under the exposed portion of the dielectric mask 109 are removed as shown in FIG. 13. In some embodiments, the exposed portion of the dielectric mask 109 and the first portion 106a of the third dielectric layer 106 are removed by dry etching or any other suitable operations. In some embodiments, the first opening 106b is formed after the removal of the first portion 106a of the third dielectric layer 106. In some embodiments, the first opening 106b is extended through the third dielectric layer 106.

[0060] In some embodiments, a first width W1 the first opening 106b is about 10 .ANG. to about 300 .ANG.. In some embodiments, the first opening 106b is not aligned with the first conductive member 102 as shown in FIG. 13. In some embodiments, the first opening 106b is disposed above and aligned with the first conductive member 102. In some embodiments, a first portion 105a of the second protective layer 105 is exposed after the formation of the first opening 106b. In some embodiments, the second photoresist 111 is removed after the formation of the first opening 106b as shown in FIG. 14. In some embodiments, the second photoresist 111 is removed by wet etching, stripping or any other suitable operations.

[0061] In operation 507, the first portion 105a of the second protective layer 105 exposed by the first opening 106b is removed as shown in FIG. 15. In some embodiments, the first portion 105a of the second protective layer 105 is removed by wet etching or any other suitable operations. In some embodiments, a first portion 104b of the second dielectric layer 104 is exposed from the second protective layer 105 after the removal of the first portion 105a of the second protective layer 105. In some embodiments, a second portion 106c of the third dielectric layer 106 is uncovered by the hard mask 110.

[0062] In operation 508, the second portion 106c of the third dielectric layer 106 is removed to form a second opening 106d as shown in FIG. 16. In some embodiments, the second portion 106c of the third dielectric layer 106 is removed by dry etching or any other suitable operations. In some embodiments, more of the third dielectric layer 106 adjacent to the hard mask 109 is etched compared with the third dielectric layer 106 away from the hard mask 109 and close to the first dielectric layer 101. As such, the second opening 106d has a step contour after the removal of the second portion 106c of the third dielectric layer 106. In some embodiments, the second opening 106d is tapered towards the first conductive member 102 and the second dielectric layer 104. In some embodiments, a second portion 105b of the second protective layer 105 is exposed by the second opening 106d after the removal of the second portion 106c of the third dielectric layer 106. In some embodiments, the dielectric mask 109 uncovered by the hard mask 110 is removed before or upon the removal of the second portion 106c of the third dielectric layer 106.

[0063] In operation 509, the first portion 104b of the second dielectric layer 104 exposed from the second protective layer 105 is removed to form a third opening 104c as shown in FIG. 16. In some embodiments, the first portion 104b of the second dielectric layer 104 is removed by dry etching or any other suitable operations. In some embodiments, a portion 103a of the first protective layer 103 is exposed by the third opening 104c after removal of the first portion 104b of the second dielectric layer 104.

[0064] In some embodiments, the second portion 106c of the third dielectric layer 106 and the first portion 104b of the second dielectric layer 104 are removed separately or simultaneously. In some embodiments, the operation 508 and the operation 509 are performed separately or simultaneously. In some embodiments, a width of the third opening 104c is substantially the same as the first width W1 of the first opening 106b. In some embodiments, a second width W2 of the second opening 106d is substantially greater than the width of the third opening 104c. In some embodiments, the second opening 106d is tapered towards the third opening 104c.

[0065] In operation 510, the portion 103a of the first protective layer 103 exposed by the third opening 104c and a second portion 105b of the second protective layer 105 exposed by the second opening 106d are removed as shown in FIG. 17. In some embodiments, the portion 103a of the first protective layer 103 and the second portion 105b of the second protective layer 105 are removed by wet etching or any other suitable operations. In some embodiments, the removal of the portion 103a of the first protective layer 103 and the removal of the second portion 105b of the second protective layer 105 are performed separately or simultaneously. In some embodiments, a portion 104a of the second dielectric layer 104 is exposed by the second opening 106d after the removal of the second portion 105b of the second protective layer 105. In some embodiments, the portion 104a of the second dielectric layer 104 is laterally protruded. In some embodiments, the first conductive member 102 or the capping layer 102d is exposed after the removal of the portion 103a of the first protective layer 103.

[0066] In operation 511, a conductive material 112 is disposed into the second opening 106d and the third opening 104c to form a second conductive member 107 as shown in FIGS. 18-19. In some embodiments, the conductive material 112 is disposed over the third dielectric layer 106. In some embodiments, the conductive material 112 is disposed over the dielectric mask 109 and the hard mask 110. In some embodiments, the conductive material 112 is formed by sputtering, electroplating, CVD, physical vapor deposition (PVD) or any other suitable operations.

[0067] In some embodiments, a second barrier layer 107f is disposed conformal to the second opening 106d and the third opening 104c before the disposing of the conductive material 112. In some embodiments, the second barrier layer 107f is formed, and then the conductive material 112 is disposed over the second barrier layer 107f. In some embodiments, the second barrier layer 107f is disposed over the third dielectric layer 106. In some embodiments, the second barrier layer 107f is disposed over the dielectric mask 109 and the hard mask 110. In some embodiments, the second barrier layer 107f is disposed by sputtering, electroplating, CVD, physical vapor deposition (PVD) or any other suitable operations.

[0068] In some embodiments, the second conductive member 107 is formed after planarization of the conductive material 112. In some embodiments as shown in FIG. 19, some of the conductive material 112 are removed to form the second conductive member 107. In some embodiments, some of the second barrier layer 107f disposed over the third dielectric layer 106, some of the conductive material 112 disposed over the third dielectric layer 106, the dielectric mask 109 and the hard mask 110 are removed by chemical mechanical planarization (CMP) or any other suitable operations. In some embodiments, the second conductive member 107 is in configurations as described above or shown in FIGS. 1-3. In some embodiments, a semiconductor structure 100 described above and shown in FIG. 1 is formed. In some embodiments, a semiconductor structure 200 having the second conductive member 107 aligned with the first conductive member 102 as described above or shown in FIG. 2 is formed. In some embodiments, a semiconductor structure 300 having tapered second conductive member 107 as described above or shown in FIG. 3 is formed.

[0069] In the present disclosure, a method of manufacturing a semiconductor structure is also disclosed. In some embodiments, a semiconductor structure is formed by a method 600. The method 600 includes a number of operations and the description and illustration are not deemed as a limitation as the sequence of the operations. FIG. 20 is an embodiment of the method 600 of manufacturing a semiconductor structure. The method 600 includes a number of operations (601, 602, 603, 604, 605, 606, 607, 608, 609, 610, 611 and 612).

[0070] In operation 601, a first dielectric layer 101 and a first conductive member 102 are provided as shown in FIG. 6. The operation 601 is substantially the same as the operation 501.

[0071] In operation 602, a first protective layer 103 is disposed over the first dielectric layer 101 and the first conductive member 102 as shown in FIG. 7. The operation 602 is substantially the same as the operation 502.

[0072] In operation 603, a second dielectric layer 104 is disposed over the first protective layer 103 as shown in FIG. 8. The operation 603 is substantially the same as the operation 503.

[0073] In operation 604, a second protective layer 105 is disposed over the second dielectric layer 104 as shown in FIG. 9. The operation 604 is substantially the same as the operation 504.

[0074] In operation 605, a third dielectric layer 106 is disposed over the second protective layer 105 as shown in FIG. 10. The operation 605 is substantially the same as the operation 505. In some embodiments, a hard mask 110 is formed over the third dielectric layer 106 as shown in FIG. 11

[0075] In operation 606, a first portion 106a of the third dielectric layer 106 is removed to form a first opening 106b as shown in FIGS. 12-14. The operation 606 is substantially the same as the operation 506.

[0076] In operation 607, the first portion 105a of the second protective layer 105 exposed by the first opening 106b is removed as shown in FIG. 15. The operation 607 is substantially the same as the operation 507.

[0077] In operation 608, the second portion 106c of the third dielectric layer 106 is removed to form a second opening 106d as shown in FIG. 16. The operation 608 is substantially the same as the operation 508.

[0078] In operation 609, the first portion 104b of the second dielectric layer 104 exposed from the second protective layer 105 is removed to form a third opening 104c as shown in FIG. 16. The operation 609 is substantially the same as the operation 509.

[0079] In operation 610, the portion 103a of the first protective layer 103 exposed by the third opening 104c and a second portion 105b of the second protective layer 105 exposed by the second opening 106d are removed as shown in FIG. 17.

[0080] In operation 611, a first conductive material is disposed to form a second conductive member 107 as shown in FIG. 21. In some embodiments, the first conductive material is disposed into the second opening 106d and the third opening 104c to form the second conductive member 107. In some embodiments, the first conductive material is disposed by electroless plating, CVD or any other suitable operations. In some embodiments, the first conductive material is grown within the third opening 104c and a portion of the second opening 106d to form the second conductive member 107. In some embodiments, the second conductive member 107 is surrounded by the first protective layer 103, the second dielectric layer 104, the second protective layer 105 and the third dielectric layer 106. In some embodiments, the first conductive material is grown to form the second conductive member 107 having a step contour.

[0081] In some embodiments, the second conductive member 107 includes a first portion 107a and a second portion 107b over the first portion 107a. In some embodiments, the first portion 107a is surrounded by the first protective layer 103 and the second dielectric layer 104. In some embodiments, the second portion 107b is surrounded by the second protective layer 105 and the third dielectric layer 106. In some embodiments, the first conductive material is grown to form the second portion 107b of the second conductive member 107 having a dome shaped contour. In some embodiments, the second portion 107b includes a convex surface 107g curving towards the second opening 106d. In some embodiments, In some embodiments, the first portion 107a includes a third surface 107d interfacing with the first protective layer 103 and the second dielectric layer 104. In some embodiments, the second portion 107b includes a fourth surface 107e interfacing with the second protective layer 105 and the third dielectric layer 106. In some embodiments, the third surface 107d is substantially parallel to the fourth surface 107e. In some embodiments, the fourth surface 107e is tapered towards the first conductive member 102. In some embodiments, the second conductive member 107 is in configuration as described above or shown in FIG. 4.

[0082] In operation 612, a second conductive material 112 is disposed to form a third conductive member 108 as shown in FIGS. 22-23. The second conductive member 107 and the third conductive member 108 are separately formed. In some embodiments, the second conductive material 112 is disposed into the second opening 106d and over the third dielectric layer 106. In some embodiments, the second conductive material 112 is disposed over the dielectric mask 109 and the hard mask 110. In some embodiments, the second conductive material 112 is formed by sputtering, electroplating, CVD, physical vapor deposition (PVD) or any other suitable operations. In some embodiments, the third conductive member 108 includes a concave surface 108a curving away from the second conductive member 107.

[0083] In some embodiments, a third barrier layer 108b is disposed conformal to the convex surface 107g of the second conductive member 107 and the second opening 106d before the disposing of the second conductive material 112. In some embodiments, the third barrier layer 108b is formed, and then the second conductive material 112 is disposed over the second barrier layer 107f. In some embodiments, the third barrier layer 108b is disposed over the third dielectric layer 106. In some embodiments, the third barrier layer 108b is disposed over the dielectric mask 109 and the hard mask 110. In some embodiments, the third barrier layer 108b is disposed by sputtering, electroplating, CVD, physical vapor deposition (PVD) or any other suitable operations. Since an interface between the second conductive member 107 and the third conductive member 108 or between the second conductive member 107 and the third barrier layer 108b is curved, a contacting surface between the second conductive member 107 and the third conductive member 108 or between the second conductive member 107 and the third barrier layer 108b is increased. As such, adhesion between the second conductive member 107 and the third conductive member 108 or between the second conductive member 107 and the third barrier layer 108b is improved.

[0084] In some embodiments, the third conductive member 108 is formed after planarization of the second conductive material 112. In some embodiments as shown in FIG. 23, some of the second conductive material 112 are removed to form the third conductive member 108. In some embodiments, some of the third barrier layer 108b disposed over the third dielectric layer 106, some of the second conductive material 112 disposed over the third dielectric layer 106, the dielectric mask 109 and the hard mask 110 are removed by chemical mechanical planarization (CMP) or any other suitable operations. In some embodiments, the third conductive member 108 is in configurations as described above or shown in FIG. 4. In some embodiments, a semiconductor structure 400 described above and shown in FIG. 4 is formed.

[0085] In some embodiments, a semiconductor structure includes a first dielectric layer; a first conductive member extended through and surrounded by the first dielectric layer; a first protective layer disposed over the first dielectric layer and the first conductive member; a second dielectric layer disposed over the first protective layer; a third dielectric layer disposed over the second dielectric layer; and a second conductive member disposed over the first dielectric layer and the first conductive member, and surrounded by the first protective layer, the second dielectric layer and the third dielectric layer, wherein the second conductive member includes a first portion and a second portion disposed over and coupled with the first portion, the first portion is extended through and surrounded by the first protective layer and the second dielectric layer, the second portion is surrounded by the third dielectric layer, at least a portion of the second dielectric layer is disposed between the first protective layer and the second portion of the second conductive member.

[0086] In some embodiments, a first width of the first portion of the second conductive member is substantially less than a second width of the second portion of the second conductive member. In some embodiments, at least a portion of the second portion of the second conductive member is protruded from the first portion of the second conductive member. In some embodiments, the second portion of the second conductive member is tapered towards the first portion of the second conductive member. In some embodiments, the first portion of the second conductive member is tapered towards the first conductive member. In some embodiments, the first portion of the second conductive member is disposed above the first conductive member. In some embodiments, the first portion of the second conductive member is disposed above the first conductive member and the first dielectric layer. In some embodiments, the semiconductor structure further includes a second protective layer disposed between the second dielectric layer and the third dielectric layer, wherein the second protective layer surrounds the second portion of the second conductive member. In some embodiments, the first protective layer and the second protective layer include nitride. In some embodiments, the second conductive member includes a third portion surrounded by the third dielectric layer, disposed over and coupled with the second portion of the second conductive member. In some embodiments, a third width of the third portion of the second conductive member is substantially greater than a first width of the first portion of the second conductive member and a second width of the second portion of the second conductive member.

[0087] In some embodiments, a semiconductor structure includes a first dielectric layer; a first conductive member extended through and surrounded by the first dielectric layer; a first protective layer disposed over the first dielectric layer and the first conductive member; a second dielectric layer disposed over the first protective layer; a second protective layer disposed over the second dielectric layer; a third dielectric layer disposed over the second dielectric layer; a second conductive member disposed over the first dielectric layer and the first conductive member, and surrounded by the first protective layer, the second dielectric layer, the second protective layer and the third dielectric layer; and a third conductive member disposed over the second conductive member and surrounded by the third dielectric layer, wherein the second conductive member includes a first portion and a second portion disposed over and coupled with the first portion, the first portion is extended through and surrounded by the first protective layer and the second dielectric layer, the second portion is surrounded by the third dielectric layer, at least a portion of the second dielectric layer is disposed between the first protective layer and the second portion of the second conductive member.

[0088] In some embodiments, a curved interface is disposed between the second portion of the second conductive member and the third conductive member. In some embodiments, the second portion of the second conductive member includes a convex surface curving towards the third conductive member. In some embodiments, the third conductive member includes a concave surface curving away from the second conductive member. In some embodiments, the second portion of the second conductive member is protruded from the first portion of the second conductive member in a length of about 3 .ANG. to about 150 .ANG.. In some embodiments, the semiconductor structure further includes a barrier layer surrounding the third conductive member, disposed over the second portion of the second conductive member and separating the third conductive member from the second conductive member.

[0089] In some embodiments, a method of manufacturing a semiconductor structure includes providing a first dielectric layer and a first conductive member surrounded by the first dielectric layer; disposing a first protective layer over the first dielectric layer and the first conductive member; disposing a second dielectric layer over the first protective layer; disposing a second protective layer over the second dielectric layer; disposing a third dielectric layer over the second protective layer; removing a first portion of the third dielectric layer to form a first opening; removing a first portion of the second protective layer exposed by the first opening; removing a second portion of the third dielectric layer to form a second opening; removing a first portion of the second dielectric layer exposed from the second protective layer to form a third opening; removing a portion of the first protective layer exposed by the third opening and a second portion of the second protective layer exposed by the second opening; and disposing a conductive material into the second opening and the third opening to form a second conductive member.

[0090] In some embodiments, a first width of the first opening is substantially less than a second width of the second opening, and the first width is substantially the same as a third width of the third opening. In some embodiments, a second portion of the second dielectric layer is exposed by the second opening after the removal of the second portion of the second protective layer.

[0091] The foregoing outlines features of several embodiments so that those skilled in the art may better understand the aspects of the present disclosure. Those skilled in the art should appreciate that they may readily use the present disclosure as a basis for designing or modifying other processes and structures for carrying out the same purposes and/or achieving the same advantages of the embodiments introduced herein. Those skilled in the art should also realize that such equivalent constructions do not depart from the spirit and scope of the present disclosure, and that they may make various changes, substitutions, and alterations herein without departing from the spirit and scope of the present disclosure.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

D00009

D00010

D00011

D00012

D00013

D00014

D00015

D00016

D00017

D00018

D00019

D00020

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.