Method of Forming High-Voltage Transistor with Thin Gate Poly

Chen; Chun ; et al.

U.S. patent application number 16/292042 was filed with the patent office on 2019-10-03 for method of forming high-voltage transistor with thin gate poly. This patent application is currently assigned to Cypress Semiconductor Corporation. The applicant listed for this patent is Cypress Semiconductor Corporation. Invention is credited to Kuo Tung Chang, Chun Chen, Inkuk Kang, Sung-Taeg Kang, Unsoon KIM, James Pak.

| Application Number | 20190304990 16/292042 |

| Document ID | / |

| Family ID | 65016688 |

| Filed Date | 2019-10-03 |

View All Diagrams

| United States Patent Application | 20190304990 |

| Kind Code | A1 |

| Chen; Chun ; et al. | October 3, 2019 |

Method of Forming High-Voltage Transistor with Thin Gate Poly

Abstract

A semiconductor device and method of fabricating the same are disclosed. The method includes depositing a polysilicon gate layer over a gate dielectric formed over a surface of a substrate in a peripheral region, forming a dielectric layer over the polysilicon gate layer and depositing a height-enhancing (HE) film over the dielectric layer. The HE film, the dielectric layer, the polysilicon gate layer and the gate dielectric are then patterned for a high-voltage Field Effect Transistor (HVFET) gate to be formed in the peripheral region. A high energy implant is performed to form at least one lightly doped region in a source or drain region in the substrate adjacent to the HVFET gate. The HE film is then removed, and a low voltage (LV) logic FET formed on the substrate in the peripheral region. In one embodiment, the LV logic FET is a high-k metal-gate logic FET.

| Inventors: | Chen; Chun; (San Jose, CA) ; Pak; James; (Sunnyvale, CA) ; KIM; Unsoon; (San Jose, CA) ; Kang; Inkuk; (San Jose, CA) ; Kang; Sung-Taeg; (Palo Alto, CA) ; Chang; Kuo Tung; (Saratoga, CA) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Assignee: | Cypress Semiconductor

Corporation San Jose CA |

||||||||||

| Family ID: | 65016688 | ||||||||||

| Appl. No.: | 16/292042 | ||||||||||

| Filed: | March 4, 2019 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 15848327 | Dec 20, 2017 | 10242996 | ||

| 16292042 | ||||

| 62534463 | Jul 19, 2017 | |||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 27/11568 20130101; H01L 29/6659 20130101; H01L 29/66833 20130101; H01L 29/7833 20130101; H01L 27/1157 20130101; H01L 27/11573 20130101; H01L 29/40117 20190801; H01L 29/66545 20130101; H01L 29/40114 20190801; H01L 27/11546 20130101; H01L 29/4933 20130101; H01L 27/11521 20130101; H01L 29/42344 20130101; H01L 21/26513 20130101; H01L 29/456 20130101; H01L 29/517 20130101; H01L 29/42328 20130101; H01L 29/792 20130101; H01L 21/28052 20130101; H01L 21/28518 20130101 |

| International Class: | H01L 27/11573 20060101 H01L027/11573; H01L 27/1157 20060101 H01L027/1157; H01L 21/265 20060101 H01L021/265; H01L 29/66 20060101 H01L029/66; H01L 21/28 20060101 H01L021/28; H01L 27/11546 20060101 H01L027/11546; H01L 27/11568 20060101 H01L027/11568; H01L 29/423 20060101 H01L029/423; H01L 29/45 20060101 H01L029/45; H01L 29/49 20060101 H01L029/49; H01L 29/78 20060101 H01L029/78; H01L 21/285 20060101 H01L021/285; H01L 27/11521 20060101 H01L027/11521; H01L 29/792 20060101 H01L029/792 |

Claims

1-21. (canceled)

22. A semiconductor device, comprising: a non-volatile memory (NVM) cell including a memory gate stack and a select gate stack separated by an inter-gate dielectric disposed in a memory region of a substrate; a first field-effect transistor (FET) including a high-K metal-gate (HKMG) stack disposed in a peripheral region of the substrate; and a second FET including a high voltage (HV) gate stack disposed in the peripheral region, wherein top surfaces of the memory gate stack and the select gate stack of the NVM cell and the HV gate stack of the second FET have an approximately same elevation from the substrate.

23. The semiconductor device of claim 22, wherein the memory gate stack includes a memory gate disposed over a multi-layer charge-trapping layer, and wherein the select gate stack includes a select gate disposed over a dielectric layer.

24. The semiconductor device of claim 22, wherein the HKMG stack of the first FET includes a metal gate disposed over a high-K dielectric layer.

25. The semiconductor device of claim 22, wherein the HV gate stack of the second FET includes a polysilicon gate disposed over a HV dielectric layer.

26. The semiconductor device of claim 22, wherein the NVM cell includes a split gate memory transistor.

27. The semiconductor device of claim 22, wherein the second FET is a HV device that is operational up to approximately 20 V and includes source and drain regions having a depth from 400 .ANG. to 2,000 .ANG. below a surface of the substrate, and wherein the polysilicon gate of the second FET has a gate height from 300 .ANG. to 1,000 .ANG..

28. The semiconductor device of claim 23, wherein a self-aligned silicide (SALICIDE) layer is disposed over at least a portion of the select gate, and wherein the SALICIDE layer is not in direct contact with the inter-gate dielectric.

29. The semiconductor device of claim 24, wherein the metal gate of the first FET has a width from 10 nm to 40 nm and a height from 300 .ANG. to 1,000 .ANG..

30. The semiconductor device of claim 24, wherein the metal gate is made of at least one of: aluminum, copper, titanium, tungsten, and alloys thereof.

31. The semiconductor device of claim 24, wherein the high-K dielectric layer includes at least one of: hafnium oxide, zirconium oxide, hafnium silicate, hafnium oxy-nitride, hafnium zirconium oxide, and lanthanum oxide.

32. A memory device, comprising: a plurality of split gate transistors in a memory region, wherein each split gate transistor includes a memory gate stack disposed adjacent to a select gate stack; a plurality of logic transistors in a peripheral region, wherein each logic transistor includes a high-K metal-gate (HKMG) stack; and a plurality of high voltage (HV) transistors in the peripheral region, wherein each HV transistor includes a HV gate stack; wherein the memory and select gate stacks of the plurality of split gate transistors and the HV gate stack of the plurality of HV transistors have an approximate same height and a commonly planarized top surfaces, and wherein the memory and peripheral regions are disposed within a single substrate.

33. The memory device of claim 32, wherein the memory gate stack includes a memory gate disposed over a multi-layer charge-trapping layer, and wherein the select gate stack includes a select gate disposed over a dielectric layer.

34. The memory device of claim 32, wherein the HKMG stacks of the plurality of logic transistors each includes a metal gate disposed over a high-K dielectric layer.

35. The memory device of claim 32, wherein the HV gate stacks of the plurality of HV transistors each includes a polysilicon gate disposed over a HV dielectric layer.

36. The memory device of claim 32, wherein the memory gate stack and select gate stack is separated by an inter-gate dielectric.

37. The memory device of claim 32, wherein the plurality of HV transistors are operational up to approximately 20 V and each includes source and drain regions having a depth from 400 .ANG. to 2,000 .ANG. below a surface of the single substrate, and wherein the polysilicon gates each has a gate height from 300 .ANG. to 1,000 .ANG..

38. The memory device of claim 36, wherein a self-aligned silicide (SALICIDE) layer is disposed over at least a portion of each of the select gate, and wherein the SALICIDE layer is not in direct contact with the inter-gate dielectric.

39. The memory device of claim 34, wherein the metal gates of the plurality of logic transistors each has a width from 10 nm to 40 nm and a height from 300 .ANG. to 1,000 .ANG..

40. The memory device of claim 34, wherein the metal gates of the plurality of logic transistors are made of at least one of: aluminum, copper, titanium, tungsten, and alloys thereof.

41. The memory device of claim 33, wherein the high-K dielectric layers of the plurality of logic transistors include at least one of: hafnium oxide, zirconium oxide, hafnium silicate, hafnium oxy-nitride, hafnium zirconium oxide, and lanthanum oxide.

Description

CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application is a Continuation of U.S. patent application Ser. No. 15/848,327, filed on Dec. 20, 2017, which claims the benefit of priority under 35 U.S.C. 119(e) to U.S. Provisional Patent Application Ser. No. 62/534,463, filed Jul. 19, 2017, both of which are incorporated by reference herein in their entirety.

TECHNICAL FIELD

[0002] This disclosure relates generally to semiconductor devices and more particularly to non-volatile memory (NVM) devices including memory cells, high-voltage field effect transistor (HVFETs) and advanced logic FETs embedded or integrally formed on a single substrate and methods for fabricating the same.

BACKGROUND

[0003] Flash or Non-volatile memory (NVM) devices typically include a grid or an array of storage elements or cells, each including at least one NVM transistor and a number of peripheral circuits including decoders, drivers, sense amplifiers and control circuits to read from and write to the array. NVM transistors generally include a charge-trapping or charge storage layer, and require a high voltage (HV) in the range of four to ten volts for program and erase operations. The peripheral circuits include logic Field Effect Transistors (FETs), which typically operate at a low voltage, as well as a number of HVFETs capable of supporting the high voltages required by the NVM transistors.

[0004] It is becoming increasingly common to monolithically incorporate logic FETs and HVFETs on the same substrate as the memory cells to provide improved efficiency, security, functionality, and reliability. However, incorporating logic FETs and HVFETs on the same substrate along with the NVM transistors is challenging as each device or transistor typically requires different fabrication parameters.

[0005] Accordingly, there is a need for a semiconductor or NVM device integrating memory cells, HVFETs and logic FETs embedded or integrally formed on a single substrate, and methods for fabricating the same.

SUMMARY

[0006] A semiconductor device and method of fabricating the same are provided. Generally, the method begins with forming an ONO stack for a memory gate (MG) to be formed over a surface of a substrate in a memory region of the substrate, and forming a gate dielectric for high-voltage Field Effect Transistor (HVFET) gate to be formed over the surface of the substrate in a peripheral region. Next, a polysilicon gate layer is deposited over the ONO stack and the gate dielectric, a dielectric layer formed over the polysilicon gate layer, and a height-enhancing (HE) film deposited over the dielectric layer. The HE film, dielectric layer, gate layer, gate dielectric and ONO stack are then patterned for the MG and HVFET gate. A source/drain (S/D) region is implanted adjacent to the HVFET gate, and the HE polysilicon layer removed to form the MG and HVFET gate. The depth of the S/D region in the substrate is generally greater than a height of the HVFET gate above the surface of the substrate. In some embodiments, the HE film includes amorphous silicon or polysilicon, and is sufficiently thick to prevent dopants from the drain implant from reaching a channel underlying the HVFET gate.

[0007] According to another embodiment the method further includes, subsequent to removing the HE film, forming a polysilicon gate for a low voltage (LV) logic FET including in the peripheral region, and replacing the polysilicon gate of the LV logic FET with a metal-gate using a high-K metal gate (HKMG) process.

[0008] Further features and advantages of embodiments of the invention, as well as the structure and operation of various embodiments of the invention, are described in detail below with reference to the accompanying drawings. It is noted that the invention is not limited to the specific embodiments described herein. Such embodiments are presented herein for illustrative purposes only. Additional embodiments will be apparent to a person skilled in the relevant art(s) based on the teachings contained herein.

BRIEF DESCRIPTION OF THE DRAWINGS

[0009] Embodiments of the invention will now be described, by way of example only, with reference to the accompanying schematic drawings in which corresponding reference symbols indicate corresponding parts. Further, the accompanying drawings, which are incorporated herein and form part of the specification, illustrate embodiments of the present invention, and, together with the description, further serve to explain the principles of the invention and to enable a person skilled in the relevant art(s) to make and use the invention.

[0010] FIG. 1 is a schematic block diagram of a non-volatile memory (NVM) device including an array of memory cells and a number of peripheral circuits including decoders, drivers, sense amplifiers and control circuits integrally formed on a single substrate;

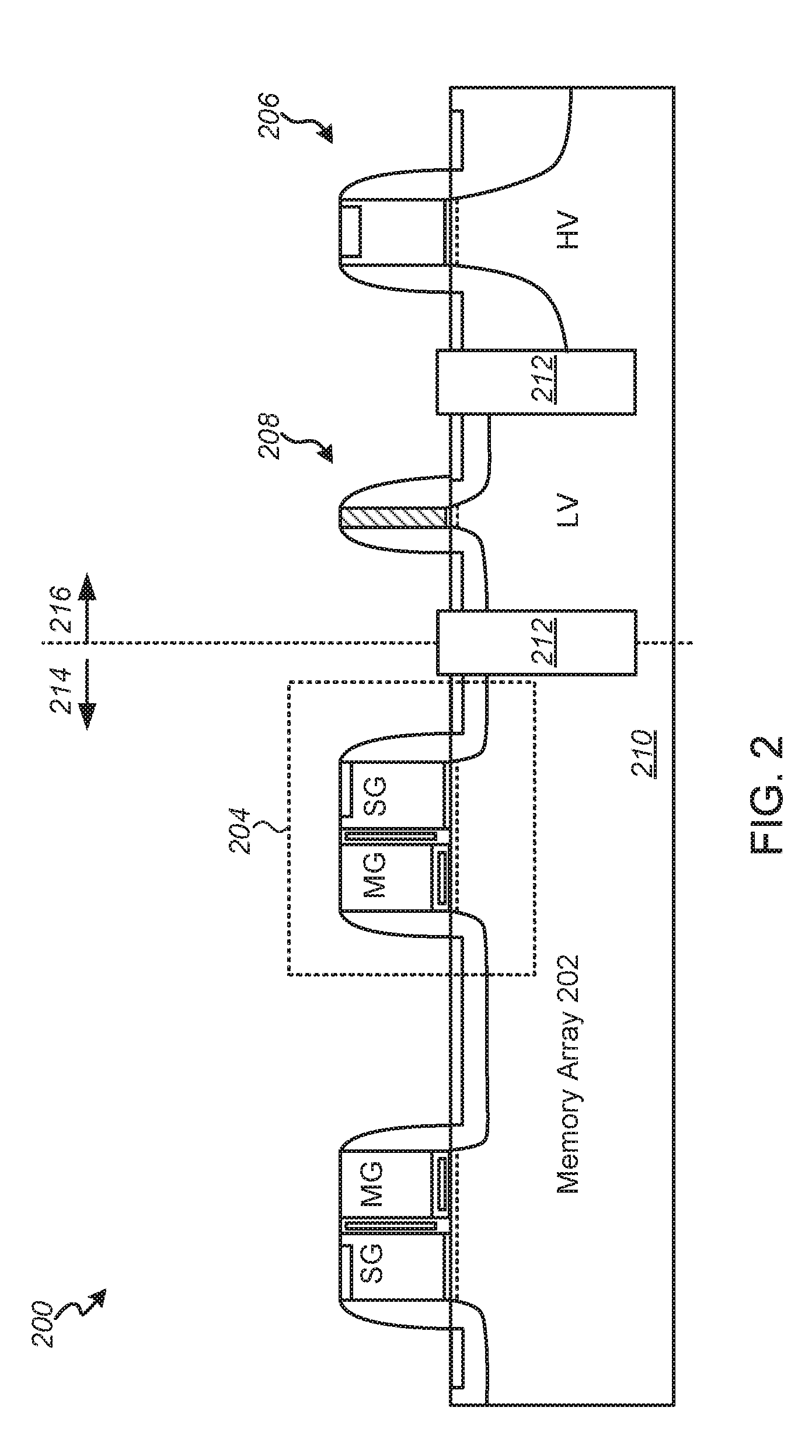

[0011] FIG. 2 is a block diagram of a cross-section of a portion of a NVM device including split-gate memory cells in a memory region, and a HVFET and logic FET in a peripheral region according to an embodiment of the present disclosure;

[0012] FIG. 3 is a detailed block diagram of a cross-section of an embodiment of a split-gate memory cell of FIG. 2 according to an embodiment of the present disclosure;

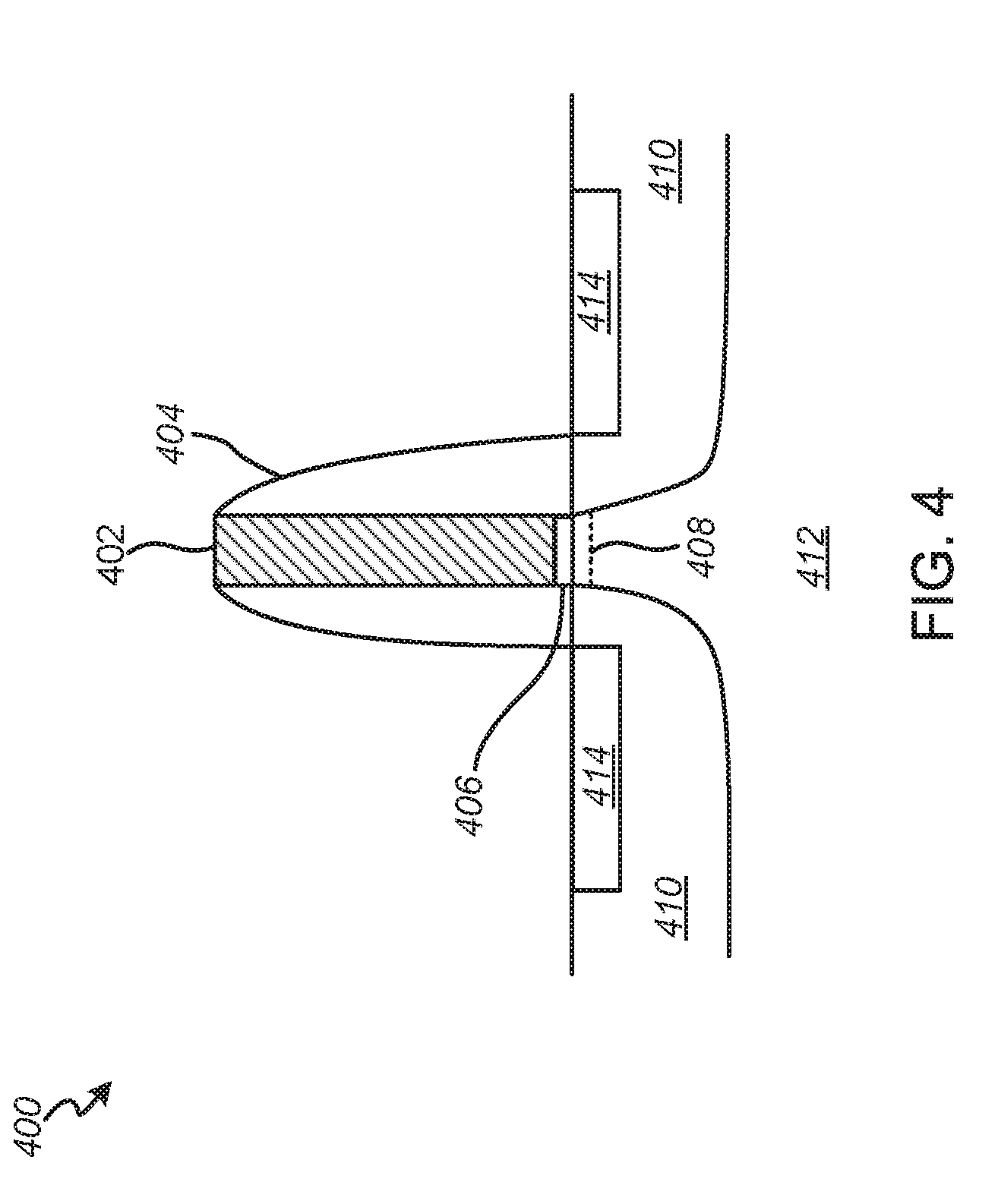

[0013] FIG. 4 is a detailed block diagram of a cross-section of an embodiment of a logic FET of FIG. 2 according to an embodiment of the present disclosure;

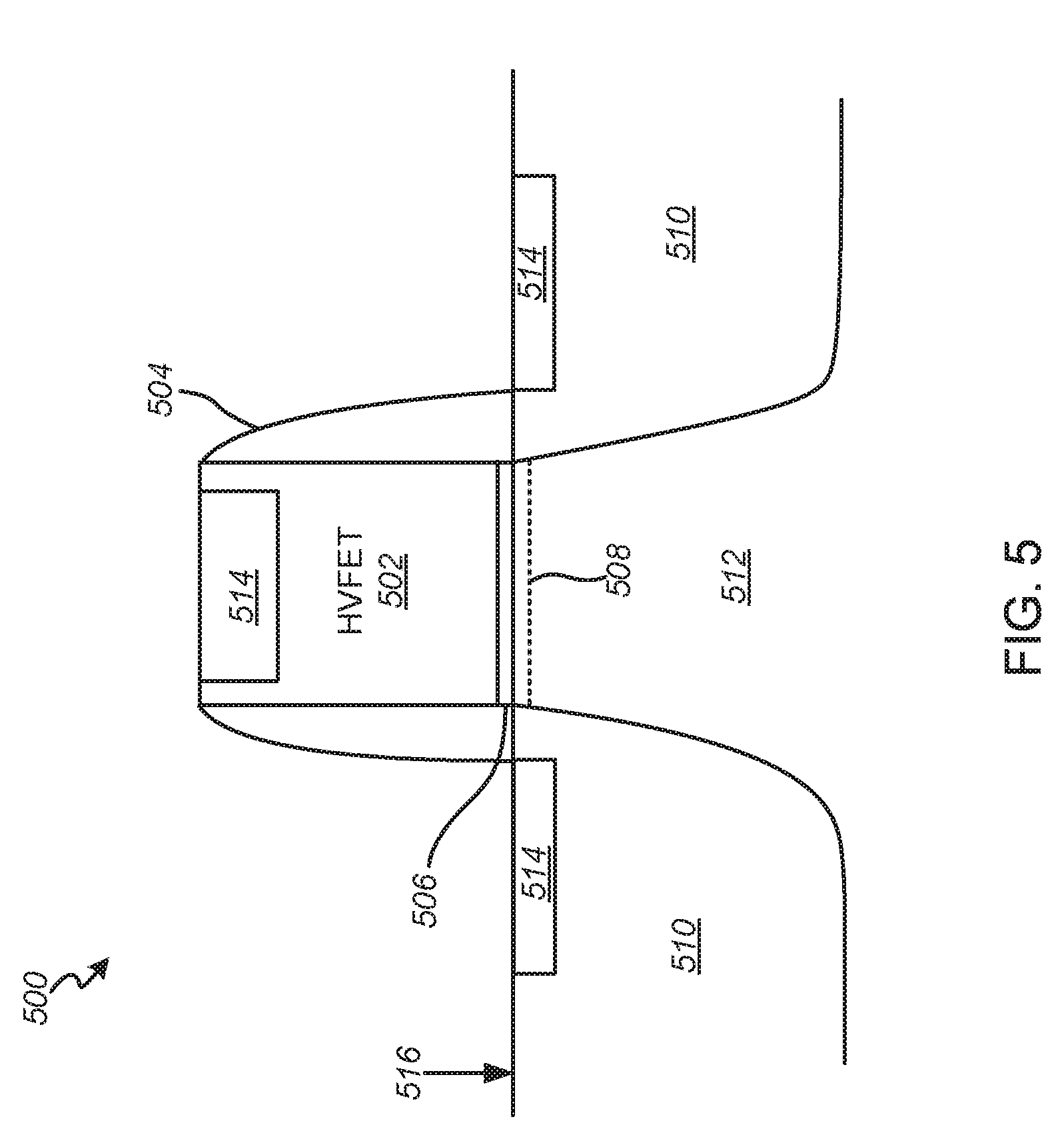

[0014] FIG. 5 is detailed a block diagram of a cross-section of an embodiment of a HVFET of FIG. 2 according to an embodiment of the present disclosure;

[0015] FIGS. 6A-6C is a flowchart depicting a method of manufacturing a NVM device according to an embodiment of the present disclosure;

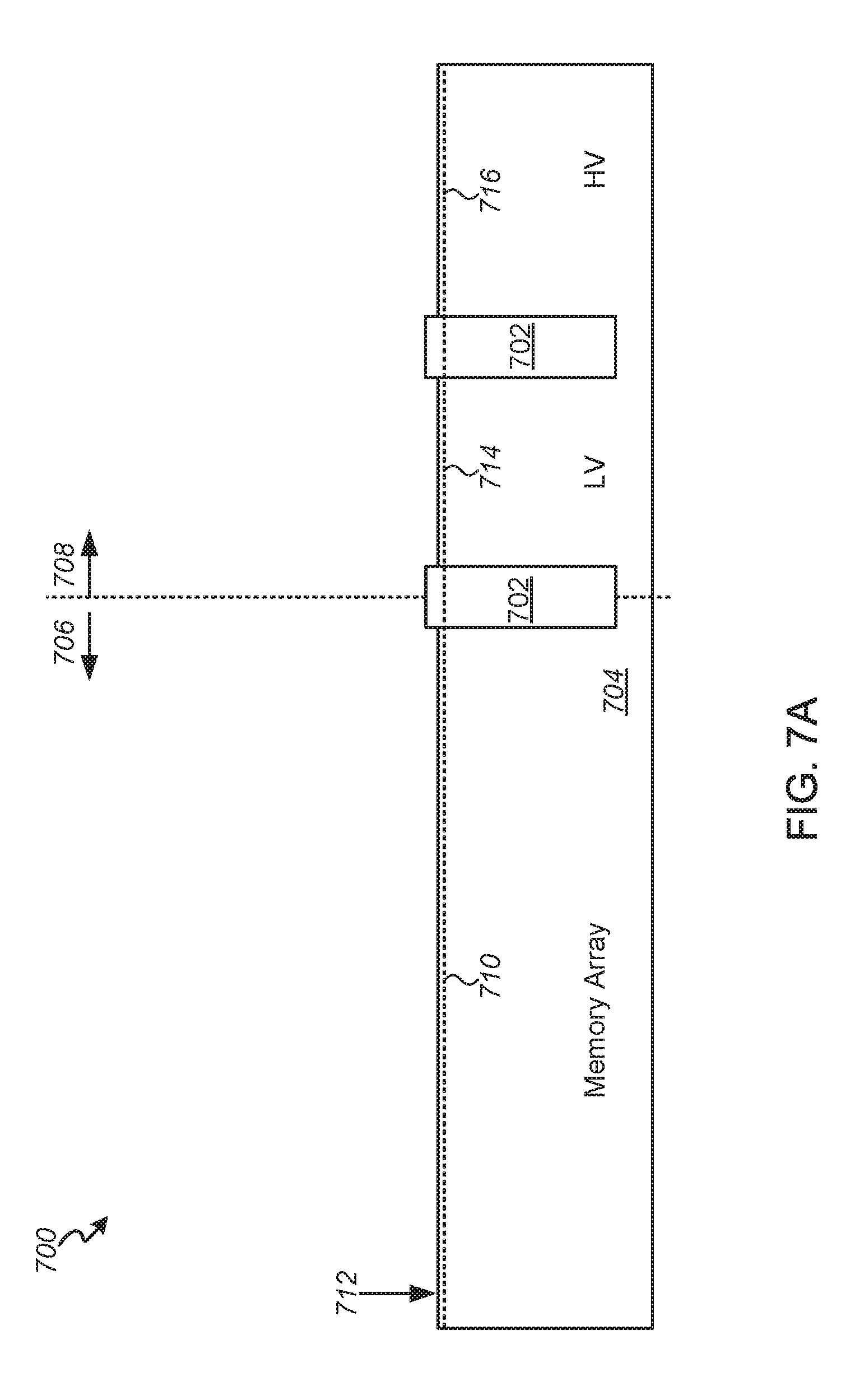

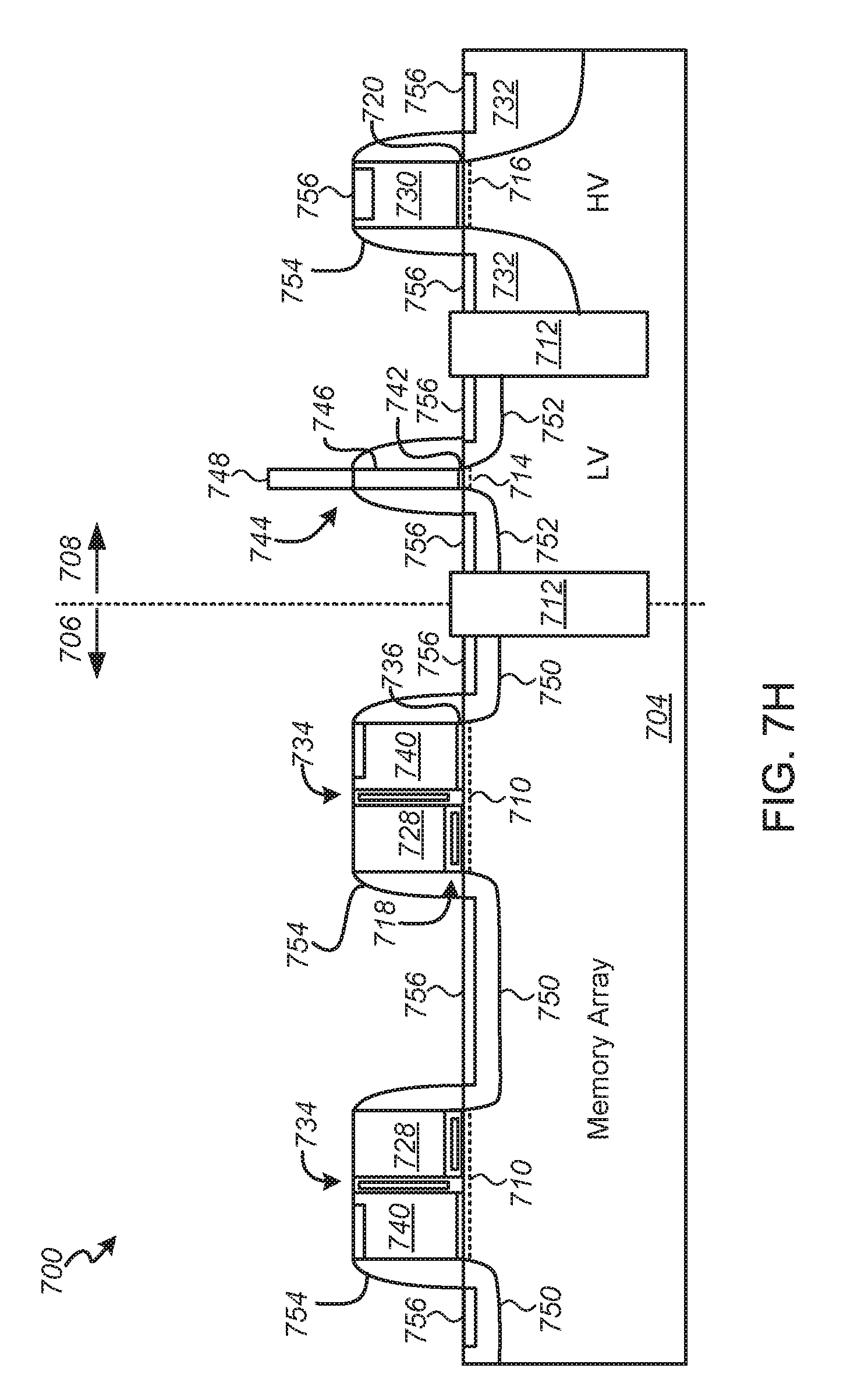

[0016] FIGS. 7A-7I illustrates a cross-section of a portion of a NVM device at various points during its manufacture according to the method of manufacturing of FIGS. 6A-6C.

[0017] The features and advantages of embodiments of the present invention will become more apparent from the detailed description set forth below when taken in conjunction with the drawings. In the drawings, like reference numbers generally indicate identical, functionally similar, and/or structurally similar elements.

DETAILED DESCRIPTION

[0018] This specification discloses one or more embodiments that incorporate the features of this invention. The disclosed embodiment(s) merely exemplify the present invention. The scope of the present invention is not limited to the disclosed embodiment(s). The present invention is defined by the claims appended hereto.

[0019] The embodiment(s) described, and references in the specification to "one embodiment," "an embodiment," "an example embodiment," etc., indicate that the embodiment(s) described may include a particular feature, structure, or characteristic, but every embodiment may not necessarily include the particular feature, structure, or characteristic. Moreover, such phrases are not necessarily referring to the same embodiment. Further, when a particular feature, structure, or characteristic is described in connection with an embodiment, it is understood that it is within the knowledge of one skilled in the art to effect such feature, structure, or characteristic in connection with other embodiments whether or not explicitly described.

[0020] Before describing the various embodiments in more detail, further explanation shall be given regarding certain terms that may be used throughout the descriptions.

[0021] The term "etch" or "etching" is used herein to generally describe a fabrication process of patterning a material, such that at least a portion of the material remains after the etch is completed. For example, it should be understood that the process of etching silicon involves the steps of patterning a masking layer (e.g., photoresist or a hard mask) above the silicon, and then removing the areas of silicon no longer protected by the masking layer. As such, the areas of silicon protected by the mask would remain behind after the etch process is complete. However, in another example, etching may also refer to a process that may or may not use a mask, and may or may not leave behind a portion of the material after the etch process is complete.

[0022] The above description serves to distinguish the term "etching" from "removing." When removing a material, substantially all of the material is removed in the process. However, in some embodiments, `removing` is considered to be a broad term that may incorporate etching.

[0023] The term "CMP" is used herein to generally describe a chemical mechanical polishing or planarization process used to smooth a surface on or over a substrate during semiconductor fabrication. The process generally uses combination of an abrasive and/or corrosive colloidal slurry in conjunction with mechanical forces provided by affixing the substrate to a dynamic polishing head pressing it against a rotating a polishing pad. The process removes material from the substrate thereby providing a planarized surface.

[0024] During the descriptions herein, various regions of the substrate upon which the memory cell, logic and high voltage transistors or devices are fabricated are mentioned. Although two different regions are described herein, it should be understood that any number of regions may exist on the substrate and may designate areas having certain, types of devices or materials. In general, the regions are used to conveniently describe areas of the substrate that include similar devices and should not limit the scope or spirit of the described embodiments.

[0025] The terms "deposit" or "dispose" are used herein to describe the act of applying a layer of material to the substrate. Such terms are meant to describe any possible layer-forming technique including, but not limited to, thermal growth, sputtering, evaporation, chemical vapor deposition, epitaxial growth, electroplating, etc. According to various embodiments, for instance, deposition may be performed according to any appropriate well-known method. For instance, deposition can comprise any process that grows, coats, or transfers material onto a substrate. Some well-known technologies include physical vapor deposition (PVD), chemical vapor deposition (CVD), electrochemical deposition (ECD), molecular beam epitaxy (MBE), atomic layer deposition (ALD), and plasma-enhanced CVD (PECVD), amongst others.

[0026] The "substrate" as used throughout the descriptions is most commonly thought to be silicon. However, the substrate may also be any of a wide array of semiconductor materials such as germanium, gallium arsenide, indium phosphide, etc. In other embodiments, the substrate may be electrically non-conductive such as a glass or sapphire wafer.

[0027] As used herein, "mask" may comprise any appropriate material that allows for selective removal (e.g., etching) of an unmasked portion a material. According to some embodiments, masking structures may comprise a photoresist such as Poly(methyl methacrylate) (PMMA), Poly(methyl glutarimide) (PMGI), a Phenol formaldehyde resin, a suitable epoxy, etc., or a hardmask including silicon nitride.

[0028] Before describing such embodiments in more detail, it is instructive to present an example memory cell and environment in which the present embodiments may be implemented.

[0029] FIG. 1 illustrates a schematic block diagram of a non-volatile memory (NVM) device 100 including a memory array 102 and a number of peripheral circuits including decoders, drivers, sense amplifiers and control circuits integrally formed on a single substrate to read from and write to the memory array 102. Referring to FIG. 1, the NVM device 100 further includes command and control circuitry 104, such as a micro-controller, micro-processor or state machine, to issue commands or control signals to each of the memory cells (not shown in this figure) in the memory array 102 along with other peripheral circuits for reading from or writing to the memory array. Generally, the peripheral circuits further include a row decoder 106, a column decoder 108, sense amplifiers 110 and a source line driver 112.

[0030] When a data word is to be stored or written to the NVM device 100, the row decoder 106 receives and decodes a memory address, which is then supplied to the command and control circuitry 104. The command and control circuitry 104 then selects a row of memory cells in the memory array 102 by applying a signal to wordlines (WL) of memory cells in the selected row, provides a column address to the column decoder 108, and provides a control signal to the source line driver 112. The column decoder 108 converts the column address and applies a signal to a bit-line (BL) of each memory cell in the selected column. The source line driver 112 then couples a high voltage, typically from about four to about ten volts DC to source lines of the memory cells to program or erase a NVM transistor in the memory cell.

[0031] Generally, when a data word is to be recalled or read out from the NVM device 100 the row decoder 106 receives, decodes and supplies the memory address, to the command and control circuitry 104, which then selects a row of memory cells in the memory array 102 by applying a signal to WLs of memory cells in the selected row, provides a column address to the column decoder 108, and provides a control signal to the source line driver 112, and the sense amplifiers 110 compare a data voltage for each memory cell in the selected row to a reference voltage to determine whether a logic `0` or `1` is read from the cell.

[0032] Each of the peripheral circuits may include a large number of low voltage, logic Field Effect Transistors (FETs), while the a row decoder 106 and a source line driver 112 further include a number of high voltage Field Effect Transistors (HVFETs) to support the voltages (e.g., 4 to 10V) required for program and erase operations.

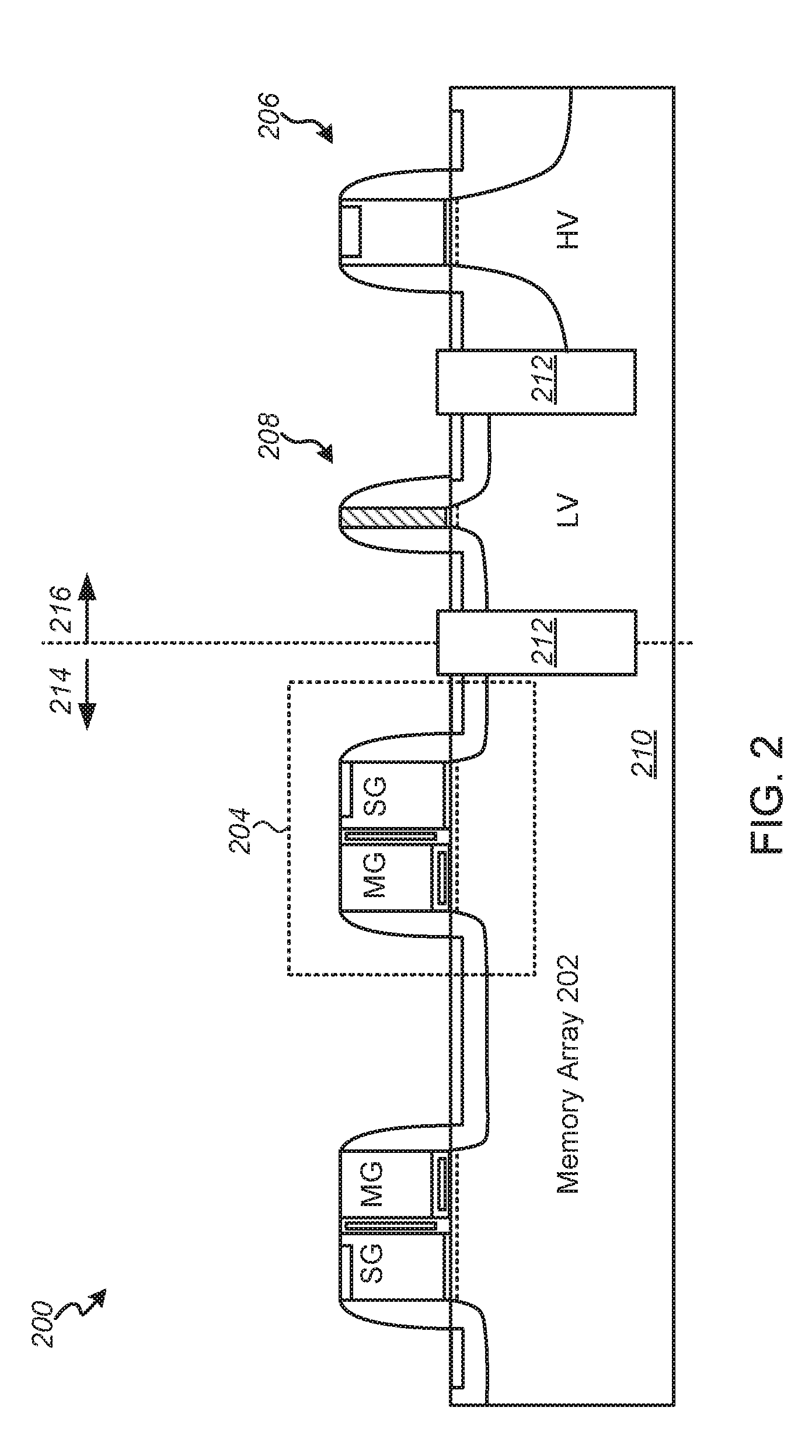

[0033] FIG. 2 illustrates a cross-section of a portion of a NVM device 200 that includes a memory array 202 formed on a substrate 210 in a memory region 214. The NVM device 200 further includes a HVFET 206 and a logic FET 208 formed in or on a peripheral region 216 of the same substrate 210. In the embodiment shown the memory cells are split-gate memory cells, each including a memory gate (MG) and a select gate (SG). Generally, as in the embodiment shown adjacent memory cells 204, HVFET 206 and logic FET 208 are isolated from one another by Shallow Trench Isolation structures (STI 212) that surround each area or region or device. In this example, substrate 210 includes a memory region 214 in which the memory cells 204 are located, and a peripheral region 216. The peripheral region 216 is further divided by STI 212 into a logic or low voltage area (LV) in which the logic FET 208 is formed, and HV area in which the HVFET 206 is formed. In the embodiment shown, the memory array 202 includes a plurality of split-gate memory cells 204, each including a memory gate (MG) and a select (SG). It should be understood that the cross-section of FIG. 2 is only exemplary, and that the peripheral region 216 may further include additional integrated circuit components such as resistors, capacitors, inductors, etc., not shown in this figure as well as the logic FET 208 and HVFET 206. It should also be understood that the memory region 214 and peripheral region 216 may be located in any area of substrate 210, including non-adjacent areas, and may include multiple instances of each of the different regions 214/216.

[0034] Substrate 210, and indeed substrates in general as used throughout the description, can be silicon according to various embodiments. However, the substrate 210 may also be any of a wide array of semiconductor materials such as germanium, gallium arsenide, indium phosphide, etc. In other embodiments, the substrate 210 may be electrically non-conductive such as a glass or sapphire wafer.

[0035] The memory cell 204, logic FET 208 and HVFET 206 will now be described in greater detail with reference to FIGS. 3 through 5.

[0036] FIG. 3 illustrates an example of a split-gate memory cell 300 including a memory gate (MG 302) and a select gate (SG 304) formed over a common or shared channel 306 on a substrate 308. Each memory cell includes first and second source/drain (S/D) regions 310 and 312. Regions 310 and 312 form either the source or drain of the split-gate memory cell 300 depending on what potentials are applied to each. In split-gate memory cells 300, for convenience, region 310, which is adjacent to the SG 304, is commonly referred to as the drain, while region 312, adjacent to the MG 302, is commonly referred to as the source, independent of the relative biases. Generally, the substrate 308 is a p-type silicon substrate or includes a p-type well in which the memory cells 300 are formed, while regions 310 and 312 are moderately to heavily doped with an n-type dopant. However, it is also possible for substrate 308 to be n-type while regions 310 and 312 are doped with a p-type dopant.

[0037] The MG 302 and SG 304 both include a doped polysilicon conductor. The doped polysilicon conductor of SG 304 is disposed on or over a select gate dielectric 314, while the doped polysilicon conductor of MG gate 302 is disposed on or over a multi-layer, charge storing or trapping stack 316 having one or more charge trapping layers between dielectric layers. In one example, charge trapping stack 316 includes a charge trapping silicon nitride layer 316b sandwiched between two silicon dioxide layers 316a, 316c to create a three-layer structure collectively and commonly referred to as an "ONO stack." Other charge trapping stacks 316 may include a polysilicon charge storing layer 316b sandwiched between two dielectric layers 316a, 316c to create a floating gate MOS field-effect transistor (FGMOS). A vertical, inter-gate dielectric 318 is also disposed between SG 304 and MG 302 to electrically isolate the doped polysilicon conductors of the gates. In some embodiments, such as that shown, the inter-gate dielectric 318 may include one or more of layers or films of dielectric materials having different dielectric properties. For example, the inter-gate dielectric 318 can include an ONO dielectric similar to that of the charge trapping dielectric 316.

[0038] The memory cell 300 further includes self-aligned silicides or SALICIDEs 320 over surfaces of the select gate 304 and S/D regions 310 and 312, and a sidewall spacer 322 surrounding both the SG and MG. The sidewall spacer 322 can include one or more layers of a dielectric material, such as silicon oxide or silicon nitride. The SALICIDEs 320 reduce resistance between contacts (not shown in this figure) to active regions of the memory cell, such as the S/D regions 310 and 312, and between contacts to the polysilicon of the SG 304 and, optionally in an embodiment not shown in this figure to the MG 302. In some embodiments, such as that shown in FIG. 3 the SALICIDE 320 formed on top of the SG 304 is pulled back or farther away from the sidewall adjacent the inter-gate dielectric 318 to provide further isolation against shorts or leakage between the SALICIDE and the MG 302. It is to be understood that this description is meant to provide a general overview of a split-gate architecture and that, in actual practice, many more detailed steps and layers are provided to form the final memory cell 300.

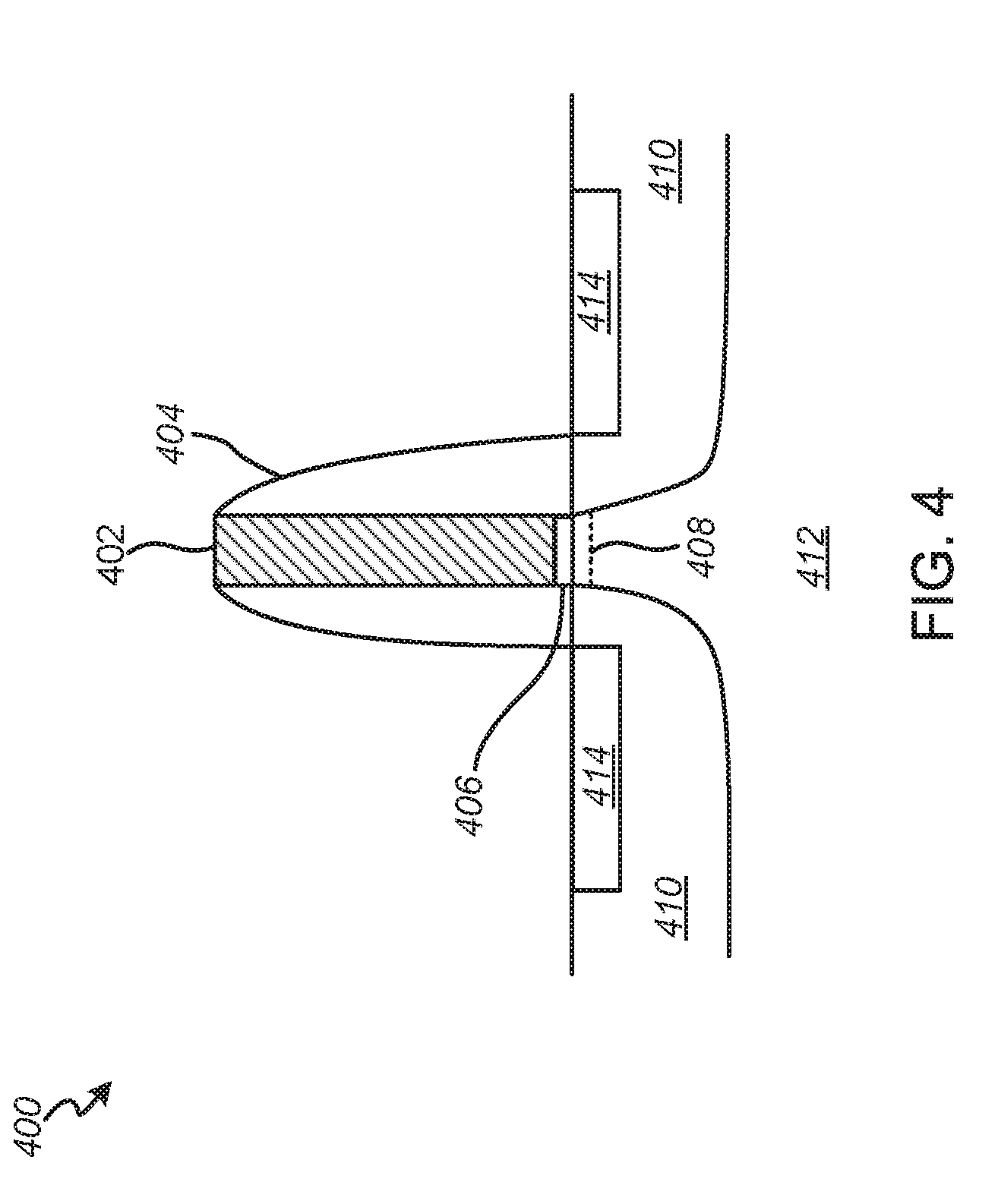

[0039] FIG. 4 illustrates an embodiment of a logic FET 400 suitable for use in the NVM device of FIGS. 1 and 2. In the embodiment shown, the logic FET 400 is a High-K Metal-Gate (HKMG) logic FET having a metal-gate 402 surrounded by a sidewall spacer 404 and a high-k gate dielectric 406 overlying a channel 408 separating source and drain (S/D) regions 410 formed in a substrate 412. The logic FET 400 further includes self-aligned silicides or SALICIDEs 414 on or over surfaces of the S/D regions 410 to reduce resistance between contacts (not shown in this figure) and the S/D regions. The metal-gate 402 can be made of any suitable metal or alloy, including but is not limited to, aluminum, copper, titanium, tungsten and alloys thereof. Suitable high-k dielectric material for the high-k gate dielectric 406 can include, but is not limited to, hafnium oxide, zirconium oxide, hafnium silicate, hafnium oxy-nitride, hafnium zirconium oxide and lanthanum oxide. Alternatively, the high-k gate dielectric 406 can include one or more layers suitable high-k dielectric material. The sidewall spacer 404 can include one or more layers of a dielectric material, such as silicon oxide or silicon nitride.

[0040] The metal-gate 402 of HKMG logic FETs 400 have a narrower width or narrower channel length than gates of previous generations of logic FETs, and therefore can improve performance of the memory device and reduce a size of a die or chip on which the memory device is fabricated.

[0041] In the past, with gates having lateral dimensions of about 40 nanometers (nm) and larger it was possible to integrally form memory cells, HVFETs and logic transistors on a single substrate using a thick gate polysilicon. However, as the lateral dimensions of circuit elements, such as gates, have continued to shrink it has become necessary to restrict heights of the circuit elements. In particular, the height of the metal gate 402 of a HKMG logic FET made using a gate replacement process is restricted to from about 300 to about 1000 angstroms (.ANG.) to ensure the high aspect ratio openings resulting from the etching or removal of a sacrificial gate are completely filled with metal.

[0042] In a gate replacement process, described in greater detail below with reference to FIGS. 6A-6C and 7A-7I, a sacrificial or dummy gate is formed over the high-K gate dielectric 406, a sidewall spacer 404 formed around the sacrificial gate, and an inter-level dielectric (ILD) formed over the sidewall spacer and sacrificial gate. The ILD is then polished and planarized using CMP to expose a top of surface of the sacrificial gate, and the sacrificial gate removed from inside the sidewall spacers 404 using a selective etch process. The metal gate 402 is then deposited inside the sidewall spacers 404. Because the narrowest width of the metal gate can be from about 10 to about 40 nm, the height of the metal gate 402 of the HKMG logic FET is restricted to from about 300 to about 1000 .ANG.. Furthermore, because of the CMP process necessary to planarize an inter-layer dielectric (not shown in this figure), the sidewall spacers 404 and expose the sacrificial gate, the heights of the gates of memory cells and HVFETs that are formed prior to or concurrently with the HKMG logic FET 400, and co-planar therewith, are also restricted to similar heights.

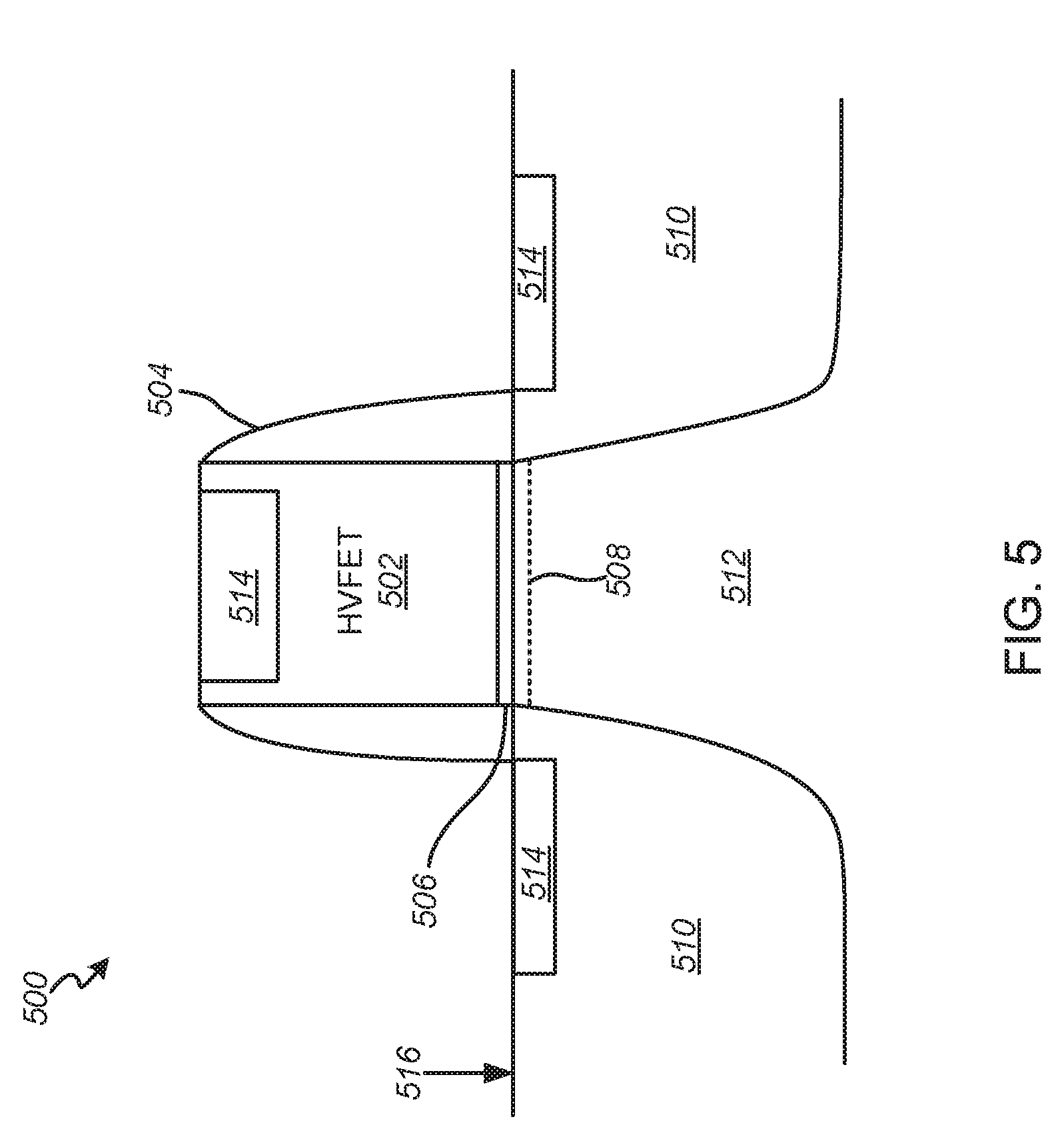

[0043] FIG. 5 illustrates an embodiment of a HVFET 500 suitable for use in the NVM device of FIGS. 1 and 2. The HVFET 500, which is fabricated according to an embodiment of the present disclosure, described in detail below with reference to FIGS. 6A-6C and 7A-7I, is capable of handling voltages of up to about 20 volts in magnitude. The HVFET 500 includes a doped polysilicon gate 502, surrounded by a sidewall spacer 504 and disposed on or over a HVFET gate dielectric 506 overlying a channel 508 separating source and drain (S/D) regions 510 formed in a substrate 512. The sidewall spacer 504 can include one or more layers of a dielectric material, such as silicon oxide or silicon nitride. The HVFET 500 further includes self-aligned silicides or SALICIDEs 514 formed on or over surfaces of the doped polysilicon gate 502 and the S/D regions 510 to reduce resistance between contacts (not shown in this figure) the doped polysilicon gate and the S/D regions.

[0044] In order to provide the required a high breakdown voltage, the HVFET 500 has a thicker HVFET gate dielectric 506, a longer channel 508, and deep S/D regions 510. The deep S/D regions 510 are formed using a high energy, low dose implant after the HVFET gate 502 formation to form a Lightly Doped Drain (LDD). By deep it is meant S/D regions 510 extending to depth of from about 400 to about 2000 .ANG. below a surface 516 of the substrate 512. By a high energy, low dose implant it is meant implanting an appropriate ion species at an energy of from about 30 to about 100 kilo-electron volts (keV), and a dose of from about 1e12 cm.sup.-3 to about 1e14 cm.sup.-3.

[0045] Previous generations of HVFETs relied on a sufficiently thick doped polysilicon gate 502 to prevent the implanted ions from penetrating through the gate stack and reaching the channel 508 during the high-energy drain region implant. However, as noted above due to limitations imposed by the gate replacement process used to form the HKMG logic FET 400 the HVFET gate 502 needs to be equal to or less than about 1000 .ANG.. Using an embodiment of the method of present disclosure the HVFET 500 can be fabricated to have deep S/D regions 510, fabricated in part by the LDD implant, with HVFET gate 502 formed from a thin polysilicon gate layer and having a gate height of from about 300 to about 1000 .ANG..

[0046] An embodiment of a method for manufacturing a NVM device including a memory cell, a HKMG logic FET and a HVFET embedded or integrally formed on a single substrate will now be described in detail with reference to FIGS. 6A-6C and 7A through 7I. FIGS. 6A-6C is a flowchart illustrating an embodiment of a method or process flow. FIGS. 7A through 7I are block diagrams illustrating cross-sectional views of a portion of a NVM device 700 during fabrication of the NVM device 700 according to the method of FIGS. 6A-6C.

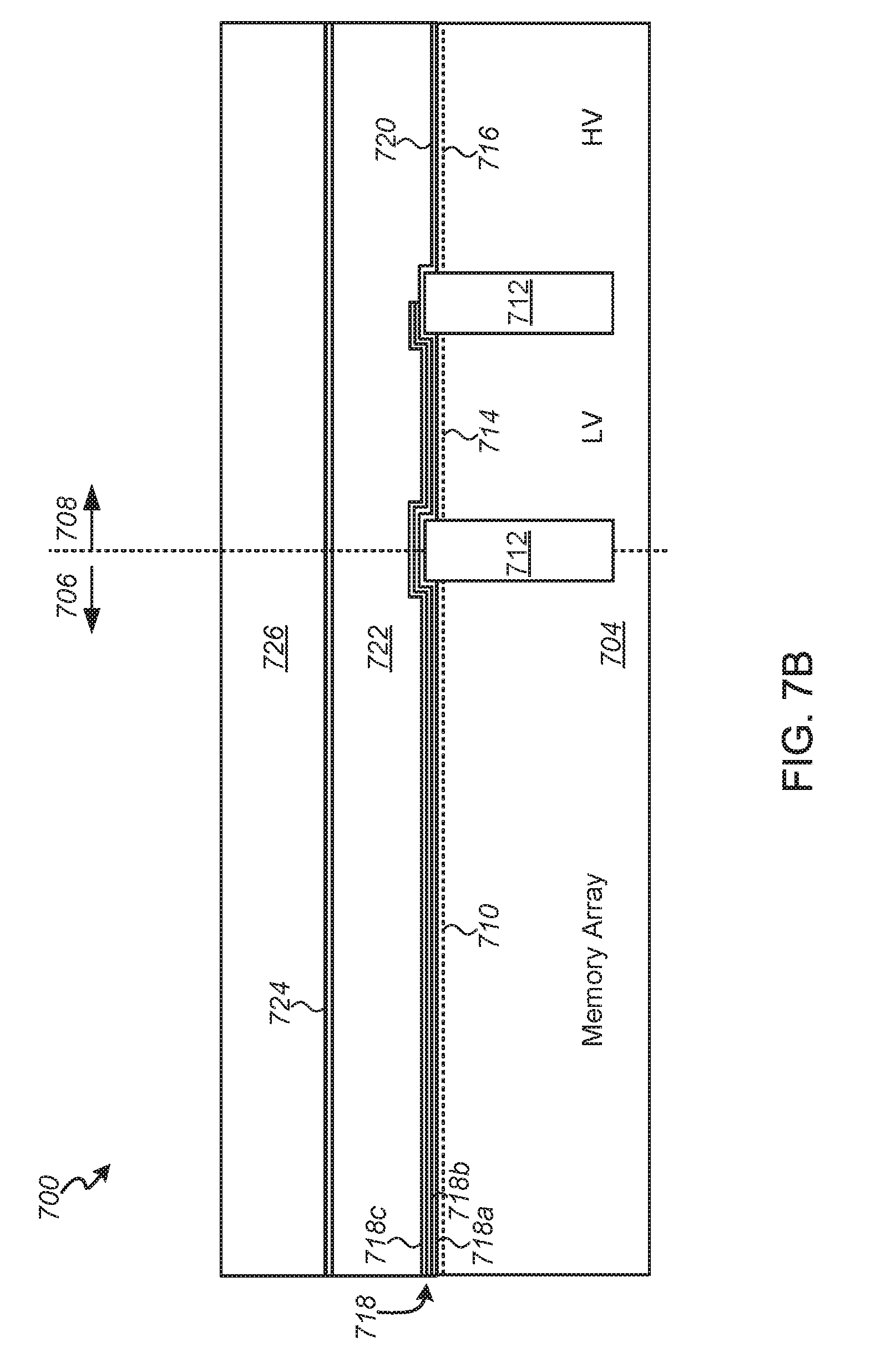

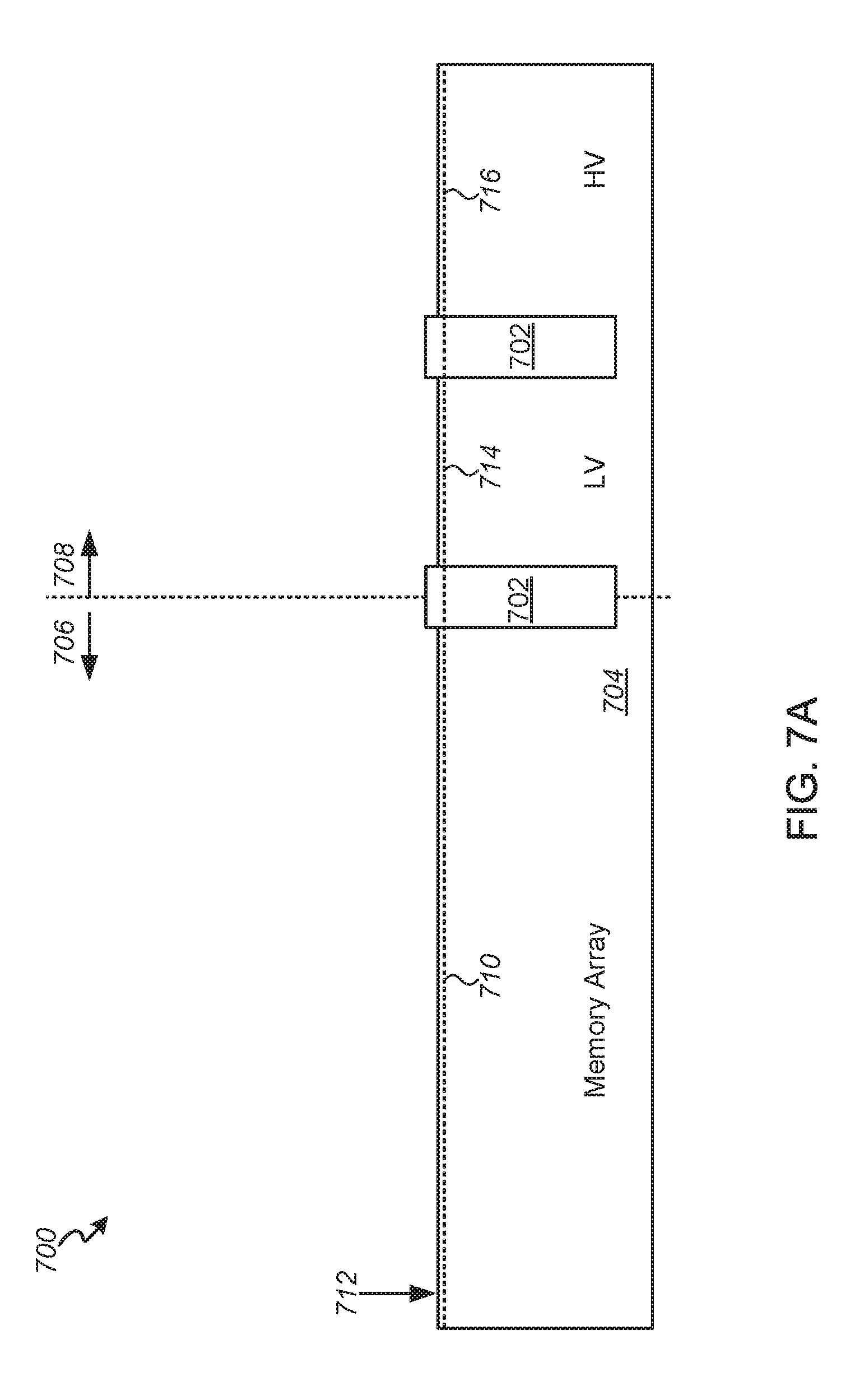

[0047] Referring to FIGS. 6A and 7A, the process begins with forming shallow trench isolation (STI) structures 702 in a substrate 704 to electrically isolate an area in which a memory array is to be formed in a memory region 706 from a peripheral region 708, and to isolate a low voltage (LV) area in which a HKMG logic FET is to be formed from a high voltage (HV) area in which a HVFET is to be formed (step 602).

[0048] Next, a contiguous first channel 710 for a memory cell or cells is formed in a surface 712 of the substrate 704 in the memory region 706, a second channel 714 for the HKMG logic FET is formed in LV area of the peripheral region 708, and a third channel 716 for the HVFET is formed in the HV area (step 604). The channels 710, 714 and 716 can be formed by implanting an appropriate ion species using ion implantation technique. For example, a p-type channel implant can include implanting boron B.sup.+ ions at energy of from about 5 to about 50 KeV, and to a concentration or dose of from about 1e11 cm.sup.-3 to about 5e13 cm.sup.-3, while a n-type channel implant can include implanting phosphorous or arsenic ions at a similar energy and to a similar dose.

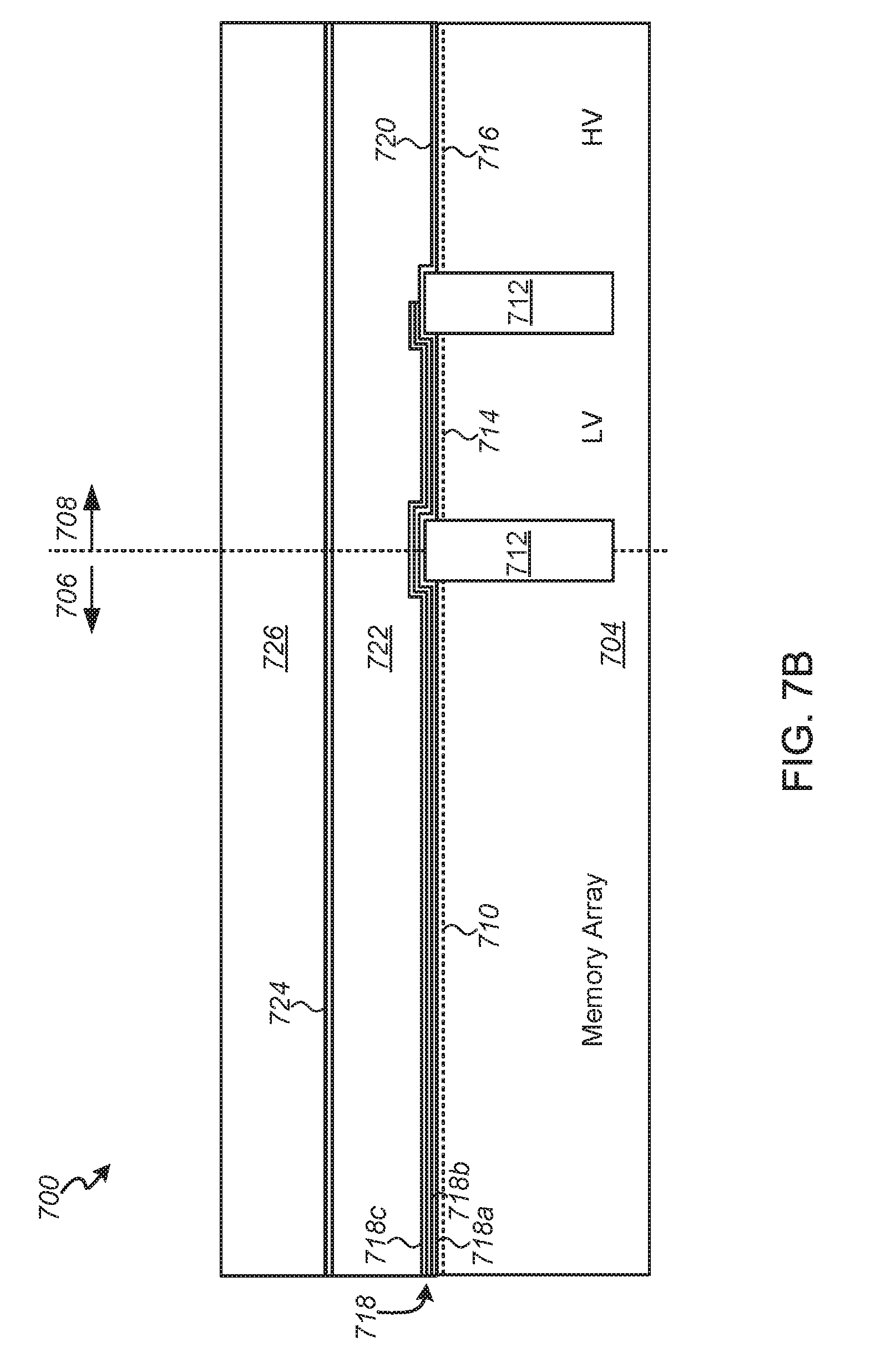

[0049] Referring to FIGS. 6A and 7B, the process continues with forming a charge-trapping stack 718 overlying the first channel 710 in the memory region 706, and a high voltage (HV) gate dielectric 720 overlying the third channel 716 in the HV area in the peripheral region 708 of the substrate 704 (step 606). In one embodiment, the charge-trapping stack 718 is formed by depositing or forming a tunnel layer 718a, a charge trapping or storage layer 718b, and a blocking layer 718c. The tunnel layer 718a can include a dielectric material, such as silicon dioxide (SiO.sub.2), and can be either thermally grown or deposited by CVD, PECVD or ALD. A suitable dielectric charge trapping layer 718b can include one or more layers of silicon nitride (SiN), silicon-rich nitride, or silicon oxynitride (SiON), deposited by CVD, PECVD or ALD. Alternatively, the charge-storage layer 718b can include a conducting floating gate charge-storage layer polysilicon deposited by CVD, PECVD or ALD. The blocking layer 718c can include one or more layers of either a thermally grown or deposited silicon dioxide (SiO.sub.2) and/or a high-k dielectric deposited by CVD, PECVD or ALD. Suitable high-k dielectric material for the blocking layer 718c can include, but is not limited to, hafnium oxide, zirconium oxide, hafnium silicate, hafnium oxy-nitride, hafnium zirconium oxide and lanthanum oxide

[0050] Since the surface 712 of the substrate in 704 in the LV area in which a HKMG logic FET is to be formed is stripped prior to forming the HKMG logic FET, the charge-trapping stack 718 can also be allowed to extend over the LV area of the peripheral region 708, as shown.

[0051] The HV gate dielectric 720 is formed overlying the third channel 716 in the HV area of the peripheral region 708. The HV gate dielectric 720 can include one or more layers of a suitable dielectric material, such as silicon dioxide (SiO.sub.2) or silicon nitride (SiN) deposited by CVD, PECVD or ALD. Alternatively, the HV gate dielectric 720 can include a high-K dielectric material, such as hafnium oxide, zirconium oxide, hafnium silicate, hafnium oxy-nitride, hafnium zirconium oxide or lanthanum oxide.

[0052] Next, a first polysilicon gate layer 722 is deposited over the charge-trapping stack 718 and the HV gate dielectric 720 (step 608). The first polysilicon gate layer 722 can be a doped polysilicon layer, and deposited to a thickness of from about 300 to about 1000 .ANG. by CVD, PECVD or ALD. Alternatively, the first polysilicon gate layer 722 can be deposited as an undoped polysilicon layer, which is subsequently doped with an appropriate ion species and to an appropriate dose to function as a MG and HV gate.

[0053] A thin, dielectric layer 724 is formed over the first polysilicon gate layer 722 (step 610). The dielectric layer 724 can include a silicon dioxide (SiO.sub.2) thermally grown or deposited to a thickness of from about 20 to about 500 .ANG. by CVD, PECVD or ALD.

[0054] Next, a height-enhancing (HE) film 726 is deposit over the dielectric layer 724 (step 612). The HE film 726 can include an amorphous silicon or a polysilicon film deposited to a thickness of from about 400 to about 1000 .ANG. by CVD, PECVD or ALD. Generally, the thickness of the HE film 726 is selected in view the thicknesses of the underlying dielectric layer 724 and first polysilicon gate layer 722, and the energy and dose of the HVFET region implant to be sufficient to prevent dopants from the region implant from reaching the third channel 716. For example, for a high energy, low dose region implant having an energy of from about 30 to about 100 keV, and a dose of from about 1e12 cm.sup.-3 to about 1e14 cm.sup.-3, a combined thickness of the first polysilicon gate layer 722, the dielectric layer 724 and the HE film 726 of from about 1000 to about 2500 .ANG.. It has been found that a combined thickness in this range is sufficient to substantially prevent implanted ions from a deep region implant from penetrating through a HVFET gate stack including the first polysilicon gate layer 722, the dielectric layer 724 and the HE film 726 and reaching the third channel 716.

[0055] Referring to FIGS. 6A and 7C, the HE film 726, the dielectric layer 724, the first polysilicon gate layer 722, the HV gate dielectric 720 and the charge-trapping stack 718 are patterned to form a memory gate (MG 728) in the memory region 706 and a HVFET gate 730 in the peripheral region 708 (step 614). The HE film 726, the dielectric layer 724, the first polysilicon gate layer 722 and the charge-trapping stack 718 can be left in place over the LV area. The patterning can be accomplished using standard photolithographic techniques to form a mask over the surface of the HE film 726, and then anisotropically etching the HE film and underlying layers using any standard dry or wet etching technique. For example, polysilicon layers can be dry etched using a low pressure etch at a moderate power (about 500 W) in a plasma of polysilicon etch chemistries, such as CHF.sub.3 or C.sub.2H.sub.2 or HBr/O.sub.2; silicon dioxides (SiO.sub.2) can be either wet or dry etched; and silicon nitride (SiN) can be dry etched using a low pressure plasma of a fluorine containing gas, such as CF.sub.4, or CHF.sub.3. After the HE film 726, the dielectric layer 724, the first polysilicon gate layer 722, the HV gate dielectric 720 and the charge-trapping stack 718 have been etched or patterned to form the MG 728 and HVFET gate 730 in shown in FIG. 7C, any remaining photoresist from the mask (not shown in this figure) is stripped and a wet clean performed. Alternatively, the MG 728 and HVFET gate 730 can patterned in separate etching steps through use of an additional mask layer.

[0056] Optionally, a pre-amorphizing implant can be performed to amorphize the HE film 726 remaining over the MG 728 and HVFET gate 730 (step 616). The pre-amorphizing implant can be performed using any suitable semiconductor material or dopant. For example, the pre-amorphizing implant can include implanting germanium (Ge) ions at an energy of from about 5 to about 50 keV, and to a dose of from about 1e13 cm.sup.-3 to about to about 5e15 cm.sup.-3. Amorphizing the HE film 726 prior to performing a high energy, low dose implant to form a deep, Lightly Doped Drain (LDD) of the HVFET, improves the ability of the HE film 726 to prevent implanted ions from penetrating through the HVFET gate stack and reaching the channel 716.

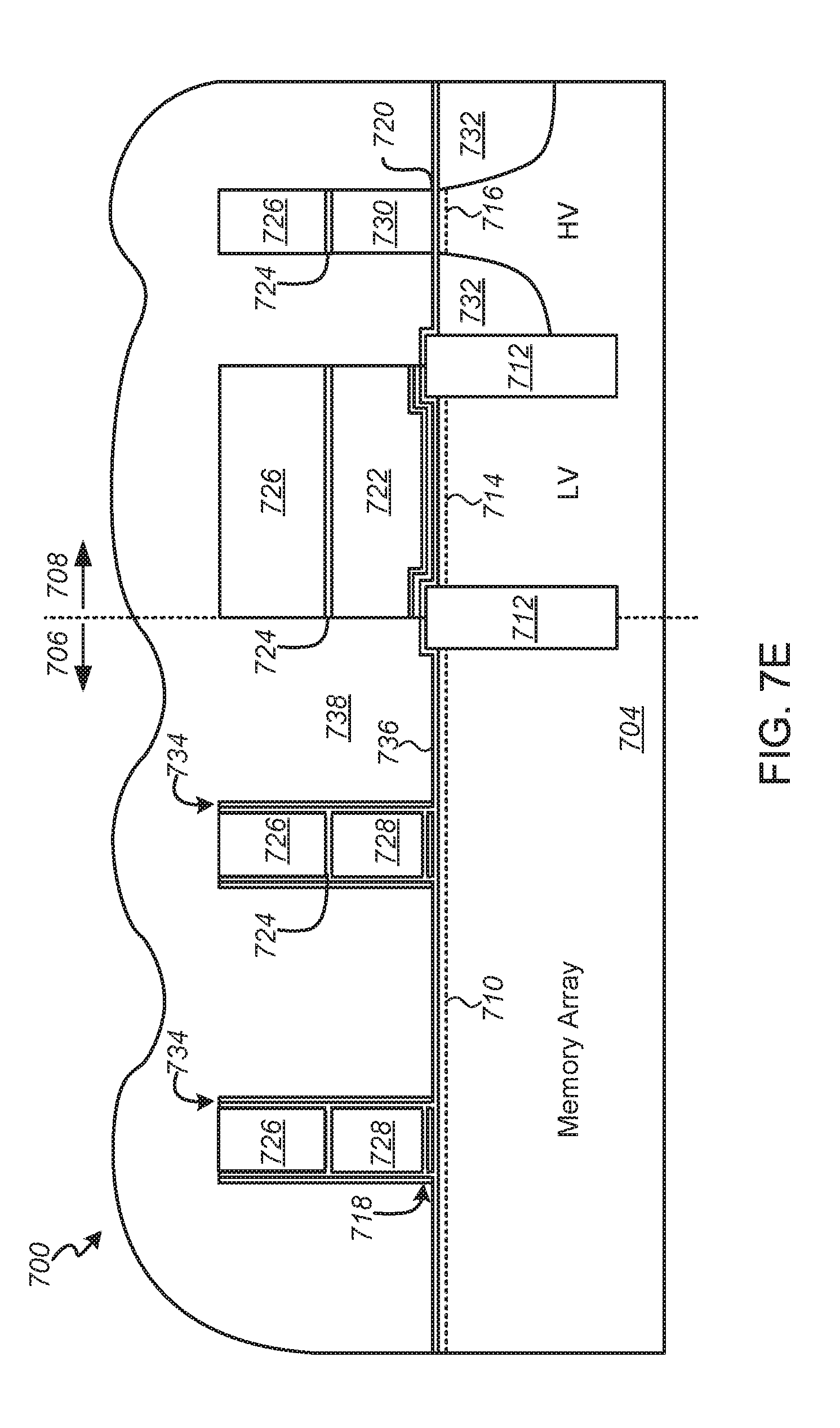

[0057] Referring to FIGS. 6B and 7D a high energy, low dose implant is performed to form one or more LDDs 732 in the substrate 704 adjacent to the HVFET gate 730 (step 618). As noted above, the implant can include implanting an appropriate ion species at an energy of from about 30 to about 100 kilo-electron volts (keV), to a dose of from about 1e12 cm.sup.-3 to about 5e14 cm.sup.-3, which will provide LDDs 732 extending to depth of from about 400 to about 2000 .ANG. below a surface of the substrate 704.

[0058] An inter-gate dielectric 734 is then formed on sidewalls of the MG 728 (step 620). As noted above, the inter-gate dielectric 734 can include one or more of layers or films of dielectric materials having different dielectric properties. For example, the inter-gate dielectric 734 can include an ONO dielectric similar to that of the charge trapping stack 718, and can be deposited using the same CVD, PECVD or ALD techniques to a thickness of from about 100 to about 500 .ANG..

[0059] Next, any material remaining on the surface of the substrate 704 from formation of the inter-gate dielectric 734 in the memory region 706 is removed, and a SG gate dielectric 736 is formed over the surface of the substrate in the memory region for a SG to be formed adjacent the MG 728 (step 622). It will be understood the material remaining on the surface can be removed using an anisotropic dry etch using any standard oxide and nitride plasma etch chemistries described above. The SG gate dielectric 736 can include one or more layers of a suitable dielectric material, such as silicon oxide or silicon nitride deposited by CVD, PECVD or ALD to a thickness of from about 10 to about 60 .ANG.. Alternatively, the SG gate dielectric 730 can include a suitable high-K dielectric material, such as hafnium oxide, zirconium oxide, hafnium silicate, hafnium oxy-nitride, hafnium zirconium oxide and lanthanum oxide.

[0060] Referring to FIGS. 6B and 7E a second polysilicon gate layer 738 is deposited over the MGs 728, the HVFET gate 730 and the surface 712 of the substrate 704 (step 624). As with the first polysilicon gate layer 722, the second polysilicon gate layer 738 can include a doped polysilicon layer or an undoped polysilicon layer that is subsequently doped, and is deposited to a thickness of at least about 400 .ANG. by CVD, PECVD or ALD.

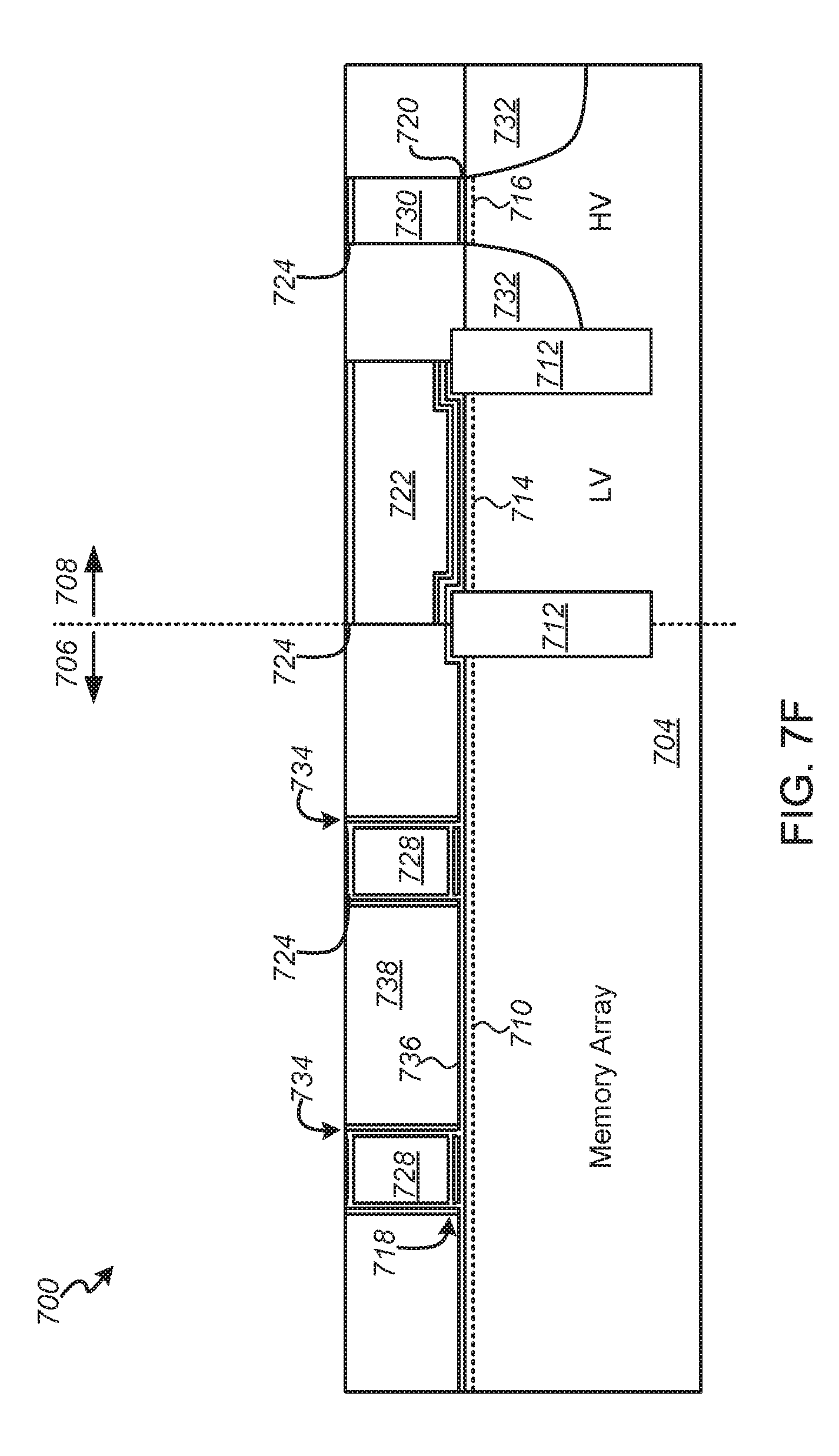

[0061] Referring to FIGS. 6B and 7F a layer on or over surface of the substrate 704 is planarized or polished using a plasma etch, a CMP process, or a combination thereof to remove the portion of the second polysilicon gate layer 738 and the HE film 726 over the MGs 728 and HVFET gate 730, and to planarize the second polysilicon gate layer (step 626). The portions of the dielectric layer 724 remaining on the MGs 728 and HVFET gate 730 can serve as a stop layer for the CMP or the plasma etch used for the planarization.

[0062] Referring to FIGS. 6B and 7G, the gate stack including the first polysilicon gate layer 722 and the dielectric layer 724 in the LV area of the periphery region of 708 is removed, exposing the surface 712 of the substrate 704. A high-K gate dielectric 742 deposited on the exposed surface, a doped or undoped polysilicon or amorphous silicon layer deposited on the high-K gate dielectric, and both layers patterned to form a logic gate pattern 744 in the LV area (step 627). After that, the second polysilicon gate layer 738 is removed from one side, e.g. a source side, of the memory cell and from the HV area, the second polysilicon gate layer 738 planarized, and patterned to form select gates (SG 740) on the other side, e.g. a drain side, of the memory cell drain in the memory region 706 (step 628). For example, polysilicon layers can be dry etched using a low pressure etch at a moderate power (about 500 W) in a plasma of standard polysilicon etch chemistries, such as CHF.sub.3 or C.sub.2H.sub.2 or HBr/O.sub.2; silicon dioxides can be either wet or dry etched; and nitride layers can be etched using a low pressure nitride etch in a plasma of a fluorine containing gas, such as CF.sub.4, or CHF.sub.3.

[0063] The high-k gate dielectric 742 can include one or more layers of high-k dielectric material, such as hafnium oxide, zirconium oxide, hafnium silicate, hafnium oxy-nitride, hafnium zirconium oxide and lanthanum oxide, deposited to a thickness of from about 10 to about 80 .ANG., using by CVD, PECVD or ALD.

[0064] The logic gate pattern 744 includes a number of dummy or sacrificial gates 746 formed from a doped or undoped polysilicon or amorphous silicon deposited to a thickness of from about 300 to about 1000 .ANG., using by CVD, PECVD or ALD, and patterned using a patterned hardmask 748 and any of the polysilicon or silicon dry etching techniques described above. The patterned hardmask 748 is generally formed by patterning a layer of dielectric material, such as silicon dioxide (SiO.sub.2) or silicon nitride (SiN), using standard photolithographic and etching techniques.

[0065] Referring to FIGS. 6C and 7H, dopant ions of an appropriate species are implanted to form a source/drain (S/D) regions 750, in the memory region 706 adjacent to the MG 728 and SG 740, and S/D regions 752 in the LV area in the peripheral region 70 adjacent to logic gate pattern 744 (step 630). Generally, because these S/D regions 750/752 are not deep, the implants are typically performed at a lower energy of from about 1 to about 50 kilo-electron volts (keV), to a moderately heavy dose of from about 1e13 cm.sup.-3 to about 2e15 cm.sup.-3. Because of the lower energy of these implants the thin polysilicon of the HVFET gate 730 is sufficiently thick to prevent any implanted ions from reaching the channel 716. However, to avoid undesirably increasing the concentration of dopants in the LDD 732, the HV area is preferably masked prior to performing the implant.

[0066] Next, spacers 754 are formed adjacent to sidewalls of the MG 728, SG 740, HVFET gate 730 and the logic gate pattern 744 (Step 632). The spacers 754 are generally formed by sequentially deposition of a conformal dielectric layer, such as silicon dioxide (SiO.sub.2) or silicon nitride (SiN), followed by a blanket or spacer etch to remove most of the dielectric material deposited on horizontal surfaces of the substrate 704, resulting in the spacer shapes shown.

[0067] Self-Aligned Silicides or SALICIDEs 756 are then formed on the LDD 732 and S/D regions 750/752 adjacent to the MG 728, SG 740 and the logic gate pattern 744 (Step 634). SALICIDEs can also be formed on the HVFET gate, and at least one of the MG and SG polysilicon gates. The SALICIDEs 756 can include any suitable transition metal, such as titanium, cobalt, nickel, platinum, and/or tungsten, and can be formed by any silicide processes commonly employed in the art, including for example a pre-clean etch, metal deposition, anneal and wet strip.

[0068] Referring to FIGS. 6C and 7I, an inter-layer dielectric (ILD 758) is formed or deposited over the substrate 704, and planarized using a CMP process to form a planarized surface through which a top surface of the sacrificial gate is exposed (step 636). Generally, the ILD 758 can include any suitable dielectric material such as silicon dioxide (SiO.sub.2), and can be deposited or formed using suitable, standard deposition technique, including CVD.

[0069] Next, a thin, patterned hardmask 760 is formed over the memory array in the memory region 706 and over the HV area in the peripheral region 708 (step 638). The patterned hardmask 760 is generally formed by patterning a layer of dielectric material, such as silicon nitride, using standard photolithographic and etching techniques.

[0070] The sacrificial gate 746 is then removed from inside the spacer 754 in the LV and the resultant openings filled with a metal to form a metal gate 756 of a HKMG logic FET (step 640). The sacrificial gate 746 can be removed using standard polysilicon etch chemistries, such as CHF.sub.3 or C.sub.2H.sub.2 or HBr/O.sub.2. Generally, the metal can include any suitable metal such as aluminum, copper, titanium, tungsten and alloys thereof, and can be deposited or formed using suitable, standard deposition technique, including CVD and physical vapor deposition (PVD), such as sputtering to deposit a metal layer, which is again planarized in a CMP process to remove the portions of the metal layer not in the spacer 754 opening. It is noted that because the MG 722, SG 734 and HVFET gate 724 are covered by patterned hardmask 760, neither the gates nor the SALICIDEs 750 are damaged in the etch or metal deposition process.

[0071] Finally, the patterned hardmask 760 may or may not be removed, and one or more vertical contacts or vias formed through the ILD 758 to the SALICIDEs 750.

[0072] It is to be appreciated that the Detailed Description section, and not the Summary and Abstract sections, is intended to be used to interpret the claims. The Summary and Abstract sections may set forth one or more but not all exemplary embodiments of the present invention as contemplated by the inventor(s), and thus, are not intended to limit the present invention and the appended claims in any way.

[0073] Thus, a NVM device including a memory cell, a HKMG logic FET and a HVFET embedded or integrally formed on a single substrate, and methods of forming the same have been disclosed. Embodiments of the present invention have been described above with the aid of functional building blocks illustrating the implementation of specified functions and relationships thereof. The boundaries of these functional building blocks have been arbitrarily defined herein for the convenience of the description. Alternate boundaries can be defined so long as the specified functions and relationships thereof are appropriately performed.

[0074] The foregoing description of the specific embodiments will so fully reveal the general nature of the invention that others can, by applying knowledge within the skill of the art, readily modify and/or adapt for various applications such specific embodiments, without undue experimentation, without departing from the general concept of the present invention. Therefore, such adaptations and modifications are intended to be within the meaning and range of equivalents of the disclosed embodiments, based on the teaching and guidance presented herein. It is to be understood that the phraseology or terminology herein is for the purpose of description and not of limitation, such that the terminology or phraseology of the present specification is to be interpreted by the skilled artisan in light of the teachings and guidance.

[0075] The breadth and scope of the present invention should not be limited by any of the above-described exemplary embodiments, but should be defined only in accordance with the following claims and their equivalents.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

D00009

D00010

D00011

D00012

D00013

D00014

D00015

D00016

D00017

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.