Package Structure And Manufacturing Method Thereof

Chang Chien; Shang-Yu ; et al.

U.S. patent application number 16/114237 was filed with the patent office on 2019-05-30 for package structure and manufacturing method thereof. This patent application is currently assigned to Powertech Technology Inc.. The applicant listed for this patent is Powertech Technology Inc.. Invention is credited to Shang-Yu Chang Chien, Hung-Hsin Hsu, Nan-Chun Lin.

| Application Number | 20190164888 16/114237 |

| Document ID | / |

| Family ID | 66632643 |

| Filed Date | 2019-05-30 |

View All Diagrams

| United States Patent Application | 20190164888 |

| Kind Code | A1 |

| Chang Chien; Shang-Yu ; et al. | May 30, 2019 |

PACKAGE STRUCTURE AND MANUFACTURING METHOD THEREOF

Abstract

A package structure including a redistribution structure, a die, a plurality of conductive structures, a first insulating encapsulant, a chip stack, and a second insulating encapsulant. The die is disposed on and electrically connected to the redistribution structure. The conductive structures are disposed on and electrically connected to the redistribution structure. The conductive structures surround the die. The first insulating encapsulant encapsulates the die and the conductive structures. The first insulating structure includes a plurality of openings exposing top surfaces of the conductive structures. The chip stack is disposed on the first insulating encapsulant and the die. The chip stack is electrically connected to the conductive structures. The second insulating encapsulant encapsulates the chip stack.

| Inventors: | Chang Chien; Shang-Yu; (Hsinchu County, TW) ; Hsu; Hung-Hsin; (Hsinchu County, TW) ; Lin; Nan-Chun; (Hsinchu County, TW) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Assignee: | Powertech Technology Inc. Hsinchu County TW |

||||||||||

| Family ID: | 66632643 | ||||||||||

| Appl. No.: | 16/114237 | ||||||||||

| Filed: | August 28, 2018 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 62591166 | Nov 27, 2017 | |||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 25/18 20130101; H01L 2224/73267 20130101; H01L 2225/0651 20130101; H01L 2224/32145 20130101; H01L 2221/68359 20130101; H01L 21/563 20130101; H01L 23/562 20130101; H01L 2224/73215 20130101; H01L 21/486 20130101; H01L 25/03 20130101; H01L 2221/68318 20130101; H01L 2224/02372 20130101; H01L 21/568 20130101; H01L 23/3128 20130101; H01L 24/85 20130101; H01L 2225/06562 20130101; H01L 24/19 20130101; H01L 2224/45144 20130101; H01L 2225/06558 20130101; H01L 2224/83191 20130101; H01L 24/49 20130101; H01L 2224/73204 20130101; H01L 23/3135 20130101; H01L 23/5389 20130101; H01L 2224/48227 20130101; H01L 23/5226 20130101; H01L 24/09 20130101; H01L 24/45 20130101; H01L 24/48 20130101; H01L 2224/48091 20130101; H01L 21/76843 20130101; H01L 21/561 20130101; H01L 25/0657 20130101; H01L 23/49816 20130101; H01L 24/32 20130101; H01L 2221/68381 20130101; H01L 2924/181 20130101; H01L 21/6835 20130101; H01L 24/17 20130101; H01L 2224/02371 20130101; H01L 2225/06548 20130101; H01L 24/97 20130101; H01L 2224/49052 20130101; H01L 24/83 20130101; H01L 2221/68372 20130101; H01L 2221/68345 20130101; H01L 2225/06506 20130101; H01L 21/4857 20130101; H01L 23/5384 20130101; H01L 24/20 20130101; H01L 2224/48235 20130101; H01L 21/56 20130101; H01L 2224/45124 20130101; H01L 25/50 20130101; H01L 23/3157 20130101; H01L 24/73 20130101; H01L 2224/48145 20130101; H01L 2224/73265 20130101; H01L 2224/48091 20130101; H01L 2924/00014 20130101; H01L 2224/45124 20130101; H01L 2924/00014 20130101; H01L 2224/45144 20130101; H01L 2924/00014 20130101; H01L 2224/73265 20130101; H01L 2224/32225 20130101; H01L 2224/48227 20130101; H01L 2924/00012 20130101; H01L 2224/73265 20130101; H01L 2224/32145 20130101; H01L 2224/48145 20130101; H01L 2924/00012 20130101; H01L 2224/73265 20130101; H01L 2224/32145 20130101; H01L 2224/48227 20130101; H01L 2924/00012 20130101; H01L 2924/181 20130101; H01L 2924/00012 20130101; H01L 2224/73204 20130101; H01L 2224/32225 20130101; H01L 2224/16225 20130101; H01L 2924/00012 20130101 |

| International Class: | H01L 23/522 20060101 H01L023/522; H01L 21/56 20060101 H01L021/56; H01L 21/768 20060101 H01L021/768; H01L 23/00 20060101 H01L023/00; H01L 23/31 20060101 H01L023/31; H01L 25/18 20060101 H01L025/18; H01L 25/00 20060101 H01L025/00 |

Claims

1. A package structure, comprising: a redistribution structure; a die disposed on and electrically connected to the redistribution structure; a plurality of conductive structures disposed on and electrically connected to the redistribution structure, wherein the conductive structures surround the die; a first insulating encapsulant encapsulating the die and the conductive structures, wherein the first insulating encapsulant comprises a plurality of openings exposing top surfaces of the conductive structures; a chip stack disposed on the first insulating encapsulant and the die, wherein the chip stack is electrically connected to the conductive structures; and a second insulating encapsulant encapsulating the chip stack.

2. The package structure according to claim 1, further comprising a plurality of conductive terminals disposed on the redistribution structure opposite to the die and the conductive structures.

3. The package structure according to claim 1, further comprising an underfill disposed between the redistribution structure and the die.

4. The package structure according to claim 1, further comprising a plurality of conductive wires embedded in the second insulating encapsulant, wherein the chip stack is electrically connected to the conductive structures through the conductive wires, and the conductive wires extend into the openings of the first insulating encapsulant.

5. The package structure according to claim 1, wherein the second encapsulant fills into the openings of the first insulating encapsulant.

6. The package structure according to claim 1, wherein each conductive structure comprises a first layer, a second layer stacked on the first layer, and a third layer stacked on the second layer, and the openings of the first insulating encapsulant expose the third layer.

7. The package structure according to claim 6, wherein a material of the third layer comprises gold.

8. The package structure according to claim 1, wherein a thickness of the first insulating encapsulant is larger than a thickness of each conductive structure.

9. The package structure according to claim 1, wherein a top surface of the first insulating encapsulant has a level height higher than the top surfaces of the conductive structures.

10. The package structure according to claim 1, wherein the die has an active surface and a rear surface opposite to the active surface, the die comprises a plurality of conductive connectors located on the active surface, and the conductive connectors are directly in contact with the redistribution structure.

11. A manufacturing method of a package structure, comprising: providing a carrier; forming a redistribution structure on the carrier; disposing a plurality of conductive structures and a plurality of dies on the redistribution structure, wherein the conductive structures surround the dies; forming a first insulating encapsulant to encapsulate the dies and the conductive structures; forming a plurality of openings in the first insulating encapsulant to expose top surfaces of the conductive structures; removing the carrier from the redistribution structure; disposing a chip stack on the dies and the first insulating encapsulant opposite to the redistribution structure, wherein the chip stack is electrically connected to the conductive structures; and encapsulating the chip stack by a second insulating encapsulant.

12. The method according to claim 11, further comprising forming a plurality of conductive terminals on the redistribution structure opposite to the dies and the conductive structures.

13. The method according to claim 11, further comprising forming a plurality of conductive wires embedded in the second insulating encapsulant, wherein the chip stack is electrically connected to the conductive structures through the conductive wires, and the conductive wires extend into the openings of the first insulating encapsulant.

14. The method according to claim 11, further comprising performing a singulation process.

15. The method according to claim 11, further comprising forming an underfill between the redistribution structure and the dies.

16. The method according to claim 11, wherein the dies are connected to the redistribution structure through flip-chip bonding.

17. The method according to claim 11, wherein the openings of the first insulating encapsulant are formed through a laser drilling process.

18. The method according to claim 11, wherein the step of encapsulating the chip stack by the second insulating encapsulant comprises filling the second insulating encapsulant into the openings of the first insulating encapsulant.

19. The method according to claim 11, wherein each of the dies has an active surface and a rear surface opposite to the active surface, and the step of forming the first insulating encapsulant comprises: forming an insulating material over the redistribution structure to cover the dies and the conductive structures; and removing a portion of the insulating material to expose the rear surfaces of the dies.

20. The method according to claim 19, wherein in the step of removing a portion of the insulating material to expose the rear surfaces of the dies, the conductive structures are not revealed.

Description

CROSS REFERENCE TO RELATED APPLICATION

[0001] This application claims the priority benefit of U.S. provisional application Ser. No. 62/591,166, filed on Nov. 27, 2017. The entirety of the above-mentioned patent application is hereby incorporated by reference herein and made a part of specification.

BACKGROUND OF THE INVENTION

Field of the Invention

[0002] The disclosure generally relates to a package structure and a manufacturing method thereof, and in particular, to a package structure having short conductive structures electrically connected to a chip stack and a manufacturing method thereof.

Description of Related Art

[0003] Development of semiconductor package technology in recent years has focused on delivering products with smaller volume, lighter weight, higher integration level, and lower manufacturing cost. For multi-functional semiconductor packages, a technique for stacking chips has been used to provide the packages with a larger capacity to store or process data. The rapid increase in demand for multi-functional electronic components with the improved desired features has become a challenge to researchers in the field.

SUMMARY OF THE INVENTION

[0004] The disclosure provides a package structure and a manufacturing method thereof, which effectively reduces the height of the package structure at a lower manufacturing cost.

[0005] The disclosure provides a package structure including a redistribution structure, a die, a plurality of conductive structures, a first insulating encapsulant, a chip stack, and a second insulating encapsulant. The die is disposed on and electrically connected to the redistribution structure. The conductive structures are disposed on and electrically connected to the redistribution structure. The conductive structures surround the die. The first insulating encapsulant encapsulates the die and the conductive structures. The first insulating structure includes a plurality of openings exposing top surfaces of the conductive structures. The chip stack is disposed on the first insulating encapsulant and the die. The chip stack is electrically connected to the conductive structures. The second insulating encapsulant encapsulates the chip stack.

[0006] The disclosure provides a manufacturing method of a package structure. The method includes at least the following steps. A carrier is provided. A redistribution structure is formed on the carrier. A plurality of dies and a plurality of conductive structures are disposed on the redistribution structure. The conductive structures surround the dies. A first insulating encapsulant is formed to encapsulate the dies and the conductive structures. A plurality of openings is formed in the first insulating encapsulant to expose top surfaces of the conductive structures. The carrier is removed from the redistribution structure. A chip stack is disposed on the dies and the first insulating encapsulant opposite to the redistribution structure. The chip stack is electrically connected to the conductive structures. The chip stack is encapsulated by a second insulating encapsulant.

[0007] Based on the above, the conductive structures may serve as vertical connecting feature within the package structure. Due to the small thickness of the conductive structures, the size of the package structure may be effectively reduced. In addition, the adaption of the short conductive structures may result in elimination of additional carrier or thicker copper pillars in the conventional package structure, thereby reducing the manufacturing cost.

[0008] To make the aforementioned more comprehensible, several embodiments accompanied with drawings are described in detail as follows.

BRIEF DESCRIPTION OF THE DRAWINGS

[0009] The accompanying drawings are included to provide a further understanding of the disclosure, and are incorporated in and constitute a part of this specification. The drawings illustrate exemplary embodiments of the disclosure and, together with the description, serve to explain the principles of the disclosure.

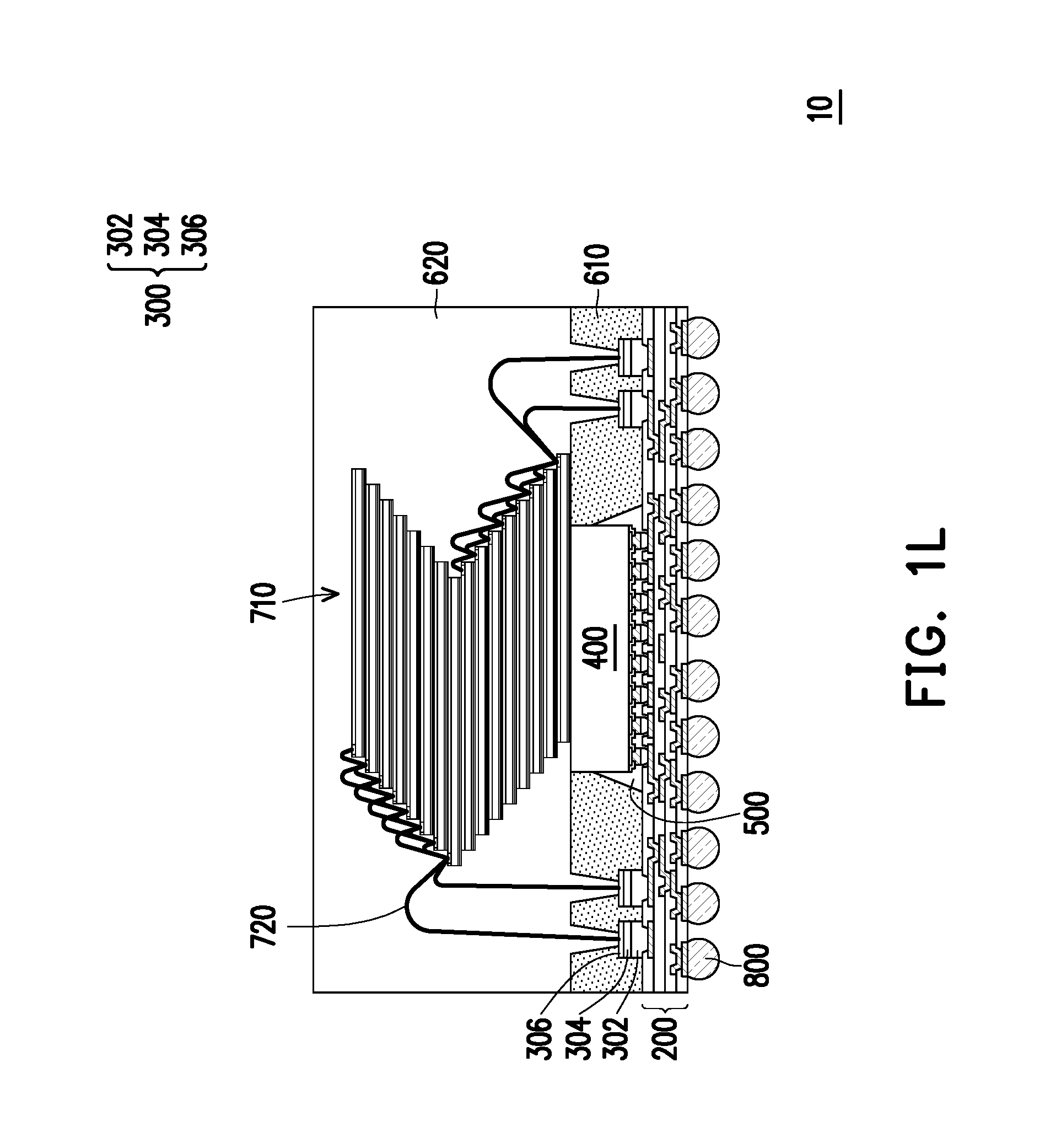

[0010] FIG. 1A to FIG. 1L are schematic cross-sectional views illustrating a manufacturing method of a package structure according to some embodiments of the disclosure.

DESCRIPTION OF THE EMBODIMENTS

[0011] Reference will now be made in detail to the present preferred embodiments of the invention, examples of which are illustrated in the accompanying drawings. Wherever possible, the same reference numbers are used in the drawings and the description to refer to the same or like parts.

[0012] FIG. 1A to FIG. 1L are schematic cross-sectional views illustrating a manufacturing method of a package structure 10 according to some embodiments of the disclosure. Referring to FIG. 1A, a carrier 100 having a de-bonding layer 102 formed thereon is provided. The carrier 100 may be a glass substrate or a glass supporting board. However, they construe no limitation in the disclosure. Other suitable substrate material may be adapted as long as the material is able to withstand subsequent processes while structurally supporting the package structure formed thereon. The de-bonding layer 102 may include light to heat conversion (LTHC) materials, epoxy resins, inorganic materials, organic polymeric materials, or other suitable adhesive materials. However, the disclosure is not limited thereto, and other suitable de-bonding layers may be used in some alternative embodiments.

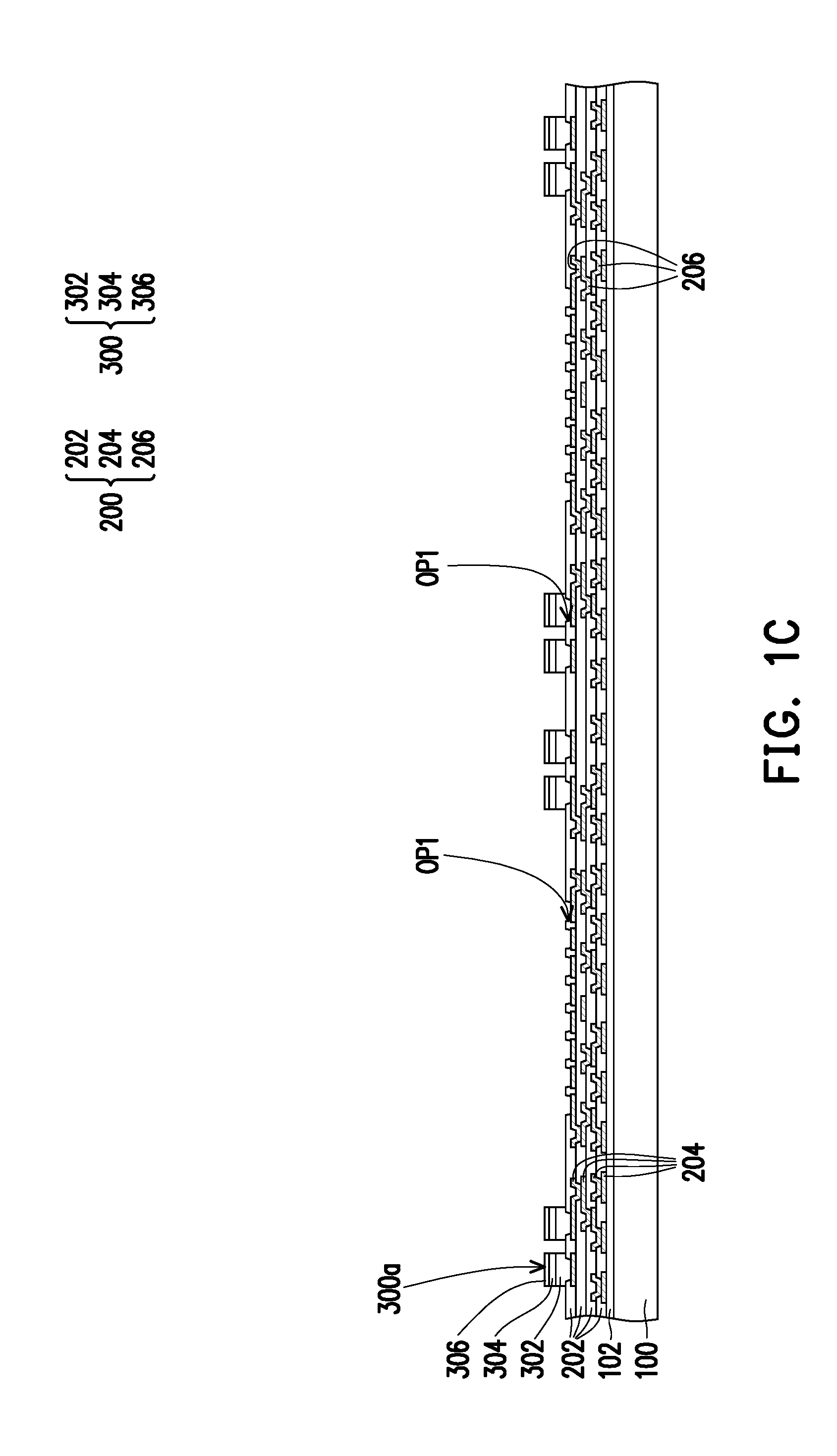

[0013] Referring to FIG. 1B, a redistribution structure 200 is formed over the carrier 100. The redistribution structure 200 may include at least one dielectric layer 202, a plurality of conductive patterns 204, and a plurality of conductive vias 206. The dielectric layers 202 may be formed by suitable fabrication techniques such as spin-on coating, chemical vapor deposition (CVD), plasma-enhanced chemical vapor deposition (PECVD), or the like. The dielectric layers 202 may be made of non-organic or organic dielectric materials such as silicon oxide, silicon nitride, silicon carbide, silicon oxynitride, polyimide, benzocyclobutene (BCB), or the like. On the other hand, the conductive patterns 204 and the conductive vias 206 may be formed by sputtering, evaporation, electro-less plating, or electroplating. The conductive patterns 204 and the conductive vias 206 are embedded in the dielectric layers 202. The dielectric layers 202 and the conductive patterns 204 may be stacked alternately. The conductive vias 206 penetrate through the dielectric layers 202 to electrically connect the conductive patterns 204 to each other. The conductive patterns 204 and the conductive vias 206 may be made of copper, aluminum, nickel, gold, silver, tin, a combination thereof, a composite structure of copper/nickel/gold, or other suitable conductive materials.

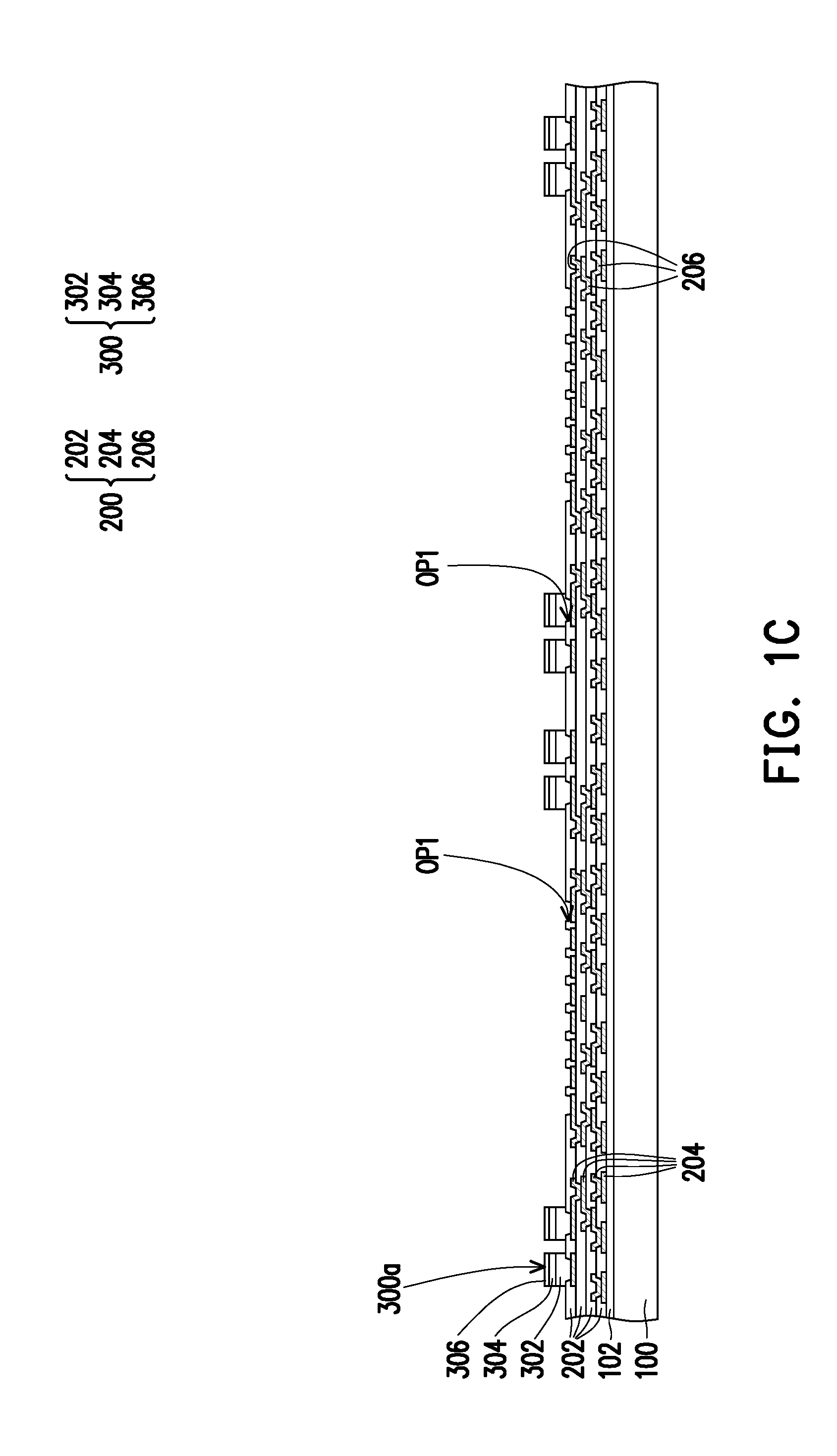

[0014] As illustrated in FIG. 1B, the redistribution structure 200 includes four dielectric layers 202. However, the number of the dielectric layers 202 is not limited and may be adjusted based on circuit design. The top dielectric layer 202 may have a plurality of openings OP1 exposing a portion of the top conductive patterns 204 for electrical connection in the subsequent processes. The bottom dielectric layer 202 exposes portions of the bottom conductive patterns 204 for further electrical connection with other circuit components.

[0015] Referring to FIG. 1C, a plurality of conductive structures 300 are disposed on the redistribution structure 200 opposite to the carrier 100. In some embodiments, the conductive structures 300 may be plated on the top conductive patterns 204 of the redistribution structure 200. The plating process may be electroplating, electroless-plating, immersion plating, or the like. In some embodiments, the conductive structures 300 may be shaped as cylindrical columns. That is, the conductive structures 300 may include conductive posts, conductive pillars, or the like. However, the disclosure is not limited thereto. In some alternative embodiments, the conductive structures 300 may take the form of polygonal columns or other suitable shapes. In some embodiments, each conductive structure 300 is a multi-layered composite structure. Each conductive structure 300 may be constituted by a first layer 302, a second layer 304 stacked on the first layer 302, and a third layer 306 stacked on the second layer 304. A material of the first layer 302, a material of the second layer 304, and a material of the third layer 306 may be different from each other. For example, the material of the first layer 302 includes copper, aluminum, tin, silver, alloys thereof, or the like. The material of the second layer 304 includes nickel, solder, or the like. The material of the third layer includes copper, gold, or other metallic material with excellent electrical conductivity and good wire bondability. In some embodiments, the first layer 302, the second layer 304, and the third layer 306 may form a Cu/Ni/Au composite structure. The third layer 306 is able to enhance the electrical connection of the conductive structures 300 with other subsequently formed elements. On the other hand, the second layer 304 is sandwiched between the first layer 302 and the third layer 306 to act as a barrier layer between the first layer 302 and the third layer 306. For example, when the first layer 302, the second layer 304, and the third layer 306 are the Cu/Ni/Au composite structure, the second layer 304 formed of nickel may prevent the copper atoms of the first layer 302 from diffusing into the third layer 306. The contamination of the third layer 306 with copper would cause the third layer 306 to oxidize easily, thereby resulting in poor wire bondability. However, with the aid of the second layer 304 as a barrier layer, the foregoing adverse effect may be sufficiently prevented. Although the conductive structures 300 are illustrated as being constituted by three layers in FIG. 1C, the disclosure is not limited thereto. In some alternative embodiments, each conductive structure 300 may be a singled layered structure or a multi-layered structure constituted by two, four, or more layers.

[0016] As illustrated in FIG. 1C, the conductive structures 300 fill up a portion of the openings OP1 of the top dielectric layer 202 of the redistribution structure 200. For example, the first layer 302 of the conductive structures 300 may be partially disposed in the openings OP1 of the top dielectric layer 202 to form electrical connection between the redistribution structure 200 and the conductive structures 300. The first layer 302 may be in physical contact with the top conductive patterns 204 of the redistribution structure 200.

[0017] Referring to FIG. 1D, a plurality of dies 400 are disposed on the redistribution structure 200 opposite to the carrier 100. The dies 400 may be disposed on the redistribution structure 200 through a picked-and-placed process. In some embodiments, the dies 400 are placed such that the conductive structures 300 surround the dies 400. The conductive structures 300 are disposed along the periphery of at least one die 400. The dies 400 may include digital dies, analog dies, or mixed signal dies. For example, the dies 400 may be application-specific integrated circuit (ASIC) dies, logic dies, or other suitable dies. Each die 400 includes a semiconductor substrate 402, a plurality of conductive pads 404, a passivation layer 406, and a plurality of conductive connectors 408. In some embodiments, the semiconductor substrate 402 may be a silicon substrate including active components (e.g., transistors or the like) and, optionally, passive components (e.g., resistors, capacitors, inductors, or the like) formed therein. The conductive pads 404 are distributed over the semiconductor substrate 402. The conductive pads 404 may include aluminum pads, copper pads, or other suitable metal pads. The passivation layer 406 is formed over the semiconductor substrate 402 to partially cover each connection pad 404. In other words, the passivation layer 406 has a plurality of contact openings revealing at least a portion of each connection pad 404. The passivation layer 406 may be a silicon oxide layer, a silicon nitride layer, a silicon oxy-nitride layer, or a dielectric layer formed of polymeric materials or other suitable dielectric materials. The conductive connectors 408 are disposed on the conductive pads 404. For example, the conductive connectors 408 may extend into the contact openings of the passivation layer 406 to render electrical connection with the conductive pads 404. In some embodiments, each conductive connector 408 may include a conductive post 408a and a conductive bump 408b disposed on the conductive post 408a. The conductive posts 408a may be plated on the conductive pads 404. The plating process may be electroplating, electroless-plating, immersion plating, or the like. The conductive posts 408a may include copper, copper alloys, or the like. On the other hand, the conductive bump 408b may be made of copper, nickel, tin, silver, or a combination thereof. In some embodiments, the conductive posts 408a may be omitted. The conductive connectors 408 may include C2 (Chip Connection) bumps or C4 (Controlled Collapse Chip Connection) bumps.

[0018] Each die 400 has an active surface 400a and a rear surface 400b opposite to the active surface 400a. As illustrated in FIG. 1D, the dies 400 are disposed in a face down manner such that the active surfaces 400a of the dies 400 face toward the redistribution structure 200. The dies 400 may be connected to the redistribution structure 200 through flip-chip bonding. The conductive connectors 408 of the dies 400 may be disposed in another portion of the openings OP1 of the top dielectric layer 202 and may be in physical contact with the top conductive patterns 204 of the redistribution structure 200. As such, the electrical connection between the dies 400 and the redistribution structure 200 may be achieved. In some embodiments, the redistribution structure 200 may be used to reroute electrical signals to/from the die 400 and may expand in a wider area than the die 400. Therefore, in some embodiments, the redistribution structure 200 may be referred to as a "fan-out redistribution structure."

[0019] As illustrated in FIG. 1D, a thickness t.sub.300 of the conductive structures 300 is smaller than a thickness t.sub.400 of the dies 400. For example, the rear surfaces 400b of the dies 400 have a level height higher than that of top surfaces 300a of the conductive structures 300 in reference to the redistribution structure 200.

[0020] In some embodiments, an underfill 500 is formed between the redistribution structure 200 and the dies 400 to protect and isolate the coupling between the conductive connectors 408 and the top conductive patterns 204. In some embodiments, the underfill 500 fills into the openings OP1 of the top dielectric layer 202. The underfill 500 may be made of a capillary underfill (CUF) including polymeric materials, resins, or silica additives.

[0021] Although the conductive structures 300 are shown to be formed prior to the placement of the dies 400 in FIG. 1C and FIG. 1D, the disclosure is not limited thereto. In some alternative embodiments, the dies 400 may be placed onto the redistribution structure 200 before the conductive structures 300 are formed. That is, the manufacturing steps shown in FIG. 1C and FIG. 1D are interchangeable.

[0022] Referring to FIG. 1E, an insulating material 612 is formed on the redistribution structure 200 to encapsulate the conductive structures 300, the dies 400, and the underfill 500. The insulating material 612 may include a molding compound formed by a molding process or an insulating material such as epoxy, silicone, or other suitable resins. In some embodiments, the insulating material 612 is formed by an over-molding process such that the conductive structures 300 and the dies 400 are not revealed. As illustrated in FIG. 1E, a top surface 612a of the insulating material 612 is located at a level height higher than that of the top surfaces 300a of the conductive structures 300 and that of the rear surfaces 400b of the dies 400.

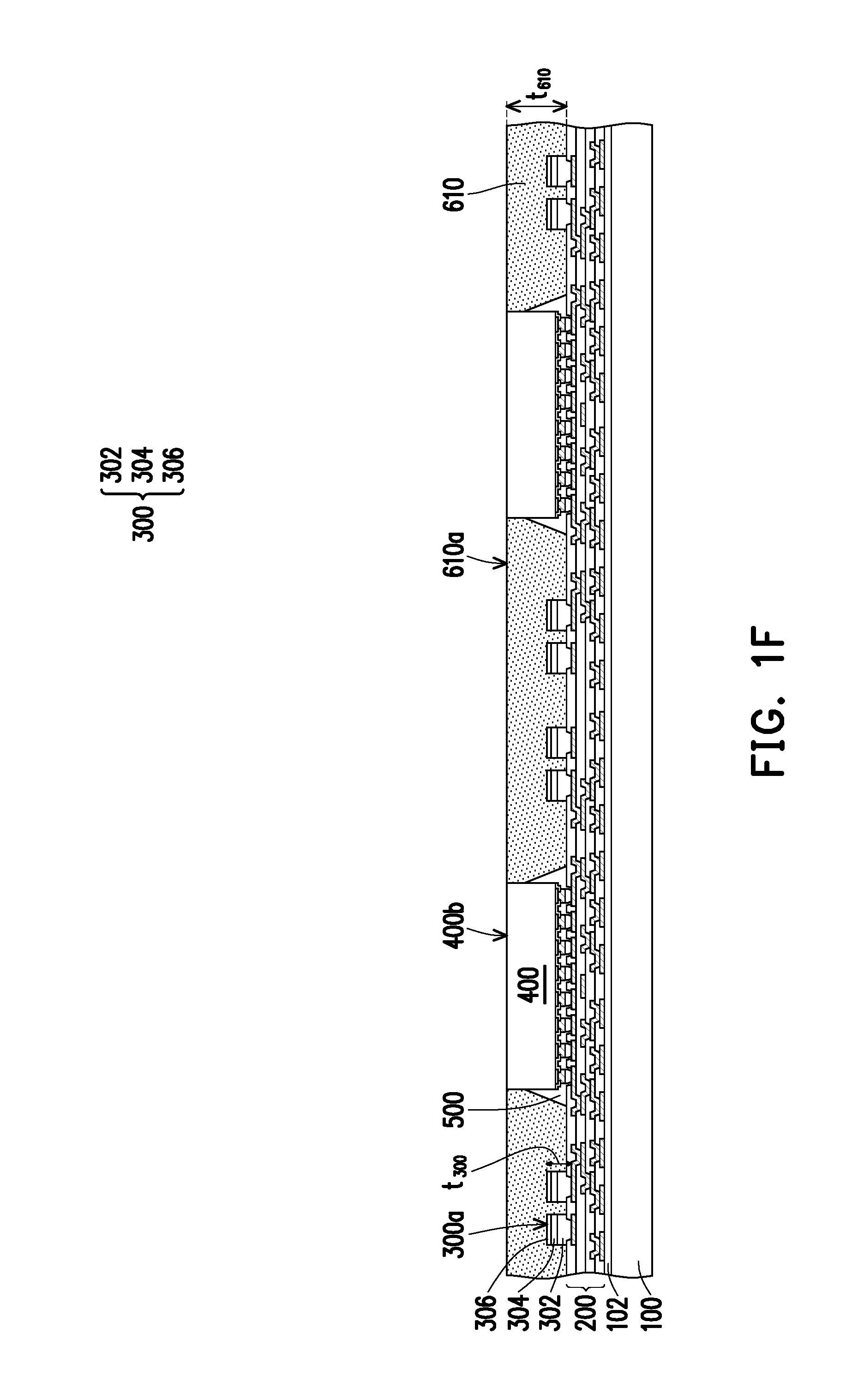

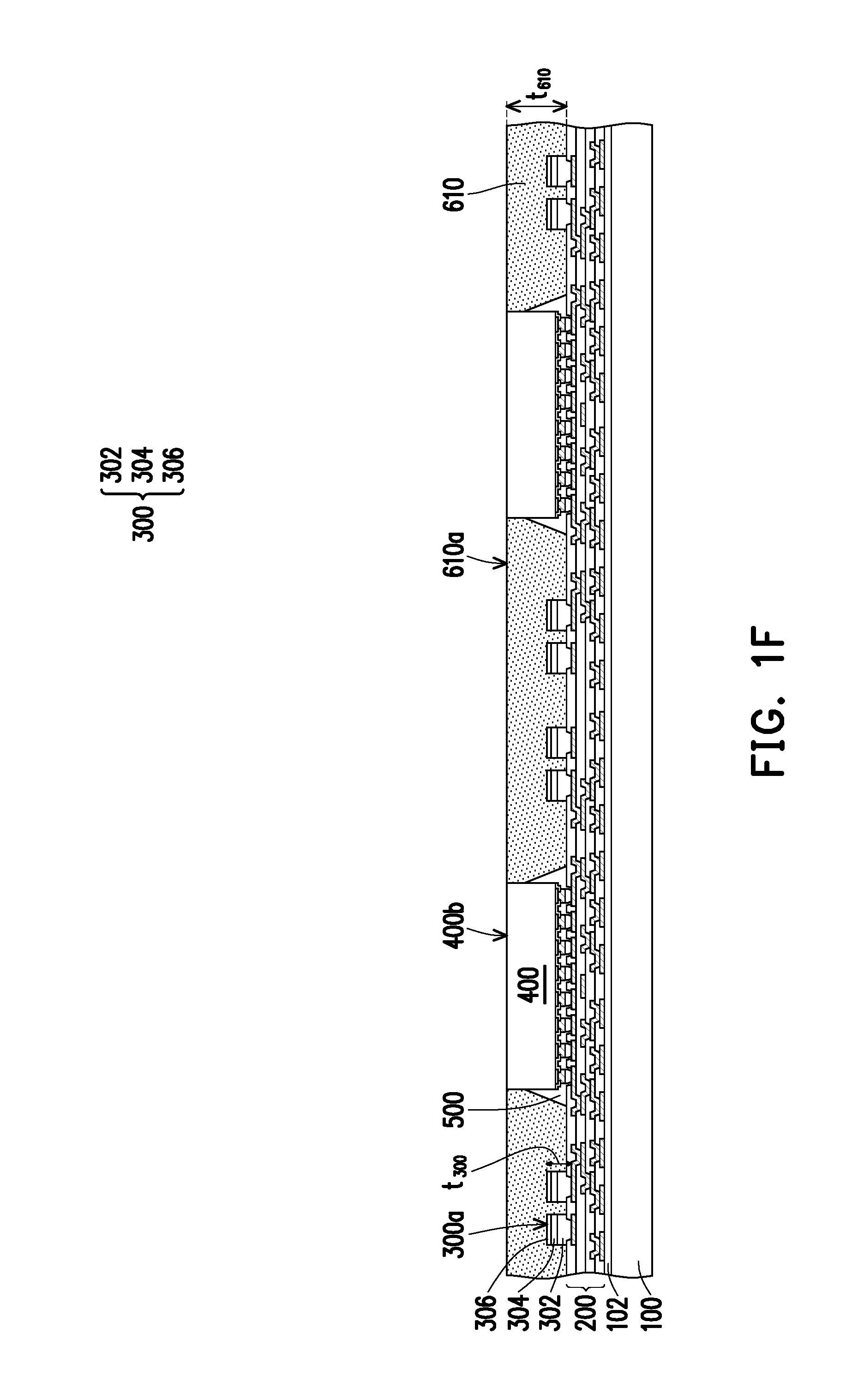

[0023] Referring to FIG. 1F, a thickness of the insulating material 612 is reduced to form a first insulating encapsulant 610. A portion of the insulating material 612 may be removed to expose the rear surfaces 400b of the dies 400 while the conductive structures 300 are still fully encapsulated by the first insulating encapsulant 610. In some embodiments, the insulating material 612 may be removed through a planarization process. The planarization process may be Chemical Mechanical Polishing (CMP), mechanical grinding, etching, or other suitable process. The planarization process may further grind the insulating material 610 and the dies 400 to reduce the overall thickness of the subsequently formed package structure 10. After the planarization process, the first insulating encapsulant 610 is disposed on the redistribution structure 200 to laterally encapsulate the dies 400. The first insulating encapsulant 610 also encapsulates sidewalls and top surfaces 300a of the conductive structures 300. A top surface 610a of the first insulating encapsulant 610 and the rear surfaces 400b of the dies 400 may be substantially coplanar to each other. On the other hand, the top surface 610a of the first insulating encapsulant 610 has a level height higher than the top surfaces 300a of the conductive structures 300. A thickness t.sub.610 of the first insulating encapsulant 610 may be greater than a thickness t.sub.300 of each conductive structure 300.

[0024] Referring to FIG. 1G, a plurality of openings OP2 is formed in the first insulating encapsulant 610. In some embodiments, the openings OP2 are formed through a laser drilling process. The first insulating encapsulant 610 located above the conductive structures 300 may be partially removed to form the openings OP2. As illustrated in FIG. 1G, locations of the openings OP2 correspond to locations of the conductive structures 300. Each of the openings OP2 may expose a portion of each conductive structure 300. The openings OP2 may expose the top surface 300a of the conductive structures 300. In some embodiments, the openings OP2 may partially expose the third layer 306 of the conductive structures 300.

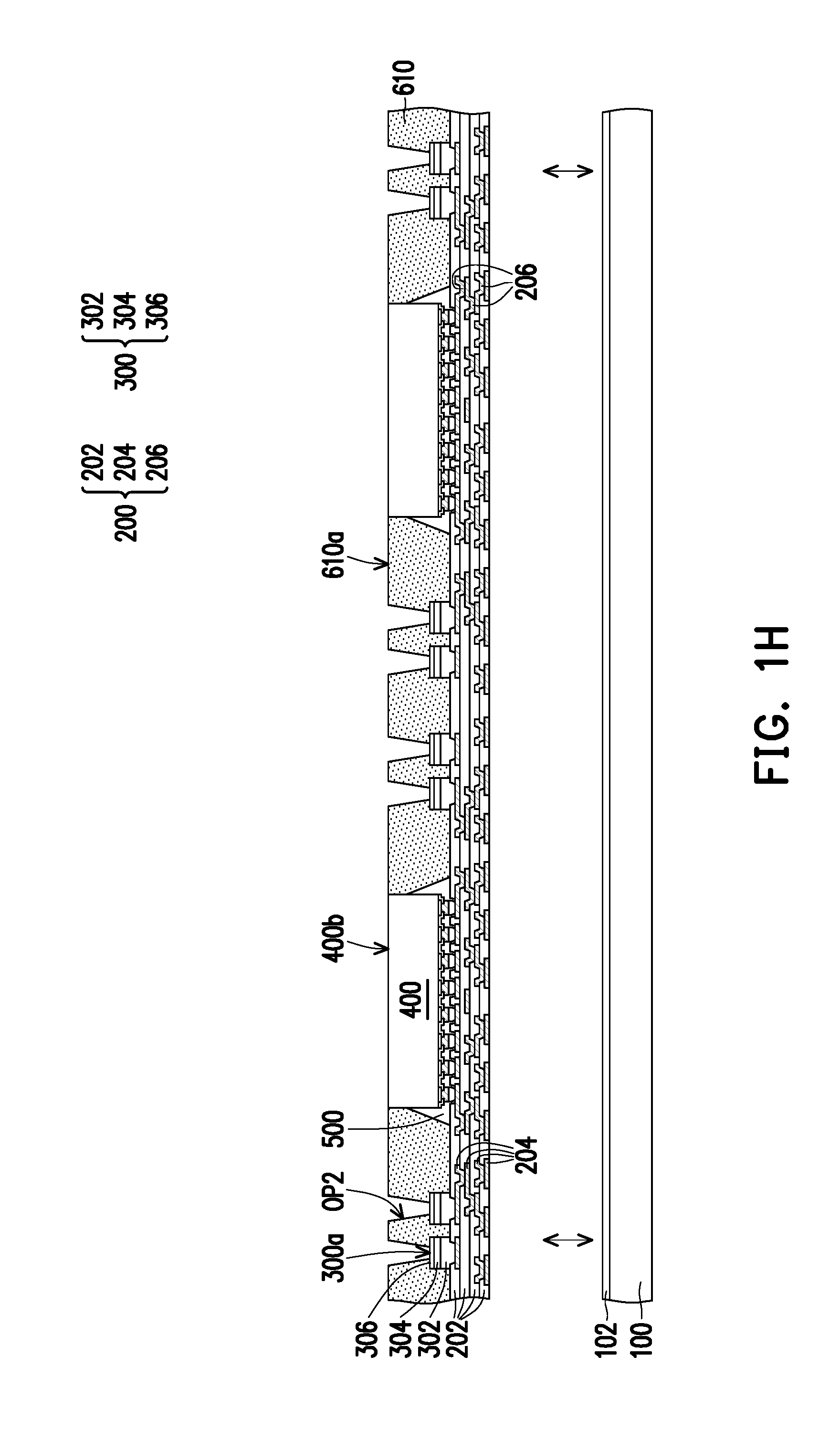

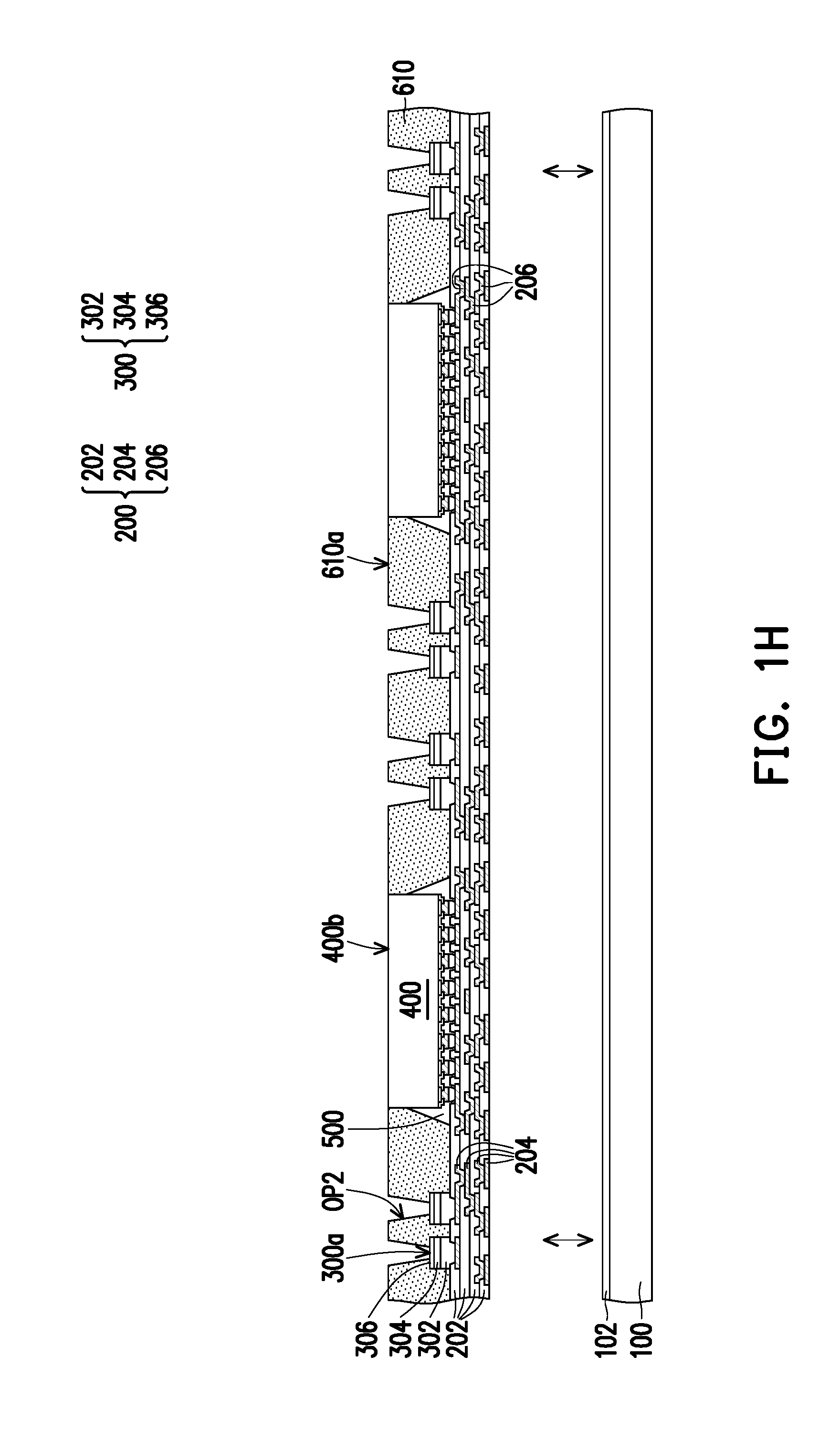

[0025] Referring to FIG. 1H, the de-bonding layer 102 and the carrier 100 are removed from the redistribution structure 200. When the de-bonding layer 102 is an LTHC layer, the de-bonding layer 102 and the carrier 100 may be peeled off and separated from the bottom dielectric layer 202 and the bottom conductive patterns 204 of the redistribution structure 200 upon exposure to a UV laser light. The structure illustrated in FIG. 1H may be sawed into strip form for conventional wire bonding assembly.

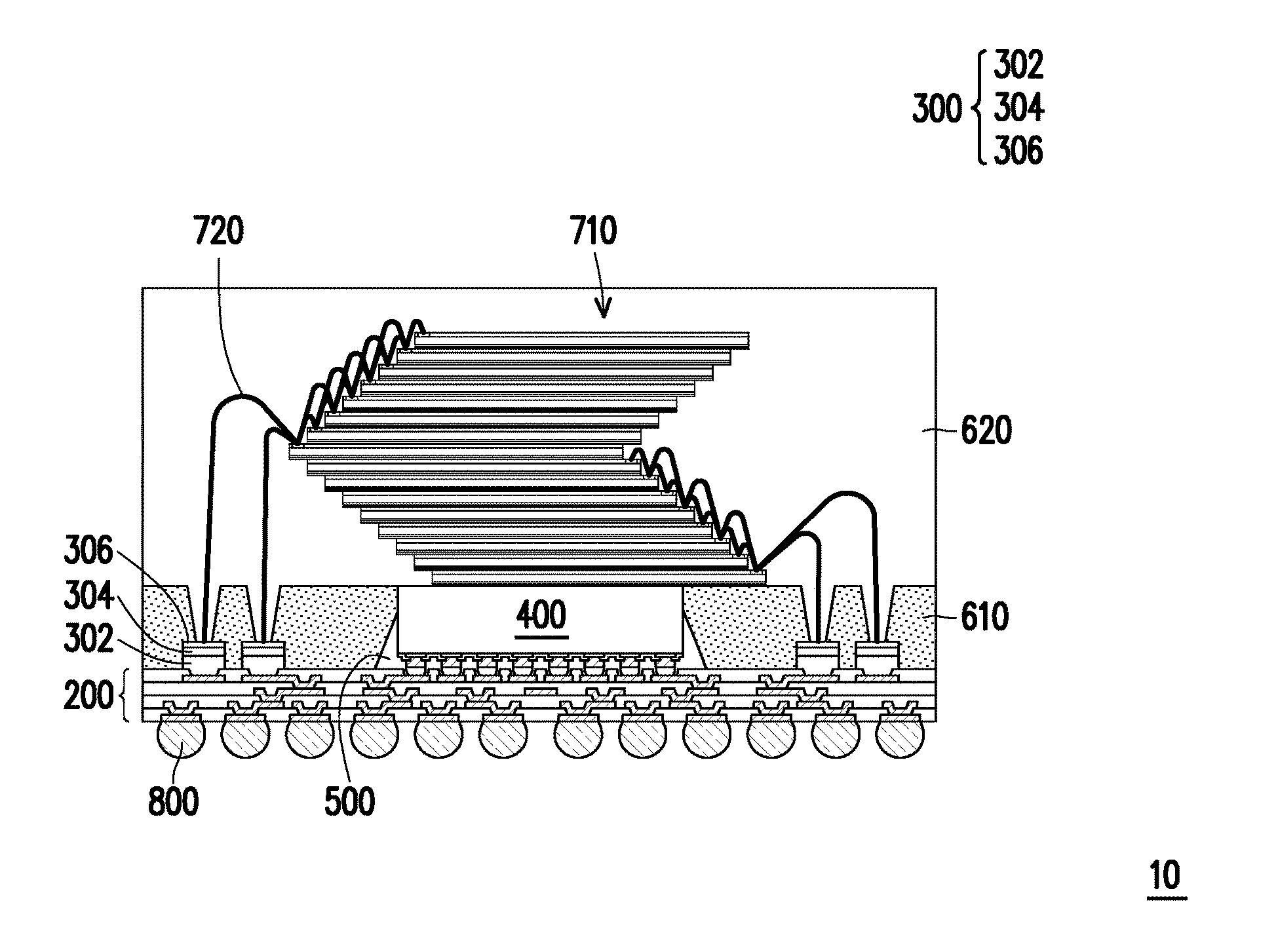

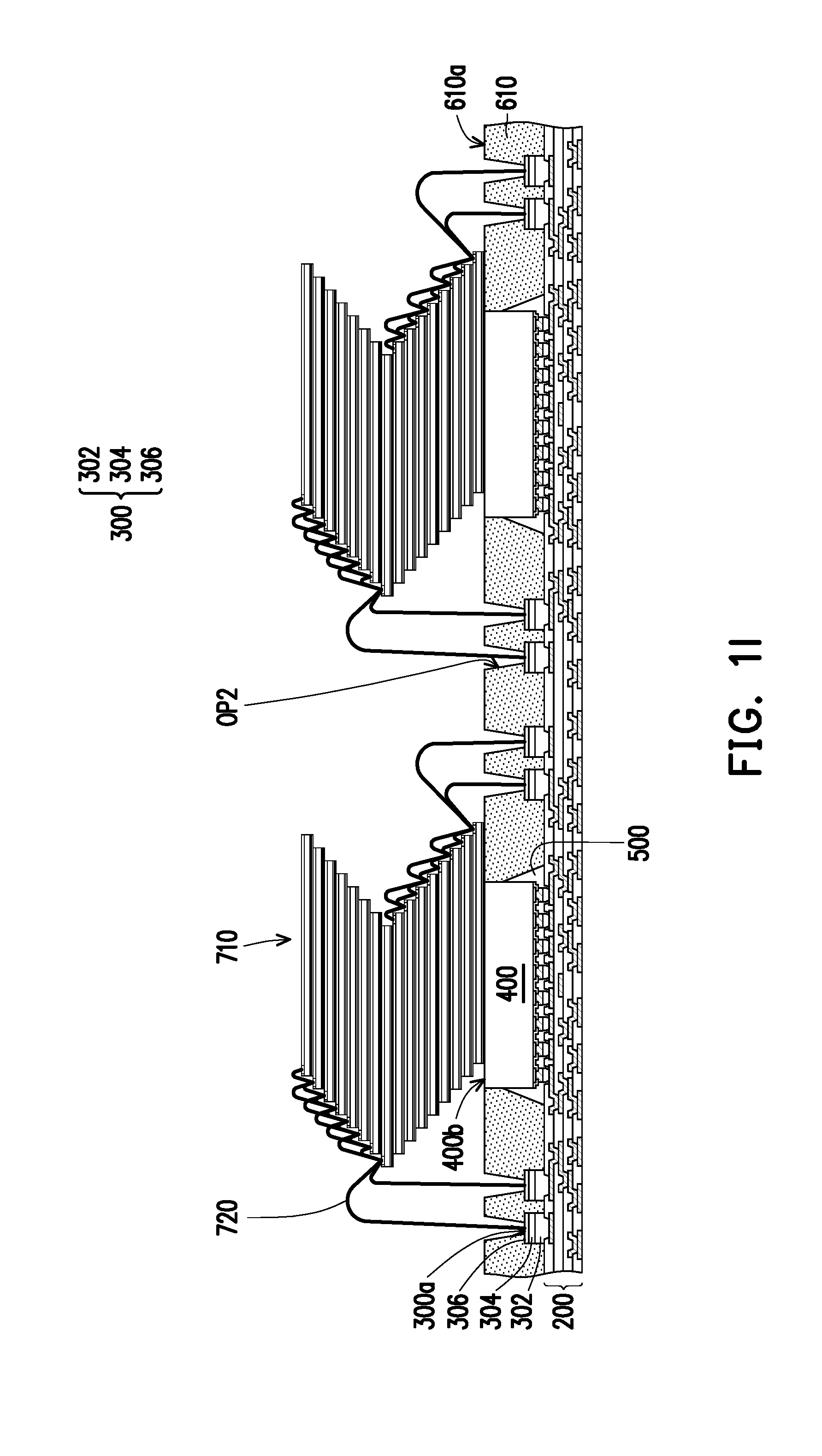

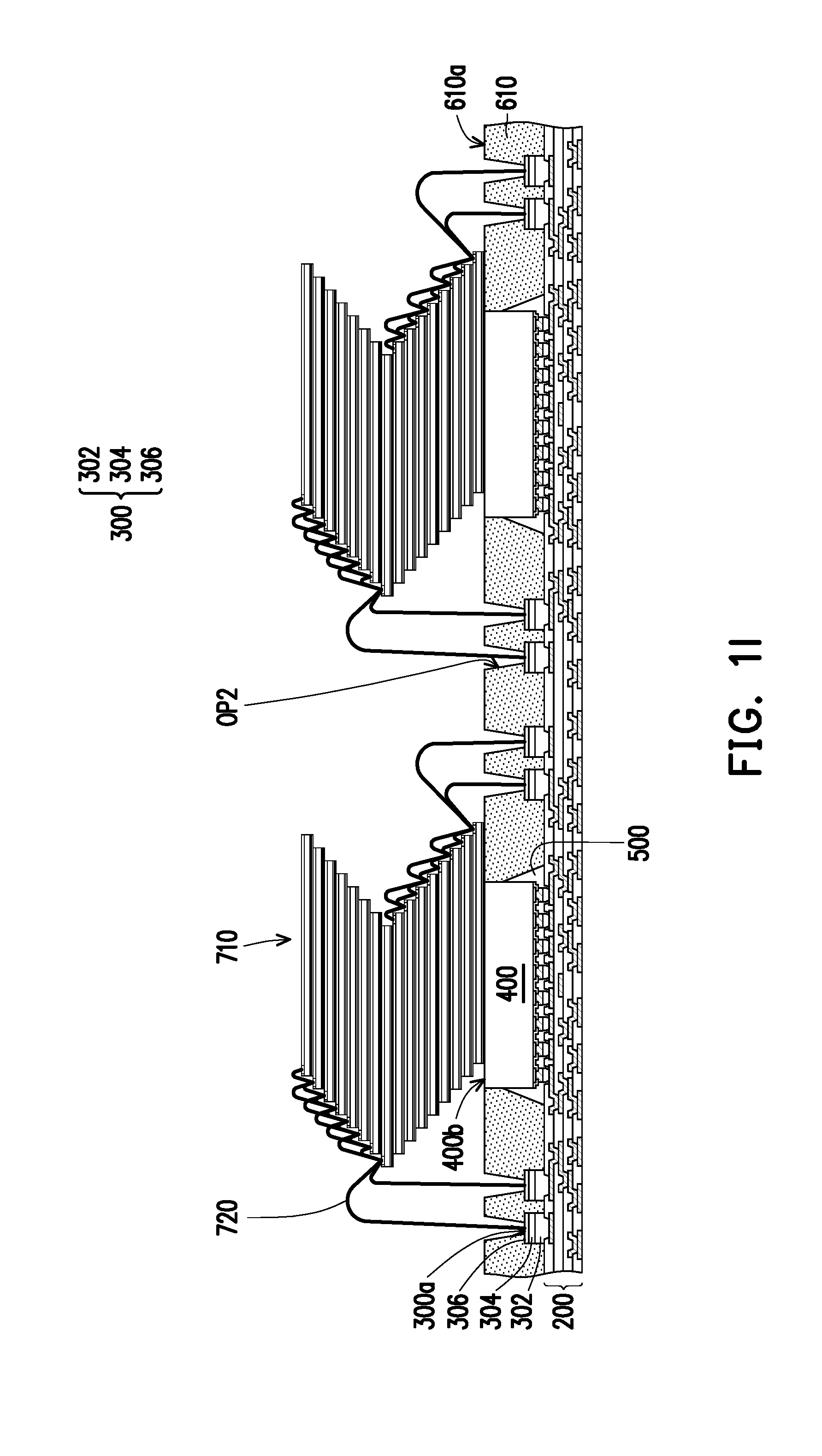

[0026] Referring to FIG. 1I, a chip stack 710 is disposed on the dies 400 and the first insulating encapsulant 610 opposite to the redistribution structure 200. The chip stack 710 may be placed on the rear surfaces 400b of the dies 400 and the top surface 610a of the first insulating encapsulant 610. The chip stack 710 may be formed by a plurality of chips stacked on top of each other. The chips may be memory chips having non-volatile memory, such as NAND flash. However, the disclosure is not limited thereto. In some alternative embodiments, the chips of the chip stack 710 may be chips capable of performing other functions, such as logic function, computing function, or the like. A chip attachment layer may be disposed between two adjacent chips in the chip stack 710 to enhance the adhesion between these two chips.

[0027] The chip stack 710 may be electrically connected to the conductive structures 300 through a plurality of conductive wires 720. When the chip stack 710 is disposed on the dies 400 and the first insulating encapsulant 610, a plurality of conductive wires 720 may be formed through a wire-bonding process. One end of the conductive wire 720 is coupled to at least one chip of the chip stack 710, the conductive wire 720 is extended into the openings OP2 of the first insulating encapsulant 610, and another end of the conductive wire 720 is coupled to the third layer 306 of the conductive structures 300. A material of the conductive wires 720 may include gold, aluminum, or other suitable conductive materials. In some embodiments, the material of the conductive wires 720 is identical to the material of the third layer 306 of the conductive structures 300.

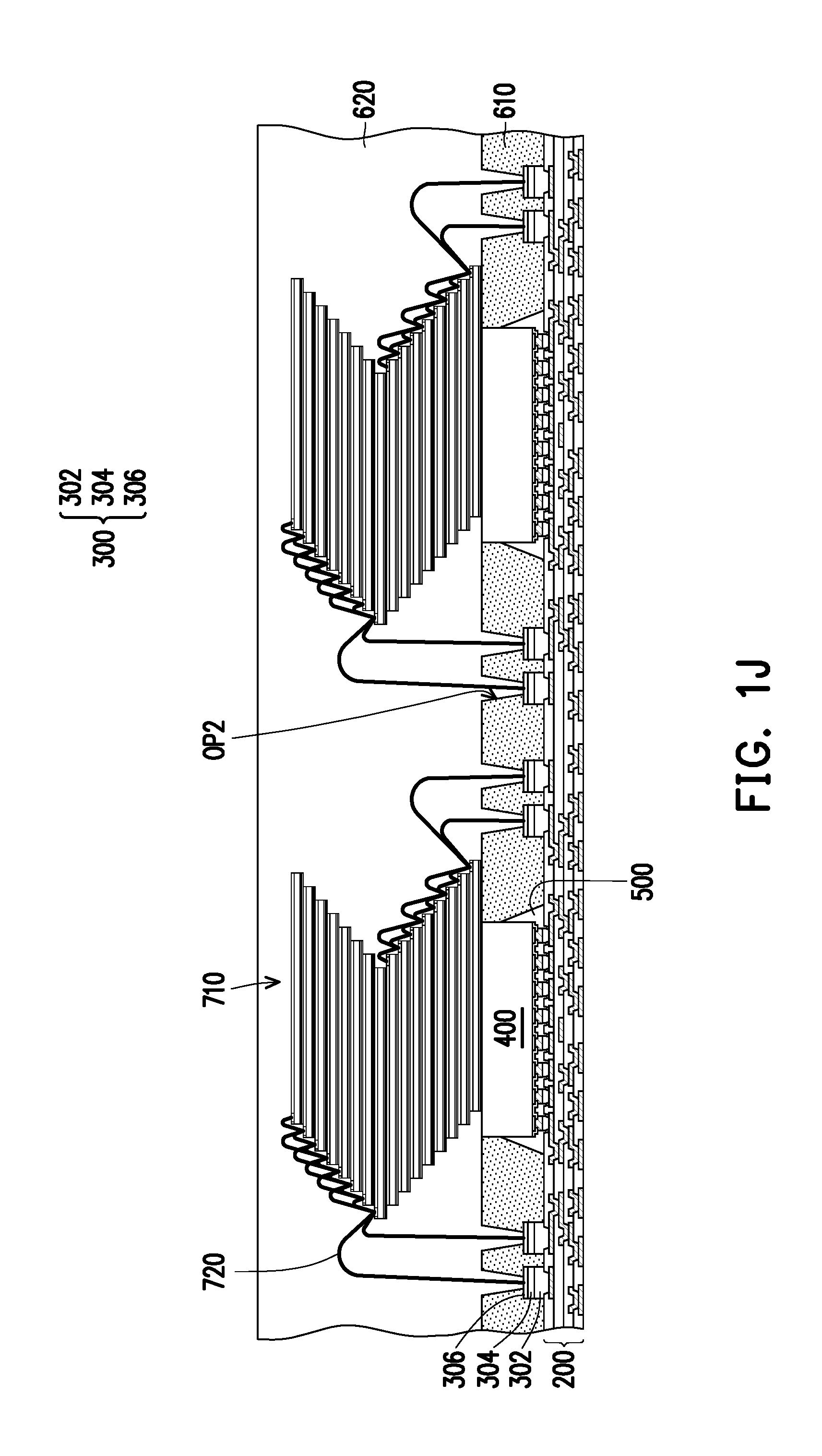

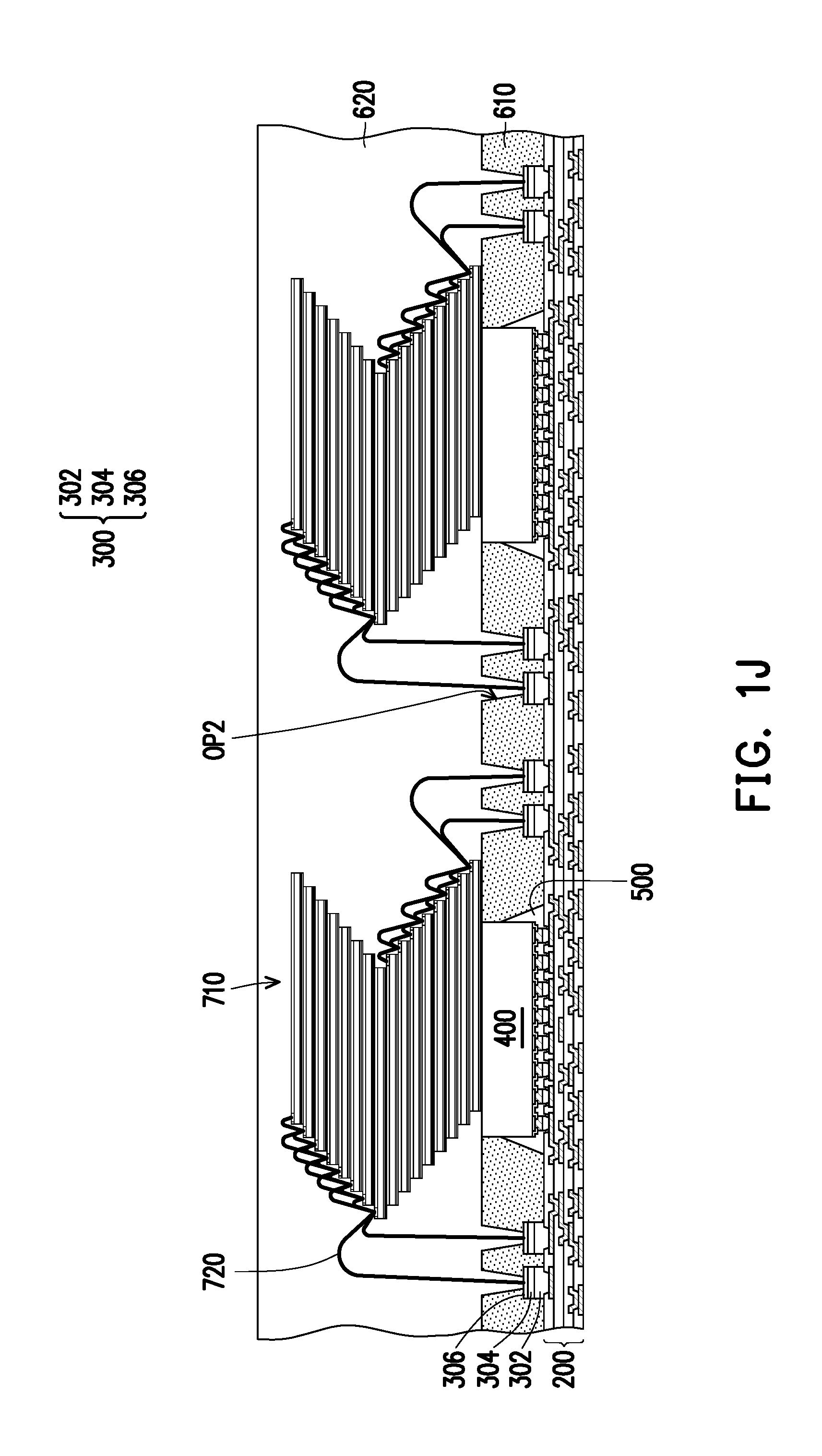

[0028] Referring to FIG. 1J, a second insulating encapsulant 620 is formed on the first insulating encapsulant 610 and the dies 400 to encapsulate the chip stack 710 and the conductive wires 720 such that the chip stack 710 and the conductive wires 720 are embedded in the second insulating encapsulant 620. A material of the second insulating encapsulant 620 may be the same or different from that of the first insulating encapsulant 610. The material of the second insulating encapsulant 620 may be epoxy, molding compound, or other suitable insulating materials. In some embodiments, the material of the second insulating encapsulant 620 may have a low moisture absorption rate. The second insulating encapsulant 620 may be formed through compression molding, transfer molding, or other encapsulation processes. As illustrated in FIG. 1J, the second insulating encapsulant 620 may fill the openings OP2 of the first insulating encapsulant 610 to protect segments of the conductive wires 720 located in the openings OP2. The second insulating encapsulant 620 may be in physical contact with a portion of the conductive structures 300. The second insulating encapsulant 620 provides physical support, mechanical protection, and electrical and environmental isolation for the chip stack 710 and the conductive wires 720.

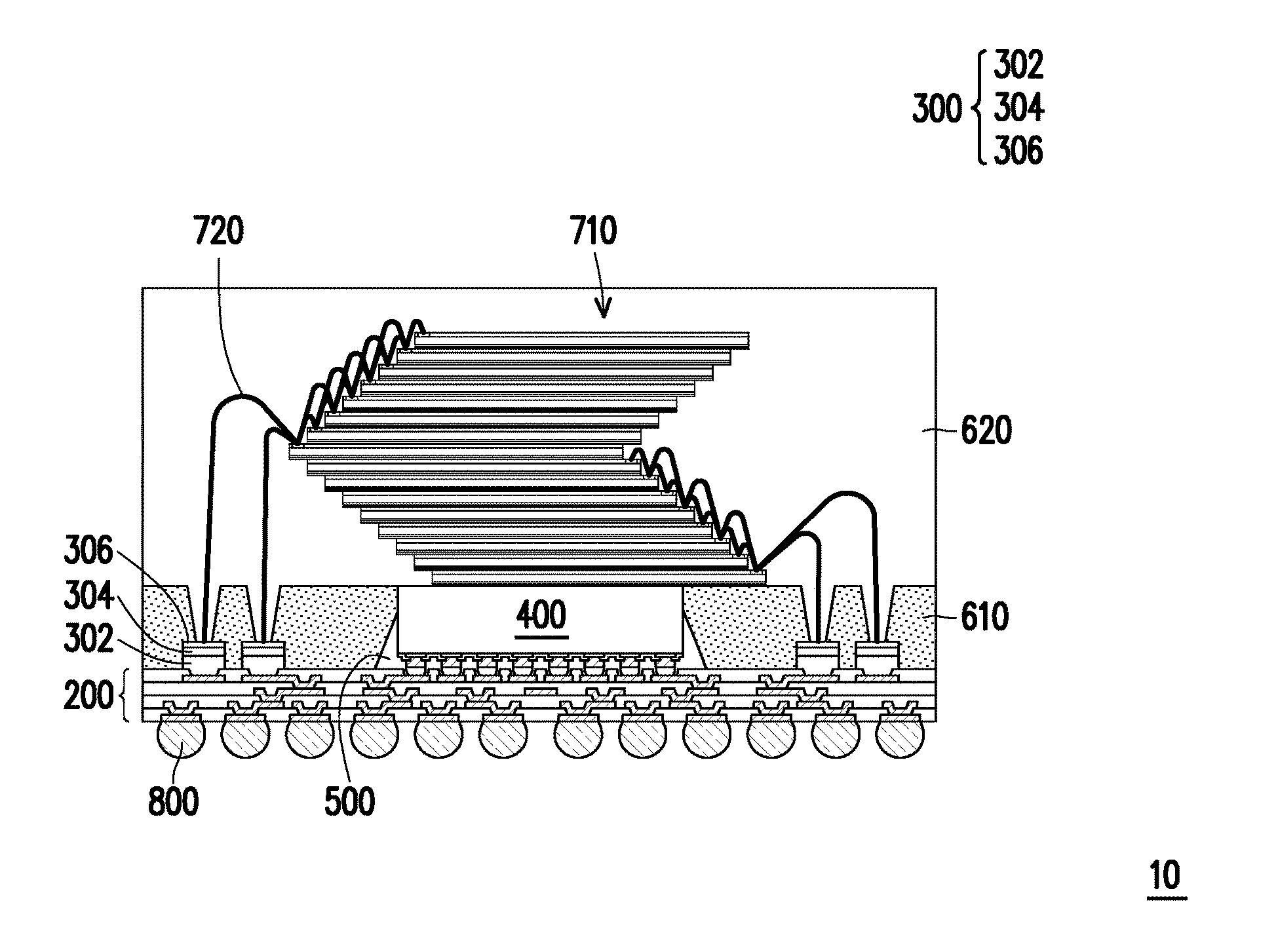

[0029] Referring to FIG. 1K, a plurality of conductive terminals 800 is formed on the redistribution structure 200 opposite to the conductive structures 300 and the dies 400. In some embodiments, the conductive terminals 800 are disposed on the bottom conductive patterns 204 of the redistribution structure 200. In other words, the bottom conductive patterns 204 of the redistribution structure 200 may be referred to as under-ball metallization (UBM) patterns. The conductive terminals 800 may be formed by a ball placement process and/or a reflow process. The conductive terminals 800 may be conductive bumps such as solder balls. However, the disclosure is not limited thereto. In some alternative embodiments, the conductive terminals 800 may take other possible forms and shapes based on design requirements. For example, the conductive terminals 800 may take the form of conductive pillars or conductive posts.

[0030] Referring to FIG. 1L, after forming the conductive terminals 800, a singulation process is performed to obtain a plurality of package structures 10. The singulation process includes, for example, cutting with a rotating blade or a laser beam.

[0031] Based on the above, the conductive structures may serve as vertical connecting feature within the package structure. Due to the small thickness of the conductive structures, the size of the package structure may be effectively reduced. In addition, the adaption of the short conductive structures may result in elimination of additional carrier or thicker copper pillars in the conventional package structure, thereby reducing the manufacturing cost.

[0032] It will be apparent to those skilled in the art that various modifications and variations can be made to the disclosed embodiments without departing from the scope or spirit of the disclosure. In view of the foregoing, it is intended that the disclosure covers modifications and variations provided that they fall within the scope of the following claims and their equivalents.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

D00009

D00010

D00011

D00012

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.