Semiconductor Wafer, Manufacturing Method For Semiconductor Wafer, And Manufacturing Method For Semiconductor Device

KOIKE; Takashi ; et al.

U.S. patent application number 16/792944 was filed with the patent office on 2021-03-04 for semiconductor wafer, manufacturing method for semiconductor wafer, and manufacturing method for semiconductor device. This patent application is currently assigned to Kioxia Corporation. The applicant listed for this patent is Kioxia Corporation. Invention is credited to Takashi KOIKE, Manabu Takakuwa.

| Application Number | 20210066068 16/792944 |

| Document ID | / |

| Family ID | 1000004667789 |

| Filed Date | 2021-03-04 |

| United States Patent Application | 20210066068 |

| Kind Code | A1 |

| KOIKE; Takashi ; et al. | March 4, 2021 |

SEMICONDUCTOR WAFER, MANUFACTURING METHOD FOR SEMICONDUCTOR WAFER, AND MANUFACTURING METHOD FOR SEMICONDUCTOR DEVICE

Abstract

A semiconductor wafer according to an embodiment includes a support region facing a support member, an outer circumferential region positioned on an outer side of the support region, and an inner circumferential region positioned on an inner side of the support region. The outer circumferential region has a convex portion with a thickness protruded upward with respect to the inner circumferential region or a concave portion with a thickness recessed downward with respect to the inner circumferential region.

| Inventors: | KOIKE; Takashi; (Yokkaichi, JP) ; Takakuwa; Manabu; (Tsu, JP) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Assignee: | Kioxia Corporation Minato-ku JP |

||||||||||

| Family ID: | 1000004667789 | ||||||||||

| Appl. No.: | 16/792944 | ||||||||||

| Filed: | February 18, 2020 |

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 21/02035 20130101; H01L 23/562 20130101 |

| International Class: | H01L 21/02 20060101 H01L021/02; H01L 23/00 20060101 H01L023/00 |

Foreign Application Data

| Date | Code | Application Number |

|---|---|---|

| Sep 4, 2019 | JP | 2019-161278 |

Claims

1. A semiconductor wafer comprising: a support region facing a support member; an outer circumferential region positioned on an outer side of the support region; and an inner circumferential region positioned on an inner side of the support region, wherein the outer circumferential region has a convex portion with a thickness protruded upward with respect to the inner circumferential region or a concave portion with a thickness recessed downward with respect to the inner circumferential region.

2. The semiconductor wafer of claim 1, wherein the support region has a shape of double rings, the wafer further comprises an intermediate region sandwiched by the support region, and the convex portion or the concave portion is provided on the intermediate region instead of the outer circumferential region.

3. The semiconductor wafer of claim 1, wherein the convex portion has a thickness larger than that of the inner circumferential region by a thickness not smaller than 10 nm and not larger than 10 .mu.m.

4. The semiconductor wafer of claim 1, wherein the outer circumferential region is a region on an outer side than 0.9R where a radius of the semiconductor wafer is R.

5. A manufacturing method for a semiconductor wafer comprising a support region facing a support member, an outer circumferential region positioned on an outer side of the support region, and an inner circumferential region positioned on an inner side of the support region, the method comprising forming a convex portion with a thickness protruded upward with respect to the inner circumferential region or a concave portion with a thickness recessed downward with respect to the inner circumferential region, on the outer circumferential region.

6. A manufacturing method for a semiconductor device, the method comprising: supporting a semiconductor wafer with a support member provided between an outer circumferential region and an inner circumferential region, the wafer comprising a convex portion with a thickness protruded upward with respect to the inner circumferential region or a concave portion with a thickness recessed downward with respect to the inner circumferential region, the convex portion or the concave portion being formed on the outer circumferential region; and processing one of surfaces of the semiconductor wafer supported by the support member.

7. The manufacturing method of claim 6, comprising performing exposure processing of the one surface of the semiconductor wafer, with the one surface divided into a plurality of exposure pattern regions.

8. The manufacturing method of claim 6, comprising ejecting a film forming gas or an etching gas toward the one surface of the semiconductor wafer in a state where plasma is generated above the one surface.

9. The manufacturing method of claim 6, wherein the support member has a shape of a ring continuously surrounding the inner circumferential region along a circumferential direction of the semiconductor wafer.

10. The manufacturing method of claim 6, wherein the support member has a shape of pins dotted to intermittently surround the inner circumferential region along a circumferential direction of the semiconductor wafer.

Description

CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application is based upon and claims the benefit of priority from Japanese Patent Application No. 2019-161278, filed on Sep. 4, 2019; the entire contents of which are incorporated herein by reference.

FIELD

[0002] Embodiments of the present invention relate to a semiconductor wafer, a manufacturing method for a semiconductor wafer, and a manufacturing method for a semiconductor device.

BACKGROUND

[0003] Processes such as exposure, film formation, and etching are performed to a semiconductor wafer when a semiconductor device is manufactured. At this time, the semiconductor wafer is adsorbed in a state of being supported by a support member to keep a horizontal attitude.

[0004] When a semiconductor wafer is adsorbed in a state of being supported by a support member, an outside region of the semiconductor wafer positioned on an outer side of the support region bends in some cases.

BRIEF DESCRIPTION OF THE DRAWINGS

[0005] FIG. 1 is a plan view of a semiconductor wafer according to a first embodiment;

[0006] FIG. 2 is a sectional view along a section line A-A illustrated in FIG. 1;

[0007] FIG. 3 is a plan view illustrating a modification of a support member;

[0008] FIG. 4A is an explanatory diagram of a manufacturing method for a semiconductor wafer;

[0009] FIG. 4B is an explanatory diagram of the manufacturing method for a semiconductor wafer;

[0010] FIG. 5 is a schematic diagram of a substrate processing apparatus that exposes a semiconductor wafer to light;

[0011] FIG. 6 is a plan a view illustrating an exposure pattern region on the semiconductor wafer;

[0012] FIG. 7 is a sectional view of a semiconductor wafer according to a modification of the first embodiment;

[0013] FIG. 8 is a sectional view of a semiconductor wafer according to another modification of the first embodiment;

[0014] FIG. 9 is a schematic diagram of a substrate processing apparatus that performs film formation or etching of the semiconductor wafer;

[0015] FIG. 10 is a plan view of a semiconductor wafer according to a second embodiment;

[0016] FIG. 11 is a sectional view along a section line B-B illustrated in FIG. 10;

[0017] FIG. 12 is a sectional view of a semiconductor wafer according to a modification of the second embodiment; and

[0018] FIG. 13 is a sectional view of a semiconductor wafer according to another modification of the second embodiment.

DETAILED DESCRIPTION

[0019] Embodiments will now be explained with reference to the accompanying drawings. The present invention is not limited to the embodiments.

[0020] A semiconductor wafer according to an embodiment includes a support region facing a support member, an outer circumferential region positioned on an outer side of the support region, and an inner circumferential region positioned on an inner side of the support region. The outer circumferential region has a convex portion with a thickness protruded upward with respect to the inner circumferential region or a concave portion with a thickness recessed downward with respect to the inner circumferential region.

First Embodiment

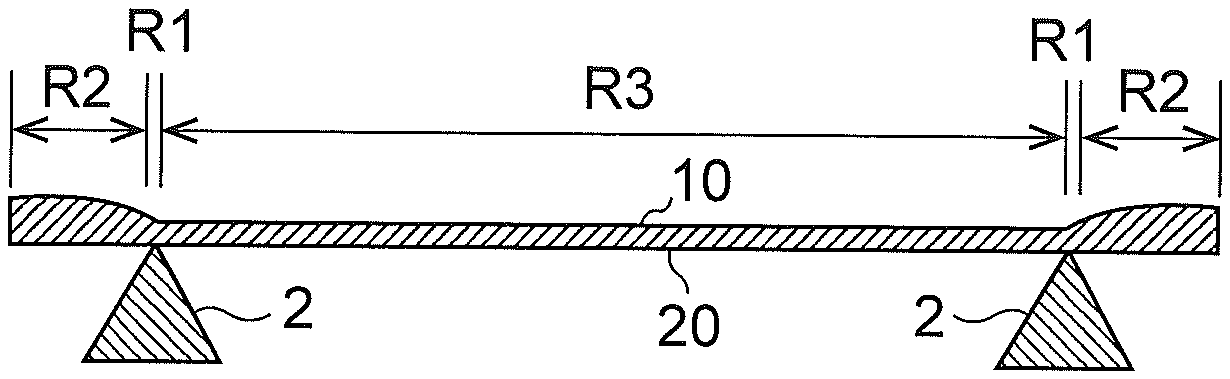

[0021] FIG. 1 is a plan view of a semiconductor wafer according to a first embodiment. FIG. 2 is a sectional view along a section line A-A illustrated in FIG. 1. FIG. 3 is a plan view illustrating a modification of a support member.

[0022] A semiconductor wafer 1 according to the present embodiment includes a first surface 10 and a second surface 20. Processes such as exposure, film formation, and etching are performed to the first surface 10. The second surface 20 is in contact with a support member 2 as illustrated in FIG. 2. The first surface 10 and the second surface 20 include a support region R1, an outer circumferential region R2, and an inner circumferential region R3.

[0023] The support member 2 has a shape of a ring continuously surrounding the inner circumferential region R3 along the circumferential direction of the semiconductor wafer 1. The support member 2 may have a shape of pins dotted to intermittently surround the inner circumferential region R3 along the circumferential direction as illustrated in FIG. 3.

[0024] The support region R1 is a region facing the support member 2 in the vertical direction. The outer circumferential region R2 is a region positioned on the outer side of the support region R1. The inner circumferential region R3 is a region positioned on the inner side of the support region R1 and including a center C of the semiconductor wafer 1.

[0025] In the present embodiment, the outer circumferential region R2 of the semiconductor wafer 1 has a convex portion with a thickness protruded upward with respect to the inner circumferential region R3 as illustrated in FIG. 2. The outer circumferential region R2 is, for example, a region on an outer side than 0.9R where the radius of the semiconductor wafer 1 is R, in other words, a region where the distance from the outer circumferential end of the semiconductor wafer 1 is 0.1R.

[0026] A manufacturing method for the semiconductor wafer 1 described above is explained below with reference to FIGS. 4A and 4B.

[0027] First, a semiconductor wafer 1a is formed as illustrated in FIG. 4A. A thickness t1 of the semiconductor wafer 1a is constant in the entire region. Next, a region corresponding to the support region R1 and the inner circumferential region R3 described above of the semiconductor wafer 1a is ground by, for example, chemical mechanical polishing (CMP) or etching until the region has a thickness t2 (<t1) as illustrated in FIG. 4B. As a result, the outer circumferential region R2 becomes a convex portion with the thickness protruded upward with respect to the inner circumferential region R3, whereby the semiconductor wafer according to the present embodiment is completed. A semiconductor device can be manufactured by performing exposure and film formation to this semiconductor wafer 1. The semiconductor device includes, for example, a three-dimensional semiconductor memory where electrode layers (word lines) are stacked.

[0028] An exposure step for the semiconductor wafer 1 according to the present embodiment is explained below with reference to FIG. 5. FIG. 5 is a schematic diagram of a substrate processing apparatus that exposes the semiconductor wafer 1 according to the present embodiment to light.

[0029] A substrate processing apparatus 100 illustrated in FIG. 5 includes a substrate stage 101, a projector 102, a mask stage 103, a light source 104, and a controller 105. The substrate processing apparatus 100 is, for example, a scanning exposure apparatus that performs projection exposure of a pattern drawn on a mask MK onto the semiconductor wafer 1 being an exposure target while synchronously moving the mask MK and the semiconductor wafer 1 with respect to each other in a scanning direction.

[0030] The substrate stage 101 holds the semiconductor wafer 1 via the support member 2. A chuck part 111 is provided on the substrate stage 101. The chuck part 111 causes the semiconductor wafer 1 to be adsorbed to the substrate stage 101 with, for example, static electricity or vacuum. The substrate stage 101 is capable of horizontally moving or rotationally moving on the basis of control of the controller 105.

[0031] The projector 102 is provided above the substrate stage 101. The mask stage 103 holding the mask MK is provided above the projector 102. The light source 104 is provided above the mask stage 103.

[0032] In the substrate processing apparatus 100, exposure light emitted from the light source 104 is diffracted by the pattern drawn on the mask MK and enters the projector 102. The projector 102 performs projection exposure of the first surface 10 of the semiconductor wafer 1 to the incident light. Accordingly, the pattern on the mask MK is transferred to the first surface 10.

[0033] FIG. 6 is a plan a view illustrating an exposure pattern region on the semiconductor wafer. The substrate processing apparatus 100 performs the exposure processing with the semiconductor wafer 1 being divided into a plurality of exposure pattern regions. The exposure pattern regions of the substrate processing apparatus 100 include an exposure pattern region E1 that entirely falls within the semiconductor wafer 1 while including an exposure pattern region E2 that partially spreads out of the semiconductor wafer 1 as illustrated in FIG. 6.

[0034] A large part of the exposure pattern region E2 is occupied by the outer circumferential region R2 of the semiconductor wafer 1. At the time of exposure processing, the semiconductor wafer 1 is adsorbed to the substrate stage 101 by the chuck part 111 in a state of being supported by the support member 2 as described above. At this time, if the thicknesses of the support region R1, the outer circumferential region R2, and the inner circumferential region R3 are all equal, the outer circumferential region R2 sometimes bends downward (hangs down) from a boundary portion with the support region R1 to be a curved surface while the inner circumferential region R3 is generally a flat surface. In this case, a desired focus accuracy is not obtained on the exposure pattern region E2 and an exposure failure is likely to occur.

[0035] In the present embodiment, the outer circumferential region R2 is processed into a convex portion with the thickness protruded upward with respect to the inner circumferential region R3. Accordingly, the outer circumferential region R2 is thicker than the inner circumferential region R3 and is therefore less likely to bend. The thickness t1 of the convex portion is set based on a largest bending amount of the outer circumferential region R2, which is supposed in a case where the respective thicknesses of the regions are equal. For example, when a radius R of the semiconductor wafer 1 is 150 millimeters (the diameter is 300 millimeters), the largest bending amount is generally not smaller than 10 nm and not larger than 10 .mu.m. In this case, to suppress bending of the outer circumferential region R2, the thickness t1 of the convex portion is desirably larger than the thickness t2 by a thickness not smaller than 10 nm and not larger than 10 .mu.m.

[0036] Due to formation of the convex portion on the outer circumferential region R2 as described above, the semiconductor wafer 1 has a generally horizontal attitude when adsorbed in the state of being supported by the support member 2. Therefore, the focus accuracy of the exposure pattern region R2 is ensured. Accordingly, an exposure failure in the outer circumferential region R2 can be reduced.

[0037] FIG. 7 is a sectional view of a semiconductor wafer according to a modification of the first embodiment. FIG. 8 is a sectional view of a semiconductor wafer according to another modification of the first embodiment.

[0038] In the embodiment described above, the first surface 10 of the outer circumferential region R2 is protruded assuming a situation in which the outer circumferential region R2 bends downward from the boundary portion with the support region R1 at the time of adsorption of the semiconductor wafer 1. However, a situation in which the outer circumferential region R2 bends upward (warps upward) at the time of adsorption of the semiconductor wafer 1 is also supposed. In this case, when the second surface 20 of the outer circumferential region R2 is protruded as illustrated in FIG. 7, deformation of the outer circumferential region R2 is suppressed and an exposure failure can be consequently reduced.

[0039] A concave portion having a thickness recessed downward with respect to the inner circumferential region R3 may be formed on the outer circumferential region R2 as illustrated in FIG. 8 in anticipation of deformation of the outer circumferential region R2, which is expected at the time of adsorption of the semiconductor wafer 1 in a case where the thicknesses of the respective regions are uniform.

[0040] A film formation step and an etching step for the semiconductor wafer 1 according to the present embodiment are explained next with reference to FIG. 9. FIG. 9 is a schematic diagram of a substrate processing apparatus that performs film formation or etching of the semiconductor wafer 1 according to the present embodiment.

[0041] A substrate processing apparatus 200 illustrated in FIG. 9 includes an electrostatic chuck part 201, a focus ring 202, a lower electrode 203, and a head 204. The substrate processing apparatus 200 is, for example, a plasma CVD (Chemical Vapor Deposition) apparatus that forms a film on the semiconductor wafer 1 by CVD in a state where plasma is generated, or an etching apparatus that etches a film formed on the semiconductor wafer 1 by dry etching using plasma.

[0042] The electrostatic chuck part 201 holds the semiconductor wafer 1 via the support member 2. The focus ring 202 is placed on the top surface of the electrostatic chuck part 201. The electrostatic chuck part 201 causes the semiconductor wafer 1 and the focus ring 202 to be adsorbed thereto with static electricity.

[0043] The focus ring 202 is formed in an annular shape surrounding the semiconductor wafer 1. The focus ring 202 is placed to uniformly generate plasma between the center of the semiconductor wafer 1 and the outer circumference thereof.

[0044] The lower electrode 203 is provided on the bottom part of the electrostatic chuck part 201. The head 204 is provided above the electrostatic chuck part 201. Plasma is generated when a high-frequency electric field is generated between the lower electrode 203 and the head 204 by supply of power from a high-frequency power source (not illustrated). When plasma is generated, the head 204 ejects a film forming gas or an etching gas toward the first surface 10 of the semiconductor wafer 1.

[0045] In the substrate processing apparatus 200, plasma generation on the outer circumferential region R2 of the semiconductor wafer 1 is particularly adjusted by installation of the focus ring 202. However, if the outer circumferential region R2 bends at the time of adsorption by the electrostatic chuck part 201, the horizontal attitude cannot be maintained and thus the controllability of film formation or etching is degraded. As a result, a film formation failure or an etching failure is likely to occur.

[0046] However, in the semiconductor wafer 1 according to the present embodiment, the shape of the outer circumferential region R2 is optimized to enable the outer circumferential region R2 to keep the horizontal attitude at the time of adsorption by the electrostatic chuck part 201. Accordingly, the controllability of film formation or etching is improved and a film formation failure or an etching failure can be reduced.

Second Embodiment

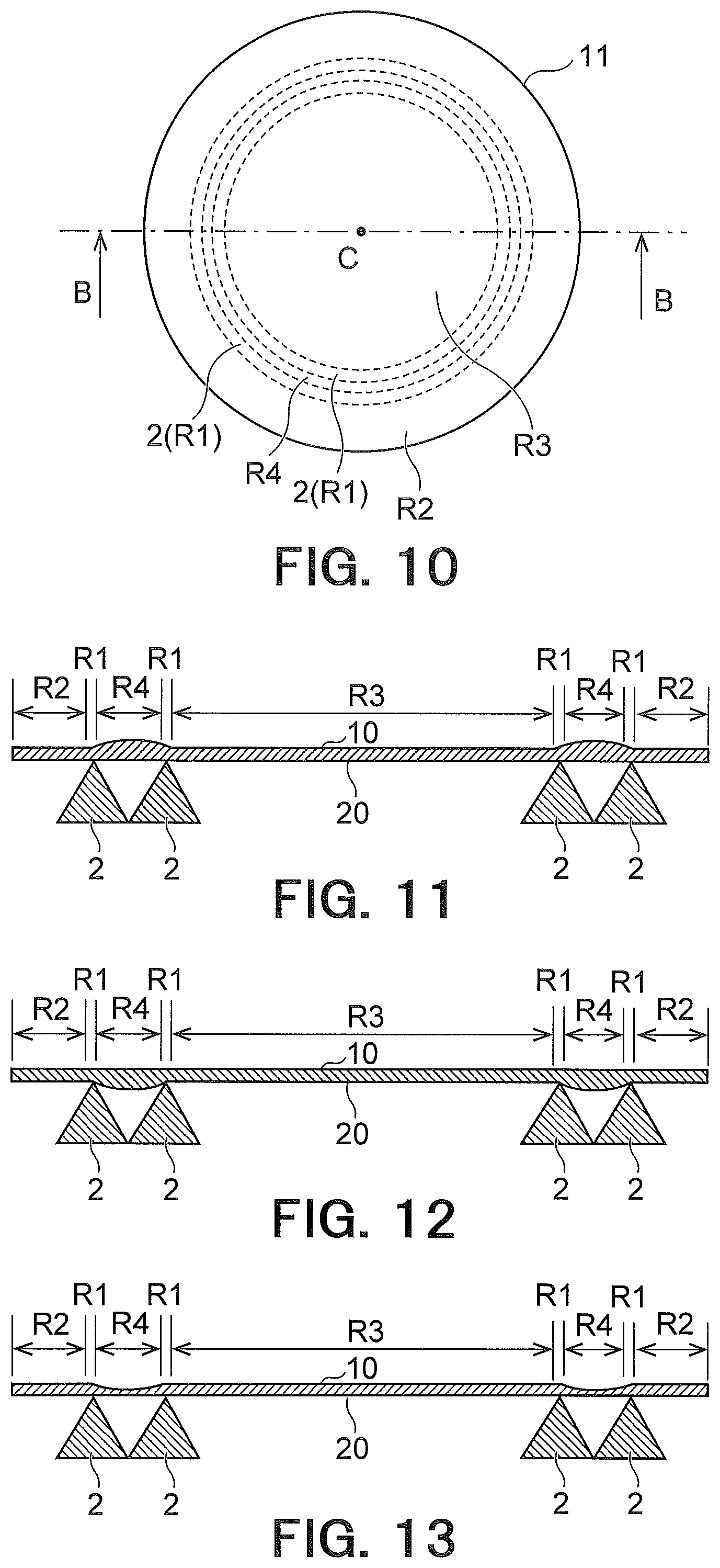

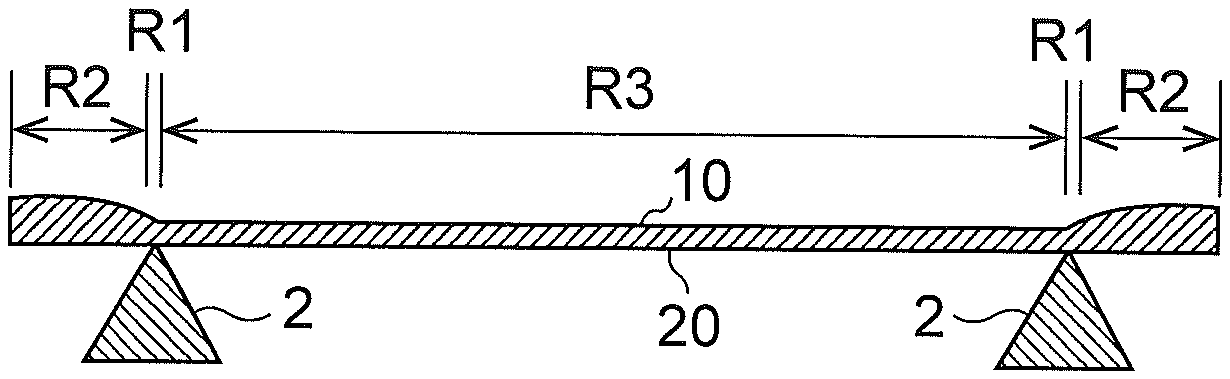

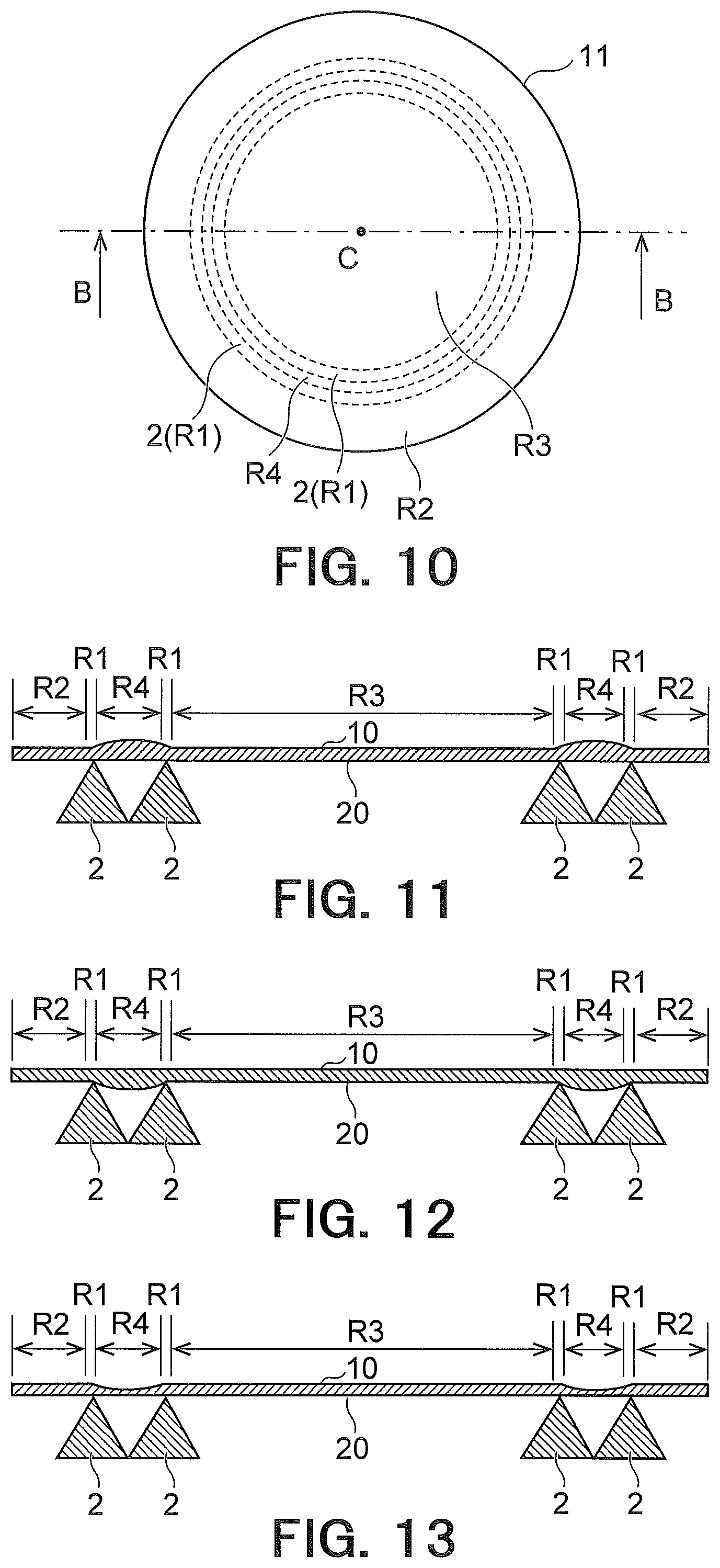

[0047] FIG. 10 is a plan view of a semiconductor wafer according to a second embodiment. FIG. 11 is a sectional view along a section line B-B illustrated in FIG. 10. In FIG. 10 and FIG. 11, constituent elements identical to those in the first embodiment described above are denoted by like reference signs, and detailed explanations thereof are omitted.

[0048] As illustrated in FIGS. 10 and 11, a semiconductor wafer 11 according to the present embodiment is supported by the support member 2 having a ring shape continuously doubly surrounding the inner circumferential region R3 along the circumferential direction. In a case of this support mode, the semiconductor wafer 11 has an intermediate region R4 sandwiched by the support region R1 in addition to the support region R1, the outer circumferential region R2, and the inner circumferential region R3. The intermediate region R4 has a possibility of bending downward when adsorbed by the substrate processing apparatus 100 and the substrate processing apparatus 200 explained in the first embodiment. In this case, process failures such as an exposure failure, a film formation failure, and an etching failure are likely to occur on the intermediate region R4.

[0049] In the present embodiment, in order to solve this problem, a portion of the intermediate region R4 on the side of the first surface 10 is processed into a convex portion with the thickness protruded upward with respect to the outer circumferential region R2 and the inner circumferential region R3. Accordingly, the intermediate region R4 is thicker than the outer circumferential region R2 and the inner circumferential region R3 and is thus less likely to bend. As a result, the semiconductor wafer 11 has a generally horizontal attitude when adsorbed by the substrate processing apparatus 100 or the substrate processing apparatus 200 and process failures on the intermediate region R4 can be reduced.

[0050] FIG. 12 is a sectional view of a semiconductor wafer according to a modification of the second embodiment. FIG. 13 is a sectional view of a semiconductor wafer according to another modification of the second embodiment.

[0051] For example, in a case in which a situation where the outer circumferential region R2 bends upward (warps upward) at the time of adsorption of the semiconductor wafer 11 is supposed, deformation of the intermediate region R4 can be suppressed when a portion of the intermediate region R4 on the side of the second surface 20 is protruded as illustrated in FIG. 12. Consequently, process failures can be reduced. Further, a concave portion recessed downward with respect to the outer circumferential region R2 and the inner circumferential region R3 may be formed by grinding the intermediate region R4 as illustrated in FIG. 13 in anticipation of deformation of the intermediate region R4, which is expected at the time of adsorption of the semiconductor wafer 1 in a case where the thicknesses of the respective regions are uniform.

[0052] While certain embodiments have been described, these embodiments have been presented by way of example only, and are not intended to limit the scope of the inventions. Indeed, the novel embodiments described herein may be embodied in a variety of other forms; furthermore, various omissions, substitutions and changes in the form of the embodiments described herein may be made without departing from the spirit of the inventions. The accompanying claims and their equivalents are intended to cover such forms or modifications as would fall within the scope and spirit of the inventions.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.