Logic Circuitry

GARDNER; James Michael ; et al.

U.S. patent application number 16/965557 was filed with the patent office on 2021-02-18 for logic circuitry. The applicant listed for this patent is Hewlett-Packard Development Company, L.P.. Invention is credited to Michael W. CUMBIE, James Michael GARDNER, Scott A. LINN, David N. OLSEN, Stephen D. PANSHIN, David Owen ROETHIG, Anthony D. STUDER, Jefferson P. WARD.

| Application Number | 20210046760 16/965557 |

| Document ID | / |

| Family ID | 1000005225534 |

| Filed Date | 2021-02-18 |

View All Diagrams

| United States Patent Application | 20210046760 |

| Kind Code | A1 |

| GARDNER; James Michael ; et al. | February 18, 2021 |

LOGIC CIRCUITRY

Abstract

In an example, a method comprises, by logic circuitry associated with a replaceable print apparatus component installed in a print apparatus, receiving a sensor data request and determining whether the request is for data indicative of a print material level or for data indicative of a pressurisation event. In the event that the request is a request for data indicative of the print material level, the method may comprise responding with a first data response in a first value range; and in the event that the request is a request for data indicative of a pressurisation event, the method may comprise responding with a second data response in a second value range.

| Inventors: | GARDNER; James Michael; (Corvallis, OR) ; LINN; Scott A.; (Corvallis, OR) ; PANSHIN; Stephen D.; (Corvallis, OR) ; WARD; Jefferson P.; (Vancouver, WA) ; ROETHIG; David Owen; (Vancouver, WA) ; OLSEN; David N.; (Corvallis, OR) ; STUDER; Anthony D.; (Corvallis, OR) ; CUMBIE; Michael W.; (Corvallis, OR) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 1000005225534 | ||||||||||

| Appl. No.: | 16/965557 | ||||||||||

| Filed: | April 5, 2019 | ||||||||||

| PCT Filed: | April 5, 2019 | ||||||||||

| PCT NO: | PCT/US2019/026161 | ||||||||||

| 371 Date: | July 28, 2020 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| PCT/US2018/063624 | Dec 3, 2018 | |||

| 16965557 | ||||

| PCT/US2018/063630 | Dec 3, 2018 | |||

| PCT/US2018/063624 | ||||

| PCT/US2018/063631 | Dec 3, 2018 | |||

| PCT/US2018/063630 | ||||

| PCT/US2018/063638 | Dec 3, 2018 | |||

| PCT/US2018/063631 | ||||

| PCT/US2018/063643 | Dec 3, 2018 | |||

| PCT/US2018/063638 | ||||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | G06F 2213/40 20130101; B41J 2/17546 20130101; G06F 13/42 20130101; G06F 21/44 20130101; G06K 15/4075 20130101 |

| International Class: | B41J 2/175 20060101 B41J002/175; G06F 13/42 20060101 G06F013/42; G06F 21/44 20060101 G06F021/44; G06K 15/00 20060101 G06K015/00 |

Claims

1. A method comprising, by logic circuitry associated with a replaceable print apparatus component installed in a print apparatus, receiving a sensor data request; determining whether the request is for data indicative of a print material level or for data indicative of a pressurisation event; and in the event that the request is a request for data indicative of the print material level, responding with a first data response in a first value range; and in the event that the request is a request for data indicative of a pressurisation event, responding with a second data response in a second value range.

2. A method according to claim 1 further comprising measuring sensor data in response to the sensor data request.

3. A method according to claim 1, wherein responding to a sensor data request comprises determining whether the sensor data request is for data indicative of a print material level or for data indicative of a pressurisation event based on an identifier.

4. A method according to claim 1, further comprising, prior to returning the first or second data response, storing the first or second data response in a predetermined memory location.

5. A method according to claim 1, comprising, in response to receiving the sensor data request, acquiring the first or second data response and prior to returning the first or second data response, receiving a request to supply the acquired first or second data response.

6. A method according to claim 5 in which the sensor data request includes a write command and the request to supply the acquired first or second data response includes a read command.

7. A method according to claim 1, further comprising receiving the request and returning the first and/or second data response via a communication bus.

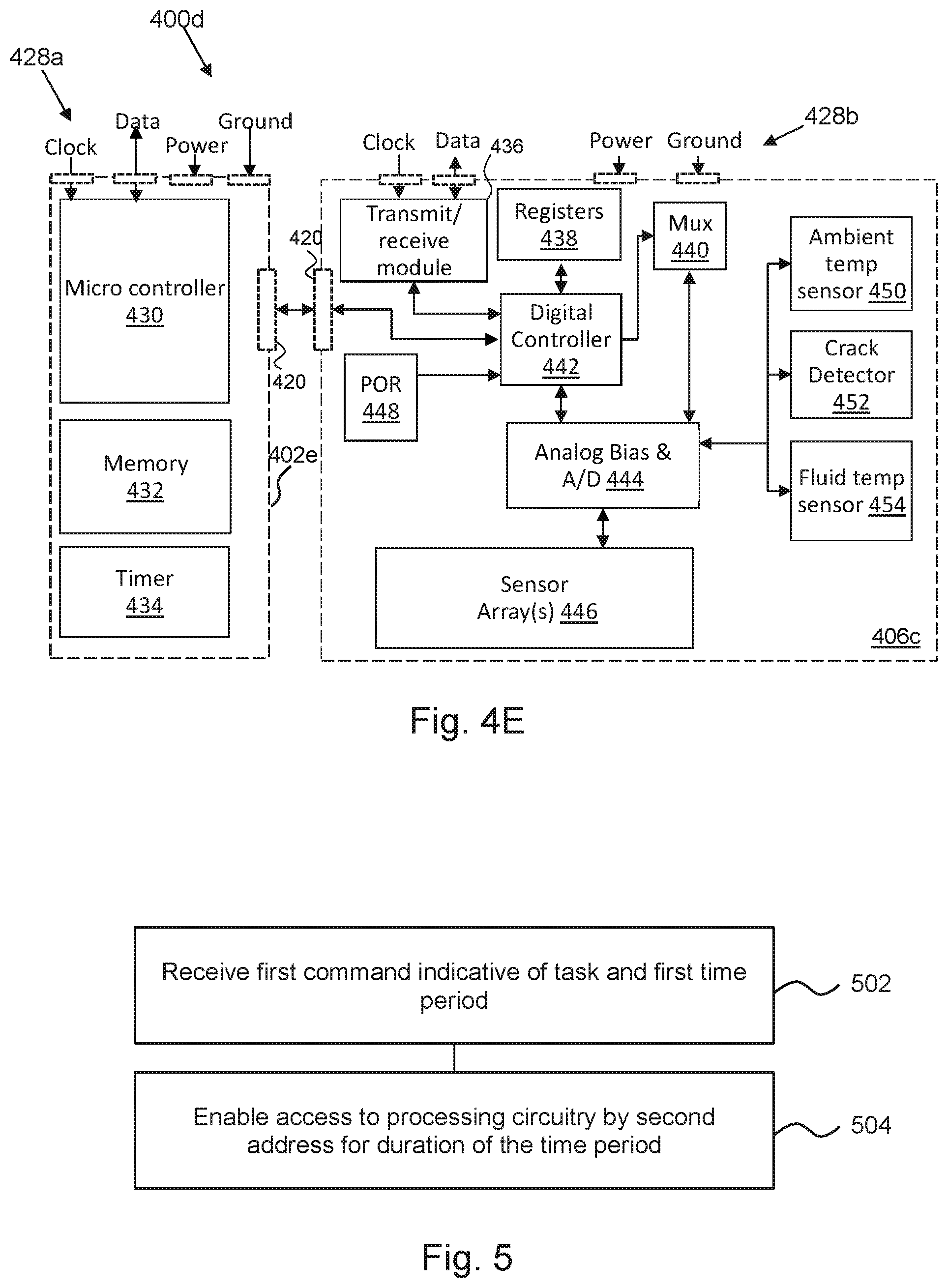

8. A method according to claim 1, further comprising, prior to receiving the sensor data request, and in response to a first command indicative of a time period sent to a first address of processing circuitry via a communications bus, enabling, by the processing circuitry, access thereto via at least one second address for a duration of the time period.

9. A method according to claim 8 wherein the second address is configured to be an initial second address at the start of the first time period.

10. A method according to claim 9 comprising reconfiguring, by the processing circuitry, the initial second address to a temporary address in response to a command sent to the initial second address and including that temporary address during the first time period.

11. A method according to claim 9 comprising, on receipt of a subsequent command indicative of the task and the first time period sent to the first address, configuring the processing circuitry to have the same initial second address.

12. A method according to claim 1, further comprising, prior to receiving the first command, responding to a first validation request to a first address associated with the logic circuitry with a cryptographically authenticated validation response.

13. A method according to claim 12 in which the first and second data responses are not cryptographically authenticated.

14. A method according to claim 1, comprising, prior to receiving the sensor data request, calibrating data response parameters.

15. A method according to claim 1, which comprises receiving a plurality of data requests for data indicative of a print material level or data indicative of a pressurisation event, and returning a plurality of first data responses in the first value range, or a plurality of second data responses in a second value range accordingly.

16. A method according to claim 15 wherein: if a plurality of first data responses is provided, the plurality of first data responses comprise a sequence of data readings having a step change, and/or if a plurality of second data responses is provided, the plurality of second data responses comprise a smoothly varying sequence of data readings.

17. A logic circuitry package configured to: communicate with a print apparatus logic circuit, determine whether a sensor data request received from the print apparatus logic circuit is for data indicative of a print material level or for data indicative of a pressurisation event; and in the event that the request is a request for data indicative of the print material level, respond with a first data response in a first value range; and in the event that the request is a request for data indicative of a pressurisation event, respond with a second data response in a second value range.

18. A logic circuitry package according to claim 17 configured to: receive a plurality of data requests for data indicative of a print material level or data indicative of a pressurisation event; and return a plurality of first data responses in the first value range, or a plurality of second data responses in a second value range accordingly, wherein: if a plurality of first data responses is provided, the plurality of first data responses include a sequence of data readings having a step change, and/or if a plurality of second data responses is provided, the plurality of second data responses include a smoothly varying sequence of data reading.

19-45. (canceled)

46. A replaceable print apparatus component including an I2C compatible logic circuitry package, wherein the I2C compatible logic circuitry package comprises: an I2C interface including a data contact to communicate via an I2C bus of a host print apparatus; a memory comprising data representing print liquid characteristics, the data retrievable and updatable via the data contact; wherein the package is configured to transmit data including said data representing print liquid characteristics to the bus over the data contact; and wherein the package is further configured to communicate with a print apparatus logic circuit, and to respond to a first sensor data request received from the print apparatus logic circuit by returning a first response, and to respond to a second sensor data request received from the print apparatus logic circuit by returning a second response, wherein the first sensor data request is a request for data or a first sensor type and the second sensor data request is a request for data or a first sensor type, and the second response is different from the first response.

47. A replaceable print apparatus component according to claim 46 wherein the I2C compatible logic circuitry package is configured to: in response to a first authenticated command received through the data contact, decode the command and respond with an authenticated message authenticated using an authentication feature, in response to at least one second authenticated command received through the same data contact, the command including a second I2C address and a timing period, set at least part of the logic to respond to commands directed to the second address, start a timer to determine the end of the timing period, after start of the timer, respond to messages sent to the second I2C address, during at least part of the timing period by providing the first and second responses, and after the timing period, respond to messages addressed to the first I2C address and not to the second I2C address.

48. A replaceable print apparatus component according to claim 46 wherein the I2C compatible logic circuitry package is configured to carry out the method of any of claims 1 to 16.

Description

BACKGROUND

[0001] Subcomponents of apparatus may communicate with one another in a number of ways. For example, Serial Peripheral Interface (SPI) protocol, Bluetooth Low Energy (BLE), Near Field Communications (NFC) or other types of digital or analogue communications may be used.

[0002] Some 2D and 3D printing systems include one or more replaceable print apparatus components, such as print material containers (e.g. inkjet cartridges, toner cartridges, ink supplies, 3D printing agent supplies, build material supplies etc.), inkjet printhead assemblies, and the like. In some examples, logic circuitry associated with the replaceable print apparatus component(s) communicate with logic circuitry of the print apparatus in which they are installed, for example communicating information such as their identity, capabilities, status and the like. In further examples, print material containers may include circuitry to execute one or more monitoring functions such as print material level sensing.

[0003] Disclosures discussing data stored on, and pertaining to, print apparatus components include EP patent publication No. 0941856, and international patent application publications Nos. WO2015/016860 and WO2016/028272, and US patent publication No. 6685290. Disclosures of communication and authentication circuits for print apparatus components include US patent publication Nos. 9619663, 9561662 and 9893893. Examples disclosures discussing print material sensors and sensor arrays for print apparatus components include international patent application publications Nos. WO2017/189010, WO2017/189011, WO2017/074342, WO2017/184147, WO2017184143, and WO2018/022038. Example disclosures discussing air and pressure regulation include US patent publication Nos. 8919935, 9056479, 9090082, 8998393, 9315030 and 9211720. These publications are incorporated by reference.

BRIEF DESCRIPTION OF DRAWINGS

[0004] Non-limiting examples will now be described with reference to the accompanying drawings, in which:

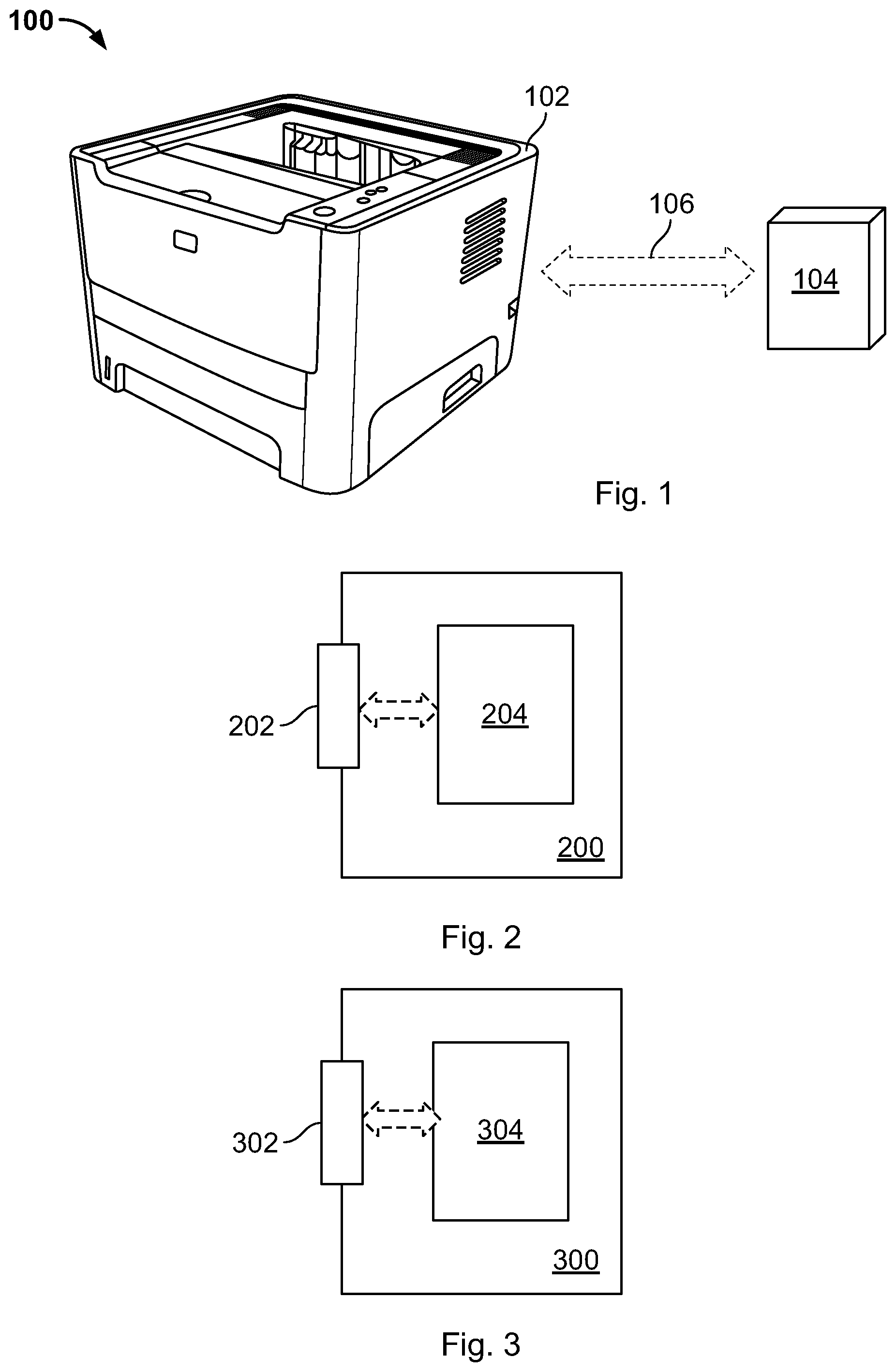

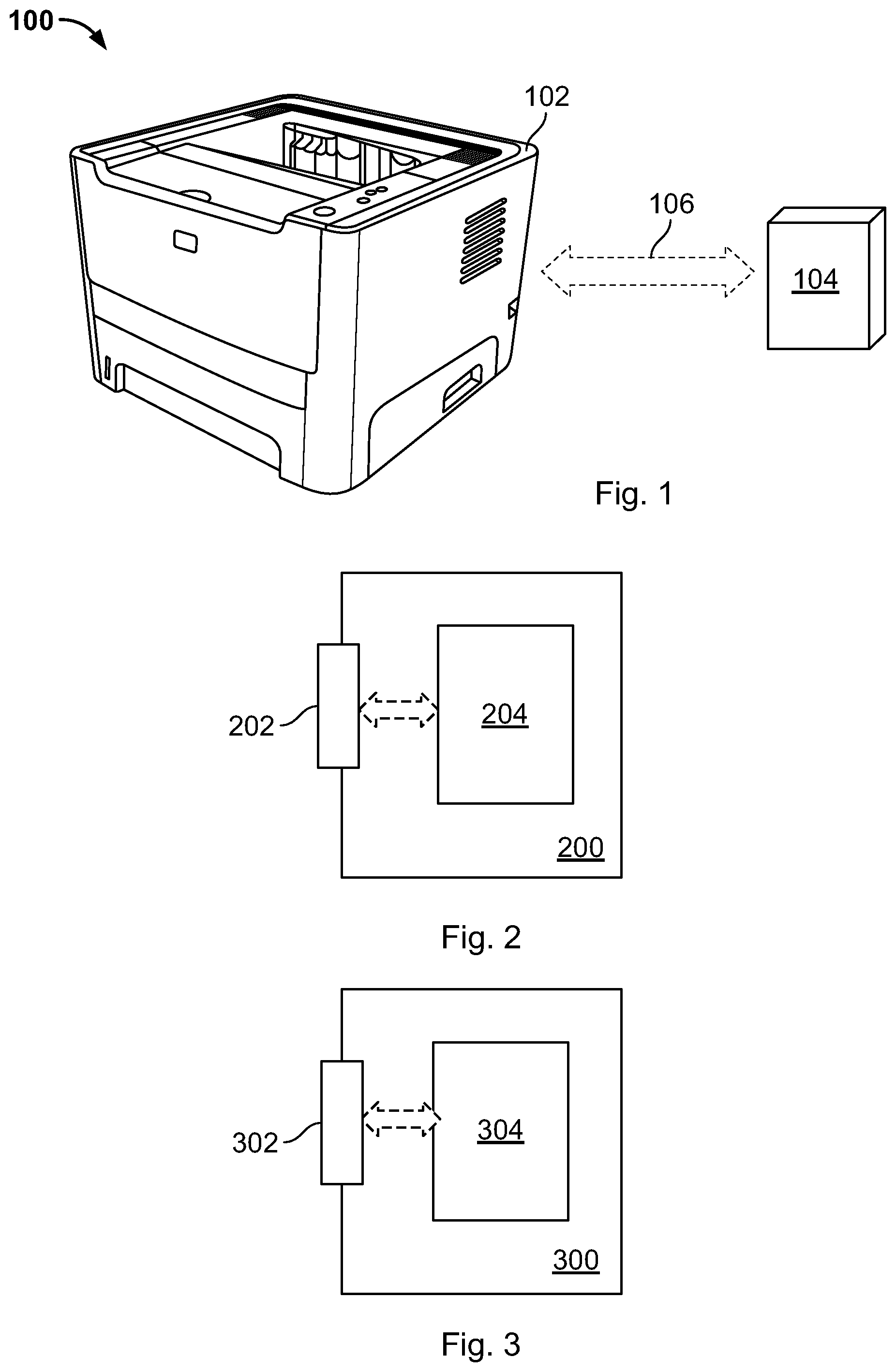

[0005] FIG. 1 is an example of a printing system;

[0006] FIG. 2 is an example of a replaceable print apparatus component;

[0007] FIG. 3 shows an example of a print apparatus;

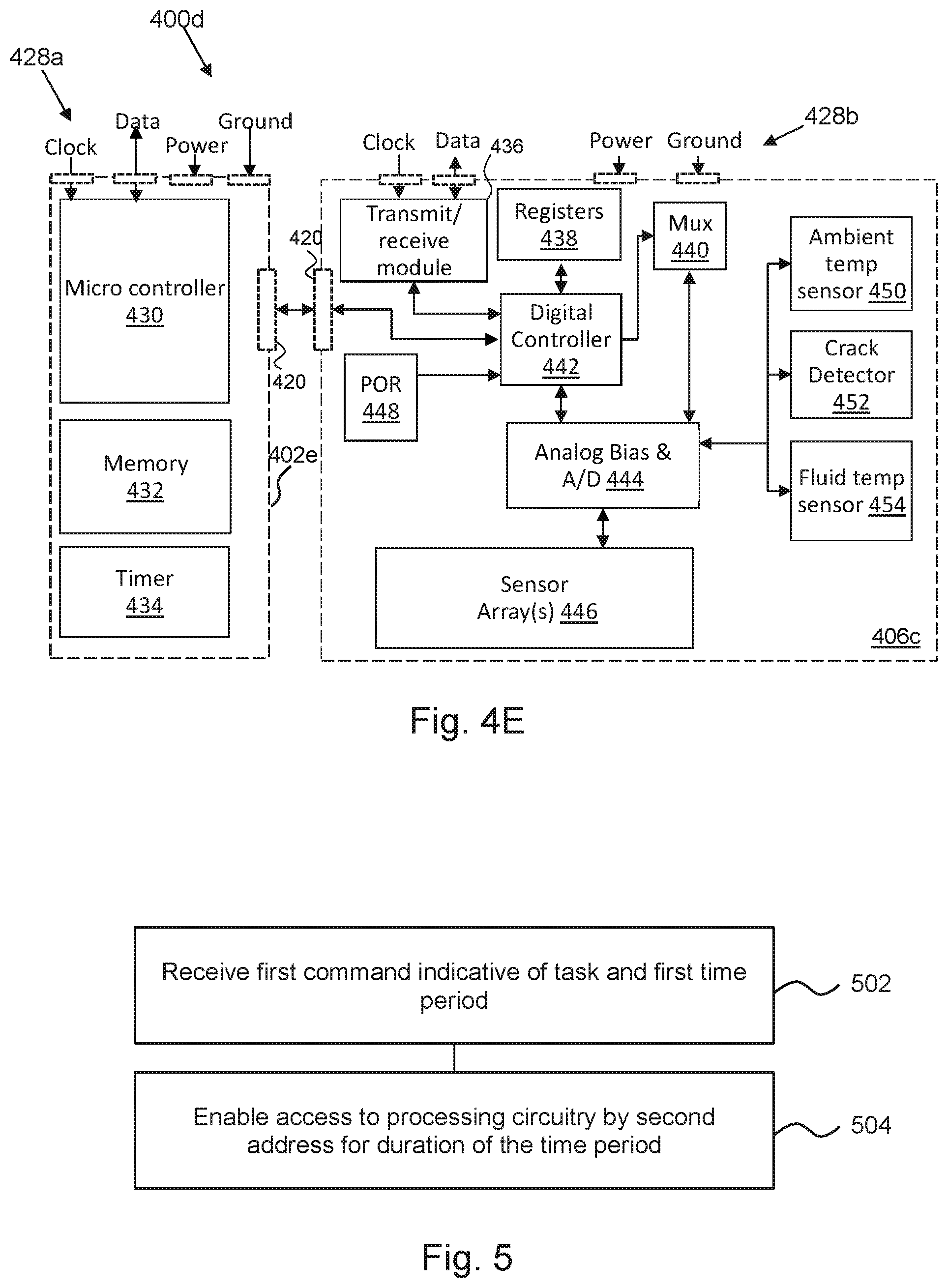

[0008] FIGS. 4A, 4B, 4C, 4D and 4E show examples of logic circuitry packages and processing circuitry;

[0009] FIG. 5 is an example of a method which may be carried out by a logic circuitry package;

[0010] FIG. 6 is a further example of a method which may be carried out by a logic circuitry package;

[0011] FIG. 7 shows an example of a method which may be carried out for example by processing circuitry;

[0012] FIG. 8 shows an example arrangement of replaceable print apparatus components in a print apparatus;

[0013] FIG. 9 shows an example of a replaceable print apparatus component;

[0014] FIG. 10 is an example of a method of validating a print apparatus component;

[0015] FIG. 11 is a further example of a method of validating a print apparatus component;

[0016] FIG. 12 shows another example of a method of validation;

[0017] FIG. 13A shows an example arrangement of a fluid level sensor;

[0018] FIG. 13B shows an example of a perspective view of a print cartridge

[0019] FIG. 14 shows an example of a logic circuitry package;

[0020] FIG. 15 shows a further example of a logic circuitry package;

[0021] FIGS. 16 to 18 show example methods of calibrating sensors;

[0022] FIGS. 19A and 19B show example methods of reading sensors;

[0023] FIG. 20A shows an example fluid level sensor and FIGS. 20B and 20C shows examples of data acquired from a fluid level sensor; and

[0024] FIG. 21A shows an example pressure event sensor and FIG. 21B shows examples of data acquired from a pressure event sensor.

DETAILED DESCRIPTION

[0025] Some examples of applications described herein are in the context of print apparatus. However, not all the examples are limited to such applications, and at least some of the principles set out herein may be used in other contexts.

[0026] The contents of other applications and patents cited in this disclosure are incorporated by reference.

[0027] In certain examples, Inter-integrated Circuit (I.sup.2C, or I2C, which notation is adopted herein) protocol allows at least one `master` integrated circuit (IC) to communicate with at least one `slave` IC, for example via a bus. I2C, and other communications protocols, communicate data according to a clock period. For example, a voltage signal may be generated, where the value of the voltage is associated with data. For example, a voltage value above x may indicate a logic "1" whereas a voltage value below x volts may indicate a logic "0", where x is a predetermined numerical value. By generating an appropriate voltage in each of a series of clock periods, data can be communicated via a bus or another communication link.

[0028] Certain example print material containers have slave logic that utilizes I2C communications, although in other examples, other forms of digital or analogue communications could also be used. In the example of I2C communication, a master IC may generally be provided as part of the print apparatus (which may be referred to as the `host`) and a replaceable print apparatus component would comprise a `slave` IC, although this need not be the case in all examples. There may be a plurality of slave ICs connected to an I2C communication link or bus (for example, containers of different colors of print agent). The slave IC(s) may comprise a processor to perform data operations before responding to requests from logic circuitry of the print system.

[0029] Communications between print apparatus and replaceable print apparatus components installed in the apparatus (and/or the respective logic circuitry thereof) may facilitate various functions.

[0030] Logic circuitry within a print apparatus may receive information from logic circuitry associated with a replaceable print apparatus component via a communications interface, and/or may send commands to the replaceable print apparatus component logic circuitry, which may comprise commands to write data to a memory associated therewith, or to read data therefrom.

[0031] This disclosure may refer to print apparatus components, which may include replaceable print apparatus components. Certain print apparatus components may include a reservoir holding print agent or print material. In this disclosure print material and print agent mean the same thing and are intended to encompass different example print materials including ink, toner particles, liquid toner, three-dimensional printing agents (including stimulators and inhibitors), three-dimensional printing build material, three-dimensional print powder.

[0032] For example, the identity, functionality and/or status of a replaceable print apparatus component and/or the logic circuitry associated therewith may be communicated to logic circuitry of a print apparatus via a communications interface. For example, a print agent container logic circuit may be configured to communicate an identity. For example, the identity may be stored on the logic circuit to facilitate the checking thereof by a compatible print apparatus logic circuit, wherein in different examples the identity may be in the form of a product serial number, another cartridge number, a brand name, a signature or bit indicating an authenticity, etc. In certain examples of this disclosure, multiple functions or logic circuits may be associated with a single logic circuit package of a single print apparatus component whereby multiple corresponding identities may be stored on and/or read from the logic circuit package. For example, the logic circuitry of the print apparatus component may store print apparatus component characteristics data, for example comprising data representative of at least one characteristic of a print material container, for example print material identifying characteristics, such as, total volume, initial fill volume and/or fill proportion (see for example EP patent publication No. 0941856); color such as cyan, magenta, yellow or black; color data including compressed or non-compressed color maps or portions thereof (see for example international patent application publication No. WO2015/016860); data to reconstruct colour maps such as recipes (see for example international patent application publication No. WO2016/028272); etc. For example, the print material characteristics may be configured to enhance a functionality or output with respect to a print apparatus in which it is installed. In a further example, a status, such as print material level-related data (e.g. a fill level) or other sensed (e.g. dynamic) property, may be provided via a communications interface, for example such that a print apparatus may generate an indication of the fill level to a user. In some examples, a validation process may be carried out by a print apparatus. An example of a cryptographically authenticated communication scheme is explained in US patent publication 9619663. For example, the print apparatus may verify that a print agent container originates from an authorized source, so as to ensure the quality thereof (for example, performing an authentication thereof). Examples of logic circuits of replaceable components that are configured to respond to authentication requests are US patent publication No. 9619663, US patent publication No. 9561662 and/or US patent publication No. 9893893.

[0033] In certain examples of this disclosure, a validation process may include an integrity check to ensure that the replaceable print apparatus component and/or the logic circuitry associated therewith is functioning as expected, for example that communicated identity or identities, print material characteristics and status are as expected. The validation process may further comprise requesting sensor information such that logic circuitry of a print apparatus component can check that this sensor data complies with expected parameters.

[0034] Examples of sensors and sensor arrays are disclosed in prior international patent application publications WO2017/074342, WO2017/184147, and WO2018/022038. These or other sensor types, or other arrangements that simulate signal outputs similar to these sensor arrays, could be used in accordance with this disclosure.

[0035] In turn, instructions to perform tasks may be sent to logic circuitry of a print apparatus component from logic circuitry associated with a print apparatus via the communications interface.

[0036] In at least some of the examples described below, a logic circuitry package is described. The logic circuitry package may be associated with a replaceable print apparatus component, for example being internally or externally affixed thereto, for example at least partially within the housing, and is adapted to communicate data with a print apparatus controller via a bus provided as part of the print apparatus.

[0037] A `logic circuitry package` as the term is used herein refers to one or more logic circuits that may be interconnected or communicatively linked to each other. Where more than one logic circuit is provided, these may be encapsulated as a single unit, or may be separately encapsulated, or not encapsulated, or some combination thereof. The package may be arranged or provided on a single substrate or a plurality of substrates. In some examples the package may be directly affixed to a cartridge wall. In some examples, the package may comprise an interface, for example comprising pads or pins. The package interface may be intended to connect to a communication interface of the print apparatus component that in turn connects to a print apparatus logic circuit, or the package interface may connect directly to the print apparatus logic circuit. Example packages may be configured to communicate via a serial bus interface.

[0038] In some examples, each logic circuitry package is provided with at least one processor and memory. In one example, the logic circuitry package may be, or may function as, a microcontroller or secure microcontroller. In use, the logic circuitry package may be adhered to or integrated with the replaceable print apparatus component. A logic circuitry package may alternatively be referred to as a logic circuitry assembly, or simply as logic circuitry or processing circuitry.

[0039] In some examples, the logic circuitry package may respond to various types of requests (or commands) from a host (e.g. a print apparatus). A first type of request may comprise a request for data, for example identification and/or authentication information. A second type of request from a host may be a request to perform a physical action, such as performing at least one measurement. A third type of request may be a request for a data processing action. There may be additional types or requests.

[0040] In some examples, there may be more than one address associated with a particular logic circuitry package, which is used to address communications sent over a bus to identify the logic circuitry package which is the target of a communication (and therefore, in some examples, with a replaceable print apparatus component). In some examples, different requests are handled by different logic circuits of the package. In some examples, the different logic circuits may be associated with different addresses.

[0041] In at least some examples, a plurality of such logic circuitry packages (each of which may be associated with a different replaceable print apparatus component) may be connected to an I2C bus. In some examples, at least one address of the logic circuitry package may be an I2C compatible address (herein after, an I2C address), for example in accordance with an I2C protocol, to facilitate directing communications between master to slaves in accordance with the I2C protocol. In other examples, other forms of digital and/or analogue communication can be used.

[0042] FIG. 1 is an example of a printing system 100. The printing system 100 comprises a print apparatus 102 in communication with logic circuitry associated with a replaceable print apparatus component 104 via a communications link 106. Although for clarity, the replaceable print apparatus component 104 is shown as external to the print apparatus 102, in some examples, the replaceable print apparatus component 104 may be housed within the print apparatus. While a particular type of 2D print apparatus 102 is shown, a different type of 2D print apparatus or a 3D print apparatus may instead be provided.

[0043] The replaceable print apparatus component 104 may comprise, for example a print material container or cartridge (which, again, could be a build material container for 3D printing, a liquid or dry toner container for 2D printing, or a liquid print agent container for 2D or 3D printing), which may in some examples comprise a print head or other dispensing or transfer component. The replaceable print apparatus component 104 may for example contain a consumable resource of the print apparatus 102, or a component which is likely to have a lifespan which is less (in some examples, considerably less) than that of the print apparatus 102. Moreover, while a single replaceable print apparatus component 104 is shown in this example, in other examples, there may be a plurality of replaceable print apparatus components, for example comprising print agent containers of different colors, print heads (which may be integral to the containers), or the like. In other examples the print apparatus components 104 could comprise service components, for example to be replaced by service personnel, examples of which could include print heads, toner process cartridges or logic circuit package by itself to adhere to corresponding print apparatus component and communicate to a compatible print apparatus logic circuit.

[0044] In some examples, the communications link 106 may comprise an I2C capable or compatible bus (herein after, an I2C bus).

[0045] FIG. 2 shows an example of a replaceable print apparatus component 200, which may provide the replaceable print apparatus component 104 of FIG. 1. The replaceable print apparatus component 200 comprises a data interface 202 and a logic circuitry package 204. In use of the replaceable print apparatus component 200, the logic circuitry package 204 decodes data received via the data interface 202. The logic circuitry may perform other functions as set out below. The data interface 202 may comprise an I2C or other interface. In certain examples the data interface 202 may be part of the same package as the logic circuitry package 204.

[0046] In some examples, the logic circuitry package 204 may be further configured to encode data for transmission via the data interface 202. In some examples, there may be more than one data interface 202 provided.

[0047] In some examples, the logic circuitry package 204 may be arranged to act as a `slave` in I2C communications.

[0048] FIG. 3 shows an example of a print apparatus 300. The print apparatus 300 may provide the print apparatus 102 of FIG. 1. The print apparatus 300 may serve as a host for replaceable components. The print apparatus 300 comprises an interface 302 for communicating with a replaceable print apparatus component and a controller 304. The controller 304 comprises logic circuitry. In some examples, the interface 302 is an I2C interface.

[0049] In some examples, the controller 304 may be configured to act as a host, or a master, in I2C communications. The controller 304 may generate and send commands to at least one replaceable print apparatus component 200, and may receive and decode responses received therefrom. In other examples the controller 304 may communicate with the logic circuitry package 204 using any form of digital or analogue communication.

[0050] The print apparatus 102, 300 and replaceable print apparatus component 104, 200, and/or the logic circuitry thereof, may be manufactured and/or sold separately. In an example, a user may acquire a print apparatus 102, 300 and retain the apparatus 102, 300 for a number of years, whereas a plurality of replaceable print apparatus components 104, 200 may be purchased in those years, for example as print agent is used in creating a printed output. Therefore, there may be at least a degree of forwards and/or backwards compatibility between print apparatus 102, 300 and replaceable print apparatus components 104, 200. In many cases, this compatibility may be provided by the print apparatus 102, 300 as the replaceable print apparatus components 104, 200 may be relatively resource constrained in terms of their processing and/or memory capacity.

[0051] FIG. 4A shows an example of a logic circuitry package 400a, which may for example provide the logic circuitry package 204 described in relation to FIG. 2. The logic circuitry package 400a may be associated with, or in some examples affixed to and/or be incorporated at least partially within, a replaceable print apparatus component 200.

[0052] In some examples, the logic circuitry package 400a is addressable via a first address and comprises a first logic circuit 402a, wherein the first address is an I2C address for the first logic circuit 402a. In some examples, the first address may be configurable. In other examples, the first address is a fixed address, e.g. "hard-wired", intended to remain the same address during the lifetime of the first logic circuit 402a. The first address may be associated with the logic circuitry package 400a at and during the connection with a print apparatus logic circuit (e.g. a controller 304), outside of the time periods that are associated with a second address, as will be set out below. In example systems where a plurality of replaceable print apparatus components are to be connected to a single print apparatus, there may be a corresponding plurality of different first addresses. In certain examples, the first addresses can be considered standard I2C address for logic circuitry packages 400a or replaceable print components.

[0053] In some examples, the logic circuitry package 400a is also addressable via a second address. For example, the second address may be associated with different logic functions and/or, at least partially, with different data than the first address. In some examples, the second address may be associated with a different hardware logic circuit or a different virtual device than the first address.

[0054] In some examples, the second address may be configurable. The second address may be an initial and/or default second address at the start of a communication session via the second address and may be reconfigured to a different second address after the start of the session. In some examples, the second address may be used for the duration of the communication session, the logic circuitry package 400a may be configured to set the second address to a default or initial address at the end of the session, or at or before the beginning of a new session. Communications in such a communication session may be directed to the second address and between communication sessions may be directed to the first address, whereby the print apparatus logic circuit 304 may verify, for example, different identities, characteristics and/or status through these different communication sessions via different addresses. In examples where the end of a communication session via the second address is associated with a loss of power to at least part of the logic circuit as is further set out below, this loss of power may cause the second `temporary` address to be discarded (for example, the second address may be held in volatile memory, whereas the initial or default address may be held in persistent memory). Therefore a `new` or `temporary` second address may be set each time after the corresponding communications session is started (although in some cases the `new` or `temporary` second address may have been previously used in relation to the logic circuitry).

[0055] In other examples the logic circuit package 400a may not set itself back to the initial second address for starting each corresponding communication session. Rather, it may allow for configuring the second address at each corresponding communication session, without switching to the initial or default second address.

[0056] In other words, the second address may be configured to be an initial second address at the start of a time period during which the communication session is to take place. The logic circuitry package 400a may be configured to reconfigure its second address to a temporary address in response to a command sent to the initial second address and including that temporary address during that time period. The logic circuitry package 400a may then be effectively reset such that upon receiving a subsequent command indicative of the task and time period sent to the first address, the logic circuitry package 400a is configured to have the same initial second address.

[0057] In some examples, the initial and/or default second address of different logic circuitry packages 204, 400a, for example associated with different print material types (such as different colours or agents) and compatible with the same print apparatus logic circuit 304, may be the same. However, for each communication session with the second address, each logic circuitry package 400a may be temporarily associated with a different temporary address, which may be set as the second address for each communication session. In certain examples, a random temporary second address can be used each time, in some examples with the condition that each enabled second address on a common I2C bus at a particular instant is different from the other enabled addresses. In some examples a `random` second address may be a second address which is selected from a predetermined pool of possible second addresses, which may, in some examples, be stored on the print apparatus. The temporary address may be generated by the print apparatus logic circuit 304 for each connected logic circuitry package 400a and communicated through said command.

[0058] In some examples, the logic circuitry package 400a may comprise a memory to store the second address (in some examples in a volatile manner). In some examples, the memory may comprise a programmable address memory register for this purpose.

[0059] In some examples, the package 400a is configured such that, in response to a first command indicative of a first time period sent to the first address (and in some examples a task), the package 400a may respond in various ways. In some examples, the package 400a is configured such that it is accessible via at least one second address for the duration of the time period. Alternatively or additionally, in some examples, the package may perform a task, which may be the task specified in the first command. In other examples, the package may perform a different task.

[0060] The first command may, for example, be sent by a host such as a print apparatus in which the logic circuitry package 400a (or an associated replaceable print apparatus component) is installed. As set out in greater detail below, the task may comprise a monitoring task, for example, monitoring a timer (and in some examples, monitoring the time period). In other examples, the task may comprise a computational task, such as performing a mathematical challenge. In some examples, the task may comprise activating a second address and/or effectively deactivating the first address for communication purposes (or may comprise performance of actions which result in the activation or enabling of a second address and/or effectively deactivating or disabling of the first address). In some examples, activating or enabling a second address may comprise setting (e.g. writing, re-writing or changing), or triggering the setting of, a second address (for example, a temporary second address), for example by writing the second address in a portion of memory which is indicative of an address of the logic circuitry package 400a.

[0061] Where a task is specified, the task and/or time period may be specified explicitly in the first command, or may be inferred by the logic circuitry package 400a by reference to a lookup table or the like. In one example, the first command may for example comprise mode data and time data. For example, a first data field, which may be sent as part of a serial data package, may comprise a mode field. This may for example be around one or a few bits or bytes in size. A second data field, which may be sent as part of the serial data packet of the first data field in some examples, may comprise a `dwell time` data field. For example, this may be around two or a few bits or bytes in size and may specify a time period, for example in milliseconds.

[0062] In some examples, the package 400a is configured so as to be inaccessible via the second address (the default or temporary second address or any address other the first address) for a second time period preceding (in some examples, immediately preceding) the first time period and/or for a third time period following (in some examples, immediately following) the first time period. In some examples, the first logic circuit 402a is to ignore I2C traffic sent to the first address (or any address other than a currently active second address) for the duration of the time period. In other words, the package 400a may respond to commands directed to the first address and not to commands directed to the second address outside the first time period; and may respond to commands directed to the second address and not to commands directed to the first address during the first time period. The term `ignore` as used herein with respect to data sent on the bus may comprise any or any combination of not receiving (in some examples, not reading the data into a memory), not acting upon (for example, not following a command or instruction) and/or not responding (i.e. not providing an acknowledgement, and/or not responding with requested data). For example, `ignoring` I2C traffic sent to the first address may be defined as the logic circuitry package 400a not responding to communications directed to the first address (or any address other than a currently active second address as perceivable by the print apparatus logic circuit 304).

[0063] Causing the first logic circuit 402a to `ignore` (or otherwise not respond to) I2C traffic sent to the first address for the duration of the time period for which the second address is activated or in use allows the first and second addresses to be entirely independent of one another. For example, the first address may be I2C compliant whereas a second address may be of any format, including in some examples a non-I2C compliant format. In addition, if the first address is effectively disabled for the duration of the time period, consideration need not be made as to any response to a command which the package 400a may consider to be addressed to the first address. For example, the first address may be represented by a particular bit sequence and, if there is a possibility that the first address may be recognized when the package is not to be addressed using the first address, precautions may be taken such that this identifying bit sequence is avoided when the package is not to be addressed using the first address. The likelihood of this event could increase in the instance where communication is established via different temporary second addresses of respective different logic circuitry packages within a single time period over the same serial bus. If these situations are not managed correctly, indeterminate or unexpected behaviour may be seen. However, if the first address is effectively disabled during the time period, there need be no such consideration or precautions, and commands which could otherwise be inadvertently received and interpreted by the package 400a as having been received by the first address will not be received as the first address is effectively inactivated. The reverse may also be true (i.e. commands which may be inadvertently taken to be addressed to any second address will not be received by the package 400a outside the time period if that address is effectively disabled outside the time period).

[0064] In some examples, the first and the second addresses may be of different lengths. For example, the first address may be a 10-bit address and the second address may be a 7-bit address. In other examples, the first and second address may be of the same length, for example both comprising a 7-bit or 10-bit address. In certain examples the first and the default second address are hardwired, while the second address allows for reconfiguration to the temporary address, as explained above. In other examples the first and second address may be programmed.

[0065] In some examples, the first logic circuit 402a is to perform a task, which may be the task specified in the command received, for the duration of the time period. However, in other examples, for example to allow for increased compatibility, the first logic circuit 402a may not perform the specified task (for example, if it is unable to do so, or it is unnecessary to do so to keep the first logic circuit 402a `busy`, as described below).

[0066] In some examples, the first logic circuit 402a may in effect not respond to (i.e., ignore) requests sent to the first address as a result of performing a task, which may be a task specified in the first command. In some examples, the task may at least substantially consume the processing capacity of the first logic circuit 402a. For example, the task may comprise monitoring a timer in such a way that the processing capacity of the first logic circuit 402a is substantially dedicated to that task. In other examples, the processing capacity may be substantially dedicated to performing a computational task, such as an arithmetical task. In a simple example, the first logic circuit 402a may be tasked with calculating a value such as pi. This task may be, according to present understanding, unlimited in the sense that a processor could continue calculating pi to further decimal places for an infinite amount of time. Therefore, the performance of this task to completion exceeds any likely time period specified in the first command. For example, such time periods may be, in some examples, in the order of seconds or tens of seconds. If the first logic circuit is dedicated to the task of calculating pi/monitoring a timer until the time period has passed, it may not also be monitoring traffic sent thereto via a communications bus or the like. Therefore, even if the communications were sent to the first address, these would be ignored. It may be noted that certain I2C slave devices will generally ignore a bus while performing any kind of processing. However, the processing specified herein is associated with the time period. It is noted that, given that the logic circuit package is not responsive to communications to its first address for the time for which the second address is activated, in some examples, the (temporary) second address could be the same as the first address whereby the desired function corresponding to that second address may still be achieved. However, as explained before, in other examples, the second address is different to the first address.

[0067] It will be appreciated that the task of calculating pi is merely one example of a task which may generally exceed a time period specified in a first command. Other examples of computational tasks having a completion time which is likely to exceed the time period may be selected, for example based on the length of the time period under consideration. For example, if the time period is to last for no longer than 3 seconds, a processing task which will exceed 3 seconds in duration may be performed (and, in some examples, instructed in the first command). Moreover, in other examples, as noted above, the task may comprise monitoring a time period.

[0068] In other examples, the logic circuitry packages 400a may be configured to, in response to such a first command including the task and time period, not respond to communications directed to its first address, not necessarily by performing a processing task but effectively by being programmed not to respond.

[0069] In some examples, the package 400a is configured to provide a first set of responses, or to operate in a first mode, in response to instructions sent to the first address and to provide a second set of responses, or to operate in a second mode, in response to instructions sent to the second address. In other words, the address may trigger different functions provided by the package 400a. In some examples, at least one response of the first set of responses is output in response to commands sent to the first address and not in response to commands sent to the second address and at least one response of the second set of responses is output in response to commands sent to the second address and not in response to commands sent to the first address. In some examples, the first set of responses may be cryptographically authenticated (i.e. accompanied by a message authentication code generated using a base key, or otherwise cryptographically `signed`, and/or encrypted, see for example US patent publication No. 9619663) and the second set of responses is not cryptographically authenticated. In some examples, the second set of responses may relate to sensor data and the first set of responses may not relate to sensor data. In some examples, messages may be accompanied by a session key identifier. For example an identity of a logic circuit of the package 400a could be communicated in the first and the second set of responses, whereby it is cryptographically authenticated in the first set but not in the second set. This may allow the package 400a to provide two distinct functions. Data may be output from an output data buffer of the package 400a.

[0070] In some examples, the package 400a may be configured to participate in a first validation process using I2C communications sent to the first address, and to participate in a second validation process using communications sent to the second address. As noted above, the second address may be a reconfigurable address, and in some examples may be reconfigured after the first validation process has been carried out. In some examples, the first validation process may comprise an exchange of encrypted or authenticable messages, wherein the messages are encrypted and/or signed based on a base key stored in the package, which may be a secret key (or based on a secret base key) that corresponds to a secret key stored or held in the print apparatus. In some examples, the second validation process may comprise an integrity check, in which the package 400a may return requested data values such that a host apparatus can verify that these data values meet predetermined criteria.

[0071] In examples set out above, the addresses used to communicate with the circuitry package 400a have been described. Further communication may be directed to memory addresses to be used to request information associated with these memory addresses. The memory addresses may have a different configuration than the first and second address of the logic circuitry package 400a. For example, a host apparatus may request that a particular memory register is read out onto the bus by including the memory address in a read command. In other words, a host apparatus may have a knowledge and/or control of the arrangement of a memory. For example, there may be a plurality of memory registers and corresponding memory addresses associated with the second address. A particular register may be associated with a value, which may be static or reconfigurable. The host apparatus may request that the register be read out onto the bus by identifying that register using the memory address. In some examples, the registers may comprise any or any combination of address register(s), parameter register(s) (for example to store gain and/or offset parameters), sensor identification register(s) (which may store an indication of a type of sensor), sensor reading register(s) (which may store values read or determined using a sensor), sensor number register(s) (which may store a number or count of sensors), version identity register(s), memory register(s) to store a count of clock cycles, memory register(s) to store a value indicative of a read/write history of the logic circuitry, or other registers.

[0072] In some examples, the package 400a may be configured to respond to a data request (for example, a sensor data request) received from the print apparatus by returning a first response, then, following receipt of a calibration (e.g. conversion) parameter (and, in some examples a subsequent data request), return a second response which is different from the first response. In some examples, this functionality may be provided from a second logic circuit. In some examples, the received calibration parameter may be used to adjust the second response, or may otherwise be used in determining a second response which is different to the first response. In some examples the print apparatus logic circuit may send a new calibration parameter if the first response does not meet predetermined criteria (for example, is outside of a predetermined range), and the second response may need to be adjusted on this basis, by the package 400a. This may for example comprise part of a calibration routine, in which response data may need to be set to be within predetermined limits, for example so as to avoid `range clipping`, in which a data reading is capped at a high or a low end of a range when a parameter reaches a threshold, even though the parameter being measured may continue to change beyond the threshold. Such a routine may continue with responses being adjusted until a response and/or a set of responses which meets predetermined criteria is seen. Examples of calibration are discussed in greater detail below.

[0073] In some examples, the package 400a may be configured to receive a data request, determine whether the request is for data indicative of a print material level sensor or for data indicative of a pressurisation (e.g. a pressure change) event, and to respond with a data response. In some examples, the data request may comprise a `read` command in which the acquired data is read from a memory of the package 400a. In some examples, the data request may comprise at least two commands. For example, a first command may comprise a `write` command, which triggers the acquisition of sensor data by the package 400a, and the acquired data is stored in a memory of the package 400a. In an example, the first command may provide information allowing a sensor type/sensor cell to be identified, and may trigger (in some examples on receipt of a specific "conversion" command, but in other examples in response to the first command) a sequence of events to carry out sensing, execute an ND conversion to store the conversion value into a memory location, which may be predetermined (for example, comprising a sensor data register). The sensing may be carried out using parameters (e.g. electrical test parameters, heating parameters, timing of measurements, etc.) which may also be stored in a memory (in some examples, in separate memory registers), and/or may be provided with the command. The ND conversion may be carried out using parameters which may also be stored in a memory (in some examples, in one or more memory register(s)). As discussed below in greater detail, the conversion parameters and/or the sensing parameters may be configured in a calibration operation. A second command may comprise a `read` command in which the acquired data is read from a memory of the package 400a.

[0074] Characteristics of the data reading may be different for different types of sensor data requested. For example, the data response may comprise one or more values in a first range when the request is for data indicative of a print material level and may comprise one or more values in a second range when the request is for data indicative of a pressurisation event. In some examples, the values may comprise count values. In some examples, to obtain the response values in the respective first and second range, first operational parameters for the corresponding sensor type may have been (over) written to respective memory fields.

[0075] In some examples, a data response may comprise, in total, a first number of data readings when the request is for data of a print material level sensor and a second number of data readings when the request is for data indicative of a pressurisation event. Such a response may be provided over a series of data exchanges with processing circuitry of the print apparatus in which the package 400a is installed. For example, each data reading of the data response may be provided in response to a read request of a plurality of read requests received from logic circuitry of a print apparatus, and each read request may follow a write request from logic circuitry of a print apparatus, wherein receipt of the read request may trigger the acquisition of a data reading.

[0076] In some examples, the number of data readings returned for a particular sensor is less than the number of sensor cells or sensing elements of that sensor. This may allow a print apparatus in which the package 400a is installed to query an appropriate number of sensor cells without excessive bandwidth. For example, it may be that there are on the order of 100 or 150 sensor cells which form part of an ink level sensor in an ink cartridge. The print material level sensor in such an example may return 100 or 150 data readings (which may for example be requested one after another as outlined above). However, there may be on the order of 30 or 40 sensor cells which form part of a pressure sensor, for example comprising strain sensors or the like. Thus the pressure change sensor in such an example may return 30 or 40 data readings (which may for example be requested one after another). In some examples, a subset of the available sensor element or cells may be queried. For example, there may be around 100 or more sensor elements/cells of a particular sensor type, and only around 30 or the set may be queried and provide readings, for example to reduce sampling times. For example, it may be that, over the duration of a pressurisation event (or any other temporary or transitory state during which sensor readings are to be acquired), there may be time to query some, but not all, of the sensors/sensor cells.

[0077] In some examples, there may be additional data requests, such as any or any combination of print material temperature, an ambient temperature, a `crack detection` sensor request, and the like.

[0078] FIG. 4B shows another example of a logic circuitry package 400b. In this example, the package 400b comprises a first logic circuit 402b, in this example comprising a first timer 404a, and a second logic circuit 406a, in this example comprising a second timer 404b. While in this example, each of the first and second logic circuits 402b, 406a comprises its own timer 404, in other examples, they may share a timer, or reference at least one external timer. In a further example, the first logic circuit 402b and the second logic circuit 406a are linked by a dedicated signal path 408.

[0079] In one example, the logic circuitry package 400b may receive a first command comprising two data fields. A first data field is a one byte data field setting a requested mode of operation. For example, there may be a plurality of predefined modes, such as a first mode, in which the logic circuitry package 400b is to ignore data traffic sent to the first address (for example, while performing a task), and a second mode in which the logic circuitry package 400b is to ignore data traffic sent to the first address and to transmit an enable signal to the second logic circuit 406a, as is further set out below.

[0080] The first command may comprise additional fields, such as an address field and/or a request for acknowledgement.

[0081] The logic circuitry package 400b is configured to process the first command. If the first command cannot be complied with (for example, a command parameter is of an invalid length or value, or it is not possible to enable the second logic circuit 406a), the logic circuitry package 400b may generate an error code and output this to a communication link to be returned to host logic circuitry, for example in the print apparatus.

[0082] If however, the first command is validly received and can be complied with, the logic circuitry package 400b measures the duration of the time period included in the first command, for example utilising the timer 404a. In some examples, the timer 404a may comprise a digital "clock tree". In other examples, the timer 404a may comprise an RC circuit, a ring oscillator, or some other form of oscillator or timer. In this example, in response to receiving a valid first command, the first logic circuit 402b enables the second logic circuit 406a and effectively disables the first address, for example by tasking the first logic circuit 402b with a processing task as described above. In some examples, enabling the second logic circuit 406a comprises sending, by the first logic circuit 402b, an activation signal to the second logic circuit 406a. In other words, in this example, the logic circuitry package 400b is configured such that the second logic circuit 406a is selectively enabled by the first logic circuit 402b.

[0083] In this example, the second logic circuit 406a is enabled by the first logic circuit 402b sending a signal via a signal path 408, which may or may not be a dedicated signal path 408, that is, dedicated to enable the second logic circuit 406a. In one example, the first logic circuit 402b may have a dedicated contact pin or pad connected to the signal path 408, which links the first logic circuit 402b and the second logic circuit 406a. In a particular example, the dedicated contact pin or pad may be a General Purpose Input/Output (a GPIO) pin of the first logic circuit 402b. The contact pin/pad may serve as an enablement contact of the second logic circuit 406a.

[0084] The voltage of the signal path 408 may be driven to be high in order to enable the second logic circuit 406a. In some examples, such a signal may be present for substantially the duration of the first time period, for example, starting following receipt of the first command and may cease at the end of the first time period. As noted above, the enablement may be triggered by a data field in the command. In other examples, the second logic circuit may be selectively enabled/disabled, for example for the duration of the time period, in another way.

[0085] In some examples, such a contact pad or pin is provided in a manner so as to be generally inaccessible from the exterior of a replaceable print apparatus component. For example, it may be relatively distant from an interface and/or may be fully enclosed by a housing. This may be useful in ensuring that it is only triggered via the first logic circuit 402b.

[0086] In this example, the second logic circuit 406a is addressable via at least one second address. In some examples, when the second logic circuit 406a is activated or enabled, it may have an initial, or default, second address, which may be an I2C address or have some other address format. The second logic circuit 406a may receive instructions from a master or host logic circuitry to change the initial address to a temporary second address. In some examples, the temporary second address may be an address which is selected by the master or host logic circuitry. This may allow the second logic circuit 406a to be provided in one of a plurality of packages 400 on the same I2C bus which, at least initially, share the same initial second address. This shared, default, address may later be set to a specific temporary address by the print apparatus logic circuit, thereby allowing the plurality of packages to have different second addresses during their temporary use, facilitating communications to each individual package. At the same time, providing the same initial second address may have manufacturing or testing advantages.

[0087] In some examples, the second logic circuit 406a may comprise a memory. The memory may comprise a programmable address register to store the initial and/or temporary second address (in some examples in a volatile manner). In some examples, the second address may be set following, and/or by executing, an I2C write command. In some examples, the second address may be settable when the enablement signal is present or high, but not when it is absent or low. The second address may be set to a default address when an enablement signal is removed and/or on restoration of enablement of the second logic circuit 406a. For example, each time the enable signal over the signal path 408 is low, the second logic circuit 406a, or the relevant part(s) thereof, may be reset. The default address may be set when the second logic circuit 406a, or the relevant part(s) thereof, is switched out-of-reset. In some examples the default address is a 7-bit or 10-bit identification value. In some examples, the default address and the temporary second address may be written in turn to a single, common, address register.

[0088] In some examples, the address of the second logic circuit 406a may be rewritten at any time at which it is enabled. In some examples, when connected to the bus, the second logic circuit 406a may be in a low current state except when it is in an enabled state.

[0089] In some examples, the second logic circuit 406a may comprise a power-on reset (POR) device. This may comprise an electronic device which detects the power applied to the second logic circuit 406a and generates a reset impulse that goes to the entire second logic circuit 406a placing it into a known state. Such a POR device may be of particular utility in testing the package 400b prior to installation.

[0090] In some examples, a plurality of further logic circuits may be `chained` together, with further pins (which may be GPIO pins) or the like. In some examples, once the second address has been written (i.e. the logic circuit has an address which is different to its default address), it may activate an `out` pin or pad, and an `in` pin or pad of the next logic circuit in the chain (if one exists) thereby be driven high and the logic circuit may be enabled. Such a further logic circuit(s) may function as described in relation to the second logic circuitry 406a. Such further logic circuits may have the same default address as the second logic circuit 406a in some examples. There is no absolute limit as to how many logic circuits can be serially chained and accessed in this way, however there may be a practical limitation in a given implementation based on the series resistance on the bus lines, the number of Slave IDs, and the like.

[0091] In one example, the first logic circuit 402b is configured to generate an enablement signal that may be an active low asynchronous reset signal. In some examples, when this signal is removed (or is driven to a logic 0), the second logic circuit 406a may immediately cease operations. For example, data transfers may immediately cease, and a default state (which may be a sleep state and/or a low current state) may be assumed by the second logic circuit 406a. In some examples, memories such as registers may revert to an initialised state (for example, a default address may comprise an initialised state of an address register).

[0092] In an example in which an I2C bus is used for communications with the package 400b, the first logic circuit 402b and the second logic circuit 406a may be connected to the same I2C bus. As noted above, an additional connection, for example provided between GPIO pins of the first logic circuit 402b and the second logic circuit 406a may be selectively enabled following receipt of a dedicated command. For example, the first logic circuit 402b may drive a dedicated GPIO pin to be high for a time period specified in a command (whereas by default the pin may be in a low state). For the duration of this time period, the first logic circuit 402b may not acknowledge (`NAK`) any attempts to communicate using the first address. At the end of the specified time period, the dedicated contact pin may be returned to the `low` state, and the first logic circuit 402b may be receptive to communications on the I2C bus sent to the first address once again. However, while the contact pin is driven to be high, the second logic circuit 406a may be enabled, and receptive to communications on the I2C bus.

[0093] It may be noted that, by sharing I2C contacts between the first logic circuit 402b and the second logic circuit 406a, electrical interconnect cost is small. Additionally, if the second logic circuit is selectively powered only for the duration of the time period, it may be less susceptible to electrochemical wear. In addition, this may allow multiple packages comprising respective first logic circuits 402b and second logic circuits 406a to be provided on the same serial I2C bus, where the second logic circuits 406a may (at least initially) share an address, which may in turn reduce manufacturing and deployment complexities.

[0094] In some examples, as outlined above, the logic circuitry package 400b comprises a first operational mode in which it responds to communication sent to the first address and not any second address and a second operational mode in which it responds to communications sent to a second address (e.g. the second address currently in use, and in some examples, currently stored in a dedicated register of the second logic circuit 406a) and not the first address.

[0095] In the example illustrated in FIG. 4b, the second logic circuit 406a comprises a first array 410 of cells and at least one second cell 412 or second array of second cells. The first cells 416 a-f, 414 a-f and the at least one second cell 412 can comprise resistors. The first cells 416 a-f, 414 a-f and the at least one second cell 412 can comprise sensors. In one example the first cell array 410 comprises a print material level sensor and the at least one second cell 412 comprises another sensor and/or other sensor array.

[0096] In this example, the first cell array 410 comprises a sensor configured to detect a print material level of a print supply, which may in some examples be a solid but in examples described herein is a liquid, for example, an ink or other liquid print agent. The first cell array 410 may comprise a series of temperature sensors (e.g. cells 414a-f) and a series of heating elements (e.g. cells 416a-f), for example similar in structure and function as compared to the level sensor arrays described in WO2017/074342, WO2017/184147, and WO2018/022038. In this example, the resistance of a resistor cell 414 is linked to its temperature. The heater cells 416 may be used to heat the sensor cells 414 directly or indirectly using a medium. The subsequent behaviour of the sensor cells 414 depends on the medium in which they are submerged, for example whether they are in liquid (or in some examples, encased in a solid medium) or in air. Those which are submerged in liquid/encased may generally heat more slowly and lose heat quicker than those which are in air because the liquid or solid may conduct heat away from the resistor cells 414 better than air. Therefore, a liquid level may be determined based on which of the resistor cells 414 are exposed to the air, and this may be determined based on a reading of their resistance following (at least the start of) a heat pulse provided by the associated heater cell 416.

[0097] In some examples each sensor cell 414 and heater cell 416 are stacked with one being directly on top of the other. The heat generated by each heater cell 416 may be substantially spatially contained within the heater element layout perimeter, so that heat delivery is substantially confined to the sensor cell 414 stacked directly above the heater cell 416. In some examples, each sensor cell 414 may be arranged between an associated heater cell 416 and the fluid/air interface.

[0098] In this example, the second cell array 412 comprises a plurality of different cells that may have a different function such as different sensing function(s). For example, the first and second cell array 410, 412 may include different resistor types. Different cells arrays 410, 412 for different functions may be provided in the second logic circuit 406a.

[0099] In one example, the second cell(s) 412 may comprise at least one sensor to detect a change in pressure and/or a pneumatic action applied by the print apparatus to a print component to which the package 400b is to be mounted. For example such at least one sensor to detect a change in pressure and/or pneumatic action may comprise strain sensing cell(s). In some examples, the strain sensing cells may comprise piezo-resistive cells. In one example, the strain sensing cells may be arranged across a surface of a chamber for containing print materials. For example, an ink cartridge may be pressurized in order to dispense ink in a predetermined manner. In order to test that such pressurization is correctly operational, a test may be carried out using strain gauges arranged across the surface of the chamber. This may comprise a `hyperinflation` event, in which the cartridge is subjected to a pressure which is greater than that used in normal operation when dispensing ink and the like. In the event of a pressurization, it may be expected that the chamber will `bulge out`. Thus strain sensors arranged across the surface may be expected to show a change in strain. Some examples of strain sensors are discussed in greater detail below.

[0100] The sensors 410, 412 may be read, and/or parameters thereof (and/or parameters of conversion apparatus associated therewith) may be calibrated. In some examples, calibration and/or reading of the sensors 410, 412 takes place when the second logic circuit 406a is enabled and/or following the setting of a temporary second address.

[0101] FIG. 4C shows an example of how a first logic circuit 402c and a second logic circuit 406b of a logic circuitry package 400c, which may have any of the attributes of the circuits/packages described above, may connect to an I2C bus and to each other. As is shown in the Figure, each of the circuits 402c, 406b has four pads (or pins) 418a-d connecting to the Power, Ground, Clock and Data lines of an I2C bus. In another example, four common connection pads are used to connect both logic circuits 402c, 406b to four corresponding connection pads of the print apparatus controller interface. It is noted that in some examples, instead of four connection pads, there may be fewer connection pads. For example, power may be harvested from the clock pad; an internal clock may be provided; or the package could be grounded through another ground circuit; so that, one or more of the pads may be omitted or made redundant. Hence, in different examples, the package could use only two or three interface pads and/or could include "dummy" pads.

[0102] Each of the circuits 402c, 406b has a contact pin 420, which are connected by a common signal line 422. The contact pin 420 of the second circuit serves as an enablement contact thereof.

[0103] In this example, each of the first logic circuit 402c and the second logic circuit 406b comprises a memory 423a, 423b.

[0104] The memory 423a of the first logic circuit 402c stores information comprising cryptographic values (for example, a cryptographic key and/or a seed value from which a key may be derived) and identification data and/or status data of the associated replaceable print apparatus component. In some examples the memory 423a may store data representing characteristics of the print material, for example any, any part, or any combination of its type, color, color map, recipe, batch number, age, et cetera.

[0105] The memory 423b of the second logic circuit 406b comprises a programmable address register to contain an initial address of the second logic circuit 406b when the second logic circuit 406b is first enabled and to subsequently contain a further (temporary) second address (in some examples in a volatile manner). The further, e.g. temporary, second address may be programmed into the second address register after the second logic circuit 406b is enabled, and may be effectively erased or replaced at the end of an enablement period. In some examples, the memory 423b may further comprise programmable registers to store any, or any combination of a read/write history data, cell (e.g. resistor or sensor) count data, Analogue to Digital converter data (ADC and/or DAC), and a clock count, in a volatile or non-volatile manner. Use of such data is described in greater detail below. Certain characteristics, such as cell count or ADC or DAC characteristics, could be derivable from the second logic circuit instead of being stored as separate data on the memory. Such registers may be addressable using memory addresses.

[0106] In one example, the memory 423b of the second logic circuit 406b stores any or any combination of an address, for example the second I2C address; an identification in the form of a revision ID; and the index number of the last cell (which may be the number of cells less one, as indices may start from 0), for example for each of different cell arrays or for multiple different cell arrays if they have the same number of cells.

[0107] In use of the second logic circuit 406b, in some operational states, the memory 423b of the second logic circuit 406 may store any or any combination of timer control data, which may enable a timer of the second circuit, and/or enable frequency dithering therein in the case of some timers such as ring oscillators; a dither control data value (to indicate a dither direction and/or value); and a timer sample test trigger value (to trigger a test of the timer by sampling the timer relative to clock cycles measurable by the second logic circuit 406b). In some examples, the memory 423b of the second logic circuit 406b may be configured to store calibration parameters associated with sensors, for example control parameters, calibration parameters, heating time or strength (power) parameters, gain parameters or the like. These parameters may be set to a default value at the beginning of a time period (for example a time period during which the second logic circuit 406b is enabled) and/or may be written and/or overwritten during the time period.

[0108] While the memories 423a, 423b are shown as separate memories here, they could be combined as a shared memory resource, or divided in some other way. The memories 423a, 423b may comprise a single or multiple memory devices, and may comprise any or any combination of volatile memory e.g. DRAM, SRAM, registers, etc. and non-volatile memory e.g. ROM, EEPROM, Flash, EPROM, memristor, etc.

[0109] While one package 400c is shown in FIG. 4C, there may be a plurality of packages with a similar or a different configuration attached to the bus.

[0110] FIG. 4D shows an example of processing circuitry 424 which is for use with a print material container. For example, the processing circuitry 424 may be affixed or integral thereto. As already mentioned, the processing circuitry 424 may comprise any of the features of, or be the same as, any other logic circuitry package of this disclosure.

[0111] In this example, the processing circuitry 424 comprises a memory 426 and a first logic circuit 402d which enables a read operation from memory 426. The processing circuitry 424 is accessible via an interface bus of a print apparatus in which the print material container is installed and is associated with a first address and at least one second address. The bus may be an I2C bus. The first address may be an I2C address of the first logic circuit 402d. The first logic circuit 402d may have any of the attributes of the other examples circuits/packages described in this disclosure.

[0112] The first logic circuit 402d is adapted to participate in authentication of the print materials container by a print apparatus in which the container is installed. For example, this may comprise a cryptographic process such as any kind of cryptographically authenticated communication or message exchange, for example based on an encryption key stored in the memory 426, and which can be used in conjunction with information stored in the printer. In some examples, a printer may store a version of a key which is compatible with a number of different print material containers to provide the basis of a `shared secret`. In some examples, authentication of a print material container may be carried out based on such a shared secret. In some examples, the first logic circuit 402d may participate in a message to derive a session key with the print apparatus and messages may be signed using a message authentication code based on such a session key. Examples of logic circuits configured to cryptographically authenticate messages in accordance with this paragraph are described in the earlier mentioned US patent publication No. 9619663.

[0113] In some examples, the memory 426 may store data comprising: identification data and read/write history data. In some examples, the memory 426 further comprises cell count data (e.g. sensor count data) and clock count data. Clock count data may indicate a clock speed of a first and/or second timer 404a, 404b (i.e. a timer associated with the first logic circuit or the second logic circuit). In some examples, at least a portion of the memory 426 is associated with functions of a second logic circuit, such as a second logic circuit 406a as described in relation to FIG. 4B above. In some examples, at least a portion of the data stored on the memory 426 is to be communicated in response to commands received via the second address. In some examples, the memory 426 comprises a programmable address register or memory field to store a second address of the processing circuitry (in some examples in a volatile manner). The first logic circuit 402d may enable read operation from the memory 426 and/or may perform processing tasks.