Memory Device

OGIWARA; Ryu ; et al.

U.S. patent application number 16/908880 was filed with the patent office on 2020-12-24 for memory device. This patent application is currently assigned to KIOXIA CORPORATION. The applicant listed for this patent is KIOXIA CORPORATION. Invention is credited to Takahiko IIZUKA, Ryu OGIWARA, Daisaburo TAKASHIMA.

| Application Number | 20200403035 16/908880 |

| Document ID | / |

| Family ID | 1000004931480 |

| Filed Date | 2020-12-24 |

View All Diagrams

| United States Patent Application | 20200403035 |

| Kind Code | A1 |

| OGIWARA; Ryu ; et al. | December 24, 2020 |

MEMORY DEVICE

Abstract

According to one embodiment, a memory device includes a memory cell and a first select transistor. The memory cell includes: a variable resistance memory region; a first semiconductor layer being in contact with the variable resistance memory region; a first insulating layer being in contact with the first semiconductor layer; and a first voltage application electrode being in contact with the first insulating layer. The first select transistor includes: a second semiconductor layer; a second insulating layer being in contact with the second semiconductor layer; and a second voltage application electrode extending in the second direction and being in contact with the second insulating layer.

| Inventors: | OGIWARA; Ryu; (Yokohama Kanagawa, JP) ; TAKASHIMA; Daisaburo; (Yokohama Kanagawa, JP) ; IIZUKA; Takahiko; (Yokohama Kanagawa, JP) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Assignee: | KIOXIA CORPORATION Tokyo JP |

||||||||||

| Family ID: | 1000004931480 | ||||||||||

| Appl. No.: | 16/908880 | ||||||||||

| Filed: | June 23, 2020 |

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 27/2436 20130101; H01L 45/144 20130101; H01L 45/1253 20130101; H01L 45/142 20130101; H01L 45/1206 20130101; H01L 45/143 20130101; H01L 45/146 20130101; H01L 45/1233 20130101 |

| International Class: | H01L 27/24 20060101 H01L027/24; H01L 45/00 20060101 H01L045/00 |

Foreign Application Data

| Date | Code | Application Number |

|---|---|---|

| Jun 24, 2019 | JP | 2019-116756 |

Claims

1. A memory device, comprising: a plurality of memory cells each including: a variable resistance memory region extending in a first direction that is orthogonal to a semiconductor substrate; a first semiconductor layer extending in the first direction and being in contact with the variable resistance memory region; a first insulating layer extending in the first direction and being in contact with the first semiconductor layer; and a first voltage application electrode extending in a second direction that is orthogonal to the first direction and being in contact with the first insulating layer; a first select transistor including: a second semiconductor layer extending in the first direction; a second insulating layer extending in the first direction and being in contact with the second semiconductor layer; and a second voltage application electrode extending in the second direction and being in contact with the second insulating layer; and a memory cell string including the first select transistor, the memory cells, and a third voltage application electrode, the memory cells being coupled in series in the first direction, one end of the first select transistor being coupled to one end of one of the memory cells that is provided at a first end portion, the third voltage application electrode being coupled to one end of one of the memory cells that is provided at a second end portion.

2. The memory device according to claim 1, wherein the third voltage application electrode is commonly coupled to the memory cell strings that are adjacent to each other in a third direction that is orthogonal to the first and second directions.

3. The memory device according to claim 1, wherein the variable resistance memory region is a phase-change element, and contains at least one of: GeTe and Sb.sub.2Te.sub.3; GeTe and BiSbTe; or Ge, Sb, and Te or a chalcogenide material.

4. The memory device according to claim 1, wherein the variable resistance memory region contains at least one of TiO.sub.x, WO.sub.x, HfO.sub.x, or TaO.sub.x.

5. The memory device according to claim 1, further comprising: a plurality of fifth voltage application electrodes each coupled to another end of the first select transistor, and extending in a third direction that is orthogonal to the first and second directions; and a sequencer configured to selectively perform a read operation or a write operation by applying a voltage between at least one of the fifth voltage application electrodes and the third voltage application electrode.

6. The memory device according to claim 1, wherein silicon nitride is provided inside the variable resistance memory region.

7. The memory device according to claim 1, wherein an air layer is provided inside the variable resistance memory region.

8. The memory device according to claim 1, wherein a core oxide film layer is provided inside the variable resistance memory region.

9. A memory device comprising: a plurality of memory cells each including: a variable resistance memory region extending in a first direction that is orthogonal to a semiconductor substrate; a first semiconductor layer extending in the first direction and being in contact with the variable resistance memory region; a first insulating layer extending in the first direction and being in contact with the first semiconductor layer; and a first voltage application electrode extending in a second direction that is orthogonal to the first direction and being in contact with the first insulating layer; a first select transistor including: a second semiconductor layer extending in the first direction; a second insulating layer extending in the first direction and being in contact with the second semiconductor layer; and a second voltage application electrode extending in the second direction and being in contact with the second insulating layer; a second select transistor including: a third semiconductor layer extending in the first direction; a third insulating layer extending in the first direction and being in contact with the third semiconductor layer; and a fourth voltage application electrode extending in the second direction and being in contact with the third insulating layer; and a memory cell string including the first and second select transistors, the memory cells, and a third voltage application electrode, the memory cells being coupled in series in the first direction, one end of the first select transistor being coupled to one end of one of the memory cells that is provided at a first end portion, one end of the second select transistor being coupled to one end of one of the memory cells that is provided at a second end portion, the third voltage application electrode being coupled to another end of the second select transistor.

10. The memory device according to claim 9, wherein the third voltage application electrode is commonly coupled to the memory cell strings which are adjacent to each other in a third direction that is orthogonal to the first and second directions.

11. The memory device according to claim 9, wherein the variable resistance memory region is a phase-change element, and contains at least one of: GeTe and Sb.sub.2Te.sub.3; GeTe and BiSbTe; or Ge, Sb, and Te or a chalcogenide material.

12. The memory device according to claim 9, wherein the variable resistance memory region contains at least one of TiO.sub.x, WO.sub.x, HfO.sub.x, or TaO.sub.x.

13. The memory device according to claim 9, further comprising: a plurality of fifth voltage application electrodes each coupled to another end of the first select transistor, and extending in a third direction that is orthogonal to the first and second directions; and a sequencer configured to selectively perform a read operation or a write operation by applying a voltage between at least one of the fifth voltage application electrodes and the third voltage application electrode.

14. The memory device according to claim 9, wherein silicon nitride is provided inside the variable resistance memory region.

15. The memory device according to claim 9, wherein an air layer is provided inside the variable resistance memory region.

16. A memory device comprising: a plurality of memory cell each including: a variable resistance memory region extending in a first direction that is orthogonal to a semiconductor substrate and being in a columnar or cylindrical shape; a first semiconductor layer extending in the first direction and covering an outer periphery of the variable resistance memory region; a first insulating layer extending in the first direction and covering an outer periphery of the first semiconductor layer; and a first voltage application electrode extending in a second direction that is orthogonal to the first direction and covering a part of an outer periphery of the first insulating layer; a first select transistor including: a second semiconductor layer extending in the first direction and being in a columnar or cylindrical shape; a second insulating layer extending in the first direction and covering an outer periphery of the second semiconductor layer; and a second voltage application electrode extending in the second direction and covering an outer periphery of the second insulating layer; and a memory cell string including the first select transistor, the memory cells, and a third voltage application electrode, the memory cells being coupled in series in the first direction, one end of the first select transistor being coupled to one end of one of the memory cells that is provided at a first end portion, the third voltage application electrode being coupled to one end of one of the memory cells that is provided at a second end portion.

17. The memory device according to claim 16, further comprising: the second select transistor including: a third semiconductor layer extending in the first direction and being in a columnar or cylindrical shape; a third insulating layer extending in the first direction and covering an outer periphery of the third semiconductor layer; and a fourth voltage application electrode extending in the second direction and covering an outer periphery of the third insulating layer, wherein the third voltage application electrode is coupled to the one end of the memory cell that is provided at the second end portion via the second select transistor.

18. The memory device according to claim 16, further comprising: a plurality of fifth voltage application electrodes each coupled to another end of the first select transistor, and extending in a third direction that is orthogonal to the first and second directions; and a sequencer configured to selectively perform a read operation or a write operation by applying a voltage between at least one of the fifth voltage application electrodes and the third voltage application electrode.

19. A memory device comprising: a memory pillar including: first voltage application electrodes and first insulating layers alternately stacked in a first direction that is orthogonal to a semiconductor substrate; a cylindrical first hole that penetrates the first voltage application electrodes and the first insulating layers in the first direction; a cylindrical second insulating layer covering an inner wall of the first hole and extending in the first direction; a cylindrical first semiconductor layer covering an inner wall of the second insulating layer and extending in the first direction; and a cylindrical or columnar-shaped variable resistance memory region covering an inner wall of the first semiconductor layer and extending in the first direction; a first select transistor including: a cylindrical second hole that penetrates a second voltage application electrode and communicates with the first hole, the second voltage application electrode being provided on the first voltage application electrodes and the first insulating layers in the first direction; a cylindrical third insulating layer covering an inner wall of the second hole and extending in the first direction; and a cylindrical third semiconductor layer covering an inner wall of the third insulating layer and extending in the first direction; and a memory cell string including the first select transistor, the memory pillar, and a third voltage application electrode, one end of the first select transistor being coupled to a first end of the memory pillar, the third voltage application electrode being coupled to a second end of the memory pillar.

20. The memory device according to claim 19, further comprising: a fifth voltage application electrode coupled to another end of the first select transistor, and extending in a third direction that is orthogonal to the first direction and a second direction; and a sequencer configured to selectively perform a read operation or a write operation by applying a voltage between at least one of the fifth voltage application electrodes and the third voltage application electrode.

Description

CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application is based upon and claims the benefit of priority from prior Japanese Patent Application No. 2019-116756, filed Jun. 24, 2019; the entire contents of which are incorporated herein by reference.

FIELD

[0002] Embodiments relate to a memory device.

BACKGROUND

[0003] Memory devices (semiconductor integrated circuit devices) in which variable resistance memory elements such as resistive random access memory (ReRAM) elements, alloy-based phase-change memory (PCM) elements, interfacial phase-change memory (iPCM) elements, and conductive-bridge RAM (CBRAM) elements are integrated on a semiconductor substrate have been proposed.

[0004] For a memory device using such a variable resistance memory element, a three-dimensional structure that can be easily manufactured, reduces the time required for development, and allows for high integration that reduces the processing cost has not been proposed.

BRIEF DESCRIPTION OF THE DRAWINGS

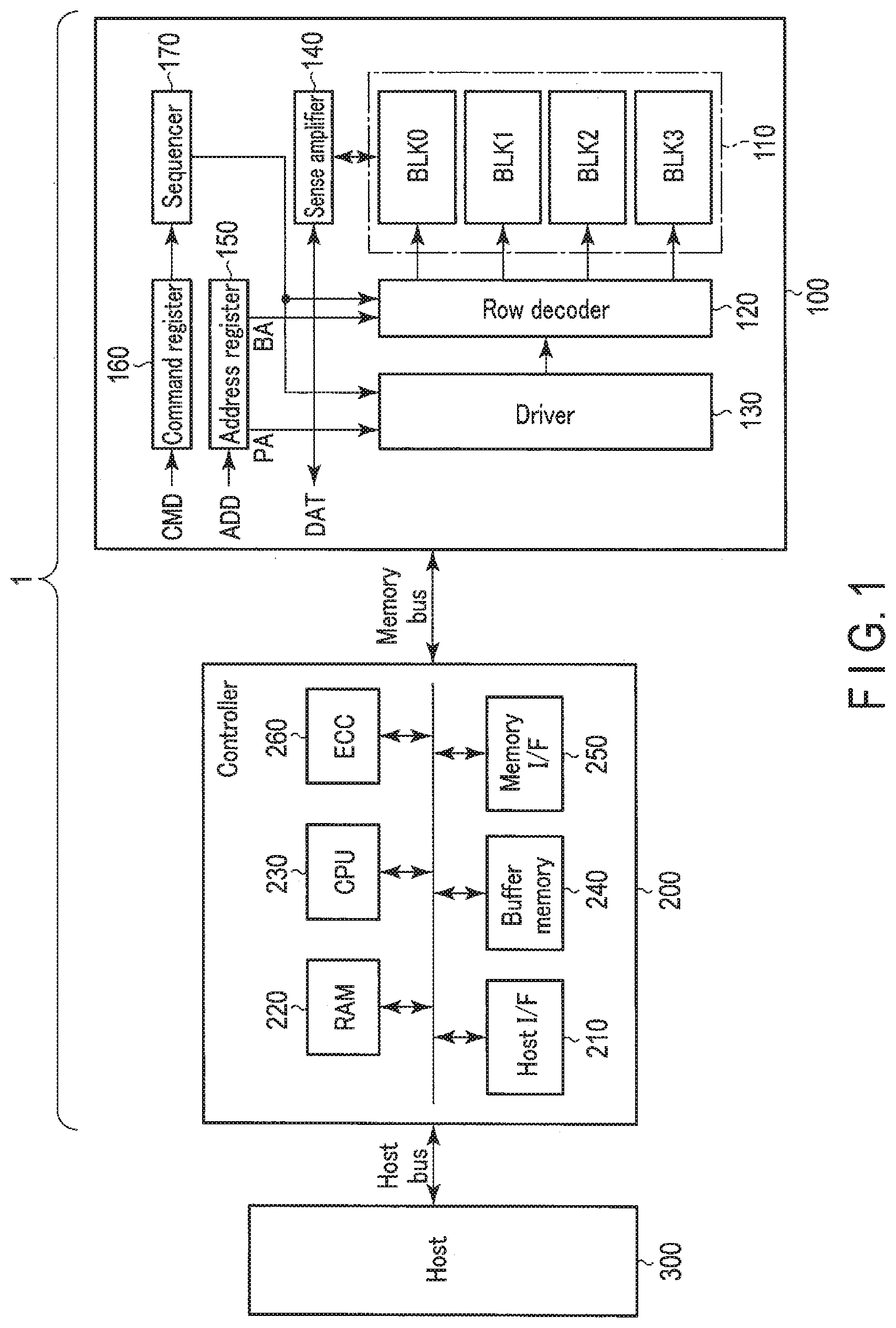

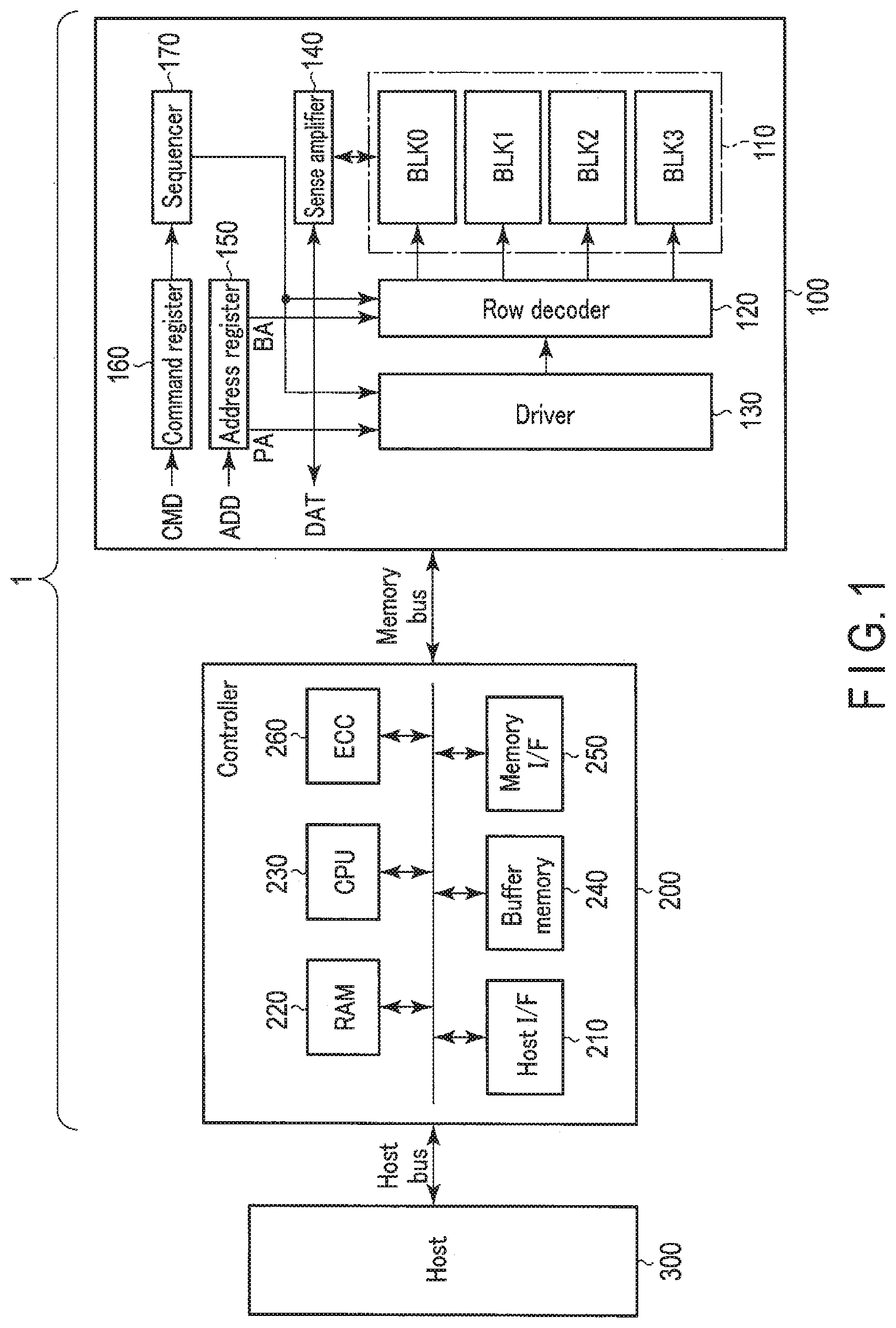

[0005] FIG. 1 is a block diagram roughly showing an overall configuration of a memory system.

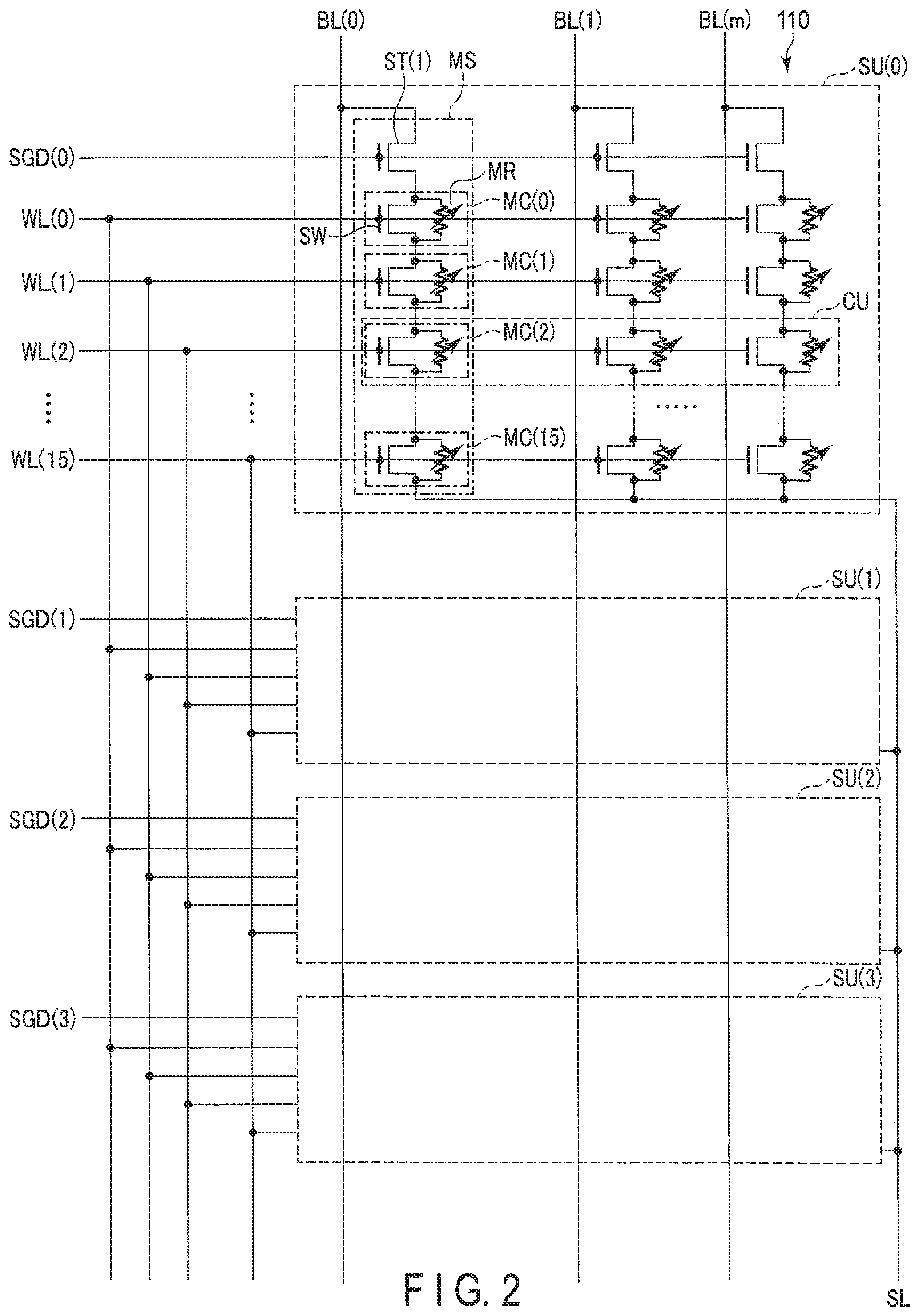

[0006] FIG. 2 is a circuit diagram showing a circuit (equivalent circuit) of a memory cell array.

[0007] FIG. 3 is a circuit diagram showing a path of a current flowing through a memory cell when a selector is turned on.

[0008] FIG. 4 is a circuit diagram showing a path of a current flowing through a memory cell when a selector is turned off.

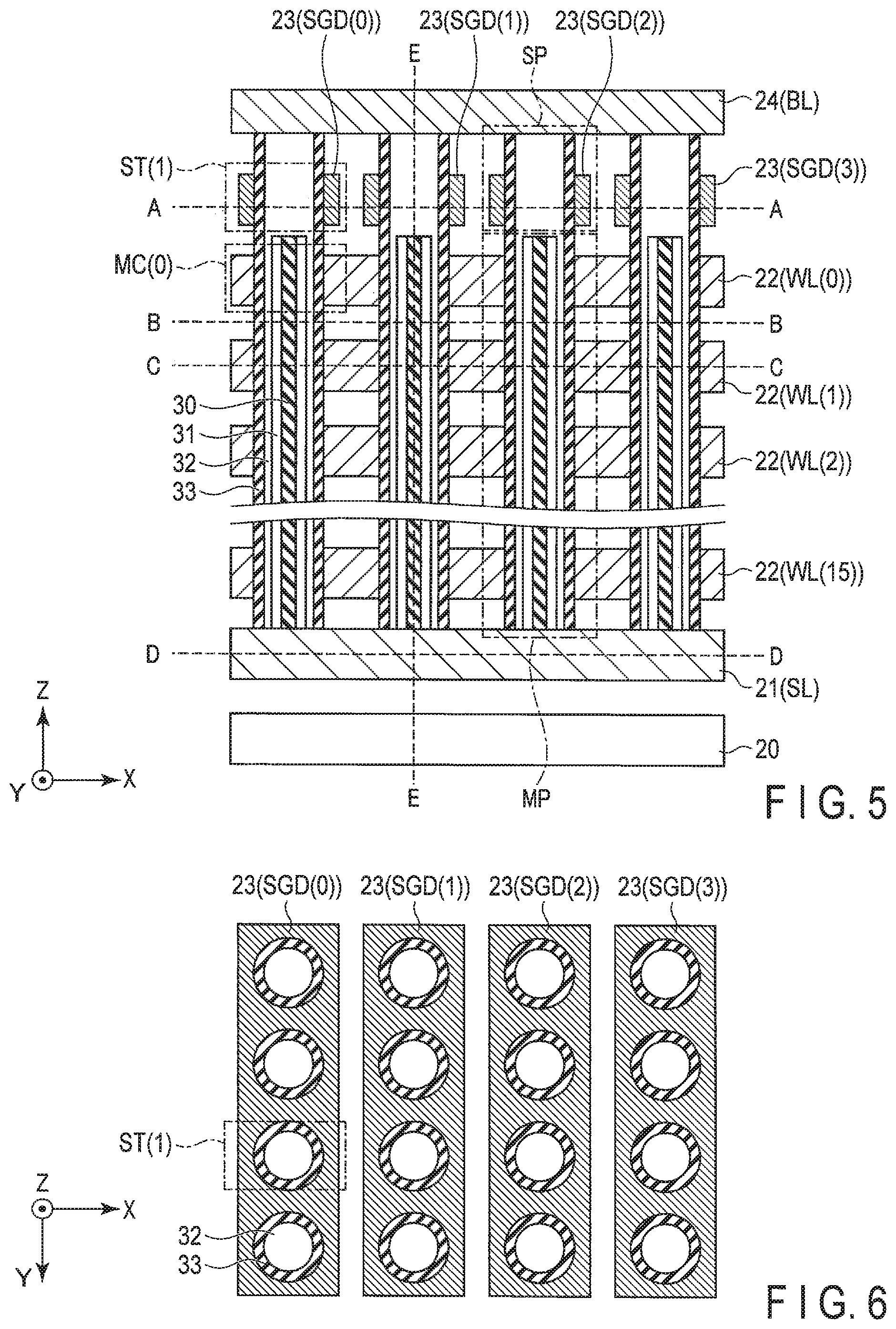

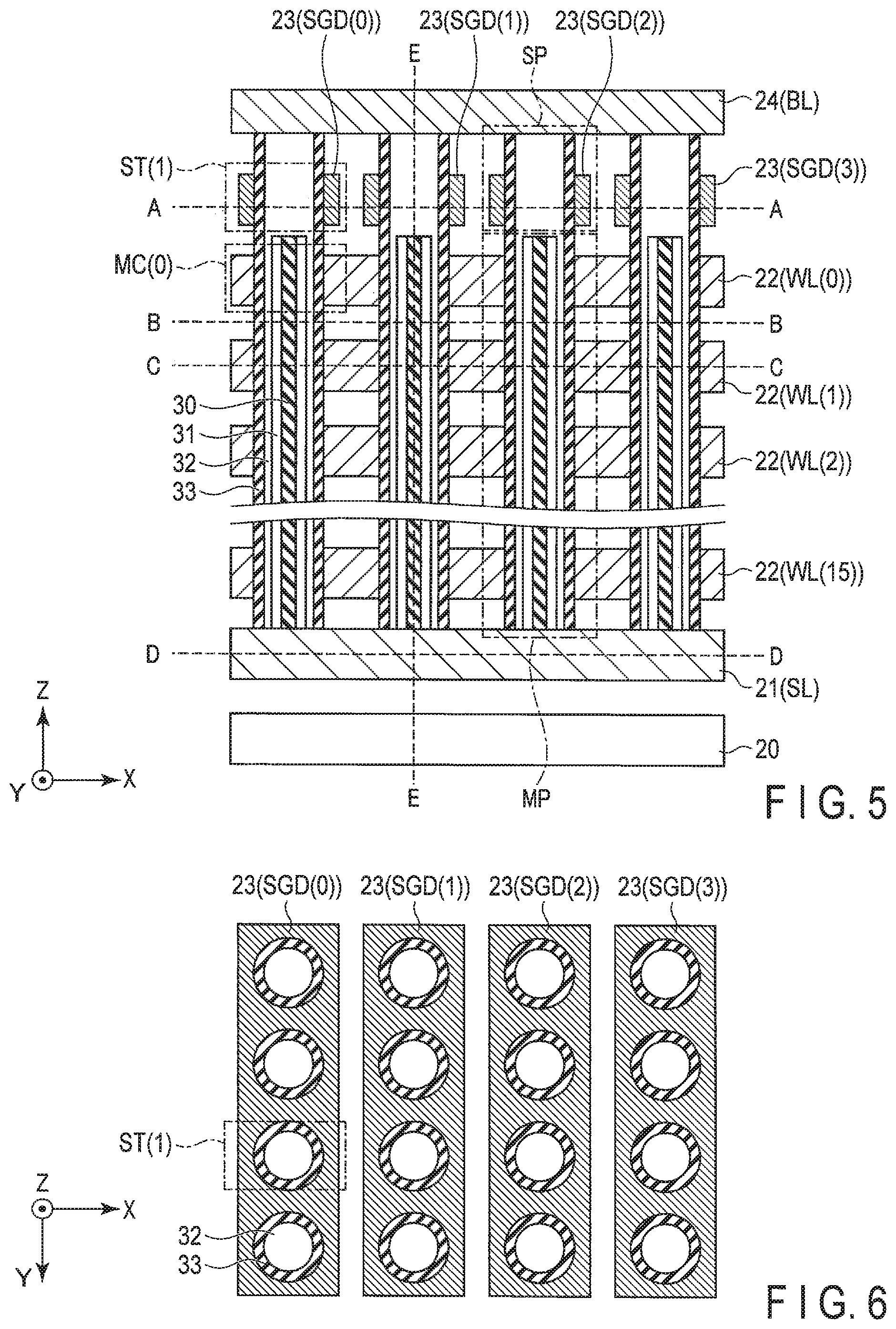

[0009] FIG. 5 is a cross-sectional view showing an example of a cross-sectional structure of a memory cell array included in a memory chip 100 according to a first embodiment.

[0010] FIG. 6 is a cross-sectional view taken along line A-A of FIG. 5.

[0011] FIG. 7 is a cross-sectional view taken along line B-B of FIG. 5.

[0012] FIG. 8 is a cross-sectional view taken along line C-C of FIG. 5.

[0013] FIG. 9 is a cross-sectional view in which a single memory cell is extracted.

[0014] FIG. 10 is a cross-sectional view taken along line D-D of FIG. 5.

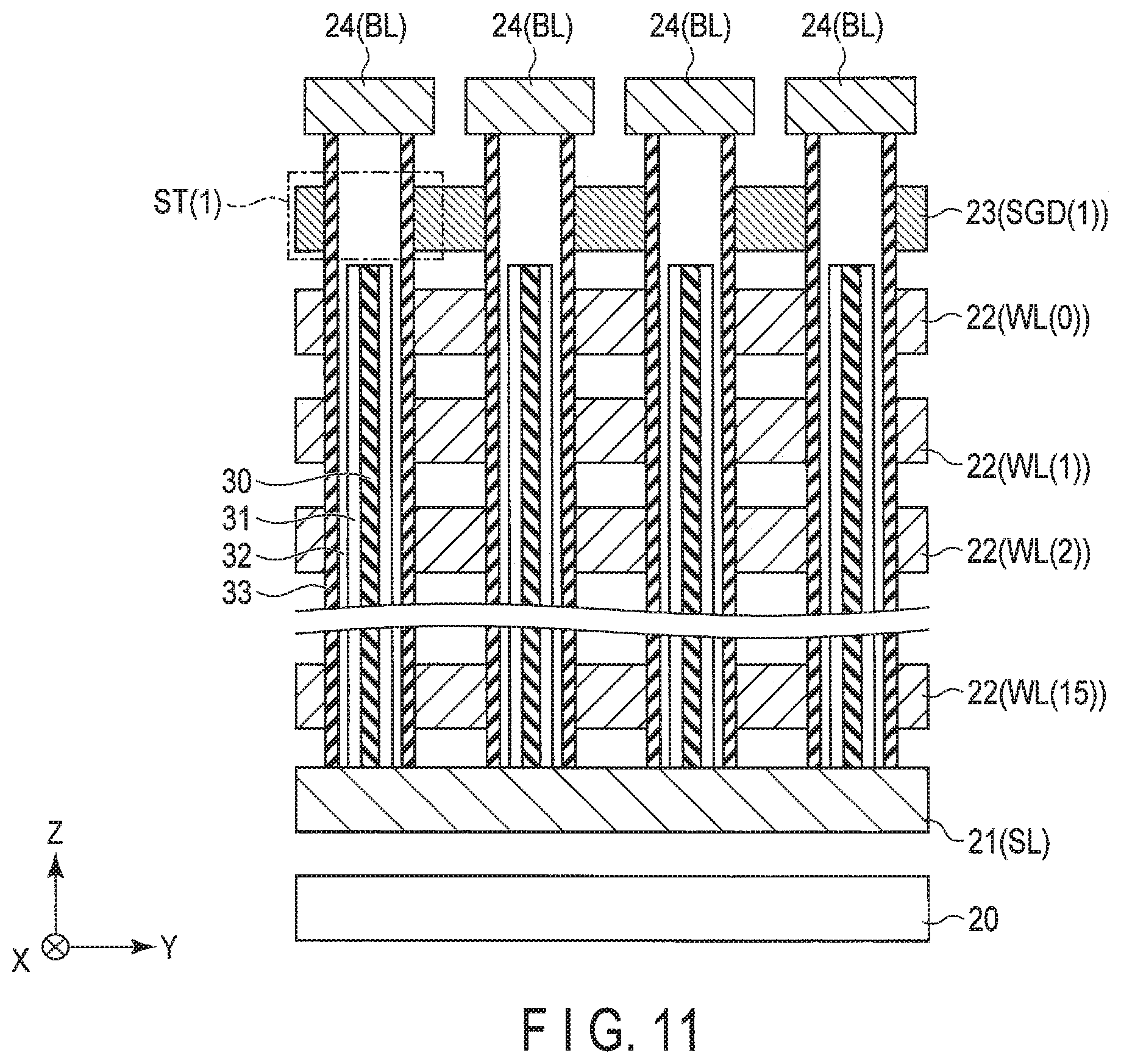

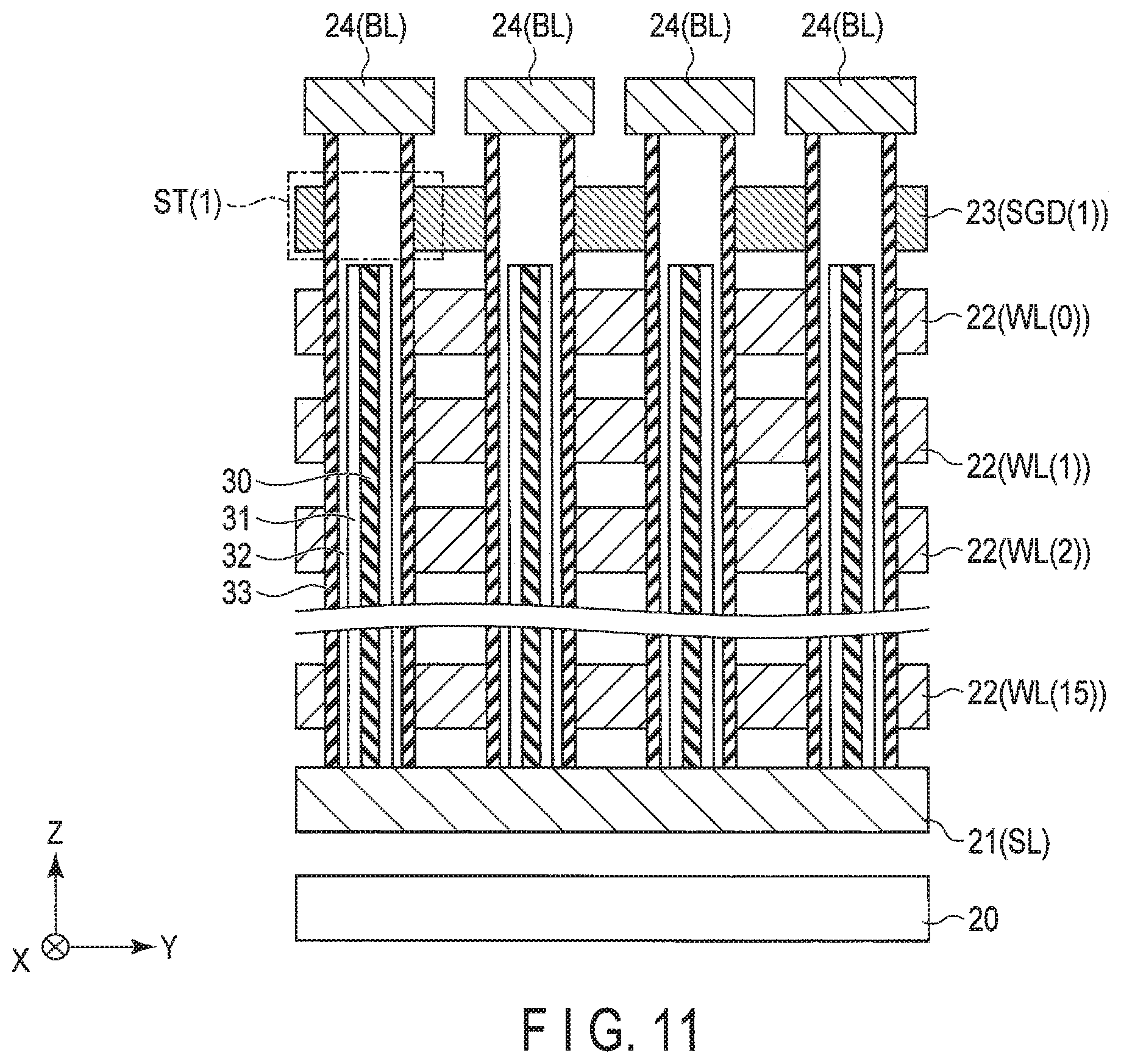

[0015] FIG. 11 shows a cross-sectional view along a direction orthogonal to the cross section shown in FIG. 5.

[0016] FIG. 12 is a circuit diagram in which a single memory cell string is extracted.

[0017] FIG. 13 is a cross-sectional view in which a memory pillar corresponding to a single memory cell string is extracted.

[0018] FIG. 14 shows a timing chart of an operation waveform.

[0019] FIG. 15 shows a relationship among selected memory cells, a selected word line, bit lines, and sense amplifiers according to a first example of a memory cell selection method.

[0020] FIG. 16 shows a relationship among a selected memory cell, a selected word line, bit lines, and a sense amplifier according to a comparative example of a memory cell selection method.

[0021] FIG. 17 shows a relationship among selected memory cells, a selected word line, bit lines, and sense amplifiers according to a second example of a memory cell selection method.

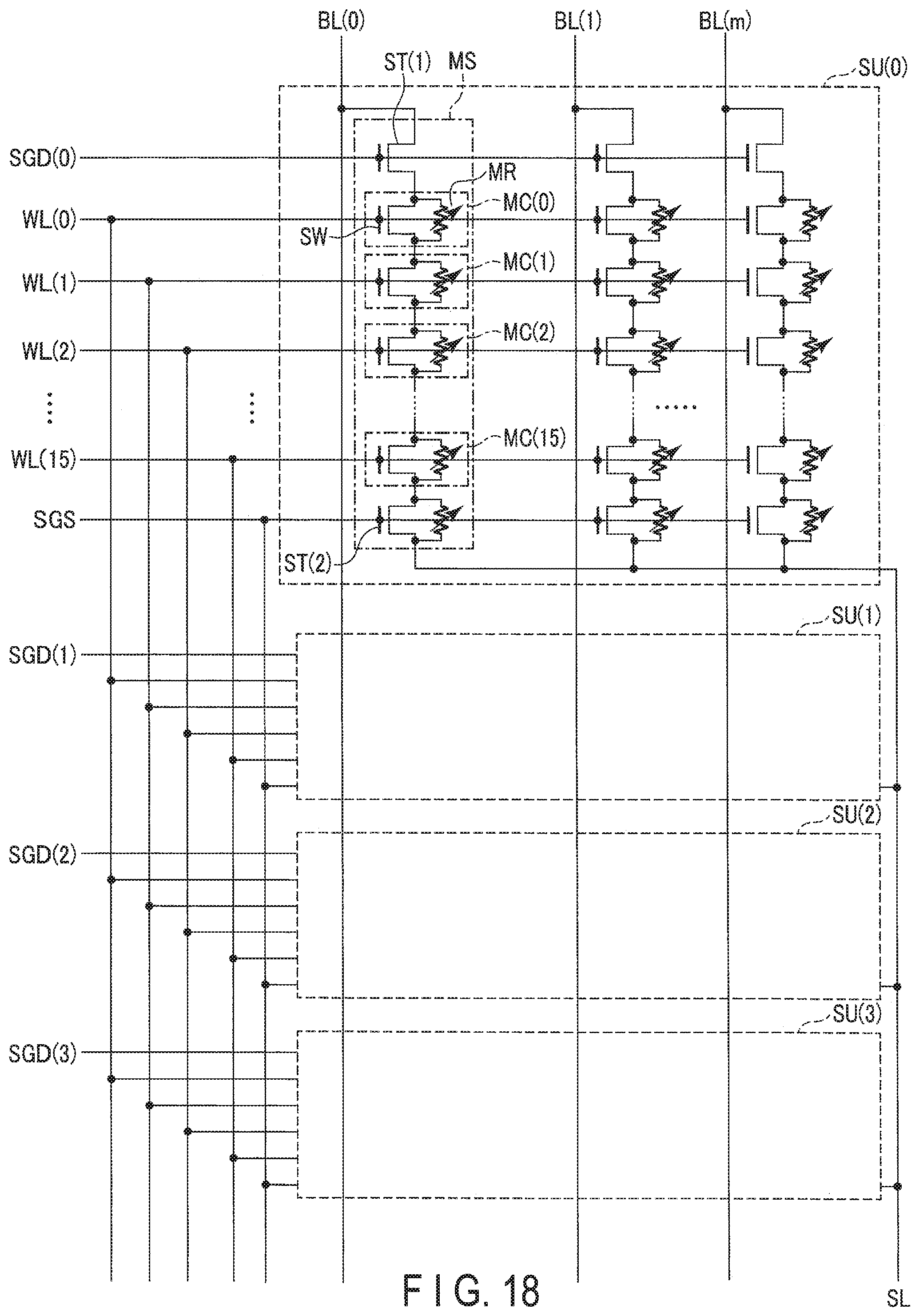

[0022] FIG. 18 is a circuit diagram showing a circuit (equivalent circuit) of a memory cell array.

[0023] FIG. 19 is a cross-sectional view showing an example of a cross-sectional structure of a memory cell array included in a memory chip according to a first modification of the first embodiment.

[0024] FIG. 20 is a cross-sectional view taken along line A1-A1 of FIG. 19.

[0025] FIG. 21 is a cross-sectional view taken along line B1-B1 of FIG. 19.

[0026] FIG. 22 is a cross-sectional view taken along line C1-C1 of FIG. 19.

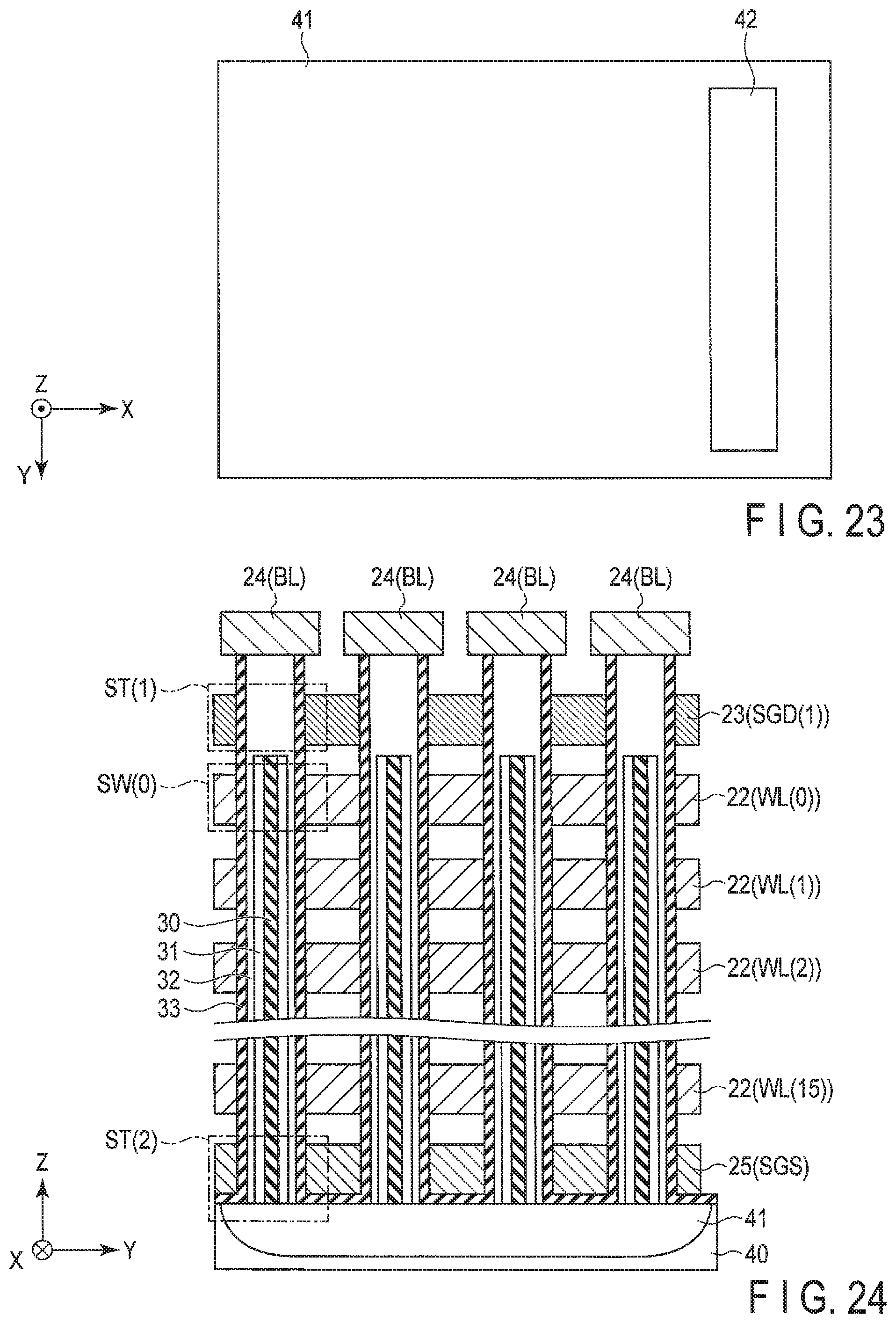

[0027] FIG. 23 is a cross-sectional view taken along line D1-D1 of FIG. 19.

[0028] FIG. 24 is a cross-sectional view taken along line E1-E1 of FIG. 19.

[0029] FIG. 25 is a circuit diagram in which a single memory cell string is extracted.

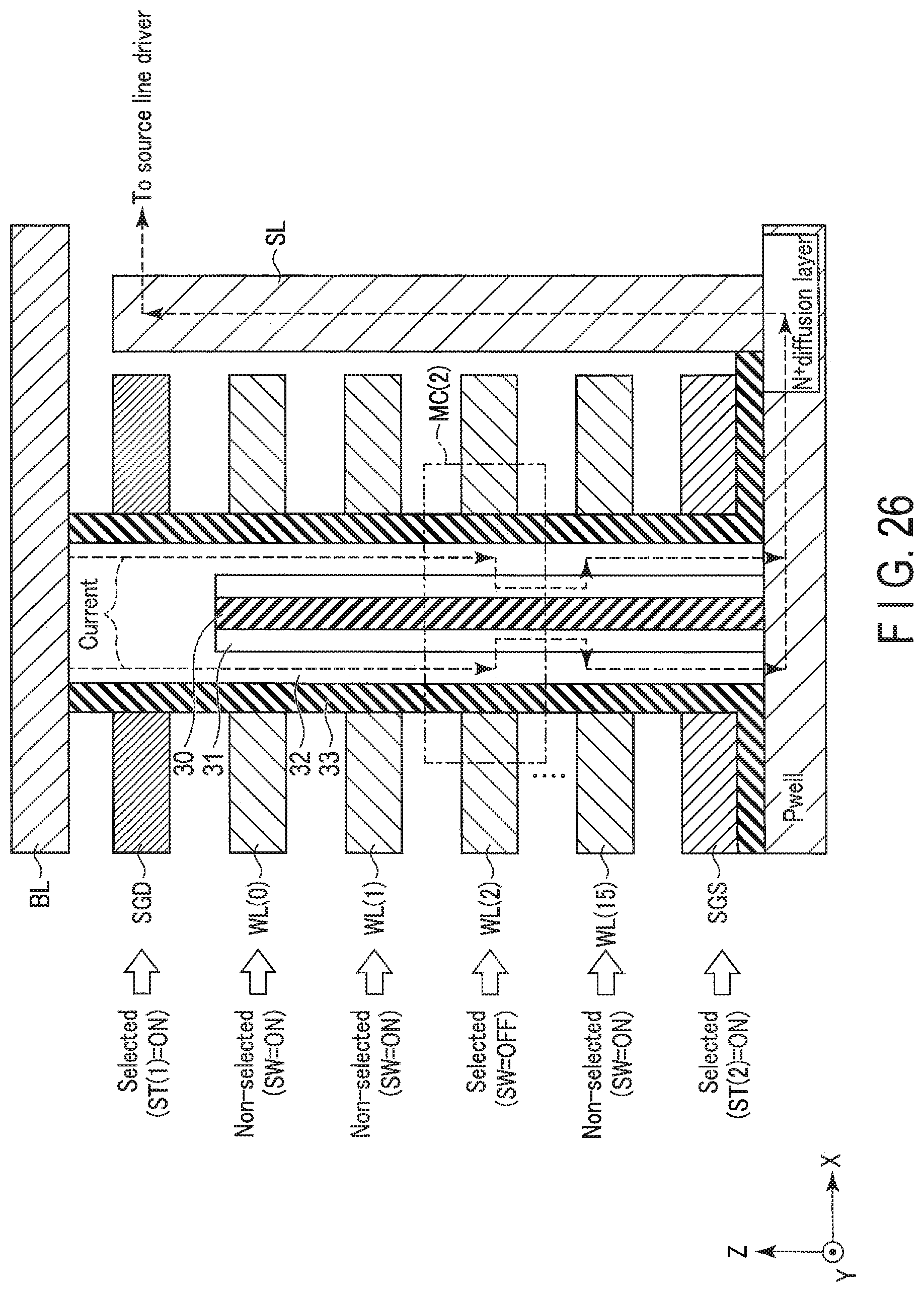

[0030] FIG. 26 is a cross-sectional view in which a memory pillar corresponding to a single memory cell string is extracted.

[0031] FIG. 27 is a cross-sectional view in which a single memory cell is extracted.

[0032] FIG. 28 is a cross-sectional view in which a memory pillar corresponding to a single memory cell string is extracted.

[0033] FIG. 29 is a cross-sectional view in which a single memory cell is extracted.

[0034] FIG. 30 is a cross-sectional view in which a single memory cell is extracted.

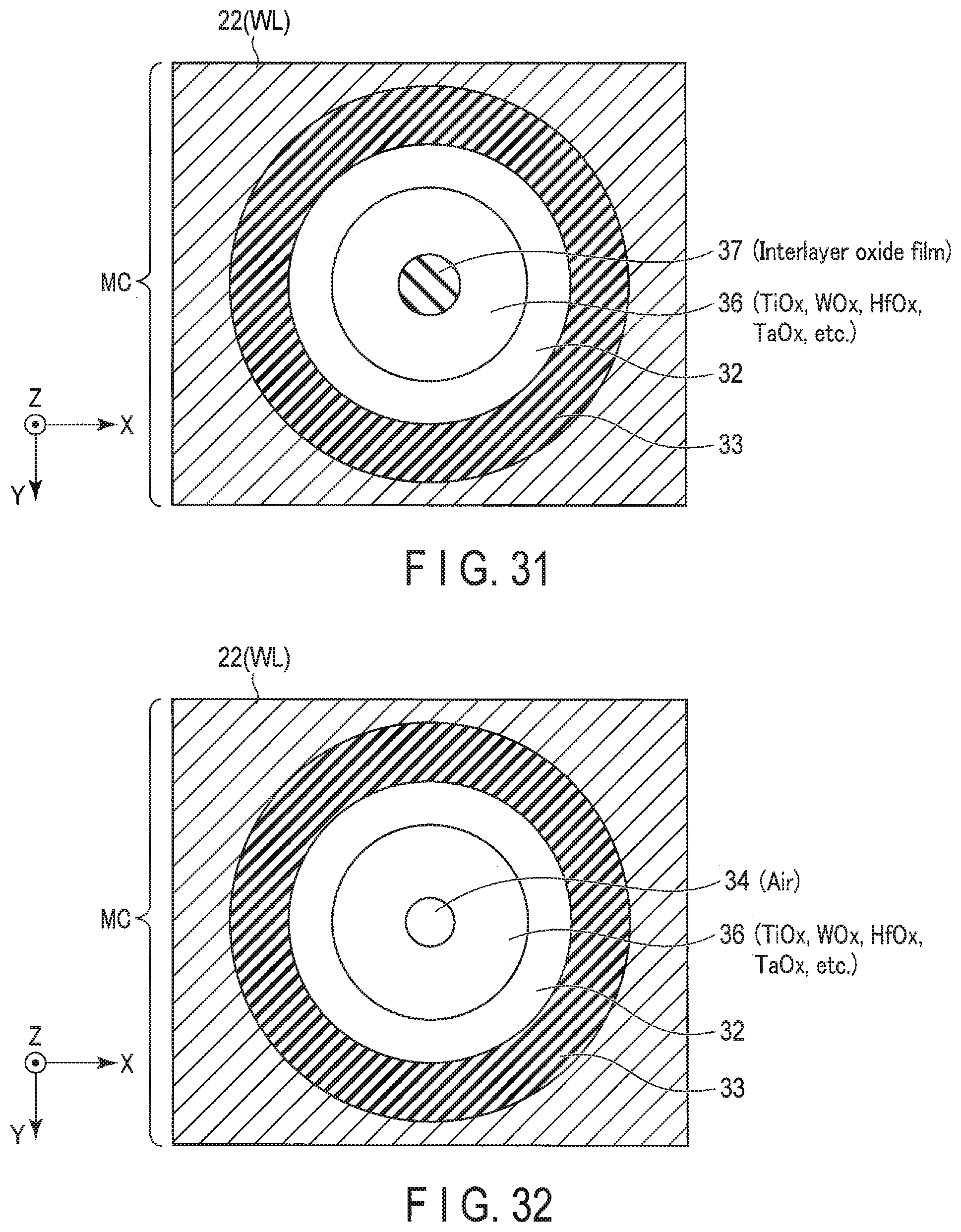

[0035] FIG. 31 is a cross-sectional view in which a single memory cell is extracted.

[0036] FIG. 32 is a cross-sectional view in which a single memory cell is extracted.

[0037] FIG. 33 is a cross-sectional view in which a single memory cell is extracted.

[0038] FIG. 34 is a cross-sectional view in which a single memory cell is extracted.

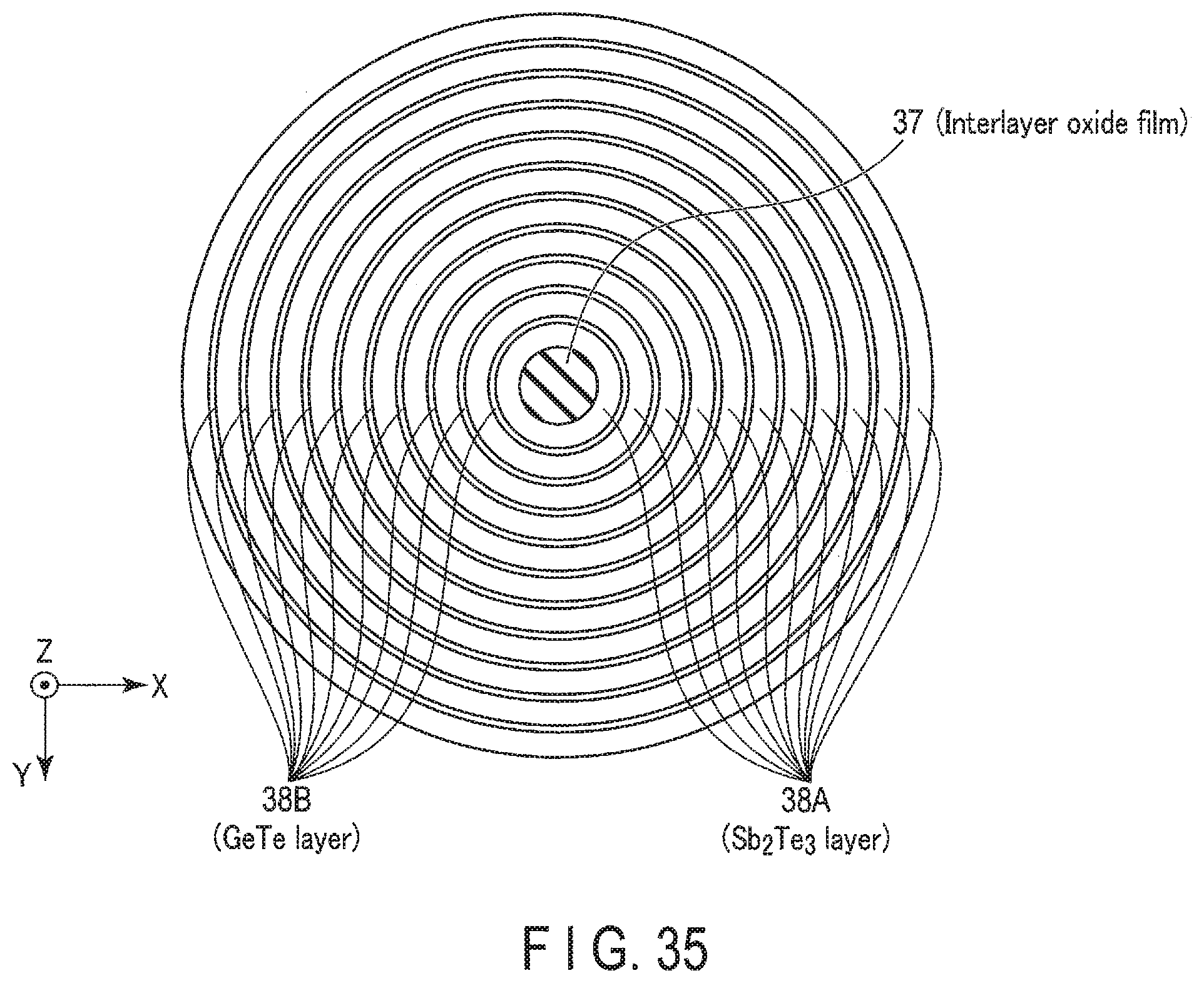

[0039] FIG. 35 is a cross-sectional view in which the variable resistance layer of FIG. 34 is shown in more detail.

[0040] FIG. 36 is a cross-sectional view in which a memory pillar corresponding to a single memory cell string is extracted.

[0041] FIG. 37 is a cross-sectional view showing F of FIG. 36.

[0042] FIG. 38 is a cross-sectional view showing another example of the variable resistance layer of FIG. 34 in more detail.

[0043] FIG. 39 is a cross-sectional view showing another example of F in FIG. 36.

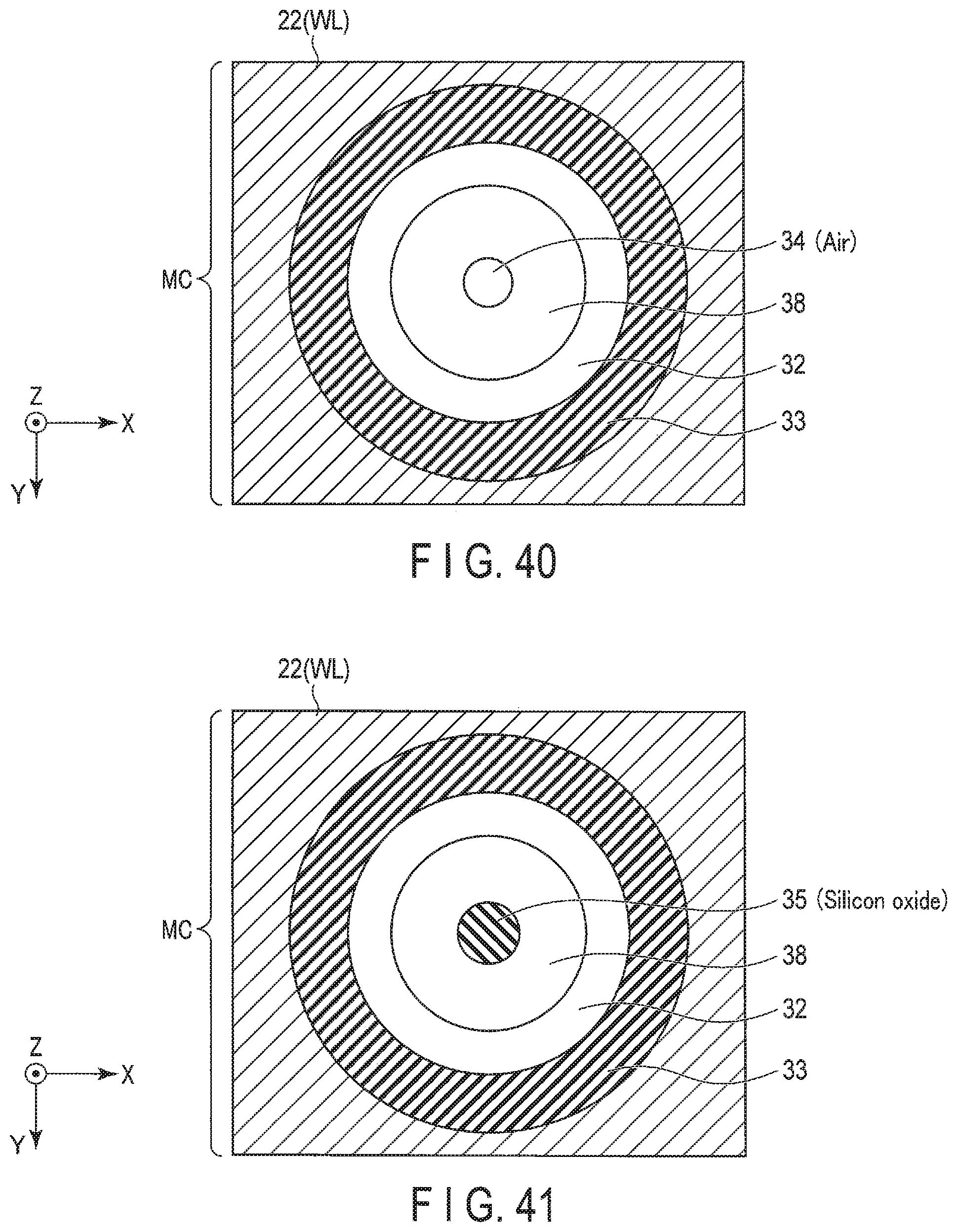

[0044] FIG. 40 is a cross-sectional view in which a single memory cell is extracted.

[0045] FIG. 41 is a cross-sectional view in which a single memory cell is extracted.

[0046] FIG. 42 shows a timing chart of an operation waveform.

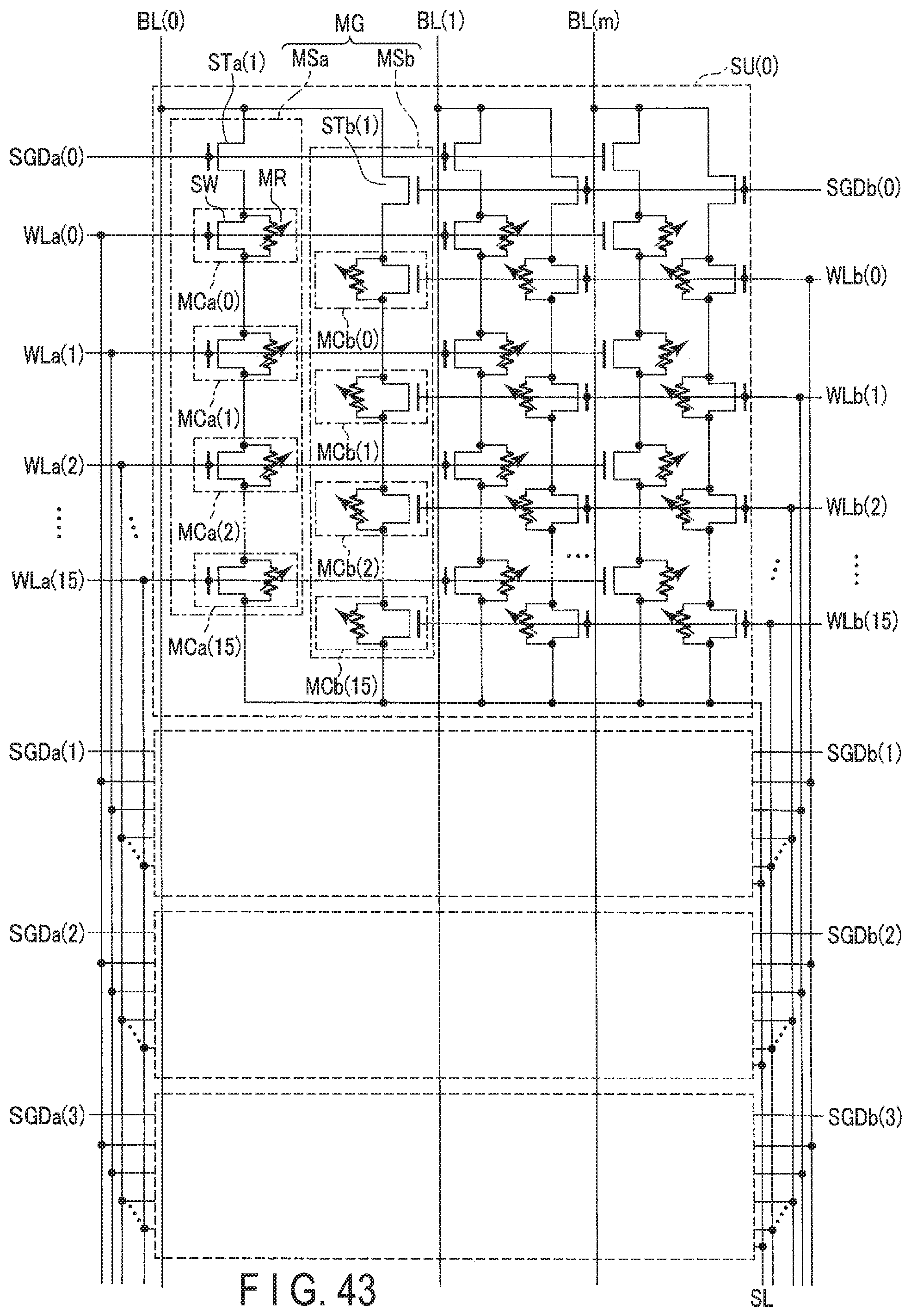

[0047] FIG. 43 is a circuit diagram showing a circuit (equivalent circuit) of a memory cell array.

[0048] FIG. 44 is a cross-sectional view showing a relationship between a bit line of a memory cell array included in a memory chip and a contact plug that couples the bit line and a memory pillar, according to a second embodiment.

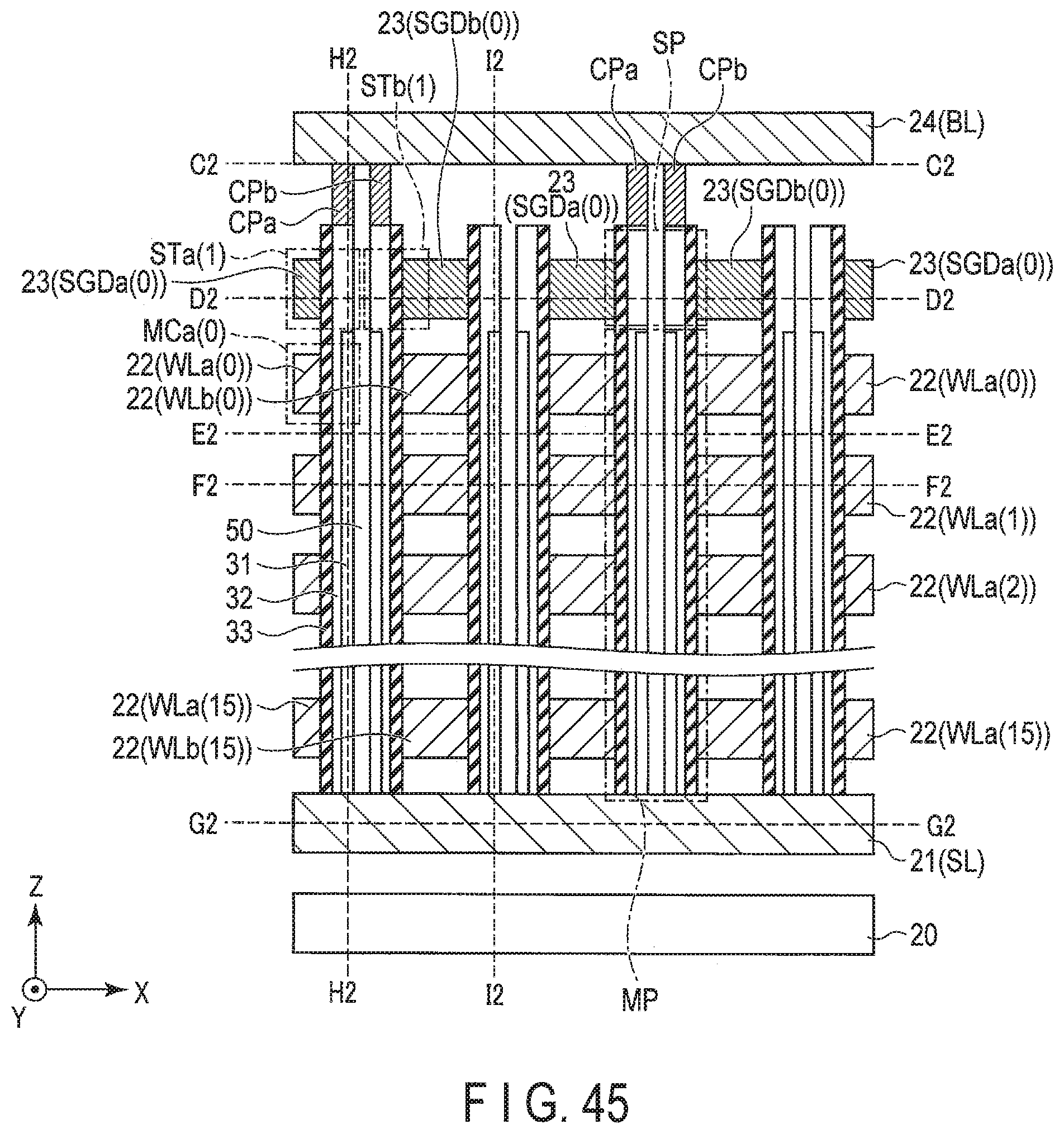

[0049] FIG. 45 is a cross-sectional view taken along line A2-A2 of FIG. 44.

[0050] FIG. 46 is a cross-sectional view taken along line B2-B2 of FIG. 44.

[0051] FIG. 47 is a cross-sectional view taken along line D2-D2 of FIGS. 45 and 46.

[0052] FIG. 48 is a cross-sectional view taken along line E2-E2 of FIGS. 45 and 46.

[0053] FIG. 49 is a cross-sectional view taken along line F2-F2 of FIGS. 45 and 46.

[0054] FIG. 50 is a cross-sectional view showing two memory cells separated by a memory trench.

[0055] FIG. 51 is a cross-sectional view taken along line G2-G2 of FIGS. 45 and 46.

[0056] FIG. 52 is a cross-sectional view taken along line H2-H2 of FIGS. 45 and 46.

[0057] FIG. 53 is a cross-sectional view taken along line 12-12 of FIGS. 45 and 46.

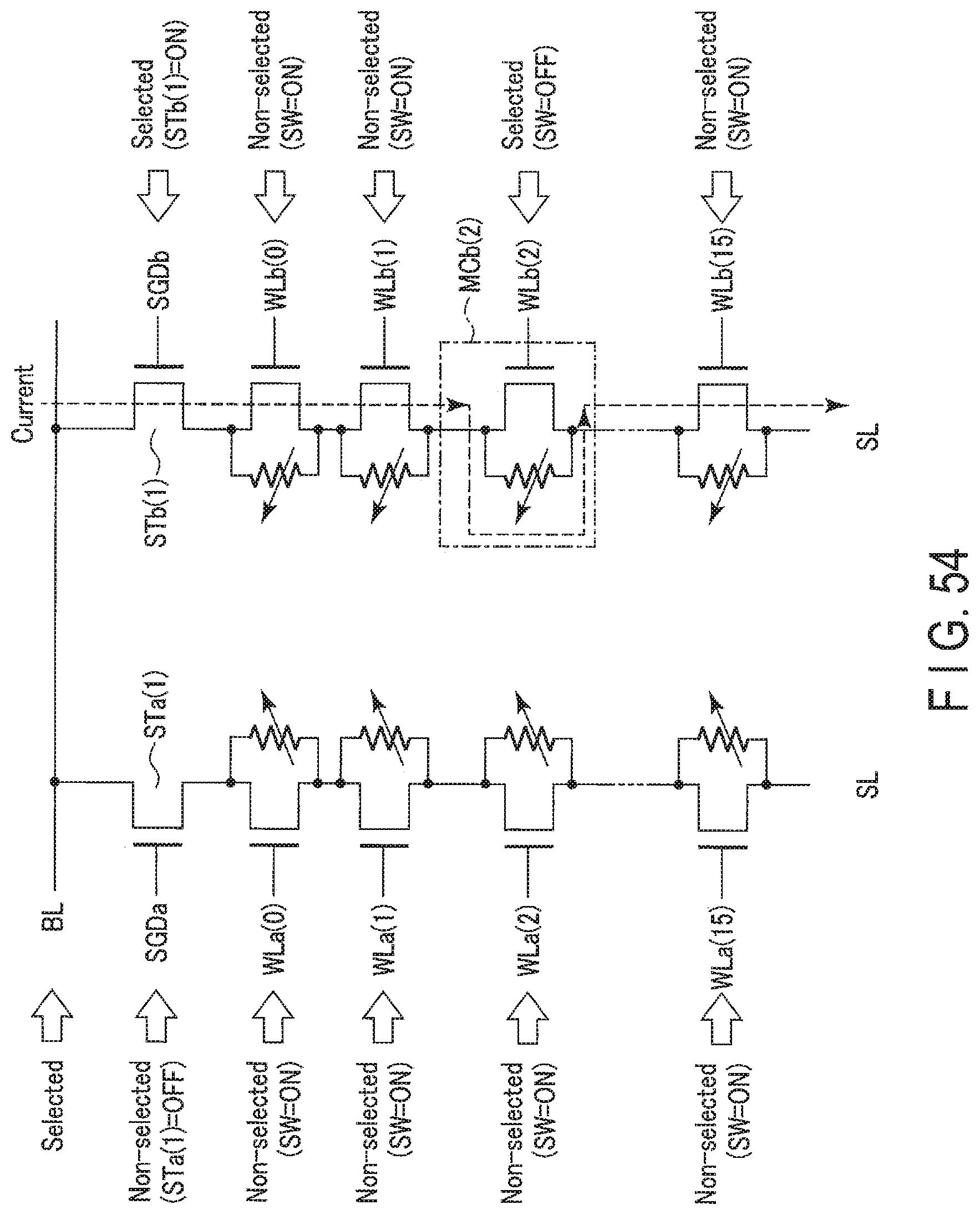

[0058] FIG. 54 is a circuit diagram in which two memory cell strings are extracted.

[0059] FIG. 55 is a cross-sectional view in which a memory pillar corresponding to two memory cell strings is extracted.

[0060] FIG. 56 is a circuit diagram showing a circuit (equivalent circuit) of a memory cell array.

[0061] FIG. 57 is a plan view showing a relationship between a bit line of a memory cell array included in a memory chip and a contact plug that couples the bit line and a memory pillar, according to a first modification of the second embodiment.

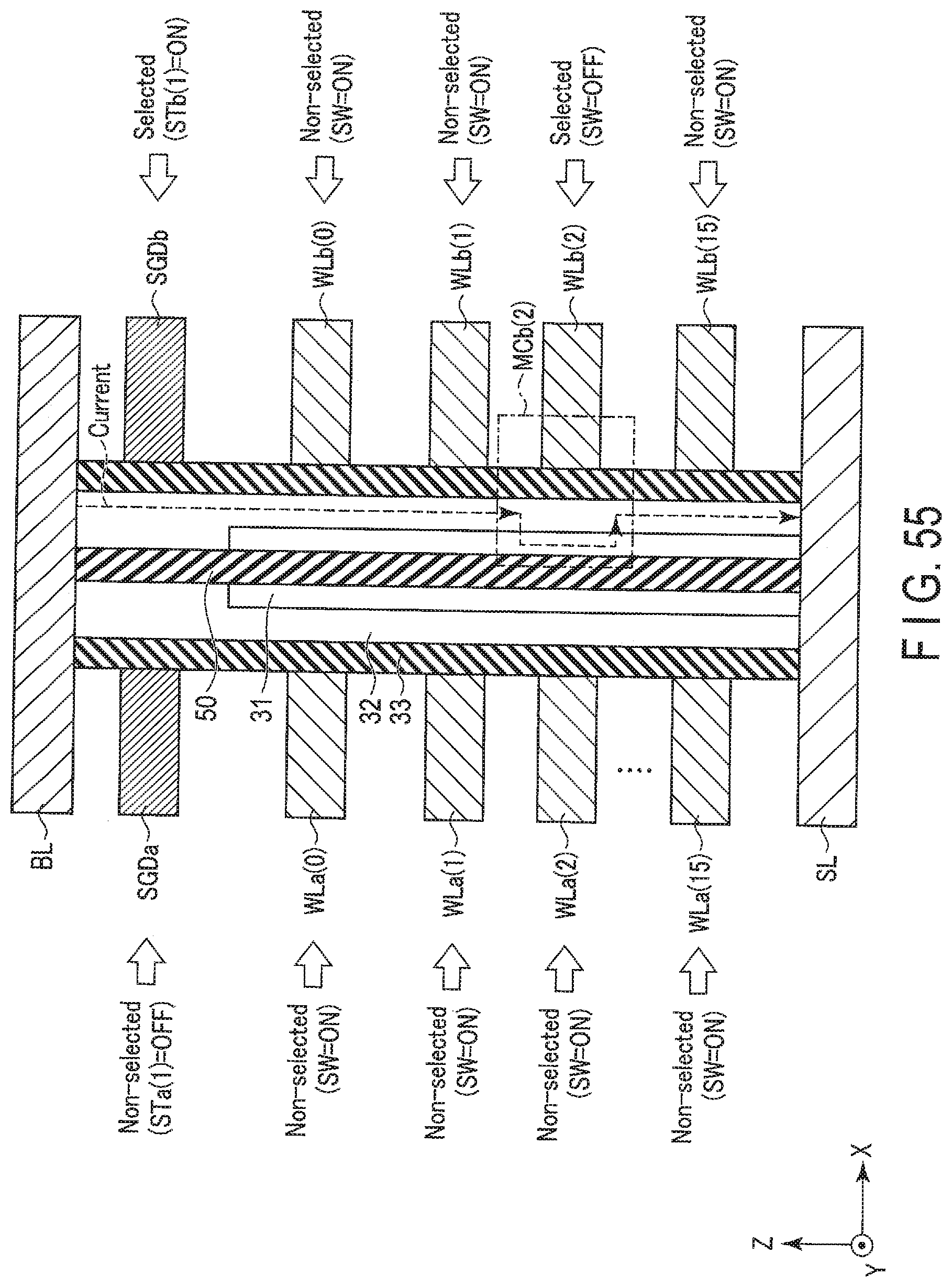

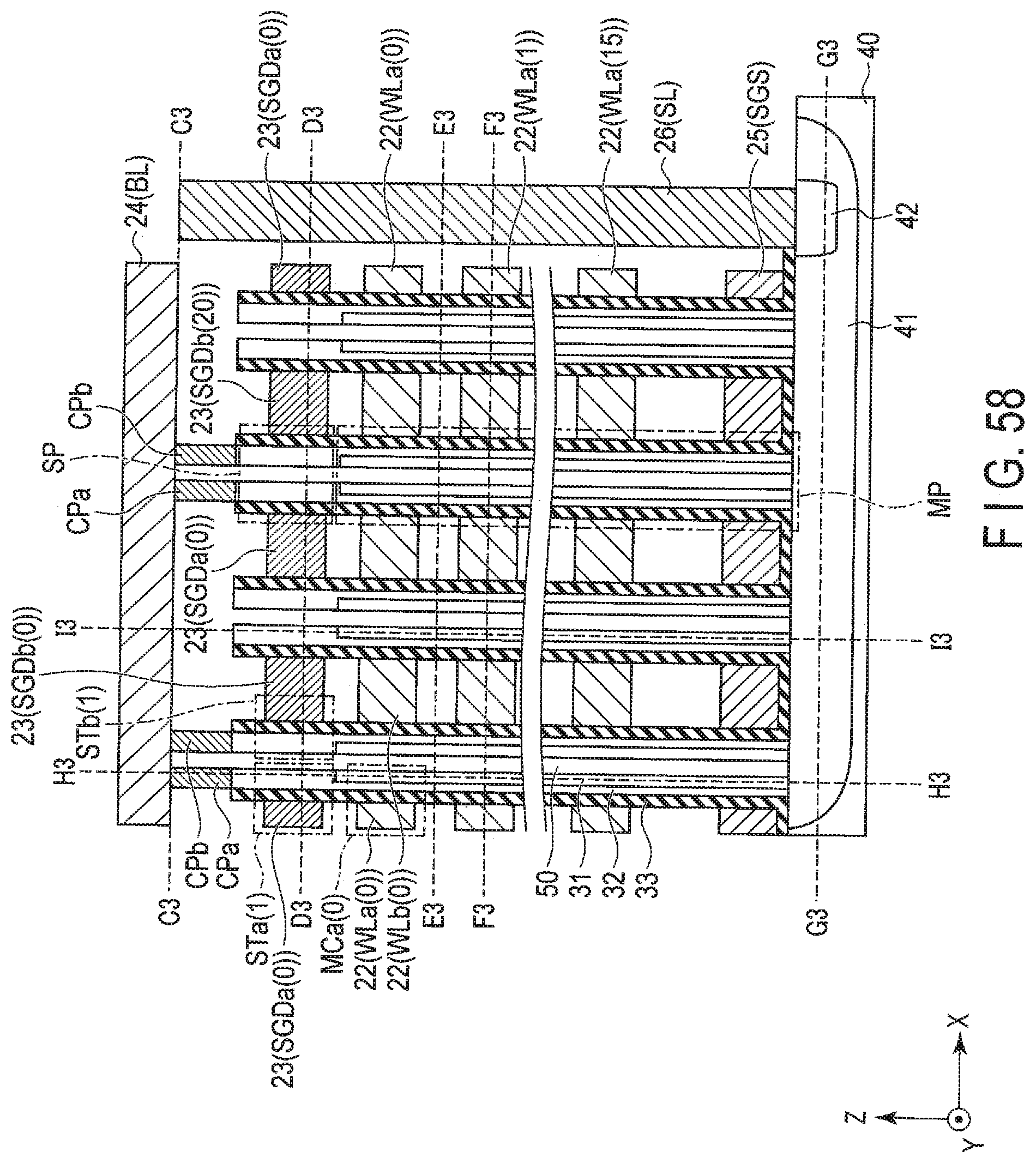

[0062] FIG. 58 is a cross-sectional view taken along line A3-A3 of FIG. 57.

[0063] FIG. 59 is a cross-sectional view taken along line B3-B3 of FIG. 57.

[0064] FIG. 60 is a cross-sectional view taken along line D3-D3 of FIGS. 58 and 59.

[0065] FIG. 61 is a cross-sectional view taken along line E3-E3 of FIGS. 58 and 59.

[0066] FIG. 62 is a cross-sectional view taken along line F3-F3 of FIGS. 58 and 59.

[0067] FIG. 63 is a cross-sectional view taken along line G3-G3 of FIGS. 58 and 59.

[0068] FIG. 64 is a cross-sectional view taken along line H3-H3 of FIGS. 58 and 59.

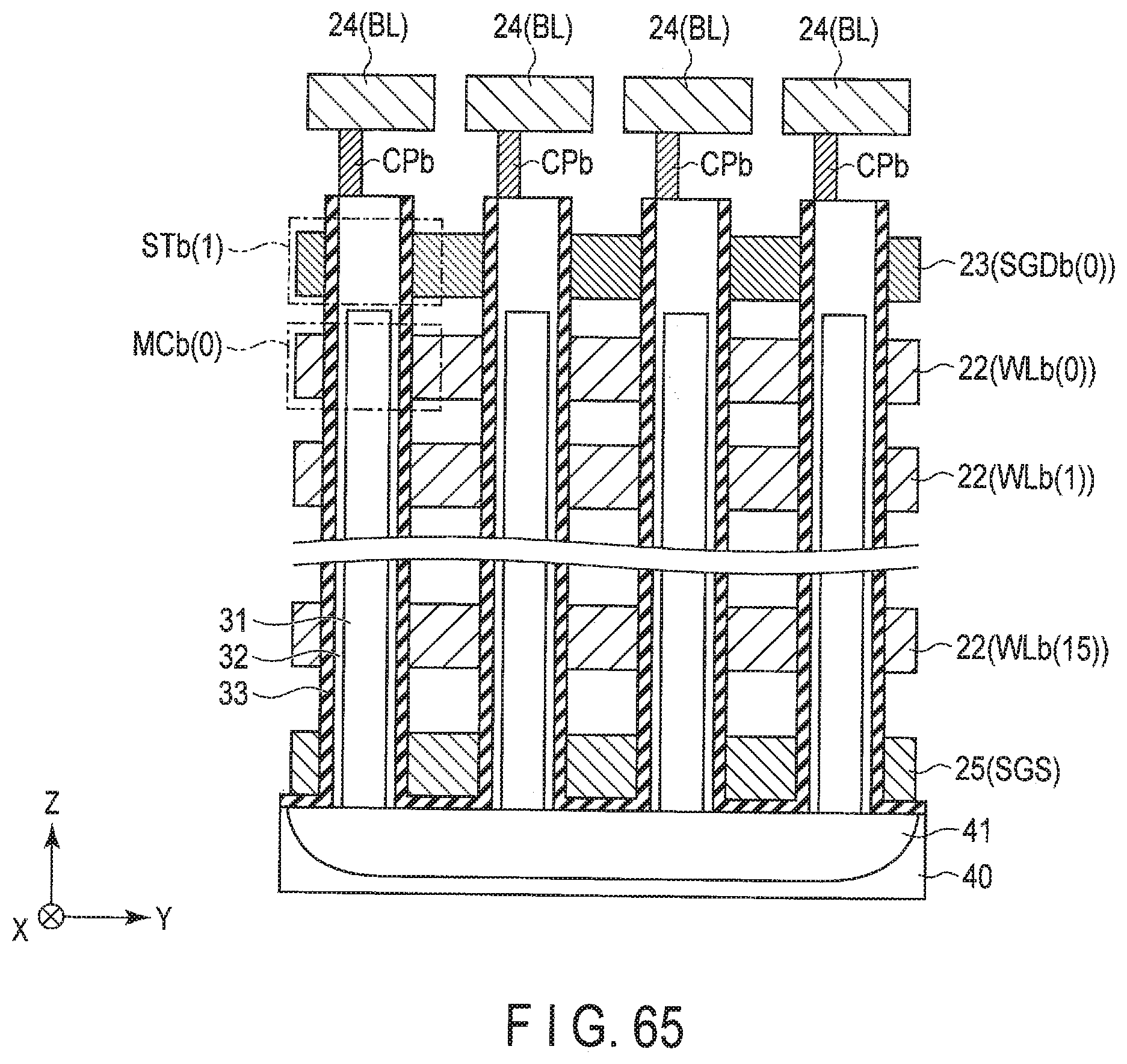

[0069] FIG. 65 is a cross-sectional view taken along line 12-12 of FIGS. 58 and 59.

[0070] FIG. 66 is a circuit diagram in which two memory cell strings are extracted.

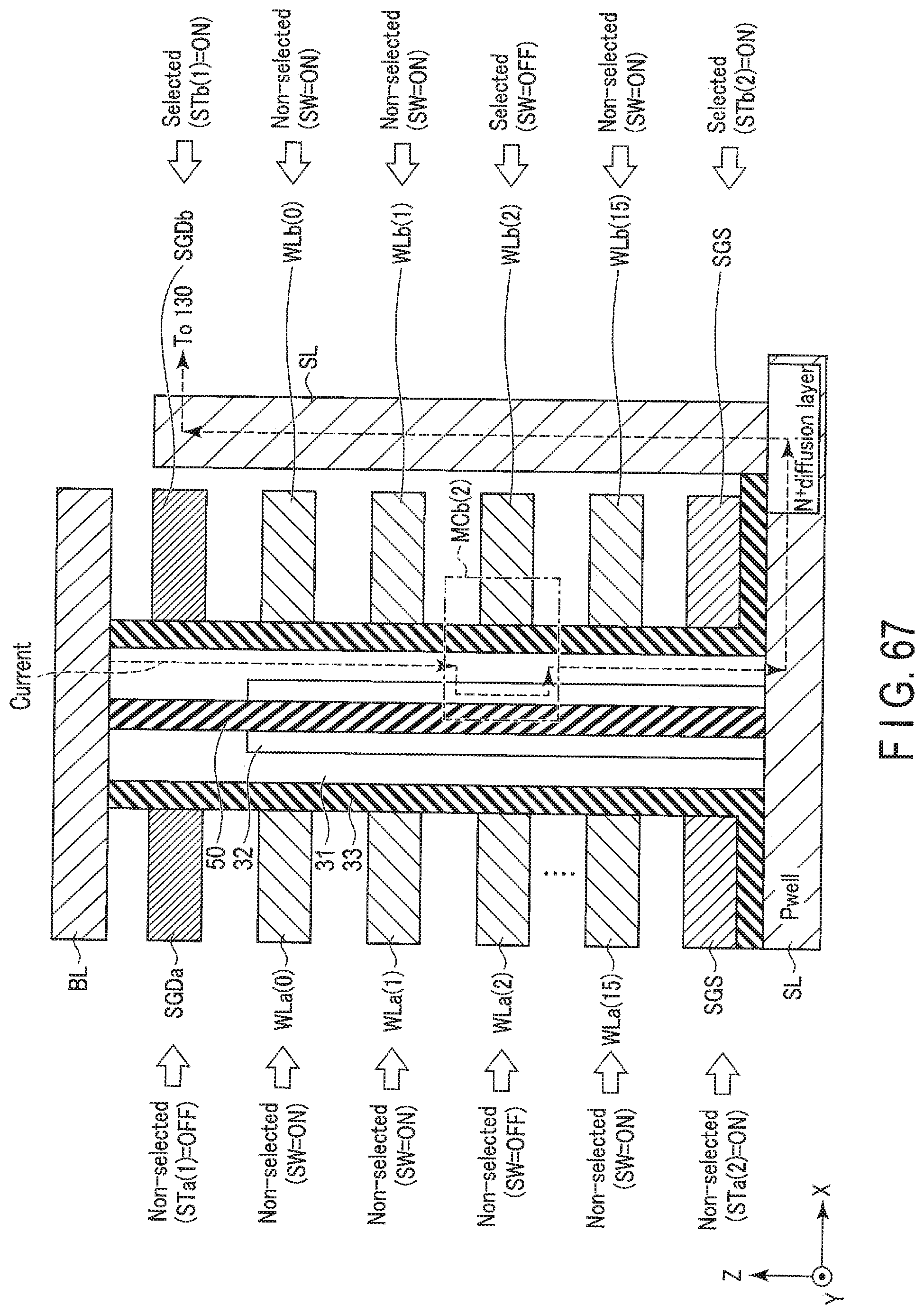

[0071] FIG. 67 is a cross-sectional view in which a memory pillar corresponding to two memory cell strings is extracted.

[0072] FIG. 68 is a cross-sectional view in which two memory cells are extracted.

[0073] FIG. 69 is a cross-sectional view in which two memory cells are extracted.

[0074] FIG. 70 is a plan view showing a first example of a relationship between a memory pillar and a bit line according to the first embodiment.

[0075] FIG. 71 is a plan view showing a second example of a relationship between memory pillars and bit lines according to the first embodiment.

[0076] FIG. 72 is a plan view showing a third example of a relationship between memory pillars and bit lines according to the first embodiment.

[0077] FIG. 73 is a cross-sectional view showing J in FIG. 72.

[0078] FIG. 74 is a plan view showing a first example of a relationship between a memory pillar and a bit line according to the second embodiment.

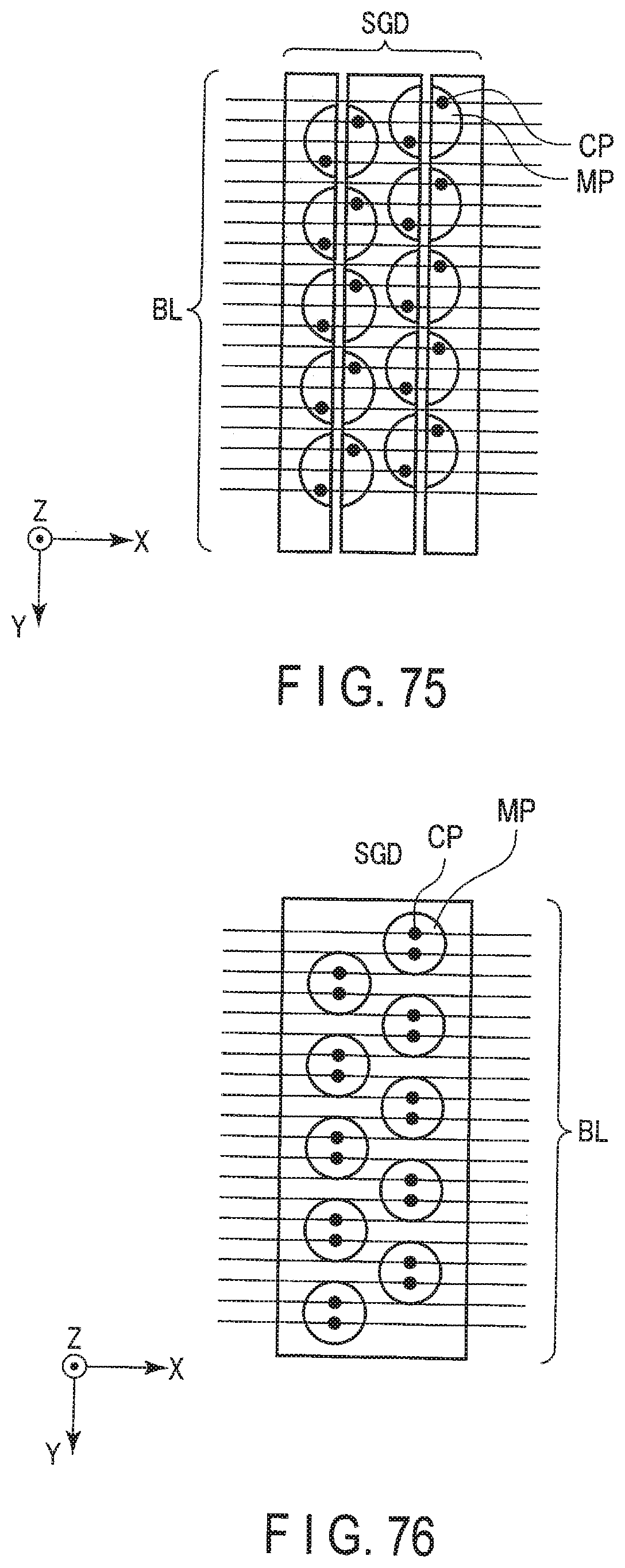

[0079] FIG. 75 is a plan view showing a second example of a relationship between memory pillars and bit lines according to the second embodiment.

[0080] FIG. 76 is a plan view showing a third example of a relationship between memory pillars and bit lines according to the second embodiment.

[0081] FIG. 77 is a plan view showing a fourth example of a relationship between memory pillars and bit lines according to the second embodiment.

[0082] FIG. 78 is a cross-sectional view showing a memory pillar.

DETAILED DESCRIPTION

[0083] In general, according to one embodiment, a memory device includes: a plurality of memory cells each including: a variable resistance memory region extending in a first direction that is orthogonal to a semiconductor substrate; a first semiconductor layer extending in the first direction and being in contact with the variable resistance memory region; a first insulating layer extending in the first direction and being in contact with the first semiconductor layer; and a first voltage application electrode extending in a second direction that is orthogonal to the first direction and being in contact with the first insulating layer; a first select transistor including: a second semiconductor layer extending in the first direction; a second insulating layer extending in the first direction and being in contact with the second semiconductor layer; and a second voltage application electrode extending in the second direction and being in contact with the second insulating layer; and a memory cell string including the first select transistor, the memory cells, and a third voltage application electrode, the memory cells being coupled in series in the first direction, one end of the first select transistor being coupled to one end of one of the memory cells that is provided at a first end portion, the third voltage application electrode being coupled to one end of one of the memory cells that is provided at a second end portion.

[0084] Hereinafter, embodiments will be described with reference to the accompanying drawings. In the description that follows, components having the same function and configuration will be denoted by a common reference numeral.

<1> First Embodiment

[0085] A memory system according to a first embodiment will be described.

[0086] <1-1> Configuration

[0087] <1-1-1> Overall Configuration of Memory System

[0088] An overall configuration of the memory system according to the present embodiment will be roughly described, with reference to FIG. 1.

[0089] As shown in FIG. 1, a memory system 1 comprises a memory chip 100 and a controller 200. The memory chip 100 and the controller 200 in combination, for example, may configure a single semiconductor device; examples of such a configuration include a memory card such as an SD.TM. card and a solid state drive (SSD).

[0090] The memory chip 100 includes a plurality of memory cells, and stores data in a non-volatile manner. The controller 200 is coupled to the memory chip 100 via a memory bus, and is coupled to a host 300 via a host bus. The controller 200 controls the memory chip 100, and accesses the memory chip 100 in response to a host command received from the host 300. The host 300 is, for example, a digital camera, a personal computer, etc., and the host bus is a bus that is compatible with, for example, an SD.TM. interface. The memory bus transmits and receives a signal that is compatible with a memory interface.

[0091] <1-1-2> Configuration of Controller 200

[0092] A detailed configuration of the controller 200 will be described with reference to FIG. 1.

[0093] As shown in FIG. 1, the controller 200 includes a host interface circuit (host I/F) 210, an embedded memory (random access memory: RAM) 220, a processor (central processing unit: CPU) 230, a buffer memory 240, a memory interface circuit (memory I/F) 250, and an error checking and correcting (ECC) circuit 260.

[0094] The host interface circuit 210 is coupled to the host 300 via the host bus, and transfers a host command and data received from the host 300 to the processor 230 and the buffer memory 240, respectively. In response to an instruction from the processor 230, the host interface circuit 210 transfers the data in the buffer memory 240 to the host 300.

[0095] The processor 230 controls the entire operation of the controller 200. Upon receiving, for example, a host command relating to a read operation from the host 300, the processor 230 causes, in response thereto, the memory interface circuit 250 to issue a read command (memory command) to the memory chip 100. Upon receiving a host command relating to a write operation from the host 300, the processor 230 performs a similar operation. Also, the processor 230 performs various processes (e.g., wear leveling) for managing the memory chip 100.

[0096] The memory interface circuit 250 is coupled to the memory chip 100 via a memory bus, and controls communications with the memory chip 100. Based on an instruction received from the processor 230, the memory interface circuit 250 transmits a variety of signals to the memory chip 100, and receives a variety of signals from the memory chip 100.

[0097] The buffer memory 240 temporarily stores write data to the memory chip 100 and read data from the memory chip 100.

[0098] The embedded memory 220 is, for example, a semiconductor memory such as a DRAM and an SRAM, and is used as a work area of the processor 230. The embedded memory 220 stores firmware for managing the memory chip 100, and various types of management tables such as a shift table, a history table, and a flag table, which will be described later.

[0099] The ECC circuit 260 performs error detection and correction processes on data stored in the memory chip 100. That is, the ECC circuit 260 generates an error correction code and appends it to write data at the time of data writing, and decodes it at the time of data reading.

[0100] <1-1-3> Configuration of Memory Chip 100

[0101] Next, a configuration of the memory chip 100 will be described.

[0102] As shown in FIG. 1, the memory chip 100 includes a memory cell array 110, a row decoder 120, a driver circuit 130, a sense amplifier 140, an address register 150, a command register 160, and a sequencer 170.

[0103] The memory cell array 110 includes a plurality of blocks BLK each including a plurality of non-volatile memory cells respectively associated with rows (words lines) and columns (bit lines). FIG. 1 shows four blocks BLK0-BLK3 as an example. The memory cell array 110 stores data supplied from the controller 200.

[0104] The row decoder 120 selects one of the blocks BLK0 to BLK3 based on a block address BA in the address register 150, and selects a word line direction in the selected block BLK.

[0105] The driver circuit 130 supplies a voltage to the selected block BLK via the row decoder 120 based on a page address PA in the address register 150. The driver circuit 130 includes, for example, a source line driver, etc.

[0106] At the time of data reading, the sense amplifier 140, which includes sense amplifier modules SA provided for respective bit lines BL, senses data DAT read from the memory cell array 110, and performs a necessary computation thereon. The data DAT is then output to the controller 200. At the time of data writing, the sense amplifier 140 transfers write data DAT received from the controller 200 to the memory cell array 110.

[0107] The address register 150 stores an address ADD received from the controller 200. The address ADD includes the above-described block address BA and page address PA. The command register 160 stores a command CMD received from the controller 200.

[0108] The sequencer 170 controls the operation of the entire memory chip 100 based on the command CMD stored in the command register 160.

[0109] <1-1-4> Circuit Configuration of Memory Cell Array 110

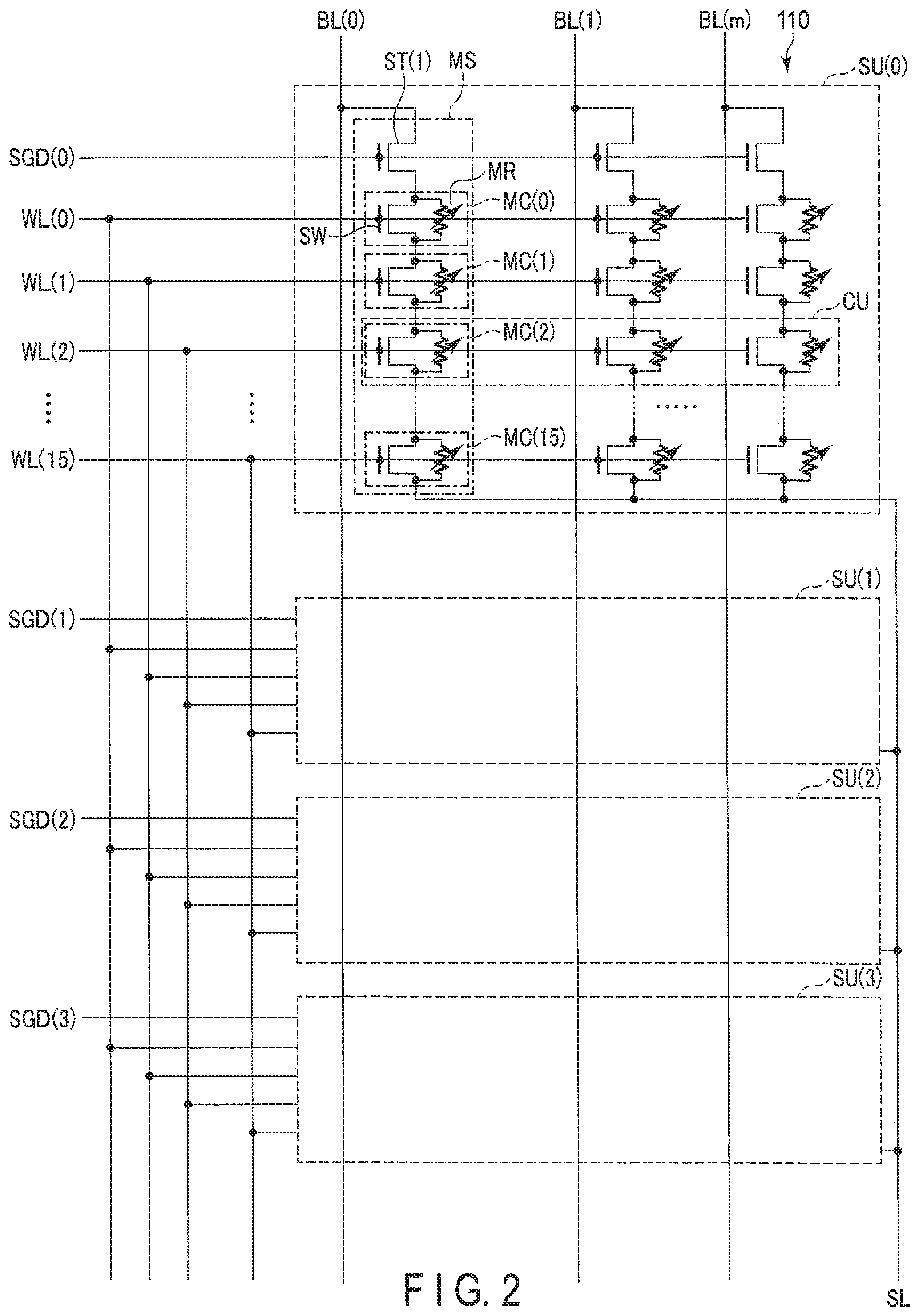

[0110] Next, a circuit (equivalent circuit) configuration of the memory cell array 110 will be described with reference to FIG. 2.

[0111] As shown in FIG. 2, each block BLK of the memory cell array 110 includes, for example, four string units SU (SU(0)-SU(3)). The number of string units SU in each block BLK may be designed to be any number. Each string unit SU includes a plurality of memory cell strings MS.

[0112] Each memory cell string MS includes, for example, 16 memory cells MC (MC(0) to MC(15)) and a select transistor ST(1). Hereinafter, when the memory cells MC(0) to MC(15) are not distinguished from one another, they will be referred to as "memory cells MC". The number of select transistors ST(1) included in each memory cell string MS may be designed to be any number greater than one.

[0113] Each memory cell MC includes a memory element (variable resistance memory region/variable resistance layer/variable resistance element) MR and a selector SW. Examples of the memory element MR include an alloy-based phase-change element (Ge.sub.2Sb.sub.2Te.sub.5). The memory element MR according to the present embodiment takes either a low resistance state or a high resistance state according to a change in crystallization state. Hereinafter, a change in the crystallization state of the memory element MR will be referred to as a "phase change", a low resistance state (LRS) of the memory element MR will be referred to as a "set state", and a high resistance state (HRS) of the memory element MR will be referred to as a "reset state". In the present embodiment, the selector SW includes a semiconductor layer, a gate insulating film, and a gate electrode. In the memory cell MC, the memory element MR and the selector SW are coupled in parallel. Also, the number of memory cells MC included in each memory cell string MS is not limited to a particular number, and may be 8, 32, 48, 64, 96, 128, etc.

[0114] When the memory cell MC is not selected, the selector SW is switched to an on state (a conductive state). When the selector SW is in the on state, as shown in FIG. 3, an inversion layer is formed in the semiconductor layer of the selector SW, and a current flows through the inversion layer. A resistance value of the memory element MR in the low resistance state is 10 times (an order of magnitude) or more higher than a resistance value of the semiconductor layer of the selector SW in the on state. This prevents a current to flow through the memory element MR that is coupled in parallel. It is a memory element MR that stores data in a memory cell MC. Thus, if a current does not flow through the memory element MR, it means that the memory cell is not selected.

[0115] When the memory cell MC is selected, the selector SW is switched to an off state (non-conductive state). When the selector SW is in the off state, as shown in FIG. 4, an inversion layer is not formed in the semiconductor layer of the selector SW. A resistance value of the memory element MR in the high resistance state is 10 times (an order of magnitude) or more lower than a resistance value of the semiconductor layer of the selector SW in the off state. This prevents a current to flow through the semiconductor layer, and flows through the memory element MR that is coupled in parallel. If a current flows through the memory element MR, it means that the memory cell is selected.

[0116] Referring back to FIG. 2, a further description will be given of the memory cell array 110. The memory cells MC(0) to MC(15) included in each memory cell string MS are coupled in series between the select transistor ST(1) and a source line SL. Control gates of the memory cells MC(0) of a plurality of memory cell strings MS included in the same block BLK are commonly coupled to a word line WL(0). Similarly, control gates of the memory cells MC(1) to MC(15) of a plurality of memory cell strings MS included in the same block BLK are commonly coupled to word lines WL(1) to WL(15).

[0117] Hereinafter, when word lines WL(0) to (15) are not distinguished from one another, they will be referred to as "word lines WL".

[0118] In the description that follows, a group of memory cells MC that are coupled to a common word line WL in each string unit SU will be referred to as a "cell unit (CU)". Also, a set of 1-bit data items stored in a cell unit will be referred to as a "page". Accordingly, when two-bit data is stored in a single memory cell MC, the cell unit stores two pages of data.

[0119] Gates of select transistors ST(1) in each string unit SU are commonly coupled to a select gate line SGD. More specifically, gates of select transistors ST(1) in a string unit SU(0) are commonly coupled to a select gate line SGD(0). Similarly, gates of select transistors ST(1) in a string unit SU(1) are commonly coupled to a select gate line SGD(1). The same is true of string units SU(2) and SU(3).

[0120] Hereinafter, when select gate lines SGD (SGD(0), SGD(1), . . . ) are not distinguished from one another, they will be referred to as "select gate lines SGD".

[0121] Both the select gate lines SGD and the word lines WL are independently controlled by the row decoder 120.

[0122] Drains of select transistors ST(1) of memory cell strings MS in the same column in the memory cell array 110 are commonly coupled to a bit line BL (BL(0) to BL(m), where m is a natural number equal to or greater than 1). That is, the bit line BL commonly couples memory cell strings MS of different blocks BLK. In addition, sources of memory cells MC(15) are commonly coupled to the source line SL.

[0123] That is, each string unit SU includes a plurality of memory cell strings MS that are coupled to different bit lines BL and coupled to the same select gate line SGD. Each block BLK includes a plurality of string units SU that share the same word line WL. The memory cell array 110 includes a plurality of blocks BLK that share the same bit line BL.

[0124] <1-1-5> Structure of Memory Cell Array 110

[0125] Hereinafter, an example structure of the memory cell array 110 according to the first embodiment will be described. In the drawings to which reference will be made below, an "X direction" refers to a direction in which the bit lines BL extend, a "Y direction" corresponds to a direction in which the word lines WL extend, and a "Z direction" corresponds to a direction vertical to a surface of the semiconductor substrate 20 on which the memory cell array 110 is formed. In the drawings, components such as insulating layers (interlayer insulating films), interconnects, contact plugs, etc. are suitably omitted for ease of reference.

[0126] FIG. 5 shows an example of a cross-sectional structure of the memory cell array 110 included in the memory chip 100 according to the first embodiment. As shown in FIG. 5, the memory cell array 110 includes, for example, conductive layers 21 to 24. The conductive layers 21 to 24 are provided above the semiconductor substrate 20.

[0127] Specifically, a conductive layer (voltage application electrode) 21 is provided above a semiconductor substrate 20, with an insulating layer interposed therebetween, as viewed in the Z direction. A circuit such as a sense amplifier 140 may be provided, for example, in the insulating layer between the semiconductor substrate 20 and the conductive layer 21. The conductive layer 21 is formed, for example, in a plate shape extending along the XY plane, and is used as a source line SL. The conductive layer 21 contains, for example, silicon (Si).

[0128] Insulating layers and conductive layers (voltage application electrode) 22 are alternately stacked above the conductive layer 21 as viewed in the Z direction. The conductive layers 22 are formed, for example, in a plate shape extending along the XY plane. The stacked conductive layers 22 are respectively used as, in the order from the side of the semiconductor substrate 20, word lines WL(15) to WL(0). The conductive layers 22 contain, for example, tungsten (W).

[0129] Conductive layers (voltage application electrode) 23, for example, are provided above the topmost conductive layer 22 (WL(0)), with an insulating layer interposed therebetween, as viewed in the Z direction. The conductive layers 23 extend along the Y direction, and are divided by select pillars SP (to be described later) in the X direction. The conductive layers 23 are respectively used as select gate lines SGD(0) to (3). The conductive layers 23 contain, for example, tungsten (W).

[0130] A plurality of conductive layers (voltage application electrodes) 24 are formed above the conductive layers 23 as viewed in the Z direction. The conductive layers 24 are formed, for example, in a line shape extending along the X direction, and are used as bit lines BL. The conductive layers 24 contain, for example, copper (Cu).

[0131] A memory pillar MP is in a columnar shape that extends along the Z direction, penetrates the conductive layers 22, and reaches, at its bottom portion, the conductive layer 21. A memory pillar MP includes, for example, a core member 30, a variable resistance layer 31, a semiconductor layer 32, and an insulating layer 33. Specifically, a memory hole MH that penetrates the stacked structure of the conductive layers 22 and insulating layers and reaches, at its bottom portion, the conductive layer 21 is provided. The memory hole MH is, for example, in a cylindrical form extending along the Z direction. Through the sequential formation of the insulating layer 33, the semiconductor layer 32, the variable resistance layer 31, and the core member 30 inside (on an inner wall of) the memory hole MH, a memory pillar MP is configured. Specifically, a memory pillar MP includes a cylindrical insulating layer 33 which covers the inner wall of the memory hole MH and extends along the Z direction, a cylindrical semiconductor layer 32 which covers an inner wall of the insulating layer 33 and extends along the Z direction, and a cylindrical or columnar-shaped variable resistance memory region 31 which covers an inner wall of the semiconductor layer 32 and extends along the Z direction.

[0132] A columnar-shaped select pillar SP that penetrates the conductive layers 23 is formed on the memory pillar MP. The select pillar SP includes, for example, the semiconductor layer 32 and the insulating layer 33. Specifically, a select pillar SP is configured by providing an SGD hole SH that penetrates the conductive layers 23 and reaches, at its bottom portion, the memory pillar MP, and sequentially forming an insulating layer 33 and a semiconductor layer 32 inside the SGD hole SH.

[0133] A layer including an interface between the memory hole MH and the SGD hole SH is included in a layer between the topmost conductive layer 22 and the conductive layers 23.

[0134] The core member 30 contains, for example, an insulator such as a silicon nitride (SiN). The core member 30 is, for example, in a columnar shape that extends along the Z direction.

[0135] The variable resistance layer 31 covers a side surface (outer periphery) of the core member 30 (is in contact with the core member 30). The variable resistance layer 31 is, for example, formed in a cylindrical shape that extends along the Z direction. A bottom portion of the variable resistance layer 31 is, for example, in contact with the conductive layer 21.

[0136] The semiconductor layer 32 in the memory pillar MP covers a side surface (outer periphery) of the variable resistance layer 31 (is in contact with the variable resistance layer 31). The semiconductor layer 32 in the memory pillar MP is, for example, formed in a cylindrical shape extending along the Z direction. The bottom portion of the semiconductor layer 32 is, for example, in contact with the conductive layer 21.

[0137] The semiconductor layer 32 in the select pillar SP is, for example, in a columnar shape. The bottom of the semiconductor layer 32 of the select pillar SP is in contact with the semiconductor layer 32 of the memory pillar MP, the variable resistance layer 31, and the core member 30.

[0138] The insulating layer 33 covers a side surface of the semiconductor layer 32. The insulating layer 33 includes, for example, a portion that is formed in a cylindrical shape. The insulating layer 33 includes an insulator such as silicon oxide (SiO.sub.2).

[0139] The conductive layer 22 covers part of a side surface of the insulating layer 33 in the memory pillar MP (namely, is in contact with the insulating layer 33).

[0140] The conductive layer 23 covers part of a side surface of the insulating layer 33 in the select pillar SP (namely, is in contact with the insulating layer 33).

[0141] Next, a cross-sectional view of the conductive layers 23 with reference to FIG. 6 will be described. FIG. 6 is a cross-sectional view taken along line A-A of FIG. 5.

[0142] As shown in FIG. 6, an insulating layer 33 and a semiconductor layer 32 are formed in an SGD hole SH that penetrates the conductive layer 23. The conductive layers 23 function as select gate lines SGD(0) to SGD(3) of the select transistors ST(1), the insulating layer 33 functions as a gate insulating film of the select transistor ST(1), and the semiconductor layer 32 functions as a semiconductor layer of the select transistor ST(1). Through the use of the select transistor ST(1), it is possible to select memory pillars MP for each word line. When the select transistor ST(1) is switched on, an inversion layer is formed in the semiconductor layer 32 that is in contact with the variable resistance layer 31 of the memory pillar MP, and the memory pillar MP can be selected by letting a current flow through the inversion layer.

[0143] Next, a cross-sectional view of portions between the memory cells MC in the Z direction will be described with reference to FIG. 7. FIG. 7 is a cross-sectional view taken along line B-B of FIG. 5. The core member 30, the variable resistance layer 31, the semiconductor layer 32, and the insulating layer 33 shown in FIG. 7 correspond to portions between the memory cells MC in the Z direction, and a current flows through the semiconductor layer 32.

[0144] Next, a cross-sectional view of the conductive layers 22 will be described with reference to FIGS. 8 and 9. FIG. 8 is a cross-sectional view taken along line C-C of FIG. 5. FIG. 9 is a cross-sectional view in which a single memory cell MC is extracted.

[0145] As shown in FIG. 9, a memory cell MC is provided at an intersection between a plate-shaped word line WL and a memory pillar MP. Specifically, an insulating layer 33, a semiconductor layer 32, a variable resistance layer 31, and a core member 30 are provided in a memory hole MH that penetrates the conductive layers 22, as shown in FIG. 9. The conductive layer 22 functions as a word line WL of a selector SW of a memory cell MC, the insulating layer 33 functions as a gate insulating film of the selector SW of the memory cell MC, and the semiconductor layer 32 functions as a semiconductor layer of the selector SW of the memory cell MC. The variable resistance layer 31 functions as a memory element MR of the memory cell MC.

[0146] Next, a cross-sectional view of the conductive layer 21 will be described with reference to FIG. 10. FIG. 10 is a cross-sectional view taken along line D-D of FIG. 5.

[0147] The conductive layer 21 is in a plate shape, and is set to a constant low voltage to let a current flow therethrough from the bit line BL. As shown in FIG. 10, the conductive layer 21 (source line) is in a plate shape, similarly to the conductive layer 22 (word line).

[0148] Next, an example of a cross-sectional structure of the memory cell array 110 will be described with reference to FIG. 11. FIG. 11 is a cross-sectional view taken along line E-E of FIG. 5. FIG. 11 shows a cross-sectional view along a direction orthogonal to the cross section shown in FIG. 5. Referring to FIGS. 5 and 11 in combination, it can be seen that the memory pillar MP is in a concentric shape about the core member 30.

[0149] <1-2> Operation

[0150] <1-2-1> Overview

[0151] Next, an overview of an operation of the memory chip 100 according to the present embodiment will be described.

[0152] Read and write operations in the memory chip 100 according to the present embodiment are performed by letting a current flow between the bit line BL and the source line SL.

[0153] A brief description will be given of a method of selecting a memory cell MC with reference to FIGS. 12 and 13. FIG. 12 is a circuit diagram in which a single memory cell string MS is extracted. FIG. 13 is a cross-sectional view in which a memory pillar MP corresponding to a single memory cell string MS is extracted.

[0154] As shown in FIGS. 12 and 13, a predetermined voltage (positive voltage) is applied to a select gate line SGD of a select transistor ST(1) that is in contact with a memory pillar MP to which a memory cell MC (e.g., MC(2)) to be selected belongs. Thereby, an inversion layer is formed in a semiconductor layer of the select transistor ST(1), allowing a current to flow therethrough (the select transistor ST(1) is switched on). This causes the bit line BL, the select transistor ST(1), and the semiconductor layer of the memory pillar MP that is in contact with the select transistor ST(1) to be brought into conduction. Also, a word line WL(2) corresponding to the select memory cell MC(2) is brought to 0[V], and word lines WL(0), (1), and (3) to (15) corresponding to the non-selected memory cells MC are applied with a predetermined voltage (positive voltage). Thereby, a current path between the bit line BL and the source line SL flows through a variable resistance layer MR in the memory cell MC(2) to be selected, and flows through semiconductor layers of selectors SW in the non-selected memory cells MC(0), (1) and (3) to (15). Since a core member 30, which is an insulating layer, is provided at a central portion of the memory pillar MP, as shown in FIG. 13, a current flows through the variable resistance layer 31 that surrounds the core member 30 in the selected memory cell MC. Examples of the material of the variable resistance layer 31 include an alloy-based phase-change element (Ge.sub.2Sb.sub.2Te.sub.5).

[0155] With the above-described configuration, it is possible to select a variable resistance layer both in a read operation and a write operation. When the present scheme is compared with a three-dimensional NAND-type flash memory, it has the advantages that it can operate at a lower voltage and at a higher speed, that there are less restrictions on the number of times of rewriting, and that the writing time is shorter.

[0156] In addition, unlike the vertical chain-cell-type PCM in the publicly-known non-patent document (`Scalable 3-D vertical chain-cell-type phase-change memory with 4F.sup.2 poly-Si diodes`, M. Kinoshita, et. al., HITACHI Sympo. on VLSI Tech. 2012, pp. 35-36), a diode need not be provided as a select element below a memory pillar MP. This is advantageous in terms of the reduced time for development, simplified processing, and the reduced manufacturing cost.

[0157] The present embodiment relates to a variable resistance memory in which an erase operation does not exist, unlike a three-dimensional NAND-type flash memory.

[0158] Also, a write operation or a read operation is performed by letting a current flow between a bit line BL and a source line SL by turning on the select transistor ST(1). This eliminates the necessity to select all the memory cell strings MS, allowing selection to be performed for any bit line (column) that is coupled to a single select gate line.

[0159] To prevent a write operation or a read operation from being performed in a certain memory cell string MS, the voltage of the source line should be set to be equal to the voltage of the bit line; in this case, a write operation or a read operation will not be performed.

[0160] In addition, unlike a three-dimensional NAND-type flash memory, an erase operation need not be performed in units of blocks BLK, and a write operation can be set/reset in units of select transistors ST(1).

[0161] A word line serves the role of selecting a memory cell MC in the stacking direction (Z direction). Accordingly, a word line may be shared among gate electrodes of a plurality of memory cells MC in the same XY plane. Similarly, a source line may be shared among a plurality of memory cell string MS. In particular, a source line may be shared among a plurality of memory cell strings MS that are adjacent to each other in the bit line direction.

[0162] Let us assume, for example, that the word line WL and the source line SL are in a plate shape extending along both the bit line direction and the word line direction. Selection of the memory cell MC need to be performed by switching the select transistor ST(1) to the on state and then letting a current flow from the bit line BL to the source line SL. Accordingly, even if the word line WL and the source line SL are selected in a plate shape, only the selected select transistor ST(1) and the memory cell MC that is in contact with the selected word line WL directly below the selected bit line BL are selected.

[0163] As described above, selection of the memory cell MC is performed by letting a current flow via the bit line BL. Accordingly, the sequencer 170 is configured to output a control signal in such a manner, for example, that a read operation and a write operation are simultaneously performed for each bit line.

[0164] The sequencer 170 is capable of outputting a control signal in such a manner that a reset write operation and a set write operation are performed for each bit line.

[0165] <1-2-2> Waveform

[0166] As described above, in the memory chip 100 according to the present embodiment, a voltage that causes the selector SW of the selected memory cell MC to be turned off and a voltage causes the selector SW of the non-selected memory cell MC to be turned on are applied to the word lines WL, respectively. Subsequently, in the memory chip 100, a voltage that causes a select transistor corresponding to the selected memory cell to be turned on is applied to the select gate line SGD, thus bringing the bit line BL and the memory pillar MP to which the select memory cell belongs into conduction. In this manner, a current flows through a semiconductor layer of a selector SW in a non-selected memory cell, and flows through a memory element MR in a selected memory cell.

[0167] A description will be given of an operation waveform of the memory chip 100 according to the present embodiment, with reference to FIG. 14. FIG. 14 shows a timing chart of an operation waveform.

[0168] First, a case of a read operation will be described. At time T0, the sequencer 170 maintains the voltage of the non-selected bit line BL (BL(Non-selected)) and the source line SL at an L level. The sequencer 170 maintains the voltage of the non-selected word line WL (WL(Non-selected)) at H level (L<H). The sequencer 170 causes the voltage of the selected word line WL (WL(Selected) to fall from an H level to L level. At time T1 and thereafter, the sequencer 170 maintains the voltage of the selected word line WL at the L level.

[0169] At time T1, the sequencer 170 increases the voltage of the select gate line SGD of a select transistor corresponding to the selected memory cell MC from the L level to the H level. Since the voltage of the non-selected word line WL is maintained at the H level, the selector SW in the non-selected memory cell MC is maintained in the on state.

[0170] The sequencer 170 applies the read voltage Vread to the bit line BL (BL(Read target)), and then brings the bit line BL to a floating state. Thereby, the voltage of the bit line BL gradually falls (the voltage is substantially maintained until time T3) when the selected memory cell MC is in the high-resistance (reset) state, and the voltage of the bit line BL rapidly falls when the selected memory cell MC is in the low-resistance (set) state. By causing the sense amplifier 140 to sense the H/L level of the voltage of the bit line BL after a predetermined period of time has passed since a voltage is applied to the bit line BL, a read operation is performed.

[0171] Next, a case of a write operation will be described. At time T0, an operation similar to a read operation is performed.

[0172] In a write operation, the sequencer 170 applies a write pulse (voltage) Vwrite to the bit line BL (BL(Write target)) at time T1, and causes the voltage to rapidly fall at time T2, thereby performing a write operation in the high-resistance reset state. When the sequencer 170 applies a write pulse (voltage) Vwrite to the bit line BL at time T1 and causes the voltage to gradually fall at time T2, a write operation is performed in the low-resistance set state. At this time, it is important to keep the voltage of the non-selected bit line BL equal to the voltage of the source line SL (e.g., at the L level). A memory cell MC is selected by application of a voltage to a bit line BL. If the voltage of a non-selected bit line BL is increased, the selection would be erroneous, resulting in erroneous writing. A voltage should be selectively applied only to a bit line BL to be read or written.

[0173] <1-2-3> Memory Cell Selection Method

[0174] Next, a memory cell selection method that is applicable to the present embodiment will be described.

[0175] FIG. 15 shows a relationship among selected memory cells MC, a selected word line WL, bit lines BL, and a sense amplifier 140 in a first example of a memory cell selection method according to the present embodiment. Of a plurality of word lines WL, only the selected word line WL is shown for the sake of simplicity.

[0176] As shown in FIG. 15, by selecting one of word lines WL, all the corresponding memory cells MC are selected, and the voltages of the bit lines BL are sensed as signals by the sense amplifier modules SA that are provided for the respective bit lines BL. The sense amplifier modules SA are included in the sense amplifier 140.

[0177] FIG. 16 shows a relationship among a selected memory cell MC, a selected word line WL, bit lines BL, and a sense amplifier 140 according to a comparative example of the memory cell selection method. Of a plurality of word lines WL, only the selected word line WL is shown for the sake of simplicity.

[0178] The sense amplifier 140 shown in FIG. 16 includes an MUX coupled to a plurality of bit lines BL, and a sense amplifier module SA coupled to the MUX.

[0179] As shown in FIG. 16, by selecting a single word line WL and a single bit line BL, a memory cell MC at the intersection is selected, and the MUX receives the voltages of the bit line BL as signal, and transfers the signal to the sense amplifier module SA. Such a configuration is referred to as a "cross-point" type.

[0180] FIG. 17 shows a relationship among selected memory cells MC, a selected word line WL, bit lines BL, and a sense amplifier 140 in a third example of a memory cell selection method according to the present embodiment. Of a plurality of word lines WL, only the selected word line WL is shown for the sake of simplicity.

[0181] The sense amplifier 140 shown in FIG. 17 includes a plurality of sets of MUX and sense amplifier module SA, with each MUX coupled to a plurality of bit lines BL, and each sense amplifier SA coupled to the corresponding MUX.

[0182] As shown in FIG. 17, by selecting a single word line WL and causing a given number of selected bit lines BL to operate, memory cells MC are selected.

[0183] In a variable resistance memory, when a voltage and a current are applied to a bit line BL, a memory cell that belongs to the bit line BL is selected. Accordingly, only a bit line BL corresponding to a memory cell MC that is to be a target of a read operation or a write operation is driven.

[0184] It is also possible to simultaneously perform a read operation and a write operation for each bit line BL, and to simultaneously perform a reset write operation and a set write operation for each bit line BL.

[0185] This is a difference from the cross point type described with reference to FIG. 16.

[0186] It is possible, for example, to simultaneously perform a read operation and a write operation on a single bit line BL, in units of four bit lines BL, as shown in FIG. 17. In this case, the sense amplifier module SA can be shared among the four bit lines BL, and the selected bit line BL can be selected by the MUX.

[0187] Specifically, in the configuration shown in FIG. 17, a read operation is performed on a memory cell MC that belongs to a bit line BL(1), and a write operation can be simultaneously performed on a memory cell MC that belongs to a bit line BL(5).

[0188] <1-3> Advantageous Effects

[0189] According to the above-described embodiment, the memory chip 100 is configured in such a manner that a memory element capable of setting a data value of one or more bits according to a resistance value is disposed at the center of a memory pillar MP, with the periphery of the memory element covered with a semiconductor layer, and the periphery thereof further covered with an insulating layer and a word line, and the memory element is, at its upper end, coupled to a bit line via a select transistor, and is, at its lower end, coupled to a source line without intervention of a select transistor.

[0190] Bit-cost scalable (BiCS.TM.) flash memories have been proposed and commercialized as non-volatile memories (three-dimensional NAND-type flash memories) in which memory cells are perpendicularly stacked on a semiconductor substrate for high integration. In such a three-dimensional NAND-type flash memory, NAND-type flash memories with a planar structure (two-dimensional NAND-type flash memories) are three-dimensionally arranged. Similarly to a two-dimensional NAND-type flash memory, a three-dimensional NAND-type flash memory has problems such as the constraints on the number of times of rewriting and the length of time required for programming.

[0191] Memory cells of a three-dimensional NAND-type flash memory contain silicon and an oxide-nitride-oxide (ONO) film. In a three-dimensional NAND-type flash memory, when a voltage is applied to a word line WL, electrons are trapped in SiN, corresponding to "N" of the ONO film of the memory cell via the silicon of the memory cell. Thereby, the threshold value of the memory cell is shifted, and information is stored in the memory cell.

[0192] On the other hand, as an example of a three-dimensional phase-change memory (PCM), a vertical chain-cell-type PCM has been proposed (see the above-described non-patent document). In this example, a channel of a transistor is formed so as to cover a pillar of a PCM layer. Selection of a memory cell is performed by applying a voltage to a selected bit line, and applying voltages Vreset, Vset, and Vread to a selected word line.

[0193] When a gate of the selected memory cell is turned off and a gate of a non-selected memory cell is turned on, a current flows through a PCM layer in the selected memory cell, and a current flows through silicon in the non-selected memory cell.

[0194] Problems with this example are that, since a diode for selection (select transistor) is provided below a pillar, it is necessary to develop such a diode, and to perform separate processes for the diode and layers above the diode. In addition, a problem arises that only a memory cell at the intersection of a word line and a bit line can be selected. The first publicly-known example of an equivalent circuit that configures a chain-type memory cell string in which a plurality of memory cells each including a variable resistance element and a select transistor coupled in parallel are coupled in series, and a block select transistor is coupled to one end of the series of memory cells is disclosed in Patent Document (U.S. Pat. No. 5,894,447) filed in 1997, However, three-dimensional examples were not proposed.

[0195] Moreover, an example of a chain PCM has been proposed, as disclosed in Patent Document 2 (U.S. Pat. No. 9,025,369); however, there is a problem that a three-dimensional structure for high integration is not proposed.

[0196] Furthermore, a patent has been proposed in which right and left current paths are separately provided in the above-described vertical chain-cell-type PCM structure, with a block select transistor coupled to its upper portion, to double the integration, as disclosed in Patent Document 3 (U.S. Pat. No. 9,966,136); however, since a diode needs to be provided as a select element below a pillar, there are still problems of the necessity to develop such a diode and the necessity to perform separate processes for the diode and layers above the diode.

[0197] As described above, the memory cell array 110 according to the present embodiment is configured in such a manner that an ONO film portion of a memory pillar in a three-dimensional NAND-type flash memory is replaced with an oxide film, and a variable resistance layer is provided inside the oxide film. In addition, unlike the example disclosed in the non-patent document, a diode for selection (select transistor between a source line and a memory cell) is not provided.

[0198] It is thereby possible to solve the above-described problems and to achieve reduction in the time required for development and facilitation of the processing. When a voltage is applied to a bit line with a select transistor and a word line selected, a given number of memory cells at the intersection of the select transistor and the bit line are automatically selected. Accordingly, a given operation can be performed on memory cells of a select transistor of a given bit line simultaneously. In the above-described non-patent document, the cross-point type ReRAM, etc., there is a problem of a voltage drop in the X and Y directions. However, since a source line is shared among memory cells of a plurality of word lines and bit lines, a voltage drop in the source line caused by the current can be greatly reduced.

[0199] As described above, according to the present embodiment, it is possible to obtain a three-dimensional variable resistance memory at the lowest possible cost with the highest possible integration, by omitting, in particular, a diode that is provided as a select element.

[0200] <1-4> First Modification

[0201] <1-4-1> Outline

[0202] Next, a first modification of the first embodiment will be described. In the above-described embodiment, a conductive layer is disposed as a source line in parallel with a semiconductor substrate. In the first modification according to the first embodiment, a semiconductor layer (P-well region) is provided as a conductive layer corresponding to a source line, and a select transistor ST(2) is provided between the source line and memory cells.

[0203] <1-4-2> Circuit Configuration of Memory Cell Array 110

[0204] A circuit configuration (equivalent circuit) of a memory cell array 110 according to a first modification of the first embodiment will be described with reference to FIG. 18.

[0205] As shown in FIG. 18, each of a plurality of memory cell strings MS further includes, for example, a select transistor ST(2), in addition to 16 memory cells MC (MC(0) to MC(15)) and a select transistor ST(1), compared with the circuit shown in FIG. 2.

[0206] In the example of FIG. 18, a memory element MR coupled in parallel with the select transistor ST(1) may be provided. Alternatively, a memory element MR coupled in parallel with the select transistor ST(2) may be omitted.

[0207] The memory cells MC(0) to MC(15) included in each memory cell string MS are coupled in series between the select transistor ST(1) and the select transistor ST(2).

[0208] Gates of select transistors ST(2) in each block BLK are coupled in common to a select gate line SGS. The select gate line SGS may be provided for each string unit SU.

[0209] Hereinafter, when select gate lines SGD (SGD(0), SGD(1), . . . ) are not distinguished from one another, they will be referred to as "select gate lines SGD".

[0210] Both the select gate lines SGD and SGS and the word lines WL are independently controlled by the row decoder 120.

[0211] In the memory cell string MS, Drain of select transistor ST(2) is coupled to a source of a memory cell MC(15). Sources of the select transistors ST(2) in the memory cell array 110 are commonly coupled to the source line SL.

[0212] By bringing the select gate line SGS of the select transistor ST(2) to the H level, an inversion layer is formed in the semiconductor layer of the select transistor ST(2) and the semiconductor substrate, allowing a current to flow through the source line SL.

[0213] <1-4-3> Structure of Memory Cell Array 110

[0214] Hereinafter, an example structure of the memory cell array 110 according to the first modification of the first embodiment will be described. In the first modification of the first embodiment, a select transistor ST(2) is provided on a semiconductor substrate. When the select transistor ST(2) is turned on, an inversion layer is formed in a P-well region of the semiconductor substrate, and a current flows through a source line via an N-type diffusion layer provided in the semiconductor substrate.

[0215] FIG. 19 shows an example of a cross-sectional structure of the memory cell array 110 included in the memory chip 100 according to the first modification of the first embodiment. Specifically, a P-well region 41 is provided in a surface region of the semiconductor substrate 40, and an N-type diffusion layer (N.sup.+ diffusion layer) 42 is provided in the P-well region 41, as shown in FIG. 19. The semiconductor substrate 40 is, for example, formed in a plate shape extending along the XY plane, and contains silicon (Si).

[0216] On the P-well region 41, a conductive layer (voltage application electrode) 25 is provided, with an insulating layer 33 interposed therebetween. The conductive layer 25 is, for example, formed in a plate shape extending along the XY plane, and functions as a select gate line SGS. The conductive layer 25 contains, for example, tungsten (W).

[0217] On the N-type diffusion layer 42, a conductive layer 26 is provided. The conductive layer 26 is, for example, formed in a plate shape extending along the ZY plane, and functions as a source line SL. The conductive layer 26 contains, for example, tungsten (W).

[0218] The select transistor ST(2) includes a conductive layer 25, a semiconductor layer 32, and a P-well region 41. When the conductive layer 25 is brought to an H level, an inversion layer is formed in the semiconductor layer 32 and the P-well region 41, allowing a current to flow therethrough.

[0219] Insulating layers and conductive layers 22 are alternately stacked above the conductive layer 25. The conductive layers 22 are formed, for example, in a plate shape extending along the XY plane. The conductive layers 22 are respectively used as, in the order from the side of the semiconductor substrate 40, word lines WL(15) to WL(0). The conductive layers 22 contain, for example, tungsten (W).

[0220] Conductive layers 23, for example, are provided above the topmost conductive layer 22 (WL(0)), with an insulating layer interposed therebetween. The conductive layers 23 extend along the Y direction, and are divided by select pillars SP (to be described later) in the X direction. The conductive layers 23 are respectively used as select gate lines SGD(0) to SGD(3). The conductive layers 23 contain, for example, tungsten (W).

[0221] Conductive layers 24 are provided above the conductive layers 23. The conductive layers 24 are formed, for example, in a line shape extending along the X direction, and are used as bit lines BL. The conductive layers 24 contain, for example, copper (Cu).

[0222] Next, a cross-sectional view of the conductive layers 23 will be described with reference to FIG. 20. FIG. 20 is a cross-sectional view taken along line A1-A1 of FIG. 19. As shown in FIG. 20, a current that is collected into the diffusion layer in the P-well region 41 is collected into a plate-shaped source line SL, flows up to the topmost layer, and then flows to a source line driver (not illustrated).

[0223] Next, a cross-sectional view of portions between the memory cells MC in the Z direction will be described with reference to FIG. 21. FIG. 21 is a cross-sectional view taken along line B1-B1 of FIG. 19. FIG. 21 shows memory pillars of portions between memory cells MC, which configuration is different from that of the first embodiment in that a plate-shaped source line SL that is orthogonal to the semiconductor substrate 40 is provided. The source line SL shown in FIG. 21 is a midway path that allows the current collected by the diffusion layer in the P-well region 41 to flow up to upper layers.

[0224] Next, a cross-sectional view of the conductive layers 22 will be described with reference to FIG. 22. FIG. 22 is a cross-sectional view taken along line C1-C1 of FIG. 19. The configuration of FIG. 22 is different from that of the first embodiment in that a plate-shaped source line that is orthogonal to the semiconductor substrate 40 is provided. The source line SL shown in FIG. 22 is a midway path that allows the current collected by the diffusion layer in the P-well region 41 to flow up to upper layers.

[0225] Next, a cross-sectional view of the P-well region 41 will be described with reference to FIG. 23. FIG. 23 is a cross-sectional view taken along line D1-D1 of FIG. 19. As shown in FIG. 23, a current that flows down from the bit line BL through the memory pillar MP reaches the P-well region 41, and then flows through an inversion layer which is formed in the P-well region 41 by the select transistor ST(2) in the on state, and reaches the diffusion layer 42. Thereafter, the current enters the source line SL, flows to the top, and then flows to a source line driver (not illustrated).

[0226] Next, an example of a cross-sectional structure of the memory cell array 110 will be described with reference to FIG. 24. FIG. 24 is a cross-sectional view taken along line E1-E1 of FIG. 19. FIG. 24 shows a cross-sectional view along a direction orthogonal to the cross section shown in FIG. 19. Referring to FIGS. 24 and 19 in combination, it can be seen that the memory pillar MP is in a concentric shape about the core member 30.

[0227] An advantageous effect of the first modification of the first embodiment, compared with the first embodiment, is that the processing can be facilitated by omitting a step of providing a conductive layer as a source line SL in the bottommost layer, and by forming the select gate lines SGS in the bottommost layer in the same step as the step of forming the word lines WL.

[0228] <1-4-4> Operation

[0229] Next, an outline of the operation of the memory chip 100 according to the first modification of the first embodiment will be described.

[0230] In the memory chip 100 according to the first modification of the first embodiment, read and write operations are performed by letting a current flow between the bit line BL and the source line SL.

[0231] A brief description will be given of a method of selecting a memory cell MC that performs a read or write operation, with reference to FIGS. 25 and 26. FIG. 25 is a circuit diagram in which a single memory cell string MS is extracted. FIG. 26 is a cross-sectional view in which a memory pillar MP corresponding to a single memory cell string MS is extracted.

[0232] As shown in FIGS. 25 and 26, a predetermined voltage (positive voltage) is applied to a select gate line SGD of a select transistor ST(1) that is in contact with a memory pillar MP to which a memory cell MC (e.g., MC(2)) to be selected belongs. Thereby, an inversion layer is formed in a semiconductor layer of the select transistor ST(1), allowing a current to flow therethrough (the select transistor ST(1) is switched on). This causes the bit line BL, the select transistor ST(1), and the semiconductor layer of the memory pillar MP that is in contact with the select transistor ST(1) to be brought into conduction. Also, a word line WL(2) corresponding to the selected memory cell MC(2) is applied with 0 [V], and word lines WL(0), (1), and (3) to (15) corresponding to the non-selected memory cells MC are applied with a predetermined voltage (positive voltage). Thereby, a current path between the bit line BL and the source line SL flows through a variable resistance layer MR in the memory cell MC(2) to be selected, and flows through semiconductor layers of selectors SW in the non-selected memory cells MC(0), (1) and (3) to (15). Since a core member 30, which is an insulating layer, is provided at a central portion of the memory pillar MP, as shown in FIG. 26, a current flows through the variable resistance layer 31 that surrounds the core member 30 in the selected memory cell MC. Also, a predetermined voltage is applied to the select gate line SGS of the select transistor ST(2). Thereby, an inversion layer is formed in a semiconductor layer of the select transistor ST(2), allowing a current to flow therethrough (the select transistor ST(2) is switched on). This causes the bit line BL, the select transistor ST(1), the semiconductor layer of the memory pillar MP that is in contact with the select transistor ST(1), the select transistor ST(2), and the source line SL to be brought into conduction.

[0233] With the above-described configuration, it is possible to select a variable resistance layer both in a read operation and a write operation. When the present scheme is compared with a three-dimensional NAND-type flash memory, it has the advantages that it can operate at a lower voltage and at a higher speed, that there are less restrictions on the number of times of rewriting, and that the writing time is shorter.

[0234] <1-5> Second Modification

[0235] Next, a second modification of the first embodiment will be described. In the second modification of the first embodiment, another example of the memory cell MC will be described.

[0236] <1-5-1> Pattern 1

[0237] First, Pattern 1 of the second modification of the first embodiment will be described with reference to FIGS. 27 and 28. FIG. 27 is a cross-sectional view in which a single memory cell MC is extracted. FIG. 28 is a cross-sectional view in which a memory pillar MP corresponding to a single memory cell string MS is extracted.

[0238] As shown in FIGS. 27 and 28, in the memory cell MC, an insulating layer 33, a semiconductor layer 32, and a variable resistance layer 31 are provided in a memory hole MH that penetrates the conductive layers 22. The difference from the first embodiment is that a core member 30 is not provided in the memory pillar MP.

[0239] <1-5-2> Pattern 2

[0240] Next, Pattern 2 of the second modification of the first embodiment will be described with reference to FIG. 29. FIG. 29 is a cross-sectional view in which a single memory cell MC is extracted.

[0241] As shown in FIG. 29, in the memory cell MC, an insulating layer 33, a semiconductor layer 32, a variable resistance layer 31, and air 34 are provided in a memory hole MH that penetrates the conductive layers 22. The difference from the first embodiment is that the air 34 is provided in the memory pillar MP instead of the core member 30.

[0242] <1-5-3> Pattern 3

[0243] Next, Pattern 3 of the second modification of the first embodiment will be described with reference to FIG. 30. FIG. 30 is a cross-sectional view in which a single memory cell MC is extracted.

[0244] As shown in FIG. 30, in the memory cell MC, an insulating layer 33, a semiconductor layer 32, a variable resistance layer 31, and a silicon oxide film 35 are provided in a memory hole MH that penetrates the conductive layers 22. The difference from the first embodiment is that a silicon oxide film 35 is provided in the memory pillar MP instead of the core member 30.

[0245] <1-5-4> Pattern 4

[0246] Next, Pattern 4 of the second modification of the first embodiment will be described with reference to FIG. 31. FIG. 31 is a cross-sectional view in which a single memory cell MC is extracted.

[0247] As shown in FIG. 31, in the memory cell MC, an insulating layer 33, a semiconductor layer 32, a variable resistance layer 36, and an interlayer oxide film 37 are provided in a memory hole MH that penetrates the conductive layers 22. The variable resistance layer 36 includes a magnetic tunnel junction (MTJ) element (which may contain a CoFe alloy, an NiFe alloy, or the like), or a variable resistance film of TiO.sub.x, WO.sub.x, HfO.sub.x, TaO.sub.x, etc. that is used in a ReRAM.