Shallow Trench Isolation For Integrated Circuits

SINGH; Gulbagh ; et al.

U.S. patent application number 16/014103 was filed with the patent office on 2019-12-26 for shallow trench isolation for integrated circuits. This patent application is currently assigned to Taiwan Semiconductor Manufacturing Co., Ltd.. The applicant listed for this patent is Taiwan Semiconductor Manufacturing Co., Ltd.. Invention is credited to Hsin-Chi Chen, Kun-Tsang Chuang, Gulbagh SINGH.

| Application Number | 20190393078 16/014103 |

| Document ID | / |

| Family ID | 68806002 |

| Filed Date | 2019-12-26 |

View All Diagrams

| United States Patent Application | 20190393078 |

| Kind Code | A1 |

| SINGH; Gulbagh ; et al. | December 26, 2019 |

SHALLOW TRENCH ISOLATION FOR INTEGRATED CIRCUITS

Abstract

The present disclosure describes a fabrication method that can form air-gaps in shallow trench isolation structures (STI) structures. For example, the method includes patterning a semiconductor layer over a substrate to form semiconductor islands and oxidizing the sidewall surfaces of the semiconductor islands to form first liners on the sidewall surfaces. Further, the method includes depositing a second liner over the first liners and the substrate and depositing a first dielectric layer between the semiconductor islands. The second liner between the first dielectric layer and the first liners is removed to form openings between the first dielectric layer and the first liners. A second dielectric layer is deposited over the first dielectric layer to enclose the openings and form air-gaps between the first dielectric layer and the first liners so that the gaps are positioned along the first liners.

| Inventors: | SINGH; Gulbagh; (Hsinchu, TW) ; Chen; Hsin-Chi; (Tainan City, TW) ; Chuang; Kun-Tsang; (Miaoli County, TW) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Assignee: | Taiwan Semiconductor Manufacturing

Co., Ltd. Hsinchu TW |

||||||||||

| Family ID: | 68806002 | ||||||||||

| Appl. No.: | 16/014103 | ||||||||||

| Filed: | June 21, 2018 |

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 27/1203 20130101; H01L 21/76283 20130101; H01L 21/76205 20130101; H01L 21/76289 20130101; H01L 27/1211 20130101 |

| International Class: | H01L 21/762 20060101 H01L021/762; H01L 27/12 20060101 H01L027/12 |

Claims

1. A structure, comprising: semiconductor islands formed over a substrate; a liner disposed on each sidewall of the semiconductor islands; and an isolation structure disposed between the semiconductor islands and comprising an air-gap formed along each liner.

2. The structure of claim 1, further comprising: an insulator layer interposed between the substrate and the semiconductor islands.

3. The structure of claim 1, wherein the liners comprise a silicon oxide layer.

4. The structure of claim 1, wherein a top surface of the isolation structure is divot-free.

5. The structure of claim 1, wherein a top surface of the isolation structure comprises a divot above the air-gap.

6. The structure of claim 2, wherein the isolation structure comprises a silicon nitride layer and an oxide layer disposed thereon.

7. The structure of claim 6, wherein the silicon nitride layer is disposed between air-gaps formed along liners of adjacent semiconductor islands.

8. The structure of claim 1, wherein the air-gap has a width between about 10 nm and about 25 nm.

9. An integrated circuit (IC), comprising: an insulating layer; a semiconductor layer disposed on the insulating layer and comprising: semiconductor islands; a liner disposed on each sidewall of the semiconductor islands; an isolation structure between the semiconductor islands comprising: an oxide layer with an air-pocket disposed along the liner of each sidewall of the semiconductor islands; and a nitride layer disposed between the insulating layer and the oxide layer; and a field effect transistor formed on one or more of the semiconductor islands.

10. The IC of claim 9, wherein the liner comprises a silicon oxide layer.

11. The IC of claim 9, wherein the air-pocket is embedded in the oxide layer and has a width between about 10 nm and about 25 nm.

12. The IC of claim 9, wherein a top surface of the isolation structure is not coplanar with a top surface of the semiconductor islands.

13. The IC of claim 9, wherein the air-pocket comprises a cavity filled with a gas or a mixture of gases.

14. The IC of claim 9, wherein the air-pocket extends through the oxide layer to the insulating layer.

15. The IC of claim 9, wherein the semiconductor layer further comprising: an other isolation structure between two other semiconductor islands free from air-pockets.

16. A method, comprising: patterning a semiconductor layer over a substrate to form semiconductor islands; oxidizing sidewall surfaces of the semiconductor islands to form first liners on the sidewall surfaces; depositing a second liner over the first liners and the substrate; depositing a first dielectric layer between the semiconductor islands; removing the second liner between the first dielectric layer and the first liners to form openings between the first dielectric layer and the first liners; and depositing a second dielectric layer over the first dielectric layer to enclose the openings and form air-gaps between the first dielectric layer and the first liners, wherein the air-gaps are positioned along the first liners.

17. The method of claim 16, wherein a width of the air-gaps is based on a thickness of the second liner.

18. The method of claim 16, wherein removing the second liner comprises selectively wet etching the second liner.

19. The method of claim 16, further comprising: forming an insulator layer between the semiconductor layer and the substrate.

20. The method of claim 16, wherein the second liner comprises silicon nitride.

Description

BACKGROUND

[0001] The rapid growth in smartphones, tablet personal computers (PCs), and other mobile consumer applications has increased the demand for chips based on radio frequency (RF) semiconductor-on-insulator (SOI) technology, particularly for antenna interface components and RF front-end-module (FEM) components like RF switches and antenna tuners.

BRIEF DESCRIPTION OF THE DRAWINGS

[0002] Aspects of the present disclosure are best understood from the following detailed description when read with the accompanying figures. It is noted that, in accordance with common practice in the industry, various features are not drawn to scale. In fact, the dimensions of the various features may be arbitrarily increased or reduced for clarity of discussion.

[0003] FIG. 1 is a flow diagram of a fabrication method that describes the formation of air-gaps along the sidewall surfaces of isolation structures, in accordance with some embodiments.

[0004] FIG. 2 is a cross-sectional view of a semiconductor layer over a substrate, in accordance with some embodiments.

[0005] FIG. 3 is a cross-sectional view of a semiconductor layer over a substrate after the formation of a photoresist layer over the semiconductor layer, in accordance with some embodiments

[0006] FIG. 4 is a cross-sectional view of a semiconductor layer over a substrate after the formation of patterned photoresist structures over the semiconductor layer, in accordance with some embodiments.

[0007] FIG. 5 is a cross-sectional view of semiconductor structures over a substrate, in accordance with some embodiments.

[0008] FIG. 6 is a cross-sectional view of semiconductor structures over a substrate after the formation of a first liner over the sidewalls of the semiconductor structures, in accordance with some embodiments.

[0009] FIG. 7 is a cross-sectional view of semiconductor structures over a substrate after the formation of a second liner over the semiconductor structures, in accordance with some embodiments.

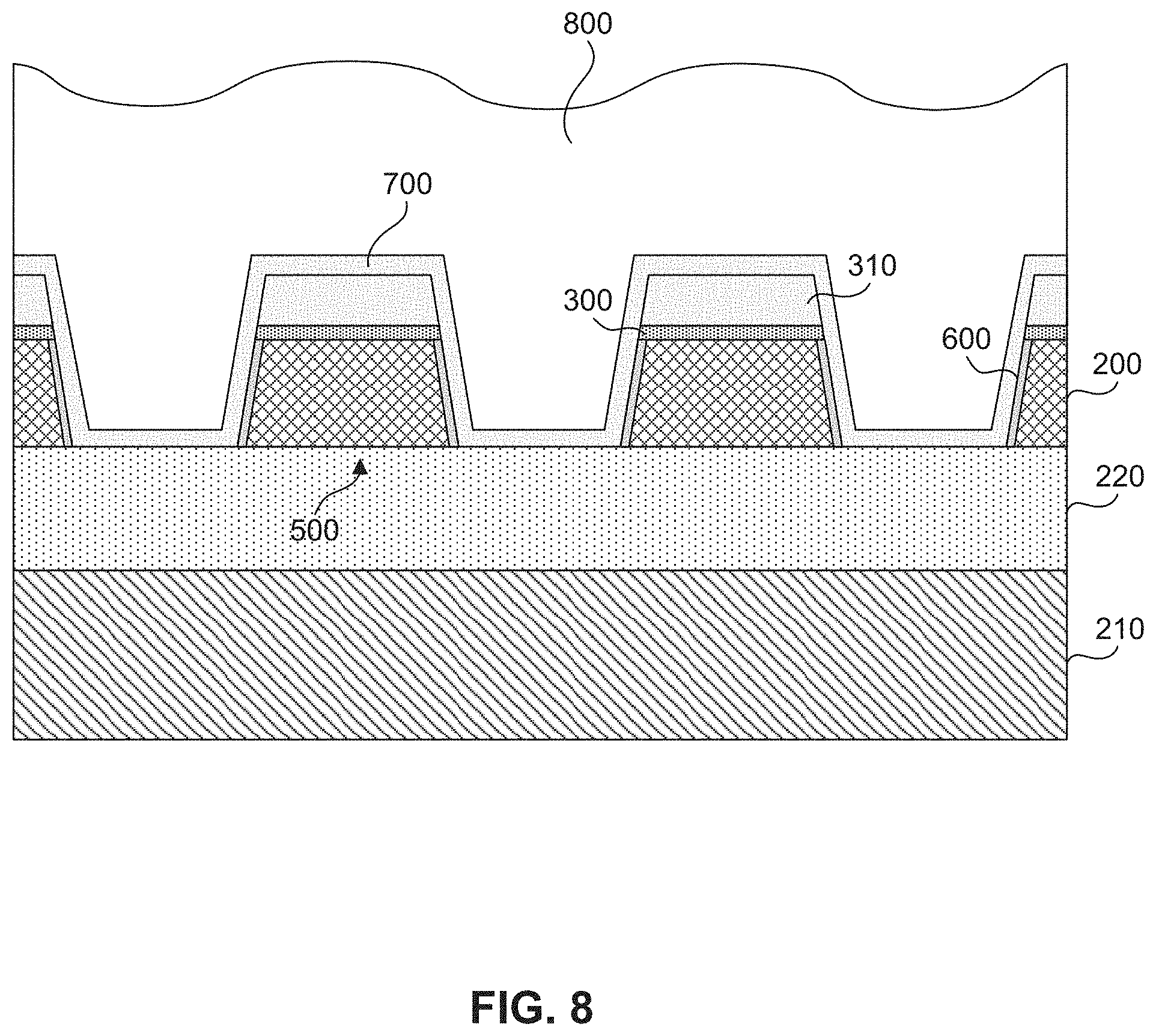

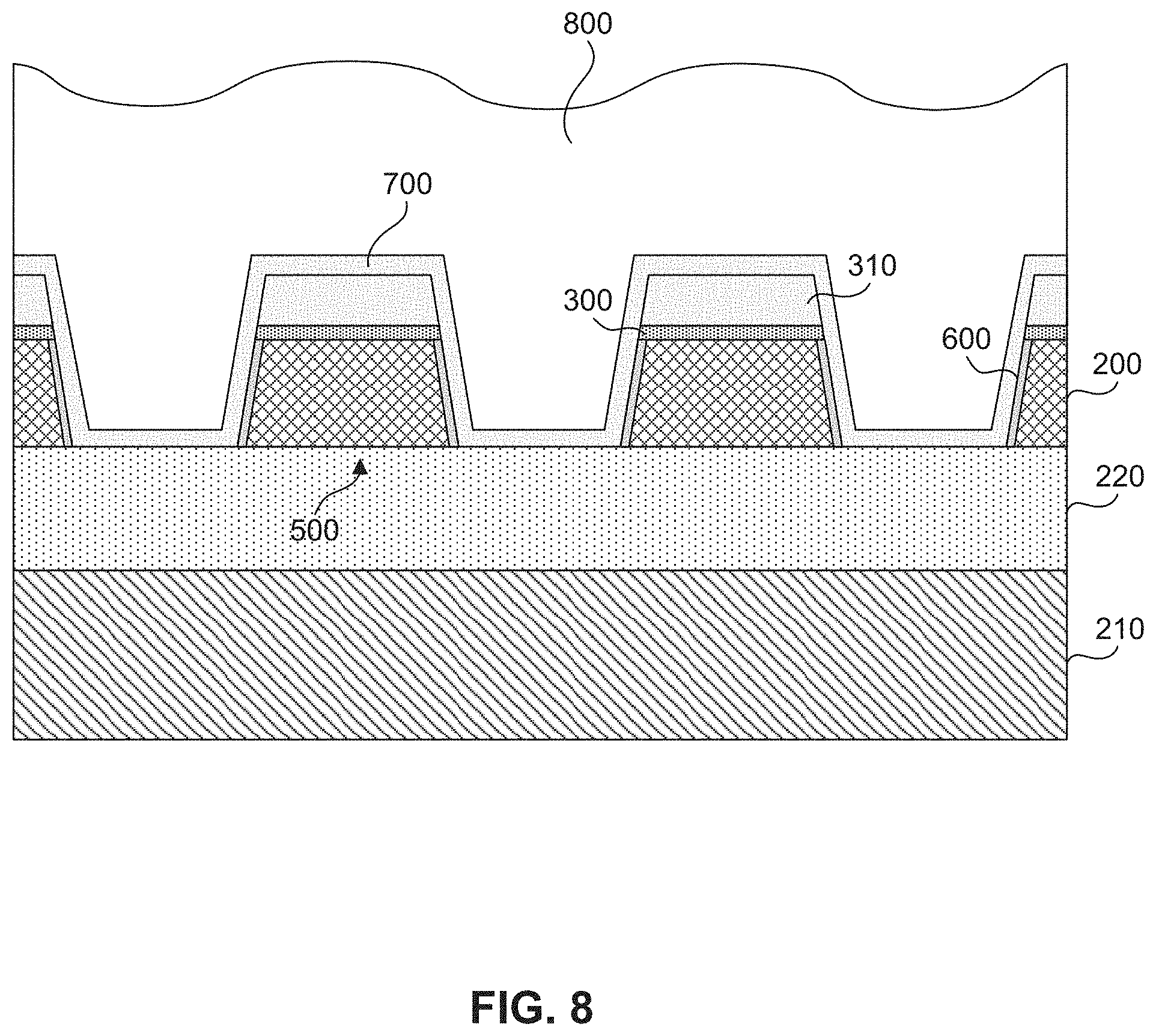

[0010] FIG. 8 is a cross-sectional view of semiconductor structures over a substrate after the deposition of a first dielectric, in accordance with some embodiments.

[0011] FIG. 9 is a cross-sectional view of isolation structures over a substrate after the etch process of a first dielectric, in accordance with some embodiments.

[0012] FIG. 10 is a cross-sectional view of isolation structures over a substrate after the removal of the second liner, in accordance with some embodiments.

[0013] FIG. 11 is a cross-sectional view of isolation structures over a substrate after the deposition of a second dielectric to form air-gaps, in accordance with some embodiments.

[0014] FIG. 12 is a cross-sectional view of isolation structures over a substrate with air-gaps therein, in accordance with some embodiments.

[0015] FIG. 13 is a cross-sectional view of different types of isolation structures over a substrate, in accordance with some embodiments.

[0016] FIG. 14 is a cross-sectional view of isolation structures with air-gaps between semiconductor structures with devices thereon, in accordance with some embodiments.

DETAILED DESCRIPTION

[0017] The following disclosure provides many different embodiments, or examples, for implementing different features of the provided subject matter. Specific examples of components and arrangements are described below to simplify the present disclosure. These are, of course, merely examples and are not intended to be limiting. For example, the formation of a first feature over a second feature in the description that follows may include embodiments in which the first and second features are formed in direct contact, and may also include embodiments in which additional features may be formed that are between the first and second features, such that the first and second features are not in direct contact.

[0018] Further, spatially relative terms, such as "beneath," "below," "lower," "above," "upper" and the like, may be used herein for ease of description to describe one element or feature's relationship to another element(s) or feature(s) as illustrated in the figures. The spatially relative terms are intended to encompass different orientations of the device in use or operation in addition to the orientation depicted in the figures. The apparatus may be otherwise oriented (rotated 90 degrees or at other orientations) and the spatially relative descriptors used herein may likewise be interpreted accordingly.

[0019] The term "nominal" as used herein refers to a desired, or target, value of a characteristic or parameter for a component or a process operation, set during the design phase of a product or a process, together with a range of values above and/or below the desired value. The range of values is typically due to slight variations in manufacturing processes or tolerances.

[0020] The term "substantially" as used herein indicates the value of a given quantity that can vary based on a particular technology node associated with the subject semiconductor device. Based on the particular technology node, the term "substantially" can indicate a value of a given quantity that varies within, for example, .+-.5% of a target (or intended) value.

[0021] The term "about" as used herein indicates the value of a given quantity that can vary based on a particular technology node associated with the subject semiconductor device. Based on the particular technology node, the term "about" can indicate a value of a given quantity that varies within, for example, 5-30% of the value (e.g., .+-.5%, .+-.10%, .+-.20%, or .+-.30% of the value).

[0022] The term "vertical," as used herein, means nominally perpendicular to the surface of a substrate.

[0023] The term "insulating layer", as used herein, refers to a layer that functions as an electrical insulator (e.g., a liner).

[0024] Embodiments of the present disclosure may be applicable to fin field effect transistors ("finFETs"). The "fins" in finFETs may be patterned by any suitable method. For example, the fins may be patterned using one or more photolithography processes, including double-patterning or multi-patterning processes. Generally, double-patterning or multi-patterning processes combine photolithography and self-aligned processes, allowing patterns to be created that have, for example, pitches smaller than what is otherwise obtainable using a single, direct photolithography process. For example, in one embodiment, a sacrificial layer is formed over a substrate and patterned using a photolithography process. Spacers are formed alongside the patterned sacrificial layer using a self-aligned process. The sacrificial layer is then removed, and the remaining spacers may then be used to pattern the fins.

[0025] A radio frequency (RF) front-end module (FEM) requires integration of multiple RF functions, including for example antenna low noise amplifiers (LNA), power amplifiers (PA), antenna tuning switches, transceivers, as well as digital processing and power management. Each RF FEM component can include a large number of field effect transistors (FETs) that are electrically isolated by shallow trench isolation (STI) structures. In addition to the electrical isolation, the STI structures can provide protection against parasitic coupling that can occur between adjacent FETs during normal device operation.

[0026] However, as the devices are continuously scaled down from one technology generation to the next, capacitive coupling between adjacent FETs can become more prominent. This is because the FETs are packed closer together and the space available for the STI structures, which are disposed between them, can be further reduced. Isolating highly packed FETs from parasitic capacitance coupling can be challenging for operating frequencies in the GHz range. Additionally, as the edge of the STI structures between the FETs comes closer to the channel region of each FET, unintentional compressive stress can be introduced to the channel region, which can be detrimental for the FET's performance (e.g., for the n-type FET's performance). For example, the unintentional compressive stress in the vicinity of the channel region can impact the electron mobility and, therefore, the current output of the NFETs.

[0027] The embodiments described herein are directed to a method that forms STI structures with air-gaps (air-pockets or cavities). The air-gaps, which can be formed along the sidewalls of the STI structures, can serve multiple purposes. In some embodiments, the STI structures with air-gaps can provide both enhanced electrical isolation between the FETs and protection against parasitic capacitance coupling when the device operates in the GHz range. This is because the air-gaps can lower the overall dielectric constant of the STI material (e.g., lower than 3.9). Further, due to the presence of air gaps, the STI structures can mitigate the compressive stress on the channel region of a neighboring FET, even if the edge of the STI structure is close to the channel region (e.g., within about 0.5 .mu.m).

[0028] FIG. 1 is a flow chart of fabrication method 100, according to some embodiments. Fabrication method 100 describes the formation of air-gaps along the sidewall surfaces of STI structures. Fabrication method 100 can be used to form air-gaps either on selective STI structures or on all the STI structures of the substrate (e.g., the wafer). Other, or additional, fabrication operations may be performed between the various operations of fabrication method 100. These fabrication operations are omitted merely for clarity.

[0029] Fabrication method 100 begins with operation 110, where a semiconductor layer is patterned over a substrate to form semiconductor structures. FIGS. 2-5 will be used to describe operation 110. For example, FIG. 2 is a cross-sectional view of semiconductor layer 200 over substrate 210. In some embodiments, substrate 210 can be a bulk silicon wafer with a dielectric layer 220 formed thereon and a top semiconductor layer 200. Dielectric layer 220 can be an oxide, such as silicon oxide (e.g., buried oxide layer), sapphire, or another suitable dielectric layer on which semiconductor layer 200 can be grown, attached, or otherwise formed. By way of example and not limitation, dielectric layer 220 is thicker than semiconductor layer 200. Further, dielectric layer 220 electrically isolates semiconductor layer 200 from substrate 210. In some embodiments, semiconductor layer 200 is directly on silicon substrate 210. In this case, substrate 210 can be a high-resistivity (HR) bulk silicon substrate. In other words, current cannot flow from semiconductor layer 200 to substrate 210.

[0030] According to some embodiments, semiconductor layer 200 can include (i) silicon, (ii) a compound semiconductor such as gallium arsenide (GaAs), gallium phosphide (GaP), indium phosphide (InP), indium arsenide (InAs), and/or indium antimonide (InSb), (iii) an alloy semiconductor including silicon germanium (SiGe), gallium arsenide phosphide (GaAsP), aluminum indium arsenide (AlInAs), aluminum gallium arsenide (AGaAs), gallium indium arsenide (GaInAs), gallium indium phosphide (GaInP), and/or gallium indium arsenide phosphide (GaInAsP), or (iv) combinations thereof.

[0031] For example purposes, semiconductor layer 200 in fabrication method 100 will be described in the context of a top silicon layer of a silicon-on-insulator substrate (e.g., SOI wafer). Based on the disclosure herein, other materials, as discussed above, can be used. These materials are within the spirit and scope of this disclosure.

[0032] Referring to FIG. 3, a stack including a bottom oxide layer 300 and a top nitride layer 310 are deposited over semiconductor layer 200. By way of example and not limitation, oxide layer 300 can include silicon oxide, and nitride layer 310 can include silicon nitride. Oxide layer 300 can be a capping layer that protects the top surface of semiconductor layer 200 during subsequent processing. By way of example and not limitation, nitride layer 310 can function as a stop layer in subsequent operations of fabrication method 100.

[0033] A photoresist layer 320 can be deposited over nitride layer 310. A bottom antireflective coating (BARC), which is not shown in FIG. 3, can be interposed between photoresist layer 320 and nitride layer 310. The BARC layer can suppress light reflections during a subsequent ultra violet (UV) or extreme ultra violet (EUV) light exposure of photoresist layer 320 and minimize undesirable generation of standing waves during the exposure process. Standing waves can increase the edge roughness of the resulting patterned photoresist structures. The BARC layer can also form a flat surface, on which photoresist layer 320 can be formed, by operating as a filler that fills small imperfections of the top surface of nitride layer 310.

[0034] Photoresist layer 320 can be patterned so that patterned photoresist structures 400 are formed over nitride layer 310, as shown in FIG. 4. Patterning of photoresist layer 320 can be accomplished by exposing photoresist layer 320 to UV or EUV light through a reticle (photomask) and subsequently removing unexposed (or exposed portions) of the photoresist layer. The pitch (e.g., spacing) of patterned photoresist structures 400 may vary over substrate 210 depending on the pattern design. Therefore, high and low density areas of patterned photoresist structures 400 (e.g., patterned photoresist structures with different pitch or spacing) may be formed over different areas of substrate 210. Further, the width of the patterned photoresist structures 400 can also vary across substrate 210.

[0035] In referring to FIG. 5, a dry etch process can remove nitride layer 310, oxide layer 300 and semiconductor layer 200 between patterned photoresist structures 400 to form semiconductor structures, or semiconductor islands, 500. In other words, patterned photoresist structures 400 can be used as an etch mask to define the geometrical aspects of semiconductor structures 500. For example, the width and the pitch of the patterned photoresist structures 400 can be used to further define the width and the pitch of the resulting semiconductor structures 500. In some embodiments, the sidewalls of the resulting semiconductor structures 500 can have a positive slope, as shown in FIG. 5. However, this is not limiting, because semiconductor structures 500 can be designed to have substantially vertical sidewalls (e.g., between about 86.degree. and about 90.degree.), or sidewalls with a negative slope. The sidewall slope (or sidewall angle) of semiconductor structures 500 can be tuned by the dry etch process conditions. Therefore, the dry etch process conditions may be adjusted to achieve the desired slope for the sidewalls of semiconductor structures 500. In some embodiments, the dry etch process can include several etch sub-steps with a different etch chemistry for each sub-step.

[0036] After semiconductor structures 500 are formed, patterned photoresist structures 400 can be removed with a wet clean process (e.g., wet strip). In some embodiments, the height of the formed semiconductor structures 500 can be up to about 200 nm. However, this is not limiting and other heights for the semiconductor structures 500 may be considered.

[0037] Semiconductor structures 500 can be silicon structures where n-type or p-type FETs can be formed thereon. For example, semiconductor structures 500 can be doped to form source/drain regions, a channel region, etc. Further, local metal contacts can be formed on semiconductor structures 500 to electrically connect the terminals of the FETs (e.g., the source/drain and gate terminals) to other components of the chip.

[0038] In referring to FIG. 1, fabrication method 100 continues with operation 120 and the formation of a first liner on each sidewall surface of semiconductor structures 500. FIG. 6 is a cross-sectional view of semiconductor structures 500 after the formation of first liner 600 on each sidewall surface of semiconductor structure 500, according to the description of operation 120. By way of example and not limitation, first liners 600 can be formed by thermal oxidation of the exposed sidewalls surfaces of semiconductor structure 500. By way of example and not limitation, thermal oxidation of the sidewall surfaces of semiconductor structures 500 can occur in an oxidizing ambient that may include water vapors or molecular oxygen (e.g., wet or dry oxidation). During the thermal oxidation process, first liner 600 can be formed by consuming the silicon from the sidewall surfaces of semiconductor structures 500. In other words, a portion of first liner 600 is grown inwards from the sidewall surface. In some embodiments, first liner 600 includes silicon oxide (e.g., silicon dioxide (SiO.sub.2)). By way of example and not limitation, the oxidation process can be performed at a temperature between about 800.degree. C. and about 1200.degree. C. (e.g., between 900.degree. C. and 1100.degree. C.). The thickness of the first liner can range from about 5 nm to about 20 nm. Since the only exposed silicon areas available for oxidation are the sidewall surfaces of semiconductor structures 500, first liners 600 will be selectively grown on (or be "self-aligned" to) the sidewall surfaces of semiconductor structures 500.

[0039] Fabrication method 100 continues with operation 130 and the deposition of a second liner 700 as shown in FIG. 7. Second liner 700 can be deposited over nitride layer 310, first liner 600 and dielectric layer 220. By way of example and not limitation, second liner 700 can be deposited by chemical vapor deposition (CVD), plasma-enhanced chemical vapor deposition (PECVD), atomic layer deposition (ALD), plasma-enhanced atomic layer deposition (PEALD), or any other suitable conformal deposition method. In some embodiments, second liner 700 has a thickness between about 10 nm and about 50 nm. By way of example and not limitation, second liner 700 and nitride layer 310 can be the same material. In other words, second liner 700 can include silicon nitride. In some embodiments, second liner 700 can be considered a "sacrificial" spacer or a sacrificial layer formed over the sidewalls of semiconductor structures 500. For example, second liner 700 can be removed in a subsequent operation of fabrication method 100.

[0040] In referring to FIGS. 1 and 8, fabrication method 100 continues with operation 140, where a first dielectric 800 is deposited between semiconductor structures 500 to form isolation structures (e.g., STI structures). In some embodiments, first dielectric 800 is deposited with a high density plasma CVD (HDP-CVD) process that has good gap-fill properties. For example, first dielectric 800 can fill completely the space between semiconductor structures 500 (e.g., without the formation of voids or gaps). In FIG. 9, a chemical mechanical planarization (CMP) process can polish first dielectric 800 until it is coplanar with the top surface of second liner 700 (e.g., second liner 700 can act as a stop layer for the CMP process). As a result, isolation structures 900 are formed. In some embodiments, isolation structures 900 are STI structures that can electrically isolate semiconductor structures 500. By way of example and not limitation, isolation structures 900 can include first dielectric 800 and portions of second liner 700 that are disposed over the sidewalls of semiconductor structures 500 and the top surface of dielectric layer 220, as shown in FIG. 9 by the dashed closed line.

[0041] Fabrication method 100 of FIG. 1 continues with operation 150. In operation 150, second liner 700 is removed between isolation structures 900 and first liner 600 to form respective openings 1000, as shown in FIG. 10. In some embodiments, removal of second liner 700 can be achieved with a wet etch process (also referred to as wet chemical strip). By way of example and not limitation, the wet etch process can include hot phosphoric acid (H.sub.3PO.sub.4) and it can be performed at a temperature of about 160.degree. C. Further, the wet etch chemistry can be selected to have high selectivity towards second liner 700 as opposed to exposed oxide material-such as oxide layer 300 and first liner 600, which are both silicon-based oxides (e.g., silicon oxide). For example, the wet etch process may exhibit a selectivity ratio for second liner 700 and oxide layer 300, or second liner 700 and first liner 600, of about 100:1. If the selectivity ratio is not high enough, portions of oxide layer 300 and first liner 600 will also be etched during the etch process.

[0042] During the wet etch process, second liner 700 and nitride layer 310 are both removed (e.g., etched) over oxide layer 300. As discussed above, both second liner 700 and nitride layer 310 can include silicon nitride. Hence, the selectivity of the wet etch process towards second liner 700 and nitride layer 310 can be the same (e.g., selectivity ratio 1:1). According to some embodiments, the wet etch process can be timed so that a portion of second liner 700 between isolation structures 900 and dielectric layer 220 is not removed (e.g., etched). In some embodiments, second liner 700 under dielectric 800 can be equal or narrower than the base of dielectric 800. In some embodiments, second liner 700 underneath dielectric 800 can be wider that the base of dielectric 800 and cover the entire exposed surface of dielectric layer 220. Alternatively, second liner 700 underneath dielectric 800 can be wider that the base of isolation structures 900 but not cover the entire exposed surface of dielectric layer 220. In some embodiments, the thickness of second liner 700 over the sidewalls of semiconductor structures 500 can be used to control the width of openings 1000 and ultimately the size of the air-gaps in the STI structures.

[0043] Referring to FIG. 1, fabrication method 100 continues with operation 160 and the deposition of a second dielectric (e.g., capping dielectric layer) to form an air-gap (e.g., an air-pocket or cavity), between first dielectric 800 and first liner 600. For example, an air-gap can be formed when the second dielectric seals the top entrance of opening 1000. Further, openings 1000 can have an aspect ratio--e.g., a high aspect ratio between about 5:1 to about 20:1--that prevents second dielectric material from filling opening 1000. According to some embodiments, the combination of the high deposition rate of second dielectric 1120 and the high aspect ratio of openings 1000 form air-gaps at the locations of openings 1000. In some embodiments, the second dielectric can be deposited by a PECVD process, a physical vapor deposition (PVD), or any other suitable oxide deposition process with appropriate deposition rate.

[0044] FIG. 11 shows the resulting air-gaps (e.g., air-pockets or cavities) 1100 after the deposition of second dielectric 1120. In some embodiments, the first and the second dielectrics (e.g., 800 and 1120, respectively) are the same material, e.g., silicon oxide (SiO.sub.2). Further, until opening 1000 is sealed, second dielectric 1120 may or may not reach the bottom of opening 1000. Therefore, in some embodiments, the resulting air-gaps may or may not extend to the top surface of dielectric layer 220. Additionally, the size of air-gaps (or air-pockets, or cavities) 1100 can be smaller than the size of openings 1000 in operation 150. This is because second dielectric 1120 may continue to be deposited into opening 1000 until the top entrance of the opening is capped (e.g., sealed). By way of example and not limitation, the size of air-gaps 1100 may depend, among other things, on (i) the size of openings 1000 (which can be modulated by the thickness of second liner 700 and the height of semiconductor structures 500), (ii) the sidewall slope of semiconductor structures 500, and (iii) the deposition process parameters of second dielectric 1120. For example, the deposition process parameters of second dielectric 1120 can modulate the gap-fill properties and the deposition rate of second dielectric 1120 in openings 1000. In some embodiments, the width of air-gaps 1100 can range from about 10 nm to about 25 nm (e.g., from 10 nm to 25 nm).

[0045] In some embodiments, air-gaps (e.g., air-pockets, or cavities) 1100 can be filled with one or more gases that are present during the deposition process of second dielectric 1120. In other words, air-gaps 1100 may not be filled with atmospheric air. In some embodiments, air-gaps (e.g., air-pockets, or cavities) 1100 can be filled with an inert gas or gases such as nitrogen, helium, and argon.

[0046] In some embodiments, a porogen containing material (e.g., carbon-doped silicon dioxide that contains loosely bounded methyl groups) can be used to fill openings 1000 of FIG. 10. The porogen containing material can be cured and converted to a porous low-k material with a k value below 3.6 (e.g., k value of about 3). During the curing process, the porogen is released leaving behind pores in the material. By way of example and not limitation, the curing process may include exposure to UV radiation that has a wavelength between about 150 nm and about 400 nm. Other curing process may be used, including a thermal process. In some embodiments, openings 1000 can be filled directly with a low-k dielectric material, such as carbon-doped silicon dioxide or any other suitable low-k dielectric material with appropriate gap-fill properties.

[0047] In some embodiments, a dry etch process, wet etch process, or a combination of a dry and a wet process can be used to remove (e.g., etch) second dielectric 1120 over semiconductor structures 500, until oxide layer 300 is exposed. By way of example and not limitation, a dry etch process can include a fluorocarbon based chemistry (e.g., fluorinated hydrocarbons), such as tetrafluoromethane (CF.sub.4), trifluromethance (CHF.sub.3), and the like. On the other hand, a wet etch process can include a diluted solution of hydrofluoric acid (HF) with a buffer, such as ammonium fluoride (NH.sub.4F), diluted HF (HF/H.sub.2O), H.sub.3PO.sub.4, sulfuric acid with deionized water (H.sub.2SO.sub.4/H.sub.2O), or any combinations thereof. The dry or wet etch process can be for example timed so that first dielectric 800 is not removed during the etch process. For example, the dry or wet etch process can be timed so that it is terminated when oxide layer 300 is exposed. The aforementioned etch chemistries are exemplary and, therefore, not limiting. Other suitable dry etch or wet etch chemistries may be used.

[0048] As a result of the aforementioned dry or wet etch process, isolation structures 1200 (e.g., STI structure 1200) with air-gaps along their sidewalls are formed, as shown in FIG. 12. As a result of the etching process, a divot 1210 can be formed on each corner of isolation structure 1200. In some embodiments, divots (e.g., like divot 1210) can have a depth between about 2 nm and 10 nm. If divots 1210 are not formed, the top surface of isolation structure 1200 can be substantially flat or lightly convex with round corners.

[0049] In some embodiments, fabrication method 100 introduces air-gaps in isolation structures (e.g., STI structures) by retaining the original size of the isolation structures and the pitch of the semiconductor structures. In other words, no modification to the pitch of the semiconductor structures is required and, subsequently, to the reticles (e.g., photomask) used in the photolithography operations. This means that fabrication method 100 can be introduced to an existing STI formation process flow without any changes to the photolithography process.

[0050] According to some embodiments, it is possible that isolation structures without air-gaps are formed alongside with isolation structures with air-gaps (e.g., like isolation structures 1200 of FIG. 12) on the same substrate (e.g. wafer). This means that the resulting chip or integrated circuit can include STI structures with and without air-gaps if desired. In other words, fabrication method 100 can be applied on selected isolation structures of substrate 210. Additionally, it is also possible that isolation structures with air-gaps and divots are formed alongside with divot-free isolation structures that have air-gaps. For example, FIG. 13 shows the three types of isolation structures that can be formed on a single substrate. In the example of FIG. 13, isolation structure 1200 A has both air-gaps and divots; isolation structure 1200 B has air-gaps but no divots (e.g., a lightly convex top surface with rounded corners); and isolation structure 1300 can have divots, or be divot-free, without air-gaps. According to some embodiments, isolation structure 1200 A and isolation structure 1200 B are formed using the fabrication method 100 of FIG. 1. As a result of fabrication method 100, the air-gaps are formed embedded in the isolation structures, along each sidewall of isolation structures 1200 A and 1200 B, e.g., along the sidewalls of semiconductor structures 500 and over first liner 600. By way of example and not limitation, application of fabrication method 100 on selective areas of substrate 210 can be achieved with photolithography methods. For example, the isolation structures that will be "air-gap" free, will be masked by a photoresist layer (or a hard mask) during operation 130 of fabrication method 100 (e.g., during the deposition of second liner 700 over semiconductor structures 500 and first liner 600).

[0051] FIG. 14 is a cross-sectional view of isolation structures (e.g., STI structures) 1200 A between semiconductor structures 500, where devices 1400, metal contacts 1410, and source/drain (S/D) regions 1420 have been formed on semiconductor structure 500. In some embodiments, devices 1400 are FETs. These FETs can be either NFETs or PFETs, and can be part of an integrated circuit (IC) formed on an SOI substrate (or a bulk, high-resistive semiconductor substrate). The channel region 1430 of FETs 1400 is located in semiconductor structure 500 between the S/D regions 1420 and below FET 1400. According to some embodiments, isolation structures 1200 A with air-gaps, fabricated with method 100 of FIG. 1, can provide enhanced electrical isolation and protection from parasitic capacitances (e.g., in the GHz range) of parasitic capacitors that can be formed between neighboring devices 1400. Further, due to the presence of air-gaps, isolation structures 1200 A can mitigate the compressive stress that is induced to channel region 1430 below FETs 1400, even if the edge of isolation structure 1200 A is close to channel region 1430 (e.g., within 0.5 .mu.m).

[0052] Fabrication method 100 may not be limited to RF SOI technology or RF SOI applications. For example, fabrication method 100 can be implemented in other complementary metal oxide (CMOS) applications where protection against parasitic capacitances is required. Alternatively, method 100 can be applied to any other semiconductor or non-semiconductor processing that includes shallow trench isolation (STI) structures, or formation thereof.

[0053] The embodiments described herein are directed to a fabrication method that can form air-gaps (air-pockets or cavities) in STI structures. In some embodiments, the fabrication method includes a sacrificial nitride layer that can be introduced prior to the deposition of the STI material between the semiconductor structures. The sacrificial nitride layer can be subsequently removed after the deposition of the STI material so that an opening can be formed along the sidewall surfaces of adjacent semiconductor structures. A second deposition of a dielectric material can seal the entrance of the opening and form an air-gap, which is embedded in the STI structure along the sidewalls of the semiconductor structure. The thickness of the sacrificial nitride layer, in combination with the process conditions during the second deposition of the dielectric material, can control in part the size of the embedded air-gaps (air-pockets or cavities) in the resulting STI structure. Further, and on the same substrate, STI structures with and without air-gaps can be formed. In other words, the fabrication method described herein can be applied to selective STI structures on the substrate. Such selectivity can be achieved with photolithography methods. For example, the STI structures that will not form air-gaps can be masked by a photoresist layer, or a hard mask, during the deposition of the sacrificial nitride layer.

[0054] In some embodiments, a structure includes semiconductor islands, which are formed over a substrate, with liners disposed on the sidewalls of the semiconductor islands and an isolation structure disposed between the semiconductor islands. Further, the isolation structure includes one or more air-gaps that are formed along the liners.

[0055] In some embodiments, an integrated circuit includes an insulating layer, a semiconductor layer disposed on the insulating layer and a field effect transistor formed on one or more of the semiconductor islands. The semiconductor layer further includes: semiconductor islands, a liner disposed on each sidewall of the semiconductor islands and an isolation structure between the semiconductor islands. The isolation structure includes an oxide layer with an air-pocket disposed along the liner of each sidewall of the semiconductor islands and a nitride layer disposed between the insulating layer and the oxide layer.

[0056] In some embodiments, a method includes patterning a semiconductor layer over a substrate to form semiconductor islands and oxidizing the sidewall surfaces of the semiconductor islands to form first liners on the sidewall surfaces. Further the method includes depositing a second liner over the first liners and the substrate and depositing a first dielectric layer between the semiconductor islands. The second liner between the first dielectric layer and the first liners is removed to form openings between the first dielectric layer and the first liners and a second dielectric layer is deposited over the first dielectric layer to enclose the openings and form air-gaps between the first dielectric layer and the first liners so that the gaps are positioned along the first liners.

[0057] It is to be appreciated that the Detailed Description section, and not the Abstract of the Disclosure section, is intended to be used to interpret the claims. The Abstract of the Disclosure section may set forth one or more but not all possible embodiments of the present disclosure as contemplated by the inventor(s), and thus, are not intended to limit the subjoined claims in any way.

[0058] The foregoing disclosure outlines features of several embodiments so that those skilled in the art may better understand the aspects of the present disclosure. Those skilled in the art will appreciate that they may readily use the present disclosure as a basis for designing or modifying other processes and structures for carrying out the same purposes and/or achieving the same advantages of the embodiments introduced herein. Those skilled in the art will also realize that such equivalent constructions do not depart from the spirit and scope of the present disclosure, and that they may make various changes, substitutions, and alterations herein without departing from the spirit and scope of the present disclosure.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

D00009

D00010

D00011

D00012

D00013

D00014

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.