Semiconductor Memory

FUKUZUMI; Yoshiaki ; et al.

U.S. patent application number 16/291347 was filed with the patent office on 2019-10-24 for semiconductor memory. The applicant listed for this patent is Toshiba Memory Corporation. Invention is credited to Fumiki AISO, Atsushi FUKUMOTO, Yoshiaki FUKUZUMI, Keisuke SUDA.

| Application Number | 20190326310 16/291347 |

| Document ID | / |

| Family ID | 68238169 |

| Filed Date | 2019-10-24 |

View All Diagrams

| United States Patent Application | 20190326310 |

| Kind Code | A1 |

| FUKUZUMI; Yoshiaki ; et al. | October 24, 2019 |

SEMICONDUCTOR MEMORY

Abstract

A semiconductor memory includes a substrate, a source line layer above the substrate in a memory region and a peripheral region of the substrate, a first insulating layer above the source line layer, a first conductive layer on the first insulating layer in the memory and peripheral regions, an alternating stack of a plurality of second insulating layers and a plurality of second conductive layers on the first conductive layer in the memory region, and a plurality of pillars extending through the alternating stack of the second insulating layers and the second conductive layers, the first conductive layer, and the first insulating layer in the memory region. A bottom end of each of the pillars is in the source line layer in a thickness direction. A carrier density of the source line layer is higher in the memory region than in the peripheral region.

| Inventors: | FUKUZUMI; Yoshiaki; (Yokkaichi Mie, JP) ; SUDA; Keisuke; (Yokkaichi Mie, JP) ; AISO; Fumiki; (Kuwana Mie, JP) ; FUKUMOTO; Atsushi; (Mie Mie, JP) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 68238169 | ||||||||||

| Appl. No.: | 16/291347 | ||||||||||

| Filed: | March 4, 2019 |

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 27/11565 20130101; G11C 5/06 20130101; H01L 27/11556 20130101; G11C 16/0408 20130101; G11C 16/0466 20130101; H01L 27/11582 20130101; G11C 16/0483 20130101; H01L 27/11575 20130101 |

| International Class: | H01L 27/11556 20060101 H01L027/11556; H01L 27/11582 20060101 H01L027/11582; G11C 5/06 20060101 G11C005/06; G11C 16/04 20060101 G11C016/04 |

Foreign Application Data

| Date | Code | Application Number |

|---|---|---|

| Apr 18, 2018 | JP | 2018-079578 |

Claims

1. A semiconductor memory comprising: a substrate; a source line layer above the substrate in a memory region and a peripheral region of the substrate; a first insulating layer above the source line layer in the memory and peripheral regions; a first conductive layer on the first insulating layer in the memory and peripheral regions; an alternating stack of a plurality of second insulating layers and a plurality of second conductive layers on the first conductive layer in the memory region; and a plurality of pillars extending through the alternating stack of the second insulating layers and the second conductive layers, the first conductive layer, and the first insulating layer in the memory region, a bottom end of each of the pillars being in the source line layer in a thickness direction, wherein a carrier density of the source line layer in the memory region is higher than a carrier density of the source line layer in the peripheral region.

2. The semiconductor memory according to claim 1, wherein each of the plurality of pillars includes a first insulator extending in a stack direction of the second insulating layer and the second conductive layers, and a first semiconductor covering bottom and side surfaces of the first insulator, and the source line layer is in contact with the first semiconductor of each of the pillars on the side surface of each of the pillars.

3. The semiconductor memory according to claim 1, further comprising: an insulating wall extending through the alternating stack of the second insulating layers and the second conductive layers, the first conductive layer, and the first insulating layer in the memory region, the insulating wall also extending in a surface direction of the substrate, and a bottom end of the insulating wall being located in the source line layer in the thickness direction.

4. The semiconductor memory according to claim 1, wherein the source line layer includes first to fifth layers stacked in order from a substrate side, and both the second layer and the fourth layer contain an oxide or a nitride.

5. The semiconductor memory according to claim 4, wherein a thickness of both the second layer and the fourth layer is 2 nm or less.

6. The semiconductor memory according to claim 1, wherein the source line layer in the memory region contains phosphorus.

7. The semiconductor memory according to claim 1, wherein the source line layer in the peripheral region contains germanium.

8. The semiconductor memory according to claim 1, wherein the source line layer contains carbon.

9. The semiconductor memory according to claim 1, wherein the source line layer contains nitrogen or oxygen.

10. The semiconductor memory according to claim 1, wherein the source line layer contains boron.

11. A semiconductor memory comprising: a substrate; a source line layer above the substrate in a memory region and a peripheral region of the substrate; an insulating layer above the source line layer in the memory and peripheral regions; a select gate line layer on the insulating layer in the memory and peripheral regions; a plurality of word line layers on the select gate line layer in the memory region; and a plurality of pillars extending through the word line layers, the select gate line layer, and the insulating layer in the memory region, a bottom end of each of the pillars being in the source line layer in a thickness direction, wherein a carrier density of the source line layer in the memory region is higher than a carrier density of the source line layer in the peripheral region.

12. The semiconductor memory according to claim 11, wherein each of the plurality of pillars includes a first insulator extending in the thickness direction and a first semiconductor covering bottom and side surfaces of the first insulator, and the source line layer is in contact with the first semiconductor of each of the pillars on the side surface of each of the pillars.

13. The semiconductor memory according to claim 11, further comprising: an insulating wall extending through the word line layers, the select gate line layer, and the insulating layer in the memory region, the insulating wall also extending in a surface direction of the substrate, and a bottom end of the insulating wall being located in the source line layer in the thickness direction.

14. The semiconductor memory according to claim 11, wherein the source line layer includes first to fifth layers stacked in order from a substrate side, and both the second layer and the fourth layer contain an oxide or a nitride.

15. The semiconductor memory according to claim 14, wherein a thickness of both the second layer and the fourth layer is 2 nm or less.

16. The semiconductor memory according to claim 11, wherein the source line layer in the memory region contains phosphorus.

17. The semiconductor memory according to claim 11, wherein the source line layer in the peripheral region contains germanium.

18. The semiconductor memory according to claim 11, wherein the source line layer contains carbon.

19. The semiconductor memory according to claim 11, wherein the source line layer contains nitrogen or oxygen.

20. The semiconductor memory according to claim 11, wherein the source line layer contains boron.

Description

CROSS-REFERENCE TO RELATED APPLICATION

[0001] This application is based upon and claims the benefit of priority from Japanese Patent Application No. 2018-079578, filed on Apr. 18, 2018, the entire contents of which are incorporated herein by reference.

FIELD

[0002] Embodiments described herein relate generally to a semiconductor memory.

BACKGROUND

[0003] As a semiconductor memory, a NAND flash memory is known.

DESCRIPTION OF THE DRAWINGS

[0004] FIG. 1 is a block diagram illustrating a configuration example of a semiconductor memory according to a first embodiment.

[0005] FIG. 2 is a circuit diagram illustrating an example of a circuit configuration of a memory cell array in the semiconductor memory according to the first embodiment.

[0006] FIG. 3 illustrates a plan view of an example of a planar layout of the memory cell array in the semiconductor memory according to the first embodiment.

[0007] FIG. 4 illustrates a plan view of an example of a more detailed planar layout of the memory cell array in the semiconductor memory according to the first embodiment.

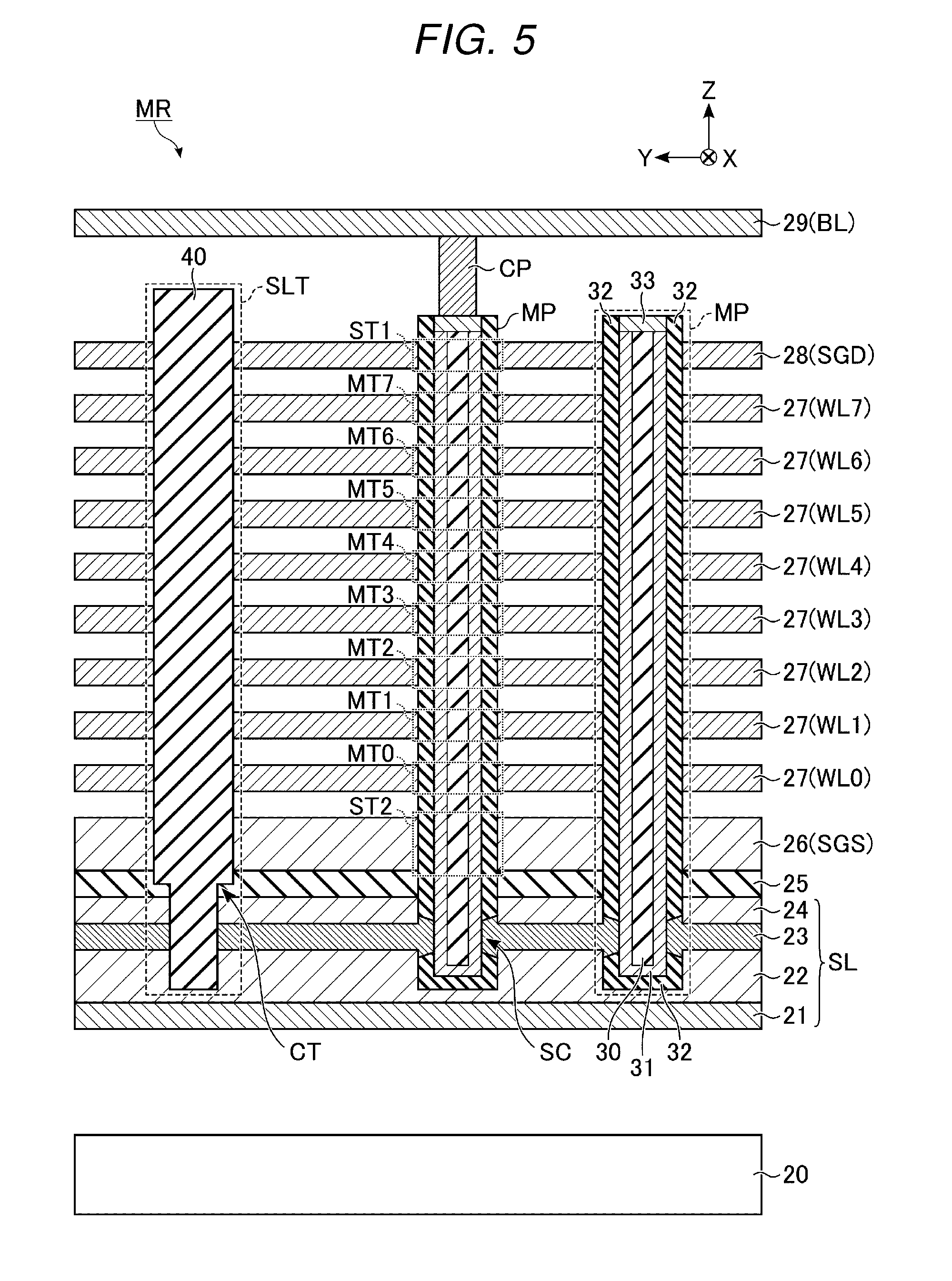

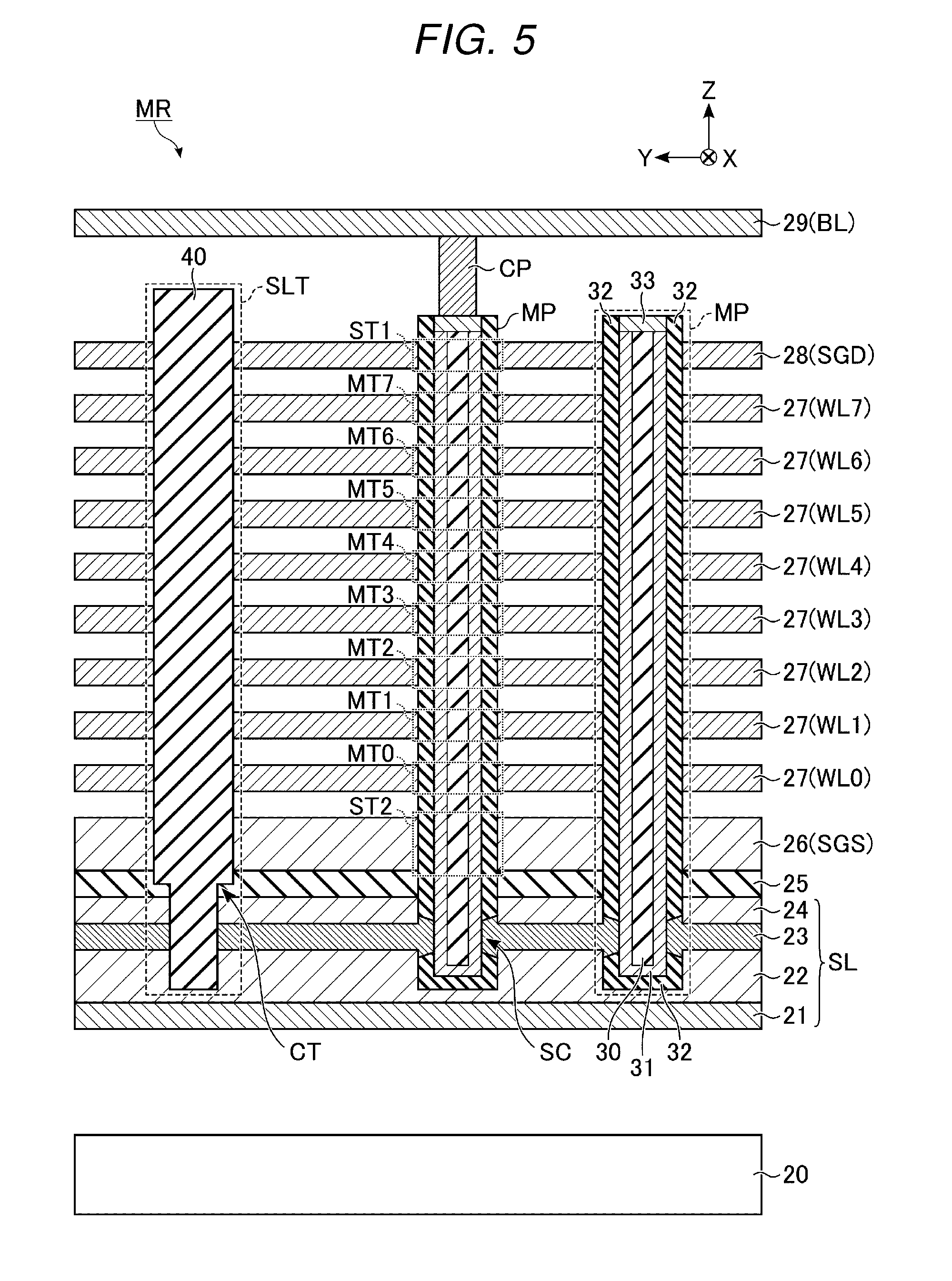

[0008] FIG. 5 illustrates a cross-sectional view of an example of a cross-sectional structure of the memory cell array taken along line V-V in FIG. 4.

[0009] FIG. 6 illustrates a cross-sectional view of an example of a cross-sectional structure of a memory pillar provided in the memory cell array in the semiconductor memory according to the first embodiment.

[0010] FIG. 7 illustrates another cross-sectional view of the example of the cross-sectional structure of the memory pillar provided in the memory cell array in the semiconductor memory according to the first embodiment.

[0011] FIG. 8 illustrates a cross-sectional view of an example of the cross-sectional structure of the memory cell array taken along line VIII-VIII of FIG. 3.

[0012] FIG. 9 is a flowchart illustrating an example of a method for manufacturing the semiconductor memory according to the first embodiment.

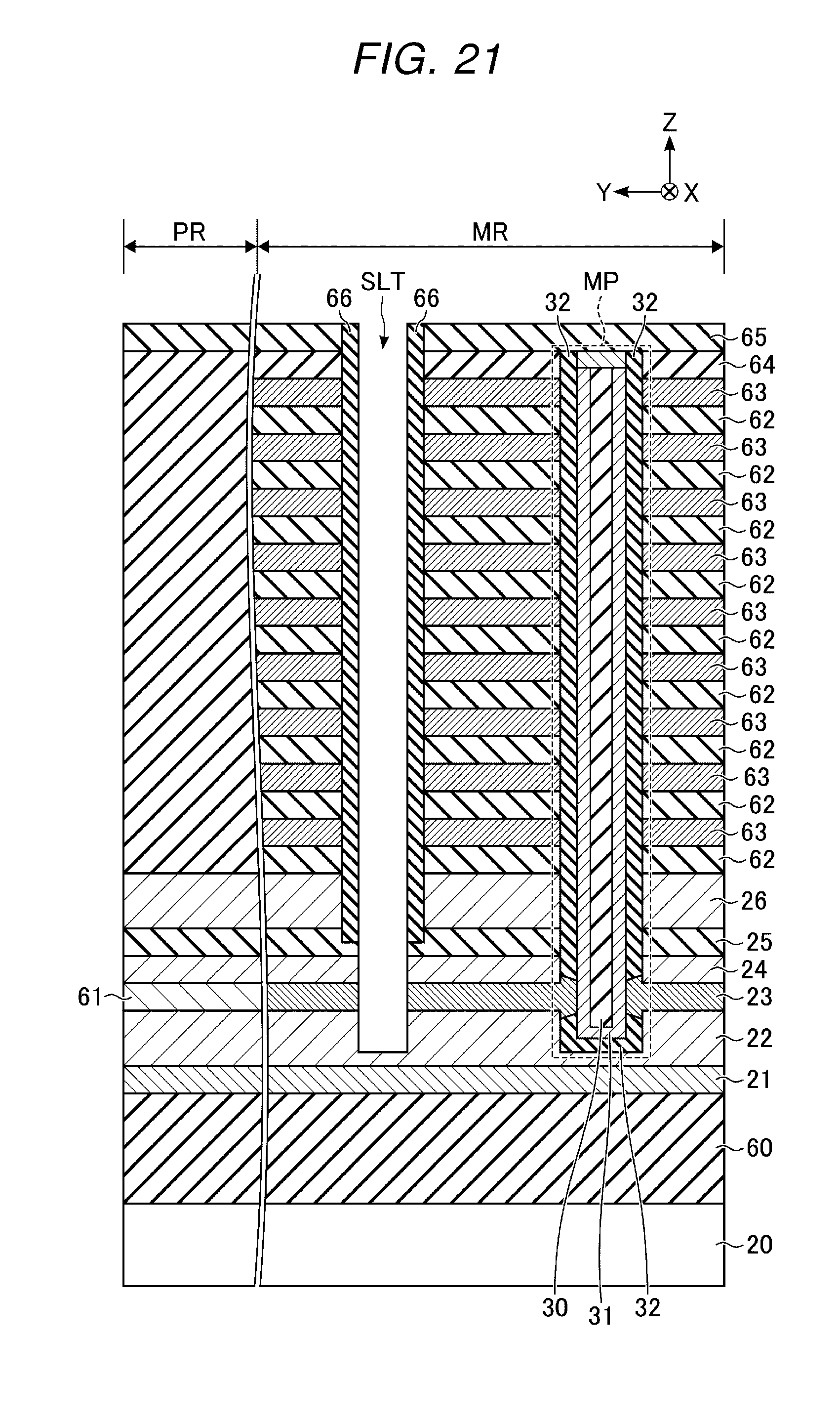

[0013] FIGS. 10-24 illustrate a cross-sectional view of a memory cell array to illustrate an example of a manufacturing process of the semiconductor memory according to the first embodiment.

[0014] FIG. 25 illustrates a cross-sectional view of an example of a cross-sectional structure in a memory region of a memory cell array in a semiconductor memory according to a second embodiment.

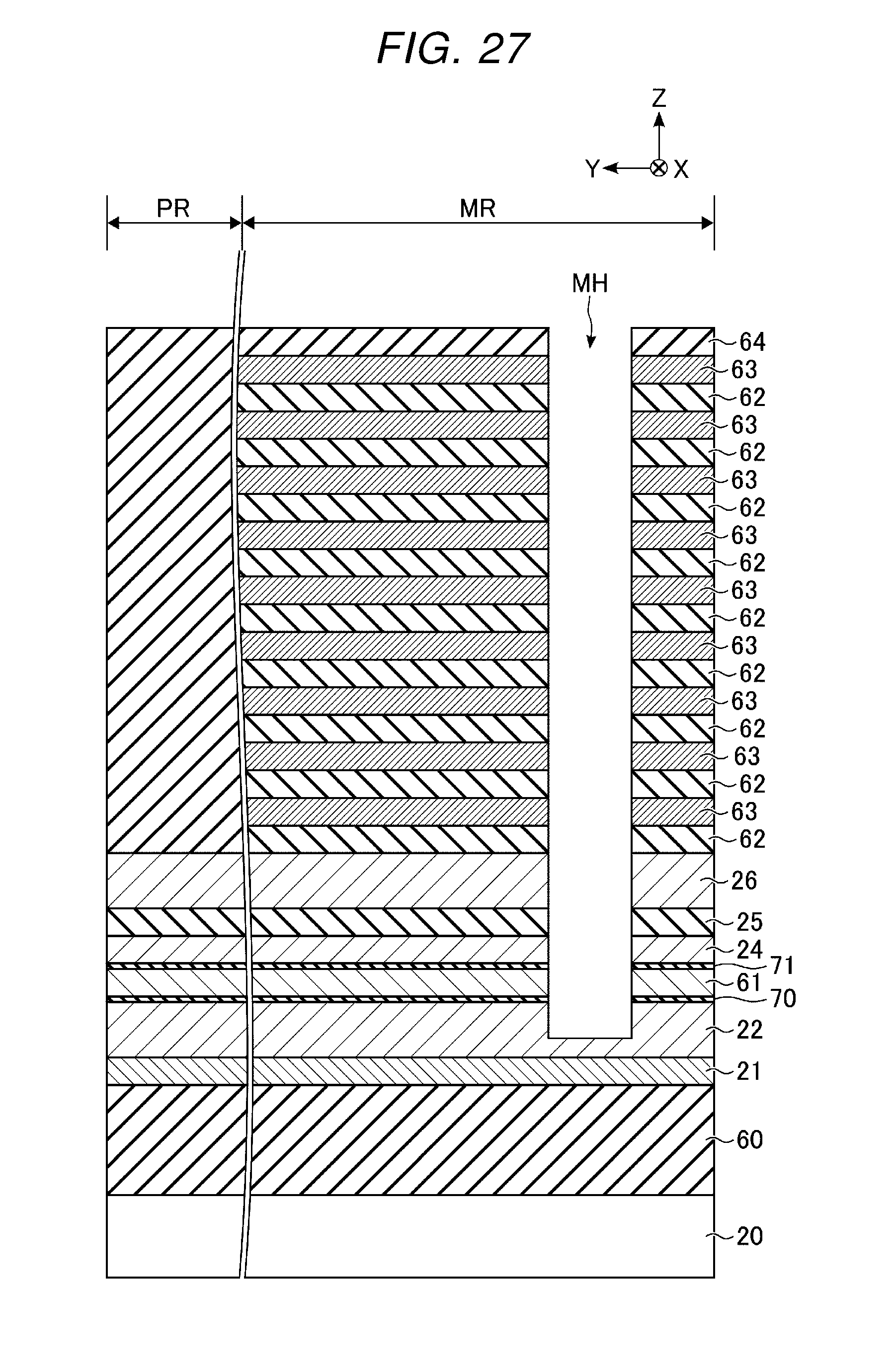

[0015] FIGS. 26-32 illustrate a cross-sectional view of a memory cell array to illustrate an example of a manufacturing process of the semiconductor memory according to the second embodiment.

[0016] FIG. 33 illustrates a cross-sectional view of an example of a cross-sectional structure in a memory region of a memory cell array in a semiconductor memory according to a third embodiment.

[0017] FIGS. 34-40 illustrate a cross-sectional view of a memory cell array to illustrate an example of a manufacturing process of the semiconductor memory according to the third embodiment.

DETAILED DESCRIPTION

[0018] One or more of embodiments are directed to increasing a yield of a semiconductor memory.

[0019] In general, according to an embodiment, a semiconductor memory includes a substrate, a source line layer above the substrate in a memory region and a peripheral region of the substrate, a first insulating layer above the source line layer in the memory and peripheral regions, a first conductive layer on the first insulating layer in the memory and peripheral regions, an alternating stack of a plurality of second insulating layers and a plurality of second conductive layers on the first conductive layer in the memory region, and a plurality of pillars extending through the alternating stack of the second insulating layers and the second conductive layers, the first conductive layer, and the first insulating layer in the memory region, a bottom end of each of the pillars being in the source line layer in a thickness direction. A carrier density of the source line layer in the memory region is higher than a carrier density of the source line layer in the peripheral region.

[0020] Hereinafter, embodiments will be described with reference to the drawings. Each embodiment exemplifies an apparatus and a method for embodying the technical idea of the present disclosure. The drawings are schematic or conceptual ones, and sizes and ratios of the drawings are not necessarily the same as actual ones. The technical idea of the present disclosure is not specified by the shape, structure, arrangement, and the like of structural elements.

[0021] In the following description, structural elements having substantially the same functions and configurations are denoted by the same reference numerals. The numerals after characters making up reference numerals are used to distinguish between elements having the same structure and referenced by the reference numerals including the same characters. When it is unnecessary to distinguish the elements denoted by the reference symbols including the same characters from each other, these elements are referenced by reference numerals including only characters.

[1] First Embodiment

[0022] Hereinafter, a semiconductor memory 1 according to a first embodiment will be described.

[1-1] Configuration of Semiconductor Memory 1

[1-1-1] Overall Configuration of Semiconductor Memory 1

[0023] The semiconductor memory 1 is a NAND flash memory capable of storing data in a nonvolatile manner, for example. The semiconductor memory 1 is controlled by, for example, an external memory controller 2. FIG. 1 illustrates a configuration example of the semiconductor memory 1 according to the first embodiment.

[0024] As illustrated in FIG. 1, the semiconductor memory 1 includes, for example, a memory cell array 10, a command register 11, an address register 12, a sequencer 13, a driver module 14, a row decoder module 15, and a sense amplifier module 16.

[0025] The memory cell array 10 includes a plurality of blocks BLK0 to BLKn (n is an integer of 1 or more). In the memory cell array 10, a plurality of bit lines and a plurality of word lines are provided. The block BLK is a group of nonvolatile memory cells and is used as, for example, a unit of data erasure. Each memory cell is associated with one bit line and one word line. A detailed configuration of the memory cell array 10 will be described below.

[0026] The command register 11 stores a command CMD received by the semiconductor memory 1 from the memory controller 2. The command CMD includes, for example, an instruction to cause the sequencer 13 to execute a read operation, a write operation, an erasing operation, and the like.

[0027] The address register 12 stores address information ADD received from the memory controller 2 by the semiconductor memory 1. The address information ADD includes, for example, a block address BA, a page address PA, and a column address CA. The block address BA, the page address PA, and the column address CA are used to select the block BLK, the word line, and the bit line, respectively.

[0028] The sequencer 13 controls an operation of the entire semiconductor memory 1. For example, the sequencer 13 controls the driver module 14, the row decoder module 15, and the sense amplifier module 16 based on the command CMD stored in the command register 11 to execute the read operation, the write operation, the erasing operation, and the like.

[0029] The driver module 14 generates a voltage to be used for the read operation, the write operation, the erasing operation, and the like. Then, based on the page address PA stored in the address register 12, the driver module 14 applies generated voltages respectively to a signal line corresponding to a selected word line and to a signal line corresponding to a non-selected word line.

[0030] The row decoder module 15 selects one block BLK based on the block address BA stored in the address register 12. Then, for example, the row decoder module 15 transfers the voltages applied to the signal line corresponding to the selected word line and the signal line corresponding to the non-selected word line to the selected word line and the non-selected word line in the selected block BLK, respectively.

[0031] In the write operation, the sense amplifier module 16 applies a desired voltage to each bit line in accordance with write data DAT received from the memory controller 2. In the read operation, the sense amplifier module 16 determines data stored in the memory cell based on the voltage of the bit line, and transfers the determination result to the memory controller 2 as read data DAT.

[0032] Communication between the semiconductor memory 1 and the memory controller 2 supports, for example, the NAND interface standard. For example, in the communication between the semiconductor memory 1 and the memory controller 2, a command latch enable signal CLE, an address latch enable signal ALE, a write enable signal WEn, a read enable signal REn, a ready busy signal RBn, and an input and output signal I/O used.

[0033] The command latch enable signal CLE is a signal indicating that the input and output signal I/O received by the semiconductor memory 1 is the command CMD. The address latch enable signal ALE is a signal indicating that the signal I/O received by the semiconductor memory 1 is address information ADD. The write enable signal WEn is a signal instructing the semiconductor memory 1 to input the input and output signal I/O. The read enable signal REn is a signal instructing the semiconductor memory 1 to output the input and output signal I/O.

[0034] The ready busy signal RBn is a signal for notifying the memory controller 2 whether the semiconductor memory 1 is in a ready state for the semiconductor memory 1 to receive an instruction from the memory controller 2 or in a busy state in which an instruction is not received. The input and output signal I/O is, for example, an 8-bit width signal and may include the command CMD, the address information ADD, the data DAT, and the like.

[0035] The semiconductor memory 1 and the memory controller 2 described as above may be combined into to configure a single semiconductor device. Examples of such a semiconductor device include a memory card such as an SD.TM. card, a solid state drive (SSD), and the like.

[1-1-2] Circuit Configuration of Memory Cell Array 10

[0036] FIG. 2 illustrates an example of a circuit configuration of the memory cell array 10 in the semiconductor memory 1 according to the first embodiment by extracting one block BLK out of a plurality of the blocks BLKs in the memory cell array 10.

[0037] As illustrated in FIG. 2, the block BLK includes, for example, four string units SU0 to SU3. Each string unit SU includes a plurality of NAND strings NS respectively associated with bit lines BL0 to BLm (m is an integer of 1 or more).

[0038] Each NAND string NS includes, for example, eight memory cell transistors MT0 to MT7 and select transistors ST1 and ST2.

[0039] The memory cell transistor MT includes a control gate and a charge storage layer, and stores data in a nonvolatile manner. Each of the select transistors ST1 and ST2 is used for selecting the string unit SU during various operations.

[0040] In each NAND string NS, the memory cell transistors MT0 to MT7 are connected in series between a source of a select transistor ST1 and a drain of a select transistor ST2. Control gates of the memory cell transistors MT0 to MT7 in the same block BLK are jointly connected to word lines WL0 to WL7, respectively.

[0041] Gates of the select transistors ST1 in each of the string units SU0 to SU3 in the same block BLK are jointly connected to the select gate lines SGD0 to SGD3, respectively. Drains of the select transistors ST1 corresponding to the same column among the plurality of blocks BLK are jointly connected to the corresponding bit lines BL.

[0042] Gates of the select transistors ST2 in the same block BLK are jointly connected to a select gate line SGS. Sources of the select transistors ST2 in each block BLK are jointly connected to a source line SL among the plurality of blocks BLK.

[0043] A plurality of memory cell transistors MT connected to a common word line WL in one string unit SU is referred to as a cell unit CU, for example. A storage capacity of each cell unit CU changes based on the number of bits of data stored in the memory cell transistor MT.

[0044] For example, one cell unit CU stores one page of data when each of the memory cell transistors MT stores one bit data, and stores two pages of data when each of the memory cell transistors MT stores 2-bit data.

[0045] The "one page of data" is defined by the total amount of data stored in the cell unit CU including the memory cell transistors MT each of which stores 1-bit data, for example.

[1-1-3] Structure of Memory Cell Array 10

[0046] In the following, an example of a structure of the memory cell array 10 in the semiconductor memory 1 according to the first embodiment will be described.

[0047] In the drawings referenced below, the X-direction corresponds to an extending direction of the word line WL, the Y-direction corresponds to an extending direction of the bit line BL, and the Z-direction corresponds to the vertical direction with respect to the surface of the semiconductor substrate 20 on which the semiconductor memory 1 is formed. In order to make figures easy to see, hatching is appropriately added to each structural element in a plan view. The hatching added to the plan view is not necessarily related to the material or characteristics of the hatched structural element. In the cross-sectional view, structural elements such as an insulating layer (interlayer insulating film), interconnection, contact, and the like are appropriately omitted.

[0048] FIG. 3 illustrates an example of a planar layout of the memory cell array 10 according to the first embodiment by extracting a structure corresponding to the block BLK0 out of a plurality of blocks BLK arranged in the Y-direction.

[0049] As illustrated in FIG. 3, for example, each of the structures corresponding to the string units SU0 to SU3 of the block BLK0 extends in the X-direction, and they are arranged in the Y-direction. Structures corresponding to the string units SU0 to SU3 are surrounded by slits SLT, respectively. That is, between the string units SU adjacent in the Y-direction, a slit SLT extending in the X-direction is provided.

[0050] In other words, a plurality of slits SLT extending in the X-direction are arranged in the Y-direction. Two slits SLT extending in the Y-direction connect end portions on one side in the X-direction of the plurality of slits SLT extending in the X-direction and connect the other end portions, respectively. The structure formed by two slits SLT extending in the Y-direction and the slits SLT adjacent in the Y-direction corresponds to one string unit SU. In such regions surrounded by the slits SLT, a plurality of string units SU may be provided.

[0051] A region in which a structure corresponding to the string unit SU is provided is classified into a memory region MR and a drawing region HR. First, a detailed structure in the memory region MR of the string unit SU will be described.

[0052] The memory region MR is a region in which data is stored. In the memory region MR, a plurality of memory pillars MP are provided, for example, in a zigzag manner. Each of the memory pillars MP functions as, for example, one NAND string NS. The number of memory pillars MP illustrated in FIG. 3 is a schematic one, and the number of memory pillars MP is not limited to the number in this diagram.

[0053] FIG. 4 illustrates an example of a detailed planar layout in the memory region MR of the memory cell array 10 according to the first embodiment, extracting structures respectively corresponding to the string units SU0 and SU1.

[0054] As illustrated in FIG. 4, in the memory cell array 10, the plurality of bit lines BL and the plurality of contacts CP are arranged corresponding to the positions of the memory pillar MP, respectively.

[0055] Each of the plurality of bit lines BL extends in the Y-direction, and the plurality of bit lines BL are arranged in the X-direction. For example, two bit lines BL overlap each memory pillar MP. The number of bit lines BL overlapping each memory pillar MP may be any number.

[0056] Each contact CP is provided between the corresponding bit line BL and memory pillar MP. Each memory pillar MP is electrically connected to one bit line through the contact CP. When a plurality of bit lines BL overlap one memory pillar MP, a contact CP is provided between one of the bit lines BL overlapping the memory pillar MP and the memory pillar MP.

[0057] FIG. 5 illustrates a cross-sectional view of the memory cell array 10 taken along the line V-V of FIG. 4, and illustrates an example of a cross-sectional structure in the memory region MR of the memory cell array 10 in the first embodiment.

[0058] As illustrated in FIG. 5, in the memory region MR, the memory cell array 10 includes, for example, a conductor 21, conductors 22 to 24, an insulating layer 25, conductors 26 to 29, the memory pillars MP, the contact CP, and the slit SLT.

[0059] The conductor 21 is provided above the semiconductor substrate 20 with an insulating layer interposed therebetween. The conductor 21 is formed in a plate shape enlarging along the XY-plane, for example. The conductor 21 contains, for example, tungsten (W). In the region between the semiconductor substrate 20 and the conductor 21, for example, circuits such as the row decoder module 15 and the sense amplifier module 16 are provided (not illustrated).

[0060] The conductor 22 is provided on the conductor 21. The conductor 23 is provided on the conductor 22. The conductor 24 is provided on the conductor 23. Each of the conductors 22 to 24 is formed in a plate shape extending along the XY-plane, for example.

[0061] The respective conductors 21 to 24 are electrically connected to each other. A set of the conductors 21 to 24 is used as a source line SL. Hereinafter, the set of the conductors 21 to 24 will be referred to as a source line portion.

[0062] Each of the conductors 22 and 24 is, for example, non-doped polysilicon (Si). The conductor 23 is, for example, phosphorus doped polysilicon (Si).

[0063] On the conductor 24, the insulating layer 25 is provided. The insulating layer 25 includes an insulator such as silicon dioxide (SiO.sub.2), for example.

[0064] On the insulating layer 25, the conductor 26 is provided. The conductor 26 is formed in a plate shape enlarging along the XY-plane, for example. The conductor 26 is used as the select gate line SGS, for example. The conductor 26 is, for example, phosphorus doped polysilicon (Si).

[0065] On the conductor 26, an insulating layer and the conductor 27 are alternately stacked. The conductor 27 is formed in a plate shape enlarging along the XY-plane, for example. The plurality of stacked conductors 27 are used as word lines WL0 to WL7 in order from the semiconductor substrate 20 side. The conductor 27 contains tungsten (W), for example.

[0066] The conductor 28 is provided on the uppermost conductor 27 through an insulating layer. The conductor 28 is formed in a plate shape enlarging along the XY-plane, for example. The conductor 28 is used as the select gate line SGD, for example. The conductor 28 includes tungsten (W), for example.

[0067] The conductor 29 is provided on the conductor 28 with an insulating layer interposed therebetween. The conductor 29 is formed in a line shape extending along the Y-direction. The conductor 29 is used as the bit line BL. That is, the plurality of conductors 29 are arranged along the X-direction in a region (not illustrated). The conductor 29 contains copper (Cu), for example.

[0068] The memory pillar MP is formed in a columnar shape extending along the Z-direction and penetrates, for example, the conductors 23 and 24, the insulating layer 25, the conductor 26, the plurality of conductors 27, and the conductor 28.

[0069] The upper end of the memory pillar MP is included in a layer between a layer provided with the conductor 28 and a layer provided with the conductor 29.

[0070] The lower end of the memory pillar MP is included in the layer provided with the conductor 22, for example. In other words, the bottom surface of the memory pillar MP stops without passing through the conductor 22.

[0071] The memory pillar MP includes, for example, a core member 30, a semiconductor 31, a stacked film 32, and a conductor 33.

[0072] The core member 30 is formed in a columnar shape extending along the Z-direction. The upper end of the core member 30 is included in a layer between, for example, a layer provided with the conductor 28 and a layer provided with the conductor 29. The lower end of the core member 30 is included, for example, in the layer provided with the conductor 22. The core member 30 includes an insulator such as silicon dioxide (SiO.sub.2), for example.

[0073] The side surfaces and the lower surface of the core member 30 are covered with the semiconductor 31. The semiconductor 31 has a side surface contact portion SC. The side surface contact portion SC is included in the layer provided with the conductor 23. The semiconductor 31 contacts the conductor 23 at the side surface contact portion SC and is electrically connected to the conductor 23. The semiconductor 31 is polysilicon (Si), for example.

[0074] An example of the structure of the memory pillar MP in the cross-section including the conductor 23 and parallel to the surface of the semiconductor substrate 20 is illustrated in FIG. 6.

[0075] As illustrated in FIG. 6, the core member 30 is provided in the central portion of the memory pillar MP in the layer including the conductor 23. The semiconductor 31 surrounds the core member 30. The conductor 23 is in contact with side surfaces (side surface contact portion SC) of the semiconductor 31.

[0076] Returning to FIG. 5, the side surfaces and the bottom surface of the semiconductor 31 are covered with the stacked film 32. In the vicinity of the side surface contact portion SC, the stacked film 32 is not provided. Between the stacked film 32 provided in the vicinity of the side surface contact portion SC of the memory pillar MP, that is, provided at the upper portion of the memory pillar MP, and the stacked film 32 provided at the lower portion of the memory pillar MP, the conductor 23 is provided as described above.

[0077] An example of the structure of the memory pillars MP in the cross-section including the conductors 27 used as word lines WL and parallel to the surface of the semiconductor substrate 20 is illustrated in FIG. 7.

[0078] As illustrated in FIG. 7, the core member 30 is provided in the central portion of the memory pillar MP in the layer including the conductor 27. The semiconductor 31 surrounds the side surfaces of the core member 30. The stacked film 32 surrounds the side surfaces of the semiconductor 31. The stacked film 32 includes, for example, a tunnel oxide film 34, an insulating film 35, and a block insulating film 36.

[0079] The tunnel oxide film 34 is in contact with the semiconductor 31 and surrounds the side surface of the semiconductor 31. The insulating film 35 is in contact with the tunnel oxide film 34 and surrounds the side surfaces of the tunnel oxide film 34. The block insulating film 36 is in contact with the insulating film 35 and surrounds the side surfaces of the insulating film 35. The conductor 27 is in contact with the block insulating film 36 and surrounds the side surfaces of the block insulating film 36.

[0080] Returning to FIG. 5 again, the conductor 33 is formed on the core member 30 and the semiconductor 31. The conductor 33 is electrically connected to the semiconductor 31. The side surfaces of the conductor 33 are covered with the stacked film 32, for example. The conductor 33 is, for example, polysilicon (Si) and may be formed integrally with the semiconductor 31.

[0081] In the configuration of the memory pillar MP described above, for example, a portion where the memory pillar MP and the conductor 26 cross each other functions as the select transistor ST2. Portions where the memory pillars MP and the plurality of conductors 27 cross each other function as the memory cell transistors MT0 to MT7, respectively. A portion where the memory pillar MP and the conductor 28 cross each other functions as the select transistor ST1.

[0082] That is, the semiconductor 31 functions as a channel of the memory cell transistor MT and each of the select transistors ST1 and ST2. The insulating film 35 functions as a charge storage layer of the memory cell transistor MT.

[0083] The memory pillar MP may have a structure in which a plurality of pillars are connected in the Z-direction. For example, the memory pillar MP may have a structure in which a pillar passing through the conductor 28 (select gate line SGS) and a pillar passing through the plurality of conductors 27 (word lines WL) are connected. In addition, the memory pillar MP may have a structure in which a plurality of pillars each passing through the plurality of conductors 27 are connected in the Z-direction.

[0084] On the conductor 33 of the memory pillar MP, the columnar contact CP is provided. One conductor 29, that is, one bit line BL, is in contact with the upper surface of the contact CP. The memory pillar MP and the conductor 29 may be electrically connected through two or more contacts or may be electrically connected through wiring.

[0085] The slit SLT is formed in a plate shape extending along the Z-direction, and divides, for example, the conductors 23 and 24, the insulating layer 25, the conductor 26, the plurality of conductors 27, and the conductor 28. For that reason, in the semiconductor memory 1 according to the first embodiment, the conductor 26, the conductor 27, and the conductor 28 all have a shape extending in the X-direction.

[0086] The upper end of the slit SLT is included in a layer between the layer provided with the conductor 28 and the layer provided with the conductor 29. The lower end of the slit SLT is included in, for example, the layer provided with the conductor 22. In other words, the bottom surface of the slit SLT stops without passing through the conductor 22. However, it suffices that the slits SLT divide at least the conductors 26 to 28.

[0087] In addition, the slit SLT includes a step portion CT, and the step portion CT is a boundary between different widths of the slit. Specifically, the step portion CT is included in the insulating layer 25, for example. The slit width in the below the step portion CT is narrower than the slit width above the step portion CT.

[0088] An insulator 40 is provided inside the slit SLT. The insulator 40 includes an insulator such as silicon dioxide (SiO.sub.2), for example. The insulator 40 may be formed of plural kinds of insulators. For example, silicon nitride (SiN) may be formed as a side wall of the slit SLT before silicon dioxide is embedded in the slit SLT.

[0089] Next, returning to FIG. 3, a detailed structure in the drawing region HR of the string unit SU will be described.

[0090] The drawing region HR is a region for connecting the wiring connected to the NAND strings NS provided in the memory region MR and the row decoder module 15s.

[0091] In the drawing region HR, a plurality of conductors respectively corresponding to the select gate line SGS, the word lines WL0 to WL7, and the select gate line SGD are provided, for example, in a stepwise shape. In the example illustrated in FIG. 3, end portions of the conductors corresponding to the word lines WL are provided in two rows of stepwise shapes.

[0092] In the drawing region HR, contacts CC are provided corresponding to, for example, the select gate line SGS, the word lines WL0 to WL7, and the select gate line SGD, respectively. Each of the select gate line SGS, the word lines WL0 to WL7, and the select gate line SGD is electrically connected to the row decoder module 15 through the corresponding contact CC.

[0093] FIG. 8 illustrates a cross-sectional view of the memory cell array 11 taken along line VIII-VIII in FIG. 3 and illustrates an example of a cross-sectional structure of the memory cell array 10 in the drawing region HR in the first embodiment. In the region illustrated in FIG. 8, configurations corresponding respectively to the select gate line SGS, the word lines WL0, WL2, WL4, and WL6, and the select gate line SGD are displayed.

[0094] As illustrated in FIG. 8, in the drawing region HR, the memory cell array 10 includes, for example, conductors 21 to 24 and 26, conductors 27 and 28, a plurality of contacts CC, and conductors 52 to 54.

[0095] For example, the end portions of the conductors 26, the conductors 27, and the conductors 28 corresponding respectively to the select gate line SGS, the word line WL, and the select gate line SGD are provided in the stepwise shape as described above. Not limited to the stepwise shape, it is sufficient that in the drawing region HR, each of end portions of the conductors 26 to 28 has a portion which does not overlap at least the conductors 27 or 28 provided in the layers above.

[0096] Each contact CC is formed in a columnar shape extending along the Z-direction and includes, for example, a conductor 50 and a spacer 51. The conductor 50 is formed in a columnar shape extending from the upper surface to the lower surface of the contact CC. The spacer 51 is formed on the side surface of the conductor 50 and formed into a cylindrical shape. In other words, the side surfaces of the conductor 50 are covered with the spacer 51. The conductor 50 contains tungsten (W), for example. The spacer 51 includes an insulator such as silicon nitride (SiN), for example.

[0097] Each of the conductors 52 to 54 is a wiring for connecting between various wirings led out from the memory region MR to the drawing region HR and the row decoder module 15. The conductor 52 is provided corresponding to the conductor 26. Each of the plurality of conductors 53 is provided corresponding to the plurality of conductors 27. The conductor 54 is provided corresponding to the conductor 28.

[0098] A contact CC is provided on the end portion of the conductor 26, and the conductor 52 is provided on the contact CC. Contacts CC are provided on the end portions of the plurality of conductors 27, respectively, and conductors 53 are provided on the plurality of contacts CC, respectively. A contact CC is provided on the end portion of the conductor 28, and the conductor 54 is provided on the contact CC.

[0099] Each of the conductors 52 to 54 described above is electrically connected to the row decoder module 15 in a region that is not illustrated. The layers in which the conductors 52 to 54 are formed may be the same or different. The end portions of the conductor 26 and the conductors 27 and 28 and the corresponding conductors 52 to 54 may be electrically connected to each other through two or more contacts or may be electrically connected to each other through other wiring.

[0100] In the structure of the memory cell array 10 described above, the number of conductors 27 is designed based on the number of word lines WL. A plurality of conductors 26 provided in a plurality of layers may be allocated to the select gate line SGS. When the select gate line SGS is provided in a plurality of layers, conductors different from the conductors 26 may be used. A plurality of conductors 28 provided in a plurality of layers may be allocated to the select gate line SGD.

[0101] In this specification, the structure in which the slit SLT divides the conductors 27 and 28 is exemplified, but the slit SLT need not divide the conductor 28. In this case, the memory pillar MP has a structure in which a plurality of pillars are connected in the Z-direction, a pillar provided at the lower portion penetrates the conductor 27, and a pillar provided at the upper portion penetrates the conductor 28. In addition, the conductor 28 is divided by a slit different from the slit SLT, and each of the plurality of divided conductors 28 functions as a select gate line SGD.

[1-2] Manufacturing Method of Semiconductor Memory 1

[0102] FIG. 9 is a flowchart illustrating an example of a method for manufacturing the semiconductor memory 1 according to the first embodiment. Each of FIGS. 10 to 24 illustrates an example of a cross-sectional structure of a structure formed in the memory region MR in a manufacturing process of the semiconductor memory 1 according to the first embodiment.

[0103] In the following, with reference to FIG. 9 and any of FIGS. 10 to 24, an example of a method for manufacturing the semiconductor memory 1 will be described by extracting a series of processes from formation of the source line portion to formation of the slit SLT.

[0104] A peripheral region PR illustrated in the cross-sectional view referenced below corresponds to a region away from the slit SLT in the memory cell array 10 described with reference to FIG. 3. In the semiconductor memory 1 according to the first embodiment, for example, a contact penetrating the memory cell array 10 and electrically connected to a circuit on the semiconductor substrate 20 is formed in the peripheral region PR.

[0105] First, as illustrated in FIG. 10, the source line portion is stacked (Step S10).

[0106] Specifically, the interlayer insulating film 60 is formed on the semiconductor substrate 20, and the conductor 21 is formed on the interlayer insulating film 60. Then, the conductor 22, a sacrificial member 61, the conductor 24, and the insulating layer 25 are stacked in order on the conductor 21. Before the conductor 21 is formed, a circuit (not illustrated) is formed in the semiconductor substrate 20 and the interlayer insulating film 60.

[0107] As the sacrificial member 61, a material capable of increasing an etching selection ratio with respect to each of the conductors 22 and 24 is selected. The sacrificial member 61 is, for example, a semiconductor containing germanium (Ge), that is, silicon germanium (SiGe). In this example, it is assumed that each of the conductors 22 and 24 is a non-doped polysilicon film and the sacrificial member 61 is a silicon germanium film.

[0108] Next, as illustrated in FIG. 11, the conductor 26 is formed, and a plurality of replacement members 63 are stacked (Step S11).

[0109] Specifically, the conductor 26 is stacked on the insulating layer 25. The insulating layer 62 and the replacement member 63 are alternately stacked on the conductor 26. The number of layers in which the replacement member 63 is formed corresponds to the number of layers of the word line WL and the select gate line SGD to be stacked, for example. The insulating layer 62 contains silicon dioxide (SiO.sub.2), for example. The replacement member 63 includes, for example, silicon nitride (SiN).

[0110] Next, the structure in the drawing region HR is processed, and the structure in the peripheral region PR is processed as illustrated in FIG. 12 (Step S12).

[0111] Specifically, in the region not illustrated, the stacked replacement member 63 is processed into a stepwise structure as described with reference to FIG. 8, for example. Then, for example, the insulating layer 62 and the replacement member 63 in the peripheral region PR are removed by main processing.

[0112] Thereafter, an insulating film 64 is formed on the structure formed on the semiconductor substrate 20, and the formed insulating film 64 is planarized by chemical mechanical polishing (CMP), for example.

[0113] Next, as illustrated in FIG. 13, a memory hole MH is formed corresponding to a region where the memory pillar MP is to be formed (Step S13).

[0114] Specifically, first, a mask in which a region for forming the memory pillar MP is open is formed on the insulating film 64 by photolithography or the like. Then, by etching in which the formed mask is utilized, the memory hole MH is formed so as to reach the conductor 22 from the upper surface of the insulating film 64.

[0115] That is, in this step, the memory hole MH passes through the insulating film 64, the plurality of replacement members 63, the plurality of insulating layers 62, the conductor 26, the insulating layer 25, the conductor 24, and the sacrificial member 61. Then, the bottom of the memory hole MH stops in the layer in which the conductor 22 is formed, for example. As an etching method in this step, anisotropic etching such as a reactive ion etching (RIE) or the like is used.

[0116] In this process, the conductor 26 may be used as an etching stopper. By utilizing the conductor 26 as the etching stopper, the bottom of the memory hole MH is restrained from excessively entering into the inside of the conductor 22, and the bottoms of the plurality of memory holes MH can be more uniformly positioned.

[0117] Next, as illustrated in FIG. 14, the memory pillar MP is formed inside the memory hole MH (Step S14).

[0118] Specifically, for example, the stacked film 32 (block insulating film 36, insulating film 35, and tunnel oxide film 34), the semiconductor 31, and the core member 30 are formed in this order on the upper surface of the insulating film 64 and the inner wall of the memory hole MH, respectively.

[0119] Thereafter, the stacked film 32, the semiconductor 31, and the core member 30 formed above the upper surface of the insulating film 64 are removed, and the core member 30 provided above the memory hole MH is removed. The "upper portion of the memory hole MH" corresponds to a portion included above the upper surface of the replacement member 63 provided on the uppermost layer. Then, the semiconductor 33 is formed in the region where the core member 30 is removed inside each of the memory holes MH.

[0120] Next, as illustrated in FIG. 15, a protective film 65 is formed on the upper surface of the insulating film 64 and the upper surface of the memory pillar MP (Step S15). As the protective film 65, for example, silicon dioxide is formed.

[0121] Next, as illustrated in FIG. 16, the slit SLT is formed (Step S16).

[0122] Specifically, first, a mask which has openings at regions for forming the slits SLT is formed on the protective film 65 by photolithography or the like. Then, by etching in which the formed mask is utilized, the slit SLT is formed so as to reach the insulating layer 25 from the upper surface of the protective film 65.

[0123] That is, in this step, the slit SLT penetrates the protective film 65, the insulating film 64, the plurality of replacement members 63, the plurality of insulating layers 62, and the conductor 26. Then, the bottom of the slit SLT stops in the layer in which the insulating layer 25 is formed, for example. As an etching method in this step, for example, anisotropic etching such as RIE is used.

[0124] In the etching of this step, although it is preferable that the bottom of the slit SLT stop within the layer in which the insulating layer 25 is formed, the bottom of the slit SLT may reach the layer where the conductor 24 is formed.

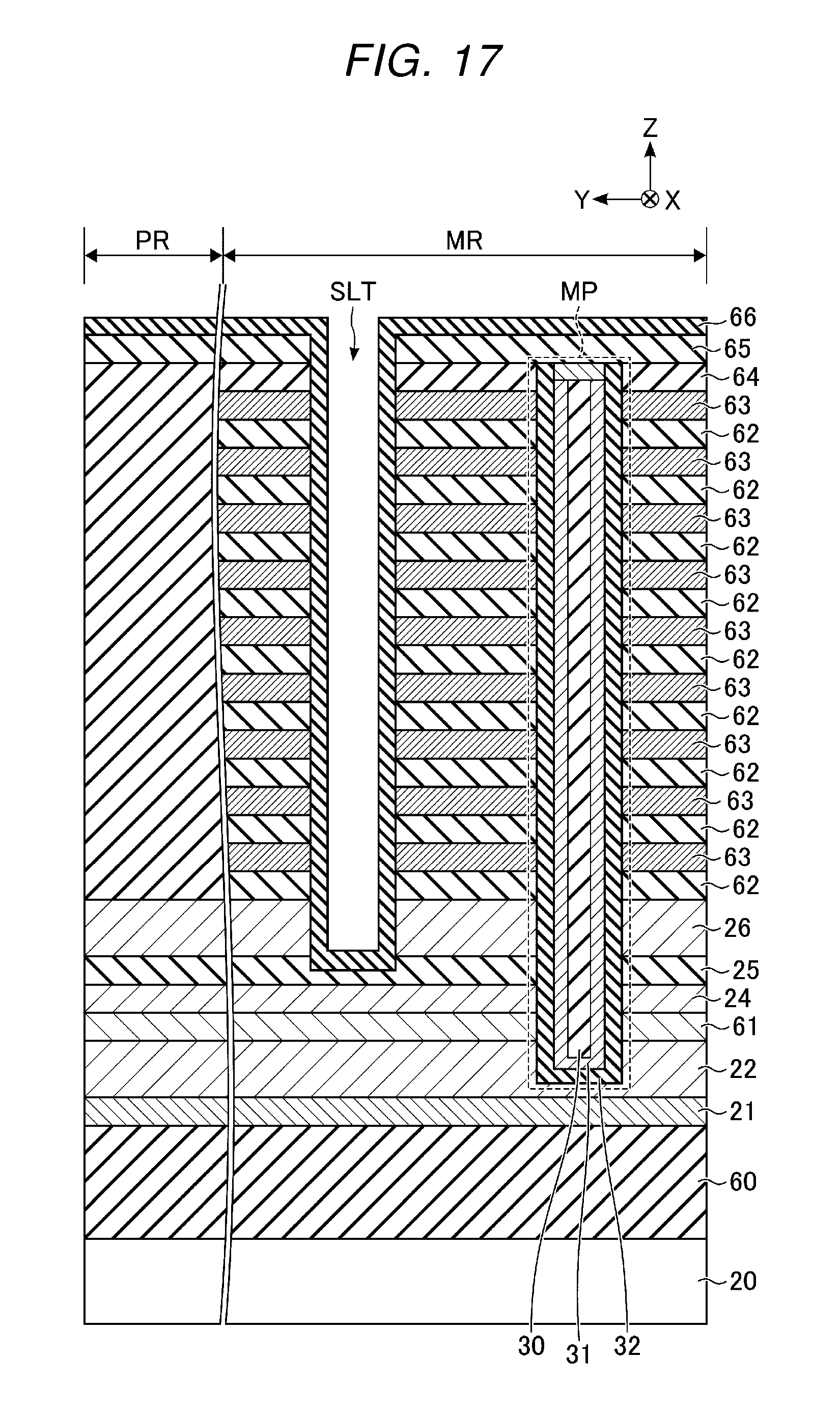

[0125] Next, as illustrated in FIG. 17, a spacer 66 is formed (Step S17).

[0126] Specifically, the spacer 66 is formed on the upper surface of the protective film 65 and on the inner walls of the slit SLT by chemical vapor deposition (CVD). As the spacer 66, for example, silicon nitride is formed.

[0127] Next, as illustrated in FIG. 18, the spacer 66 is processed (Step S18).

[0128] Specifically, the spacer 66 formed on the upper surface of the protective film 65 and the spacer 66 formed at the bottom of the slit SLT are removed by, for example, RIE. With this, side walls of silicon nitride, for example, are formed on the side surfaces of the slit SLT.

[0129] Etching in this step is continued even after the spacer 66 formed at the bottom of the slit SLT is removed. As a result, the bottom of the slit SLT reaches, for example, the layer in which the sacrificial member 61 is formed by etching in this step.

[0130] In this process, the slit SLT may penetrate the sacrificial member 61, or the bottom of the slit SLT may reach the inside of the layer in which the conductor 22 is formed. In this process, the slit SLT may reach at least the sacrificial member 61.

[0131] Next, as illustrated in FIG. 19, the sacrificial member 61 is removed (Step S19).

[0132] Specifically, when the sacrificial member 61 is formed of silicon germanium, the sacrificial member 61 is selectively etched through the slit SLT and the sacrificial member 61 is selectively removed by chemical dry etching (CDE) using, for example, chlorine trifluoride (ClF.sub.3) gas. As a result, the side surfaces of the stacked film 32 are exposed at the lower portion of the memory pillar MP. The sacrificial member 61 may remain in the peripheral region PR without being removed.

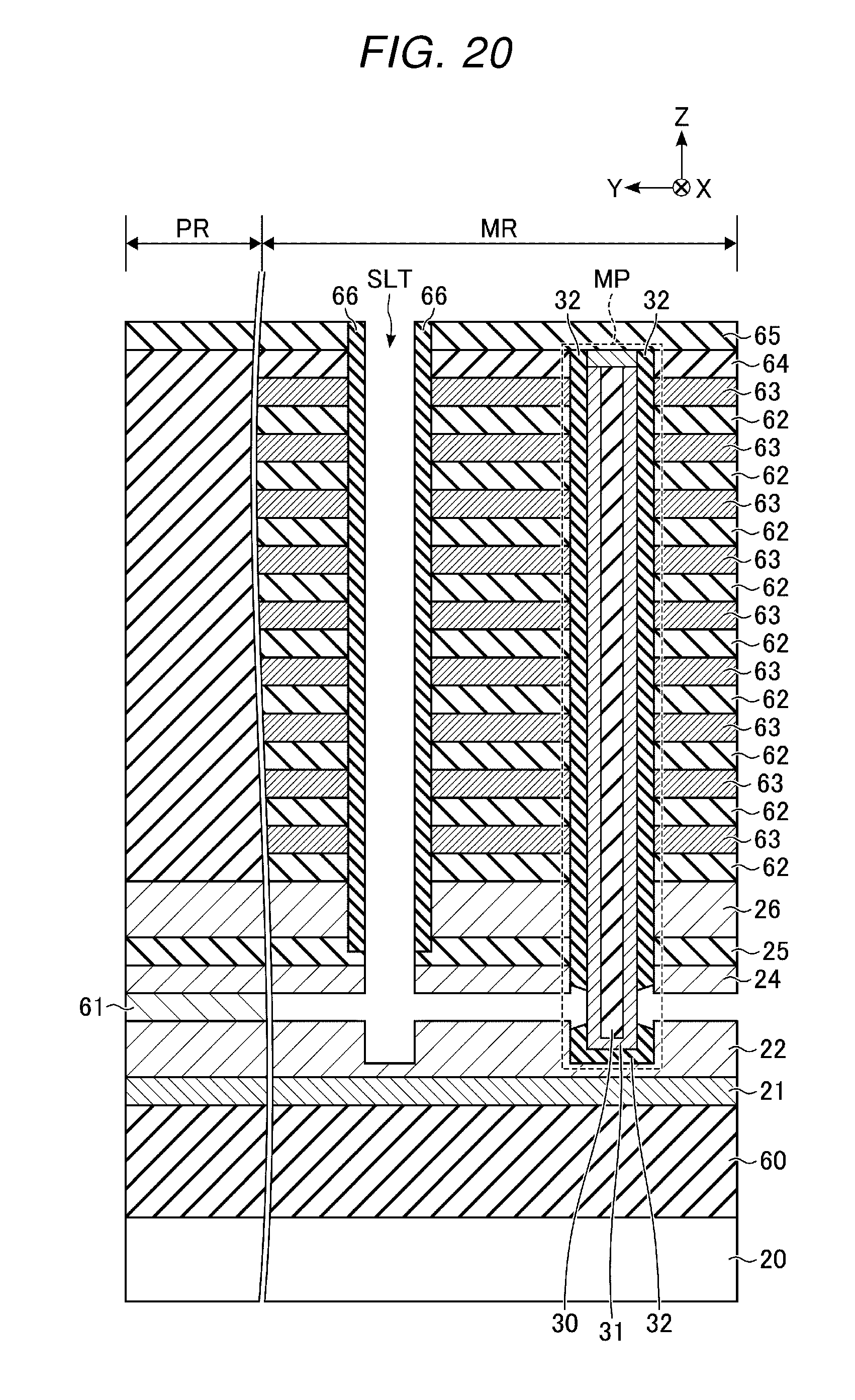

[0133] Next, as illustrated in FIG. 20, the stacked film 32 at the bottom of the memory pillar MP is removed (Step S20).

[0134] Specifically, the block insulating film 36, the insulating film 35, and the tunnel oxide film 34 are sequentially removed by wet etching or dry etching, for example. As a result, the side surfaces of the semiconductor 31 are exposed at the lower portion of the memory pillar MP.

[0135] Next, as illustrated in FIG. 21, the conductor 23 is formed (Step S21).

[0136] Specifically, the conductor 23 is formed in a space created after the sacrificial member 61 is removed in Step S20, by CVD, for example, and then etched back. As a result, the semiconductor 31 of the memory pillar MP and the source line portion (set of the conductors 21 to 24) are electrically connected. As the conductor 23, for example, phosphorus doped polysilicon is formed.

[0137] As a method of etching back after the conductor 23 is formed, isotropic etching is used, for example. In this process, although the space from which the sacrificial member 61 has been removed is embedded with the conductor 23 (for example, phosphorus doped polysilicon), a groove of the slit SLT is required not to be embedded with, for example, the conductor 23. In this case, a width of the bottom of the slit SLT needs to be larger than a width of the sacrificial member 61 in the stack direction.

[0138] Next, as illustrated in FIG. 22, the spacer 66 and the replacement member 63 are removed (Step S22).

[0139] Specifically, first, surfaces of the conductors 22 to 24 (polysilicon film) exposed in the slit SLT are oxidized, and an oxidation protective film (not illustrated) is formed thereon. When the oxidation protective film is formed on the surfaces of the polysilicon films, it is necessary that an oxide protective film is not formed on the surface of the spacer 66. That is, it is necessary to selectively oxidize when forming the oxidation protective film in this step.

[0140] Thereafter, the spacer 66 and the replacement member 63 are removed by, for example, wet etching with a hot phosphoric acid. A three-dimensional structure of the structure from which the replacement member 63 is removed is maintained, for example, by the memory pillar MP.

[0141] Next, as illustrated in FIG. 23, the conductors 27 and 28 are formed (Step S23).

[0142] Specifically, a conductor corresponding to the conductor 27 or 28 is formed in the space from which the replacement member 63 is removed in Step S22. For example, after a block film of aluminum oxide (Al.sub.2O.sub.3) or the like is formed, a metal film such as tungsten (W) is embedded.

[0143] Then, the conductor formed in the slit SLT is removed by wet etching, for example. Then, the plurality of conductors 27 and the conductors 28 provided in different layers are separated from each other. As a result, for example, the plurality of conductors 27 corresponding respectively to the word lines WL0 to WL7 and the conductor 28 corresponding to the select gate line SGD are formed, respectively.

[0144] Next, as illustrated in FIG. 24, the insulator 40 is formed in the slit SLT (Step S24). In this process, silicon nitride or the like may be formed as the side wall of the slit SLT before the insulator 40 is embedded in the slit SLT.

[0145] According to the manufacturing process described above, the NAND string NS, the source line SL connected to the NAND string NS, the select gate lines SGS and SGD, and the word line WL are formed, respectively. The manufacturing process described above is merely an example, and other processing may be inserted between each manufacturing process.

[1-3] Other Configuration of Source Line Portion

[0146] In the configuration and the manufacturing method of the memory cell array 10 described above, a stacked structure of the source line portion may have other configurations. For example, a combination of the material used as the conductors 22 and 24 and the material used as the sacrificial member 61 may be other combinations. Hereinafter, a first to seventh combinations of the conductors 22 and 24 and the sacrificial member 61 will be sequentially described.

First Combination

[0147] In the first combination, carbon (C) doped polysilicon (Si) is used as each of the conductors 22 and 24, and silicon germanium (SiGe) is used as the sacrificial member 61.

[0148] When the first combination is applied to the first embodiment, wet etching using an aqueous solution containing, for example, hydrogen fluoride (HF) and nitric acid (HNO.sub.3) is executed in Step S19 of the manufacturing process of the semiconductor memory 1.

Second Combination

[0149] In the second combination, nitrogen (N) doped polysilicon is used as each of the conductors 22 and 24, and silicon germanium is used as the sacrificial member 61.

[0150] When the second combination is applied to the first embodiment, wet etching using an aqueous solution containing, for example, hydrogen fluoride and nitric acid is executed in Step S19 of the manufacturing process of the semiconductor memory 1.

Third Combination

[0151] In the third combination, oxygen (O) doped polysilicon is used as each of the conductors 22 and 24, and silicon germanium is used as the sacrificial member 61.

[0152] When the third combination is applied to the first embodiment, wet etching using an aqueous solution containing, for example, hydrogen fluoride and nitric acid is executed in Step S19 of the manufacturing process of the semiconductor memory 1.

Fourth Combination

[0153] In the fourth combination, boron (B) doped polysilicon is used as each of the conductors 22 and 24, and silicon germanium is used as the sacrificial member 61.

[0154] When the fourth combination is applied to the first embodiment, wet etching using an aqueous solution containing, for example, hydrogen fluoride and nitric acid is executed in Step S19 of the manufacturing process of the semiconductor memory 1.

Fifth Combination

[0155] In the fifth combination, carbon doped polysilicon is used as each of the conductors 22 and 24, and non-doped polysilicon is used as the sacrificial member 61.

[0156] When the fifth combination is applied to the first embodiment, wet etching using an aqueous solution containing, for example, potassium hydroxide (KOH) is executed in Step S19 of the manufacturing process of the semiconductor memory 1.

Sixth Combination

[0157] In the sixth combination, nitrogen doped polysilicon is used as each of the conductors 22 and 24, and non-doped polysilicon is used as the sacrificial member 61.

[0158] When the sixth combination is applied to the first embodiment, wet etching using an aqueous solution containing, for example, choline is executed in Step S19 of the manufacturing process of the semiconductor memory 1.

Seventh Combination

[0159] In the seventh combination, oxygen doped polysilicon is used as each of the conductors 22 and 24, and non-doped polysilicon is used as the sacrificial member 61.

[0160] When the seventh combination is applied to the first embodiment, wet etching using an aqueous solution containing, for example, choline is executed in Step S19 of the manufacturing process of the semiconductor memory 1.

Eighth Combination

[0161] In the eighth combination, boron doped polysilicon is used as each of the conductors 22 and 24, and non-doped polysilicon is used as the sacrificial member 61.

[0162] When the eighth combination is applied to the first embodiment, wet etching using an aqueous solution containing, for example, tetramethylammonium hydroxide (TMAH) is executed in Step S19 of the manufacturing process of the semiconductor memory 1.

[0163] In each of the first to fourth combinations described above, silicon germanium is used as the sacrificial member 61. In the wet etching in Step S19, for example, an HF/HNO.sub.3 aqueous solution having a high etching rate of silicon germanium is used. As a result, in the etching of Step S19, the etching selection ratio between the conductors 22 and 24 and the sacrificial member 61 is increased, and the sacrificial member 61 can be selectively removed.

[0164] In each of the fifth to eighth combinations, non-doped polysilicon is used as the sacrificial member 61. Then, by using some impurities doped polysilicon as the conductors 22 and 24, the etching rate of the conductors 22 and 24 in the wet etching using an organic alkaline aqueous solution in Step S19 becomes low. As a result, in the etching of Step S19, the etching selection ratio between the conductors 22 and 24 and the sacrificial member 61 is increased, and the sacrificial member 61 can be selectively removed.

[0165] In the fourth and eighth combinations, it is desirable to compensate for boron of the conductors 22 and 24 formed in the region where the sacrificial member 61 is formed with the conductor 23 (for example, polysilicon doped with phosphorus), and operate the conductors 22 and 24 as an n-type semiconductor films as a whole. In other words, in the semiconductor layer of the source line portion formed by the conductors 22 to 24, it is desirable to make electron density higher than hole density. The reason for this is that the NAND string NS is desirably operated as an n-type NAND string NS, and it is necessary to make the conductors 22 and 24 used for the source line portion into n-type.

[0166] In the fourth and eighth combinations, in order to make the conductors 22 and 24 into an n-type semiconductor film, for example, phosphorus in the conductor 23 is diffused into the conductors 22 and 24 by heat treatment after the conductor 23 is formed. Then, each of the conductors 22 and 24 contains phosphorus and boron, and a doping amount of phosphorus exceeds a doping amount of boron.

[0167] As a result, in the semiconductor layer of the source line portion, the electron density exceeds the hole density, and each of the conductors 22 and 24 can be operated as the n-type.

[0168] In the description as above, although the case where the conductors 22 and 24 are made of the same material is described by way of an example, the conductor 22 and the conductor 24 may have different compositions. For example, concentrations of impurities doped in the conductor 22 and the conductor 24 may be different from each other, or the impurities doped in the conductor 22 and the impurities doped in the conductor 24 may be different from each other.

[0169] In the configuration and the method for manufacturing the semiconductor memory 1 according to the first embodiment described above, polysilicon may be in an amorphous state at the time of film formation. For example, in the manufacturing process of the semiconductor memory 1, the conductor 23 formed in Step S21 may be in the amorphous state by reducing heat treatment in the middle. A silicon film formed in the amorphous state is crystallized by, for example, subsequent heat treatment.

[1-4] Effects of First Embodiment

[0170] According to the semiconductor memory 1 according to the first embodiment described above, a yield of the semiconductor memory 1 can be improved. Details of this effect will be described below.

[0171] In a manufacturing process of a semiconductor memory device in which memory cells are three-dimensionally stacked, a memory hole is formed after a stacked body in which replacement members and insulating layers are alternately stacked is formed. In the memory hole, a multilayer film including, for example, an oxide-nitride-oxide (ONO) film and a channel semiconductor is formed, and a memory pillar functioning as a NAND string is formed. In each memory pillar, for example, the ONO film at the bottom is removed and the channel semiconductor in the memory pillar is electrically connected to the source line through the bottom surface of the memory pillar.

[0172] Thereafter, a slit is formed in the structure on which the memory cell array is formed, and processing of replacing the replacement member with a semiconductor is executed. As a result, a stacked wiring structure in which wiring connected to the NAND string NS is stacked is formed. As a method of increasing storage capacity per unit area in such a semiconductor memory device, it is conceivable to increase the number of stacked word lines and increase the number of memory cells in one NAND string.

[0173] However, when the number of stacked word lines is increased, an aspect ratio of the memory hole is increased, and difficulty of removing the ONO film formed at the bottom of the memory hole is increased by RIE or the like. That is, as the aspect ratio of the memory hole becomes higher, it may become more difficult to secure contact of the source line from the bottom surface of the memory pillar.

[0174] In contrast, in the semiconductor memory 1 according to the first embodiment, the channel semiconductor (semiconductor 31) in the memory pillar MP and the source line SL (for example, conductor 23) are electrically connected through the lower side surface of the memory pillar MP.

[0175] Specifically, in the manufacturing process of the semiconductor memory 1 according to the first embodiment, first, a conductor 22, a sacrificial member 61, and a conductor 24 are stacked in this order, as the source line portion. After the slit SLT is formed and before replacement processing of the word line WL and the like is executed, the sacrificial member 61 is removed via the slit SLT. Thereafter, the ONO film (stacked film 32) on the lower side surface of the memory pillar is removed through the space from which the sacrificial member 61 is removed, and the conductor 23 is formed in the space.

[0176] As a result, in the semiconductor memory 1 according to the first embodiment, the semiconductor 31 in the memory pillar MP and the conductor 23 in the source line portion are in contact with the lower side surface of the memory pillar MP. That is, the channel semiconductor of the memory pillar MP and the source line SL are electrically connected through the lower side surface of the memory pillar MP.

[0177] In the method for manufacturing the semiconductor memory 1 according to the first embodiment, contacts with the source line SL on the lower side surface of the memory pillar MP are formed so as to make it possible to omit RIE for the bottom of the memory hole MH having a high aspect ratio.

[0178] With this configuration, in the method for manufacturing the semiconductor memory 1 according to the first embodiment, it is possible to reduce process difficulty at the time of forming the contact of the source line SL and to alleviate restriction at the time of processing the memory hole MH. Accordingly, in the method for manufacturing the semiconductor memory 1 according to the first embodiment, it is possible to improve the yield of the semiconductor memory 1.

[0179] In the semiconductor memory 1 according to the first embodiment, the following effects can be further obtained. Other effects of the semiconductor memory 1 according to the first embodiment will be listed below.

[0180] In the method for manufacturing the semiconductor memory 1 according to the first embodiment, the area of the contact between the semiconductor 31 in the memory pillar MP and the source line portion can be more uniform, so that variation in characteristics of the NAND string NS can be reduced.

[0181] In the method for manufacturing the semiconductor memory 1 according to the first embodiment, a material capable of achieving a high etching selection ratio between the sacrificial member 61 and the conductors 22 and 24 sandwiching the sacrificial member 61 is selected. The conductors 22 and 24 and the sacrificial member 61 basically have a stacked structure of semiconductor films made of homologous elements. An example of the stacked structure of the source line portion is Si/SiGe/Si (conductor 22/sacrificial member 61/conductor 24).

[0182] In this case, in the method for manufacturing the semiconductor memory 1 according to the first embodiment, complicated step switching is unnecessary in RIE for forming the memory hole MH. That is, in the method for manufacturing the semiconductor memory 1 according to the first embodiment, processing of the memory hole MH is facilitated and controllability of a hole diameter of the memory hole MH is improved. Accordingly, in the method for manufacturing the semiconductor memory 1 according to the first embodiment, the yield and the variation in characteristics can be favorably changed.

[0183] In the manufacturing process of the semiconductor memory 1 according to the first embodiment, in the process of removing the sacrificial member 61, the conductor 26 is protected by the spacer 66 being formed between the opening of the slit SLT and the conductor 26. On the other hand, the conductors 22 and 24 have a high etching selection ratio with respect to the sacrificial member 61, so that it is possible to prevent the conductors 22 and 24 from being processed into an unintended shape by etching in this step.

[0184] For that reason, in the semiconductor memory 1 according to the first embodiment, the side surfaces of the conductors 22 and 24 need not be protected when removing the sacrificial member 61, and a range in which the spacers 66 are formed can be narrowed.

[0185] As a result, in the semiconductor memory 1 according to the first embodiment, it is possible to prevent defective embedding of the conductor 23, which can occur when the range where the spacer 66 is formed reaches the layer in which the sacrificial member 61 is formed. Accordingly, in the method for manufacturing the semiconductor memory 1 according to the first embodiment, it is possible to stably form the conductor 23, and the yield can be increased.

[0186] In the method for manufacturing the semiconductor memory 1 according to the first embodiment, the conductor 23 (for example, phosphorus doped polysilicon) is embedded in the space from which the sacrificial member 61 is removed. This conductor 23 is also formed on the side walls and the bottom of the slit SLT. Then, the conductor 23 formed on the side walls and bottom of the slit SLT is removed by etching back.

[0187] A film thickness of the conductor 23 formed in the slit SLT varies based on a layer thickness of the sacrificial member 61. For that reason, in the semiconductor memory 1 according to the first embodiment, it is possible to reduce the film thickness of the conductor 23 in the slit SLT by preventing the layer thickness of the sacrificial member 61.

[0188] When the layer thickness of the sacrificial member 61 is designed as thin as possible, an etching back amount after forming the conductor 23 can be reduced. As a result, in the semiconductor memory 1 according to the first embodiment, the width of the slit SLT can be reduced. Accordingly, in the semiconductor memory 1 according to the first embodiment, it is possible to reduce the area of the memory cell array 10 and reduce the manufacturing cost.

[0189] In the structure of the semiconductor memory 1 according to the first embodiment, there may be a region (for example, peripheral region PR) where the sacrificial member 61 remains. In the peripheral region PR, a through-contact for connecting a wiring (for example, conductor 53) drawn out from the word line WL or the like, for example, to a circuit on the semiconductor substrate 20 is formed. Such a through contact is insulated from the source line portion by, for example, a spacer insulating film formed on the side walls of the through contact.

[0190] Also in such a case, since the sacrificial member 61 in the semiconductor memory 1 according to the first embodiment is in a state of being electrically connected to each of the conductors 22 and 24, unintended charge accumulation or the like is prevented.

[0191] As a result, in the semiconductor memory 1 according to the first embodiment, it is possible to prevent short-circuit defects that are induced to occur in a region in which the sacrificial member 61 remains and the through-contact penetrates the source line portion. Accordingly, in the semiconductor memory 1 according to the first embodiment, it is easy to identify defects relating to the source line portion, and the yield can be increased.

[0192] When any one of the fifth to eighth combinations is applied to the semiconductor memory 1 according to the first embodiment, the only differences between the conductors 22 and 24 and the sacrificial member 61 are the kind and amount of impurities to be doped.

[0193] For that reason, the manufacturing cost of the semiconductor memory 1 when any one of the fifth to eighth combinations is applied may be lower than the manufacturing cost of the semiconductor memory 1 to which any one of the first to fourth combinations in which SiGe is used is applied.

[2] Second Embodiment

[0194] A semiconductor memory 1 according to a second embodiment is different from that according to the first embodiment in the stacked structure of the source line portion. Hereinafter, points of the semiconductor memory 1 according to the second embodiment that are different from the first embodiment will be described.

[2-1] Structure of Memory Cell Array 10

[0195] FIG. 25 illustrates an example of a cross-sectional structure in the memory region MR of the memory cell array 10 in the second embodiment by extracting a region similar to FIG. 5 described in the first embodiment.

[0196] As illustrated in FIG. 25, the memory cell array 10 in the second embodiment has a structure in which a thin film 70 is provided between the conductors 22 and 23 and a thin film 71 is provided between the conductors 23 and 24, in the memory cell array 10 in the first embodiment described with reference FIG. 5.

[0197] The thin films 70 and 71 are insulators such as silicon dioxide (SiO.sub.2) and silicon nitride (SiN), for example. The thickness of the thin film 70 is designed so as not to electrically insulate the conductors 22 and 23. The thickness of the thin film 71 is designed so as not to electrically insulate the conductors 23 and 24. The thickness of each of the thin films 70 and 71 is desirably 2 nm or less, for example.

[0198] The same material or different materials may be used for the thin films 70 and 71. Each of the thin films 70 and 71 may contain impurities contained in the semiconductor layer which is in contact therewith. In addition, the film thickness of the thin film 70 and the film thickness of the thin film 71 may be the same or different.

[0199] The other structure of the semiconductor memory 1 according to the second embodiment is the same as that of the first embodiment and thus description thereof will be omitted.

[2-2] Manufacturing Method of Semiconductor Memory 1

[0200] The method for manufacturing the semiconductor memory 1 according to the second embodiment is, for example, the same as the flowchart described with reference to FIG. 9 in the first embodiment. Each of FIGS. 26 to 32 illustrates an example of a cross-sectional structure of a structure formed in the memory region MR in the manufacturing process of the semiconductor memory 1 according to the second embodiment.

[0201] Hereinafter, regarding the method for manufacturing the semiconductor memory 1 according to the second embodiment, points different from those of the first embodiment will be described with reference to FIG. 9 and FIGS. 26 to 32.

[0202] First, in Step S10, a source line portion is stacked as illustrated in FIG. 26. Specifically, the interlayer insulating film 60 is formed on the semiconductor substrate 20, and the conductor 21 is formed on the interlayer insulating film 60. Then, the conductor 22, the thin film 70, the sacrificial member 61, the thin film 71, the conductor 24, and the insulating layer 25 are stacked in order on the conductor 21.

[0203] Next, processing of steps S11 to S13 is executed in order. Briefly, the conductor 26 is formed on the insulating layer 25, and the insulating layer 62 and the replacement member 63 are alternately stacked thereon. Thereafter, the drawing region HR is processed, and the insulating film 64 is formed. Then, as illustrated in FIG. 27, the memory hole MH is formed.

[0204] In this process, the memory hole MH is formed so as to reach the conductor 22 from the upper surface of the insulating film 64 similarly as in the first embodiment. That is, in this step, the memory hole MH penetrates the insulating film 64, the plurality of replacement members 63, the plurality of insulating layers 62, the conductor 26, the insulating layer 25, the thin film 71, the conductor 24, the sacrificial member 61, and the thin film 70. Then, the bottom of the memory hole MH stops in the layer in which the conductor 22 is formed, for example.

[0205] Next, processing of Steps S14 to S16 is executed in order. Briefly, the memory pillar MP is formed inside the memory hole MH. Thereafter, the protective film 65 is formed on each of the upper surface of the insulating film 64 and the upper surface of the memory pillar MP. Then, as illustrated in FIG. 28, the slit SLT is formed.

[0206] Next, processing of Steps S17 and S18 is executed. Briefly, the spacers 66 are formed on each of the upper surface of the protective film 65 and the inner wall of the slit SLT. Then, the spacer 66 formed on the upper surface of the protective film 65 and the spacer 66 formed on the bottom of the slit SLT are removed by, for example, RIE.

[0207] Etching in this step is continued even after the spacer 66 formed at the bottom of the slit SLT is removed. By the etching, the bottom of the slit SLT reaches, for example, the layer in which the conductor 22 is formed, as illustrated in FIG. 29.

[0208] That is, the slit SLT penetrates the protective film 65, the insulating film 64, the plurality of replacement members 63, the plurality of insulating layers 62, the conductor 26, the insulating layer 25, the thin film 71, the conductor 24, the sacrificial member 61, and the thin film 70. Then, the bottom of the slit SLT stops in the layer in which the conductor 22 is formed, for example.

[0209] Next, processing of Step S19 is executed, and the sacrificial member 61 is removed as illustrated in FIG. 30. Similarly as in the first embodiment, the sacrificial member 61 may remain without being removed in the peripheral region PR.

[0210] Next, processing of Step S20 is executed, and the stacked film 32 at the bottom of the memory pillar MP is removed, as illustrated in FIG. 31. In FIG. 31, an example where the thin films 70 and 71 remain after processing of this step is shown. The thin films need not remain; the thin films 70 and 71 in the memory region MR may be removed by etching in this step.

[0211] Next, processing of Step S21 is executed, and the semiconductor 23 is formed as illustrated in FIG. 32. Details of the manufacturing process of the semiconductor memory 1 according to the second embodiment and other manufacturing processes are the same as those of the first embodiment, and thus, description thereof will be omitted.

[2-3] Effects of Second Embodiment

[0212] As described above, in the manufacturing process of the semiconductor memory 1 according to the second embodiment, the thin film 70 is provided between the conductor 22 and the sacrificial member 61, and the thin film 71 is provided between the conductor 24 and the sacrificial member 61, as opposed to the manufacturing process of the semiconductor memory 1 described in the first embodiment.

[0213] The thin film 70 can prevent diffusion of impurities between the conductor 22 and the sacrificial member 61 in heat treatment. The thin film 71 can prevent diffusion of impurities between the conductor 24 and the sacrificial member 61 in heat treatment.

[0214] With this configuration, in the manufacturing process of the semiconductor memory 1 according to the second embodiment, impurity concentrations of the conductors 22 and 24 and the sacrificial member 61 are less likely to change in a period from formation of the source line portion to formation of the conductor 23.

[0215] As a result, in the method for manufacturing the semiconductor memory 1 according to the second embodiment, the etching rate of each of the conductors 22 and 24 and the sacrificial member 61 can be more uniform, and shape of the source line portion can be more uniform. Accordingly, in the method for manufacturing the semiconductor memory 1 according to the second embodiment, it is possible to prevent occurrence of defects caused by contact of the source line SL, and it is possible to improve the yield.

[3] Third Embodiment

[0216] The semiconductor memory 1 according to a third embodiment is different from the first embodiment in the stacked structure of the source line portion. In the following, differences of the semiconductor memory 1 according to the third embodiment from the first and second embodiments will be described.

[3-1] Structure of Memory Cell Array 10

[0217] FIG. 33 illustrates an example of the cross-sectional structure in the memory region MR of the memory cell array 10 in the third embodiment by extracting the region similar to FIG. 5 described in the first embodiment.

[0218] As illustrated in FIG. 33, the memory cell array 10 in the third embodiment has a structure in which an insulating film 80 is provided between the conductors 22 and 23 and an insulating film 81 is provided between the conductors 23 and 24, in the memory cell array 10 in the first embodiment described with reference FIG. 5.