Wafer Scale Test Interface Unit: Low Loss and High Isolation Devices and Methods for High Speed and High Density Mixed Signal In

Thompson; Rick L. ; et al.

U.S. patent application number 16/426459 was filed with the patent office on 2019-09-12 for wafer scale test interface unit: low loss and high isolation devices and methods for high speed and high density mixed signal in. The applicant listed for this patent is Cubic Corporation. Invention is credited to Anatoliy O. Boryssenko, Jean Marc Rollin, Rick L. Thompson, Kenneth Vanhille.

| Application Number | 20190277910 16/426459 |

| Document ID | / |

| Family ID | 53543624 |

| Filed Date | 2019-09-12 |

View All Diagrams

| United States Patent Application | 20190277910 |

| Kind Code | A1 |

| Thompson; Rick L. ; et al. | September 12, 2019 |

Wafer Scale Test Interface Unit: Low Loss and High Isolation Devices and Methods for High Speed and High Density Mixed Signal Interconnects and Contactors

Abstract

Devices and methods for multilayer packages, antenna array feeds, test interface units, connectors, contactors, and large format substrates.

| Inventors: | Thompson; Rick L.; (Amherst, NH) ; Vanhille; Kenneth; (Cary, NC) ; Boryssenko; Anatoliy O.; (Belchertown, MA) ; Rollin; Jean Marc; (Chapel Hill, NC) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 53543624 | ||||||||||

| Appl. No.: | 16/426459 | ||||||||||

| Filed: | May 30, 2019 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 15111252 | Jul 13, 2016 | 10310009 | ||

| PCT/US15/11789 | Jan 16, 2015 | |||

| 16426459 | ||||

| 61928767 | Jan 17, 2014 | |||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | G01R 1/0491 20130101; G01R 1/07357 20130101; G01R 1/06722 20130101; H01Q 21/065 20130101; H01Q 1/2283 20130101; G01R 1/06716 20130101; H01Q 21/0093 20130101; G01R 31/2889 20130101; G01R 1/07307 20130101; G01R 1/07378 20130101; H01Q 21/0006 20130101 |

| International Class: | G01R 31/28 20060101 G01R031/28; H01Q 21/00 20060101 H01Q021/00; G01R 1/067 20060101 G01R001/067; G01R 1/073 20060101 G01R001/073 |

Claims

1. A wafer level test interface device, comprising a contactor probe assembly having a housing with a plurality of passageways extending therethrough from a first surface of the housing to an opposing second surface of the housing, the housing comprised of a plurality of planar conductive strata adjoining one another, each stratum disposed parallel to the first surface of the housing, and comprising a plurality of conductive probes, each probe disposed in a receptive one of the passageways.

2. The wafer level test interface device of claim 1, wherein the conductive probes have end portions that extend outward from the first surface of the probe assembly, and wherein the end portions are resiliently movable relative to the first surface of the probe assembly.

3. The wafer level test interface device of claim 2, wherein the conductive probes have end portions that extend outward from the second surface of the probe assembly, and wherein the end portions are resiliently movable relative to the second surface of the probe assembly.

4. The wafer level test interface device of claim 1, wherein the conductive probes comprise a spring.

5. The wafer level test interface device of claim 4, wherein the spring is comprised of a plurality of layers of a conductive material.

6. The wafer level test interface device of claim 5, wherein the spring comprises a "C"-shape.

7. The wafer level test interface device of claim 5, wherein the spring comprises alternating "C"-shaped sections where each "C"-shaped section comprises a flexure.

8. The wafer level test interface device of claim 1, wherein the passageways have respective ends spaced relative to one another at the first surface separated by a first distance and have respective ends spaced relative to one another at the second surface separated by a second distance which is larger than the first distance.

9. A method of forming a wafer level test interface device comprising a contactor probe assembly by a sequential build process, comprising: sequentially depositing a plurality of strata on top of one another, wherein the plurality of strata comprises one or more layers of a conductive material and one or more layers of a sacrificial material, the plurality of strata collectively providing a housing with a plurality of passageways extending therethrough from a first surface of the housing to an opposing second surface of the housing, the housing comprised of a plurality of planar conductive strata adjoining one another, each stratum disposed parallel to the first surface of the housing; and, providing a conductive probe in each of a receptive one of the passageways.

10. The method of claim 9, wherein the conductive probes have end portions that extend outward from the first surface of the probe assembly, and wherein the end portions are resiliently movable relative to the first surface of the probe assembly.

11. The method of claim 10, wherein the conductive probes have end portions that extend outward from the second surface of the probe assembly, and wherein the end portions are resiliently movable relative to the second surface of the probe assembly.

12. The method of claim 9, wherein the conductive probes comprise a spring.

13. The method of claim 12, wherein the spring is comprised of a plurality of layers of the conductive material.

14. The wafer level test interface device of claim 13, wherein the spring comprises a "C"-shape.

15. The method of claim 13, wherein the spring comprises alternating "C"-shaped sections where each "C"-shaped section comprises a flexure.

16. The method of claim 9, wherein the passageways have respective ends spaced relative to one another at the first surface separated by a first distance and have respective ends spaced relative to one another at the second surface separated by a second distance which is larger than the first distance

Description

RELATED APPLICATIONS

[0001] This application is a continuation of U.S. application Ser. No. 15/111,252 filed on Jul. 13, 2016, now U.S. Pat. No. 10,310,009 issued on Jun. 4, 2019, which is a 371 application of International Application No. PCT/US2015/011789 filed Jan. 16, 2015, which claims the benefit of priority of U.S. Provisional Application No. 61/928,767 filed on Jan. 17, 2014, the entire contents of which application(s) are incorporated herein by reference.

FIELD OF THE INVENTION

[0002] The present invention relates generally to mixed signal RF, high speed digital interconnects, shielded DC lines, and more particularity, but not exclusively, to their implementation for multilayer packages, antenna array feeds, test interface units, connectors, contactors, and large format substrates, including methods for their fabrication.

BACKGROUND OF THE INVENTION

[0003] Printed Circuit Boards (PCB) are the current mainstay for virtually all integrated circuit assembly and packaging today for computers, laptops, cell phones, cameras, TVs, appliances, avionics, etc. However new high speed and high density circuit technologies are emerging which will severely impact PCB performance. As Moore's Law for integrated circuits continues to scale toward smaller transistor sizes, the results are higher clock rate frequencies and increased functionality as more transistors are packed into ever smaller areas. Consequently, new integrated circuit inputs and outputs (I/O) are physically smaller, are much closer together in spacing (called pitch), can be either RF, DC, analog or digital, and operate at much higher data rates and higher frequencies.

[0004] Current PCB materials and construction methods are not scalable for the smaller geometries and higher densities of the new integrated circuits and are inadequate as the clock rates approach 100 Gigabits per second (Gb/s). Presently, PCB high speed digital and RF interconnects are implemented as transmission lines; either microstrip or stripline to control the impedance (usually 50 ohms). These lines are manufactured using metal foil bonded to organic substrate or dielectric material using: (i) glass-reinforced epoxy laminate sheets (called FR-4); or (ii) polytetrafluoroethylene (trade name is called Teflon); or (iii) a flexible material such as polyimide; or (iv) a combination of thereof. Patterns are etched into the foil to form interconnects and vias are drilled and plated. To make multilayer PCB, subsequent sheets are processed similarly and finally all the respective layers are bonded together using heat and pressure to form a signal multilayer PCB. The final step in the process is to plate the top and bottom surfaces with a material suitable for assembly (gold or solder) and then coated with a material to seal the inner layers and provide a solder stop or resist.

[0005] As a function of Moore's Law, integrated circuits continue grow in the number of transistors per chip and proportionately need more I/O for a given chip. The effect of more I/O in a given area causes the pitch of the contacts of the I/O to be smaller. The construction methods of PCB by etching foil bonded to organic materials is limited in how small the interconnects can be patterned. Another limitation is the via size needed to route a signal from one layer of the PCB to another layer. In addition to the size of the via, minimum spacing rules between the vias and the conductive `capture pads` around the vias increases the trace-to-trace pitch achievable with PCB technologies. Also, multiple rows of vias are necessary for optimal trace-to-trace isolation. Multiple layers are needed for all the I/O to "escape" the small area of the chip and be routed to other destinations on the PCB. The more signal interconnects needed result in more layers and a thicker PCB. The thicker a PCB is, the bigger the via is, since a bigger drill bit is needed to drill through thicker PCB materials. The bigger vias cause congestion in the interconnects around the chip I/O escape area which also degrades performance.

[0006] Due to these construction methods, PCB signal interconnects are in direct contact with the dielectric material and thus a major source of signal loss, especially at higher data rates and RF frequencies (called dielectric loss). Another source of higher frequency loss is due to the skin effects of the metal foil interconnects; the surface roughness of the interconnect causes signal loss to electromagnetic wave propagation (called skin effect loss). Moreover, the skin effects are most severe at the bottom of the metal interconnect trace as the copper foil must have a certain amount of surface roughness to ensure adequate bonding strength to the PCB substrate material. Bigger vias (as described above) are another source of loss in the signal (called a discontinuity).

[0007] Another major problem with PCB materials and construction techniques is the isolation or crosstalk between two adjacent digital signal interconnects. Crosstalk is when the energy content of one signal (sometimes referred to as the "offender" line) is transferred onto a different signal (called the "victim") and causing signal degradation or a bit error of the victim. As the data rates increase to 100 Gb/s the frequency content of the signal also increases which makes it easier for the offender data lines to contaminate the victim digital data lines. The crosstalk problem becomes quite acute as the pitch of signal interconnects becomes closer together.

[0008] PCB interfaces are connections and contactors that serve to make or break between: (i) two different PCBs; (ii) a PCB and a cable; (iii) a PCB and a test interface unit; and (iv) test interface unit to a device under test (DUT). A DUT may typically be one or more semiconductor die on a wafer or removed from a wafer. For each of these interfaces, the contactors must take different form factors to serve the application. For example, PCB-to-PCB interface might require just a few mating cycles for a given mean time between failure (MTBF). A PCB-to-cable will require a higher number of mating cycles between failure. And finally a test interface unit will have a specified number of make-break cycles of the contactors. All of the contactors interfaces are inadequate for 100 Gb/s (loss and crosstalk performance) or are limited in very high signal density as a function of very small pitches demanded by new semiconductors.

[0009] Thus, it would be an advancement to the art to provide a high density interconnect that can scale to the small geometries of the integrated circuit and provide a low loss medium and provide very high isolation as the speed of the semiconductor approach 100 Gb/s as well as providing methods of their manufacture.

SUMMARY OF THE INVENTION

[0010] In one of its aspects the present invention relates to a 3D coaxial distribution network structure or mostly air-filled dielectric coaxial structure that is photolithographically defined with very tight tolerances. Such a construction is the optimal structure to provide high speed digital, shielded DC, and RF interconnects and routing. This is particularly the case when a 2D planar grid of electrical contact points on a small pitch must be interfaced with complex electronics that require pitch that necessitates a much larger 2D planar grid. For example in EHF phased arrays, antennas must be on a small spacing dictated by the wavelength or frequency of operation, however the support electronics needed for each antenna may need a much larger spacing in order to fit. Thus a 3D redistribution network must route from the pitch of the electronics down to the pitch of the smaller antennas.

[0011] A somewhat similar problem occurs in testing integrated circuit devices where the test electronics and the pitch of the bond pads or solder bumps on the chip or multi-chip module (MCM) are quite small, the test equipment is large, and particularly at frequencies and data rates increasing, for example approaching 10's or 100 Gb/s. In wafer die testing, as the communications chips on wafers require increasing frequency RF testing, and complex circuit testing, to determine pass/fail criteria before being sold, the industry faces a challenge to route input and output RF test signals as well as DC feed lines on 2D pitches where pads may be spaced on 0.5 mm spacing, but continue to trend to smaller pitches which are ultimately limited by the ability to test pads or solder bumps on the desired spacing. At these increasing frequencies, the ability to maintain both high isolation between DC and RF test and power lines as well as substantially low insertion loss in the interconnection between test equipment and the contacts into the chip are both desirable features. Thus a shielded 3D transmission line structure is an ideal approach to solve the problem. The 3D coax structure may be composed almost entirely of metal and air, with no confining substrate.

[0012] In a preferred configuration, the 3D coax structure may be implemented with a copper center conductor suspended in an air dielectric (using small dielectric support structures) and surrounded by copper ground shielding. At microwave frequencies, air is the lowest loss practical medium possible. Moreover, using a precision layer by layer manufacturing process leveraging lithography and photomolds achieves great precision and smooth surfaces thus minimizing skin effect losses and discontinuity losses. One such process is the PolyStrata.RTM. technology offered by Nuvotronics, LLC and described in the patent documents, such as: U.S. Pat. Nos. 7,012,489, 7,649,432, 7,948,335, 7,148,772, 7,405,638, 7,656,256, 7,755,174, 7,898,356, 8,031,037, 2008/0199656 and 2011/0123783, 2010/0296252, 2011/0273241, 2011/0181376, 2011/0210807, the contents of which are incorporated herein by reference. The center conductor with an air dielectric is the lowest loss method for handling high speed digital and RF for frequencies at 100 Gb/s in a compact 3D RF transmission line.

[0013] The 3D coaxial signal conductor may be surrounded by ground shielding on all four sides in the case of rectacoax (or the surrounding outer conductor in any other coaxial shape) and may provide optimum isolation between two adjacent signal lines (each surrounded by metal shielding). Such a configuration can allow two adjacent 3D coaxial interconnects that are in extremely close proximity to handle high speed digital and mixed signals with the low crosstalk. (See FIGS. 1, 2 for examples of PolyStrata.RTM. architecture 91 having crossover lines 92 with high isolation. The metal shield separating adjacent signal traces provides much greater I/O routing and redistribution densities and higher impedance control than is available in the prior art for high-speed IC test applications.) Two center conductors suspending in an air dielectric and surrounded by ground shielding can provide an optimal approach for 100 Gb/s routing of differential signals. As integrated circuits are built with more transistors and operate at higher clock rate frequencies, much more noise is induced by the simultaneous switching action of millions or billions of transistors on the chip processing the data operations. This noise is coupled onto the DC power and ground supplies and can affect performance, especially bit error rate performance. The creation of a 3D coax or mostly air dielectric 3D coax differential signal pair with high common mode rejection will mitigate the effects of DC line noise.

[0014] Moreover, very small geometrical feature sizes can be achieved because the 3D coax is processed via photolithography, allowing connections and contactors to interface at very small pitches for high density interconnections. This can be critical for test interface units and contactors to directly contact semiconductor chip I/O or its interposer during testing with high density interconnections and very low crosstalk.

[0015] In another of its aspects, the present invention provides a test interface unit contactor to permit direct transition from a low-loss high isolation 3D coax interconnect to a metal probe that provides make-break contacts (i.e. mating cycles) to a substrate's connection pads for wafer level or multi-device testing. For purposes of this application, when we say wafer level testing we mean any suitable testing of die on a wafer where said die are tested one or several at a time. Sometimes said die may be tested in clusters of 4, 8, 16, 32 or more. Typically testing is accomplished by moving the wafer in a step and repeat manner until all die on the wafer are tested. The design and construction of the contactor may provide a compliant temporary connection to the wafer pads or bumps and allow for many more mating cycles to chips and wafer electrical contact points than would be possible mating the probe card directly to the device under test.

[0016] Additionally, the three-dimensional, controlled-impedance routing of the signal traces that is possible using 3D coaxial design and fabrication techniques means signal integrity may be maintained for even the most dense routing requirements, such as in wafer-level or multi-site testing. The layer-to-layer interconnects do not require more space than in-plane routed transmission lines (as is required for traditional multi-layer PCBs). Considering the routing on a Cartesian grid, routing architectures in accordance with the present invention could have, for each independent transmission line, and input in one XYZ "point A" and output in a completely new XYZ "point B", thus not being confined to any particular plane due to the 3D nature of routing using the substrate-free architecture. (See U.S. patent application No. 61/788,675 the entire contents of which are incorporated by reference.) For instance, the pitch in the input can be greatly reduced to accommodate a fine pitch die, employing coax to ground-signal-ground (GSG) transitions in order to reduce the pitch to less than 100 .mu.m. Then the outputs of each individual coax line can be fanned out to a wider pitch some distance away from the mating make-break or connector connection--without losing signal integrity due to loss or isolation issues. The wider pitch allows standard connectors and cables to route the transmission line back to the main signal processing or higher level board controller tier, or to fit additional processing ICs directly on a PCB or flex circuit at the coax line outputs that are now spaced further apart. In phased array architectures this change in pitch accomplished by a redistribution network may be called a "dilation", and in semiconductor interposers this change is called a "fan-out" or space transformer.

[0017] In the case of both the antenna grid of a phased array or the IC pad or bump pitch of chip or wafer to be tested, interconnect challenge is primarily one of a roughly 2D planar grid of devices in a plane. Returning to the Cartesian model with a X and Y in the plane of the wafer, chip pads or bumps, or antennas and Z being the orthogonal "height" or "depth" axis, one would determine some typically periodic pitch, or periodicity, for the contact points in the X, Y plane, say on a 1 mm spacing on X and Y. In this case, the height or Z plane is the contact plane for the device under test or antennas with the origin at Z=0, +/-some tolerance due to manufacturing variability. If the electronics or connectors needed to interface to this grid require a contact surface area 10x this pitch, or for example, then require 10 mm.times.10 mm contact region to fit and mount their interface, then we are faced with the need to redistribute or reroute with our intermediary 3D redistribution structure. What is less apparent is it that this can be done in multiple planes and multiple ways.

[0018] For example, one solution in accordance with the present invention would be to have another plane defined at different Z, say Z=1 mm, and then have transmission lines simply route diagonally to a new XY grid on the 10 mm pitch with diagonal fan-out transmission lines. This a smaller "checkerboard" of contact points for the device under test (DUT) or antenna array is fanned out and "up" to the larger checkerboard at Z=1 mm on the XY pitch of 10 mm. This is one way to interface the large connectors with a mounting surface area which is 10.times. too large on two linear dimensions or 100.times. too large in surface area to this smaller grid for the DUT or antenna array. It can be noted however that only the DUT or antenna array is constrained essentially to a single Z-plane in this example, and the connectors could be distributed onto a multitude of larger surfaces to solve the problem. So, a fan-up to a checkerboard on 10x pitch on the XY plane at a Z=1 mm plane is one approach, but so is a fan out that is tiered with mounting surfaces on the XZ or YZ planes, or diagonal planes, or even over the surface of a hemisphere or pyramid. Any of these solutions can provide the ability to move from the small Cartesian grid of the DUT or antenna and spread out and up to a new surface or series of tiered surfaces on any of these planes. The most pragmatic solution to choose where and how the fan-out is achieved will in part be dictated by the manufacturing and assembly methods used to assemble the 3D transmission lines redistribution network.

[0019] In yet another of its aspects, the present invention may provide, at the input or output of each independent transmission line, a transition designed such that it provides mechanical or electrical connection to a standard RF connector. The connector could also be fabricated at the same time as the transmission line, or provide for an interlock mating surface for a COTS (commercial off the shelf) connector such as the G4PO.RTM. connection components offered by Corning. At the input or output of each independent transmission line, the transition can be designed such that it terminates in an antenna fabricated using the same methodology as was used to fabricate the transmission line, or there could be provided a mechanical interlock to the antenna. This arrangement could allow for coupling at distance to a device under test (DUT) or to conduct any other sensing or radar application.

[0020] PolyStrata.RTM. based architecture can also incorporate various passive components such as power dividers/combiners, filters, inductors, capacitors, couplers, and baluns. These components can be integrated at a terminal end (input or output) or in-line with the transmission line in order to process or condition the RF signals before routing to an external connection. In addition, the 3D coaxial transmission line structure can route many lines to active devices such as RF switches in order to minimize the RF processing needed in the overall testing system. Other active devices, such as but not limited to amplifiers, can be connected through appropriate transitions to the PolyStrata.RTM. architecture or other shielded distribution network to provide for RF processing before passing to external connections and processors. Switches, and RF switches in particular, can greatly reduce the amount of cabling and processing further into the testing system. As an example, a bank of 1.times.4 switches connected to the transmission lines leading to a DUT could reduce the amount of RF sources, receivers, cables, connectors, and other microwave passives and actives by 4 times. This reduction in components can simplify the testing assembly and minimize cost, assembly, and impact to system yield.

[0021] In still another of the aspects of the present invention, at the input end of the 3D coax lines, where the inner conductors meet the DUT pads, various make-break connection (contactor probe) designs can be fabricated or integrated. A design of the probe can feature a center conductor as well as an outer conductor, providing isolation shielding as close as possible to the DUT pad or solder bump or post. Alternative designs of the probes could be separately fabricated probe assemblies that are affixed to the 3D coax architecture either permanently or through compression interfaces held in place with precision screws or bolts or clamps or interlocking features. These multi-probe assemblies could be made using but not limited to: micro electro mechanical systems (MEMS), cantilevers, fuzz-button arrays, compliant springs, the PolyStrata.RTM. technology, pogo pins, or antenna elements.

[0022] By leveraging the 3D networking architecture provided, much higher densities of chips or devices under test (DUT) can be tested at one time, scaling this test interface unit to a true wafer-scale test interface unit. From 4 chips to 8, 16, 32, and up to entire wafers, the architecture lends itself to building out the structure in a large backplane to accommodate many thousands of connections.

BRIEF DESCRIPTION OF THE DRAWINGS

[0023] The foregoing summary and the following detailed description of exemplary embodiments of the present invention may be further understood when read in conjunction with the appended drawings, in which:

[0024] FIG. 1 schematically illustrates a 3D plan view of an exemplary 4.times.4 switch matrix comprising 3D coax PolyStrata.RTM. architecture in accordance with the present invention;

[0025] FIG. 2 schematically illustrates a partially cutaway view of the exemplary 4.times.4 switch matrix of FIG. 1 showing the detail of a 3D coaxial PolyStrata.RTM. line crossover in the overall PolyStrata.RTM. architecture;

[0026] FIG. 3 schematically illustrates an exploded view of the components of an exemplary wafer level test interface unit in accordance with the present invention;

[0027] FIG. 4 schematically illustrates a cross-sectional, non-exploded view of the exemplary test interface unit of FIG. 3;

[0028] FIG. 5 schematically illustrates an alternative configuration of the test interface unit of FIG. 3 but having a different orientation of RF connectors relative to the device under test;

[0029] FIG. 6 schematically illustrates an exploded view of the components of an exemplary wafer level test interface unit in accordance with the present invention similar to that of FIG. 3, but having an interposer disposed between connector and the DC/RF dilation;

[0030] FIG. 7 schematically illustrates a 3D plan view in partial cross-section of the test interface unit of FIG. 3;

[0031] FIG. 8 schematically illustrates enlarged detailed views of portions of the features of the test interface unit of FIG. 7;

[0032] FIG. 9 schematically illustrates a cross-sectional view of the probe assembly of FIG. 7;

[0033] FIG. 10 schematically illustrates an exploded, cut-away view in partial cross-section of the probe assembly of FIG. 9 showing the pogo pin and associated housing;

[0034] FIG. 11 schematically illustrates, in partial cross-section, an alternative exemplary probe assembly having a tapered housing in accordance with the present invention;

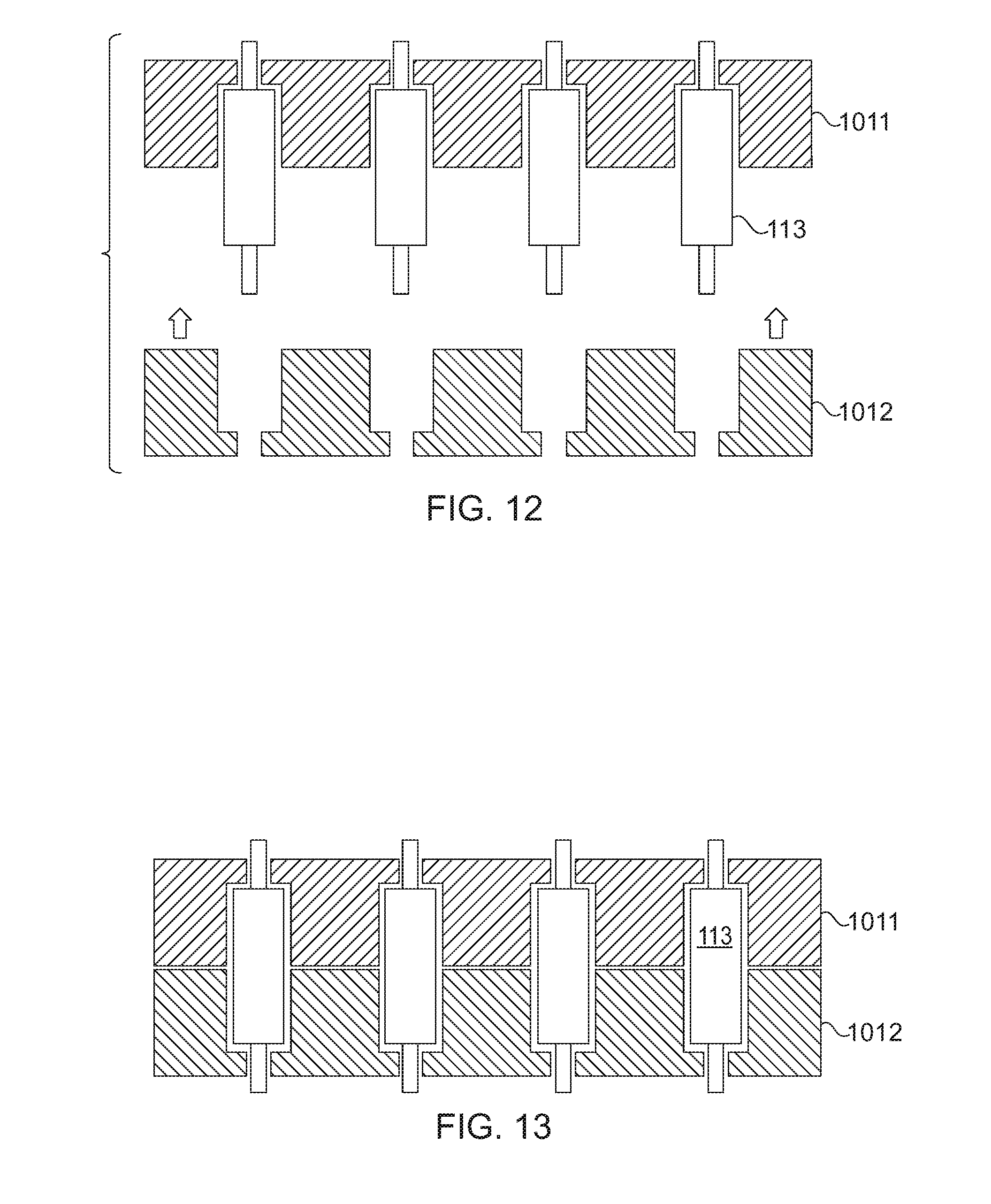

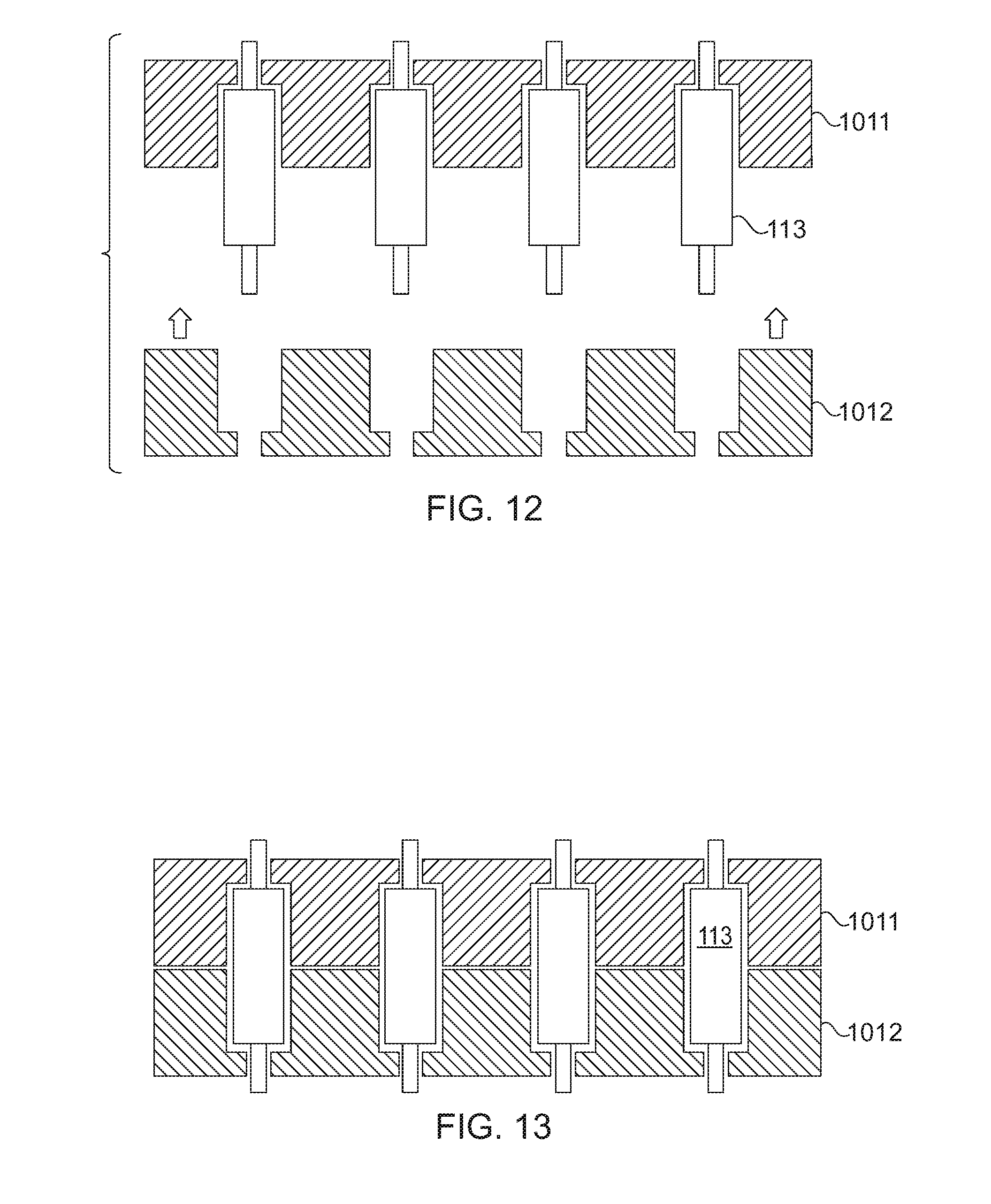

[0035] FIG. 12 schematically illustrates exploded view in partial cross-section of an exemplary probe assembly in accordance with the present invention;

[0036] FIG. 13 schematically illustrates a non-exploded view of the probe assembly of FIG. 12;

[0037] FIG. 14 schematically illustrates a cut-away view in partial cross-section of an exemplary probe assembly of the present invention comprising layers formed by the PolyStrata.RTM. process;

[0038] FIG. 15 schematically illustrates a cut-away view in partial cross-section of an exemplary probe assembly of the present invention comprising a three-piece, stacked housing;

[0039] FIG. 16 schematically illustrates cross-sectional views of alternative configurations of an exemplary probe interface layer in accordance with the present invention having recessed conductor areas disposed in the probe interface layer;

[0040] FIG. 17 schematically illustrates cross-sectional views of alternative configurations of a probe assembly and probe interface layer in accordance with the present invention having multi-level, recessed conductor areas disposed in the probe interface layer;

[0041] FIGS. 18-24 schematically illustrate cross-sectional views of exemplary probe assemblies in accordance with the present invention;

[0042] FIGS. 25-30 schematically illustrate an exemplary wafer level test interface units in accordance with the present invention for testing one or more devices, respectively, and showing how the wafer level test interface unit of the present invention scale with test device number;

[0043] FIG. 31 schematically illustrates a vertical card prober with an integrated space transformer which routes signal lines from a smaller pitch to a larger pitch in accordance with the present invention;

[0044] FIG. 32 schematically illustrates a stacked array of vertical card probers of the type shown in FIG. 31;

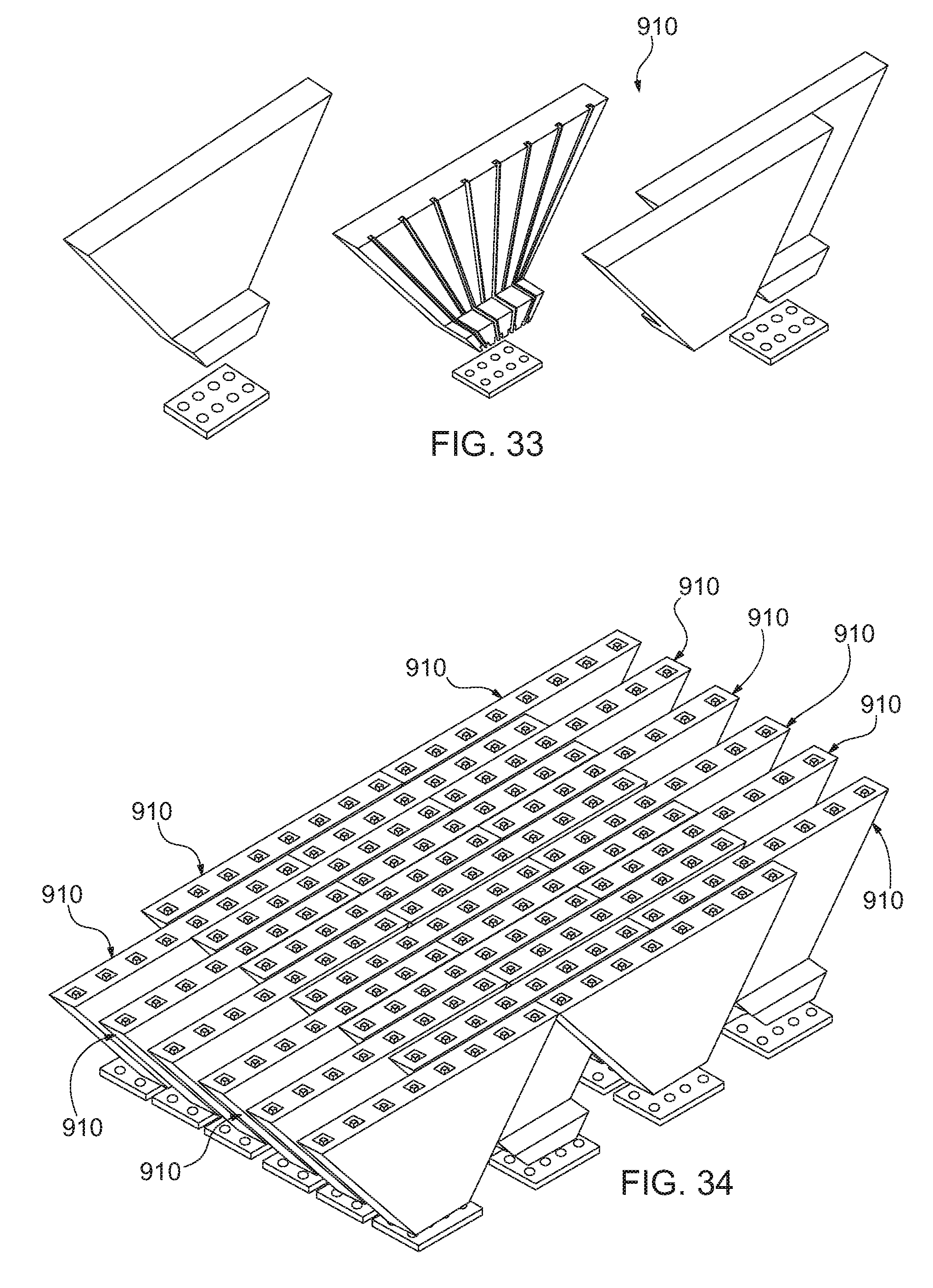

[0045] FIG. 33 schematically illustrates another vertical card prober with an integrate space transformer in accordance with the present invention;

[0046] FIG. 34 schematically illustrates a stacked, interleaved array of vertical card probers of the type shown in FIG. 33;

[0047] FIG. 35 schematically illustrates DC and RF routing for a tester in accordance with the present invention and could be arrayed using a staggering technique shown in FIG. 34;

[0048] FIG. 36 schematically illustrates an exemplary probe similar in certain respects to the probe of FIG. 18 and having a spring region;

[0049] FIG. 37 schematically illustrates a wafer level test interface unit in accordance with the present invention; and

[0050] FIG. 38 schematically illustrates integration of passives components inside a coax line.

DETAILED DESCRIPTION OF THE INVENTION

[0051] Referring now to the figures, wherein like elements are numbered alike throughout, FIGS. 3-4 schematically illustrate an exemplary configuration of a wafer level test interface unit 100 in accordance with the present invention for use in testing a device under test (DUT) 106. The wafer level test interface unit 100 may be configured to provide repeated testing of multiple devices under test 106, especially at the grid/wafer level, while overcoming numerous problems in the existing art. For example, typically, the device under test 106 will include RF and DC circuitry, which is typically tested through the use of a probe card assembly comprised of printed circuit boards 105 and a contactor array 101. (The printed circuit board 105 can represent a non-coaxial printed circuit card where processing or interfacing with active and passive components can be conducted close to the device under test 106.) However, the pitch of features on the device under test 106 is most often much finer than that achievable in the printed circuit board 105; thus, there may be a pitch mismatch between the device under test 106 and the printed circuit board 105 that needs to be addressed. Additionally and increasingly, devices under test 106 also include RF circuits which are difficult or impractical to test via the printed circuit board 105. Thus, the wafer level test interface unit 100 may be configured to accommodate both DC signal paths as well as RF signal paths. Consequently, the structure of the wafer level test interface unit 100 of the present invention may provide at least the following three features. First, the wafer level test interface unit 100 may be configured to include a dilation (a change in pitch) in the signal paths that matches the finer pitch of the device under test 106 to the relatively larger pitch of the printed circuit board 105. Second, the wafer level test unit 100 may include separate conductive pathways for each of the DC circuits on the device under test 106 and the RF circuits of the device under test 106. Third, the wafer level test interface unit 100 may be structured to permit repeated, mechanical/electrical make-break connections to each of the circuits of the device under test 106. This is an improvement in the art because of the highly improved electrical shielding while decreasing the minimum pitch possible by other approaches. The electro-mechanical nature of the construction that eliminates solid dielectric in part of all of the dilation also reduces RF signal loss and enables the opportunity to directly create a mechanically compliant interface region in the hardware.

[0052] For example, in one exemplary configuration the wafer level test interface unit 100 may include a plurality of structures that provide the aforementioned features. The make-break connections with the device under test 106 may be made by a contactor probe assembly 101; the dilation of the DC lines of the device under test 106 to the printed circuit board 105 may be accomplished by an interposer 104; and, dilation of the RF circuits of the device under test 106 as well as routing of both the DC circuits and RF circuits from the device under test may be provided by a 3D probe interface layer 102 having RF connectors 103. While each of the three features of dilation, make-break connection, and RF signal routing may be provided by three separate structures 101, 102, 104, other configurations are possible in which the three separate structures 101, 102, 104 are provided by a unitary monolithic part.

[0053] In addition, as examples of other exemplary configurations of wafer level test interface units in accordance with the present invention, a wafer level test interface unit 500 may include a probe interface layer 502 which routes the RF signal from the device under test 106 to a lower surface of the probe interface layer 502 to position the RF connectors 103 at such lower surface, FIG. 5. Such a configuration may offer more room for assembly of a test interface unit, because the RF connectors 103 are routed to the opposite side of the probe interface layer 502 to the DC signals which pass through the interposer 104. Such a configuration may be suitable for testing singulated or grids of die or multi-chip module (MCM) devices that require testing allowing clearance between the connectors and the DUT. Further, a wafer level test interface unit 600 similar to that shown in FIG. 3, may optionally include an interposer 117 disposed between the RF connectors 103 and probe interface layer 102 to provide enhanced mechanical rigidity to the assembly as well as additional room for DC and/or RF routing and/or embedded or surface mount passive or active circuits. The interposer 117 may comprise an alumina board, printed circuit board, or any other suitable material to provide electrical contact between the connectors 103 and probe interface layer 102.

[0054] FIG. 7 schematically illustrates a 3D plan view in partial cross-section of the test interface unit of FIG. 3, further showing the routing of the coaxial lines 107 within the probe interface layer 102 and interposer 104, as well as the non-coaxial transmission lines 111 through the printed circuit board 105. Active or passive components 110 may be provided on the top or embedded in the circuit board 105. 105 may also serve as an interface contact layer to an upper probe card or connector layer. Such an upper probe card and the DC board 105 may pass power and I/O to the DUT and interface to the test system electronics that otherwise do not require shielded transmission lines to interface to the rest of the test system. Additional detail of the interface between probe interface layer 102, contactor probe assembly 101, and the device under test 106 is illustrated in FIG. 8. Specifically, the contactor probe assembly 101 may include pogo pins 113 disposed in a housing 119. An array of such pogo pins can be made such as a using a clamshell sheath with holes to form a complaint connector layer 101. The pogo pins 113 may be configured to provide electrical and mechanical connection between individual solder bumps or pads on 112 of the device under test 106 on one side and respective center conductors 107 of the probe interface layer 102. In FIG. 8 on the right a small perspective cross-section of 3D probe interface layer 102 is shown to highlight a shielded RF transmission line 107 of the probe interface layer 102 electrically interfacing with the center of a compliant contactor 118, in this case being represented with a double-sided pogo pin, with only the upper contactor shown 118 of pogo pin 113. An example of the dilation aspect of the probe interface layer 102, which assists in routing of the DC and RF signals as well as matching the pitch between the device under test 106 and a printed circuit board 105, may further be seen and described in FIG. 25.

[0055] The contactor probe assembly 101 may be attached to the probe interface layer 102 by solder, glue, epoxy, or may simply rely on mechanical contact. An adhesive material such as these could affix the lower outer surfaces of 102 to 101. 101 may or may not be made of a conductive material depending on the construction of the pogo pin and housing. The upper surface of the pogo pin 113 may be flat or have any shape suitable for improving mechanical and electrical connection between the center conductors 107 of 102 on one side and also the contact surface of the DUT on the opposing side. In this case FIG. 9 shows details of a "bed of nails" concept using and 2D array of double-sided compliant interface connectors in a housing structure to form 101. 101 is here comprised of a quantity of double-ended spring loaded contactors/connectors (pogo pins) where 118 is the central contactor of each pogo pin 113. A double-sided pogo pin as shown in FIG. 9 is comprised on two contactor ends 118, an internal spring 1103, and a housing 119. Single-sided pogo pins may be used as shown in FIG. 7 item 101. Other exemplary configurations of the probe interface layer 102, especially alternative configurations of the housing for the pogo pins 113, are illustrated in FIGS. 10-17.

[0056] FIGS. 10-13, for instance, schematically illustrate cut-away views in partial cross-section of the contactor probe assembly 101 showing a double-sided pogo pin 113 and associated upper housing portion 1011 and lower housing portion 1012. The housing portions 1011, 1012 may be fabricated from a non-conductive material, such as alumina, glass, or any suitable ceramic material, or a semiconductor material. The housing portions 1011, 1012 may be fabricated by dry etching, deep reactive ion etching, and/or laser drilling. The upper housing portion 1019, and/or lower housing portion, may include a diameter step or a tapered via, FIG. 11. Further, rather than upper and lower housing portions 1011, 1012, the housing may include upper, lower, and intermediate housing portions 1015, 1016, 1017, FIG. 15. The intermediate housing portion 1016 may be larger than the upper and lower portions 1015, 1017, so that, when assembled, the pogo pin assemblies, are trapped between the upper and lower housing portions 1015, 1017. As an alternative fabrication approach, the housing 1013 of the contactor probe assembly 101 may be fabricated using PolyStrata.RTM. technology with additional passivation 1014 to prevent electrical contact between the pogo pins 113 and the conductive strata of the housing 1013 as shown in FIG. 14. Other methods of manufacture may include 3-D printing of appropriate materials.

[0057] In addition to variations in the configuration of the contactor probe assembly 101, variations in the structure of the probe interface layer 102 may also be desirable. For example, FIG. 16 schematically illustrates cross-sectional views of an alternative configuration of the probe interface layer 202. The probe interface layer 202 may include center conductors 207 which include enlarged end portions 219 which may improve electrical and mechanical contact between the center conductors 207 and pogo pins 113. At the same time, center conductors 207 can have a smaller cross-sectional width and the enlarged end portions 219, which provides additional room for, and thus more effective routing of, the center conductors 207 within the probe interface layer 202. In addition the enlarged end portions 219 may be recessed and protected within cavities 203 of the probe interface layer 202. In FIG. 17, the probe interface layer 302 may include center conductors 307, 308, 309 that terminate at differing heights within the probe interface layer 302, for example within cavities 311, 313 of the probe interface layer 302. At the same time, contactor probe assembly 301 may include pogo pin assemblies 316, 317, 318 of differing heights matched to the termination heights of the respective center conductors 309, 308, 307 to which such pogo pin assemblies 316, 317, 318 are to make electrical and mechanical contact.

[0058] Still further, in addition to pogo pin assemblies, structures other than pogo pins 113 may be utilized within contactor probe assemblies 101 of the present invention, such as PolyStrata.RTM. center conductor springs 807. Using the center conductor to make a compliant layer can be accomplished in multiple ways. For example, FIG. 18 schematically illustrates a cross-sectional view of section of an exemplary probe 800 in accordance with the present invention having a center conductor 802 with a spring region 807, which may be fabricated by the PolyStrata.RTM. process. Specifically, the probe assembly 800 may include a center conductor 802 disposed within an outer conductor 815 to provide a coaxial structure. The center conductor 802 may include a spring portion 807 which can flex or deflect allowing compressive movement of the center conductor 802 in region 807 when contacting a device under test. The center conductor 802 may be supported within the outer conductor 815 by a dielectric support 816. Such a spring may be one or more repeated C sections meandering in a plane or a 3D spiral, for example. Alternatively, a coaxial center conductor 828 of a probe assembly 825 in accordance with the present invention may include a cantilever region 8027 about which the center conductor 828 pivots or rotates or flexes being affixed in regions 826 by a non-conductor, FIG. 19.

[0059] Additionally, in FIG. 20, movement of a coaxial center conductor 837 within a probe assembly 830 may be affected by flexure or bending of a dielectric support member 836 disposed between the center conductor 837 and the coaxial outer conductor 835, FIG. 20. In FIG. 22, instead of bending, a dielectric support member 856 may be provided between a coaxial center conductor 857 and outer conductor 855, which support member 856 pivots to allow movement of the center conductor 857, FIG. 22. In addition, the center conductor 857 can move a sufficient amount relative to the outer conductor 855 to permit a solder bump 852 of the device under test to be shielded within the coaxial outer conductor 855 of the probe assembly 850. Still further, in FIG. 21, probe assemblies 840 of the present invention may operate without physical contact between a coaxial center conductor 847 and the device under test. Instead the coaxial center conductor 847 may be configured to operate as an antenna which communicates with the device under test. The coaxial center conductor antenna 847 may be disposed within a coaxial outer conductor 845 and supported therein by a dielectric support member 846, FIG. 21. In FIG. 23, probe assemblies 860 of the present invention may also include shielding, such as shield walls 861, to minimize crosstalk within the probe assembly 860 between two neighboring devices under test 866, 867, which facilitates multi-site, or multichip, or wafer-level testing, FIG. 23.

[0060] To further facilitate multi-device testing, a switch 878, which may be a MEMS switch, may be provided between multiple devices under test 871-874 and an RF connector 876. FIGS. 1 and 2 illustrate a perspective view and detailed close up section of a 4.times.4 non-blocking switch matrix. In FIG. 1 there are 8 ports with coaxial input regions, two on each of the 4 sides of the device. The switching is done with 1.times.4 (SP4T) RF-MEMS switches 93 in this case using 8 parts number RMSW240 obtained from Radant MEMS in Littletown, Mass. To create a non-blocking 4.times.4 switch matrix, all of the binary coaxial wiring interconnecting these eight 1.times.4 switches is done using PolyStrata.RTM. Coaxial network which also provides all the RF shielded coaxial cross-overs. FIG. 2 highlights how the MEMS s 93 are in this case mounted face up and interconnected using wirebonds. Flip-chip could also be used to attach such switches to the PolyStrata switch fabric. To the left and right of the 8 RF I/O launches into and out of the matrix 95, the DC control lines needed to operate the switch can also be seen, 94. FIGS. 1 and 2 thus illustrate ways to incorporate die level switches into a coaxial routing fabric. Similarly FIG. 24 shows in a block diagram format each of a plurality of RF outputs 875 on a respective series of devices under test 871-874 (also shown as 106 in FIG. 3) may be connected to the switch 878, which in turn may be selectively connected to a probe interface layer 102 in accordance with the present invention. Thus, the number of connectors 103 and cabling could be reduced by integrating switches 878 with the probe interface layer 102 or the optional interposer 117 as shown in FIG. 6. Without switching, separate RF and DC coaxial lines (and RF connectors 103) are required for each corresponding circuit of devices under test 106 which increases the complexity and cost of the contactor probe assembly. It should be clear that RF and DC switches can be integrated on any surface or even within the PolyStrata.RTM. fabric 102 or could be added in other locations as needed to tester assembly. In addition, the switch 878 and/or the coax lines 890 may be disposed within probe interface layer 102 or on the surface thereof. Furthermore, while the switch 878 and the coax lines 890 illustrated in connection with the probe interface layer 102, the switch 878 and/or the coax lines 890 may be disposed within the interposer 104 or on the surface thereof or on the surface thereof.

[0061] FIG. 25 depicts the fanning out process using the air-coax structure. The bottom view shows the small pitch of the contact point, the transparent view shows the fanning out and re-routing happening in the probe interface layer 102. The top view shows the new position of the contact after the fanning out. FIG. 26 shows the RF or DC being routed on each side of the probe interface layer 102.

[0062] FIG. 27 shows that the routing density and high isolation offered by the coax lines allow for all the RF or DC lines to be routed on only one side of the probe interface layer 102, enabling a larger number of DUT 106 to measure at the same time. FIG. 28 shows that the dimensions of the 3D coax-line routing can be miniaturize enough to route two DUTs side by side to only one side of the probe interface layer 102. FIG. 29 shows 4 DUTs being probed, demonstrating the possibility to scale the number of devices to be tested simultaneously by duplicating the structure in FIG. 28.

[0063] FIG. 30 shows another increase of the number of DUTs tested simultaneously, accomplished by mirroring the probe interface layer. The wafer level test interface unit 100 shows 8 devices being tested at a time, but a larger number could be implemented similarly. The routing and fanning out could also be configured to match a specific distribution of DUT on the wafer or test pattern.

[0064] FIG. 31 shows a novel configuration using a micro-fabricated vertical card 900 which may provide the function of one or more of, and substitute for, the contactor probe assembly 101, the probe interface layer 102, and the interposer 104 of FIG. 3. For example, the transmission lines 907 may transform the fine wiring pitch from a device under test 106 to a wider spacing for the RF or DC connector. The center conductor of coaxial transmission lines 907 may include spring portions such as 902 which may replace the spring function provided by the pogo pin 113 of the contactor probe assembly 101. Optionally, the spring portion 902 may be omitted, FIG. 33. Multiple vertical cards 900 may be assembled, such as by soldering or mechanical attachment, to create an array of vertical cards 900, FIGS. 31-34. To further assist in the routing of coaxial lines, FIG. 34 also shows a novel architecture enabled by the ability to route small diameter coax lines 901 into a common vertical space transformer (or dilation) board 910. The signal coming from either separate contactor layer as described in connection with FIG. 16 or a monolithic contactor as described in connection with FIG. 31 may be routed on only one side of the vertical space transformer 910. Routing on only one side allows staggered vertical boards 910 next to each other by switching the routing side. Using such a configuration, it is possible create an N by N testing probe array. FIG. 35 shows a novel DC and RF routing device 920 for a single chip tester or n by n tester using the staggering technique showed in FIG. 34. The DC and RF can be divided and exit 920 on different surfaces. The DC output routing 923 and the RF connector 924 may be provided on sides of the device 920. The DC outputs 923 can be routed to a final circuit board using a flexible cable 921. The DC connector in 923 can be part of the micro-fabrication of the coax lines and be soldered to the flex-cable. This architecture allows one to improve the connector space transformer for the high density required by the device under test to the output I/Os.

[0065] FIG. 36 illustrates an exemplary probe similar in certain respects to the probe of FIG. 18, where the common ground 900 and the center conductor 907 could include a spring in the region 902 fabricated in the PolyStrata.RTM. process which will provide the same function as the pogo pin and the probe 102 and replacing the contactor probe assembly 101. The concept presented demonstrates that meandering the center conductor while maintaining control over the OD of the meandering region allows a region that can function as a spring and as well as allow some deflection, yet still also function as a transmission line. In this case a 200 um ID for the outer conductor--is shown while the inner conductor is centered within and has a 80 um OD. Instead of being a solid center conductor, it is made of 10 um layers that form alternating "C" sections where each "C" is a small flexure that can deform within its elastic limits to allow compression and contact with non-planar surfaces. This example shows the "C" section of the flexure or spring region meandering only to the left and right in the picture, however meandering in and out is also possible or combining in, our, left and right to allow the flexure to deflect in any direction. Many other mechanical designs could be chosen to combine a transmission line with a spring or compliant region. To ensure such a combination of spring and transmission line can function electrically, such a structure as shown was simulated using ANSYS's HFSS and a suitably low return loss could be produced as shown despite compressing the spring. Just like finite element (FE) mechanical analysis must be done, FE electromagnetic analysis is required as the effective length, capacitance, and inductance are based on how the spring is formed and how much it is compressed. This novel approach offers very good RF matching up to 100 GHz and provides shielding of the line under test, low insertion loss and high isolation as shown in the simulated response of the test structure comprising 907, 900 and 902. This micro-fabricated spring could allow very tight pitch down to 200 .mu.m and below.

[0066] FIG. 37 shows a wafer level test interface unit 100. The 3D-routing capability of the probe interface layer 102 enables clearance between the PCB 105 and the probe interface layer. This clearance permits passive or active devices 371 to be integrated on the PCB or on top of the probe interface layer 102. The ability to integrate passive devices 371 enables higher density circuits, reduces the complexity of the PCB design and/or the probe interface layer 102 and provides better testing performance of the DUT 106.

[0067] FIG. 38 shows the integration of passive components 381 such as capacitors, resistors and/or active devices such as diodes or transistors inside the coax line. The passive components can be integrated either on both sides of the center conductor 107 or on only one side between the center conductor 107 and the outer conductor 109. Inline integration on the center conductor 107 of such active or passive components 381 is also possible. The air-coax can also integrate dielectric support 826. The ability to integrate such active and/or passive components to provide tuning functions or decoupling functions for high speed digital signals is very important. The micro-integration of these components very close to the device under test offers added performance by maximizing the reduction of the parasitic effects due to the transmission lines inductance.

[0068] These and other advantages of the present invention will be apparent to those skilled in the art from the foregoing specification. Accordingly, it will be recognized by those skilled in the art that changes or modifications may be made to the above-described embodiments without departing from the broad inventive concepts of the invention. It should therefore be understood that this invention is not limited to the particular embodiments described herein, but is intended to include all changes and modifications that are within the scope and spirit of the invention as set forth in the claims.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

D00009

D00010

D00011

D00012

D00013

D00014

D00015

D00016

D00017

D00018

D00019

D00020

D00021

D00022

D00023

D00024

D00025

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.