Methods Of Patterning Dielectric Layers For Metallization And Related Structures

Bouche; Guillaume

U.S. patent application number 16/369050 was filed with the patent office on 2019-07-25 for methods of patterning dielectric layers for metallization and related structures. The applicant listed for this patent is GLOBALFOUNDRIES Inc.. Invention is credited to Guillaume Bouche.

| Application Number | 20190229059 16/369050 |

| Document ID | / |

| Family ID | 66817060 |

| Filed Date | 2019-07-25 |

View All Diagrams

| United States Patent Application | 20190229059 |

| Kind Code | A1 |

| Bouche; Guillaume | July 25, 2019 |

METHODS OF PATTERNING DIELECTRIC LAYERS FOR METALLIZATION AND RELATED STRUCTURES

Abstract

Structures including metallization layers and metal lines, and methods of forming thereof. A patterning stack, a masking layer, and a spacer patterning layer are formed over a dielectric layer, and an opening is formed in the spacer patterning layer. First and second spacers are formed on a portion of the masking layer at sidewalls of an opening in the spacer patterning layer. The first spacer and the second spacer overlie and traverse first portions of the dummy line. After removing the spacer patterning layer and masking layer, second portions of the dummy line are removed to form a feature in the patterning stack that includes a first gap beneath the first spacer and a second gap beneath the second spacer. A metal line is formed in the dielectric layer using the feature, and includes cuts at the first gap and the second gap in the feature.

| Inventors: | Bouche; Guillaume; (Albany, NY) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 66817060 | ||||||||||

| Appl. No.: | 16/369050 | ||||||||||

| Filed: | March 29, 2019 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 15860193 | Jan 2, 2018 | |||

| 16369050 | ||||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 23/5386 20130101; H01L 23/53209 20130101; H01L 23/5384 20130101; H01L 23/5226 20130101; H01L 21/76816 20130101; H01L 21/76897 20130101 |

| International Class: | H01L 23/538 20060101 H01L023/538; H01L 23/522 20060101 H01L023/522; H01L 21/768 20060101 H01L021/768 |

Claims

1. A structure comprising: a first metallization layer comprising a plurality of first metal lines and a metal island, the metal island electrically isolated from the plurality of first metal lines; a second metallization layer disposed below the first metallization layer, the second metallization layer including a second metal line; a third metallization layer disposed above the first metallization layer, the third metallization layer including a third metal line; a first conductive via connecting the metal island to the second metal line; and a second conductive via connecting the metal island to the third metal line.

2. The structure of claim 1 wherein the metal island has a length of less than or equal to fifteen nm.

3. The structure of claim 1 wherein the metal island is comprised of cobalt or ruthenium.

4. The structure of claim 1 wherein the metal island is comprised of cobalt.

5. The structure of claim 1 wherein the metal island, the first conductive via, and the second conductive via are comprised of the same material.

6. The structure of claim 1 wherein the first metallization level includes a fourth metal line arranged adjacent to the first metal line, and the fourth metal line is spaced from the first metal line by a first gap with a dimension of about five nm.

7. The structure of claim 6 wherein the metal island has a length of less than or equal to fifteen nm.

8. The structure of claim 6 wherein the first metallization level includes a fifth metal line arranged adjacent to the first metal line, the first metal line is laterally arranged between the fourth metal line and the fifth metal line, and the fifth metal line is spaced from the first metal line by a second gap with a dimension of about five nm.

9. The structure of claim 8 wherein the metal island has a length of less than or equal to fifteen nm.

10. The structure of claim 6 wherein the metal island and the fourth metal line are comprised of cobalt.

11. The structure of claim 6 wherein the metal island, the fourth metal line, the first conductive via, and the second conductive via are comprised of the same material.

12. The structure of claim 6 wherein the first metallization level includes a dielectric layer, and the gap is filled by dielectric material of the dielectric layer.

13. The structure of claim 1 wherein the metal island is substantially equal in size to the first conductive via.

14. The structure of claim 1 wherein the metal island is substantially equal in size to the second conductive via.

15. The structure of claim 1 wherein the metal island is substantially equal in size to the first conductive via, and the metal island is substantially equal in size to the second conductive via.

16. A structure comprising: a first metallization layer comprising a plurality of first metal lines and a metal island, the metal island electrically isolated from the plurality of first metal lines; a second metallization layer disposed below the first metallization layer, the second metallization layer including a second metal line; a third metallization layer disposed above the first metallization layer, the third metallization layer including a third metal line; a first conductive via connecting the metal island to the second metal line; and a second conductive via connecting the metal island to the third metal line, wherein the metal island is comprised of cobalt, the metal island has a length of less than or equal to fifteen nm, and the metal island is comprised of cobalt, and the metal island is substantially equal in size to the first conductive via.

17. The structure of claim 16 wherein the first metallization level includes a fourth metal line arranged adjacent to the first metal line, and the fourth metal line is spaced from the first metal line by a first gap with a dimension of about five nm.

18. The structure of claim 17 wherein the first metallization level includes a fifth metal line arranged adjacent to the first metal line, the first metal line is laterally arranged between the fourth metal line and the fifth metal line, and the fifth metal line is spaced from the first metal line by a second gap with a dimension of about five nm.

19. The structure of claim 16 wherein the metal island is substantially equal in size to the second conductive via.

20. The structure of claim 16 wherein the first metallization level includes a dielectric layer, and the gap is filled by dielectric material of the dielectric layer.

Description

BACKGROUND

[0001] The present invention relates to semiconductor device fabrication and integrated circuits and, more specifically, to methods of patterning dielectric layers for metal line formation and fabrication of metallization layers integrated circuits.

[0002] Metallization layers in integrated circuits allow for electrical connection between layers of integrated circuits and external devices. As circuit sizes have continued to shrink, new methods for patterning metallization layers and forming metallization lines continue to be developed to overcome limitations of existing fabrication equipment in meeting design requirements for newer and even smaller metal line features.

SUMMARY

[0003] In an embodiment of the invention, a method includes forming a patterning stack over a dielectric layer, forming a masking layer over the patterning stack and a spacer patterning layer over the masking layer, and etching an opening in the spacer patterning layer to expose a portion of the masking layer overlying a dummy line of the patterning stack. The method further includes forming a first spacer and a second spacer on the exposed portion of the masking layer at sidewalls of the opening. The first spacer and the second spacer overlie and traverse respective first portions of the dummy line. The method further includes removing the spacer patterning layer and the masking layer selective to the patterning stack, the first spacer, and the second spacer to expose second portions of the dummy line, and removing the second portions of the dummy line selective to the first spacer and the second spacer to form a feature in the patterning stack that includes a first gap beneath the first spacer and a second gap beneath the second spacer. A metal line is formed in the dielectric layer using the feature in the patterning stack. The metal line includes respective cuts at the first gap and the second gap in the feature in the patterning stack.

[0004] In another embodiment of the invention, a structure includes a first metallization layer including a plurality of first metal lines and a metal island, a second metallization layer including a second metal line arranged or disposed below the first metallization layer, and a third metallization layer including a third metal line arranged or disposed above the first metallization layer. A first conductive via connects the metal island to the second metal line and a second conductive via connects the metal island to the third metal line. The first conductive via, second conductive via, and metal island provide electrical connectivity between the second metal line and third metal line.

BRIEF DESCRIPTION OF THE DRAWINGS

[0005] The accompanying drawings, which are incorporated in and constitute a part of this specification, illustrate various embodiments of the invention and, together with a general description of the invention given above and the detailed description of the embodiments given below, serve to explain the embodiments of the invention.

[0006] FIGS. 1-10 are cross-sectional views of a structure at successive fabrication stages of a processing method in accordance with embodiments of the invention.

[0007] FIG. 1A is a top view of the structure in which FIG. 1 is taken generally along line 1-1.

[0008] FIG. 3A is a top view of the structure in which FIG. 3 is taken generally along line 3-3.

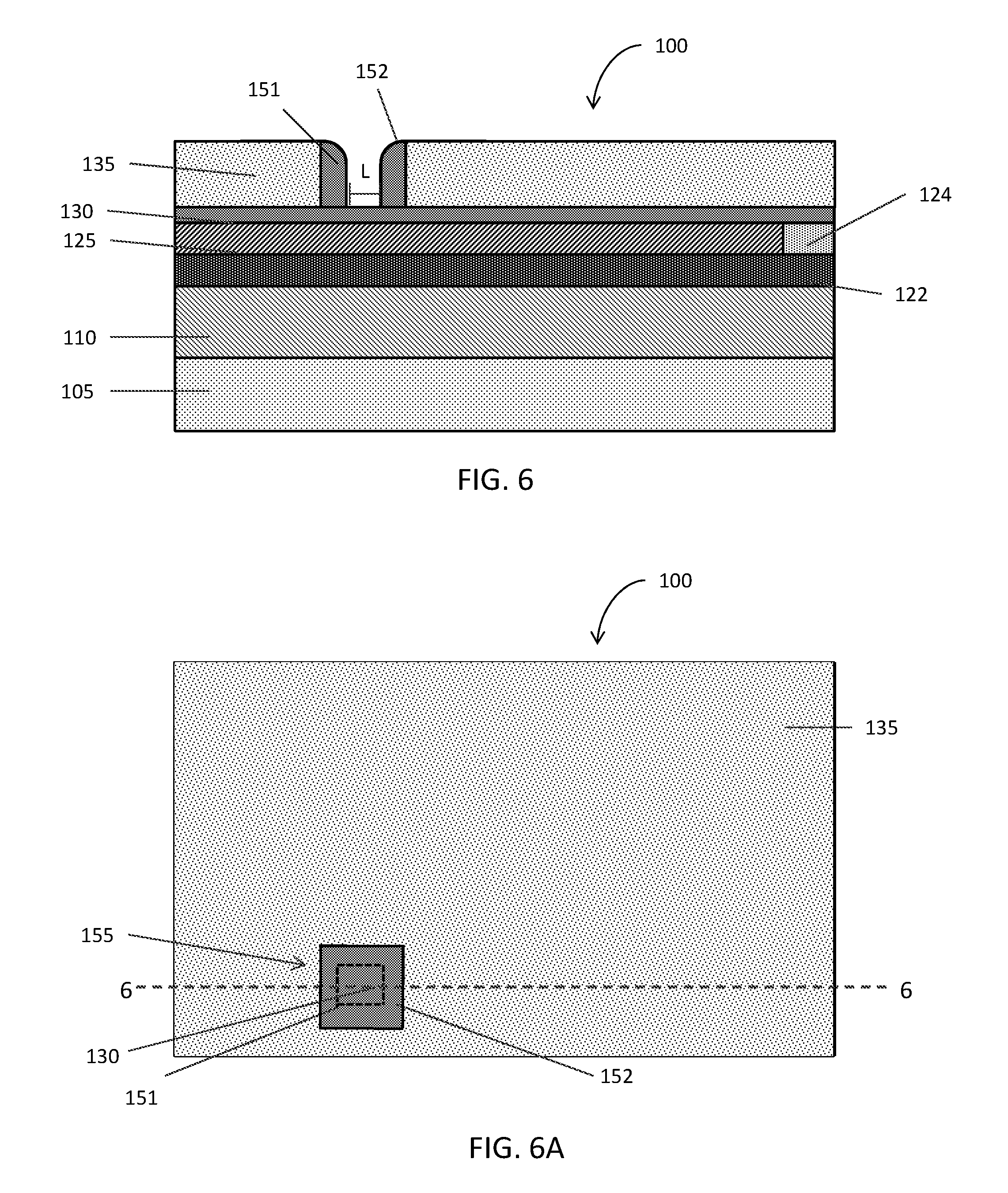

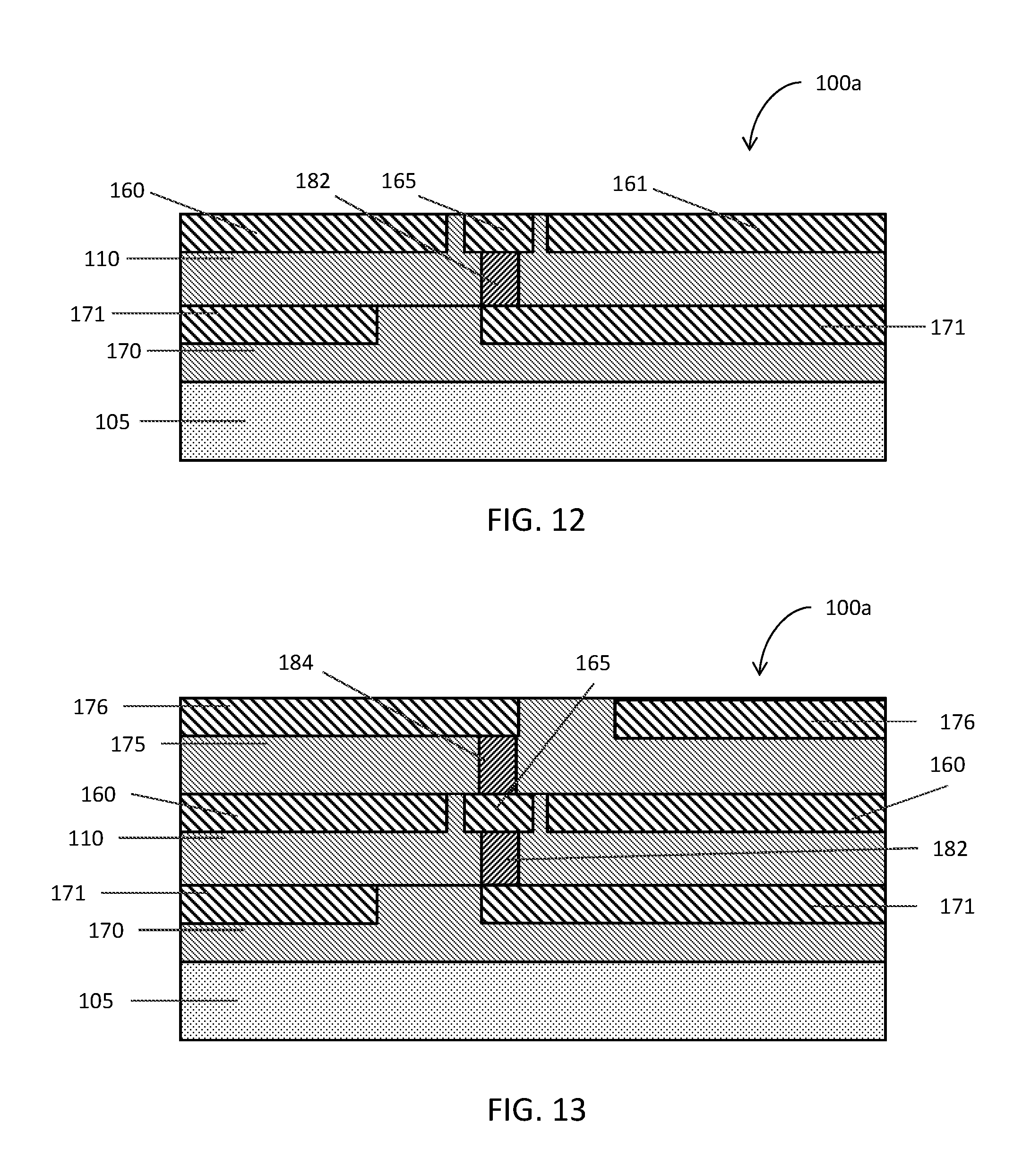

[0009] FIG. 6A is a top view of the structure in which FIG. 6 is taken generally along line 6-6.

[0010] FIG. 7A is a top view of the structure in which FIG. 7 is taken generally along line 7-7.

[0011] FIG. 8A is a top view of the structure in which FIG. 8 is taken generally along line 8-8.

[0012] FIG. 9A is a top view of the structure in which FIG. 9 is taken generally along line 9-9.

[0013] FIG. 10A is a top view of the structure in which FIG. 10 is taken generally along line 10-10.

[0014] FIG. 11 is a cross-sectional view of a structure at an alternative fabrication stage following FIG. 6 of a processing method in accordance with embodiments of the invention.

[0015] FIG. 11A is a top view of the structure in which FIG. 11 is taken generally along line 11-11.

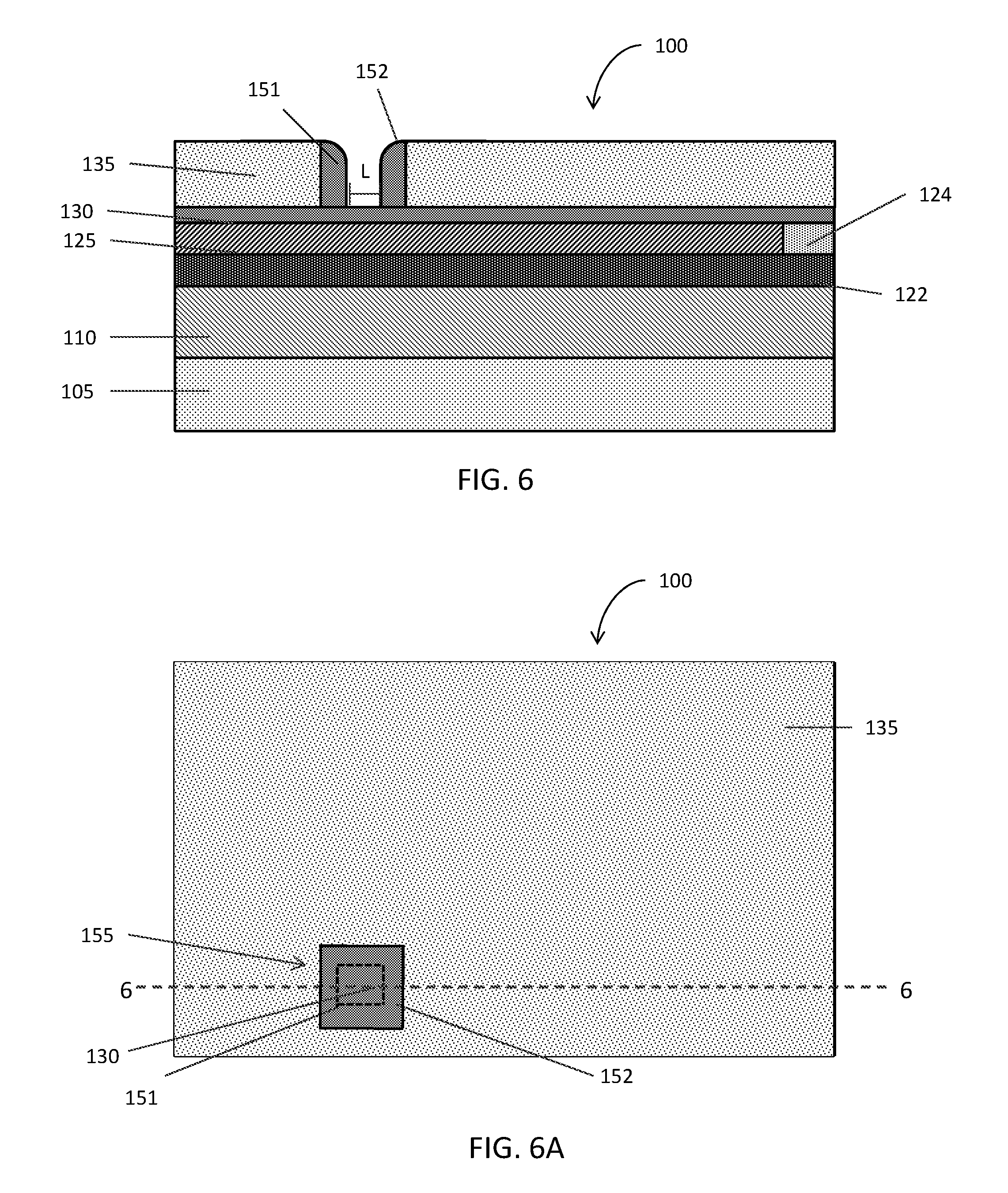

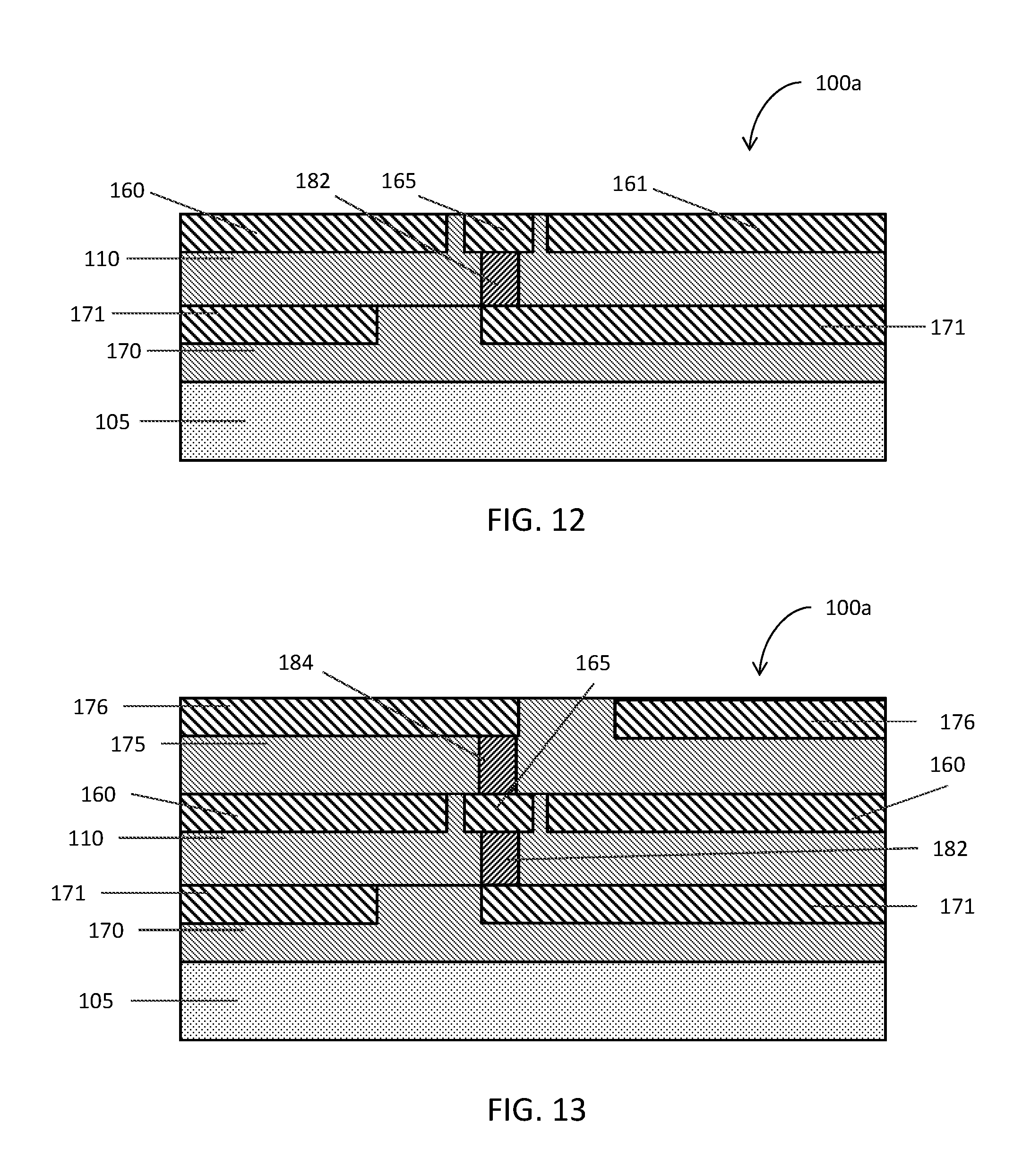

[0016] FIGS. 12 and 13 are cross-sectional views of the structure of FIGS. 1-10 at further fabrication stages of a processing method in accordance with embodiments of the invention.

DETAILED DESCRIPTION

[0017] With reference to FIGS. 1 and 1A and in accordance with embodiments of the invention, a structure 100 includes one or more lower circuit structure layers 105, a dielectric layer 110, and a patterning stack 120 that includes a hardmask layer 122, a dielectric layer 124, and dummy lines 125, 126. Dummy lines 125, 126 may be formed by a lithography and etch process from a deposited layer of its material. Dummy lines 125, 126, which may be composed of a sacrificial material, such as amorphous silicon (a-Si), are embedded in the dielectric layer 124. Dummy lines 126 are patterned with large tip-to-tip spacings.

[0018] Dielectric layer 124 may be composed of, for example, silicon dioxide deposited by plasma-enhanced chemical vapor deposition (PECVD) on the hardmask layer 122 and over the dummy lines 125, 126, and then polished to exposed the dummy lines 125, 126 at the top surface of the dielectric layer 124. Hardmask layer 122 may be composed, for example, of titanium nitride, titanium oxide, or other hardmask material. Dielectric layer 110 may be composed of a dielectric material, such as an oxide of silicon or a nitride of silicon, in which metallization lines are to be patterned using patterning stack 120, as described in part below.

[0019] With reference to FIG. 2 in which like reference numerals refer to like features in FIGS. 1 and 1A and at a subsequent fabrication stage of the processing method, a masking layer 130 and a spacer patterning layer 135 are formed over the patterning stack 120. Masking layer 130 may be composed of a dielectric material, such as a nitride-based dielectric material, and spacer patterning layer 135 may be composed of a different dielectric material from masking layer 130, such as an oxide-based dielectric material, so that masking layer 130 and spacer patterning layer 135 have differing etch selectivity properties. For example, masking layer 130 may be composed of silicon nitride and spacer patterning layer 135 may be composed of silicon dioxide. Spacer patterning layer 135 may be formed to a selected thickness T.sub.1 that may, in part, facilitate formation of spacers as described further below. Masking layer 130 may have a thickness T.sub.2 that is less than the thickness T.sub.1 of spacer patterning layer 135. The thickness T.sub.1 of spacer patterning layer 135 may, as described below, partially define a height of spacers 151 and 152 formed on sidewalls of an opening 137 (FIG. 4) patterned in the spacer patterning layer 135.

[0020] With reference to FIGS. 3 and 3A and in which like reference numerals refer to like features in FIG. 2 and at a subsequent fabrication stage of the processing method, a lithography stack 140 and a resist layer 144 are formed over spacer patterning layer 135. Lithography stack 140 may include an organic spin-on hardmask (SOH) layer, a silicon oxynitride (SiON) hardmask layer, and an anti-reflective coating layer. The resist layer 144 is patterned to form an opening 145, or multiple openings as described below, aligned over portions of dummy line 125 that is designated to be cut to provide small tip-to-tip spacings. The opening 145 exposes a portion of spacer patterning layer 135 to be etched and removed as described below.

[0021] With reference to FIG. 4 in which like reference numerals refer to like features in FIGS. 3 and 3A and at a subsequent fabrication stage of the processing method, an opening 137 is etched in spacer patterning layer 135. Opening 137 may be formed, for example, by a reactive ion etch (ME) process. The opening 137 may have a width dimension W that is about equal to twice a selected thickness T.sub.3 of a conformal layer 150 to be formed over spacer patterning layer 135 plus a length L separating a spacer 151 from a spacer 152 (which are formed from conformal layer 150) as shown in FIG. 5. For example, selected thickness T.sub.3 of conformal layer 150 may be about 5 nm, and length L separating spacers 151 and 152 may be about 15 nm, so that width W of opening 137 may be about 25 nm. The etching may be a selective etch process that is controlled to remove the exposed portion of spacer patterning layer 135 and to terminate on the material of the masking layer 130. The opening 137 exposes a portion of masking layer 130 overlying a portion of dummy line 125. As used herein, the term "selective" in reference to a material removal process (e.g., etching) denotes that, with an appropriate etchant choice, the material removal rate (i.e., etch rate) for the targeted material is greater than the removal rate for at least another material exposed to the material removal process.

[0022] The opening 137, which is a single opening of relatively large dimensions in the spacer patterning layer 135, may be used to form multiple closely-spaced cuts, as subsequently described, in contrast with conventional techniques that require multiple "colors" or stages of patterning to form closely-spaced cuts of small relative dimensions. In addition, the spacing between adjacent conventional cuts may be limited due to lithography resolution limits, which is mitigated through the use of spacers as described below.

[0023] With reference to FIG. 5 in which like reference numerals refer to like features in FIG. 4 and at a subsequent fabrication stage of the processing method, a conformal layer 150 is deposited on the spacer patterning layer 135 and over the sidewalls and base of the opening 137 in spacer patterning layer 135. The sections of conformal layer 150 deposited on sidewalls of opening 137 define a spacer 151 and a spacer 152. As depicted and described below in FIG. 6A, spacer 151 and spacer 152 may be included among a plurality of spacers that are arranged to form a "spacer ring" 155 on the sidewalls of the opening 137. As also described and depicted below in FIG. 6A, spacer 151 and spacer 152 overlie and traverse dummy line 125. The thickness T.sub.1 of spacer patterning layer 135 may define, at least in part, a height of spacers 151 and 152 formed on sidewalls of the opening 137 of spacer patterning layer 135. The thickness T.sub.3 of the conformal layer 150 may be selected to determine a thickness T.sub.4 of spacers 151 and 152 and may further define, at least partially, a length L separating spacer 151 and spacer 152. The thickness T.sub.4 of spacer 151 and of spacer 152 may also define a size of gaps separating ends of metal lines formed in dielectric layer 110, as described further below. For example, a conformal layer 150 having a thickness T.sub.3 of 5 nm may form spacers 151, 152 having thickness T.sub.4 of 5 nm, so that gaps formed between the ends of metal lines in dielectric layer 110 are also 5 nm. The length L separating spacer 151 and spacer 152 may be 15 nm or less, so that a resulting metal island 165 formed in dielectric layer 110, as described further below, may have a length L.sub.m of 15 nm or less. The conformal layer 150, and by extension, the spacers 151 and 152, and masking layer 130 may be composed of the same material, for example a nitride-based dielectric material such as silicon nitride.

[0024] With reference to FIGS. 6 and 6A in which like reference numerals refer to like features in FIG. 5 and at a subsequent fabrication stage of the processing method, conformal layer 150 is removed from over spacer patterning layer 135, leaving spacer ring 155, including spacer 151 and spacer 152, disposed over the exposed portion of masking layer 130. The conformal layer 150 may be removed, for example, by a selective anisotropic etch process, such as a reactive-ion etch (RIE) process, controlled to terminate when spacer patterning layer 135 is exposed by the etch. A controlled anisotropic etch process allows for removal of the conformal layer 150 with minimal etching of spacers 151, 152. As FIG. 6A illustrates, the conformal layer 150 deposited on sidewalls of the opening 137 in spacer patterning layer 135 may form the spacer ring 155 or ring-like spacer formation, including the spacer 151 and spacer 152 that overlie and traverse dummy line 125.

[0025] With reference to FIGS. 7 and 7A in which like reference numerals refer to like features in FIGS. 6 and 6A and at a subsequent fabrication stage of the processing method, spacer patterning layer 135 and masking layer 130 are removed, which leaves spacers 151 and 152 disposed over different sections of the dummy line 125. As FIGS. 7 and 7A show, spacer 151 and spacer 152 overly and traverse dummy line 125 in a spaced apart fashion. Spacer patterning layer 135 may be removed by a selective etch process that selectively removes the material of spacer patterning layer 135 without etching either the masking layer 130 or spacers 151, 152. Masking layer 130 may be etched by a selective etch process controlled to remove masking layer 130 without fully etching or removing spacer 151 and spacer 152, such as a reactive ion etching (RIE) process controlled to terminate when the dielectric layer 124 of patterning stack 120 is exposed by the etch process.

[0026] With reference to FIGS. 8 and 8A in which like reference numerals refer to like features in FIGS. 7 and 7A and at a subsequent fabrication stage of the processing method, dummy lines 125 and 126 are removed to expose underlying portions of hardmask layer 122. Spacer 151 and spacer 152 protect underlying portions 127, 128 of dummy line 125 from removal, so that in subsequent fabrication stages, as described below, the portions of hardmask layer 122 underlying the remaining portions 127, 128 of dummy line 125 will remain unetched and form "cuts" or gaps in a final metallization line to be formed in dielectric layer 110.

[0027] With reference to FIGS. 9 and 9A in which like reference numerals refer to like features in FIGS. 8 and 8A and at a subsequent fabrication stage of the processing method, the exposed portions of hardmask layer 122 are etched to form trenches in the hardmask layer 122 and expose portions of the dielectric layer 110 to be etched. Remaining portions of spacers 151 and 152 are also removed. The material of spacers 151 and 152, as well as other spacers of spacer ring 155, may be removed by, for example, a selective etch process. Dielectric layer 124 may be removed via a separate selective etch process, as illustrated in FIG. 9. Alternatively, dielectric layer 124 may remain to be etched during a subsequent etch of dielectric 110, illustrated in FIG. 10 and further described below. Remaining portions 127, 128 of dummy line 125 protect the underlying portions 122a, 122b of hardmask layer 122 and define gaps in the trenches formed in hardmask layer 122. Dummy lines 125, 126 may be removed, for example, by a selective anisotropic etch process such as a reactive ion etching (RIE) process.

[0028] With reference to FIGS. 10 and 10A in which like reference numerals refer to like features in FIGS. 9 and 9A and at a subsequent fabrication stage of the processing method, metallization trenches are formed in dielectric layer 110 using the trenches etched in hardmask layer 122, and the trenches are filled with a conductive material to form metal lines 160, 161. Remaining portions of the hardmask layer 122 are removed, exposing the dielectric layer 110. Metal line 165, resulting from the cuts or gaps defined by the spacers 151 and 152 as described above, may be considered a "metal island" as it is electrically isolated from surrounding metal lines 160, 161. The metal island 165 may have a length L.sub.m of 15 nm or less. The conductive material may be any conductive material, such as cobalt or ruthenium or copper or other conductive material used to form metal lines in a circuit structure. Cobalt may be a preferred conductive material for forming metal lines 160, 161 and metal island 165 because cobalt may be used to form very short metal lines, such as metal islands of 15 nm or less, whereas copper metal lines generally must have a minimum length that is greater than 15 nm due to the material properties of copper and due to reliability issues during service and use of an integrated circuit structure.

[0029] With reference to FIGS. 11 and 11A in which like reference numerals refer to like features in FIGS. 7 and 7A in a further embodiment of the processing method, multiple sets of spacers 156, 157, 158 may be formed over dummy line 125 to define multiple sets of cuts or gaps in the dummy line 125, and subsequently in metal lines formed in dielectric layer 110. Multiple sets of spacers 156, 157, 158 may be formed via a lithographic etch process, as described in part above, in which multiple openings are etched in spacer patterning layer 135 and the conformal layer 150 subsequently deposited over spacer patterning layer 135 forms multiple spacers 156, 157, 158. In embodiments in which an even number of cuts or gaps are needed in dummy line 125, multiple wider openings, similar to opening 137 in spacer patterning layer 135 depicted in FIGS. 4-5, may be formed in spacer patterning layer 135 that result in the formation of multiple spacer rings or ring-like spacers similar to the single spacer ring illustrated in FIGS. 5-6A. In embodiments in which an odd number of cuts or gaps in dummy line 125 are needed, multiple wider openings, similar to opening 137 in spacer patterning layer 135 depicted in FIGS. 4-5, may be formed in spacer patterning layer 135 that result in the formation of multiple spacer rings, and an additional narrow opening may be formed in spacer patterning layer 135 that results in spacers 158. The additional narrow opening in spacer patterning layer 135 may have a width dimension W.sub.N that is less than twice the thickness T.sub.3 of the conformal layer 150 formed over the spacer patterning layer 135, resulting in spacers 158 that merge into a single spacer block disposed over dummy line 125. The single spacer block formed by spacers 158 then forms a single cut or gap in dummy line 125.

[0030] With reference to FIGS. 12 and 13 in which like reference numerals refer to like features in FIGS. 1-10A and in a further embodiment of the processing method, the dielectric layer 110, including metal lines 160, 161, and metal island 165, may be one metallization layer in a circuit structure 100a and may be disposed above a lower metallization layer 170 having a plurality of metal lines 171 and below an upper metallization layer 175 having a plurality of metal lines 176. As depicted in FIG. 12, a lower metallization layer 170 may be formed first and a via 182 formed to connect to one metal line 171 in lower metallization layer 170. The dielectric layer 110 may then be formed, as described above, with a metal island 165 aligned with the via 182 connected to metal line 171. Conductive via 182 may be formed, for example, by etching a hole through the dielectric material of dielectric layer 110, prior to formation of metal lines 160, 161, and metal island 165, and subsequently filling the hole with a conductive material such as cobalt, ruthenium, or copper. The conductive via 182 may be filled along with metal lines 160, 161, and metal island 165 in the same processing step or may be filled prior to forming metal lines 160, 161, and metal island 165 as described above. As depicted in FIG. 13, another conductive via 184 may then be formed that connects to metal island 165, and the upper metallization layer 175 may then be formed over dielectric layer 110 with one metal line 176 in upper metallization layer 175 aligned to and connecting with the other conductive via 184. Conductive via 184 may be formed by similar processes as for forming via 182. The circuit structure 100a formed thus has an interconnection between upper metallization layer 175 and lower metallization layer 170, wherein dielectric layer 110 separates the upper metallization layer 175 and lower metallization layer 170. Conductive vias 182 and 184, in conjunction with metal island 165 formed in dielectric layer 110, form an extended via or "super via" that permits interconnection between metal lines of non-adjacent metallization levels in circuit structure 100a. The metal island 165 formed as described herein allows for efficient conductive connection between conductive vias 182 and 184 as metal island 165 may be formed to have a size substantially equal to a size of conductive vias 182 and 184 so as to minimize area losses.

[0031] The methods as described above are used in the fabrication of integrated circuit chips. The resulting integrated circuit chips can be distributed by the fabricator in raw wafer form (e.g., as a single wafer that has multiple unpackaged chips), as a bare die, or in a packaged form. In the latter case, the chip is mounted in a single chip package (e.g., a plastic carrier, with leads that are affixed to a motherboard or other higher level carrier) or in a multichip package (e.g., a ceramic carrier that has either or both surface interconnections or buried interconnections). In any case, the chip may be integrated with other chips, discrete circuit elements, and/or other signal processing devices as part of either an intermediate product or an end product.

[0032] References herein to terms such as "vertical", "horizontal", "lateral", etc. are made by way of example, and not by way of limitation, to establish a frame of reference. Terms such as "horizontal" and "lateral" refer to a direction in a plane parallel to a top surface of a semiconductor substrate, regardless of its actual three-dimensional spatial orientation. Terms such as "vertical" and "normal" refer to a direction perpendicular to the "horizontal" and "lateral" direction. Terms such as "above" and "below" indicate positioning of elements or structures relative to each other and/or to the top surface of the semiconductor substrate as opposed to relative elevation.

[0033] A feature "connected" or "coupled" to or with another element may be directly connected or coupled to the other element or, instead, one or more intervening elements may be present. A feature may be "directly connected" or "directly coupled" to another element if intervening elements are absent. A feature may be "indirectly connected" or "indirectly coupled" to another element if at least one intervening element is present.

[0034] The descriptions of the various embodiments of the present invention have been presented for purposes of illustration, but are not intended to be exhaustive or limited to the embodiments disclosed. Many modifications and variations will be apparent to those of ordinary skill in the art without departing from the scope and spirit of the described embodiments. The terminology used herein was chosen to best explain the principles of the embodiments, the practical application or technical improvement over technologies found in the marketplace, or to enable others of ordinary skill in the art to understand the embodiments disclosed herein.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

D00009

D00010

D00011

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.