Shift register unit, shift register and driving method, and display apparatus

Hao , et al. April 5, 2

U.S. patent number 11,295,652 [Application Number 16/954,503] was granted by the patent office on 2022-04-05 for shift register unit, shift register and driving method, and display apparatus. This patent grant is currently assigned to BEIJING BOE TECHNOLOGY DEVELOPMENT CO., LTD., BOE TECHNOLOGY GROUP CO., LTD.. The grantee listed for this patent is BEIJING BOE TECHNOLOGY DEVELOPMENT CO., LTD., BOE TECHNOLOGY GROUP CO., LTD.. Invention is credited to Xueguang Hao, Yong Qiao, Xinyin Wu, Jianbo Xian.

View All Diagrams

| United States Patent | 11,295,652 |

| Hao , et al. | April 5, 2022 |

Shift register unit, shift register and driving method, and display apparatus

Abstract

A shift register unit can include a storage circuit and an output circuit respectively connected to a pull-up node, a gate electrode driving signal output terminal, and an output voltage signal input terminal, and can connect or disconnect the gate electrode driving signal output terminal and the output voltage signal input terminal under the control of electric potential of the pull-up node; the storage circuit can be respectively connected to the pull-up node and the gate electrode driving signal output terminal and can control the electric potential of the pull-up node during the gate electrode driving signal output stage, such that the output circuit can connect the gate electrode driving signal output terminal and the output voltage signal input terminal. During a gate electrode driving signal output stage, the electric potential of the pull-up node can be maintained, such that gate electrode driving signals can be outputted normally.

| Inventors: | Hao; Xueguang (Beijing, CN), Xian; Jianbo (Beijing, CN), Qiao; Yong (Beijing, CN), Wu; Xinyin (Beijing, CN) | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Applicant: |

|

||||||||||

| Assignee: | BEIJING BOE TECHNOLOGY DEVELOPMENT

CO., LTD. (Beijing, CN) BOE TECHNOLOGY GROUP CO., LTD. (Beijing, CN) |

||||||||||

| Family ID: | 66727946 | ||||||||||

| Appl. No.: | 16/954,503 | ||||||||||

| Filed: | November 19, 2019 | ||||||||||

| PCT Filed: | November 19, 2019 | ||||||||||

| PCT No.: | PCT/CN2019/119380 | ||||||||||

| 371(c)(1),(2),(4) Date: | June 16, 2020 | ||||||||||

| PCT Pub. No.: | WO2020/108344 | ||||||||||

| PCT Pub. Date: | June 04, 2020 |

Prior Publication Data

| Document Identifier | Publication Date | |

|---|---|---|

| US 20210166600 A1 | Jun 3, 2021 | |

Foreign Application Priority Data

| Nov 26, 2018 [CN] | 201821954354.X | |||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | G09G 3/20 (20130101); G11C 19/28 (20130101); G09G 2310/0267 (20130101); G09G 2310/08 (20130101); G09G 2310/0286 (20130101) |

| Current International Class: | G09G 3/20 (20060101) |

References Cited [Referenced By]

U.S. Patent Documents

| 2016/0267864 | September 2016 | Xiao |

| 2020/0273419 | August 2020 | Wang |

| 103280196 | Sep 2013 | CN | |||

| 107068106 | Aug 2017 | CN | |||

| 107424552 | Dec 2017 | CN | |||

| 108682380 | Oct 2018 | CN | |||

Other References

|

International Search Report in Application No. PCT/CN2019/119380, dated Feb. 28, 2020. cited by applicant. |

Primary Examiner: Lee; Laurence J

Attorney, Agent or Firm: Syncoda LLC Ma; Feng

Claims

What is claimed is:

1. A shift register unit, comprising: an output circuit; and a storage circuit; wherein: the output circuit is respectively connected to a pull-up node, a gate electrode driving signal output terminal that is connected to a pull-down node, and an output voltage signal input terminal, the output circuit being configured to connect or disconnect the gate electrode driving signal output terminal and the output voltage signal input terminal under control of an electric potential of the pull-up node; the storage circuit is respectively connected to the pull-up node and the gate electrode driving signal output terminal; and the storage circuit is configured to control the electric potential of the pull-up node during a gate electrode driving signal output stage, such that the output circuit is configured to connect the gate electrode driving signal output terminal and the output voltage signal input terminal; the shift register unit further comprising: a pull-down node reset circuit, the pull-down node reset circuit being respectively connected to the pull-down node, the gate electrode driving signal output terminal, and a pull-down reset voltage input terminal; wherein the pull-down node reset circuit is configured to connect or disconnect the pull-down reset voltage input terminal and the pull-down node under the control of the gate electrode driving signal output terminal.

2. The shift register unit according to claim 1, wherein: the storage circuit comprises a first storage capacitor; the first terminal of the first storage capacitor is connected to the pull-up node; and the second terminal of the first storage capacitor is connected to the gate electrode driving signal output terminal.

3. The shift register unit according to claim 1, wherein: the pull-down node reset circuit further comprises a pull-down node reset transistor; wherein: the gate electrode of the pull-down node reset transistor is connected to the gate electrode driving signal output terminal, wherein the first electrode of the pull-down node reset transistor is connected to the pull-down node; and wherein the second electrode of the pull-down node reset transistor is connected to the pull-down reset voltage input terminal.

4. The shift register unit according to claim 3, wherein: the pull-down node reset circuit also includes a holding capacitor being provided between a signal side and an electrical connection side of the pull-down node; and the holding capacitor is configured to maintain an output potential of the output transistor.

5. The shift register unit according to claim 3, further comprising: an output reset circuit provided connected between the pull-down node and the gate electrode driving a signal output terminal; a pull-down node control circuit operatively connected to the output reset circuit, the pull-down-node, and a pull-up node control circuit, the pull-up node control circuit being operatively connected to the output circuit and the pull-up node; wherein: the pull-down node control circuit is connected to a forward scan control, the forward scan control terminal being provided at an input side of the pull-up node control unit; and the pull-down node control circuit is connected between the pull-down node and a reverse scan control terminal, the reverse scan control terminal being provided at an input side of the pull-up node control unit independent from the forward scan control terminal.

6. The shift register unit according to claim 1, wherein: the output circuit comprises an output transistor, wherein the gate electrode of the output transistor is connected to the pull-up node; the first electrode of the output transistor is connected to the output voltage signal input terminal; and the second electrode of the output transistor is connected to the gate electrode driving signal output terminal.

7. The shift register unit of claim 6, wherein the output voltage signal input terminal is an output clock signal input terminal.

8. A gate electrode driving circuit, comprising a plurality of levels of shift register units, each shift level unit being provided in accordance with the shift register unit of claim 1.

9. A display apparatus comprising the gate electrode driving circuits according to claim 8.

10. A shift register unit, comprising: an output circuit; and a storage circuit; wherein: the output circuit is respectively connected to a pull-up node, a gate electrode driving signal output terminal that is connected to a pull-down node, and an output voltage signal input terminal, the output circuit being configured to connect or disconnect the gate electrode driving signal output terminal and the output voltage signal input terminal under control of an electric potential of the pull-up node; the storage circuit is respectively connected to the pull-up node and the gate electrode driving signal output terminal; the storage circuit is configured to control the electric potential of the pull-up node during a gate electrode driving signal output stage, such that the output circuit is configured to connect the gate electrode driving signal output terminal and the output voltage signal input terminal; the output circuit comprises an output transistor, wherein the gate electrode of the output transistor is connected to the pull-up node; the first electrode of the output transistor is connected to the output voltage signal input terminal; and the second electrode of the output transistor is connected to the gate electrode driving signal output terminal; the shift register unit further comprising: an output reset circuit; a pull-up node control circuit; and a pull-down node control circuit; wherein: the output reset circuit is respectively connected to the pull-down node, the gate electrode driving signal output terminal and a first voltage input terminal, and configured to connect or disconnect the gate electrode driving circuit output terminal and the first voltage input terminal under a control of an electric potential of the pull-down node; the pull-up node control circuit is connected to the pull-up node, and configured to control the electric potential of the pull-up node; and the pull-down node control circuit is connected to the pull-down node, and configured to control the electric potential of the pull-down node.

11. The shift register unit according to claim 10, wherein: the pull-up node control circuit is further respectively connected to the pull-down node, an adjacent upper level gate electrode driving signal output terminal, an adjacent lower level gate electrode driving signal output terminal, and a forward scan control terminal and a reverse scan control terminal; and the pull-up node control circuit is configured to connect or disconnect the pull-up node and the first voltage input terminal under the control of the pull-down node, connect or disconnect the forward scan control terminal and the pull-up node under the control of the adjacent upper level gate driving signal output terminal, and connect or disconnect the reverse scan control terminal and the pull-up node under the control of the adjacent lower level gate driving signal output terminal.

12. The shift register unit according to claim 11, wherein: the pull-up node control circuit comprises a first pull-up control transistor, a second pull-up control transistor, and a third pull-up control transistor; the gate electrode of the first pull-up control transistor is connected to the adjacent upper level gate electrode driving signal output terminal; the first electrode of the first pull-up control transistor is connected to the pull-up node; the second electrode of the first pull-up control transistor is connected to the forward scan control terminal; the gate electrode of the second pull-up control transistor is connected to the lower level gate electrode driving signal output terminal; the first electrode of the second pull-up control transistor is connected to the reverse scan control terminal; the second electrode of the second pull-up control transistor is connected to the pull-up node; the gate electrode of the third pull-up control transistor is connected to the pull-down node; the first electrode of the third pull-up control transistor is connected to the pull-up node; and the second electrode of the third pull-up control transistor is connected to the first voltage input terminal.

13. The shift register unit according to claim 10, wherein: the pull-down node control circuit is further connected to the pull-up node, a forward scan control terminal, a forward scan clock signal input terminal, a reverse scan control terminal, a reverse scan clock signal input terminal, the first voltage input terminal, and a second voltage input terminal; the pull-down node control circuit is configured to connect or disconnect the forward scan clock signal input terminal and a pull-down control node under the control of the forward scan control terminal, connect or disconnect the reverse scan clock signal input terminal and the pull-down control node under the control of the reverse scan control terminal, connect or disconnect the pull-down node and the second voltage input terminal under the control of the electric potential of the pull-down control node, and connect or disconnect the pull-down node and the first voltage input terminal under the control of the pull-up node.

14. The shift register unit according to claim 13, wherein: the pull-down node control circuit comprises a first pull-down control transistor, a second pull-down control transistor, a third pull-down control transistor and a fourth pull-down control transistor; the gate electrode of the first pull-down control transistor is connected to the forward scan control terminal; the first electrode of the first pull-down control transistor is connected to the forward scan clock signal input terminal; the second electrode of the first pull-down control transistor is connected to the pull-down control node; the gate electrode of the second pull-down control transistor is connected to the reverse scan control terminal; the first electrode of the second pull-down control transistor is connected to the reverse scan clock signal input terminal; the second electrode of the second pull-down control transistor is connected to the pull-down control node; the gate electrode of the third pull-down control transistor is connected to the pull-down control node; the first electrode of the third pull-down control transistor is connected to the pull-down node; the second electrode of the third pull-down control transistor is connected to the second voltage input terminal; the gate electrode of the fourth pull-down control transistor is connected to the pull-up node; the first electrode of the fourth pull-down control transistor is connected to the first voltage input terminal; and the second electrode of the fourth pull-down control transistor is connected to the pull-down node.

15. The shift register unit according to claim 13, wherein: the shift register unit is provided with a first input clock terminal, a second input clock terminal, a third input clock terminal, and a fourth input clock terminal, wherein the forward scan clock signal input terminal is the third input clock terminal; the reverse scan clock signal input terminal is the first input clock terminal; the first voltage input terminal is a low voltage terminal; and the second voltage input terminal is a high voltage terminal.

16. The shift register unit according to claim 15, wherein: the first input clock terminal is configured to receive input regarding a first clock signal; the second input clock terminal is configured to receive input regarding a second clock signal; the third input clock terminal is configured to receive input regarding a third clock signal; and wherein the fourth input clock terminal is configured to receive input regarding a fourth clock signal.

17. The shift register unit according to claim 16, wherein: the period of the first clock signal, the period of the second clock signal, the period of the third clock signal, and the period of the fourth clock signal are equal, and a total period is defined as T; and the duty ratio of the first clock signal, the duty ratio of the second clock signal, the duty ratio of the third clock signal and the duty ratio of the fourth clock signal are all 1/4T.

18. The shift register unit according to claim 10, wherein the output reset circuit comprises: an output reset transistor, wherein a gate electrode of the output reset transistor is connected to the pull-down node, wherein a first electrode of the output reset transistor is connected to the gate electrode driving signal output terminal, wherein a second electrode of the output reset transistor is connected to the first voltage input terminal; and a second storage capacitor, wherein a first terminal of the second storage capacitor is connected to the pull-down node, and wherein a second terminal of the second storage capacitor is connected to the first voltage input terminal.

Description

CROSS-REFERENCE TO RELATED APPLICATIONS

The present application is a national stage of International Application No. PCT/CN2019/119380 filed on Nov. 19, 2019, which claims priority to Chinese Patent Application No. 201821954354.X filed on Nov. 28, 2018. The disclosures of these applications are hereby incorporated by reference in their entirety.

TECHNICAL FIELD

The present disclosure relates generally to a field of display technologies, and specifically to a shift register unit, a gate electrode driving circuit and a display apparatus.

BACKGROUND

In gate electrode driving circuits in existing technologies, a pull-up node and an electrode plate that maintains capacitance with the pull-up node can be connected to a low voltage terminal, as a result, during an output stage, the capacitance of the pull-up node can be held up and thus will not contribute to the increase of the electric potential of the pull-up node, only the electric potential of the gate electrode of the output transistor can be held up, because the electric potential of the gate electrode driving signal output terminal can be increased to become high electric potential at this time, the output transistor can be shut off by mistake, the output of the gate electrode driving signal can therefore be negatively impacted.

SUMMARY

Various embodiments of the present disclosure provide a shift register unit, a gate electrode driving circuit and a display apparatus, which can solve the problems such as unstable output of gate electrode driving signals.

In a first aspect of the present disclosure, a shift register unit can be provided.

The shift register unit can include:

an output circuit; and

a storage circuit;

wherein:

the output circuit is respectively connected to a pull-up node, a gate electrode driving a signal output terminal, the signal output terminal being connected to a pull-down node, and an output voltage signal input terminal, the output circuit being configured to connect or disconnect the gate electrode driving signal output terminal and the output voltage signal input terminal under the control of the electric potential of the pull-up node;

the storage circuit is respectively connected to the pull-up node and the gate electrode driving signal output terminal; and

the storage circuit is configured to control the electric potential of the pull-up node during the gate electrode driving voltage output stage, such that the output circuit can connect the gate electrode driving signal output terminal and the output voltage signal input terminal.

In some embodiments:

the storage circuit comprises a first storage capacitor;

the first terminal of the first storage capacitor is connected to the pull-up node; and

the second terminal of the first storage capacitor is connected to the gate electrode driving signal output terminal.

In some embodiments, the shift register can further include:

a pull-down node reset circuit, the pull-down node reset circuit being respectively connected to the pull-down node, the gate electrode driving signal output terminal, and the pull-down reset voltage input terminal;

wherein the pull-down node reset circuit is configured to connect or disconnect the pull-down reset voltage input terminal and the pull-down node under the control of the gate electrode driving signal output terminal.

In some embodiments:

the pull-down node reset circuit further includes a pull-down node reset transistor;

wherein:

the gate electrode of the pull-down node reset transistor is connected to the gate electrode driving signal output terminal, wherein the first electrode of the pull-down node reset transistor is connected to the pull-down node; and

wherein the second electrode of the pull-down node reset transistor is connected to the pull-down rest voltage input terminal.

In some embodiments:

the output circuit comprises an output transistor, wherein the gate electrode of the output transistor is connected to the pull-up node;

the first electrode of the output transistor is connected to the output voltage signal input terminal; and

the second electrode of the output transistor is connected to the gate electrode driving signal output terminal.

In some embodiments, the output voltage signal input terminal is an output clock signal input terminal.

In some embodiments, the shift register unit can further include:

an output reset circuit;

a pull-up node control circuit; and

a pull-down node control circuit;

wherein:

the output reset circuit is respectively connected to the pull-down node, the gate electrode driving signal output terminal and the first voltage input terminal, it is utilized to connect or disconnect the gate electrode driving circuit output terminal and the first voltage input terminal under the control of electric potential of the pull-down node;

the pull-up node control circuit is connected to the pull-up node, it is utilized to control the electric potential of the pull-up node; and

the pull-down node control circuit is connected to the pull-down node, it is utilized to control the electric potential of the pull-down node.

In some embodiments:

the pull-up node control circuit is further respectively connected to the pull-down node, an adjacent upper level gate electrode driving signal output terminal, an adjacent lower level gate electrode driving signal output terminal, and a forward scan control terminal and a reverse scan control terminal; and

the pull-up node control circuit is configured to connect or disconnect the pull-up node and the first voltage input terminal under the control of the pull-down node, connect or disconnect the forward scan control terminal and the pull-up node under the control of the adjacent upper level gate driving signal output terminal, and connect or disconnect the reverse scan control terminal and the pull-up node under the control of the adjacent lower level gate driving signal output terminal.

In some embodiments:

the pull-up node control circuit comprises a first pull-up control transistor, a second pull-up control transistor, and a third pull-up control transistor;

the gate electrode of the first pull-up control transistor is connected to the adjacent upper level gate electrode driving signal output terminal;

the first electrode of the first pull-up control transistor is connected to the pull-up node;

the second electrode of the first pull-up control transistor is connected to the forward scan control terminal;

the gate electrode of the second pull-up control transistor is connected to the lower level gate electrode driving signal output terminal;

the first electrode of the second pull-up control transistor is connected to the reverse scan control terminal;

the second electrode of the second pull-up control transistor is connected to the pull-up node;

the gate electrode of the third pull-up control transistor is connected to the pull-down node;

the first electrode of the third pull-up control transistor is connected to the pull-up node; and

the second electrode of the third pull-up control transistor is connected to the first voltage input terminal.

In some embodiments:

the pull-down node control circuit is further connected to the pull-up node, the forward scan control terminal, the forward scan clock signal input terminal, the reverse scan control terminal, the reverse scan clock signal input terminal, the first voltage input terminal, and the second voltage input terminal;

the pull-down node control circuit is configured to connect or disconnect the forward scan clock signal input terminal and the pull-down control node under the control of the forward scan control terminal, connect or disconnect the reverse scan clock signal input terminal and the pull-down control node under the control of the reverse scan control terminal, connect or disconnect the pull-down node and the second voltage input terminal under the control of the electric potential of the pull-down control node, and connect or disconnect the pull-down node and the first voltage input terminal under the control of the pull-up node.

In some embodiments:

the pull-down node control circuit comprises a first pull-down control transistor, a second pull-down control transistor, a third pull-down control transistor and a fourth pull-down control transistor;

the gate electrode of the first pull-down control transistor is connected to the forward scan control terminal;

the first electrode of the first pull-down control transistor is connected to the forward scan clock signal input terminal;

the second electrode of the first pull-down control transistor is connected to the pull-down control node;

the gate electrode of the second pull-down control transistor is connected to the reverse scan control terminal;

the first electrode of the second pull-down control transistor is connected to the reverse scan clock signal input terminal;

the second electrode of the second pull-down control transistor is connected to the pull-down control node;

the gate electrode of the third pull-down control transistor is connected to the pull-down control node;

the first electrode of the third pull-down control transistor is connected to the pull-down node;

the second electrode of the third pull-down control transistor is connected to the second voltage input terminal;

the gate electrode of the fourth pull-down control transistor is connected to the pull-up node;

the first electrode of the fourth pull-down control transistor is connected to the first voltage input terminal; and

the second electrode of the fourth pull-down control transistor is connected to the pull-down node.

In some embodiments, the output reset circuit includes:

an output reset transistor, wherein a gate electrode of the output reset transistor is connected to the pull-down node, wherein a first electrode of the output reset transistor is connected to the gate electrode driving signal output terminal, wherein a second electrode of the output reset transistor is connected to the first voltage input terminal; and

a second storage capacitor, wherein a first terminal of the second storage capacitor is connected to the pull-down node, and wherein a second terminal of the second storage capacitor is connected to the first voltage input terminal.

In another aspect, a gate electrode driving circuit is provided, including a plurality of levels of shift register units, each shift level unit being provided in accordance with the shift register unit described above.

In another aspect, a display apparatus is provided, including the gate electrode driving circuits described above.

In some embodiments:

the pull-down node reset circuit also includes a holding capacitor being provided between a signal side and an electrical connection side of the pull-down node;

and the holding capacitor is configured to maintain an output potential of the output transistor.

In some embodiments:

the pull-down node reset circuit also includes a holding capacitor being provided between a signal side and an electrical connection side of the pull-down node; and

the holding capacitor is configured to maintain an output potential of the output transistor.

In some embodiments, the shift register unit further includes an output reset circuit provided connected between the pull-down node and the gate electrode driving a signal output terminal.

In some embodiments, the shift register unit further includes:

a pull-down node control circuit operatively connected to the output reset circuit, the pull-down-node, and

a pull-up node control circuit, the pull-up node control circuit being operatively connected to the output circuit and the pull-up node.

In some embodiments, the pull-down node control circuit is connected to a forward scan control, the forward scan control terminal being provided at an input side of the pull-up node control unit.

In some embodiments, the pull-down node control circuit is connected between the pull-down node and a reverse scan control terminal, the reverse scan control terminal being provided at an input side of the pull-up node control unit independent from the forward scan control terminal.

In some embodiments, the pull-down node control circuit is connected to a reverse scan control terminal, the reverse scan control terminal being provided at an input side of the pull-up node control unit.

In some embodiments:

the shift register unit is provided with a first input clock terminal, a second input clock terminal, a third input clock terminal, and a fourth input clock terminal, wherein the forward scan clock signal input terminal can be the third clock signal input terminal;

the reverse scan clock signal input terminal is the first clock signal input terminal;

the first voltage input terminal is a low voltage terminal; and

the second voltage input terminal can be a high voltage terminal.

In some embodiments:

the first input clock terminal is configured to receive input regarding a first clock signal;

the second input clock terminal is configured to receive input regarding a second clock signal;

the third input clock terminal is configured to receive input regarding a third clock signal; and

wherein the fourth input clock terminal is configured to receive input regarding a fourth clock signal.

In some embodiments:

the period of the first clock signal, the period of the second clock signal, the period of the third clock signal, and the period of the fourth clock signal are equal, and a total period is defined as T; and

the duty ratio of the first clock signal, the duty ratio of the second clock signal, the duty ratio of the third clock signal and the duty ratio of the fourth clock signal are all 1/4 T.

In some embodiments:

the second clock signal is delayed by T/4 compared with the first clock signal;

the third clock signal is delayed by T/4 compared with the second clock signal; and

the fourth clock signal is delayed by T/4 compared with the third clock signal.

It is to be understood that both the above general description and the following detailed description are exemplary and explanatory only and are not restrictive of the present disclosure.

BRIEF DESCRIPTION OF DRAWINGS

To more clearly illustrate some of the embodiments, the following is a brief description of the drawings.

The drawings in the following descriptions are only illustrative of some embodiments. For those of ordinary skill in the art, other drawings of other embodiments can become apparent based on these drawings.

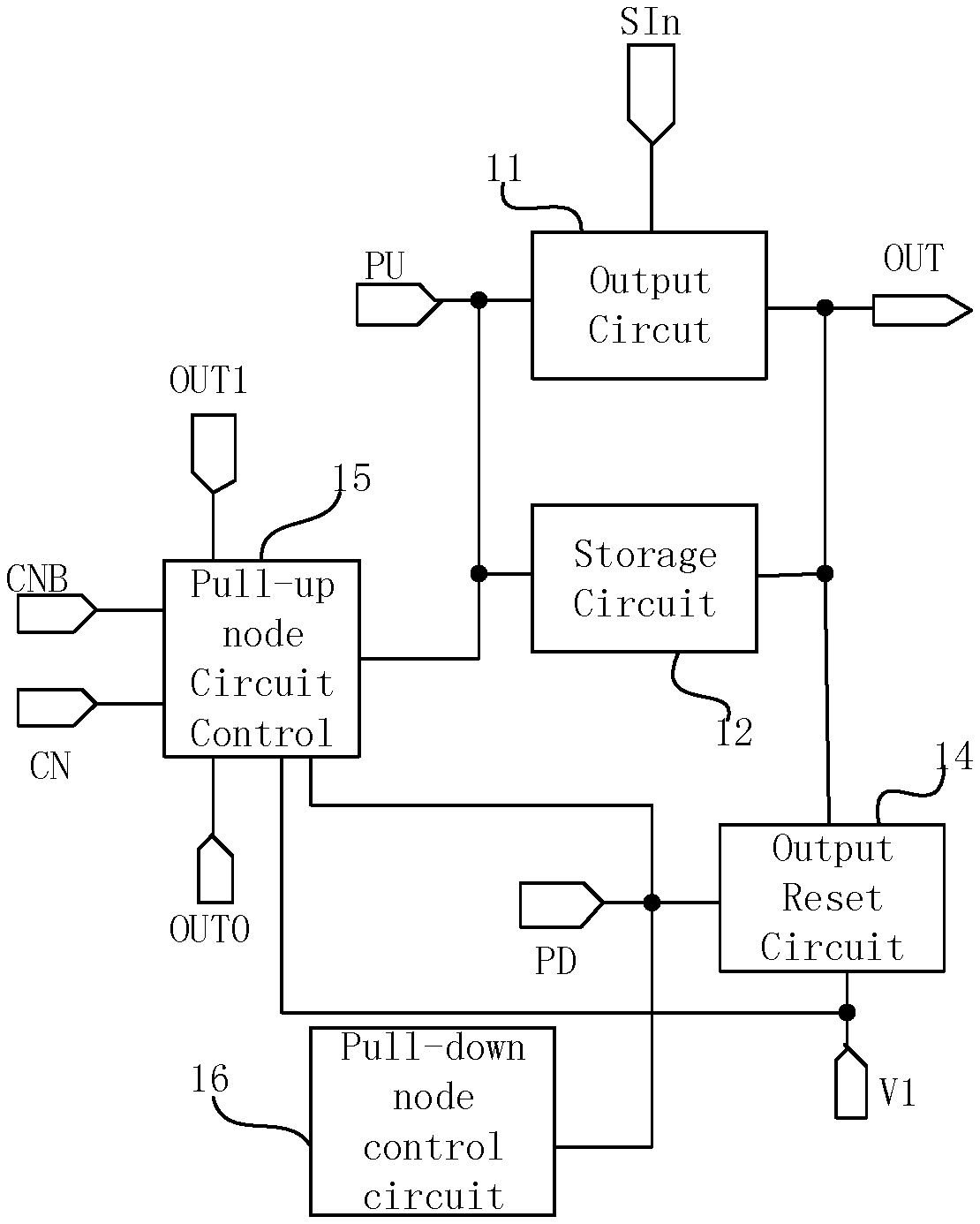

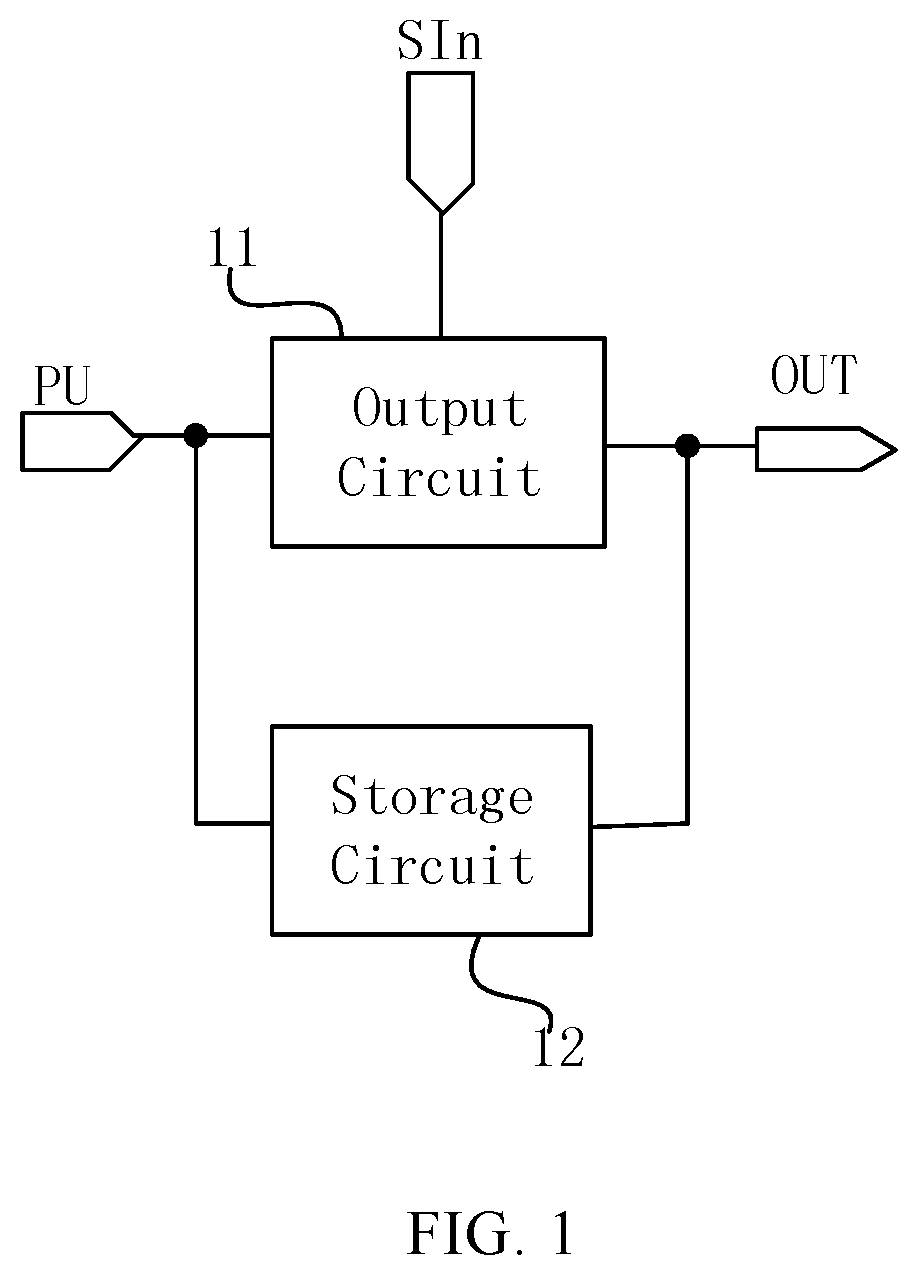

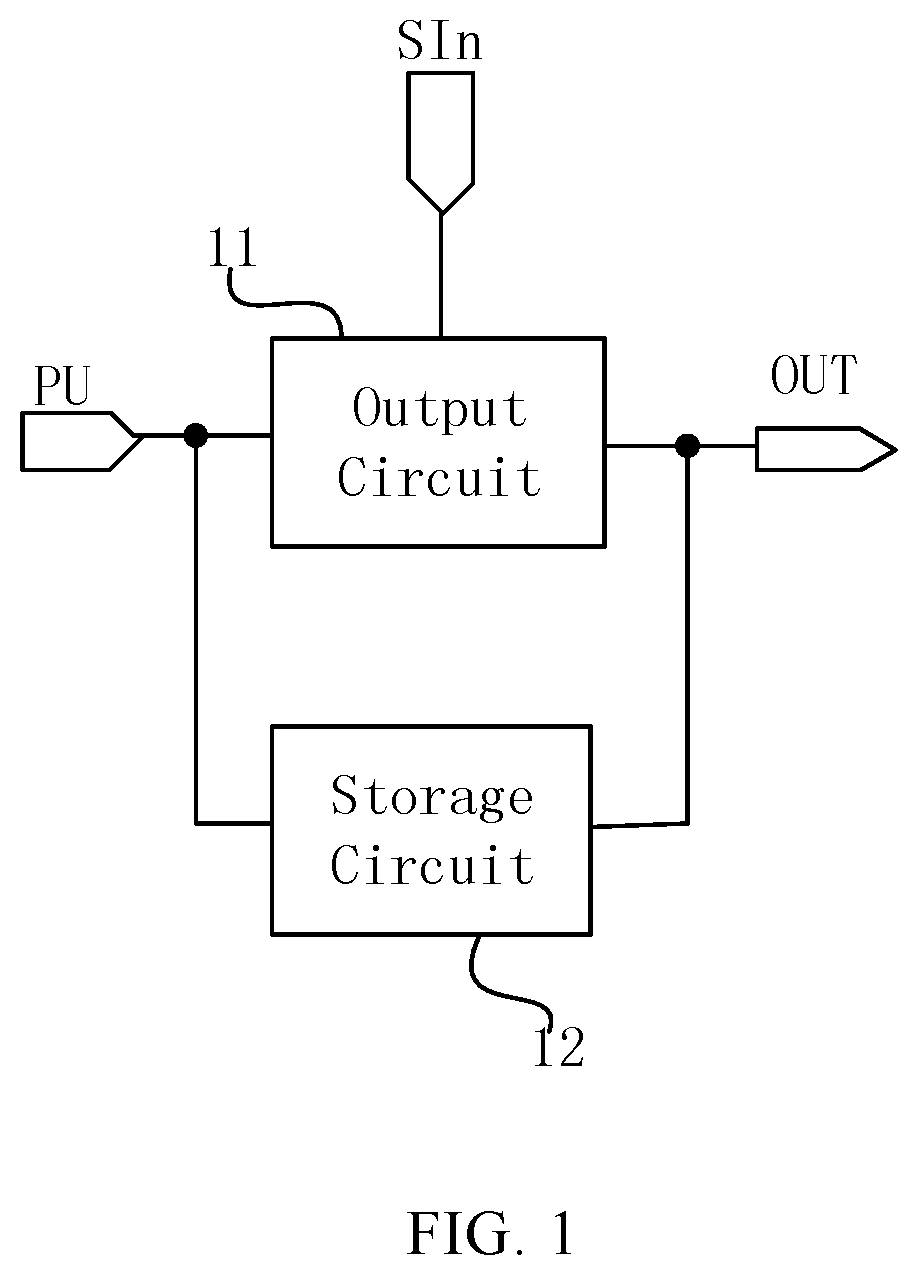

FIG. 1 illustrates a structural diagram of a shift register unit according to some embodiments of the present disclosure;

FIG. 2 illustrates a structural diagram of another shift register unit according to some other embodiments of the present disclosure;

FIG. 3 illustrates a structural diagram of yet another shift register unit according to yet some other embodiments of the present disclosure;

FIG. 4 illustrates a structural diagram of yet another shift register unit according to yet some other embodiments of the present disclosure;

FIG. 5 illustrates a structural diagram of yet another shift register unit according to yet some other embodiments of the present disclosure;

FIG. 6 illustrates a structural diagram of yet another shift register unit according to yet some other embodiments of the present disclosure;

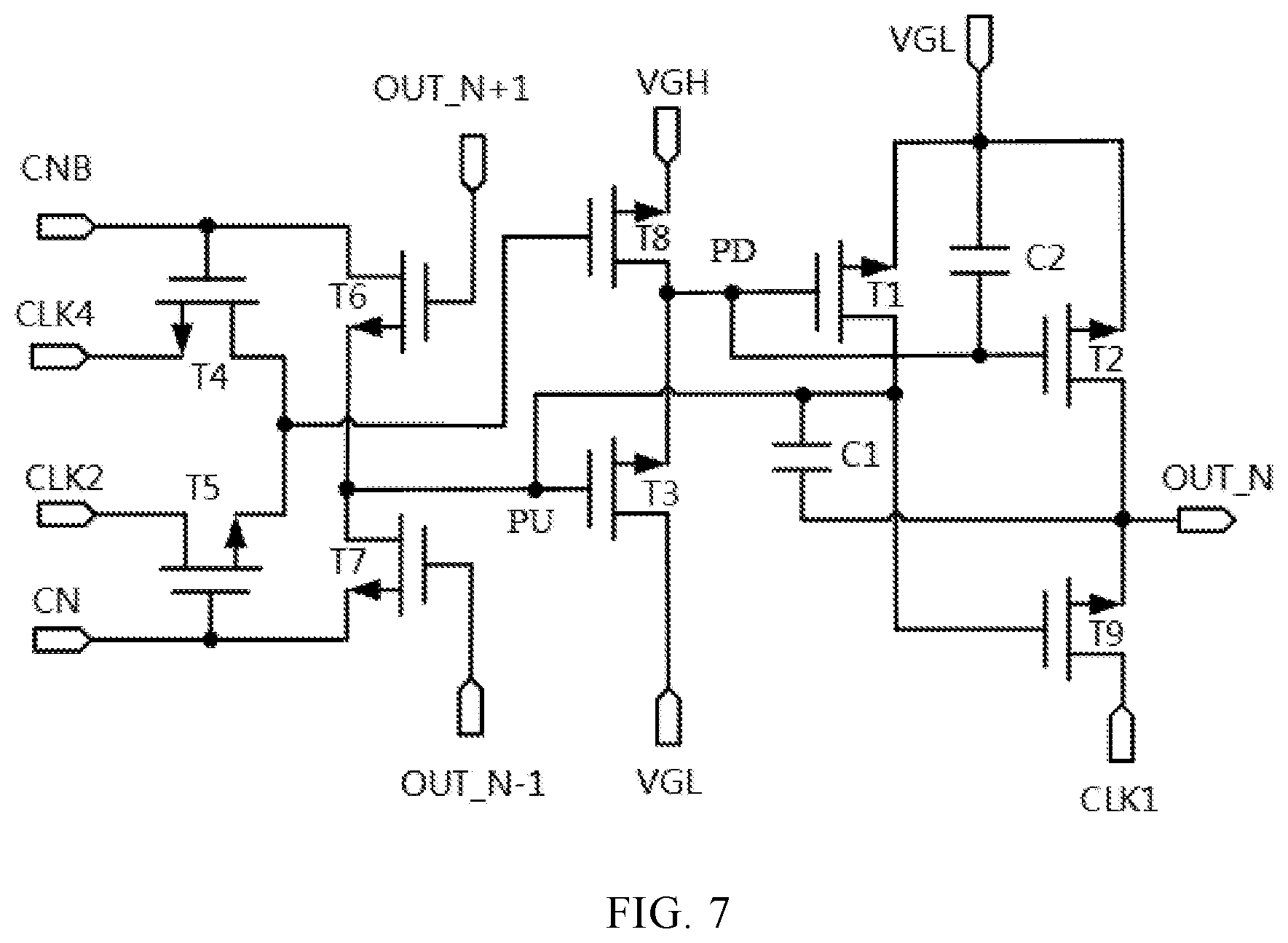

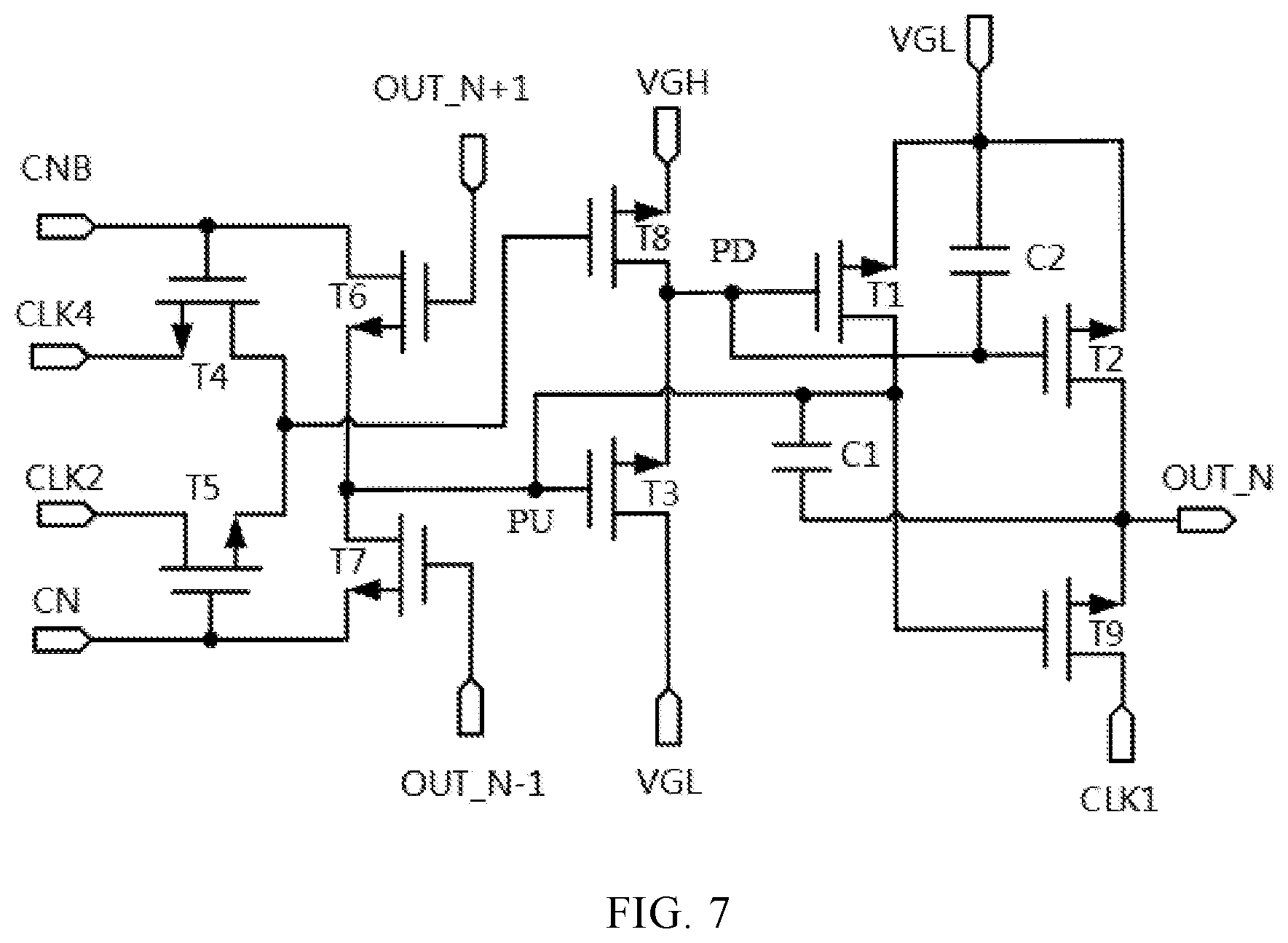

FIG. 7 illustrates a circuit diagram of a shift register unit according to the first embodiment of the present disclosure;

FIG. 8 illustrates a working sequence diagram of a shift register unit according to the first embodiment of the present disclosure during a forward scanning stage;

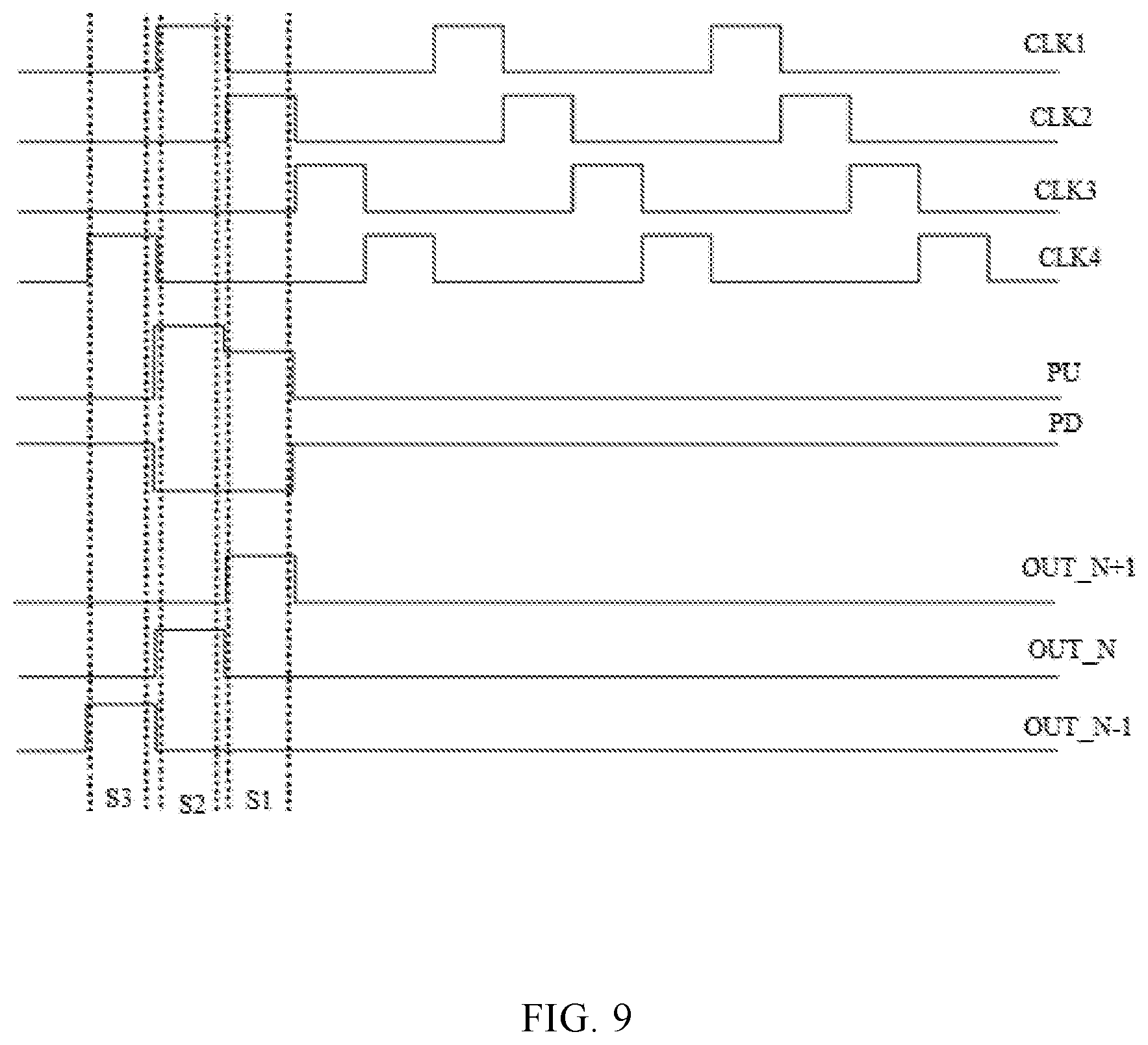

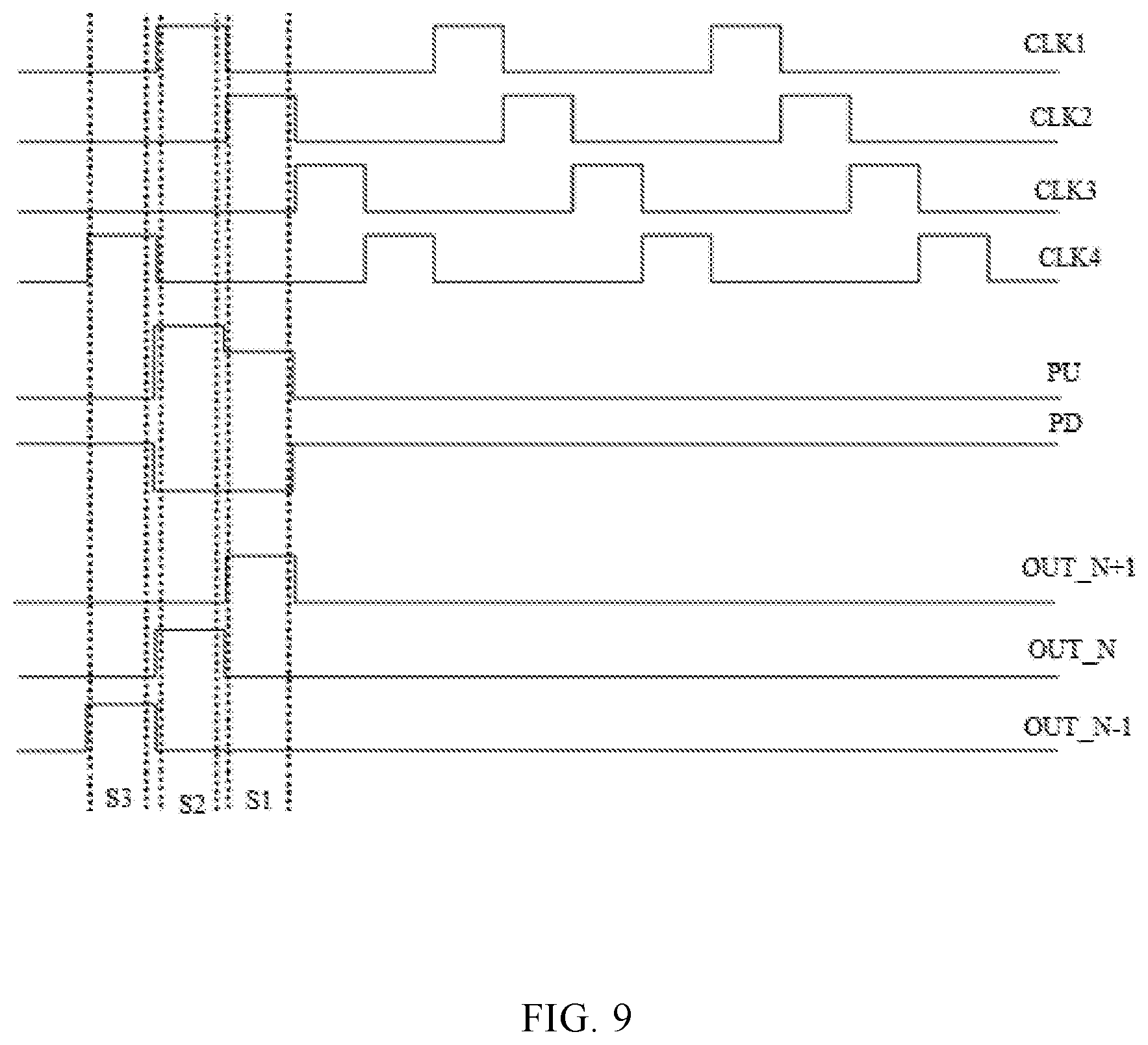

FIG. 9 illustrates a working sequence diagram of a shift register unit according to the first embodiment of the present disclosure during reverse scanning stage;

FIG. 10 illustrates a circuit diagram of a shift register unit according to the second embodiment of the present disclosure;

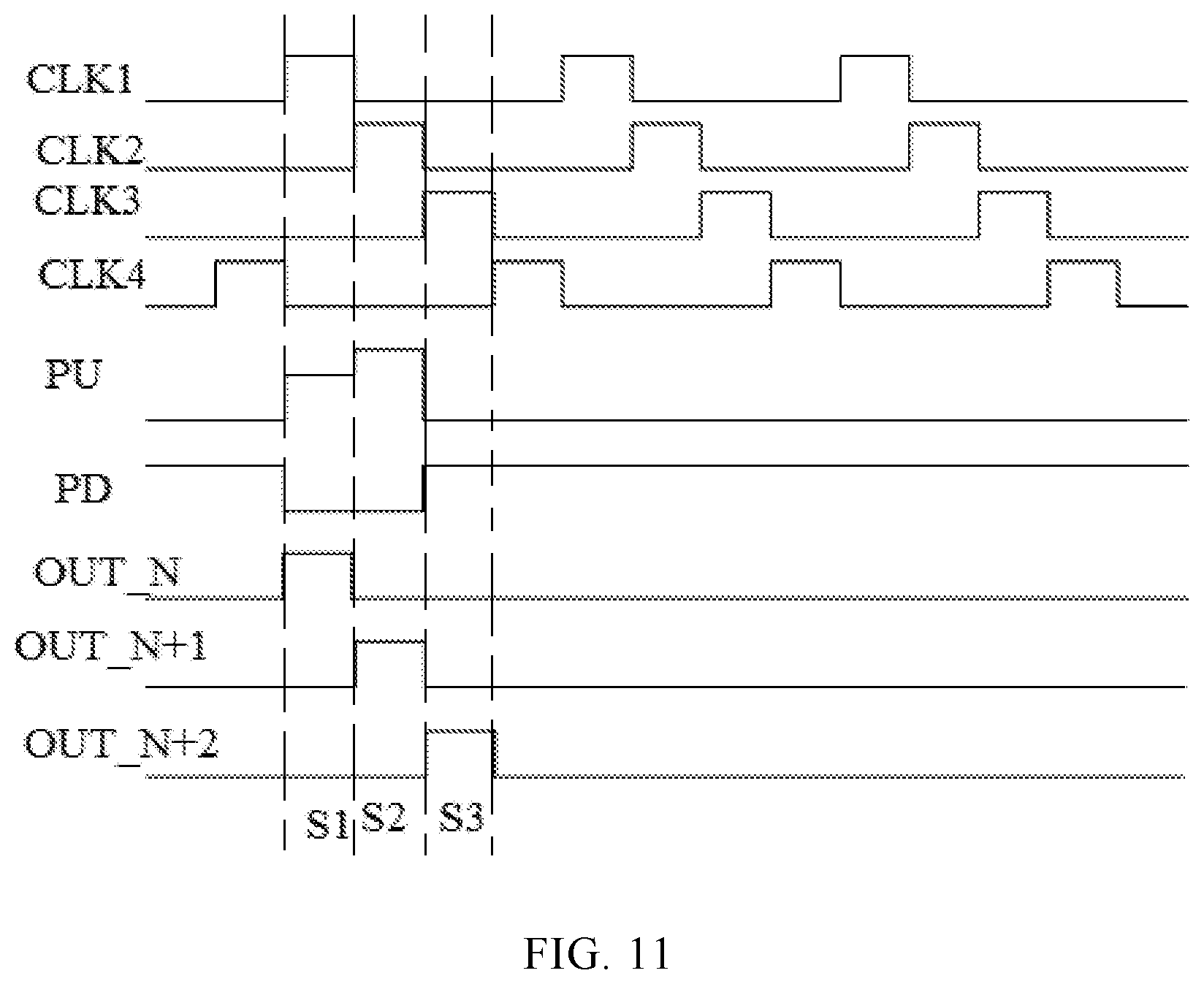

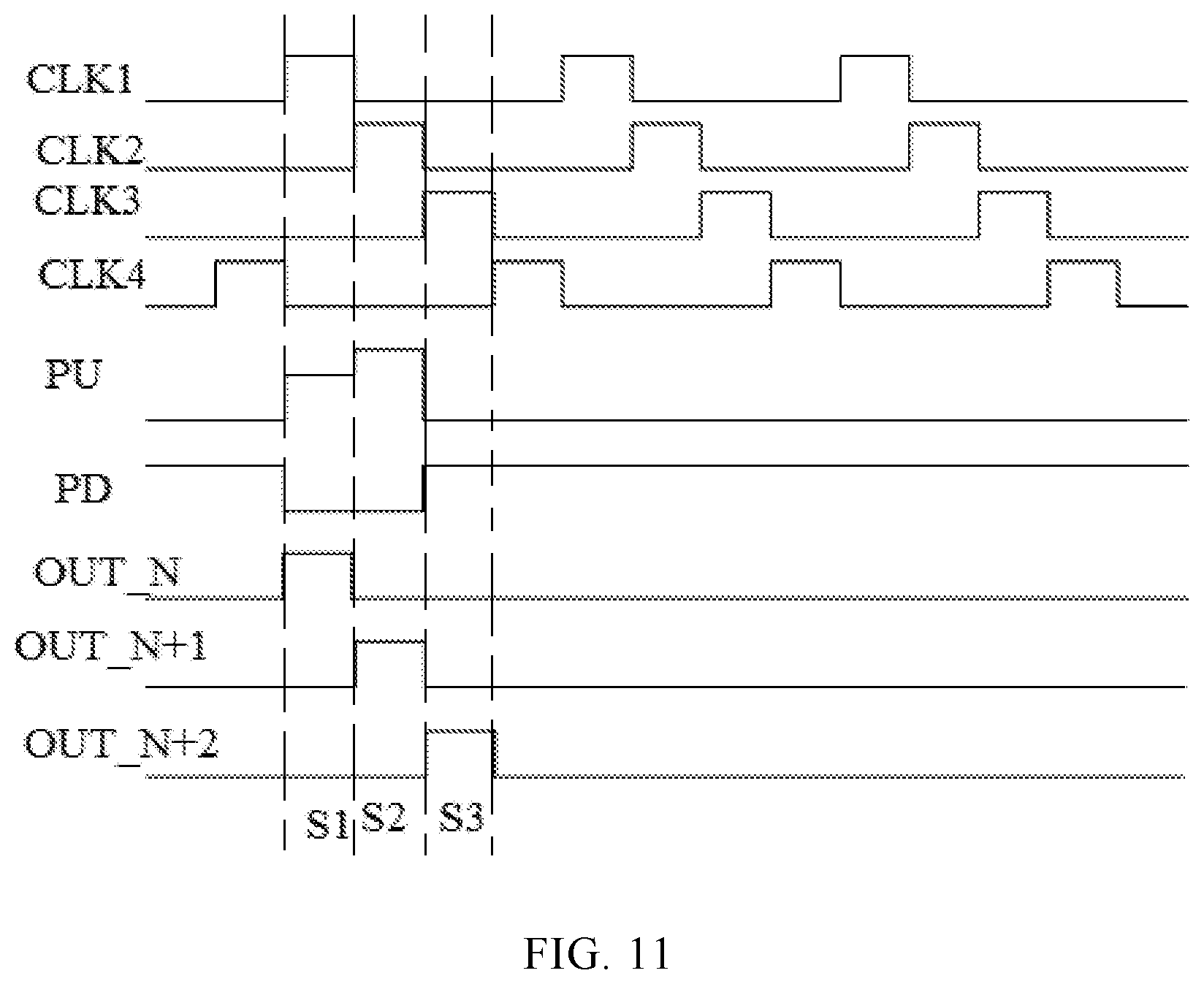

FIG. 11 illustrates a working sequence diagram of a shift register unit according to the second embodiment of the present disclosure during forward scanning stage;

FIG. 12 illustrates a working sequence diagram of a shift register unit according to the second embodiment of the present disclosure during reverse scanning stage;

FIG. 13 illustrates a circuit diagram of a shift register unit according to the third embodiment of the present disclosure;

FIG. 14 illustrates a working sequence diagram of a shift register unit according to the third embodiment of the present disclosure during forward scanning stage;

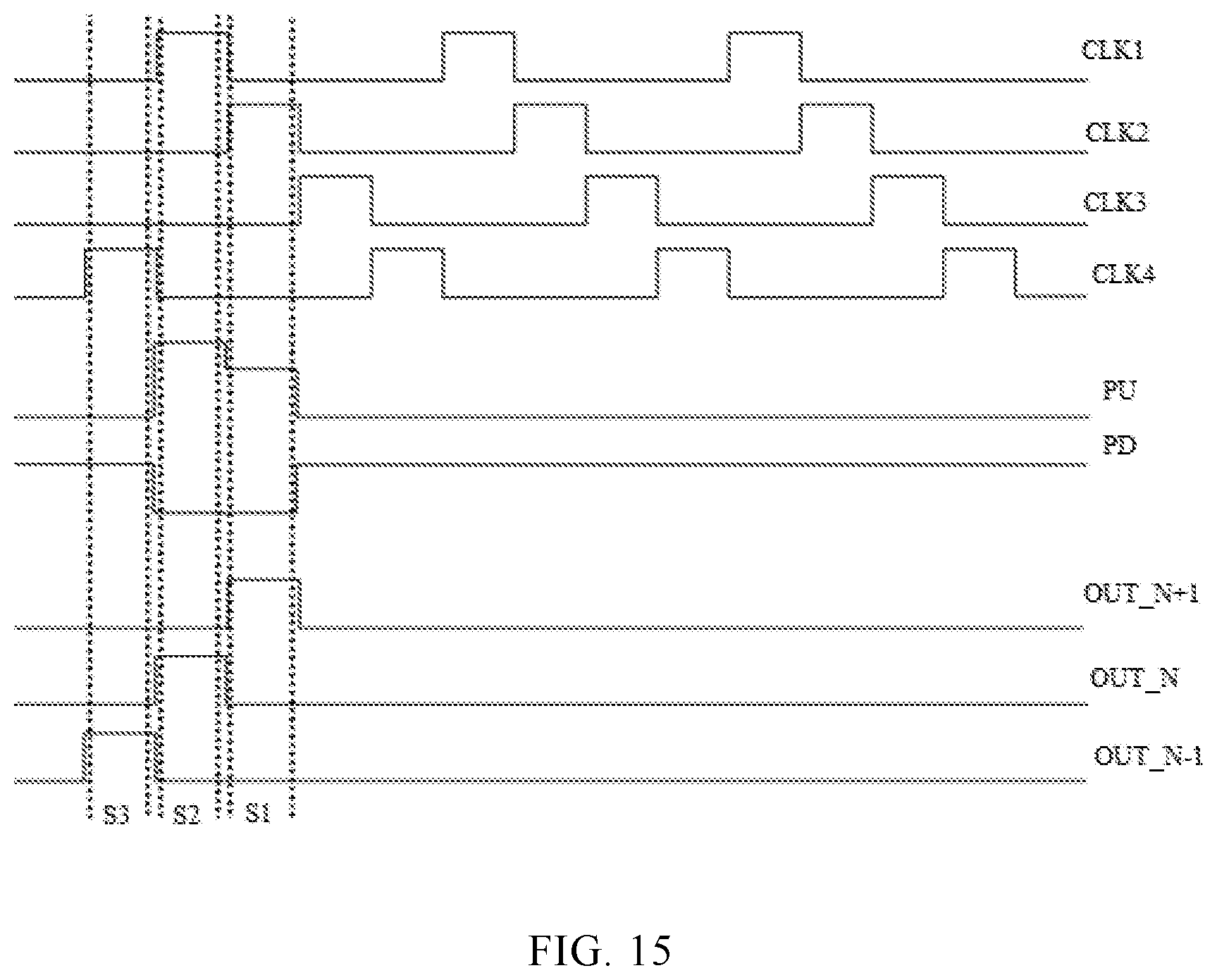

FIG. 15 illustrates a working sequence diagram of a shift register unit according to the third embodiment of the present disclosure during reverse scanning stage;

FIG. 16 illustrates a circuit diagram of a shift register unit according to the fourth embodiment of the present disclosure;

FIG. 17 illustrates a working sequence diagram of a shift register unit according to the fourth embodiment of the present disclosure during forward scanning stage;

FIG. 18 illustrates a working sequence diagram of a shift register unit according to the fourth embodiment of the present disclosure during reverse scanning stage;

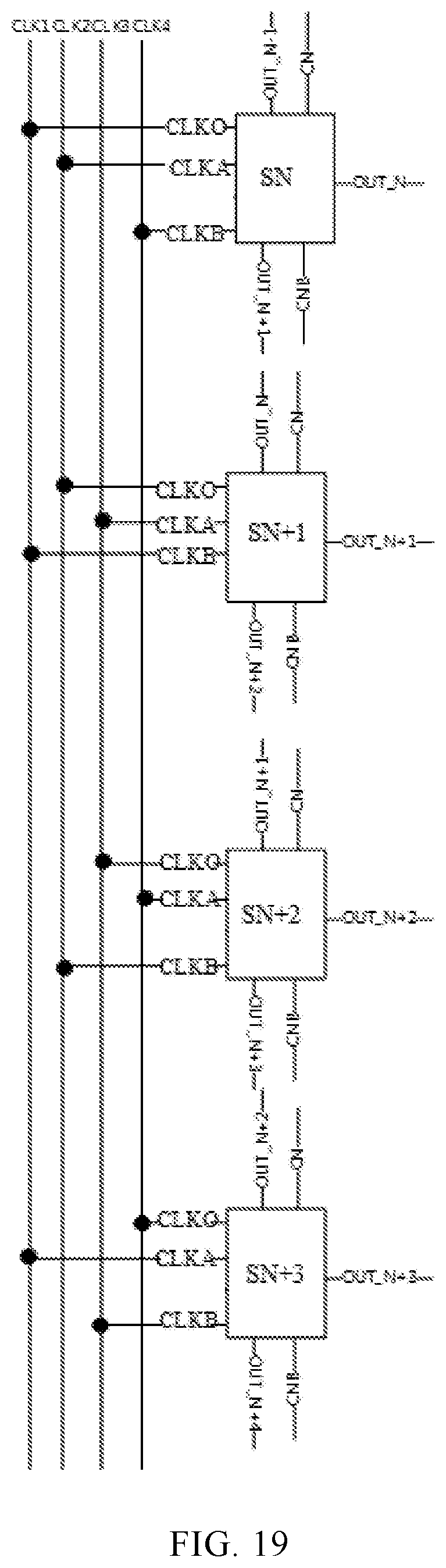

FIG. 19 illustrates a structural diagram of a gate electrode driving circuit including four levels of shift register units according to some embodiments of the present disclosure;

FIG. 20A illustrates a perspective view of an exemplary mobile phone having a display apparatus according to embodiments of the present disclosure which can include the abovementioned gate electrode driving circuits and shift register units;

FIG. 20B illustrate a perspective view of an exemplary tablet computer having a display apparatus according to embodiments of the present disclosure which can include the abovementioned gate electrode driving circuits and shift register units; and

FIG. 20C illustrates a perspective view of an exemplary laptop computer having a display apparatus according to embodiments of the present disclosure which can include the abovementioned gate electrode driving circuits and shift register units.

DETAILED DESCRIPTION

The embodiments set forth below represent the necessary information to enable those skilled in the art to practice the embodiments and illustrate the best mode of practicing the embodiments. Upon reading the following description in light of the accompanying drawing figures, those skilled in the art will understand the concepts of the disclosure and will recognize applications of these concepts not particularly addressed herein. It should be understood that these concepts and applications fall within the scope of the disclosure and the accompanying claims.

It will be understood that, although the terms first, second, etc. can be used herein to describe various elements, these elements should not be limited by these terms. These terms are only used to distinguish one element from another. For example, a first element could be termed a second element, and, similarly, a second element could be termed a first element, without departing from the scope of to the present disclosure. As used herein, the term "and/or" includes any and all combinations of one or more of the associated listed items.

It will be understood that when an element such as a layer, region, or other structure can be referred to as being "on" or extending "onto" another element, it can be directly on or extend directly onto the other element or intervening elements can also be present. In contrast, when an element is referred to as being "directly on" or extending "directly onto" another element, there are no intervening elements present.

Likewise, it will be understood that when an element such as a layer, region, or substrate can be referred to as being "over" or extending "over" another element, it can be directly over or extend directly over the other element or intervening elements can also be present. In contrast, when an element is referred to as being "directly over" or extending "directly over" another element, there are no intervening elements present. It will also be understood that when an element is referred to as being "connected" or "coupled" to another element, it can be directly connected or coupled to the other element or intervening elements can be present. In contrast, when an element is referred to as being "directly connected" or "directly coupled" to another element, there are no intervening elements present.

Relative terms such as "below" or "above" or "upper" or "lower" or "horizontal" or "horizontal" can be used herein to describe a relationship of one element, layer, or region to another element, layer, or region as illustrated in the Figures. It will be understood that these terms and those discussed above are intended to encompass different orientations of the device in addition to the orientation depicted in the Figures.

The terminology used herein is for the purpose of describing particular embodiments only and is not intended to be limiting of the disclosure. As used herein, the singular forms "a," "an," and "the" are intended to include the plural forms as well, unless the context clearly indicates otherwise. It will be further understood that the terms "comprises," "comprising," "includes," and/or "including" when used herein specify the presence of stated features, integers, steps, operations, elements, and/or components, but do not preclude the presence or addition of one or more other features, integers, steps, operations, elements, components, and/or groups thereof.

Unless otherwise defined, all terms (including technical and scientific terms) used herein have the same meaning as commonly understood by one of ordinary skill in the art to which this disclosure belongs. It will be further understood that terms used herein should be interpreted as having a meaning that is consistent with their meaning in the context of this specification and the relevant art and will not be interpreted in an idealized or overly formal sense unless expressly so defined herein.

Various embodiments of the present disclosure provide a shift register unit, a gate electrode driving circuit and a display apparatus. The shift register unit can include an output circuit and a storage circuit; the output circuit can be respectively connected to a pull-up node, a gate electrode driving signal output terminal and output voltage signal input terminal, it can be utilized to connect or disconnect the gate electrode driving signal output terminal and the output voltage signal input terminal under the control of electric potential of the pull-up node; the storage circuit can be respectively connected to the pull-up node and the gate electrode driving signal output terminal, it can be utilized to control the electric potential of the pull-up node during the gate electrode driving signal output stage, such that the output circuit can connect the gate electrode driving signal output terminal and the output voltage signal input terminal. During a gate electrode driving signal output stage, the electric potential of the pull-up node can be maintained, such that gate electrode driving signals can be outputted normally.

It should be understood, the transistors according to embodiments of the present disclosure can be thin film transistors or transverse-field transistors or other components with same characteristics. In the present disclosure, in order to distinguish the two electrodes of a transistor other than the gate electrode, one electrode can be described as the first electrode, while an alternative electrode can be described as the second electrode. In practical operations, the first electrode can be a drain electrode, the second electrode can be a source electrode; or, the first electrode can be a source electrode, the second electrode can be a drain electrode.

In a first aspect, a shift register unit can be provided, such as the shift register illustrated in FIG. 1, wherein the shift register unit according to embodiments of the present disclosure can include an output circuit 11 and a storage circuit 12.

The output circuit 11 can be respectively connected to a pull-up node PU, a gate electrode driving signal output terminal OUT, and an output voltage signal input terminal Sin. In this manner, the output circuit 11 can be utilized to connect or disconnect the gate electrode driving signal output terminal OUT, and the output voltage signal input terminal SIn under the control of the electric potential of the pull-up node PU.

The storage circuit 12 can be respectively connected to the pull-up node PU and the gate electrode driving signal output terminal OUT. In this manner the storage circuit 12 can be utilized to control the electric potential of the pull-up node PU during a gate electrode driving signal output stage, such that the output circuit 11 can connect the gate electrode driving signal output terminal OUT and the output voltage signal input terminal SIn.

According to embodiments of the present disclosure, the second terminal of the storage circuit 12 can be provided to be connected to the gate electrode driving signal output terminal OUT, such that the electric potential of the pull-up node PU can be maintained during a gate electrode driving signal output stage, such that a gate electrode driving signal can be outputted normally.

According to embodiments of the present disclosure, one terminal of the storage circuit 12 can be electrically connected to the pull-up node PU, while the other terminal of the storage circuit 12 can be electrically connected to the gate electrode driving signal output terminal OUT. In practical operations, the storage circuit 12 can include a first storage capacitor, and when the gate electrode driving signal output terminal OUT outputs high electric potential, because of the bootstrap function of the first storage capacitor during the gate electrode driving signal output stage, the electric potential of the pull-up node PU can be increased continuously.

In this manner, the source-gate voltage of the output transistor included in the output circuit can become larger, such that the output transistor can be turned on, and the output transistor will not be mistakenly turned off because of the gradual increase of the voltage of the gate electrode driving signal output terminal OUT. Ultimately, this results in increased maintained stability of the gate electrode driving output voltage.

In some embodiments, the output voltage signal input terminal SIn can be an output clock signal input terminal, however, this arrangement is made by way of example only, and those having skill in the art will recognize alternative applications, components, and arrangements and as such no limitations are intended thereby.

As illustrated in FIG. 2, the storage circuit 12 can include a first storage capacitor C1, wherein the first terminal of the first storage capacitor C1 can be connected to the pull-up node PU, and the second terminal of the first storage capacitor C1 can be connected to the gate electrode driving signal output terminal OUT.

In some embodiments, the shift register unit according to embodiments of the present disclosure can further include a pull-down node reset circuit, wherein the shift register can be respectively connected to the pull-down node, the gate electrode driving signal output terminal, and the pull-down reset voltage input terminal. In this manner, the shift register unit can be utilized to connect or disconnect the pull-down node and the pull-down reset voltage input terminal under the control of the gate electrode driving signal output terminal.

As illustrated in FIG. 3, on the basis of the embodiment of the shift register unit as illustrated in FIG. 1, the shift register unit according to embodiments of the present disclosure can further include a pull-down node reset circuit 13, wherein the shift register unit can be respectively connected to the pull-down node PD, the gate electrode driving signal output terminal OUT, and the pull-down reset voltage input terminal ReIn.

In this manner, the shift register unit can be utilized to connect or disconnect the pull-down node PD and the pull-down reset voltage input terminal ReIn under the control of the gate electrode driving signal output terminal OUT.

The pull-down node reset circuit 13 can then be utilized so as to ensure the voltage of the pull-down node PD and can be a dead voltage during the gate electrode driving signal output stage, such that the corresponding output reset transistor can be turned off, the outputting of gate electrode driving signal will not be influenced.

A dead voltage refers to a voltage than can turn off a transistor which gate electrode can be connected to the voltage source.

In some embodiments, the pull-down reset voltage terminal ReIn to can be a low voltage terminal, however, this arrangement is made by way of example only, and those having skill in the art will recognize alternative applications, components, and arrangements and as such no limitations are intended thereby.

In some embodiments, the pull-down node reset circuit can include a pull-down node reset transistor.

The gate electrode of the pull-down node reset transistor can be connected to the gate electrode driving signal output terminal, the first electrode of the pull-down node reset transistor can be connected to the pull-down node, the second electrode of the pull-down node reset transistor can be connected to the pull-down reset voltage input terminal.

As illustrated in FIG. 4, on the basis of the shift register unit illustrated in FIG. 3, the pull-down node reset circuit 13 can include a pull-down node reset transistor T10. In such an embodiment, the gate electrode of the pull-down node reset transistor T10 can be connected to the gate electrode driving signal output terminal OUT, wherein the drain electrode of the pull-down node reset transistor T10 can be connected to the pull-down node PD, and wherein the source electrode of the pull-down node reset transistor T10 can be connected to the low voltage terminal. In this manner, the low voltage terminal can be utilized to input a low voltage VGL.

In the embodiments illustrated in FIG. 4, T10 can be provided as an n-type transistor, however, this arrangement is made by way of example only, and those having skill in the art will recognize alternative applications, components, and arrangements and as such no limitations are intended thereby.

In the embodiments illustrated in FIG. 4, the pull-down reset voltage input terminal can be provided as a low voltage terminal, however, this arrangement is made by way of example only, and those having skill in the art will recognize alternative applications, components, and arrangements.

During the working process of the shift register unit according to embodiments of the present disclosure as illustrated in FIG. 4, during the gate electrode driving signal output stage, the gate electrode driving signal output terminal OUT can output high electric potential. In this manner, the pull-down node reset transistor T10 can turned on and the pull-down node PD can be connected to the low voltage VGL, such that the output reset transistor which the gate electrode is connected to PD can be turned off. As a result, the output of the gate electrode driving signal can be maintained or otherwise not be influenced.

In some embodiments, the output circuit can include an output transistor, wherein the gate electrode of the output transistor can be connected to the pull-up node. The first electrode of the output transistor can then be connected to the output voltage signal input terminal, wherein the second electrode of the output transistor can be connected to the gate electrode driving signal output terminal.

In some embodiments, the output voltage signal input terminal can be an output clock signal input terminal, however, as discussed above, this arrangement is made by way of example only, and those having skill in the art will recognize alternative applications, components, and arrangements and as such no limitations are intended thereby.

In some embodiments, the shift register unit can further include an output reset circuit, a pull-up node control circuit and a pull-down node control circuit, wherein the output reset circuit can be respectively connected to the pull-down node, the gate electrode driving signal output terminal and the first voltage input terminal. The output reset circuit can then be utilized to connect or disconnect the gate electrode driving signal output terminal and the first voltage input terminal under the control of electric potential of the pull-down node.

In some additional embodiments, the pull-up node control circuit can be connected to the pull-up node, wherein the pull-up node control can be utilized to control the electric potential of the pull-up node. In such embodiments, the pull-down node control circuit can be connected to the pull-down node, such that the pull-down node control circuit can be utilized to control the electric potential of the pull-down node.

In some embodiments, the pull-up node control circuit can further be respectively connected to the pull-down node, the adjacent upper level gate electrode driving signal output terminal, the adjacent lower level gate electrode driving signal output terminal, the forward scan control terminal, and the reverse scan control terminal. In such embodiments, the pull-up node control circuit can then be utilized to connect or disconnect the pull-up node and the first voltage input terminal under the control of the pull-down node, connect or disconnect the forward scan control terminal and the pull-up node under the control of the adjacent upper level gate electrode driving signal output terminal, and connect or disconnect the reverse scan control terminal and the pull-up node under the control of the adjacent lower level gate electrode driving signal output terminal.

A gate electrode driving circuit including the shift register units according to embodiments of the present disclosure can be configured so as to conduct forward scanning and reverse scanning under the control of the forward scan control terminal and the reverse scan control terminal.

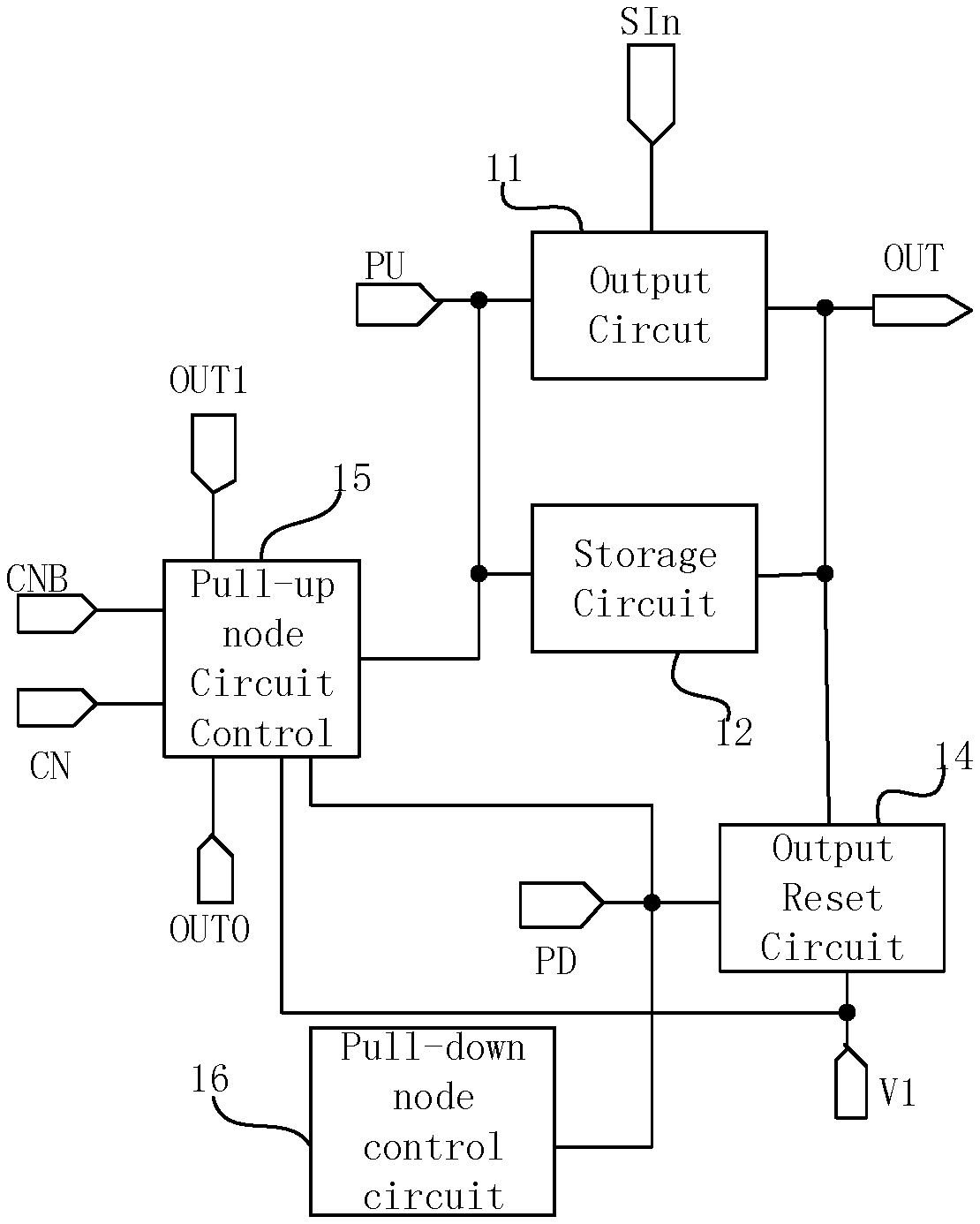

As illustrated in FIG. 5, on the basis of the embodiment of the shift register unit illustrated in FIG. 1, the shift register unit according to embodiments of the present disclosure can further include a reset circuit 14, a pull-up node control circuit 15, and a pull-down node control circuit 16.

In such embodiments, the output reset circuit 14 can be respectively connected to the pull-down node PD, the gate electrode driving signal output terminal OUT, and the first voltage input terminal V1. The output reset circuit 14 can then be utilized to connect or disconnect the gate electrode driving signal output terminal OUT and the first voltage input terminal V1 under the control of electric potential of the pull-down node PD.

In some such embodiments, the pull-up node control circuit 15 can be respectively connected to the pull-down node PD, the first voltage input terminal V1, the adjacent upper level gate electrode driving signal output terminal OUT0, the adjacent lower level gate electrode driving signal output terminal OUT1, the forward scan control terminal CN, and the reverse scan control terminal CNB. The pull-up node control circuit 15 can then be utilized to connect or disconnect the pull-up node PU and the first voltage input terminal V1 under the control of the pull-down node PD, connect or disconnect the forward scan control terminal CN and the pull-up node PU under the control of the adjacent upper level gate electrode driving signal output terminal OUT0, and connect or disconnect the reverse scan control terminal CNB and the pull-up node PU under the control of the adjacent lower level gate electrode driving signal output terminal OUT1;

In some embodiments, the pull-down node control circuit 16 can be connected to the pull-down node PD, wherein the pull-down node control circuit 16 can be utilized to control the electric potential of the pull-down node PD.

In some embodiments, the first voltage input terminal V1 can be a low voltage terminal, however, this arrangement is made by way of example only, and those having skill in the art will recognize alternative applications, components, and arrangements and as such no limitations are intended thereby.

During the working process of the shift register unit according to embodiments of the present disclosure, during forward scanning stage, CN can output a high electric potential, wherein CNB can output low electric potential, when OUT0 outputs high electric potential, the pull-up node control circuit 15 can control the pull-up node PU and the forward scan control terminal CN to be connected to each other, such that the electric potential of PU can be pulled up. Further, during reverse scanning stage, CN can output a low electric potential, wherein CNB can output high electric potential, when OUT1 outputs high electric potential, the pull-up node control circuit 15 can control the pull-up node PU and the reverse scan control terminal CNB to be connected to each other, such that the electric potential of PU can be pulled up.

In some embodiments, the pull-up node control circuit can include a first pull-up control transistor, a second pull-up control transistor, and a third pull-up control transistor.

In some such embodiments, the gate electrode of the first pull-up control transistor can be connected to the upper level gate electrode driving signal output terminal, the first electrode of the first pull-up control transistor can be connected to the pull-up node, and the second electrode of the first pull-up control transistor can be connected to the forward scan control terminal.

Further, the gate electrode of the second pull-up control transistor can be connected to the lower level gate electrode driving signal output terminal, the first electrode of the second pull-up control transistor can be connected to the reverse scan control terminal, and the second electrode of the second pull-up control transistor can be connected to the pull-up node. Additionally, the gate electrode of the third pull-up control transistor can be connected to the pull-down node, the first electrode of the third pull-up control transistor can be connected to the pull-up node, and the second electrode of the third pull-up control transistor can be connected to the first voltage input terminal.

In practical operations, the pull-down node control circuit can be connected to the pull-up node, the forward scan control terminal, the forward scan clock signal input terminal, the reverse scan control terminal, the reverse scan clock signal input terminal, the first voltage input terminal, and the second voltage input terminal.

In such embodiments, the pull-down node control circuit can be utilized to connect or disconnect the forward scan clock signal input terminal and the pull-down control node under the control of the forward scan control terminal, connect or disconnect the reverse scan clock signal input terminal and the pull-down control node under the control of the reverse scan control terminal, connect or disconnect the pull-down node and the second voltage input terminal under the control of the electric potential of the pull-down control node, and connect or disconnect the pull-down node and the first voltage input terminal under the control of the pull-up node.

As illustrated in FIG. 6, on the basis of the shift register unit according to embodiments of the present disclosure as illustrated in FIG. 5, the pull-down node control circuit 16 can further be connected to the pull-up node PU, the forward scan control terminal CN, the forward scan clock signal input terminal CLKA, the reverse scan control terminal CNB, the reverse scan clock signal input terminal CLKB, the first voltage input terminal V1, and the second voltage input terminal V2.

In this manner, the shift register unit can be utilized to connect or disconnect the forward scan clock signal input terminal CLKA and the pull-down control node PDCN under the control of the forward scan control terminal CN, connect or disconnect the reverse scan clock signal input terminal CLKB and the pull-down control node PDCN under the control of the reverse scan control terminal CNB, connect or disconnect the pull-down node PD and the second voltage input terminal V2 under the control of the electric potential of the pull-down control node PDCN, and connect or disconnect the pull-down node PD and the first voltage input terminal V1 under the control of the pull-up node PU.

In some embodiments, the first voltage input terminal V1 can be a low voltage terminal, the second voltage terminal V2 can be a high voltage terminal, however, this arrangement is made by way of example only, and those having skill in the art will recognize alternative applications, components, and arrangements and as such no limitations are intended thereby.

During the working process of the shift register unit, according to embodiments of the present disclosure as illustrated in FIG. 6, during the forward scanning stage, CN can output high electric potential, CNB can output low electric potential, then under the control of CN, the pull-down node control circuit 16 can control the PDCN and CLKA to be connected to each other.

When CLKA inputs high electric potential, under the control of the PDCN, the pull-down node control circuit 16 can control the pull-down node PD and the second voltage input terminal V2 to be connected to each other. During the reverse scanning stage, CN can output low electric potential, CNB can output high electric potential, under the control of CNB, the pull-down node control circuit 16 can control the PDCN and CLKB to be connected to each other, when CLKB inputs high electric potential, then under the control of PDCN, the pull-down node control circuit 16 can control the pull-down node PD and the second voltage input terminal V2 to be connected to each other.

In some embodiments, the pull-down node control circuit can include a first pull-down control transistor, a second pull-down control transistor, a third pull-down control transistor, and a fourth pull-down control transistor.

In such embodiments, the gate electrode of the first pull-down control transistor can be connected to the forward scan control terminal, wherein the first electrode of the first pull-down control transistor can be connected to the forward scan clock signal input terminal, and wherein the second electrode of the first pull-down control transistor can be connected to the pull-down control node. Further, the gate electrode of the second pull-down control transistor can be connected to the reverse scan control terminal, the first electrode of the second pull-down control transistor can be connected to the reverse scan clock signal input terminal, and the second electrode of the second pull-down control transistor can be connected to the pull-down control nod.

Additionally, the gate electrode of the third pull-down control transistor can be connected to the pull-down control node, the first electrode of the third pull-down control transistor can be connected to the pull-down node, and the second electrode of the third pull-down control transistor can be connected to the second voltage input terminal.

Finally, the gate electrode of the fourth pull-down control transistor can be connected to the pull-up node, the first electrode of the fourth pull-down control transistor can be connected to the first voltage input terminal, and the second electrode of the fourth pull-down control transistor can be connected to the pull-down node.

In some embodiments, the output reset circuit can include: an output reset transistor having a gate electrode which can be connected to the pull-down node, wherein a first electrode of the output reset transistor can be connected to the gate electrode driving signal output terminal, and wherein a second electrode of the output reset transistor can be connected to the first voltage input terminal; a second storage capacitor, wherein a first terminal of the second storage capacitor can be connected to the pull-down node, and wherein a second terminal of the second storage capacitor can be connected to the first voltage input terminal.

In the following, the shift register unit according to embodiments of the present disclosure will be described through specific embodiments.

As illustrated in FIG. 7, in the first embodiment of the shift register unit of the present disclosure, the shift register unit can include an output circuit, a storage circuit, an output reset circuit, a pull-up node control circuit and a pull-down node control circuit.

In some such embodiments, the storage capacitor can include a first storage capacitor C1, wherein the first terminal of the first storage capacitor C1 can be connected to a pull-up node PU, and the second terminal of the first storage capacitor C1 can be connected to a n-level gate electrode driving signal output terminal OUT-N. Further, the pull-up node control circuit can include a first pull-up control transistor T7, a second pull-up control transistor T6, and a third pull-up control transistor T1.

Additionally, the gate electrode of the first pull-up control transistor T7 can be connected to a N-1 level gate electrode driving signal output terminal OUT-N-1, wherein the drain electrode of the first pull-up control transistor T7 can be connected to the pull-up node PU, and the source electrode of the first pull-up control transistor T7 can be connected to a forward scan control terminal CN.

As illustrated here, the gate electrode of the second pull-up control transistor T6 can be connected to a N+1 level gate electrode driving signal output terminal OUT-N+1, the drain electrode of the second pull-up control transistor T6 can be connected to a reverse scan control terminal CNB, and the source electrode of the second pull-up control transistor T6 can be connected to the pull-up node PU. Ultimately, the gate electrode of the third pull-up control transistor T1 can be connected to a pull-down node PD, the drain electrode of the third pull-up control transistor T1 can be connected to the pull-up node PU, and the second electrode of the third pull-up control transistor T1 can be connected to a low voltage terminal, wherein the low voltage terminal can be utilized to input a low voltage VGL.

In some additional embodiments, the pull-down node control circuit can include a first pull-down control transistor T5, a second pull-down control transistor T4, a third pull-down control transistor T8, and a fourth pull-down control transistor T3.

In some such embodiments, the gate electrode of the first pull-down control transistor T5 can be connected to the forward scan control terminal CN, the drain electrode of the first pull-down control transistor T5 can be connected to a second clock signal input terminal CLK2, and the source electrode of the first pull-down control transistor T5 can be connected to a pull-down control node PDCN.

Additionally, the gate electrode of the second pull-down control transistor T4 can be connected to the reverse scan control terminal CNB, the drain electrode of the second pull-down control transistor T4 can be connected to a fourth clock signal input terminal CLK4, and the source electrode of the second pull-down control transistor T4 can be connected to the pull-down control node PDCN.

Additionally, the gate electrode of the third pull-down control transistor T8 can be connected to the pull-down control node PDCN, the drain electrode of the third pull-down control transistor T8 can be connected to the pull-down node PD, and the source electrode of the third pull-down control transistor T8 can be connected to a high voltage terminal, wherein the high voltage terminal can be utilized to input a high voltage VGH.

Additionally, the gate electrode of the fourth pull-down control transistor T3 can be connected to the pull-up node PU, the drain electrode of the fourth pull-down control transistor T3 can be connected to the low voltage terminal, and the source electrode of the fourth pull-down control transistor T3 can be connected to the pull-down node PD.

In some additional embodiments, the output reset circuit can include an output reset transistor T2 and a second storage capacitor C2.

In some such embodiments, the gate electrode of the output reset transistor T2 can be connected to the pull-down node PD, the drain electrode of the output reset transistor T2 can be connected to the N-level gate electrode driving signal output terminal OUT-N, and the source electrode of the output reset transistor T2 can be connected to the low voltage terminal.

Additionally, the first terminal of the second storage capacitor C2 can be connected to the pull-down node PD, and the second terminal of the second storage capacitor C2 can be connected to the low voltage terminal.

In some embodiments, the output circuit can include an output transistor T9;

In some such embodiments, the gate electrode of the output transistor T9 can be connected to the pull-up node PU, the drain electrode of the output transistor T9 can be connected to the first clock signal input terminal CLK1, and the source electrode of the output transistor T9 can be connected to the N-level gate electrode driving signal output terminal OUT-N.

In the first embodiment of the shift register unit of the present disclosure illustrated in FIG. 7, all transistors can be n-type transistors, however, this arrangement is made by way of example only, and those having skill in the art will recognize alternative applications, components, and arrangements and as such no limitations are intended thereby.

In one embodiment of the shift register unit as contemplated by the inventive concepts of the present disclosure, the input clock signal input terminal can be the first clock signal input terminal CLK1, the forward scan clock signal input terminal can be the second clock signal input terminal CLK2, the reverse scan clock signal input terminal can be the fourth clock signal input terminal CLK4, the first voltage input terminal can be the low voltage terminal, and the second voltage terminal can be the high voltage terminal.

As illustrated in FIG. 8, CLK3 refers to the third clock signal input terminal.

In some such embodiments CLK1 can be utilized to input a first clock signal, CLK2 can be utilized to input a second clock signal, CLK3 can be utilized to input a third clock signal, and CLK4 can be utilized to input a fourth clock signal.

As illustrated in FIG. 8, the period of the first clock signal, the period of the second clock signal, the period of the third clock signal and the period of the fourth clock signal can be equal, wherein the period is T;

In some embodiments, the duty ratio of the first clock signal, the duty ratio of the second clock signal, the duty ratio of the third clock signal and the duty ratio of the fourth clock signal can all be 1/4 T. In other words, the second clock signal can be delayed by T/4 compared with the first clock signal, the third clock signal can be delayed by T/4 compared with the second clock signal, the fourth clock signal can be delayed by T/4 compared with the third clock signal.

The shift register unit of the first embodiment of the present FIG. 7 can be a N-level Gate on Array (GOA) unit, wherein, N is a positive integer.

FIG. 8 then illustrates an exemplary time sequence diagram of the first embodiment of the shift register unit of the present disclosure during forward scanning stage. During forward scanning stage, CN can output high electric potential, CNB can output low electric potential.

As illustrated in FIG. 8, in the first embodiment of the shift register unit, is illustrated as operating in a forward scanning stage.

In this exemplary operation, during the input stage S1, CN can output high electric potential, OUT-N-1 can output high electric potential, T7 can be turned on, the electric potential of PU can be pulled up, C1 can be charged, T3 can be turned on, the electric potential of PD can be pulled down, T9 can be turned on, and at this time, CLK1 can input low electric potential, OUT_N can output a low electric potential;

During the gate electrode driving signal output stage S2, because of the bootstrap function of C1, the electric potential of PU can be increased continuously. In such a situation, T9 can still be turned on, CLK1 can input a high electric potential, and OUT_N can output a high electric potential.

During an exemplary reset stage S3, CLK2 can input high electric potential, T8 can be turned on, the electric potential of PD can be pulled up, T1 and T2 can both be turned on, such that the electric potential of PU can be pulled down and OUT_N can be controlled to output a low electric potential to charge C2.

During each other stage of the same frame after the reset stage, because the hold function of C2 and the influence of high electric potential inputted by CLK2, the electric potential of PD can be always at a high level, the electric potential of PU and the gate electrode driving signal outputted by OUT_N can be always in a pulled-down state, which, as a result, can effectively prevent noise.

FIG. 9 illustrates a time sequence diagram of the shift register unit of the first embodiment of the present disclosure during reverse scanning stage. During reverse scanning stage, CN can output low electric potential, and CNB can output a high electric potential.

As illustrated in FIG. 9, CLK3 refers to a third clock signal input terminal, CLK1 can be utilized to input a first clock signal, CLK2 can be utilized to input a second clock signal, CLK3 can be utilized to input a third clock signal, and CLK4 can be utilized to input a fourth clock signal.

As illustrated in FIG. 9, the period of the first clock signal, the period of the second clock signal, the period of the third clock signal and the period of the fourth clock signal are equal, each having a period of T;

The duty ratio of the first clock signal, the duty ratio of the second clock signal, the duty ratio of the third clock signal and the duty ratio of the fourth clock signal can then all be 1/4T.

In such an embodiment, the second clock signal can be delayed by T/4 compared with the first clock signal, the third clock signal can be delayed by T/4 compared with the second clock signal, and the fourth clock signal can be delayed by T/4 compared with the third clock signal.

As illustrated in FIG. 9, in the shift register unit is operating during reverse scanning stage according to the first embodiments of the present disclosure.

In such a situation, during the input statgeS1, OUT-N+1 can output a high electric potential, wherein T6 can be turned on. As such, the electric potential of PU can be pulled up to charge C1, wherein T3 can be turned on, and the electric potential of PD can be pulled down. Additionally, T9 can be turned on, and at this time CLK2 can input a low electric potential, wherein OUT_N can output a low electric potential.

In such a situation, during the gate electrode driving signal output state S2, because of the bootstrap function of C1, the electric potential of PU can be increased continuously, T9 can still be turned on, CLK1 can input a high electric potential, and OUT_N can output a high electric potential.

In such a situation, during the reset stage S3, CLK4 can input high electric potential, T8 can be turned on, such that the electric potential PD can be pulled up, T1 and T2 can both be turned on, the electric potential of PU can be pulled down, OUT_N can output a low electric potential to charge C2.

In such a situation, during each stage of the same frame after the reset stage S3, because of the bootstrap function of C2 and the influence of high electric potential inputted by CLK4, the electric potential of PD can be always at high level, the electric potential of PU and the gate electrode driving signal outputted by OUT-N can always be in a pulled-down state, as a result, noise can be effectively prevented.

As illustrated in FIG. 10, the shift register unit of the second embodiment of the present disclosure can also include an output circuit, a storage circuit, an output reset circuit, a pull-up node control circuit, and a pull-down node control circuit;

As illustrated here, the storage circuit can include a first storage capacitor C1, wherein the first terminal of the first storage capacitor C1 can be connected to the pull-up node PU, and the second terminal of the first storage capacitor C1 can be connected to the N+1 level gate electrode driving output terminal OUT_N+1;

In some such embodiments, the pull-up node control circuit can include a first pull-up control transistor T7, a second pull-up control transistor T6, and a third pull-up control transistor T1.

In this embodiment, the gate electrode of the first pull-up control transistor T7 can be connected to the N-level gate electrode driving signal output terminal OUT_N, the drain electrode of the first pull-up control transistor T7 can be connected to the pull-up node PU, and the source electrode of the first pull-up control transistor T7 can be connected to the forward scan control terminal CN.

Further, The gate electrode of the second pull-up control transistor T6 can be connected to the N+2-level gate electrode driving signal output terminal OUT_N+2, the drain electrode of the second pull-up control transistor T6 can be connected to the reverse scan control terminal CNB, and the source electrode of the first pull-up control transistor T6 can be connected to the pull-up node PU.

Additionally, the gate electrode of the third pull-up control transistor T1 can be connected to the pull-down node PD, the drain electrode of the third pull-up control transistor T1 can be connected to the pull-up node PU, and the second electrode of the third pull-up control transistor T1 can be connected to the low voltage terminal, wherein the low voltage terminal can be utilized to input a low voltage VGL.

In some embodiments, as illustrated here, the pull-down node control circuit can include a first pull-down control transistor T5, a second pull-down control transistor T4, a third pull-down control transistor T8, and a fourth pull-down control transistor T3;

In this embodiment, the gate electrode of the first pull-down control transistor T5 can be connected to the forward scan control terminal CN, the drain electrode of the first pull-down control transistor T5 can be connected to the third clock signal input terminal CLK3, and the source electrode of the first pull-down control transistor T5 can be connected to the pull-down control node PDCN.

Additionally, the gate electrode of the second pull-down control transistor T4 can be connected to the reverse scan control terminal CNB, the drain electrode of the second pull-down control transistor T4 can be connected to the first clock signal input terminal CLK1, and the source electrode of the second pull-down control transistor T4 can be connected to the pull-down control node PDCN.

Further, the gate electrode of the third pull-down control transistor T8 can be connected to the pull-down control node PDCN, the drain electrode of the third pull-down control transistor T8 can be connected to the pull-down node PD, and the source electrode of the third pull-down control transistor T8 can be connected to the high voltage terminal, wherein the high voltage terminal can be utilized to input a high voltage VGH;

In some such embodiments, the gate electrode of the fourth pull-down control transistor T3 can be connected to the pull-up node PU, the drain electrode of the fourth pull-down control transistor T3 can be connected to the low voltage terminal, and the source electrode of the fourth pull-down control transistor T3 can be connected to the pull-down node PD.

As illustrated, the output reset circuit can include an output reset transistor T2 and a second storage capacitor C2.

In this embodiment, the gate electrode of the output reset transistor T2 can be connected to the pull-down node PD, the drain electrode of the output reset transistor T2 can be connected to the N+1 level gate electrode signal output terminal OUT_N+1, and the source electrode of the output reset transistor T2 can be connected to the low voltage terminal;

Further, the first terminal of the second storage capacitor C2 can be connected to the pull-down node PD, and the second terminal of the second storage capacitor C2 can be connected to the low voltage terminal.

In some embodiments contemplated herein the output circuit can include an output transistor T9, wherein the gate electrode of the output transistor T9 can be connected to the pull-up node PU, the drain electrode of the output transistor T9 can be connected to the second clock signal input terminal CLK2, and the source electrode of the output transistor T9 can be connected to the N+1 level gate electrode driving signal output terminal OUT_N+1.

In the shift register unit of the second embodiment of the present disclosure as illustrated in FIG. 10, all transistors can be n-type transistors, however, this arrangement is made by way of example only, and those having skill in the art will recognize alternative applications, components, and arrangements and as such no limitations are intended thereby.