Memory device capable of reducing program disturbance and erasing method thereof

Tang , et al. May 4, 2

U.S. patent number 10,998,063 [Application Number 16/726,802] was granted by the patent office on 2021-05-04 for memory device capable of reducing program disturbance and erasing method thereof. This patent grant is currently assigned to Yangtze Memory Technologies Co., Ltd.. The grantee listed for this patent is Yangtze Memory Technologies Co., Ltd.. Invention is credited to Xiang Fu, Qiang Tang.

| United States Patent | 10,998,063 |

| Tang , et al. | May 4, 2021 |

Memory device capable of reducing program disturbance and erasing method thereof

Abstract

An erasing method is used in a memory device. The memory device includes a string of memory cells and a controller, the string of memory cells including a plurality of special memory cells not for storing data and a plurality of main memory cells for storing data. The erasing method includes: the controller verifying if at least one special memory cell of the plurality of special memory cells has failed; the controller resetting the at least one special memory cell if the at least one special memory cell has failed; and the controller erasing the plurality of main memory cells.

| Inventors: | Tang; Qiang (Wuhan, CN), Fu; Xiang (Wuhan, CN) | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Applicant: |

|

||||||||||

| Assignee: | Yangtze Memory Technologies Co.,

Ltd. (Wuhan, CN) |

||||||||||

| Family ID: | 1000004561822 | ||||||||||

| Appl. No.: | 16/726,802 | ||||||||||

| Filed: | December 24, 2019 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | Issue Date | ||

|---|---|---|---|---|---|

| PCT/CN2019/118332 | Nov 14, 2019 | ||||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | G11C 16/3436 (20130101); G11C 16/107 (20130101); G11C 16/08 (20130101); G11C 16/14 (20130101); G11C 16/28 (20130101); G11C 29/44 (20130101) |

| Current International Class: | G11C 8/00 (20060101); G11C 16/28 (20060101); G11C 16/10 (20060101); G11C 29/44 (20060101); G11C 16/08 (20060101); G11C 16/34 (20060101); G11C 16/14 (20060101) |

| Field of Search: | ;365/185.17,185.03,185.11,185.14,185.29,185.2,185.22,218,185.13,185.19,185.24 |

References Cited [Referenced By]

U.S. Patent Documents

| 2014/0369129 | December 2014 | Dutta |

| 2016/0260489 | September 2016 | Lee |

| 2017/0256320 | September 2017 | Lang |

| 2018/0068726 | March 2018 | Song |

| 2018/0308550 | October 2018 | Shiino |

| 1538459 | May 2010 | CN | |||

| 109119120 | Jan 2019 | CN | |||

| 109949835 | Jun 2019 | CN | |||

| 200509136 | Mar 2005 | TW | |||

| 200603169 | Jan 2006 | TW | |||

| 200715293 | Apr 2007 | TW | |||

| 200717526 | May 2007 | TW | |||

| 201027538 | Jul 2010 | TW | |||

Attorney, Agent or Firm: Hsu; Winston

Parent Case Text

CROSS REFERENCE TO RELATED APPLICATIONS

This is a continuation of PCT patent application No. PCT/CN2019/118332, filed on 14 Nov. 2019 and included herein by reference in its entirety.

Claims

What is claimed is:

1. A memory device comprising: a string of memory cells comprising: a plurality of special memory cells coupled in series, arranged at one end of the string of memory cells, and not for storing data; and a plurality of main memory cells for storing data and coupled in series, one of the plurality of main memory cells being coupled to one of the plurality of special memory cells; a plurality of special word lines coupled to the plurality of special memory cells, respectively; a plurality of main word lines coupled to the plurality of main memory cells, respectively; and a controller, coupled to the plurality of special word lines and the plurality of word lines, and configured to verify if at least one special memory cell of the plurality of special memory cells has failed, reset the at least one special memory cell if the at least one special memory cell has failed, and erase the plurality of main memory cells; wherein no pulse is applied to reset the at least one special memory cell and no pulse is applied to erase the plurality of main memory cells prior to verifying if the at least one special memory cell of the plurality of special memory cells has failed.

2. The memory device of claim 1, wherein the controller is configured to verify if the at least one special memory cell has failed prior to erasing the plurality of main memory cells.

3. The memory device of claim 2, wherein the controller verifies the plurality of special memory cells using a verification level, and when a threshold voltage of the at least one special memory cell is less than the verification level, the controller applies a program pulse to the at least one special memory cell.

4. The memory device of claim 2, wherein the controller verifies the plurality of special memory cells using a verification level, and when a threshold voltage of the at least one special memory cell is higher than the verification level, the controller performs a soft erasing operation on the at least one special memory cell.

5. The memory device of claim 1, wherein the controller is configured to erase the plurality of main memory cells prior to verifying if the at least one special memory cell has failed.

6. The memory device of claim 5, wherein the controller is configured to erase the plurality of special memory cells and the plurality of main memory cells, and apply a program pulse to the plurality of special memory cells if the at least one special memory cell has failed.

7. The memory device of claim 1, wherein: the plurality of special memory cells comprise: a selection transistor arranged at one end of the plurality of special memory cells; and a dummy memory cell coupled to the selection transistor; the plurality of special word lines comprise: a selection word line coupled to the selection transistor; and a dummy word line coupled to the dummy memory cell.

8. The memory device of claim 7, wherein: the at least one special memory cells comprises the selection transistor.

9. The memory device of claim 7, wherein: the at least one special memory cells comprises the dummy memory cell.

10. The memory device of claim 1, wherein the memory device is a 3-dimentional NAND flash memory device.

11. An erasing method for use in a memory device, the memory device comprising a string of memory cells and a controller, the string of memory cells comprising a plurality of special memory cells not for storing data and a plurality of main memory cells for storing data, and the erasing method comprising: the controller verifying if at least one special memory cell of the plurality of special memory cells has failed; the controller resetting the at least one special memory cell if the at least one special memory cell has failed; and the controller erasing the plurality of main memory cells; wherein no pulse is applied to reset the at least one special memory cell and no pulse is applied to erase the plurality of main memory cells prior to verifying if the at least one special memory cell of the plurality of special memory cells has failed.

12. The method of claim 11, wherein the controller verifying if the at least one special memory cell has failed prior to the controller erasing the plurality of main memory cells.

13. The method of claim 12, wherein the controller verifying if the at least one special memory cell of the plurality of special memory cells has failed comprises: the controller verifying the plurality of special memory cells using a verification level; and resetting the at least one special memory cell if the at least one special memory cell has failed comprises: when a threshold voltage of the at least one special memory cell is less than the verification level, the controller applying a program pulse to the at least one special memory cell.

14. The method of claim 12, wherein the controller verifying if the at least one special memory cell of the plurality of special memory cells has failed comprises: the controller verifying the plurality of special memory cells using a verification level; and resetting the at least one special memory cell if the at least one special memory cell has failed comprises: when a threshold voltage of the at least one special memory cell is higher than the verification level, the controller performing a soft erasing operation on the failed special memory cell.

15. The method of claim 11, wherein the controller erasing the plurality of main memory cells is performed prior to the controller verifying if the at least one special memory cell has failed.

16. The method of claim 15, wherein the controller resetting the at least one special memory cell if the at least one special memory cell has failed comprises: the controller erasing the plurality of special memory cells and the plurality of main memory cells, and applying a program pulse to the special memory cells.

17. The method of claim 11, wherein: the plurality of special memory cells comprises: a selection transistor arranged at the one end of the string of memory cells; and a dummy memory cell coupled to the selection transistor and the one of the plurality of memory cells; the plurality of special word line comprises: a selection word line coupled to the selection transistor; and a dummy word line coupled to the dummy memory cell.

18. The method of claim 17, wherein the at least one special memory cells comprises the selection transistor.

19. The method of claim 17, wherein the at least one special memory cells comprises the dummy memory cell.

20. The method of claim 11, wherein the memory device is a 3-dimentional NAND flash memory device.

Description

BACKGROUND OF THE INVENTION

1. Field of the Invention

The invention relates to memory device, and in particular, to a memory device capable of reducing program disturbance and an erasing method thereof.

2. Description of the Prior Art

As technology advances, high-density memory cells have been incorporated in semiconductor memory devices to reduce overall device sizes and increase data storage capabilities. Nevertheless, the increase in integration density may lead to an increase in coupling between memory cells and an unselected memory cell may be inadvertently programmed. The unintentional programming of the unselected memory cell is referred to as "program disturbance".

SUMMARY OF THE INVENTION

In one embodiment, a memory device includes a string of memory cells, a plurality of special word lines, a plurality of main word lines and a controller. The string of memory cells includes a plurality of special memory cells and a plurality of main memory cells. The plurality of special memory cells are coupled in series, arranged at one end of the string of memory cells, and not for storing data. The plurality of main memory cells are for storing data and coupled in series. One of the plurality of main memory cells is coupled to one of the plurality of special memory cells. The plurality of special word lines are coupled to the plurality of special memory cells, respectively. The plurality of main word lines are coupled to the plurality of main memory cells, respectively. The controller is coupled to the plurality of special word lines and the plurality of word lines, and used to verify if at least one special memory cell of the plurality of special memory cells has failed, reset the at least one special memory cell if the at least one special memory cell has failed, and erase the plurality of main memory cells.

In another embodiment, an erasing method is adopted in a memory device. The memory device includes a string of memory cells and a controller. The string of memory cells includes a plurality of special memory cells not for storing data and a plurality of main memory cells for storing data. The erasing method includes: the controller verifying if at least one special memory cell of the plurality of special memory cells has failed; the controller resetting the at least one special memory cell if the at least one special memory cell has failed; and the controller erasing the plurality of main memory cells.

These and other objectives of the present invention will no doubt become obvious to those of ordinary skill in the art after reading the following detailed description of the preferred embodiment that is illustrated in the various figures and drawings.

BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a perspective view of a memory device according to an embodiment of the invention.

FIG. 2 is a block diagram of the memory device in FIG. 1.

FIG. 3 is a flowchart of an erasing method for use in the memory device in FIG. 1.

FIG. 4 is a flowchart of a resetting method incorporated in the erasing method in FIG. 3.

FIG. 5 is a flowchart of another erasing method for use in the memory device in FIG. 1.

FIG. 6 is a flowchart of a resetting method incorporated in the erasing method in FIG. 5.

DETAILED DESCRIPTION

FIG. 1 is a perspective view of a memory device 1 according to an embodiment of the invention. The memory device 1 may be a 3-dimentional (3D) NAND flash device, and may include a substrate 10, a controller 12 and a memory circuit 14. The controller 12 and the memory circuit 14 may be disposed on the substrate 10. The memory circuit 14 may contain a plurality of cell arrays 141 to 14M stacked in layers and used for data storage, M being a positive integer. The controller 12 may be coupled to the memory circuit 14 to control reading, programming and/or erasing operations of the memory circuit 14, and may communicate with an external host to receive data for storage in the memory circuit 14 and to transmit data fetched from the memory circuit 14.

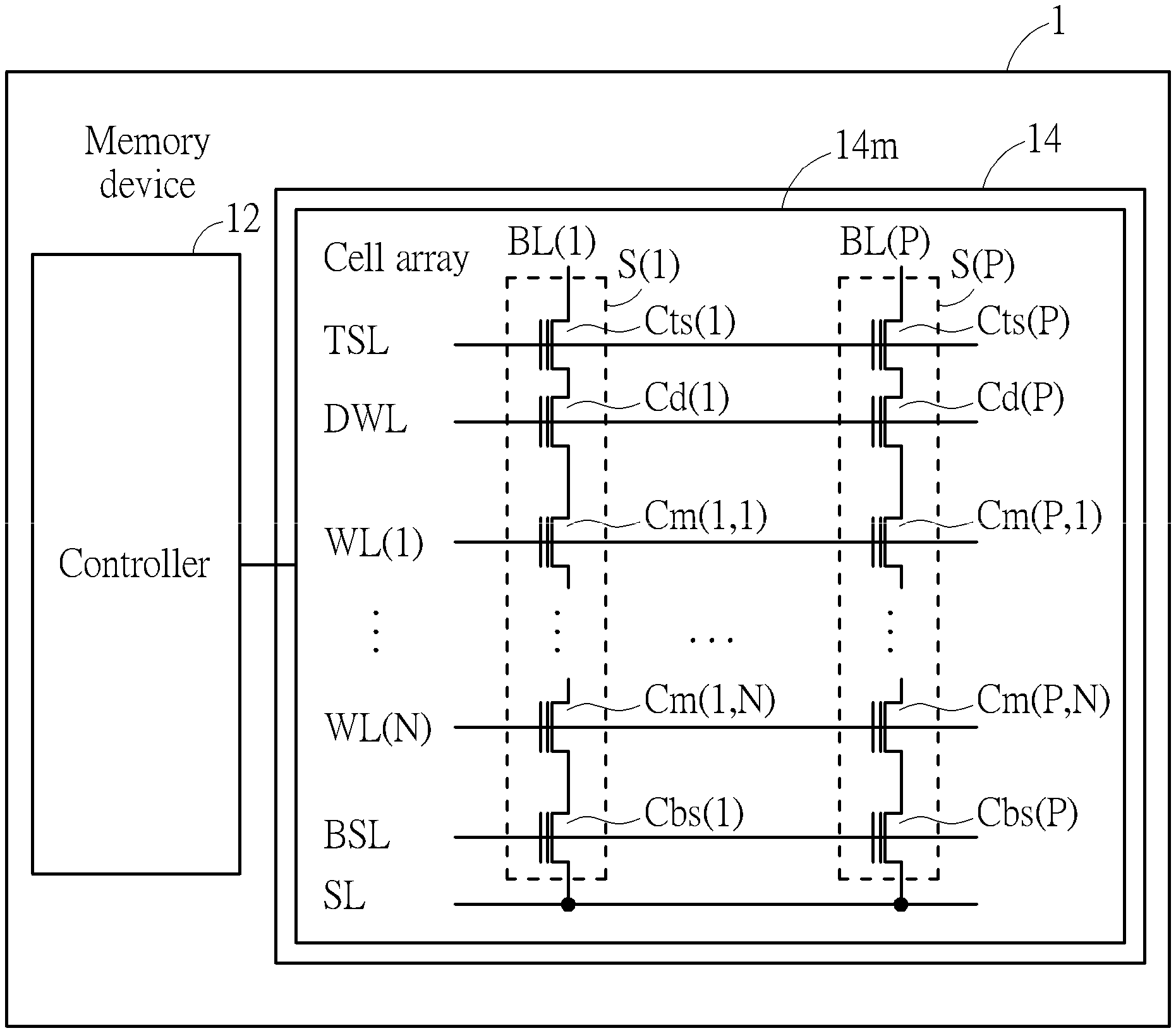

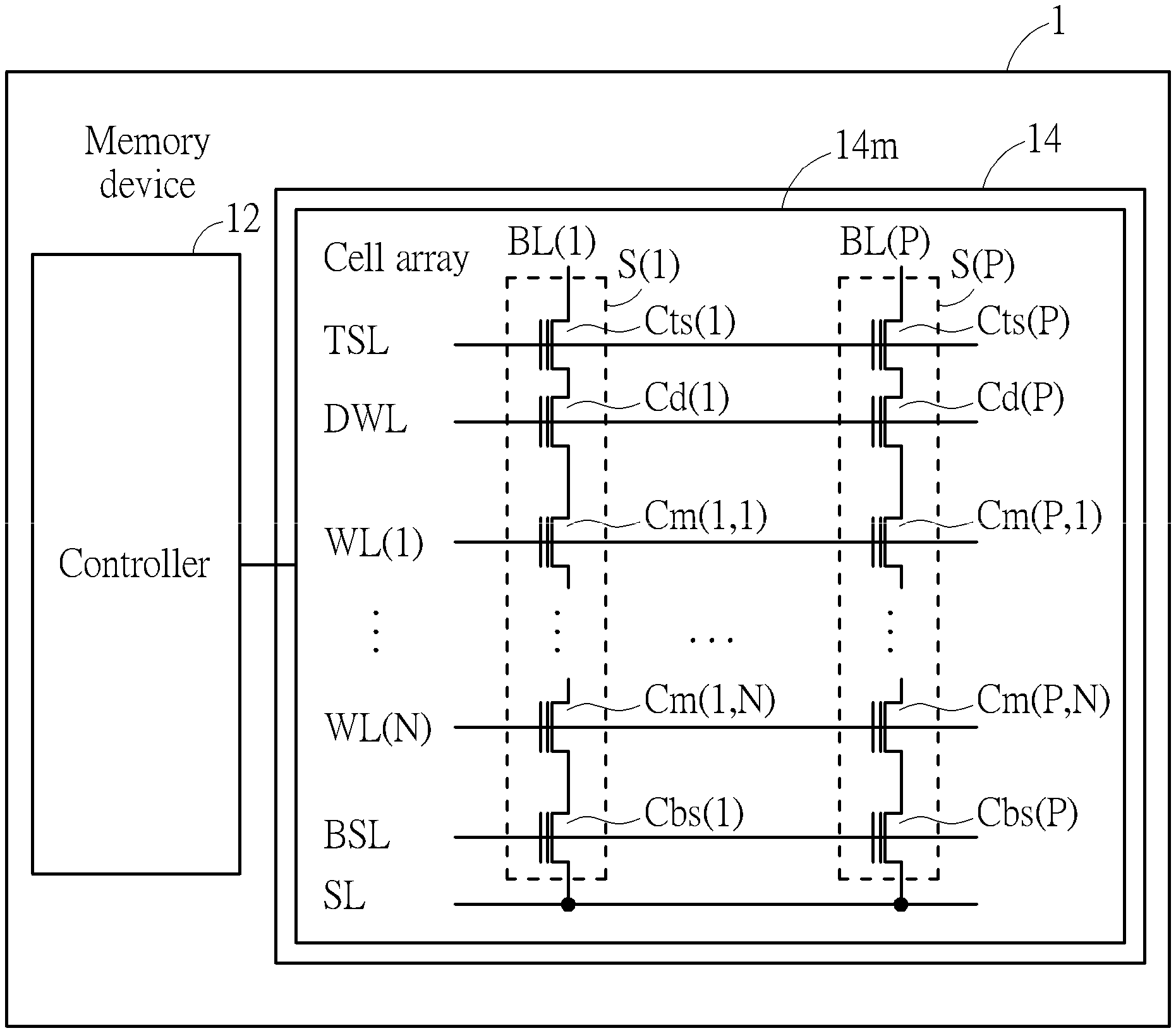

FIG. 2 is a block diagram of the memory device 1. The memory device 1 may include a top selection line TSL, a dummy word line DWL, word lines WL(1) to WL(N), a bottom selection line BSL, a source line SL, bit lines BL(1) to BL(P), the controller 12, and the memory circuit 14 including a plurality of cell arrays 141 to 14M where only the cell array 14m is shown on FIG. 2, wherein N, P are positive integers, e.g., N=64 and P=8192, m being a positive integer and m.ltoreq.M. The top selection line TSL and the dummy word line DWL may be referred to as special word lines.

The cell array 14m may include top selection cells Cts(1) to Cts(P), dummy memory cells Cd(1) to Cd(P), main memory cells Cm(1,1) to Cm(P,N), bottom selection cells Cbs(1) to Cbs(P) arranged into cell strings S(1) to S(P). In some embodiments, the cell array 14m may include two or more rows of the top selection cells, dummy memory cells and bottom selection cells. Moreover, in some embodiments, the cell array 14m may include one or more rows of dummy memory cells between the row of bottom selection cells and the main memory cells Cm(1,1) to Cm(P,N). The memory device 1 may be used to verify and reset the top selection cells Cts(1) to Cts(P) and the dummy memory cells Cd(1) to Cd(P) of the cell arrays 141 to 14M during an erasing operation, thereby reducing program disturbance.

Each of the top selection cells Cts(1) to Cts(P), the dummy memory cells Cd(1) to Cd(P), the main memory cells Cm(1,1) to Cm(P,N) and the bottom selection cells Cbs (1) to Cbs(P) may be a floating-gate transistor or a charge-trapping transistor including a control terminal, a first terminal and a second terminal. The top selection line TSL may be coupled to the control terminals of the top selection cells Cts(1) to Cts(P), and the bit lines BL(1) to BL(P) may be respectively coupled to the first terminals of the top selection cells Cts(1) to Cts(P). The dummy word line DWL may be coupled to the control terminals of the dummy memory cells Cd(1) to Cd(P), and the first terminals of the dummy memory cells Cd(1) to Cd(P) may be respectively coupled to the second terminals of the top selection cells Cts(1) to Cts(P). The word lines WL(1) to WL(N) may be coupled to the main memory cells Cm(1,1) to Cm(P,1) in a first row to the main memory cells Cm(1,N) to Cm(P,N) in an Nth row, respectively, and the first terminals of the main memory cells Cm(1,1) to Cm(P,1) may be coupled to the second terminals of the dummy memory cells Cd(1) to Cd(P), respectively. The bottom selection line BSL may be coupled to the control terminals of the bottom selection cells Cbs(1) to Cbs(P), the first terminals of the bottom selection cells Cbs(1) to Cbs(P) may be respectively coupled to the second terminals of the main memory cells Cm(1,N) to Cm(P,N), and the source line SL may be coupled to the second terminals of the bottom selection cells Cbs(1) to Cbs(P). The controller 12 may address the main memory cells Cm(1,1) to Cm(P N) using the word lines WL(1) to WL(N) and the bit lines BL(1) to BL(P).

The top selection cells Cts(1) to Cts(P) and the dummy memory cells Cd(1) to Cd(P) may be referred to as special memory cells. Each string S(p) may contain special memory cells Cts(p), Cd(p), main memory cells Cm(p,1) to Cm(p,N), and a bottom selection cell Cbs(p), p being a positive integer and p.ltoreq.P. The special memory cells Cts(p), Cd(p) are not used to store user data, are arranged at one end of the string S(p), and are coupled in series. The main memory cells Cm(p,1) to Cm(p,N) are used to store user data and coupled in series. The top selection cells Cts(1) to Cts(P), the dummy memory cells Cd(1) to Cd(P), the main memory cells Cm(1,1) to Cm(P,N) and the bottom selection cells Cbs(1) to Cbs(P) may be of a single-level cell (SLC) type, a multi-level cell (MLC) type, a triple-level cell (TLC) type, a quad-level cell (QLC) type, or a higher-level type, and programmed into one of Q possible states, Q being a positive integer greater than 1, e.g., Q=2 for an SLC, Q=4 for an MLC, Q=8 for a TLC, and Q=16 for a QLC.

In a programming operation, the supply voltage (e.g., 3.3V) may be applied to the top selection line TSL, the ground voltage (e.g., 0V) may be applied to the bottom selection line BSL, a program voltage (e.g., 20V) may be applied to a selected word line, a pass voltage (e.g., 10V) may be applied to unselected word lines and the dummy word line DWL, the ground voltage may be applied to a selected bit line, and the supply voltage may be applied to an unselected bit line. For example, when programming the main memory cell Cm(1,1), the top selection line TSL is driven by 3.3V, the bottom selection line BSL is grounded at 0V, the word line WL(1) is driven by 20V, the word lines WL(2) to WL(M) and the dummy word line DWL are driven by 10V, the bit line BL(1) is grounded at 0V and the bit lines BL(2) to BL(P) are driven by 3.3V. In such an arrangement, a large voltage difference is present between a channel region and the control terminal of a selected main memory cell, causing electrons to be injected from the channel region into a floating gate or charge-trapping layer of the selected main memory cell to program the same, while boosted voltages (e.g., 8V) are established at channel regions of unselected main memory cells by capacitive coupling the pass voltage from the control terminals to the channel regions thereof, preventing the unselected main memory cells from being programmed and reducing program disturbance. The top selection cells Cts(1) to Cts(P) may be programmed into a predetermined state (e.g., an erased state) prior to the programming operation. The dummy memory cells Cd(1) to Cd(P) may be programmed into a predetermined state (e.g., the erased state) prior to the programming operation, and biased at the control terminals thereof by the pass voltage or a dummy bias voltage during the programming operation, providing a gradual transition in channel voltages from the channel voltages of channel regions of the main memory cells Cm(1,1) to Cm(P,1) to the channel voltages of channel regions of the top selection cells Cts(1) to Cts(P), reducing program disturbance by suppressing gate induced drain leakage (GIDL) during the programming operation, particularly during programming one of the main memory cells Cm(1,1) to Cm(P,1). In some embodiments, the dummy bias voltage may be selected from a range between the pass voltage and the supply voltage.

In an erasing operation, in addition to erasing user data from the main memory cells Cm(1,N) to Cm(P,N), the threshold voltages of the top selection cells Cts(1) to Cts(P) and the dummy memory cells Cd(1) to Cd(P) may be verified and reset if the verification fails, thereby enabling the top selection cells Cts(1) to Cts(P) and the dummy memory cells Cd(1) to Cd(P) to operate properly and reduce the program disturbance in the programming operation. In some embodiments, the reset of the top selection cells Cts(1) to Cts(P) and the dummy memory cells Cd(1) to Cd(P) may be optional, and the setting of reset preference may be stored in a register in the memory device 1. When the reset preference is set to be enabled, the controller 12 may reset the top selection cells Cts(1) to Cts(P) and the dummy memory cells Cd(1) to Cd(P) upon detecting that the top selection cells Cts(1) to Cts(P) and the dummy memory cells Cd(1) to Cd(P) fail the verification; whereas when the reset preference is not set to be enabled, the controller 12 may abort the erasing operation upon detecting that the top selection cells Cts(1) to Cts(P) and the dummy memory cells Cd(1) to Cd(P) fail the verification. FIGS. 3 to 6 outline erasing methods and resetting methods of resetting the top selection cells Cts(1) to Cts(P) and the dummy memory cells Cd(l) to Cd(P) in the erasing operation.

FIG. 3 is a flowchart of an erasing method 300 for use in the memory device 1. The erasing method 300 comprises Steps S302 to S308, resetting the special memory cells prior to erasing data from the main memory cells Cm(1,N) to Cm(P,N). Steps S302 to S306 are used to set the special memory cells to proper threshold voltage ranges, and Step S308 is used to erase the main memory cells Cm(1,N) to Cm(P,N). In some embodiments, the erasing method may be adopted by the memory device 1 to verify and reset the top selection cells Cts(1) to Cts(P). Any reasonable step change or adjustment is within the scope of the disclosure. Steps S302 to S308 are explained as follows:

Step S302: The controller 10 verifies the special memory cells;

Step S304: Has at least one special memory cell failed the verification? If so, go to Step S305; and if not, go to Step S308;

Step S305: Is reset preference enabled? If so, go to Step S306; and if not, exit the method 300;

Step S306: The controller 10 resets the at least one special memory cell; go to Step S308;

Step S308: The controller 10 erases the main memory cells; exit the method 300.

Upon initialization of the erasing method 300, the controller 10 verifies the special memory cells using an upper verification level and a lower verification level (S302). The upper verification level and the lower verification level may be selected according to the lower bound and the upper bound of a predetermined threshold voltage distribution range of the special memory cells, respectively. When the threshold voltage of at least one special memory cell is outside the predetermined threshold voltage distribution range, the at least one special memory cell may not function properly and may lead to program disturbance, and the at least one special memory cell has failed the verification. The controller 10 next determines whether at least one special memory cell has failed the verification (S304), if not, the controller 10 erases the main memory cells Cm(1,1) to Cm(P,N) (S308) and exits the method 300, and if so, the controller 10 determines whether the reset preference is set to be enabled (S305). If the at least one special memory cell has failed the verification and the reset preference is not set to be enabled, the method 300 is exited without erasing the memory cells Cm(1,1) to Cm(P,N). If at least one special memory cell has failed the verification and the reset preference is set to be enabled, the controller 10 resets the at least one special memory cell by bringing the threshold voltage of the at least one special memory cell back within the predetermined threshold voltage distribution range (S306), and then erases the main memory cells Cm(1,1) to Cm(P,N) (S308).

FIG. 4 is a flowchart of a resetting method 400 to be incorporated in the method 300. The resetting method 400 comprises Steps S402 to S412 for verifying and resetting the special memory cells. Any reasonable step change or adjustment is within the scope of the disclosure. Steps S402 to S412 are explained as follows:

Step S402: The controller 10 verifies the special memory cells using a lower verification level;

Step S404: Is the threshold voltage of at least one special memory cell less than the lower verification level? If so, go to Step S406; and if not, go to Step S408;

Step S406: The controller 10 applies a program pulse to the at least one special memory cell; go to Step S408;

Step S408: The controller 10 verifies the special memory cells using an upper verification level;

Step S410: Is the threshold voltage of at least one special memory cell higher than the upper verification level? If so, go to Step S412; and if not, exit the method 400;

Step S412: The controller 10 performs a soft erasing operation on the at least one special memory cell; exit the method 400.

In Step S402, the controller 10 applies the lower verification level to the control terminals of the special memory cells while reading the states thereof, and in Step S404, the controller 10 determines whether the threshold voltage of at least one special memory cell is less than the lower verification level according to the reading result. If a state of at least one special memory cell is read correctly using the lower verification level, the threshold voltage of the at least one special memory cell is less than the lower verification level and being too low, and therefore, in Step S406, the controller 10 applies one or more program pulses to the at least one special memory cell until the controller 10 is unable to read the state of the at least one special memory cell. Next in Step S408, the controller 10 applies the upper verification level to the control terminals of the special memory cells while reading the states thereof, and in Step S410, the controller 10 determines whether the threshold voltage of at least one special memory cell is higher than the lower verification level according to the reading result. If a state of at least one special memory cell is read incorrectly using the upper verification level, the threshold voltage of the at least one special memory cell is not higher than the upper verification level, and the method 400 is exited. If a state of at least one special memory cell is read incorrectly using the upper verification level, the threshold voltage of the at least one special memory cell is higher than the upper verification level and being too high, and therefore, in Step S412, the controller 10 performs a soft erasing operation on the at least one special memory cell to bring the threshold voltage thereof to below the upper verification level, and exits the method 400. The soft erasing operation may be performed by grounding the control terminal of the at least one special memory cell while applying an appropriate soft erasing voltage to the bit line of the at least one special memory cell, thereby discharging excessive charges from the floating gate or charge-trapping layer of the at least one special memory cell. The soft erasing voltage may be a positive voltage and smaller in magnitude than an erasing voltage adopted in an erasing operation. In some embodiments, the order of verifying and correcting the special memory cells too low in threshold voltages and the special memory cells too high in threshold voltages may be exchanged, that is, Steps S408 to S412 and Steps S402 to S406 may be swapped in places.

FIG. 5 is a flowchart of another erasing method 500 for use in the memory device 1. The erasing method 500 comprises Steps S502 to S508, erasing data from the main memory cells Cm(1,N) to Cm(P,N) prior to resetting the special memory cells. Step S502 is used to erase the main memory cells, and Steps S505 to S508 are used to set the special memory cells to proper states. In some embodiments, the erasing method may be adopted by the memory device 1 to verify and reset the dummy memory cells Cd(1) to Cd(P). Any reasonable step change or adjustment is within the scope of the disclosure. Steps S502 to S508 are explained as follows:

Step S502: The controller 10 erases the main memory cells;

Step S504: The controller 10 verifies the special memory cells;

Step S506: Has at least one special memory cell failed the verification? If so, go to Step S507; and if not, exit the method 500;

Step S507: Is reset preference enabled? If so, go to Step S508; and if not, exit the method 500;

Step S508: The controller 10 resets the at least one special memory cell; exit the method 500.

Upon initialization of the erasing method 500, the controller 10 erases the main memory cells Cm(1,N) to Cm(P,N) (S502), and next verifies the special memory cells using an upper verification level and a lower verification level (S504). The upper verification level and the lower verification level may be selected according to the lower bound and the upper bound of a predetermined threshold voltage distribution range of the special memory cells, respectively. When the threshold voltage of at least one special memory cell is outside the predetermined threshold voltage distribution range, the at least one special memory cell may not function properly and may lead to program disturbance, and the at least one special memory cell has failed the verification. The controller 10 determines whether at least one special memory cell has failed the verification (S506), if not, the controller 10 exits the method 500, and if so, the controller 10 determines whether the reset preference is set to be enabled (S507). If at least one special memory cell has failed the verification and the reset preference is not set to be enabled, the method 500 is exited directly without resetting the at least one special memory cell. If the at least one special memory cell has failed the verification and the reset preference is set to be enabled, the controller 10 resets the at least one special memory cell by bringing the threshold voltage of the at least one special memory cell back within the predetermined threshold voltage distribution range (S508), and then exits the method 500 (S508).

FIG. 6 is a flowchart of a resetting method 600 to be incorporated in the method 500. The method 600 comprises Steps S602 to S608 for resetting the special memory cells. Any reasonable step change or adjustment is within the scope of the disclosure. Steps S602 to S608 are explained as follows:

Step S602: The controller 10 verifies the special memory cells;

Step S604: Is the threshold voltage of at least one special memory cells higher than an upper verification level or less than a lower verification level? If so, go to Step S606; and if not, exit the method 600;

Step S606: The controller 10 erases the special memory cells and the main memory cells;

Step S608: The controller 10 programs the special memory cells; exit the method 600.

In Step S602, the controller 10 applies the lower verification level or the upper verification level to the control terminals of the special memory cells to read the states thereof, and in Step S604, the controller 10 determines whether the threshold voltage of at least one special memory cell is higher than the upper verification level or less than the lower verification level according to the reading result. If a state of at least one special memory cell is read correctly using the lower verification level, the threshold voltage of the at least one special memory cell is less than the lower verification level and being too low, and if a state of at least one special memory cell is read incorrectly using the upper verification level, the threshold voltage of the at least one special memory cell is higher than the upper verification level and being too high. If the threshold voltage of at least one special memory cell is higher than the upper verification level or less than the lower verification level, the controller 10 erases the special memory cells and the main memory cells Cm(1,1) to Cm(P,N) (S606), then programs the special memory cells to the corresponding predetermined states (S608), and exits the method 600. The erasing of the special memory cells and the main memory cells Cm(1,1) to Cm(P,N) may be performed by grounding the control terminals of the special memory cells and the main memory cells Cm(1,1) to Cm(P,N) while applying an appropriate erasing voltage to the bit lines of the special memory cells and the main memory cells Cm(1,1) to Cm(P,N), thereby discharging all charges from the floating gate or charge-trapping layer of the special memory cells and the main memory cells Cm(1,1) to Cm(P,N).

The memory device 1 and the methods 300 to 600 may be adopted to verify and reset special memory cells in the memory device 1 in an erasing operation, thereby reducing program disturbance and enhancing device performance.

Those skilled in the art will readily observe that numerous modifications and alterations of the device and method may be made while retaining the teachings of the invention. Accordingly, the above disclosure should be construed as limited only by the metes and bounds of the appended claims.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.