Soft-switching Voltage-edge-rate-limiting Power Inverter

Wasynczuk; Oleg ; et al.

U.S. patent application number 17/551071 was filed with the patent office on 2022-04-07 for soft-switching voltage-edge-rate-limiting power inverter. This patent application is currently assigned to Purdue Research Foundation. The applicant listed for this patent is Purdue Research Foundation. Invention is credited to Minyu Cai, Oleg Wasynczuk.

| Application Number | 20220109379 17/551071 |

| Document ID | / |

| Family ID | |

| Filed Date | 2022-04-07 |

View All Diagrams

| United States Patent Application | 20220109379 |

| Kind Code | A1 |

| Wasynczuk; Oleg ; et al. | April 7, 2022 |

SOFT-SWITCHING VOLTAGE-EDGE-RATE-LIMITING POWER INVERTER

Abstract

An auxiliary resonant soft-edge pole inverter circuit is provided. The power inverter circuitry may include a first pair of capacitors in parallel with a corresponding pair of main power switching modules, each power switching module comprising a switch and a diode in parallel and sharing a common central node with the first pair of capacitors. The power inverter circuit may further include a first pair of auxiliary switches connected in series with a first pair of inductors, respectively, to generate resonant current from a DC power source, the first pair of inductors also sharing the common central node. The power inverter circuitry may further include a second pair of auxiliary switches connected in series with a second pair of capacitors, respectively, the second pair of auxiliary switches also sharing the common central node, the circuit producing an alternating current output at the common central node.

| Inventors: | Wasynczuk; Oleg; (West Lafayette, IN) ; Cai; Minyu; (Roseville, MN) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Assignee: | Purdue Research Foundation West Lafayette IN |

||||||||||

| Appl. No.: | 17/551071 | ||||||||||

| Filed: | December 14, 2021 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 16887013 | May 29, 2020 | 11201562 | ||

| 17551071 | ||||

| 62865292 | Jun 23, 2019 | |||

| International Class: | H02M 7/48 20070101 H02M007/48; H02M 7/5387 20070101 H02M007/5387 |

Goverment Interests

STATEMENT REGARDING GOVERNMENT FUNDING

[0002] This invention was made with government support under DE-EE0005568 awarded by the Department of Energy. The government has certain rights in the invention.

Claims

1. An auxiliary resonant soft-edge pole inverter circuit, comprising: a first pair of capacitors in parallel with a corresponding pair of main power switching modules, each power switching module comprising a switch and a diode in parallel and sharing a common central node with the first pair of capacitors; a first pair of auxiliary switches connected in series with a first pair of inductors, respectively, to generate resonant current from a DC power source, the first pair of inductors also sharing the common central node; and a second pair of auxiliary switches connected in series with a second pair of capacitors, respectively, the second pair of auxiliary switches also sharing the common central node, the circuit producing an alternating current output at the common central node.

2. The circuit of claim 1, further comprising a second pair of diodes respectively connected in series with the first pair of auxiliary switches.

3. The circuit of claim 1, further comprising a second pair of diodes connected between the second pair of auxiliary switches and the inductors, respectively.

4. The circuit of claim 3, further comprising a third pair of diodes connected in parallel with the second set of auxiliary switches and sharing the common central node.

5. The circuit of claim 4, further comprising a fourth pair of diodes connected between the second pair of auxiliary switches and the DC power source.

6. The circuit of claim 1, wherein at least one of the switches comprises insulated-gate bipolar transistor.

7. The circuit of claim 1, wherein at least one of the switches comprise a metal-oxide-semiconductor field-effect transistor (MOSFET).

8. A power inverter circuit, comprising: a plurality of capacitors comprising a first capacitor, a second capacitor, a third capacitor, and a fourth capacitor; a plurality of switches comprising a first switch, a second switch, a third switch, a fourth switch, a fifth switch, and a sixth switch; a plurality of inductors comprising a first inductor and a second inductor; and a plurality of diodes comprising a first diode, a second diode, wherein the first switch is connected in parallel with the first capacitor and the first diode, and the second switch is connected in parallel with a second capacitor and a second diode, wherein the third switch is connected in series with the first inductor and the fourth switch is connected in series with the second inductor, wherein the fifth switch is connected in series with the third capacitor and the sixth switch is connected in series with the fourth capacitor, and wherein the first and second switch, the first and second diode, the first and second capacitor, the first and second inductor, and the fifth and sixth switch share a common node.

9. The power inverter of claim 8, wherein the third and fourth switches comprise metal-oxide-semiconductor field-effect switches (MOSFET), and the diodes further comprise third and fourth diode, the third diode connected in series with the third switch, and the fourth diode connected in series with the fourth switch.

10. The power inverter of claim 8, wherein the diodes further comprise third and fourth diode, the third diode is between the third switch and the first inductor, and the fourth diode is connected between the second inductor and the fourth switch.

11. The power inverter of claim 10, wherein the diodes further comprise a fifth and sixth diode, wherein the fifth diode is connected in parallel with the fifth switch and the sixth diode connected in parallel with the sixth switch, the fifth and sixth diode both connected to the common node.

12. The power inverter of claim 11, further comprising a seventh and eighth diode, wherein the seventh diode is connected between the fourth switch and a DC power source, and the eighth diode is connected between the third switch and the DC power source.

13. The power inverter of claim 8, wherein at least one of the switches comprises insulated-gate bipolar switches.

14. The power inverter of claim 8, wherein at least one of the switches comprise a metal-oxide-semiconductor field-effect transistor (MOSFET).

Description

CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application is a continuation of U.S. application Ser. No. 16/887,013 filed May 29, 2021, which claims the benefit of U.S. Provisional Application No. 62/865,292 filed Jun. 23, 2019, the entireties of which is hereby incorporated by reference.

TECHNICAL FIELD

[0003] The present application relates to DC-to-AC power inverters, and more specifically, to soft-switching inverters.

BACKGROUND

[0004] Switch-mode DC-to-AC inverters are widely used in variable-speed motor drive systems and other applications. To increase switching frequency and reduce switching loss, power switches have been made faster in the past decades. The switching times of insulated-gate bipolar transistors (IGBTs) have reduced to tens of nanoseconds, while those of wide-bandgap (WBG) devices, such as Silicon Carbide and Gallium Nitride devices, have reduced to several nanoseconds.

[0005] As switches are made faster, the inverter output voltage edge rate (dv/dt) becomes larger. Various deleterious effects have been experienced and documented since the introduction of IGBTs. These problems include overvoltages at the motor/inverter terminals, electromagnetic interference, large common-mode currents, and the failure of motor bearings due to induced micro-arcs. To reduce the occurrence of problems resulting from high dv/dt, some standards have been established that limit the dv/dt going into motor drives, among which the US National Electrical Manufacturers Association (NEMA) MG1 Part 31 is commonly observed in the US.

[0006] Conventional dv/dt-limiting methods include increasing the external gate resistance or Miller capacitance of the switches, and adding a dv/dt filter between the inverter and the motor. All of these methods, especially the dv/dt filter, can effectively reduce the dv/dt but will introduce extra losses, size and weight of the system.

[0007] Soft-switching inverters that are originally developed to reduce switching loss can also limit the dv/dt in the circuits. They can possibly replace the dv/dt filter which may result in reduction in total loss and size/weight. Among various soft-switching inverter topologies, the auxiliary resonant commutated pole (ARCP) inverter and its variants are suitable for variable-speed motor drive systems because they have full pulse width modulation (PWM) control capabilities. The original ARCP inverter can realize zero-voltage switching (ZVS) and zero-current switching (ZCS) in its main and auxiliary switches, respectively. However, it has several drawbacks. First, the necessary mid-voltage point requires extra balancing circuits. Secondly, a boost current needs to be generated, which requires accurate current sensing and/or switch triggering, and results in complicated control. Thirdly, the reverse-recovery current of the auxiliary diodes will induce a large voltage across the auxiliary switches. Therefore, snubbers or voltage-clamping circuits are required, which generate extra losses. To eliminate these drawbacks, some variants of the ARCP were proposed over the past decades.

[0008] One approach to improve the ARCP is to use a transformer or coupled inductor. A topology described in J. D. Herbst, F. D. Engelkemeir, and A. L. Gattozzi, "High power density and high effciency converter topologies for electric ships," in Proc. IEEE Electric Ship Technol. Symp. (ESTS), April 2013, pp. 360-365 uses a 1:1 transformer to create a virtual mid-voltage point, and the auxiliary switches only conduct half of the resonant current. However, the transformer needs to be reset after each switching cycle by extra circuits. A transformer-assisted resonant pole inverter is proposed in X. Yuan and I. Barbi, "Analysis, designing, and experimentation of a transformer-assisted pwm zero-voltage switching pole inverter," IEEE Trans. Power Electron., vol. 15, no. 1, pp. 72-82, January 2000. Its transformer has a turns ratio different from one so the boost current is not required, which makes control simpler. The transformer current can be properly reset. However, the transformer is bulky and its leakage inductance is part of the resonant inductor which makes parameter design more challenging.

[0009] The other approach to improve the ARCP is represented by the auxiliary resonant pole (ARP). The ARP connects the resonant inductor to the upper or lower DC bus through auxiliary switches so it does not need a mid-voltage point. Due to this configuration, the boost current is not required, and the auxiliary switch turn-on and the main switch turn-off can be triggered at the same time, which makes control simpler. In addition, the transient voltage across auxiliary switches is clamped to the DC-bus voltage by auxiliary diodes. However, there are still some drawbacks with the ARP inverter. The auxiliary switches have lossy hard-switched turn-off. In addition, there may be a circulating current in the auxiliary circuits when a main switch module is conducting continuously, which again generates loss. A circuit proposed in W. Yu, J. S. Lai, and S. Y. Park, "An improved zero-voltage switching inverter using two coupled magnetics in one resonant pole," IEEE Trans. Power Electron., vol. 25, no. 4, pp. 952-961, April 2010 uses two coupled magnetics as resonant inductors so the circulating current can be prevented. However, the turn-off transients of the auxiliary switches are not perfect ZCS because of the remaining magnetizing current. Therefore, improvements are needed in the field.

[0010] The active auxiliary edge resonant pole (AAERP) (see M. Nakamura, T. Yamazaki, Y. Fujii, T. Ahmed, and M. Nakaoka, "A novel prototype of auxiliary edge resonant bridge leg link snubber-assisted soft-switching sine-wave PWM inverter," Elect. Eng. Jpn., vol. 155, no. 4, pp. 64-76, 2006) and the double ARCP (DARCP) (see E. Chu, X. Zhang, and L. Huang, "Research on a novel modulation strategy for double auxiliary resonant commutated pole soft-switching inverter with the shunt dead time," IEEE Trans. Power Electron., vol. 31, no. 10, pp. 6855-6869, October 2016.) improve upon ARP by adding a second pair of capacitors to realize ZVS turn off in the auxiliary switches. However, the second pair of capacitors may not be precharged to the DC-bus voltage, so the output dv/dt may sometimes be large.

BRIEF DESCRIPTION OF THE DRAWINGS

[0011] In the following description and drawings, identical reference numerals have been used, where possible, to designate identical features that are common to the drawings.

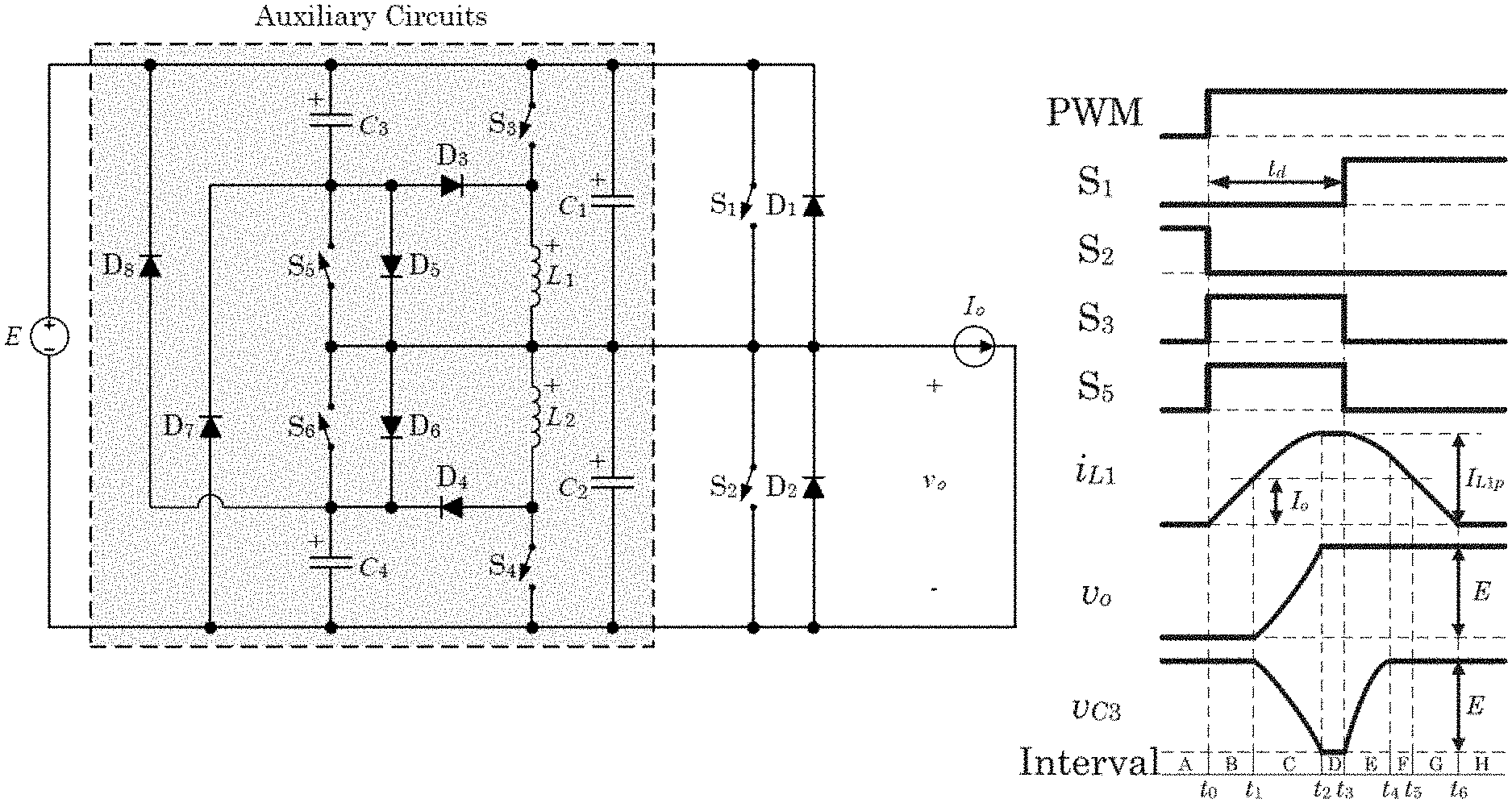

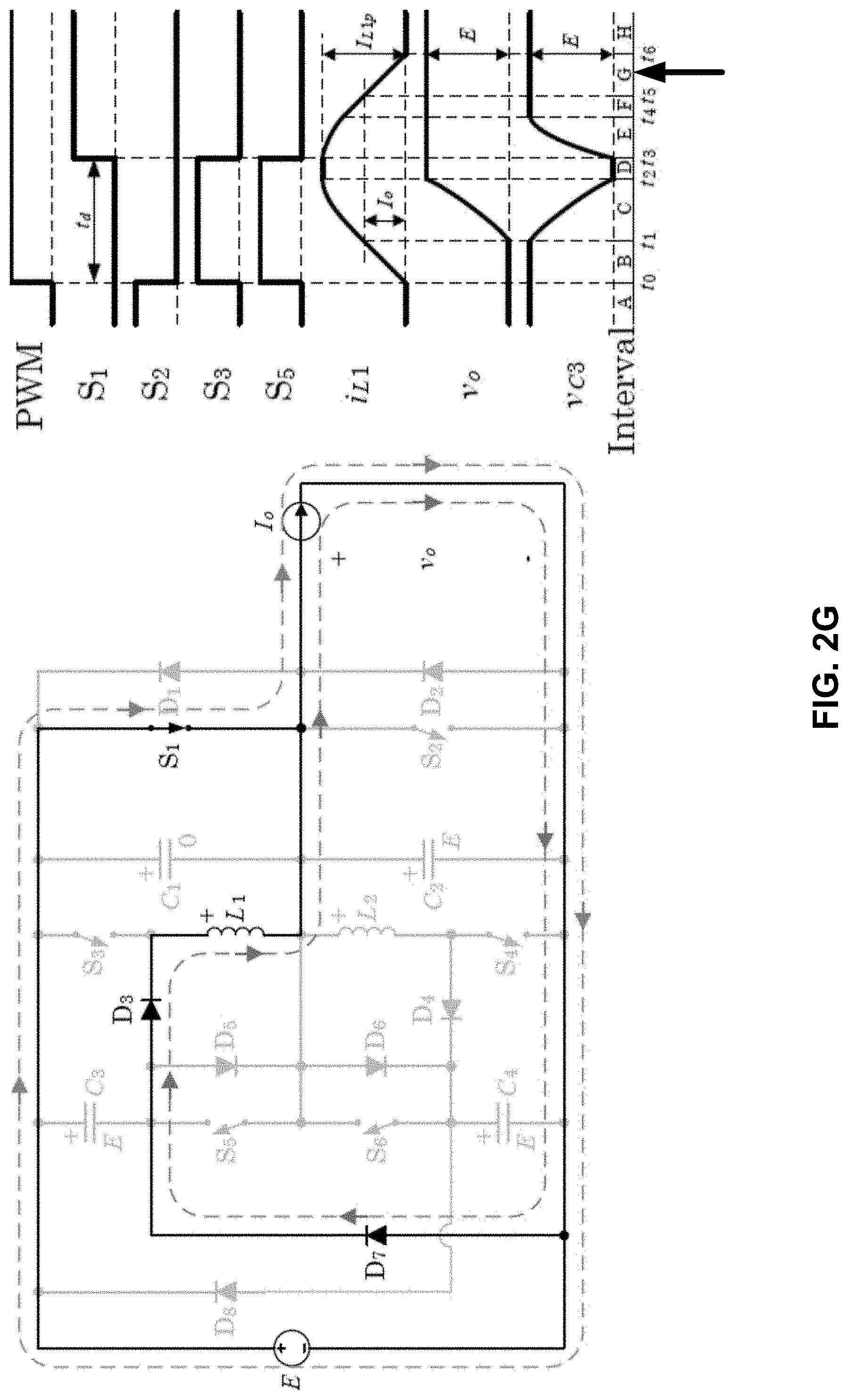

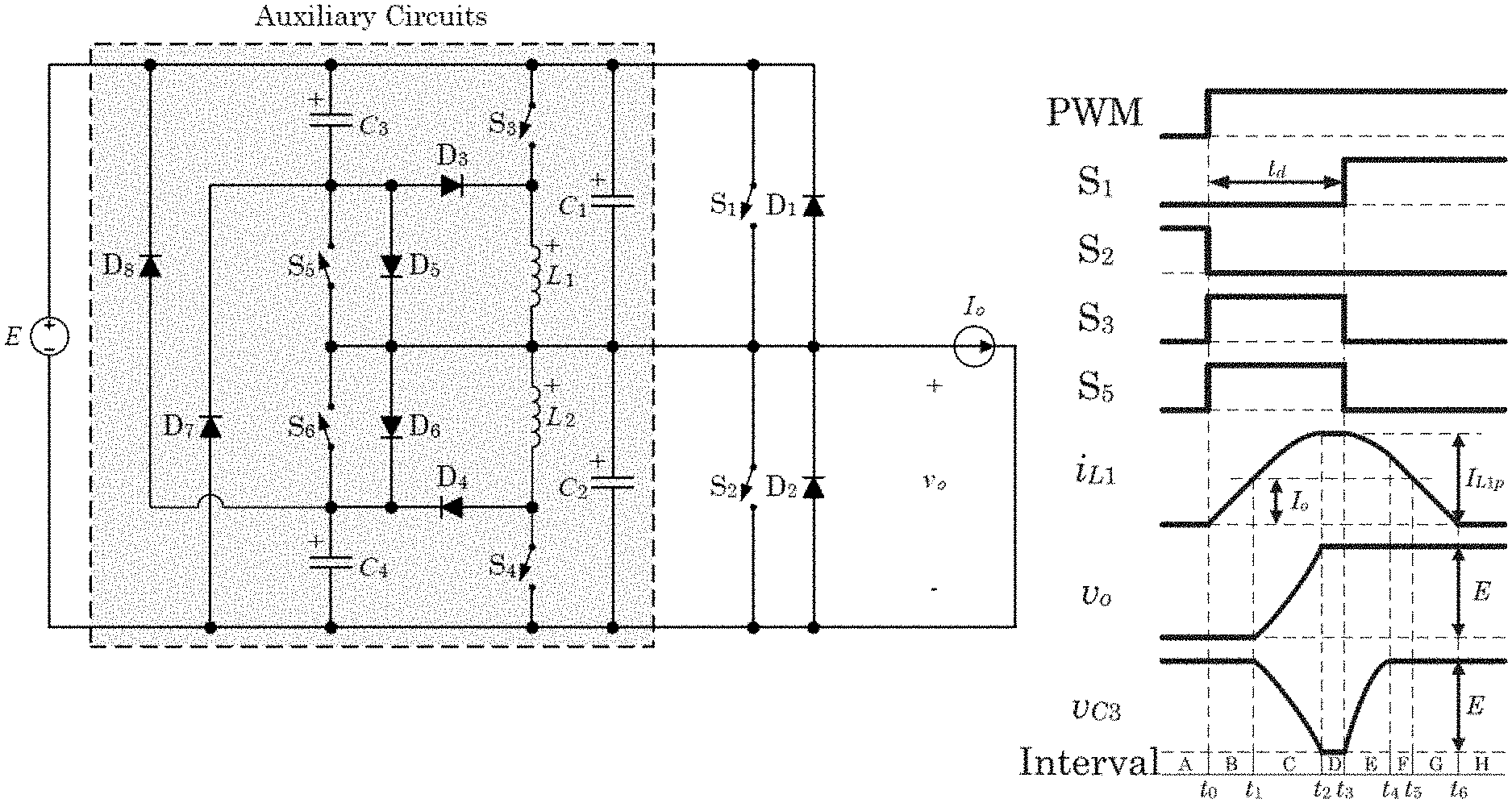

[0012] FIG. 1 is a schematic and timing diagram illustrating an auxiliary resonant soft-edge pole inverter circuit according to various aspects.

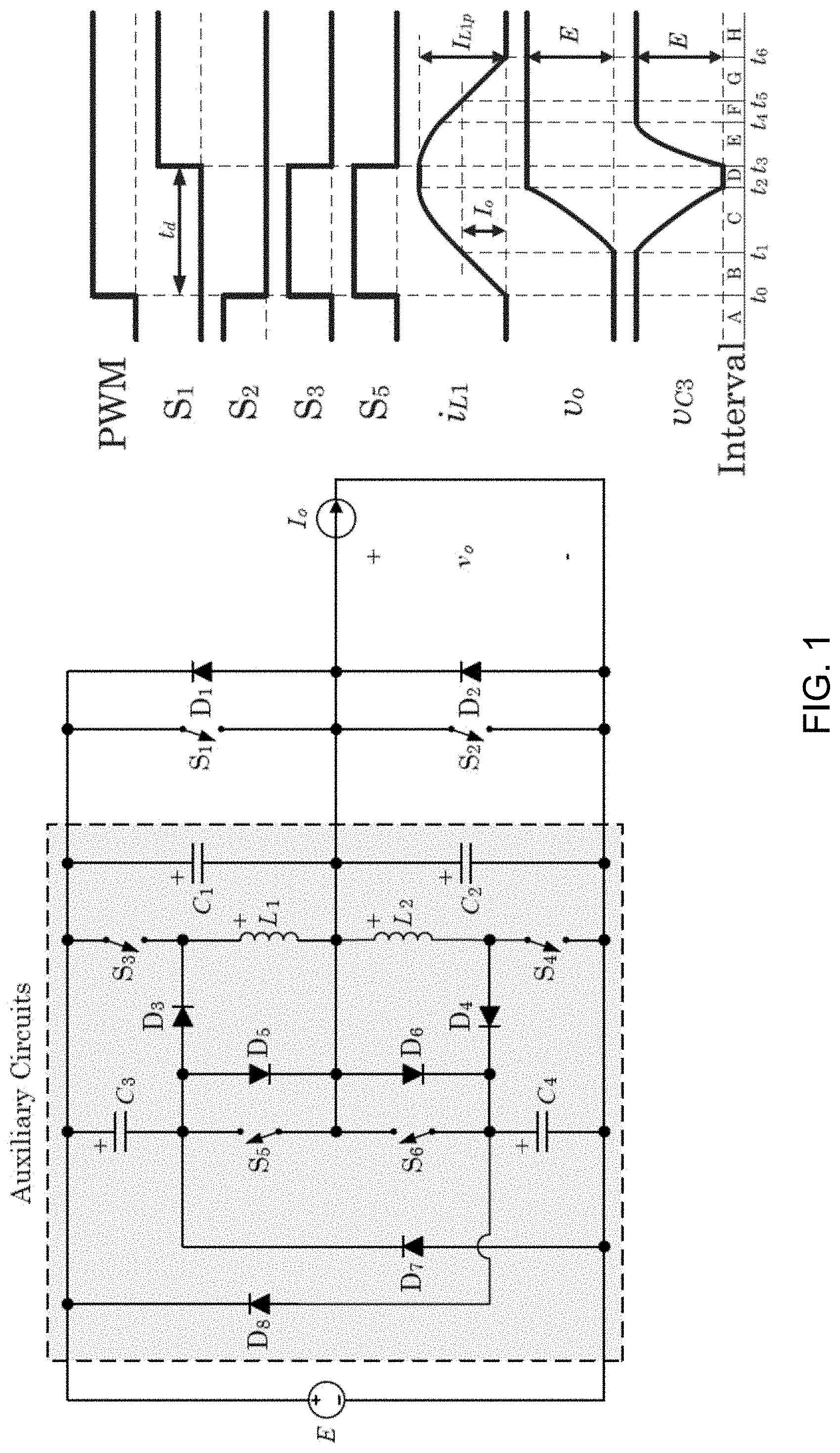

[0013] FIG. 2A is a schematic and timing diagram illustrating operation of a power inverter in a diode-to-switch (D2S) commutation during time Interval A according to various aspects.

[0014] FIG. 2B is a schematic and timing diagram illustrating operation of a power inverter in a D2S commutation during time Interval B according to various aspects.

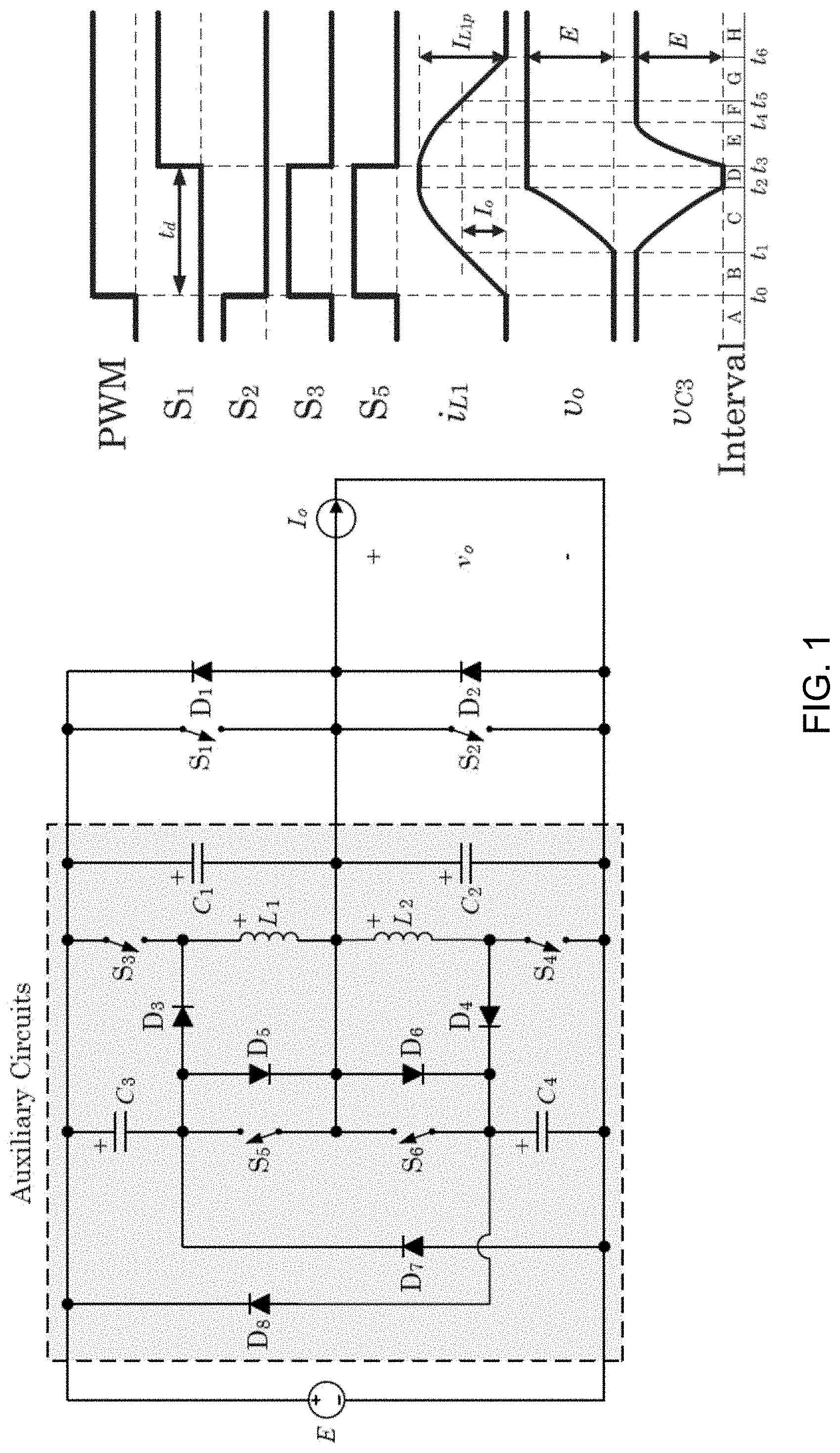

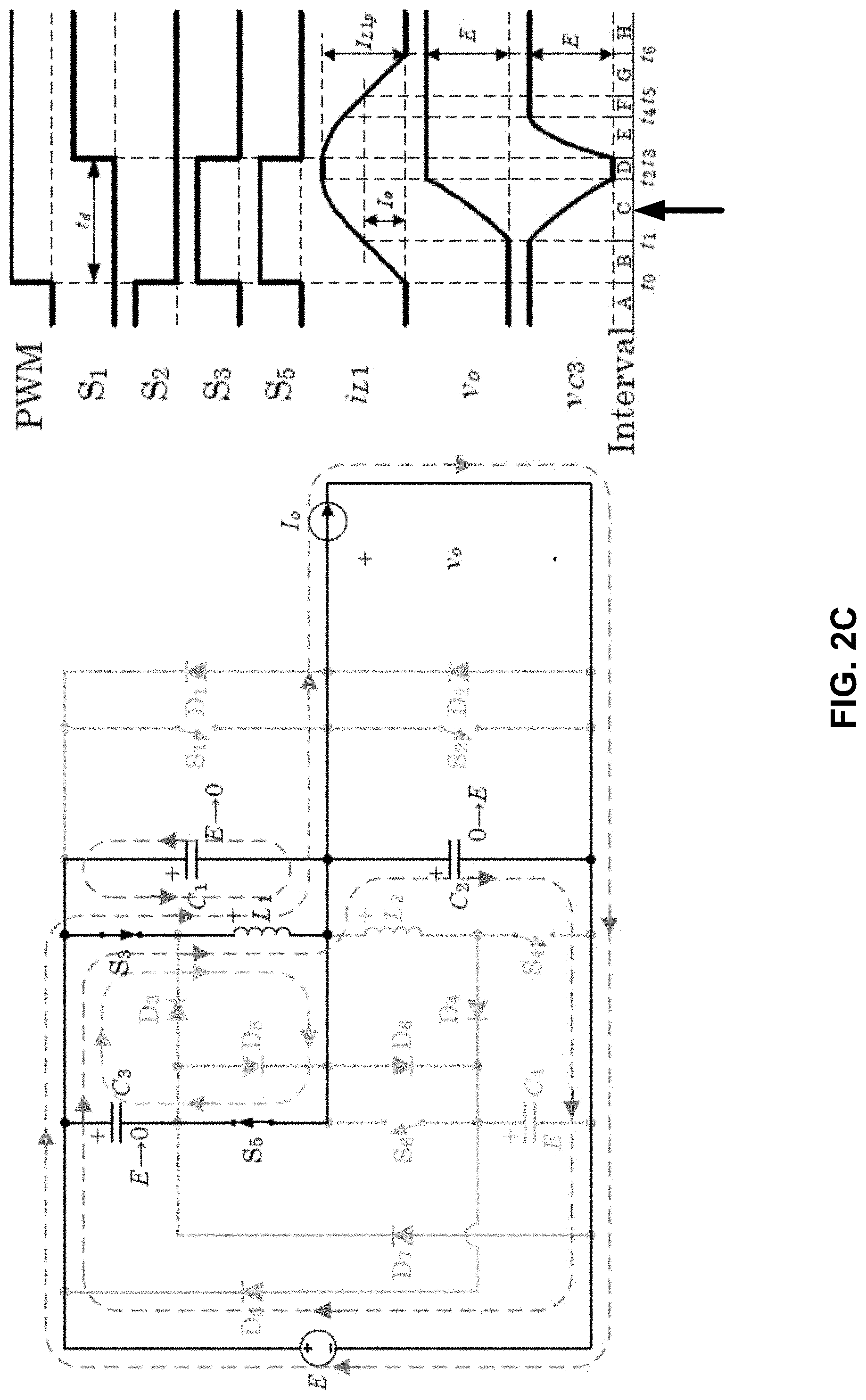

[0015] FIG. 2C is a schematic and timing diagram illustrating operation of a power inverter in a D2S commutation during time Interval C according to various aspects.

[0016] FIG. 2D is a schematic and timing diagram illustrating operation of a power inverter in a D2S commutation during time Interval D according to various aspects.

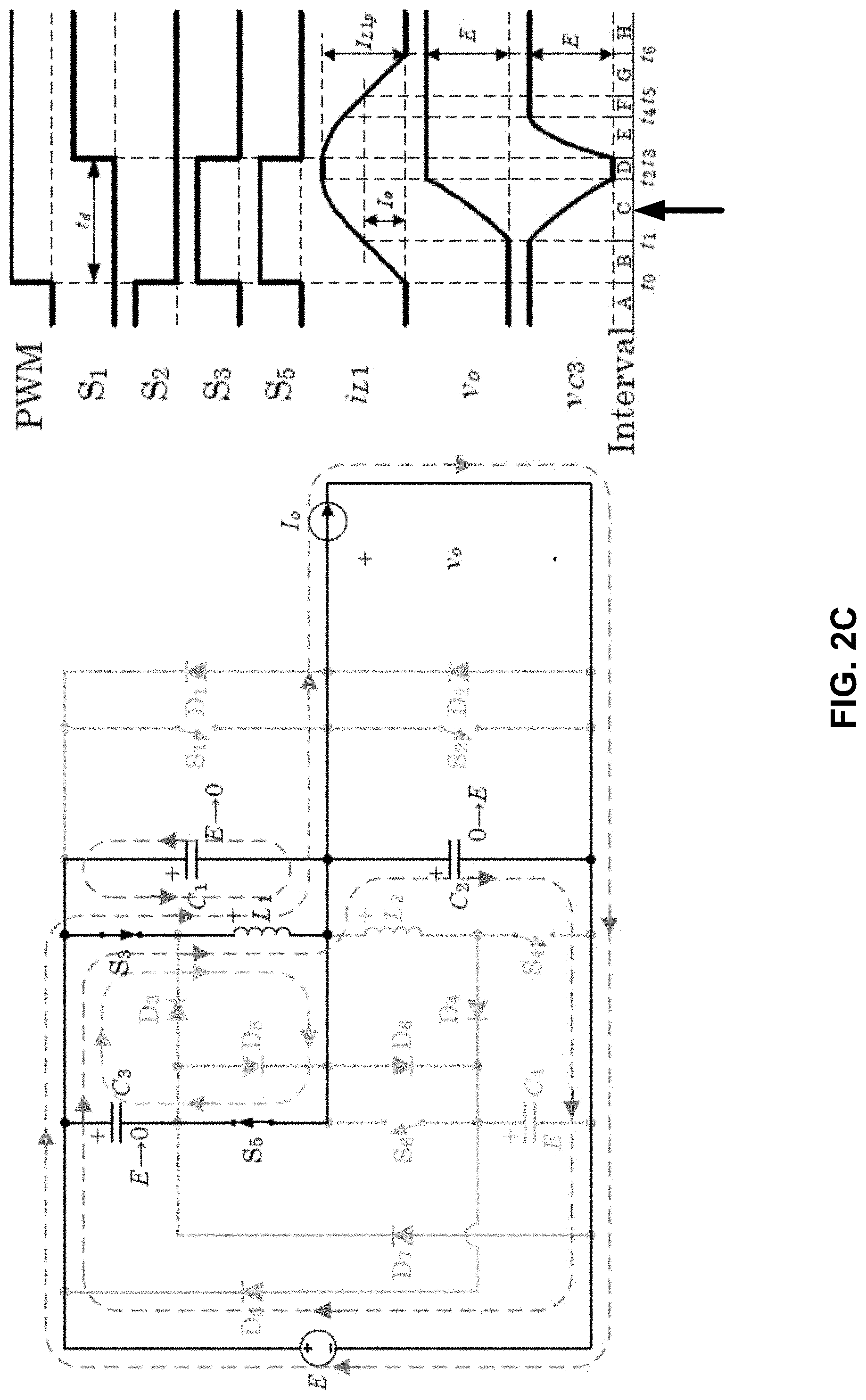

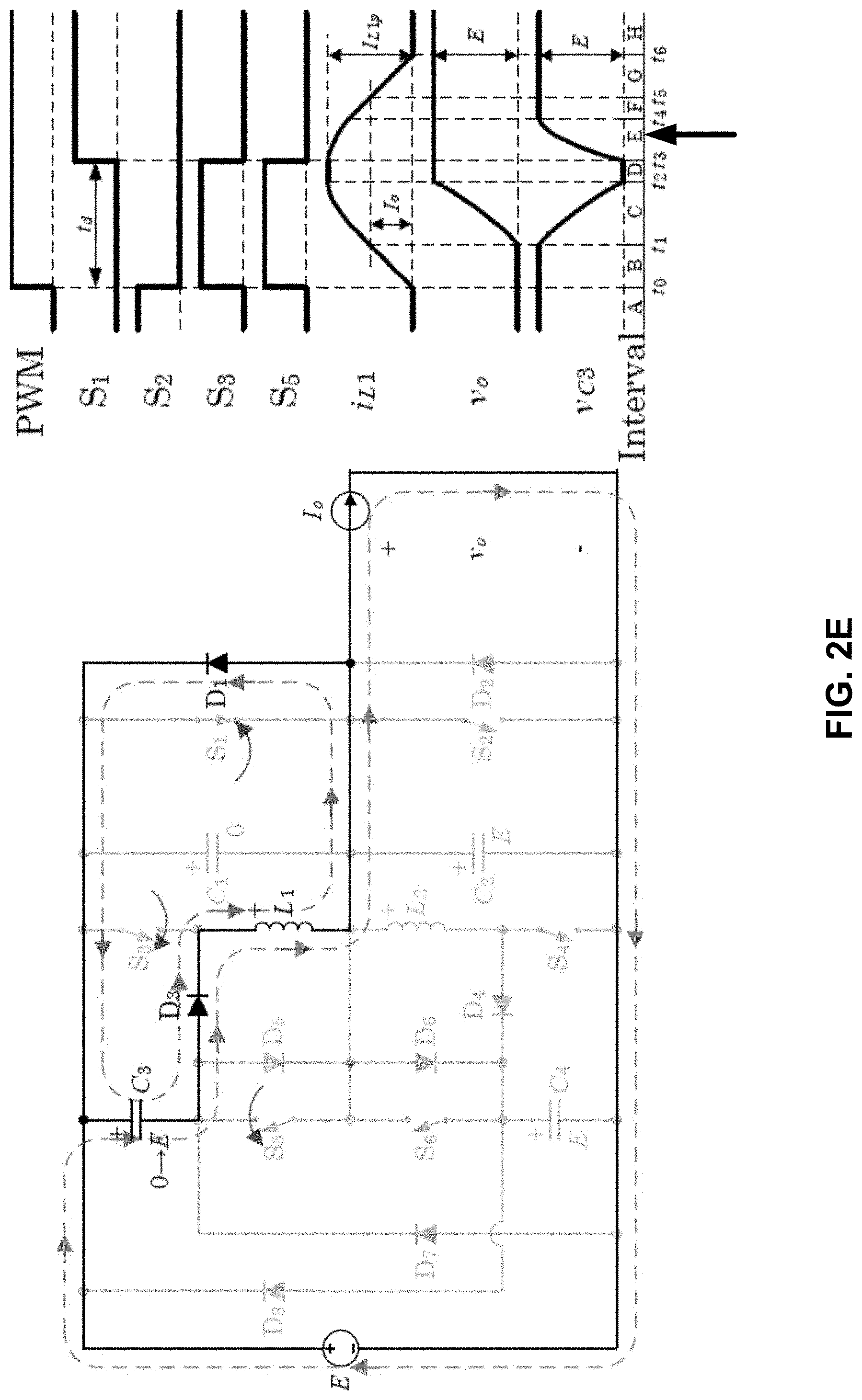

[0017] FIG. 2E is a schematic and timing diagram illustrating operation of a power inverter in a D2S commutation during time Interval E according to various aspects.

[0018] FIG. 2F is a schematic and timing diagram illustrating operation of a power inverter in a D2S commutation during time Interval F according to various aspects.

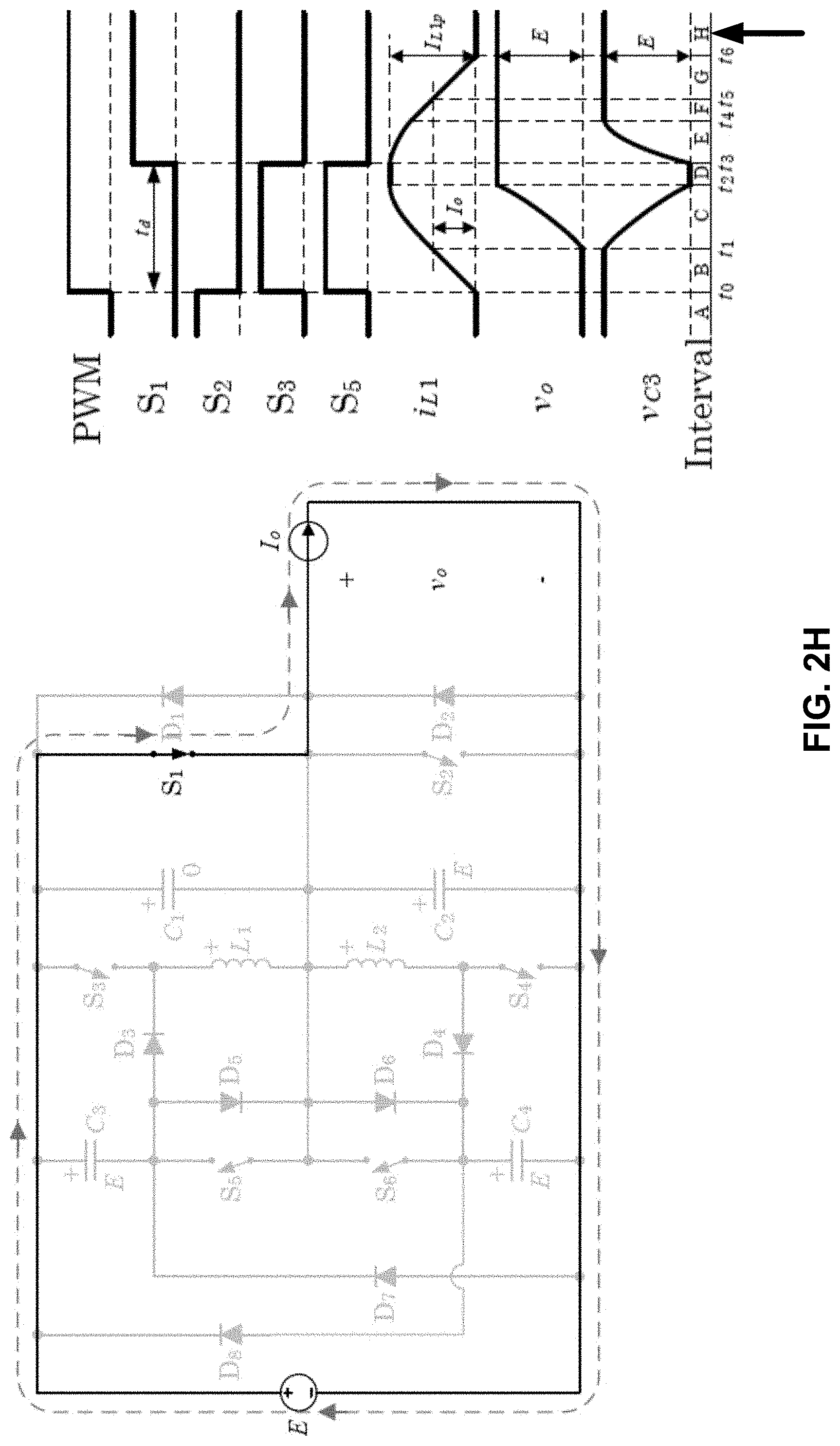

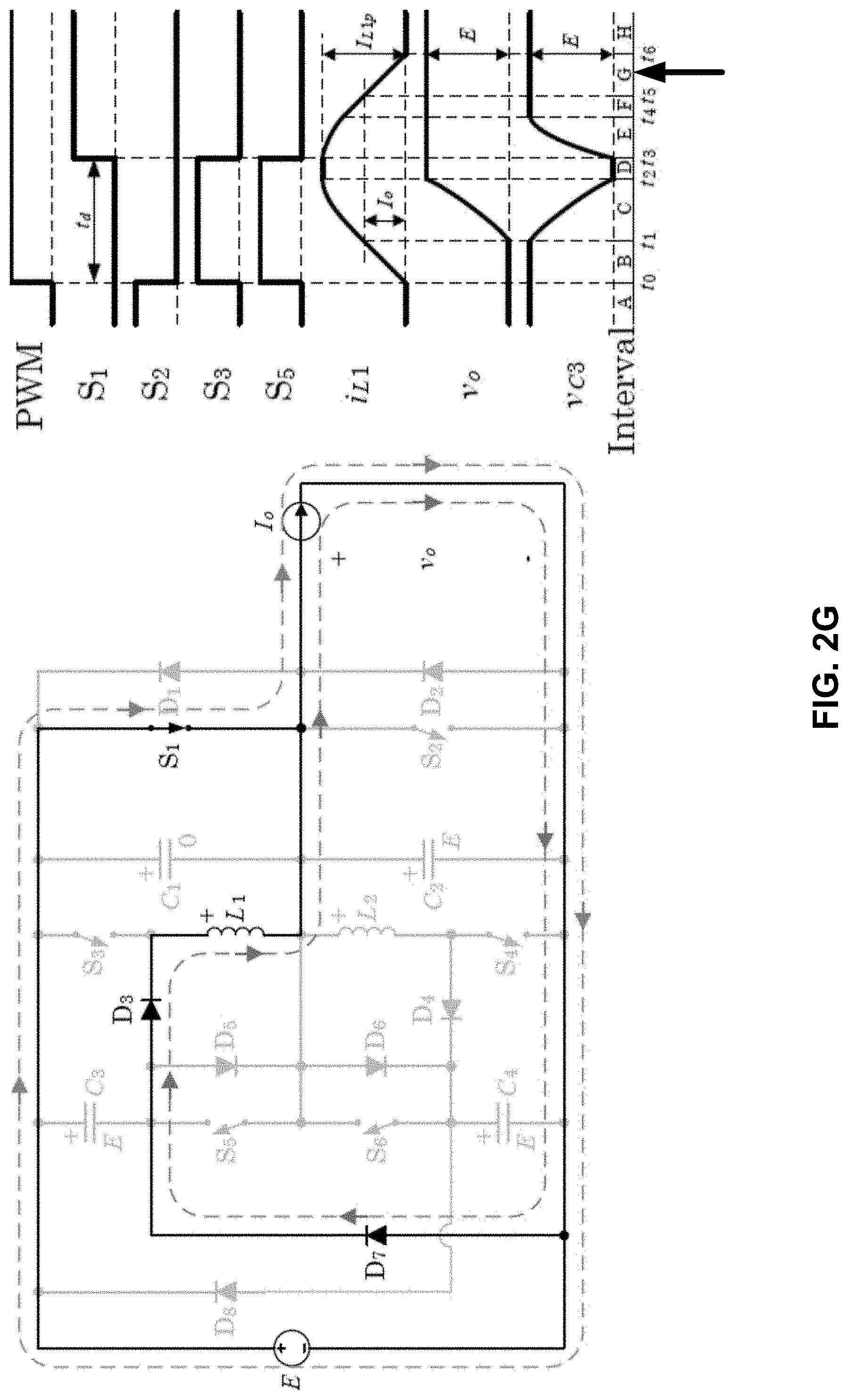

[0019] FIG. 2G is a schematic and timing diagram illustrating operation of a power inverter in a D2S commutation during time Interval G according to various aspects.

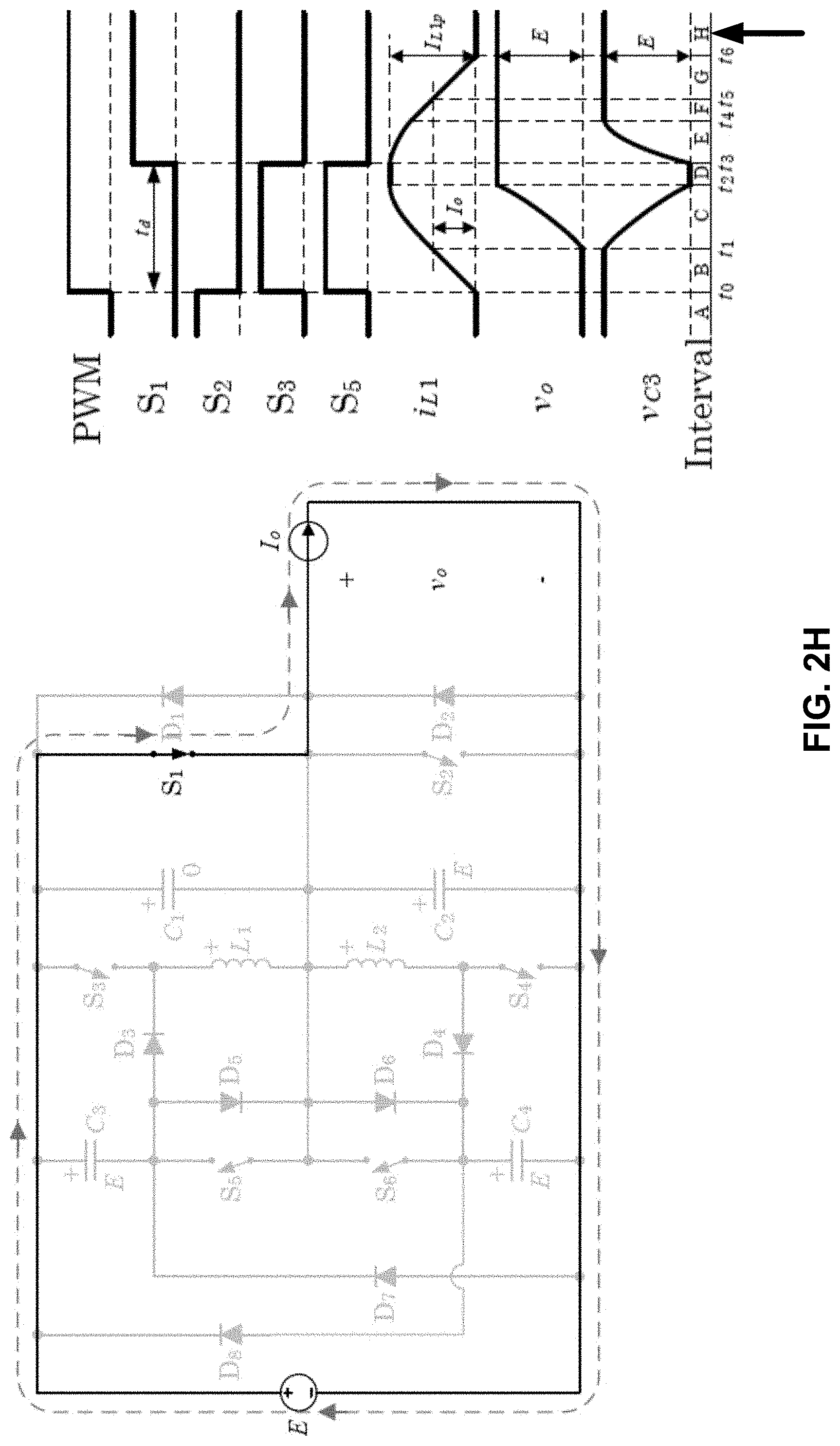

[0020] FIG. 2H is a schematic and timing diagram illustrating operation of a power inverter in a D2S commutation during time Interval H according to various aspects.

[0021] FIG. 3A is a schematic and timing diagram illustrating operation of a power inverter in a switch-to-diode (S2D) commutation during time Interval H according to various aspects.

[0022] FIG. 3B is a schematic and timing diagram illustrating operation of a power inverter in an S2D commutation during time Interval I according to various aspects.

[0023] FIG. 3C is a schematic and timing diagram illustrating operation of a power inverter in an S2D commutation during time Interval J according to various aspects.

[0024] FIG. 3D is a schematic and timing diagram illustrating operation of a power inverter in an S2D commutation during time Interval K according to various aspects.

[0025] FIG. 3E is a schematic and timing diagram illustrating operation of a power inverter in an S2D commutation during time Interval L according to various aspects.

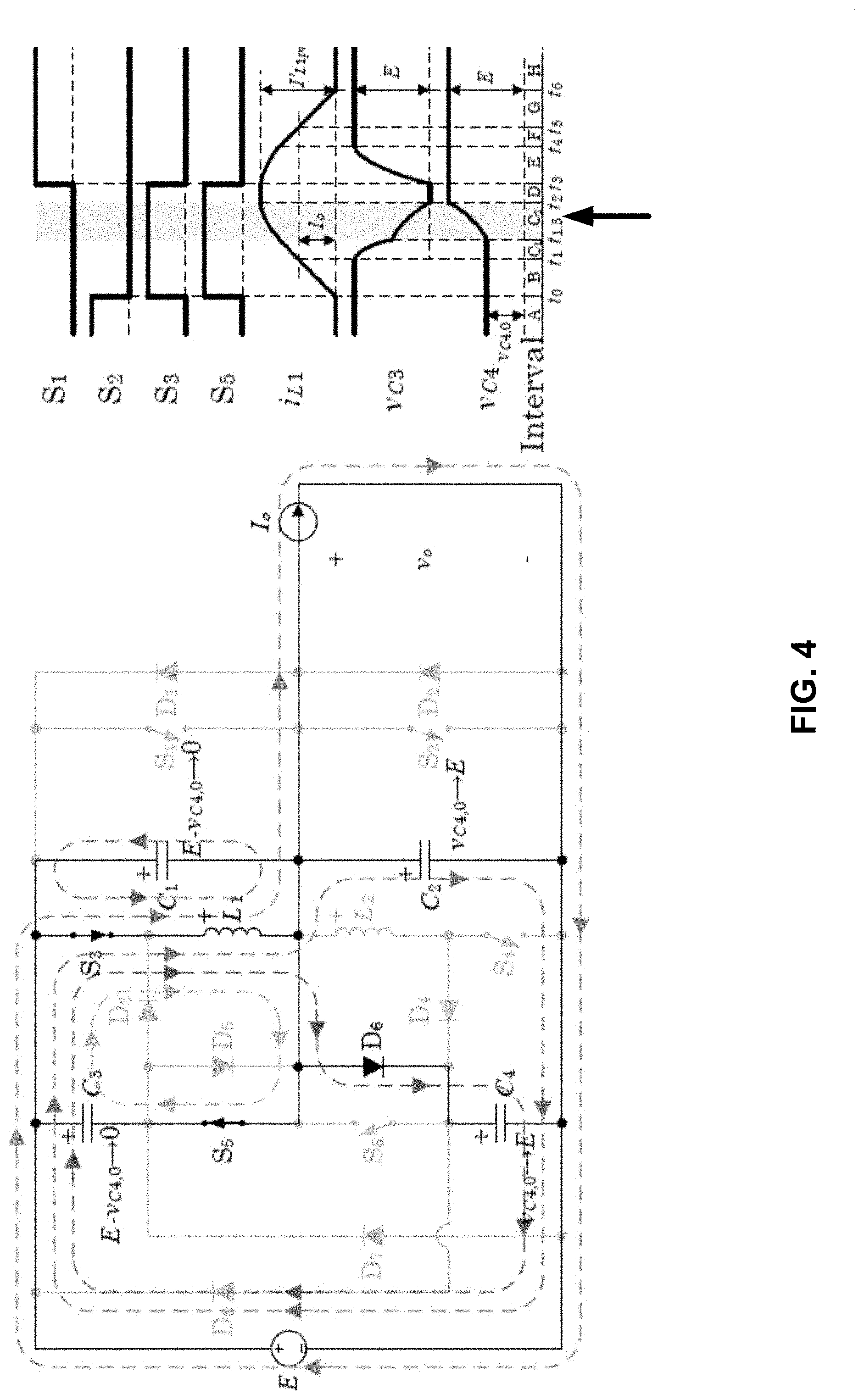

[0026] FIG. 4 is a schematic and timing diagram illustrating operation of a power inverter circuit in a D2S commutation during time Interval C.sub.2 according to various aspects.

[0027] FIG. 5A-B are state-plane plots of ARSEP and AAERP according to various aspects.

[0028] FIG. 6 is a schematic illustrating an auxiliary resonant soft-edge pole inverter circuit with metal-oxide-semiconductor field-effect transistors (MOSFETs) according to various aspects.

[0029] The attached drawings are for purposes of illustration and are not necessarily to scale.

DETAILED DESCRIPTION

[0030] In the following description, some aspects will be described in terms that would ordinarily be implemented as software programs. Those skilled in the art will readily recognize that the equivalent of such software can also be constructed in hardware, firmware, or micro-code. Because data-manipulation algorithms and systems are well known, the present description will be directed in particular to algorithms and systems forming part of, or cooperating more directly with, systems and methods described herein. Other aspects of such algorithms and systems, and hardware or software for producing and otherwise processing the signals involved therewith, not specifically shown or described herein, are selected from such systems, algorithms, components, and elements known in the art. Given the systems and methods as described herein, software not specifically shown, suggested, or described herein that is useful for implementation of any aspect is conventional and within the ordinary skill in such arts.

[0031] The present disclosure provides a soft-switching circuit to control an inverter output dv/dt with less loss, size and weight than prior-art dv/dt limiting methods, while eliminating the drawbacks of prior-art soft-switching circuits. A circuit topology is provided, referred to herein as an auxiliary resonant soft-edge pole (ARSEP) inverter that realizes soft-switching in all of the main and auxiliary switches and ensures that the inverter dv/dt is limited by circuit parameters. The second pair of resonant capacitors will always be fully pre-charged so the inverter dv/dt can be well-controlled.

[0032] One embodiment of a single-phase ARSEP inverter is shown in FIG. 1, in which auxiliary circuits are illustrated using a dashed box. Capacitors C.sub.1 and C.sub.2 are connected in parallel with the main switch modules S.sub.1/D.sub.1 and S.sub.2/D.sub.2. Auxiliary switches S.sub.3 and S.sub.4 are connected in series with inductors L.sub.1 and L.sub.2 to generate resonant current.

[0033] It is notable that S.sub.3 and S.sub.4 are unidirectional to prevent circulating current. Capacitors C.sub.3 and C.sub.4 have two roles. When S.sub.5 (S.sub.6) is on, C.sub.3 (C.sub.4) facilitates soft-switching of the main switches; when S.sub.5 (S.sub.6) is off, C.sub.3 (C.sub.4) and D.sub.3 (D.sub.4) serve as the turn-off snubber of S.sub.3 (S.sub.4). Diodes D.sub.5 and D.sub.6 enable pre-charging of C.sub.3 and C.sub.4, which prepares them for the next resonant process so that the dv/dt is well-controlled by circuit parameters. Diodes D.sub.7 and D.sub.8 direct residue energy in L.sub.1 and L.sub.2 back to the power source. It is assumed that C.sub.1=C.sub.2=C.sub.a, C.sub.3=C.sub.4=C.sub.b, and L.sub.1=L.sub.2=L. The "+" signs in FIG. 1 define the ports where positive current goes into the devices.

[0034] Output Current I.sub.o may be constant during commutation. Since inverter operation is symmetric for positive and negative output current I.sub.o, without losing generality, the circuit operation with a positive output current (I.sub.o>0) will be explained in the following subsections. The output current is generally constant during the commutation because the commutation time is relatively short.

[0035] A. Diode-to-Switch Commutation

[0036] A commutation in which the output current I.sub.o commutes from a diode to a switch is called a diode-to-switch (D2S) commutation.

[0037] Interval A (t<t.sub.0): Initially, S.sub.2 is ON while D.sub.2 actually conducts I.sub.o (FIG. 2A). Voltages .nu..sub.C1=E, .nu..sub.C2=0, and .nu..sub.C3=E due to the presence of D.sub.5. In order to demonstrate the basic operation of the circuit, it is assumed that C.sub.4 is initially pre-charged, i.e., .nu..sub.C4,0=E. The situation where .nu..sub.C4.0<E will be discussed further below.

[0038] Interval B (t.sub.0.ltoreq.t<t.sub.1): At t.sub.0, a D.sub.2S commutation is commanded. Switch S.sub.2 is turned off while S.sub.3 and S.sub.5 are turned on (FIG. 2B). Since D.sub.2 is conducting, S.sub.2 is turned off with zero-voltage-zero-current switching (ZVZCS). Since i.sub.L1(t.sub.0)=0, S.sub.3 is turned on with ZCS. Since .nu..sub.C3(t.sub.0)=E, S.sub.5 is turned on with ZVZCS. Current i.sub.L1 increases substantially linearly.

[0039] Interval C (t.sub.1.ltoreq.t<t.sub.2): At t.sub.1, i.sub.L1 increases to I.sub.o whereupon D.sub.2 stops conducting and L.sub.1 starts to resonate with C.sub.1, C.sub.2, and C.sub.3 (FIG. 2C). Voltage .nu..sub.o increases while .nu..sub.C4 stays at E since S.sub.6 is OFF.

[0040] Interval D (t.sub.2.ltoreq.t<t.sub.3): At 12, .nu..sub.o reaches E and the resonance stops (FIG. 2D). Current i.sub.L1 supplies I.sub.o. Since i.sub.L1>I.sub.o, the extra current circulates in the circuit shown in FIG. 2D. Based on simulation and experiment, the extra current circulates in the L.sub.1-D.sub.1-S.sub.3 and L.sub.1-S.sub.5-D.sub.3 loops. The current in the L.sub.1-D.sub.6-D.sub.8-S.sub.3 loop is negligible because there are two diodes in this loop. Ideally, i.sub.L1 is constant and is actually at its peak value

I L .times. 1 p = E Z 1 + I o ( 1 ) where Z 1 = L 2 .times. C a + C b ( 2 ) ##EQU00001##

[0041] Interval E (t.sub.3.ltoreq.t<t.sub.4): At t.sub.3, S.sub.1 is turned on while S.sub.3 and S.sub.5 are turned off so i.sub.L1 starts to charge C.sub.3 (FIG. 2E). Since D.sub.1 is conducting, S.sub.1 is turned on with ZVZCS. Since .nu..sub.C3(t.sub.3)=0, S.sub.3 and S.sub.5 are turned off with ZVS. The energy in L.sub.1 at t.sub.3 is

W.sub.L1=1/2L.sub.1L.sub.L1p.sup.2>1/2C.sub.bE.sup.2+1/2LI.sub.o.sup.- 2 (3)

Therefore, L.sub.1 has enough energy to charge C.sub.3 to E.

[0042] Interval F (t.sub.4.ltoreq.t<t.sub.5): At t.sub.4, C.sub.3 is charged to E whereupon D.sub.7 starts to conduct (FIG. 2F). The energy transferred to C.sub.3 is 1/2C.sub.bE.sup.2, so the energy remains in L.sub.1 is still higher than 1/2LI.sub.o.sup.2 according to (3). Therefore, i.sub.L1(t.sub.4)>I.sub.o, so D.sub.1 still conducts current. Current i.sub.L1 will decrease linearly, and the energy will flow back to the DC source.

[0043] Interval G (t.ltoreq.t<t.sub.6): At t.sub.5, i.sub.L1 decreases to I.sub.o while D.sub.1 stops conducting and S.sub.1 starts to conduct (FIG. 2G). Current i.sub.L1 decreases linearly to zero at t.sub.6, which ends the D2S commutation.

[0044] B. Switch-to-Diode Commutation

[0045] A commutation in which the output current commutes from a switch to a diode is called a switch-to-diode (S2D) commutation.

[0046] Interval H (t.sub.6.ltoreq.t<t.sub.7): Prior to an S2D commutation, the circuit is in Interval H where S.sub.1 is conducting (FIG. 3A).

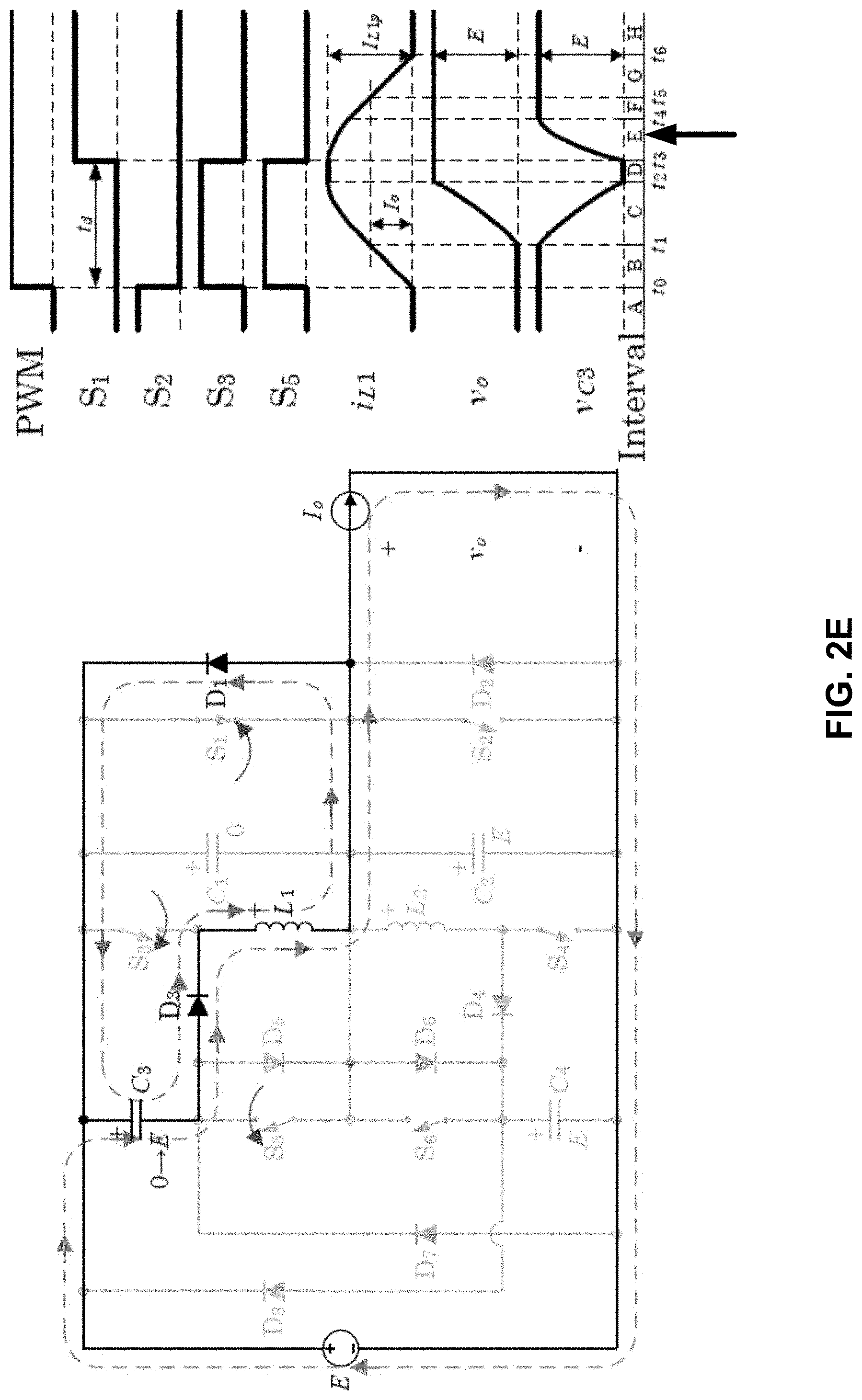

[0047] Interval I (t.sub.7.ltoreq.t<t.sub.8): At t.sub.7, an S2D commutation is commanded so S.sub.1 is turned off while S.sub.4 and S.sub.6 are turned on. Inductor L.sub.2 starts to resonate with C.sub.1, C.sub.2, and C.sub.4 (FIG. 3B). Since .nu..sub.C1(t.sub.7)=0, S.sub.1 is turned off with ZVS. Since i.sub.L2(t.sub.7)=0, S.sub.4 is turned on with ZCS. Since .nu..sub.C4(t.sub.7)=E, S.sub.6 is turned on with ZVZCS. Voltage .nu..sub.o decreases and .nu..sub.C3 stays at E since S.sub.5 is OFF.

[0048] Interval J (t.sub.8.ltoreq.t<t.sub.9): At t.sub.8, .nu..sub.o decreases to zero and i.sub.L2 starts to circulate in the circuit (FIG. 3C). According to the simulation and experiment, i.sub.L2 circulates in the L.sub.2-S.sub.4-D.sub.2 and L.sub.2-D.sub.4-S.sub.6 loops. The current in the L.sub.2-S.sub.4-D.sub.7-D.sub.5 loop is negligible. Ideally, i.sub.L2 is constant and is at its peak value

I L .times. 2 .times. p = I o 2 + ( E Z 1 ) 2 - I o ( 4 ) ##EQU00002##

[0049] Interval K (t.sub.9.ltoreq.t<t.sub.10): At t.sub.9, S.sub.2 is turned on while S.sub.4 and S.sub.6 are turned off. Current i.sub.L2 starts to charge C.sub.4 (FIG. 3D). Since D.sub.2 is conducting, S.sub.2 is turned on with ZVZCS. Since .nu..sub.C4(t.sub.9)=0, S.sub.4 and S.sub.6 are turned off with ZVS. Unlike the D2S commutation, L.sub.2 may not have sufficient energy to charge C.sub.4 up to E. Here, it is assumed that L.sub.2 has sufficient energy so .nu..sub.C4 reaches E.

[0050] Interval L (t.sub.10.ltoreq.t<t.sub.11): At t.sub.10, .nu..sub.C4 reaches E and D.sub.8 starts to conduct. Current i.sub.L2 decreases linearly to zero at t.sub.11, which completes an S2D commutation.

[0051] C. Alternative Mode of Operation

[0052] According to (4), I.sub.L2p decreases when I.sub.o increases. The energy in L.sub.2 in Interval J is

W.sub.L2=1/2LI.sub.L2p.sup.2 (5)

[0053] It may be less than 1/2C.sub.bE.sup.2, especially when I.sub.o is large or C.sub.a is much smaller than C.sub.b. Therefore, C.sub.4 may not be charged to E even absorbing all energy in L.sub.2. In this case, Interval K ends at t'.sub.10 when i.sub.L2 decreases to zero. The circuit operation will then skip Interval L and goes directly to Interval A. Then, the initial voltage of C.sub.4 for the next D.sub.2S commutation .nu..sub.C4,0 is less than E. In the next D.sub.2S commutation, C.sub.4 stays at .nu..sub.C4,0 in Interval B. Interval C will actually have two subintervals denoted by Intervals C.sub.1 and C.sub.2.

[0054] Interval C.sub.1 (t.sub.1.ltoreq.t<t.sub.1.5): This interval is similar to Interval C (FIG. 2C) except that .nu..sub.C4 stays at .nu..sub.C4,0.

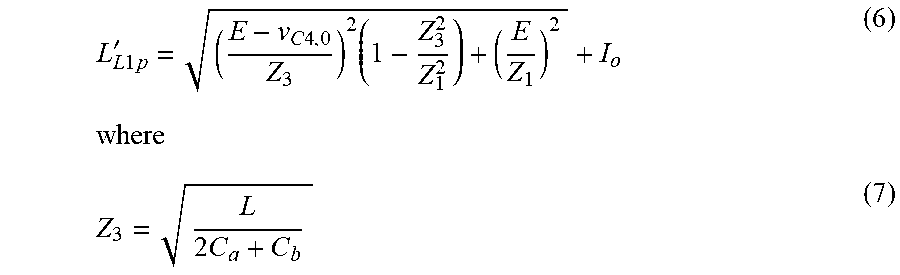

[0055] Interval C.sub.2 (t.sub.1.5.ltoreq.t<t.sub.2): At t.sub.1.5, .nu..sub.o increases to .nu..sub.C4,0 and D.sub.6 starts to conduct current (FIG. 4). Inductor L.sub.1 starts to resonate with C.sub.1-4. When .nu..sub.o increases to E, i.sub.L1 increases to its peak value

L L .times. 1 .times. p ' = ( E - v C .times. 4 , 0 Z 3 ) 2 .times. ( 1 - Z 3 2 Z 1 2 ) + ( E Z 1 ) 2 + I o ( 6 ) where Z 3 = L 2 .times. C a + C b ( 7 ) ##EQU00003##

Since Z.sub.3<Z.sub.1 and I.sub.L1P'>I.sub.L1p, according to (3), L.sub.1 has enough energy to charge C.sub.3 up to E, and the remaining i.sub.L1 is still greater than I.sub.o. This interval ends at t.sub.2 when .nu..sub.o increases to E. Voltage .nu..sub.C4 increases to E at t.sub.2, which prepares for the next S2D commutation. This pre-charging feature is not available in AAERP or DARCP, so they may result in high dv/dt.

[0056] D. Summary of Circuit Operation

[0057] The gating signals of the ARSEP inverter can be generated based on the PWM signal and a time delay t.sub.d, as shown in FIG. 3. The requirement on t.sub.d is

t d > t B + t C = I o .times. L E + t C ( 8 ) where .pi. 2 .times. .omega. 1 .ltoreq. t C < .pi. 2 .times. .omega. 3 ( 9 ) .omega. 1 = 1 L .function. ( 2 .times. C a + C b ) ( 10 ) .omega. 3 = 1 L .function. ( 2 .times. C a + 2 .times. C b ) ( 11 ) ##EQU00004##

[0058] From (8), t.sub.d is a function of I.sub.o. The first term depends on circuit parameters, and the second term is mainly determined by allowable dv/dt. Therefore, it is possible to reduce t.sub.d through the parameter design to cater to high switching frequencies.

[0059] If t.sub.d is constant, all gating signals can be generated without any sensing. Then, t.sub.d should be longer than the maximum possible voltage commutation time

t c , max = ( t B + t C ) max = I p .times. L E + .pi. 2 .times. .omega. 3 ( 12 ) ##EQU00005##

[0060] where I.sub.p is the peak output current. If I.sub.o is measured by a current sensor, a lookup table can be used to determine the required t.sub.d. Then, the duration of Intervals D and J as well as the associated losses can be reduced without affecting the dv/dt performance.

[0061] The circuit operation can be represented in a more concise way using a state-plane plot as shown in FIG. 5A. The two normalized states for the state-plane plot are defined as:

i _ = iZ 1 E , .times. v _ = v E ( 13 ) ##EQU00006##

[0062] The moving directions of the state are indicated by arrows. From t.sub.1 to t.sub.1.5, the state follows a circular arc about the center (1, .sub.o) with a rotational speed of .omega..sub.1. Similarly, from t.sub.7 to t.sub.8, the state follows another circular arc about the center (0, .sub.o) with the same speed .omega..sub.1. If .nu..sub.C4,0=E, from Point P, the state will keep following the solid circular arc to Point Q. If .nu..sub.C4,0<E, from Point P, the state follows the dashed curve and goes to Point R.

[0063] The state-plane plot of AAERP is shown in FIG. 5B. When C.sub.3 and C.sub.4 are fully charged, the state follows the solid line to Point Q. However, when C.sub.3 or C.sub.4 is lightly charged (which is likely when I.sub.o is large), the state moves from the origin to Point P and then to Point R, during which high dv/dt will occur. DARCP suffers a similar problem. ARSEP solves the problem by pre-charging C.sub.3 (C.sub.4) through diode D.sub.5 (D.sub.6) so that dv/dt can be well controlled by circuit parameters.

[0064] E. Voltage and Current Characteristics

[0065] The peak inductor current, di/dt, and dv/dt in the ARSEP inverter can be derived as:

I L , max = E Z 3 + I p = ( 1 Z _ 3 + 1 ) .times. I p ( 14 ) di L dt max = E L ( 15 ) dv o dt max = 0.8 .times. E .times. .omega. 1 .DELTA..theta. T .times. 2 .times. D .function. ( Z _ 1 ) ( 16 ) where .DELTA..theta. S2D .function. ( Z _ 1 ) = cos - 1 .times. 0.1 Z _ 1 2 + 1 - cos - 1 .times. 0.9 Z _ 1 2 + 1 ( 17 ) ##EQU00007##

is the angle being swept when .nu..sub.o decreases from 0.9 to 0.1, as shown in FIG. 5A, because dv/dt defined by the NEMA MG-1 standard is the average voltage-change rate when the voltage changes between 10% and 90%. The normalized impedance is defined as

Z _ = I p .times. Z E ( 18 ) ##EQU00008##

[0066] F. Example

TABLE-US-00001 TABLE 1 ARSEP Inverter Design Specification (Example) Item Value DC-bus voltage, E 200 V Peak output current, I.sub.p 20 A Maximum voltage edge rate, dv/dt.sub.limit 200 V/.mu.s Maximum current edge rate, di/dt.sub.limit 50 A/.mu.s Maximum inductor current, I.sub.L, limit 50 A Switching frequency, f.sub.sw 10 kHz Maximum commutation time 5 .mu.s

[0067] By way of example, given the specifications in Table 1, an ARSEP inverter may be designed as follows. Referring to (14)

Z _ 3 > I p I L , limit - I p = 0.67 ( 19 ) ##EQU00009##

[0068] It is selected that Z.sub.3=1 to limit the maximum inductor current. Based on (2) and (7), it can be concluded that Z.sub.1>Z.sub.3, so it is selected that Z.sub.1=1.1. Subsequently, according to (16) and (17)

.DELTA..theta. S2D = 0.583 .times. .times. rad ( 20 ) .omega. 1 = dv dt limit .times. .DELTA..theta. S2D 0.8 .times. E = 0.729 .times. .times. rad/.mu.s ( 21 ) ##EQU00010##

[0069] Based on Z.sub.1, Z.sub.3, and .omega..sub.1, the values of the resonant components are calculated to be L=15 .mu.H, C.sub.a=50 nF, and C.sub.b=25 nF. In order to maximize the benefit of soft switching, C.sub.b should be large enough so that S.sub.3 and S.sub.4 are over-snubbed. With this design, according to (12) and (14)-(16), t.sub.cmax=3.9 .mu.s, I.sub.Lmax=40 A, di.sub.L/dt.sub.max=13.3 A/.mu.s, and dv.sub.o/dt.sub.max=200 V/.mu.s, which satisfy NEMA standards.

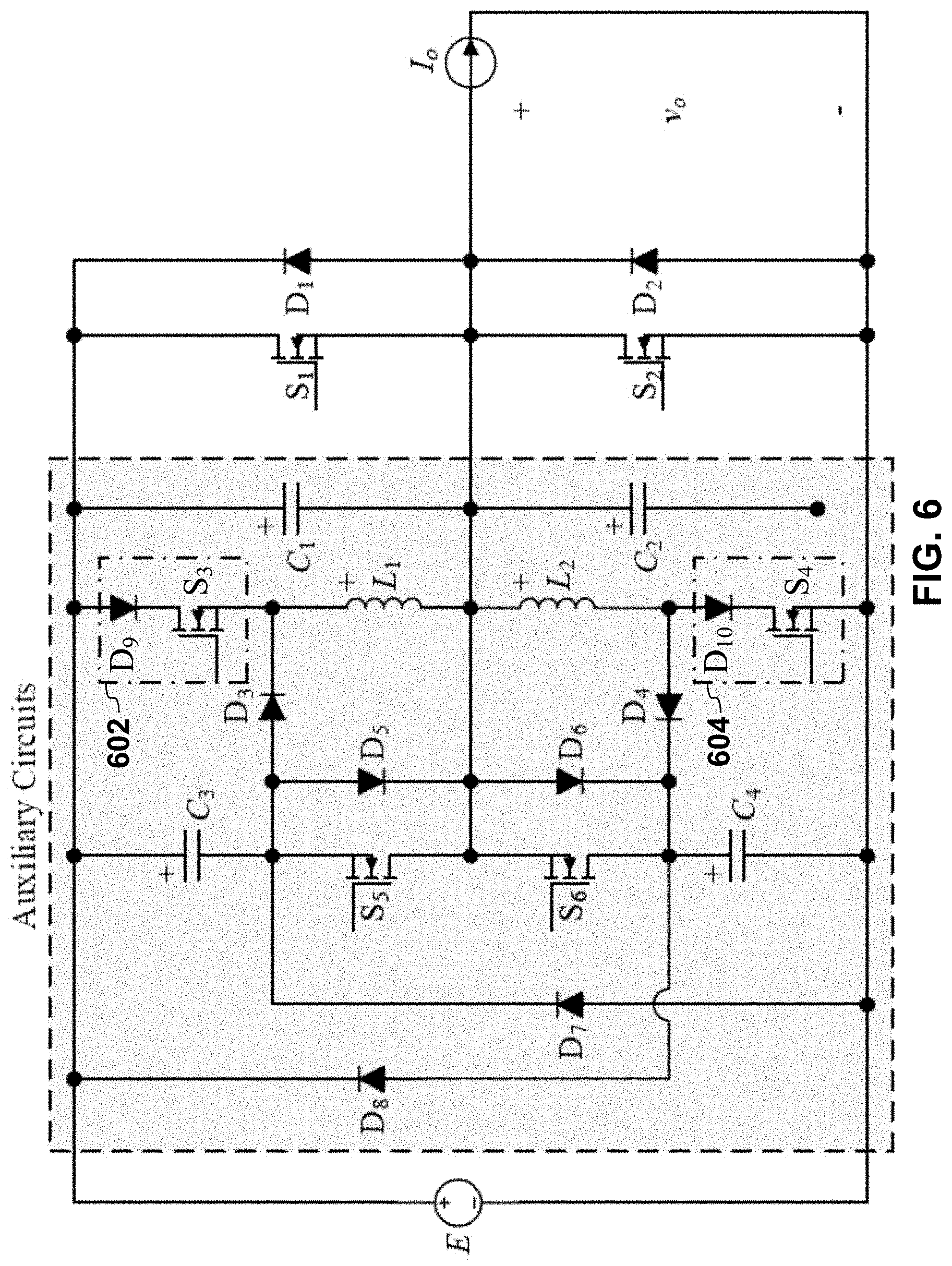

[0070] FIG. 6 illustrates an example of the circuit. The switches may be include metal-oxide-semiconductor field-effect transistors (MOSFETs) (as shown in FIG. 6), an insulated-gate bipolar junction transistor (IGBT), or other suitable transistor. When the switches labelled S.sub.3 and S.sub.4 are MOSFET devices, there are diodes in series with the MOSFET "switch" (labeled D.sub.9 and D.sub.10 in FIG. 6), since the unidirectional switches S.sub.3 and S.sub.4 should conduct current in one direction only.

[0071] The presently disclosed ARSEP circuit may be implemented to control power inverters in hybrid and electric vehicles, aircraft actuators, ship propulsion, and grid integration of renewable energy sources, or other applications.

[0072] In various aspects and examples, the auxiliary resonant soft-edge pole inverter circuit may include a first pair of capacitors (C.sub.1 and C.sub.2) in parallel with a corresponding pair of main power switching modules, each power switching module comprising a switch (S.sub.1/S.sub.2) and a diode (D.sub.1/D.sub.2) in parallel and sharing a common central node with the first pair of capacitors.

[0073] The auxiliary resonant soft-edge pole inverter circuit may further include a first pair of auxiliary switches (S.sub.3 and S.sub.4) connected in series with a first pair of inductors (L.sub.1 and L.sub.2) to generate resonant current from a DC power source (E), the first pair of inductors also sharing the common central node.

[0074] The auxiliary resonant soft-edge pole inverter circuit may further include a second pair of auxiliary switches (S.sub.5 and S.sub.6) connected in series with a second pair of capacitors (C.sub.3 and C.sub.4). The second pair of auxiliary switches (S.sub.5 and S.sub.6) also sharing the common central node, the circuit producing an alternating current output at the common central node.

[0075] The auxiliary resonant soft-edge pole inverter circuit may further include a second pair of diodes (D.sub.3 and D.sub.4) connected between the second pair of auxiliary switches (S.sub.5 and S.sub.6) and the inductors (L.sub.1 and L.sub.2).

[0076] The auxiliary resonant soft-edge pole inverter circuit may further include a third pair of diodes (D.sub.5 and D.sub.6) connected in parallel with the second set of auxiliary switches (S.sub.5 and S.sub.6) and sharing the common central node.

[0077] The auxiliary resonant soft-edge pole inverter circuit may further include a fourth pair of diodes (D.sub.7 and D.sub.9) connected between the second pair of auxiliary switches (S.sub.3 and S.sub.4) and the DC power source (E).

[0078] The auxiliary resonant soft-edge pole inverter circuit may further include a fifth pair of diodes (D.sub.9 and D.sub.10) respectively connected in series with the second pair of auxiliary switches (S3 and S4).

[0079] In various aspects and examples, the power inverter may include a plurality of capacitors comprising a first capacitor C.sub.1, a second capacitor C.sub.2, a third capacitor C.sub.3, and a fourth capacitor C.sub.4. The power inverter may further include a plurality of switches. The switches may include a first switch S.sub.1, a second switch S.sub.2, a third switch S.sub.3, a fourth switch S.sub.4, a fifth switch S.sub.5, and a sixth switch S.sub.6. The power inverter may include a plurality of inductors. The inductors may include a first inductor L.sub.1 and a second inductor L.sub.2. The power inverter may further include a plurality of diodes comprising a first diode D.sub.1 and a second diode D.sub.2.

[0080] The first switch S.sub.1 may be connected in parallel with the first capacitor C.sub.1 and the first diode D.sub.1. The second switch S.sub.2 may be connected in parallel with a second capacitor C.sub.2 and a second diode D.sub.2.

[0081] The third switch S.sub.3 may be connected in series with the first inductor L.sub.1. The fourth switch S.sub.4 may be connected in series with the second inductor L.sub.2.

[0082] The fifth switch S.sub.5 may be connected in series with the third capacitor C.sub.3 and the sixth switch S.sub.6 may be connected in series with the fourth capacitor C.sub.4.

[0083] The first switch S.sub.1, the second switch S.sub.2, the first diode D.sub.1, the second diode D.sub.2, the first capacitor C.sub.1, the second capacitor C.sub.2, the first inductor L.sub.1, the second inductor L.sub.2, and the fifth switch S.sub.5 and the sixth switch S.sub.6 may share a common node.

[0084] In some examples, the diodes further comprise third diode D.sub.3 and fourth diode D.sub.4. The third diode D.sub.3 may be connected between the third switch S.sub.3 and the first inductor L.sub.1. The fourth diode D.sub.4 may be connected between the second inductor L.sub.2 and the fourth switch S.sub.4.

[0085] In some examples, the diodes may further include a fifth diode D.sub.5 and sixth diode D.sub.6. The fifth diode D.sub.5 may be connected in parallel with the fifth switch S.sub.5 and the sixth diode D.sub.6 may be connected in parallel with the sixth switch S.sub.6. Further, the fifth diode D.sub.5 and the sixth diode D.sub.6 may both connect to the common node.

[0086] In some examples, the diodes may include a seventh diode D.sub.7 and an eight diode d.sub.8. The seventh diode D.sub.7 may be connected between the fourth switch S.sub.4 and a DC power source E. The eight diode D.sub.8 may be connected between the third switch S.sub.3 and the DC power source E.

[0087] In some examples, the third switch S.sub.3 and the fourth switch S.sub.4 may include MOSFETs. In such examples, the diodes may further include a diode D.sub.9 and a diode D.sub.10. The diode D.sub.9 may be connected in series with the third switch in S.sub.3. The diode D.sub.10 may be connected in series with the fourth switch in S.sub.4. Alternatively or in addition, the power inverter may include switch circuitry (identified as 602 and 604 in FIG. 6). The switch circuitry may include a series connection of a diode and a MOSFET.

[0088] The invention is inclusive of combinations of the aspects described herein. References to "a particular aspect" and the like refer to features that are present in at least one aspect of the invention. Separate references to "an aspect" (or "embodiment") or "particular aspects" or the like do not necessarily refer to the same aspect or aspects; however, such aspects are not mutually exclusive, unless so indicated or as are readily apparent to one of skill in the art. The use of singular or plural in referring to "method" or "methods" and the like is not limiting. The word "or" is used in this disclosure in a non-exclusive sense, unless otherwise explicitly noted.

[0089] The invention has been described in detail with particular reference to certain preferred aspects thereof, but it will be understood that variations, combinations, and modifications can be effected by a person of ordinary skill in the art within the spirit and scope of the invention.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

D00009

D00010

D00011

D00012

D00013

D00014

D00015

D00016

D00017

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.