Switched Capacitor Arrangement For Tuning A Differential Circuit

SJOLAND; Henrik ; et al.

U.S. patent application number 17/166112 was filed with the patent office on 2021-05-27 for switched capacitor arrangement for tuning a differential circuit. The applicant listed for this patent is TELEFONAKTIEBOLAGET LM ERICSSON (PUBL). Invention is credited to Torbjorn SANDSTROM, Henrik SJOLAND.

| Application Number | 20210159854 17/166112 |

| Document ID | / |

| Family ID | 1000005374556 |

| Filed Date | 2021-05-27 |

View All Diagrams

| United States Patent Application | 20210159854 |

| Kind Code | A1 |

| SJOLAND; Henrik ; et al. | May 27, 2021 |

SWITCHED CAPACITOR ARRANGEMENT FOR TUNING A DIFFERENTIAL CIRCUIT

Abstract

A switched capacitor arrangement for tuning a differential circuit is disclosed. The switched capacitor arrangement comprises a first node, a second node and a third node. The switched capacitor arrangement further comprises a first capacitor (C1) coupled between the first node and the second node, a second capacitor (C2) coupled between the second node and the third node, and a first switch branch comprising a first switch (S 1) coupled between the second node and a signal ground node. The first switch (S 1) has an on state and an off state. The first node and third node are configured to be connected to respective differential nodes (Vtank, -Vtank) of the differential circuit. The switched capacitor arrangement is configured to tune the differential circuit by controlling the state of the first switch.

| Inventors: | SJOLAND; Henrik; (Lund, SE) ; SANDSTROM; Torbjorn; (Malmo, SE) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 1000005374556 | ||||||||||

| Appl. No.: | 17/166112 | ||||||||||

| Filed: | February 3, 2021 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 16339661 | Apr 4, 2019 | 10951165 | ||

| PCT/EP2016/074015 | Oct 7, 2016 | |||

| 17166112 | ||||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H03B 5/1228 20130101; H03B 2200/005 20130101; H03B 5/1265 20130101; H03B 5/1215 20130101 |

| International Class: | H03B 5/12 20060101 H03B005/12 |

Claims

1. A differential circuit, comprising a switched capacitor arrangement for tuning the differential circuit comprising: a first node, a second node and a third node; a first capacitor directly connected to the first node with a first terminal and directly connected to the second node with a second terminal; a second capacitor directly connected to the third node with a first terminal and directly connected to the second node with a second terminal; and a first switch branch comprising a first switch coupled between the second node and a signal ground node; wherein the first switch has an on state and an off state; the first node and third node are connected to respective differential nodes (Vtank, -Vtank) of the differential circuit; and the switched capacitor arrangement is configured to tune the differential circuit by controlling the state of the first switch.

2. The differential circuit according to claim 1, wherein the first switch branch further comprises a third capacitor coupled in series with the first switch.

3. The differential circuit according to claim 1, wherein the switched-capacitor arrangement further comprises a plurality of switch branches coupled between the second node and the signal ground node, wherein each switch branch comprises a capacitor coupled in series with a switch.

4. The differential circuit according to claim 1, wherein the first capacitor and the second capacitor have the same capacitance.

5. The differential circuit according to claim 1, wherein the first switch is implemented by metal oxide semiconductor, MOS, transistor.

6. The differential circuit according to claim 1, wherein the differential circuit is a differential digitally controlled oscillator or a digital to time converter.

7. An electronic device comprising a differential circuit according to claim 1.

8. The electronic device according to claim 7, wherein the electronic device is a wireless communication device, a base station, a mobile terminal, a wireless transceiver, or a frequency synthesizer.

Description

TECHNICAL FIELD

[0001] Embodiments herein relate to a switched capacitor arrangement for tuning a differential circuit. In particular, they relate to digital frequency tuning of a differential Digitally Controlled Oscillator, delay tuning of a digital to time converter, and frequency tuning of a differential digitally controlled filter in an electronic device, such as a frequency synthesiser, a transceiver, a wireless communication device, a base station, a mobile terminal.

BACKGROUND

[0002] Wireless communication systems usually comprise transceivers which comprise receivers and transmitters. The transmitters typically up-convert baseband signals to radio frequency (RF) signals for transmission, and the receivers down-convert received RF signals to baseband signals for processing. Such frequency conversion requires producing reliable mixing frequency signals, typically referred to as local oscillator (LO) signals, for use in an RF integrated circuit in a wireless communication device. Phase locked loops (PLLs) in frequency synthesizers are often used to provide such mixing frequency signals.

[0003] There is a strong trend towards more digital architectures in frequency synthesizers for local oscillator generation in transceivers. Some benefits are increased opportunities to use adaptive digital filters to obtain faster frequency changes without compromising signal quality, and possibility to use digital signal processing to mitigate effects of various impairments and disturbances. For high performance applications like transceivers in cellular communication systems, where low phase noise is required, all-digital phase locked loop (ADPLL) may be used.

[0004] A key building block in an ADPLL is the digitally controlled oscillator (DCO). For high performance applications, oscillators with inductor and capacitor (LC) tank are used, normally of a differential type as differential signals are preferred in integrated circuits. The key difference between a DCO and a voltage controlled oscillator (VCO) that is used in conventional PLLs is that the DCO has a digital frequency control input rather than a frequency control voltage input. This digital input will control the frequency by changing the effective capacitance in the LC tank. This is achieved by an arrangement of digitally controlled switch transistors selectively connecting a bank of capacitors to the tank. When a capacitor is connected to the oscillator tank, the frequency will take a step down. Under operation these steps must be very small not to degrade the signal quality. The very small frequency step corresponds to an extremely small capacitance being switched, for example 1 aF. Further it must be possible to cover a large frequency range without an unpractically large number of steps. Several capacitor tuning banks are therefore normally used, with different ranges and resolution. FIG. 1 shows one example of a prior art DCO 100. The DCO 100 comprises a negative resistance circuit 110 which comprises a cross coupled differential pair of transistors to produce a negative resistance to compensate LC tank losses for generating the oscillation. The LC tank comprises inductor L.sub.tank and several banks of capacitors 120, 130, 140 for fine tuning, medium tuning and coarse tuning of the frequency controlled by respective digital control words F0, . . . Fn1, M0, . . . Mn2, C0, . . . Cn3.

[0005] Obtaining fine enough frequency resolution in the capacitor bank for frequency fine tuning is a challenge. Typically the required capacitance step is smaller than the smallest capacitor in a process design kit. To obtain such small capacitance steps the effective capacitance step seen at the LC tank must therefore be much smaller than the actual capacitance that is switched. This may be achieved in different ways, for example using a capacitive voltage divider before a switched capacitor to reduce the signal energy inside it. With less energy it will provide less effective capacitance. A problem is that such voltage dividers will use large sized components to sufficiently attenuate the signal, i.e. large capacitors are required to achieve high enough attenuation.

[0006] There is also a technique using tunable capacitive source degeneration for fine frequency tuning as discussed in L. Fanori etc. "3.3 GHz DCO with a frequency resolution of 150 Hz for All-digital PLL", IEEE ISSCC, pp. 48-49, 2010. In this solution, a bank of fine tuning capacitors is coupled between the source terminals of the differential pair transistors in the DCO. Although this technique provides attenuated voltage for the fine tuning capacitors, it reduces the transconductance of the differential pair transistors and thereby also the important loop gain of the DCO. Further, the frequency tuning sensitivity is non-linear and dependent on the transistor parameters.

SUMMARY

[0007] It is an object of embodiments herein to provide an improved circuit arrangement for digitally fine tuning of a differential circuit.

[0008] According to one aspect of embodiments herein, the object is achieved by a switched capacitor arrangement for tuning a differential circuit.

[0009] According to a first embodiment, the switched capacitor arrangement comprises a first node, a second node and a third node. The switched capacitor arrangement further comprises a first capacitor coupled between the first node and the second node, a second capacitor coupled between the second node and the third node, a first switch branch comprising a first switch coupled between the second node and a signal ground node. The first switch has an on state and an off state. The first node and third node are configured to be connected to respective differential nodes of the differential circuit. The switched capacitor arrangement is configured to tune the differential circuit by controlling the state of the first switch.

[0010] According to a second embodiment, the switched capacitor arrangement comprises a first capacitor branch. The first capacitor branch comprises a first node, a second node and a third node. The first capacitor branch further comprises a first capacitor coupled between the first node and the second node, a second capacitor coupled between the second node and the third node. The switched capacitor arrangement further comprises a second capacitor branch. The second capacitor branch comprises a first node, a second node and a third node. The second capacitor branch further comprises a third capacitor coupled between the first node and the second node, a fourth capacitor coupled between the second node and the third node. The switched capacitor arrangement further comprises a first switch branch comprising a first switch coupled between the second nodes of the first and second capacitor branches. The first switch has an on state and an off state. The first nodes and the third nodes of the first and second capacitor branches are configured to be connected to respective differential nodes of the differential circuit. The switched capacitor arrangement is configured to tune the differential circuit by controlling the state of the first switch.

[0011] The embodiments herein are based on using capacitive voltage dividers across a differential resonator of a differential circuit. Some advantages with the switched capacitor arrangements according to the embodiments herein are:

[0012] If two capacitors of equal size or nearly equal size are series connected between the differential nodes with positive and negative voltages of the resonator, the middle node will have a voltage close to zero. Therefore small signal voltages can be achieved without the need for large capacitor ratios.

[0013] The requirements on the switch may be considerably relaxed compared to switching a capacitance in a regular structure, i.e. direct connection of a switched capacitor across the differential circuit nodes, where the switch is in series with the capacitor. Since the voltage on the middle node is close to zero, the switch connected to the middle node according to embodiments herein will have considerable much less signal current flow in its on-state compared to the switch in the regular structure. The on-resistance may thus be higher in the switch for the same differential capacitor quality factor.

[0014] For the second embodiment, the switched capacitor arrangement is coupled to respective differential nodes of a differential circuit, and the switch is coupled between the middle nodes of two series connected capacitors. In this way, the switched capacitor arrangement is placed across the differential nodes of the differential circuit, i.e. not using any other nodes of the differential circuit which would introduce dependence on transistor parameters.

[0015] The tuning of a differential circuit, e.g. the frequency tuning of a DCO, may be controlled with high resolution, while still using a limited range of capacitor sizes, i.e. not smaller than existing capacitors in a design-kit, and not very large ones to save chip area.

[0016] Therefore embodiments herein provide improved circuit arrangements for digitally fine tuning of a differential circuit.

BRIEF DESCRIPTION OF THE DRAWINGS

[0017] Examples of embodiments herein are described in more detail with reference to attached drawings in which:

[0018] FIG. 1 is a schematic block view illustrating a basic structure of a DCO;

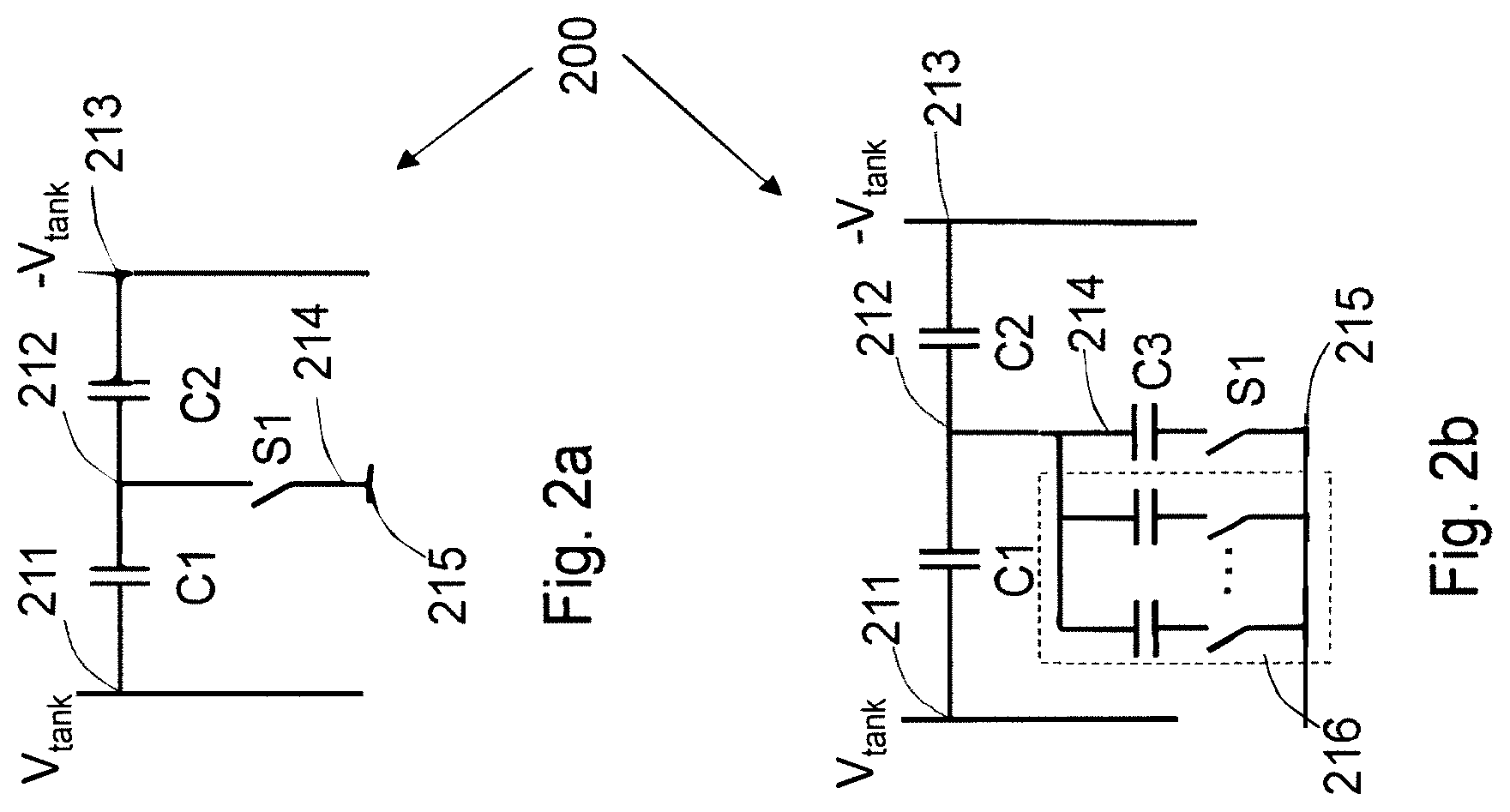

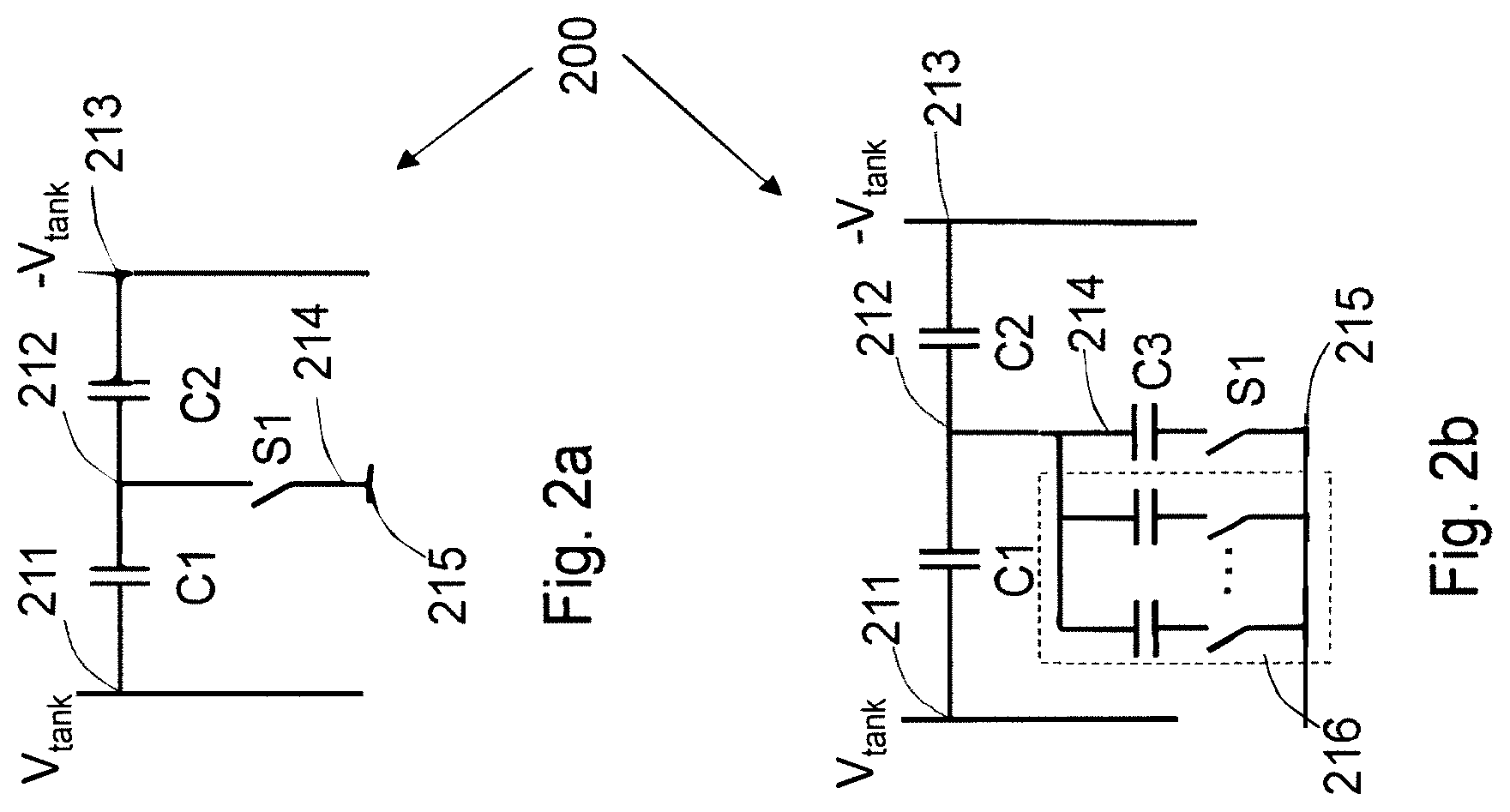

[0019] FIGS. 2a and 2b are schematic views illustrating switched capacitor arrangements according to embodiments herein;

[0020] FIG. 2c are waveforms showing the fundamental and the 2.sup.nd harmonic waveforms;

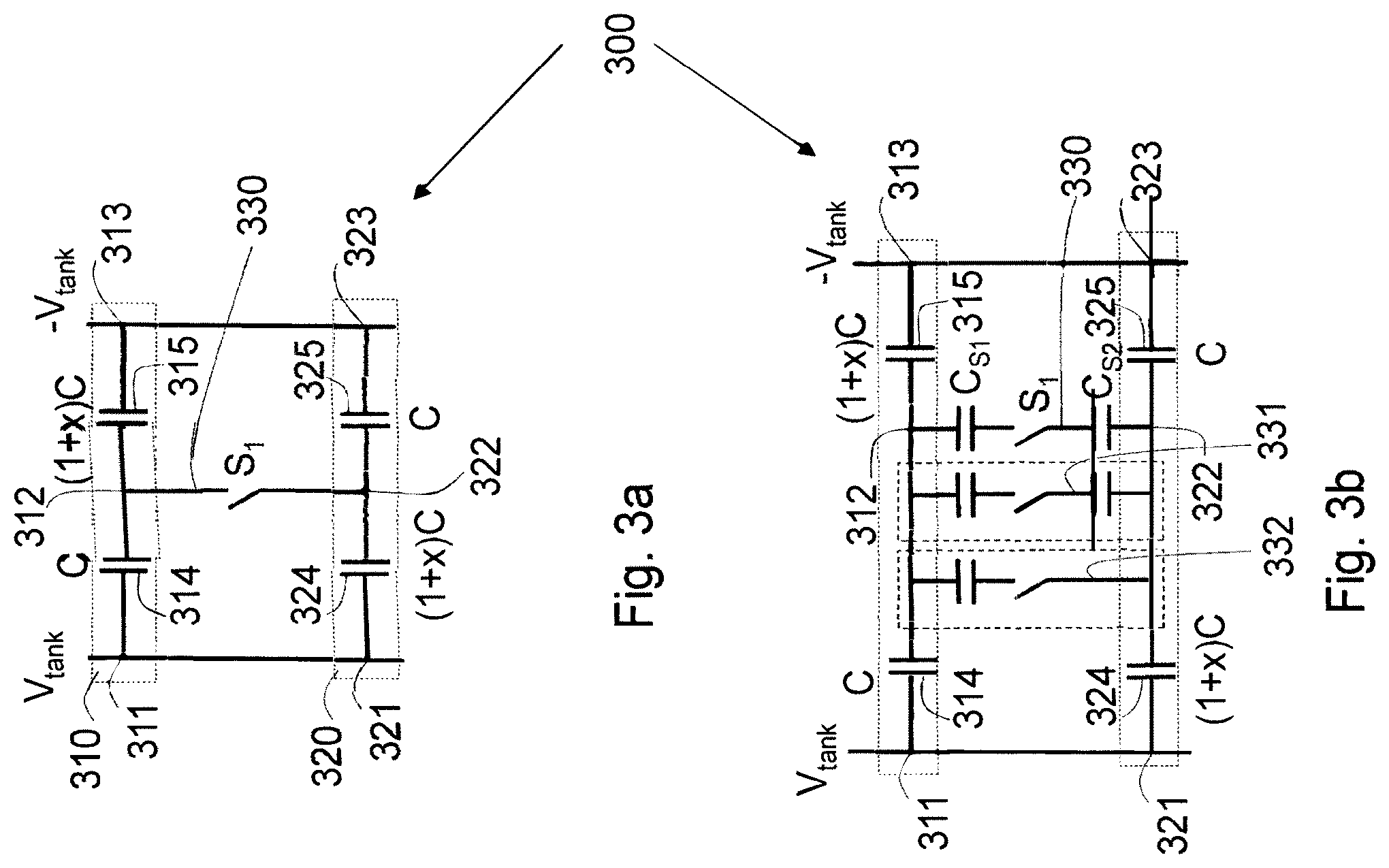

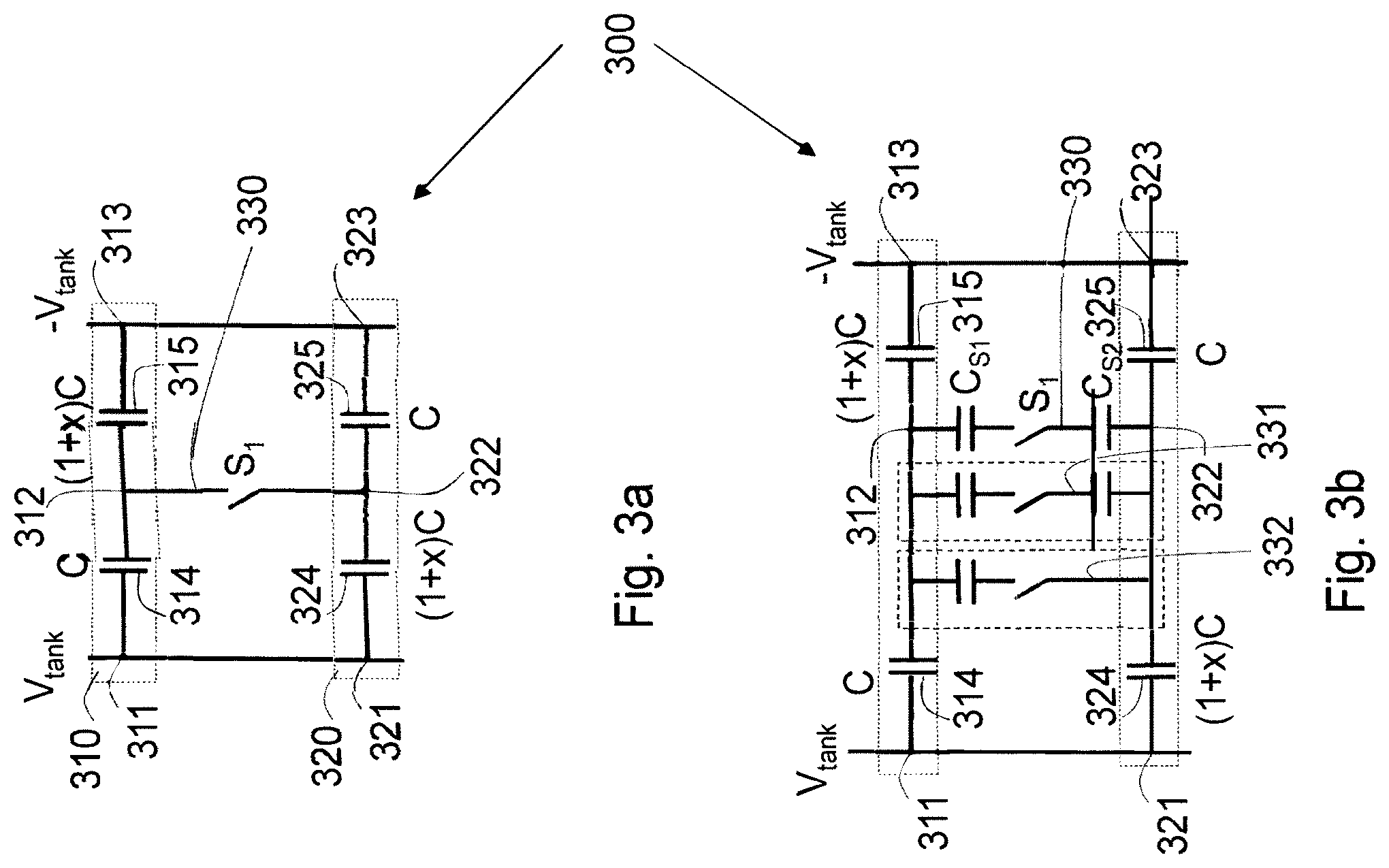

[0021] FIGS. 3a and 3b are schematic views illustrating switched capacitor arrangements according to embodiments herein; and

[0022] FIG. 4 is a schematic block view illustrating a differential circuit in which embodiments herein may be implemented.

[0023] FIG. 5 is a block diagram illustrating an electronic device in which embodiments herein may be implemented.

DETAILED DESCRIPTION

[0024] To achieve a small capacitance control step in a circuit, e.g. a DCO, while still using a limited range of capacitor sizes, i.e. not smaller than existing capacitors in a design-kit, and not very large ones to save chip area, a capacitive voltage divider across differential nodes of a differential circuit may be used according to embodiments herein. In this way small signal voltages can be achieved without the need for large capacitor ratios. If two capacitors of equal size or nearly equal size are series connected between the positive and negative voltages of the differential circuit, the middle node will have a signal voltage close to zero. This may be exploited in different ways which lead to different embodiments.

[0025] FIG. 2a shows a switched capacitor arrangement 200 according to one embodiment for tuning a differential circuit, e.g. tuning the frequency of a DCO. The switched capacitor arrangement 200 comprises a first node 211, a second node 212 and a third node 213. The switched capacitor arrangement 200 further comprises a first capacitor C1 coupled between the first node 211 and the second node 212, a second capacitor C2 coupled between the second node 212 and the third node 213, and a first switch branch comprising a first switch S1 coupled between the second node 212 and a signal ground node. The first switch S1 has an on state and an off state. The first node 211 and third node 213 are configured to be connected to respective differential nodes Vtank, -Vtank of the differential circuit and the switched capacitor arrangement 200 is configured to tune the differential circuit by controlling the state of the first switch S1.

[0026] This tuning technique has an advantage that equal size capacitors may be used, i.e. the first capacitor C1 and the second capacitor C2 may have same capacitance. Therefore better matching may be achieved. This technique relies on even order harmonic contents of the waveforms from the differential circuit for the tuning mechanism. Having equal sized capacitors, only common-mode voltages will be present at the middle node 212. With the first switch S1 open, the voltage at the middle node 212 will be dominated by the second order harmonic. The effective capacitance will be the series connection of the two capacitors C1 and C2, i.e. equal to C1/2. When the first switch S1 in FIG. 2a is closed, the voltage Vc1 and Vc2 across the capacitors C1 and C2 will no longer be equal, due to the second order harmonic voltage. This is shown in FIG. 2c, where the fundamental waveforms for the differential nodes 211, 213 and the 2.sup.nd harmonic waveform at the middle node 212 are shown.

[0027] When the switch is closed the second harmonic common mode voltage will be added to the capacitor voltages. As can be seen in FIG. 2c, the second harmonic will be "in phase" with the positive oscillator fundamental voltage in the first half period t1. The signal voltage across the first capacitor C1 will then be reduced, resulting in less stored energy. The voltage across the second capacitor C2 will instead become larger, with increased stored energy. In the second half period t2, it is the other way around, with the first capacitor C1 storing more energy, and the second capacitor C2 less. Due to the quadratic dependence of capacitive energy to voltage, the increase of energy in one capacitance will be larger than the corresponding decrease of the other, resulting in a total net increase of energy in the capacitors when the first switch S1 is closed. As described in J. Groszkowski, "The interdependence of frequency variation and harmonic content, and the problem of constant-frequency oscillators", Proc. of the IRE, vol. 21, pp. 958-981, 1933, when the energy is increased in the capacitance of an LC-resonator due to harmonics, the energy must be increased in the inductance to maintain the balance, and this will cause the frequency of oscillation to reduce. This is usually referred to as the Groszkowski effect, i.e. a shift in oscillation frequency induced by higher harmonics current flowing into the LC tank of a harmonic oscillator. The tuning mechanism may thus be explained by second order harmonic signal being switched into a programmable fraction of the capacitive part of the resonator, which due to the Groszkowski effect causes a reduction of the oscillation frequency.

[0028] According to some embodiments, the first switch branch may further comprise a third capacitor C3 coupled in series with the first switch S1. This is shown in FIG. 2b. When the first switch S1 in FIG. 2b is closed, the second harmonic current will flow in C3 as well as C1 and C2. The amount of second harmonic current in C1 and C2 will be proportional to C3 for small values of C3. This provides a new degree of freedom in setting the tuning sensitivity.

[0029] According to some embodiments, the switched capacitor arrangement 200 may further comprise a plurality of switch branches coupled between the second node 212 and the signal ground node, wherein each switch branch comprises a capacitor coupled in series with a switch, as shown in FIG. 2b dotted line box. The capacitor in each switch branch may have same capacitance or some capacitors in some switch branches may have different capacitance. This embodiment may provide different tuning capacitances and resolutions depending on different combinations of the capacitors in the plurality of switch branches

[0030] In the following, embodiments using two capacitors of nearly equal size series connected between the positive and negative voltages of the differential circuit as capacitive voltage divider will be described.

[0031] FIG. 3a shows a switched capacitor arrangement 300 according to one embodiment for tuning a differential circuit, e.g. tuning the frequency of a DCO. The switched capacitor arrangement 300 comprises a first capacitor branch 310. The first capacitor branch 310 comprises a first node 311, a second node 312 and a third node 313. The first capacitor branch 310 further comprises a first capacitor 314 coupled between the first node 311 and the second node 312, a second capacitor 315 coupled between the second node 312 and the third node 313.

[0032] The switched capacitor arrangement 300 further comprises a second capacitor branch 320. The second capacitor branch 320 comprises a first node 321, a second node 322 and a third node 323. The second capacitor branch 320 further comprises a third capacitor 324 coupled between the first node 321 and the second node 322, a fourth capacitor 325 coupled between the second node 322 and the third node 323.

[0033] The switched capacitor arrangement 300 further comprises a first switch branch comprising a first switch S1 coupled between the second nodes 312, 322 of the first and second capacitor branches.

[0034] The first switch S1 has an on state and an off state. The first nodes 311, 321 and the third nodes 313, 323 of the first and second capacitor branches are configured to be connected to respective differential nodes of the differential circuit. The switched capacitor arrangement 300 is configured to tune the differential circuit by controlling the state of the first switch S1.

[0035] According to some embodiments, the first and second capacitor branches 310, 320 may have same capacitance. A capacitance ratio of the first capacitor to the second capacitor may be 1/(1+x), and a capacitance ratio of the third capacitor to the fourth capacitor may be (1+x), where 0<x<1. That is if the first capacitor 314 has capacitance of C, the second capacitor 315 may have capacitance of (1+x)C, then the third capacitor 324 may have capacitance of (1+x)C, and the fourth capacitor 325 may have capacitance of C, or other way around.

[0036] When the first switch S1 is on, the capacitance across the differential nodes is

Con = 1 2 [ C + ( 1 + x ) C ] = C ( 1 + x 2 ) ( 1 ) ##EQU00001##

[0037] When the first switch S1 is off, the capacitance across the differential nodes is

C off = 2 C ( 1 + x ) C C ( 1 + x ) + C = C 2 + 2 x 2 + x = C ( 1 + x 2 - x 2 2 ( 2 + x ) ) ( 2 ) ##EQU00002##

[0038] So the capacitance difference is

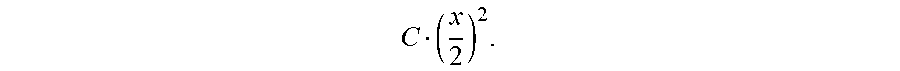

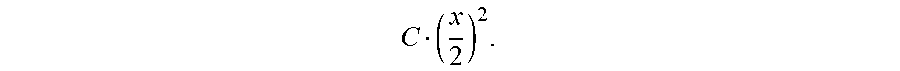

C on - C off = C x 2 2 ( 2 + x ) .apprxeq. C ( x 2 ) 2 ( 3 ) ##EQU00003##

[0039] That is the difference in differential tank capacitance between the switch being on and off becomes approximately

C ( x 2 ) 2 . ##EQU00004##

Different tuning sensitivities may be obtained by different values of C and x.

[0040] According to some embodiments, the first switch branch may further comprise two capacitors Cs.sub.1, Cs.sub.2 in series with the first switch S1. As shown in FIG. 3b, one capacitor Cs.sub.1 may be coupled between the second node 312 of the first capacitor branch 310 and the first switch S1, and another capacitor Cs.sub.2 may be coupled between the second node 322 of the second capacitor branch 320 and the first switch S1.

[0041] According to some embodiments, the first switch branch may further comprise a capacitor Cs in series with the first switch S1. That is the two capacitors Cs.sub.1, Cs.sub.2 shown in FIG. 3b may be combined as one capacitor Cs and connected in series with the first switch S1.

[0042] In these embodiments, when the first switch S1 is off, the capacitance across the differential nodes is the same as in equation (2).

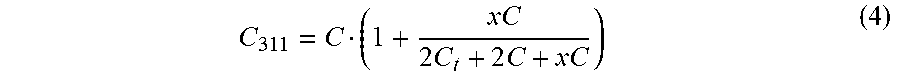

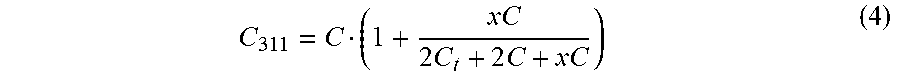

[0043] When the first switch S1 is on, assume Cs has capacitance of Ct, or each of the two capacitors Cs.sub.1, Cs.sub.2 has capacitance of 2Ct, the capacitance to signal ground of the first capacitor branch 310 at node 311 is

C 3 1 1 = C ( 1 + xC 2 C t + 2 C + xC ) ( 4 ) ##EQU00005##

[0044] The capacitance to signal ground of the second capacitor branch 320 at node 321 is

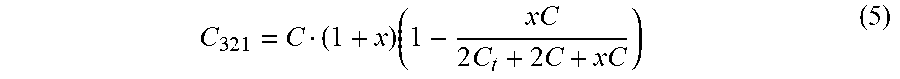

C 3 2 1 = C ( 1 + x ) ( 1 - xC 2 C t + 2 C + xC ) ( 5 ) ##EQU00006##

[0045] So the capacitance across the differential nodes is

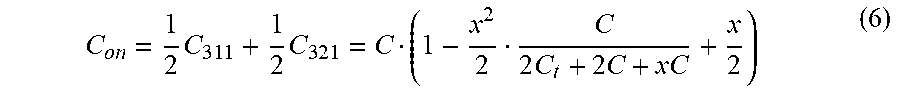

C on = 1 2 C 3 1 1 + 1 2 C 3 2 1 = C ( 1 - x 2 2 C 2 C t + 2 C + x C + x 2 ) ( 6 ) ##EQU00007##

[0046] So the capacitance difference is

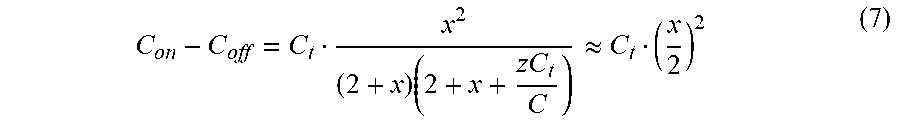

C on - C off = C t x 2 ( 2 + x ) ( 2 + x + zC t C ) .apprxeq. C t ( x 2 ) 2 ( 7 ) ##EQU00008##

[0047] It can be seen that the effective switched capacitance has been reduced by a factor of x.sup.2/4, compared to direct connection of a switched capacitor with capacitance Ct at the differential nodes. By making x small, very small capacitance steps may be achieved. Therefore tuning resolution may be increased and tuning sensitivity may be reduced without using very small capacitors. For example, if x is equal to 0.2, the tuning sensitivity is thus reduced to 1%.

[0048] According to some embodiments, the switched capacitor arrangement 300 may further comprise a plurality of switch branches coupled between the second nodes 312, 322 of the first and second capacitor branches. Each switch branch may comprise one or two capacitors connected in series with a switch, as shown in FIG. 3b dotted line box.

[0049] Depending on different requirements on tuning range and tuning sensitivity, the capacitance of each switch branch may be chosen differently. For example, different switch branches may have same capacitance or different capacitance, or some switch branches may have same capacitance and some switch branches may have different capacitance. The two capacitors in each switch branch may have same capacitance.

[0050] According to some embodiments, the first switch S1 in the switch branches may be implemented by switching transistors, such as metal oxide semiconductor field effect transistors (MOSFET/MOS).

[0051] To investigate the frequency tuning techniques according to embodiments herein, a DCO for a 5G frequency synthesizer has been simulated in a 28 nm CMOS SOI design-kit for different attenuations, i.e. the attenuation parameter x is 0.1, 0.2, 0.3, 0.4. The tuning sensitivity responds as expected when changing x. The effective tuning capacitance being proportional to the square of the attenuated voltage gives a large dynamic range in sensitivity programmability. For example, when x=0.1, the sensitivity=0.040 MHz/fF, when x=0.2, the sensitivity=0.12 MHz/fF, when x=0.3, the sensitivity=0.29 MHz/fF, when x=0.4, the sensitivity=0.49 MHz/fF.

[0052] The embodiments herein are based on using capacitive voltage dividers across a differential resonator of a differential circuit. To achieve minimum tuning sensitivity, the voltage division capacitors, e.g. the first and second capacitors 314, 315 and the third and the fourth capacitors 324, 325 in the switched capacitor arrangement 300 shown in FIG. 3b, may be chosen to be a bit larger than e.g. minimum sized capacitor, for best matching. The switched capacitor banks, i.e. the plurality of switch branches coupled between the second nodes 312, 322 of the first and second capacitor branches 310, 320 may then be subjected to a very small voltage. The accuracy of this small voltage is limited only by the voltage division capacitor matching, and matching of capacitors is typically very good on chip. By using minimum sized capacitors for Ct, Cs1, Cs2 for minimum frequency step, it may therefore be possible to create accurate attenuations in the order of 1% of the signal voltage, corresponding to about 10000 times reduction of the capacitance step size. Further, large size voltage division capacitors will also provide good tuning linearity.

[0053] To summarise the discussions above, some advantages of the switched capacitor arrangements 200, 300 according to embodiments herein include:

[0054] Firstly, for the capacitor arrangement 300, since the switched capacitor arrangement is coupled to respective differential nodes of a differential circuit, i.e. not using any other nodes, e.g. source terminals of a cross coupled differential pair of transistors in the differential circuit, which would introduce dependence on transistor parameters, the capacitive attenuation technique according to embodiments herein is completely independent on transistor parameters when setting the attenuation level and controlling the tuning sensitivity. That is a well-controlled reduction of the tuning sensitivity may be achieved.

[0055] Secondly, if two capacitors of equal size or nearly equal size are series connected between the differential nodes with positive and negative voltages of the resonator, the middle node of the two series connected capacitors will have a signal voltage close to zero. Therefore small signal voltages may be achieved without the need for large capacitor ratios. The second harmonic tuning technique shown in FIGS. 2a and 2b has the advantage of using equal sized capacitors in the voltage divider which increases matching accuracy.

[0056] Thirdly, the requirements on the switch may be considerably relaxed compared to switching a capacitance in a regular structure, i.e. direct connection of a switched capacitor across the differential nodes of the circuit, where the switch is in series with the capacitor. Since the voltage on the middle node is close to zero, the switch connected to the middle node according to embodiments herein will have considerable much less signal current flow, i.e. 1/x times less, in its on-state compared to the switch in the regular structure. The on-resistance may thus be higher, e.g. 1/x.sup.2 times higher, in the switch for the same capacitance quality factor. A good compromise may be achieved by multiplying the regular structure switch width by x to find a good balance between off-state parasitic capacitance, on-state quality factor, and chip area.

[0057] Fourthly, very fine capacitance step can be achieved while still using a limited range of capacitor sizes, i.e. not smaller than existing capacitors in a design-kit, and not very large to save chip area. Without using extreme component values which pose hard component requirements, effective capacitance steps of less than 1% of the minimum capacitor of the current technology may be achieved. This corresponds to more than 100 times increased capacitance resolution compared to a regular structure. In fact, the switched capacitor arrangements 200, 300 according to embodiments herein using the capacitive attenuation technique optimized for capacitance resolution may be able to reach robust attenuation levels of about 1%, corresponding to 10000 times increased capacitance resolution. Very fine capacitance step results in very fine frequency resolution.

[0058] The switched capacitor arrangements 200, 300 according to embodiments herein are suitable for tuning of a differential circuit 400, as shown in FIG. 4. The differential circuit 400 may be any one of a DCO, a digital to time converter or a digitally controlled filter comprised in any electronic devices. For example, the switched capacitor arrangements 200 may be used to tune the frequency of a DCO, or the delay of a digital to time converter. The switched capacitor arrangement 300 may be used to tune the frequency of a DCO, the frequency of a differential digitally controlled filter, or the delay of a digital to time converter.

[0059] The differential circuit 400 may comprise one or a plurality of switched capacitor arrangement 200, 300, for fine tuning the differential circuit 400 controlled by digital control words F0, . . . Fn1. The differential circuit 400 may comprise coarse tuning and medium tuning controlled by respective digital control words C0, . . . Cn3, M0, . . . Mn2 as in any prior art solutions.

[0060] In each switched capacitor arrangement of the plurality of switched capacitor arrangement 300, a capacitance ratio of the first capacitor to the second capacitor may be 1/(1+x), and a capacitance ratio of the third capacitor to the fourth capacitor may be (1+x), where 0<x<1. The attenuation parameter x may be different for each switched capacitor arrangement 300 or may be same for some of the switched capacitor arrangements 300.

[0061] FIG. 5 shows an electronic device 500 which comprises a differential circuit 400 in which the switched capacitor arrangements 200, 300 according to embodiments herein may be implemented. The electronic device 500 may be any one of a wireless communication device, a base station, a mobile terminal, a wireless transceiver, a frequency synthesiser etc.

[0062] The electronic device 500 may comprise other units, e.g. a processing unit 520 for generating digital control words and signal processing etc.

[0063] When using the word "comprise" or "comprising" it shall be interpreted as non-limiting, i.e. meaning "consist at least of".

[0064] Also note that terminology such as a first capacitor and a second capacitor should be considered to be non-limiting and does in particular not imply a certain hierarchical relation between the two.

[0065] The embodiments herein are not limited to the above described preferred embodiments. Various alternatives, modifications and equivalents may be used. Therefore, the above embodiments should not be taken as limiting the scope of the invention, which is defined by the appending claims.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.