Gate Drive Circuit

OKAWAUCHI; Yuta ; et al.

U.S. patent application number 16/771995 was filed with the patent office on 2021-03-18 for gate drive circuit. This patent application is currently assigned to ROHM CO., LTD.. The applicant listed for this patent is Rohm Co., Ltd.. Invention is credited to Ken NAKAHARA, Yusuke NAKAKOHARA, Yuta OKAWAUCHI.

| Application Number | 20210083563 16/771995 |

| Document ID | / |

| Family ID | 1000005287282 |

| Filed Date | 2021-03-18 |

View All Diagrams

| United States Patent Application | 20210083563 |

| Kind Code | A1 |

| OKAWAUCHI; Yuta ; et al. | March 18, 2021 |

GATE DRIVE CIRCUIT

Abstract

A gate drive circuit, which drives a gate of a first transistor, includes a first switch on a high potential side and a second switch on a low potential side connected in series at a second connection node between a high potential end and a low potential end of a series connection structure, constituted of a first voltage source and a second voltage source connected in series at a first connection node; and a third switch and an inductor connected in series between the first connection node and the second connection node. The gate of the first transistor can be electrically connected to the second connection node

| Inventors: | OKAWAUCHI; Yuta; (Kyoto, JP) ; NAKAKOHARA; Yusuke; (Kyoto, JP) ; NAKAHARA; Ken; (Kyoto, JP) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Assignee: | ROHM CO., LTD. Kyoto JP |

||||||||||

| Family ID: | 1000005287282 | ||||||||||

| Appl. No.: | 16/771995 | ||||||||||

| Filed: | November 16, 2018 | ||||||||||

| PCT Filed: | November 16, 2018 | ||||||||||

| PCT NO: | PCT/JP2018/042479 | ||||||||||

| 371 Date: | June 11, 2020 |

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H02M 3/158 20130101; H02M 1/08 20130101; H03K 17/04123 20130101; H02M 2001/0054 20130101 |

| International Class: | H02M 1/08 20060101 H02M001/08; H02M 3/158 20060101 H02M003/158; H03K 17/0412 20060101 H03K017/0412 |

Foreign Application Data

| Date | Code | Application Number |

|---|---|---|

| Dec 12, 2017 | JP | 2017237685 |

| Apr 16, 2018 | JP | 2018078349 |

Claims

1. A gate drive circuit arranged to drive a gate of a first transistor, comprising: a first switch on a high potential side and a second switch on a low potential side connected in series at a second connection node between a high potential end and a low potential end of a series connection structure, constituted of a first voltage source and a second voltage source connected in series at a first connection node; and a third switch and an inductor connected in series between the first connection node and the second connection node, wherein the gate of the first transistor is capable of being electrically connected to the second connection node.

2. The gate drive circuit according to claim 1, further comprising; at least one of a first current blocking unit arranged to block current from the second connection node to the high potential side and a second current blocking unit arranged to block current from the low potential side to the second connection node; and a backflow prevention unit arranged to prevent backflow of current flowing in the inductor.

3. The gate drive circuit according to claim 2, wherein the third switch is a bidirectional switch, the backflow prevention unit prevents bidirectional backflow, and both the first current blocking unit and the second current blocking unit are provided.

4. The gate drive circuit according to claim 3, wherein the bidirectional switch is made of a second transistor and a third transistor connected in series, and the backflow prevention unit is a diode of the second transistor and a diode of the third transistor.

5. The gate drive circuit according to claim 3, wherein the first switch and the second switch are a fourth transistor and a fifth transistor, and the first current blocking unit and the second current blocking unit are a diode.

6. The gate drive circuit according to claim 2, wherein only the first current blocking unit out of the first current blocking unit and the second current blocking unit is provided, and the backflow prevention unit prevents backflow only in a direction from the second connection node to the first connection node.

7. The gate drive circuit according to claim 6, wherein the first switch is a sixth transistor, and the third switch is a seventh transistor including a diode, and the first current blocking unit is a diode, and the backflow prevention unit is a different diode from the diode included in the seventh transistor.

8. The gate drive circuit according to claim 2, wherein only the second current blocking unit out of the first current blocking unit and the second current blocking unit is provided, and the backflow prevention unit prevents backflow only in a direction from the first connection node to the second connection node.

9. The gate drive circuit according to claim 8, wherein the second switch is an eighth transistor, and the third switch is a ninth transistor including a diode, and the second current blocking unit is a diode, and the backflow prevention unit is a different diode from the diode included in the ninth transistor.

10. The gate drive circuit according to claim 1, comprising the first voltage source and the second voltage source, which are a capacitor.

11. The gate drive circuit according to claim 1, wherein an ON time of the third switch is variable in accordance with a load current flowing in the first transistor.

12. A gate drive circuit that is arranged to drive a gate of a first transistor, and to which a first voltage source and a second voltage source connected in series at a first connection node, and an inductor can be electrically connected, the gate drive circuit comprising: a first switch on a high potential side and a second switch on a low potential side connected in series at a second connection node between a high potential end and a low potential end of a series connection structure, constituted of the first voltage source and the second voltage source; and a third switch connected in series to the inductor between the first connection node and the second connection node, wherein the gate of the first transistor is capable of being electrically connected to the second connection node.

13. A gate drive circuit arranged to drive a gate of a first transistor, comprising: a first switch on a high potential side and a second switch on a low potential side connected in series at a second connection node between a high potential end and a low potential end of a series connection structure, constituted of a first voltage source and a second voltage source connected in series at a first connection node; and a third switch and an inductor connected in series between the first connection node and the second connection node, wherein the gate drive circuit controls current to flow in the inductor through the third switch before the first switch or the second switch begins to control the first transistor.

14. The gate drive circuit according to claim 12, comprising the first voltage source and the second voltage source, which are a capacitor.

15. A power conversion device comprising: the gate drive circuit according to claim 1; and a transistor having a gate driven by the gate drive circuit.

16-28. (canceled)

Description

TECHNICAL FIELD

[0001] The present invention relates to a gate drive circuit.

BACKGROUND ART

[0002] Conventionally, various gate drive circuits that drive the gate of a transistor such as a MOS field-effect transistor (MOSFET) have been developed.

[0003] For instance, Patent Document 1 discloses one example of a conventional gate drive circuit. The gate drive circuit of Patent Document 1 includes a switching circuit that switches three levels of output voltages, and a reactor is connected between the switching circuit and the gate of a transistor. The switching circuit switches zero level, medium level, and double medium level that is a power level.

[0004] When the transistor is turned on, the switching circuit switches the output voltage from zero level to medium level. Then a resonance occurs due to the reactor and a gate-source capacitance of the transistor. In this case, a gate voltage rapidly increases to the power level, and a variation point of the gate voltage becomes zero at a certain time point. At this time point, the switching circuit switches the output voltage to the power level, so that the gate voltage is kept at the power level. When being turned off, the operation is performed in the opposite order to when being turned on.

[0005] Further, conventionally, there is proposed a method of temporarily changing a gate voltage of a switching, element only for an instant of switching so as to achieve high speed switching, in a gate drive circuit that switches a switching element of a switching power supply, a motor driver, or the like (see, for example, Patent Documents 2 to 4).

LIST OF CITATIONS

Patent Literature

[0006] Patent Document 1: JP-A-2007-282326

[0007] Patent Document 2: JP-A-2009-200891

[0008] Patent Document 3: Japanese Patent No. 4804142

[0009] Patent Document 4: JP-A-2010-51165

[0010] Patent Document 5: JP-A-2017-183979

SUMMARY OF THE INVENTION

Technical Problem

[0011] Here, a transistor has an internal gate resistor (parasitic resistor), and when the transistor is driven by a gate drive circuit, a gate current that charges and discharges the gate of the transistor is limited by the internal gate resistor. In particular, a transistor using a semiconductor material such as SiC has a large internal gate resistor, which limits more the gate current. This causes a problem that a switching speed of the transistor is decreased and a switching loss is increased.

[0012] However, the gate drive circuit of Patent Document 1 described above is aimed at suppressing an overshoot of the gate voltage when being turned on and an undershoot of the gate voltage when being turned off, and a decrease in the switching speed due to the internal gate resistor of the transistor as described above has not been considered.

[0013] In view of the above-mentioned circumstances, it is expected to achieve higher switching speed of the transistor to be driven.

[0014] Further, in Patent Document 2, so many passive elements are necessary as means for temporarily increasing the gate voltage, and hence there is a problem that a circuit scale is increased.

[0015] Further, in Patent Document 3, a gate voltage is temporarily increased by switching a plurality of power supplies, and hence in addition to the problem of increasing a circuit scale, there is a problem that complicated control is also required.

[0016] Further, in Patent Document 4, the drive target is a current drive type switching element (junction-type FET), in which a gate current is required to flow also in a steady ON state. Therefore, the capacitor proposed in this document should be connected in parallel to a gate resistor that is an essential circuit element, and it is not supposed that the capacitor is used solely. In this viewpoint, the conventional technique of Patent Document 4 looks similar to but is clearly different from the present invention in essential structure.

[0017] Note that the applicant of this patent application proposes in Patent Document 5, in view of the problems described above, a gate drive circuit that can easily achieve high speed switching. However, this conventional technique still needs more consideration concerning variations of the capacitor and an input capacitance.

[0018] In view of this situation, it is also expected to provide a gate drive circuit that can achieve high speed switching easily and appropriately even if the capacitor or the input capacitance has a variation.

Means for Solving the Problem

[0019] A gate drive circuit according to an aspect of the present invention, which is a gate drive circuit arranged to drive a gate of a first transistor, includes a first switch on a high potential side and a second switch on a low potential side, connected in series at a second connection node between a high potential end and a low potential end of a series connection structure, constituted of a first voltage source and a second voltage source connected in series at a first connection node: and a third switch and an inductor connected in series between the first connection node and the second connection node. The gate of the first transistor can be electrically connected to the second connection node.

[0020] Further, a gate drive circuit according to another aspect of the present invention includes a first transistor having a first terminal connected to an application terminal of a first voltage and a second terminal connected to a gate of a switching element via a capacitor; a second transistor having a first terminal connected to the gate of the switching element via the capacitor and a second terminal connected to an application terminal of a second voltage lower than the first voltage, the second transistor being driven in the opposite phase to the first transistor; a third transistor having a first terminal connected to an application terminal of a third voltage higher than the second voltage and a second terminal connected to the gate of the switching element via a first rectifier element, the third transistor being driven in the same phase as the first transistor; and a fourth transistor having a first terminal connected to the gate of the switching element via a second rectifier element and a second terminal connected to an application terminal of a fourth voltage lower than the third voltage, the fourth transistor being driven in the same phase as the second transistor. The first voltage is higher than the third voltage and the second voltage is equal to the fourth voltage, or the second voltage is lower than the fourth voltage and the first voltage is equal to the third voltage, or the first voltage is higher than the third voltage and the second voltage is lower than the fourth voltage.

Advantageous Effects of the Invention

[0021] According to the gate drive circuit of the present invention, switching speed can be appropriately increased.

BRIEF DESCRIPTION OF DRAWINGS

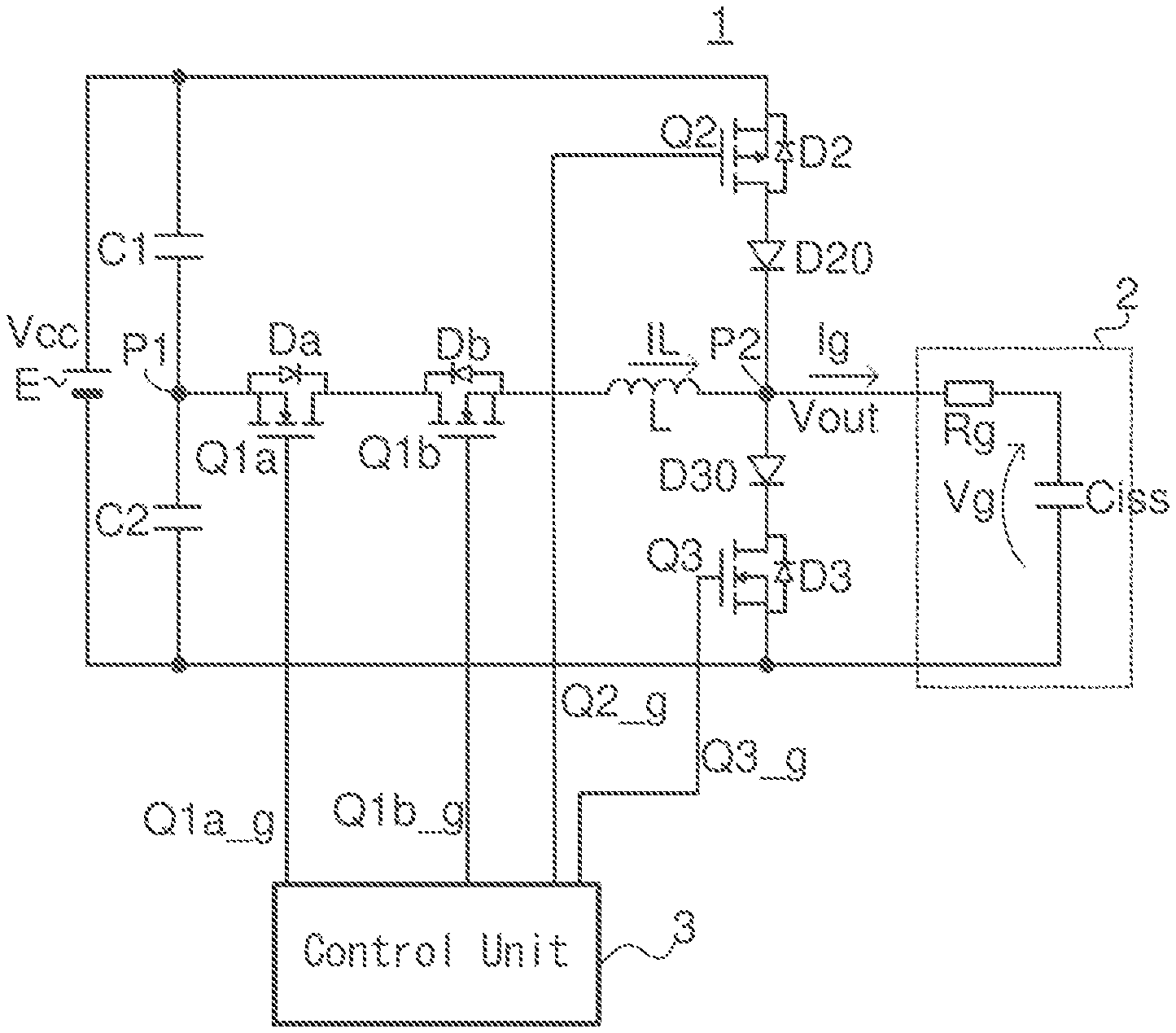

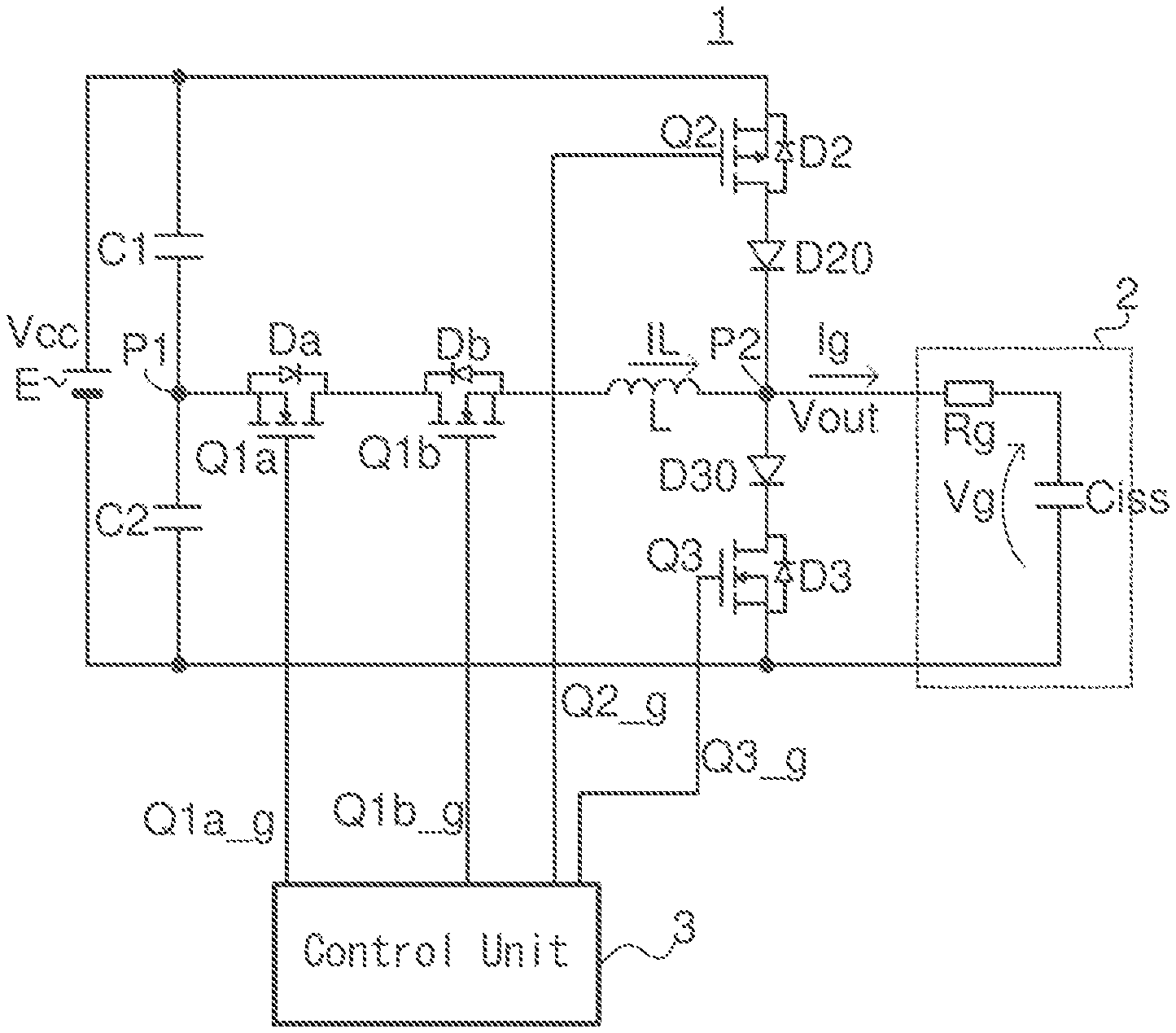

[0022] FIG. 1 is a circuit diagram illustrating a structure of a gate drive circuit according to one embodiment of the present invention.

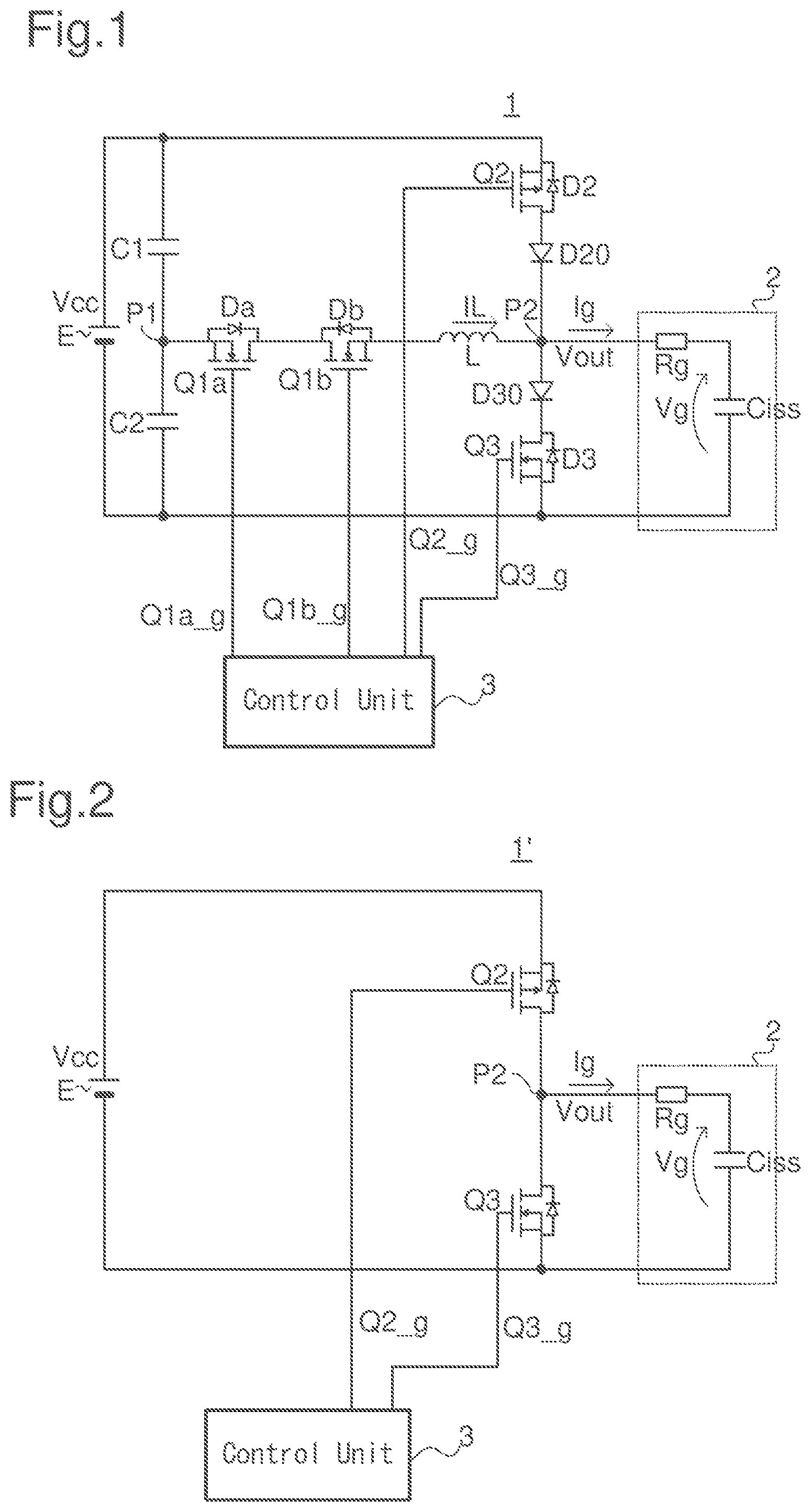

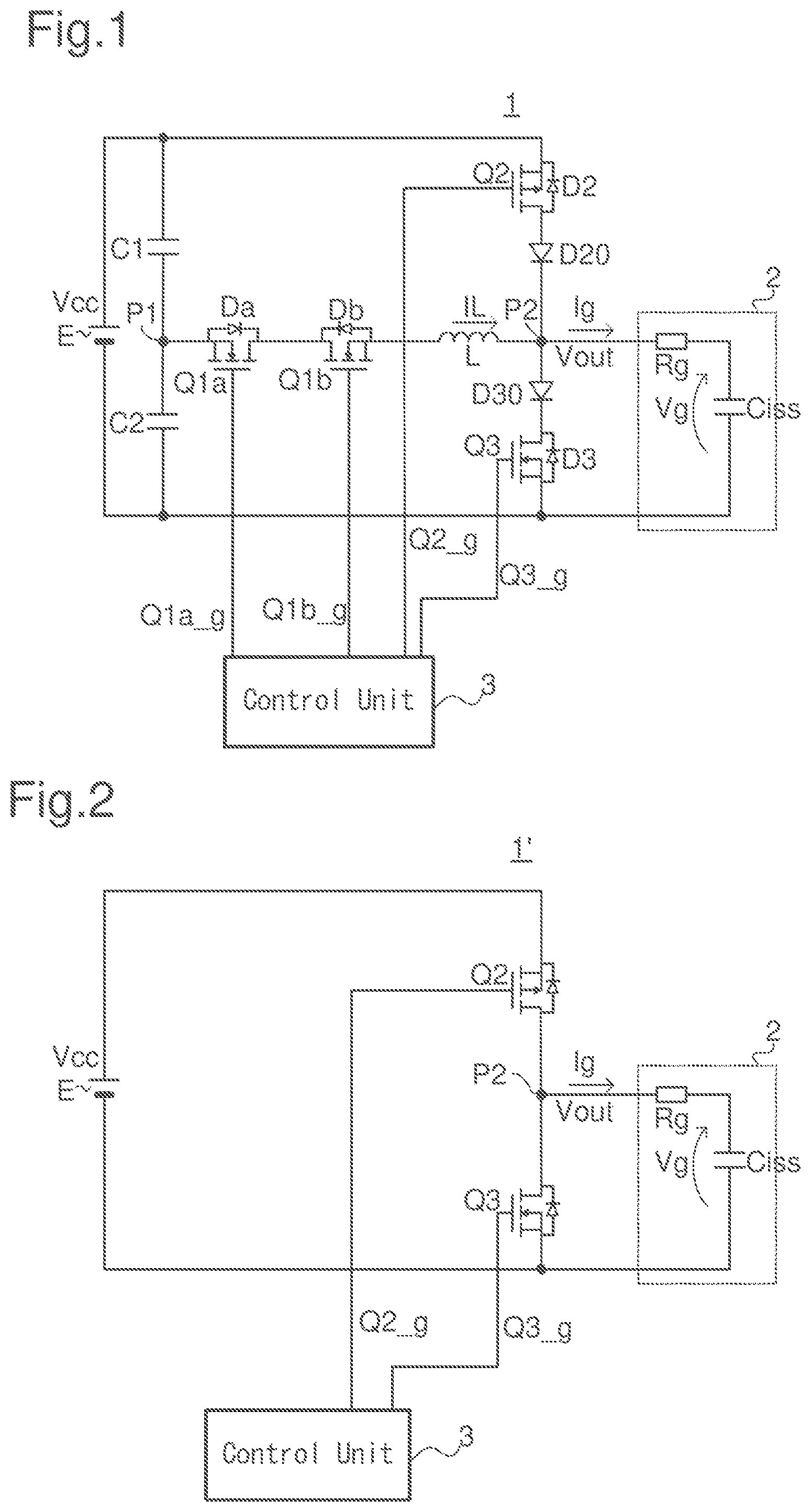

[0023] FIG. 2 is a circuit diagram illustrating one example of a conventional gate drive circuit.

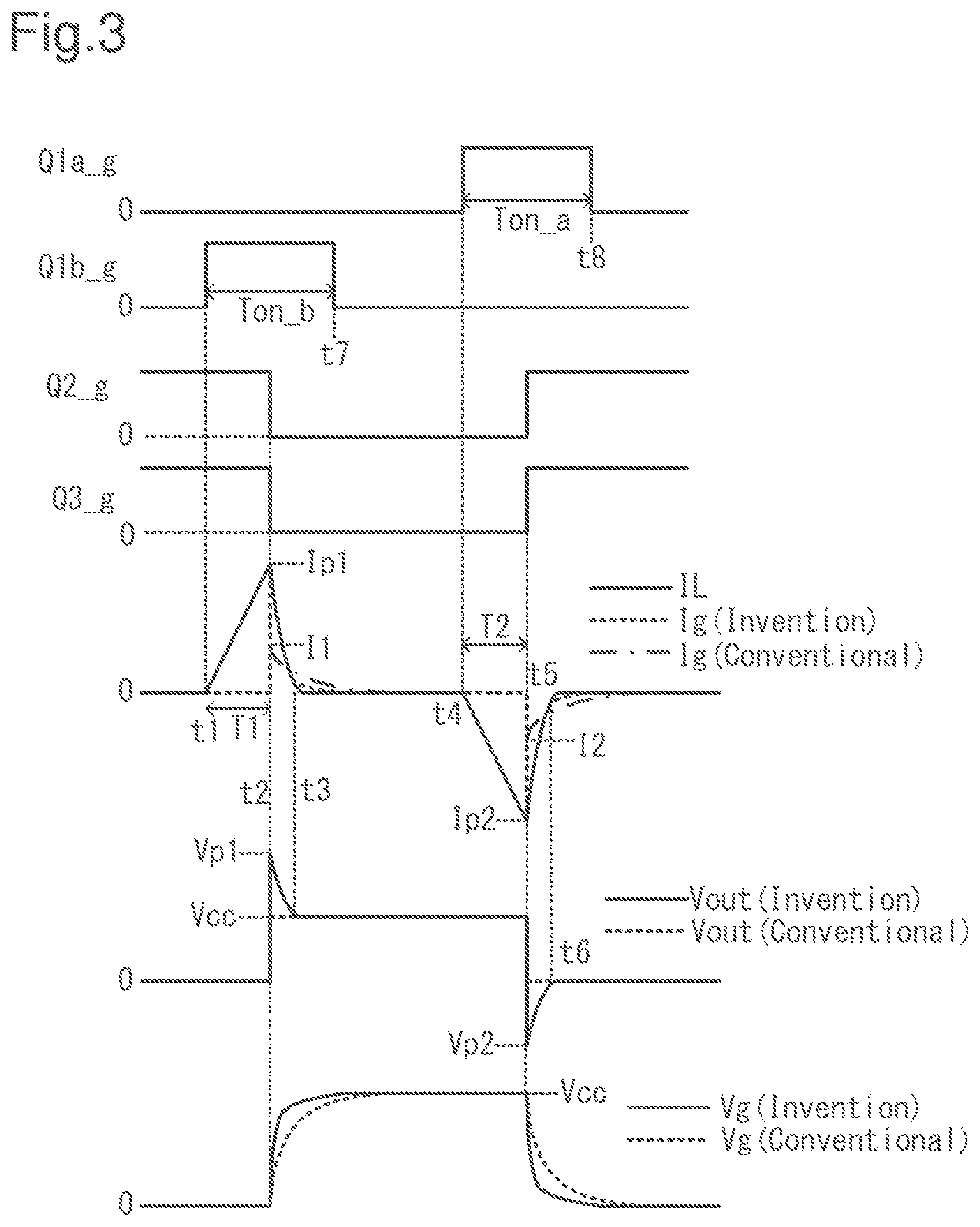

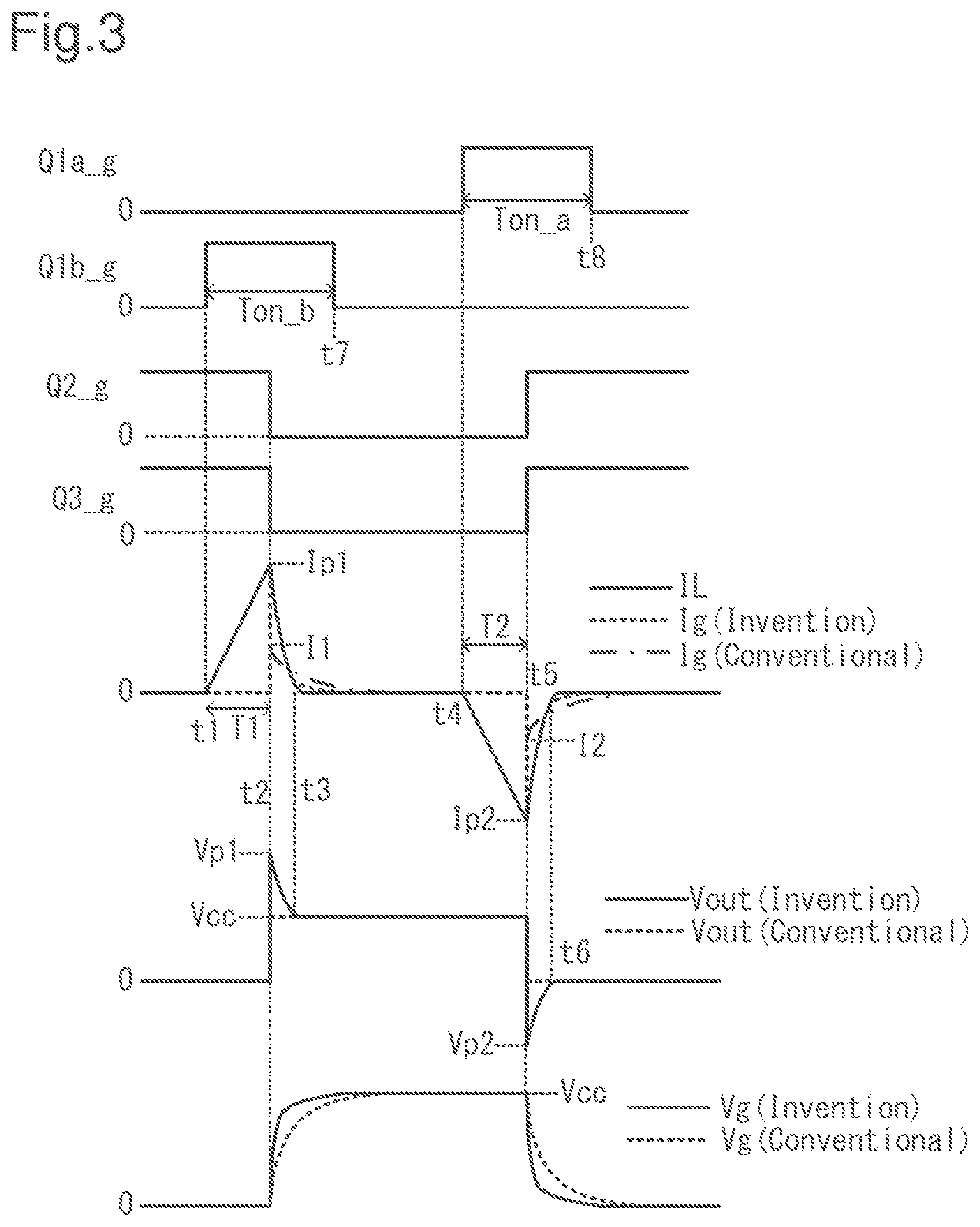

[0024] FIG. 3 is a timing chart of operations when a transistor is turned on and when it is turned off.

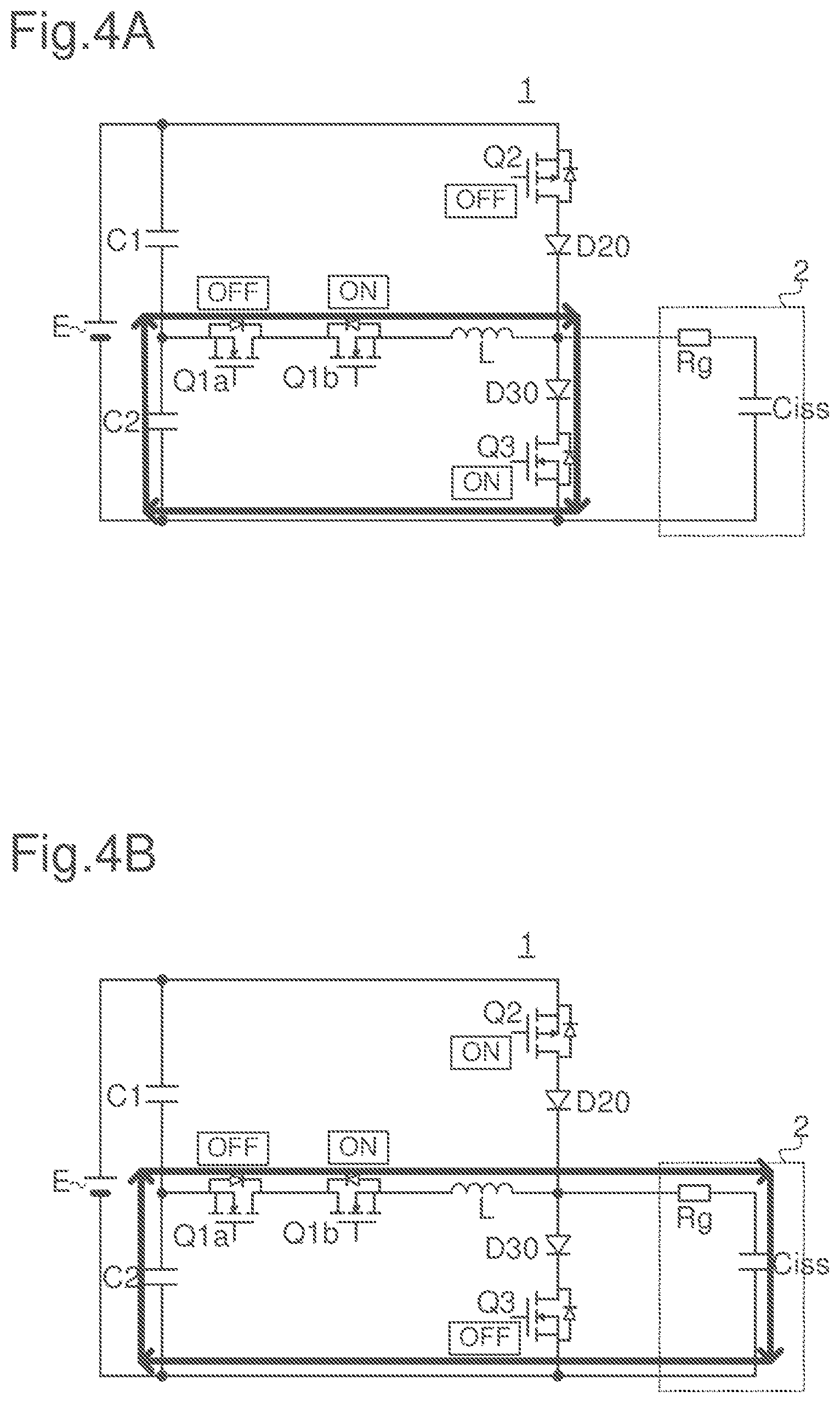

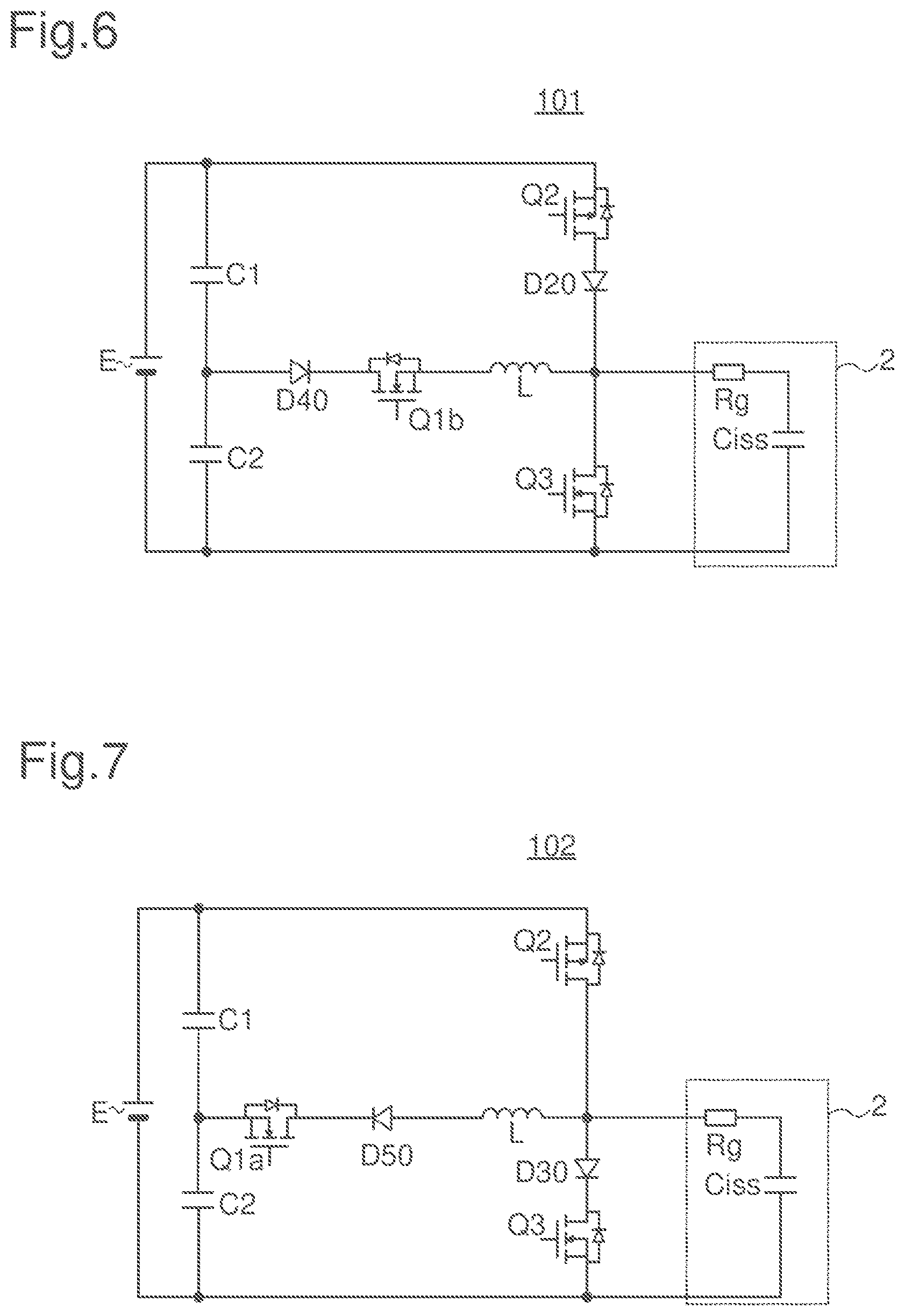

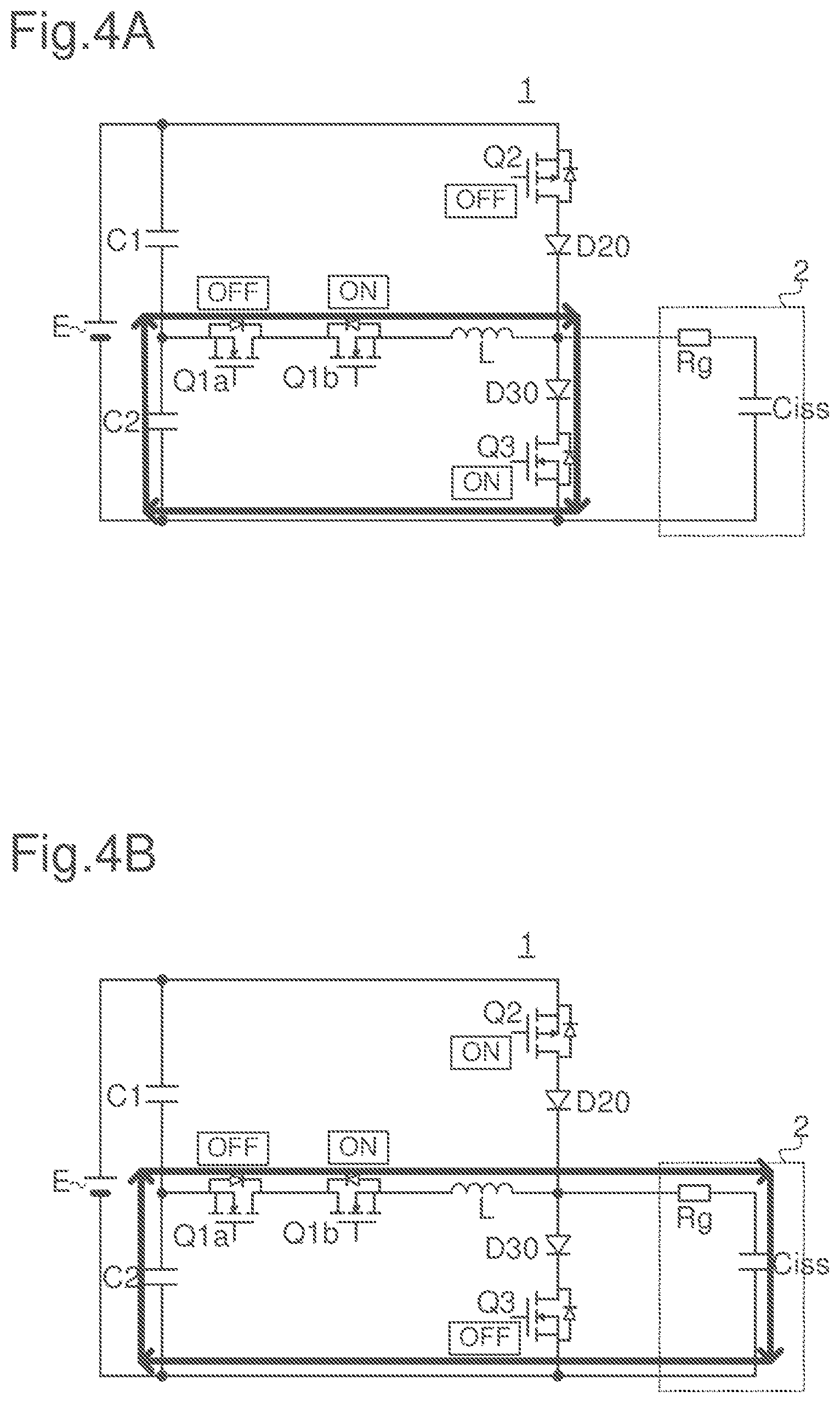

[0025] FIG. 4A is a circuit diagram illustrating a first operating state when being turned on.

[0026] FIG. 4B is a circuit diagram illustrating a second operating state when being turned on.

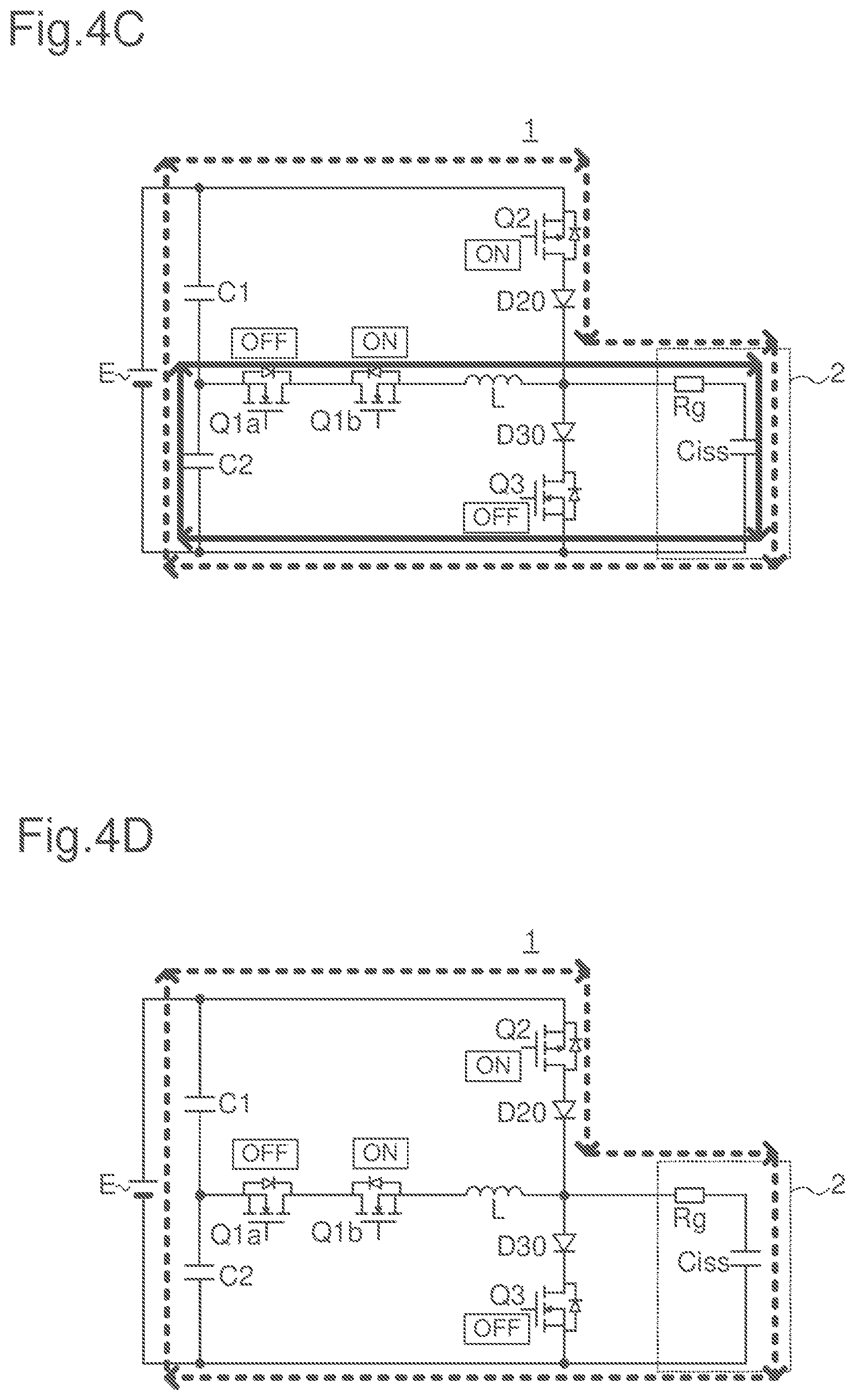

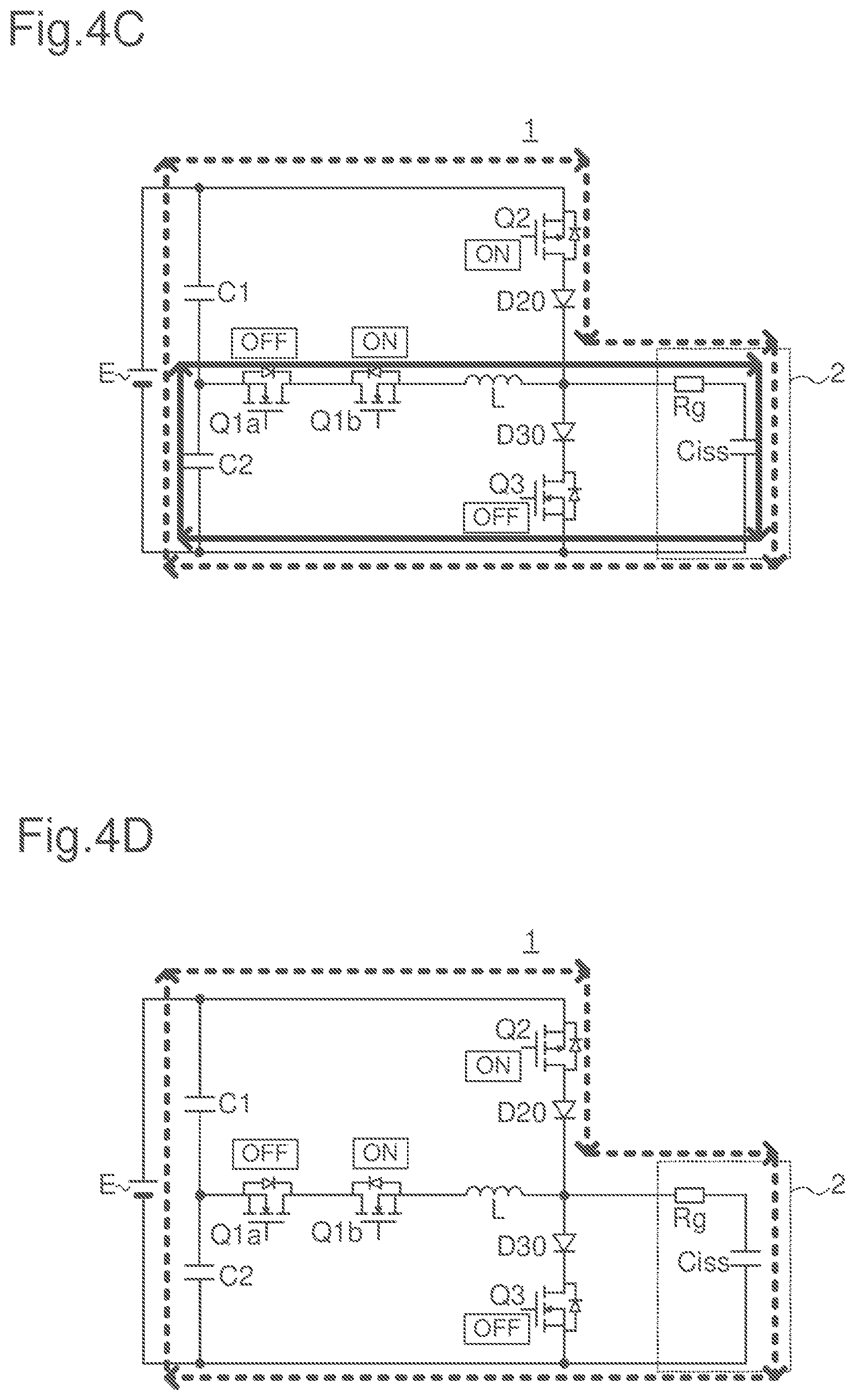

[0027] FIG. 4C is a circuit diagram illustrating a third operating state when being turned on.

[0028] FIG. 4D is a circuit diagram illustrating a fourth operating state when being turned on.

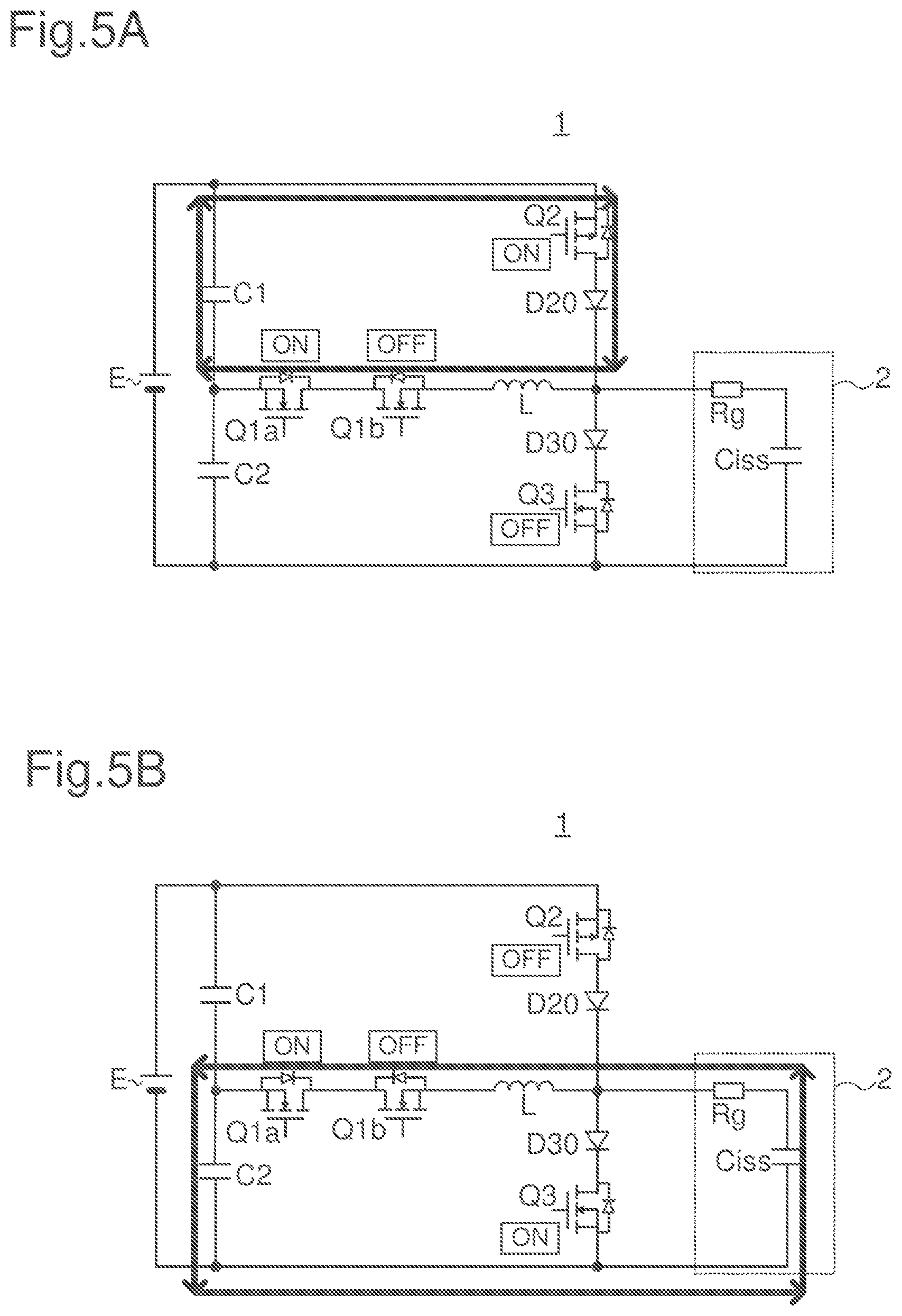

[0029] FIG. 5A is a circuit diagram illustrating a first operating state when being turned off.

[0030] FIG. 5B is a circuit diagram illustrating a second operating state when being turned off.

[0031] FIG. 5C is a circuit diagram illustrating a third operating state when being turned off.

[0032] FIG. 5D is a circuit diagram illustrating a fourth operating state when being turned off.

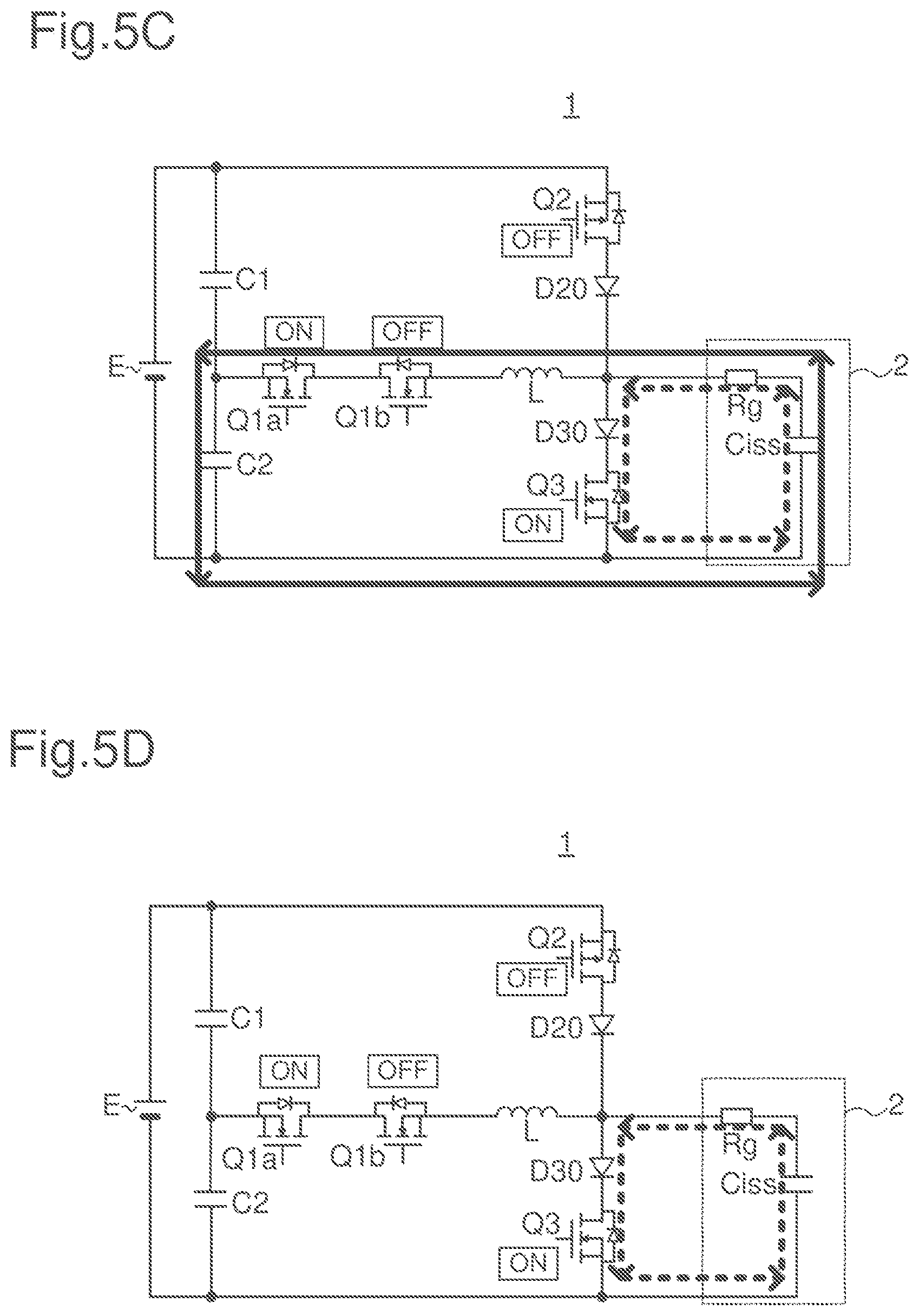

[0033] FIG. 6 is a circuit diagram illustrating a structure of the gate drive circuit according to a variation.

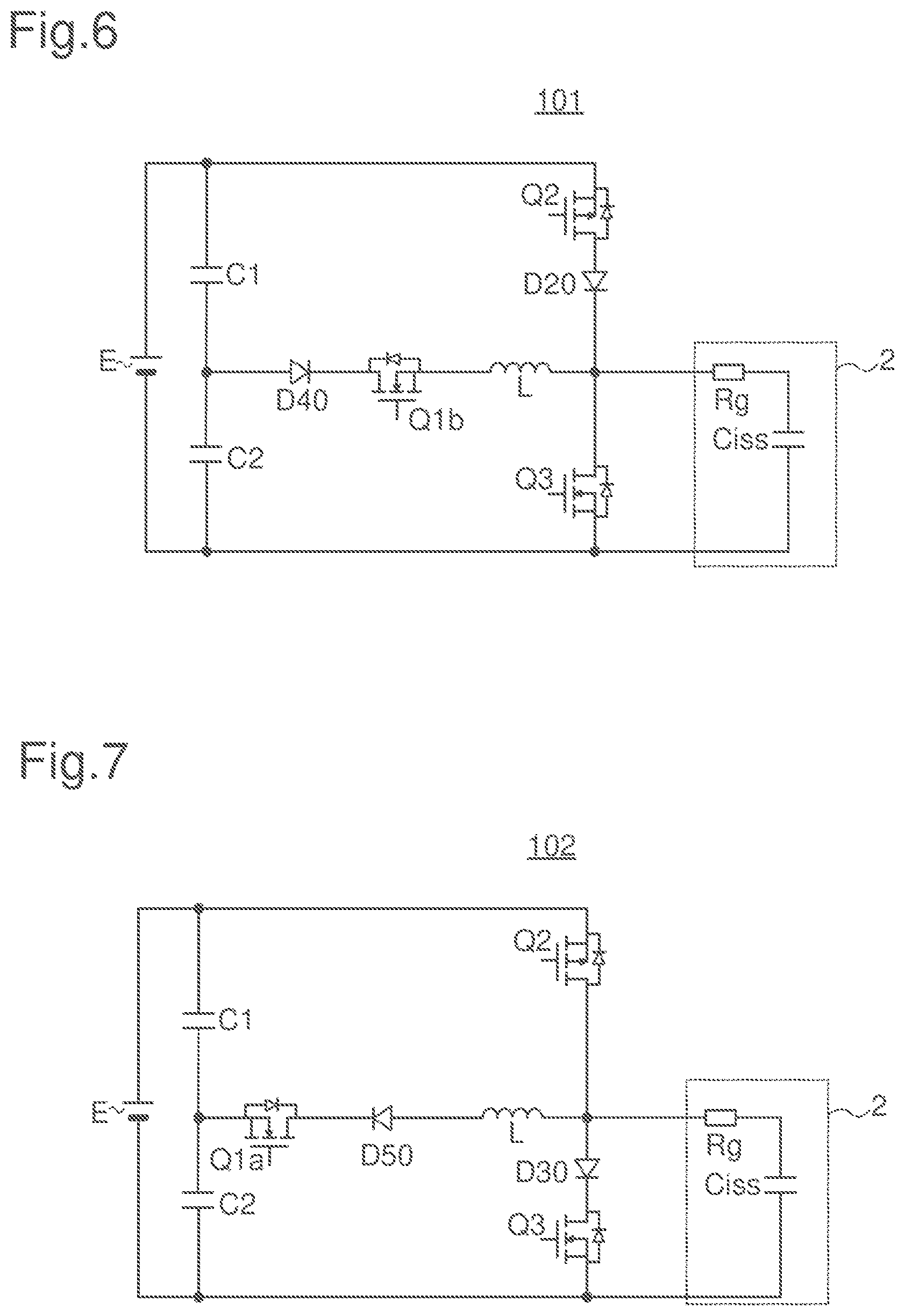

[0034] FIG. 7 is a circuit diagram illustrating a structure of the gate drive circuit according to another variation.

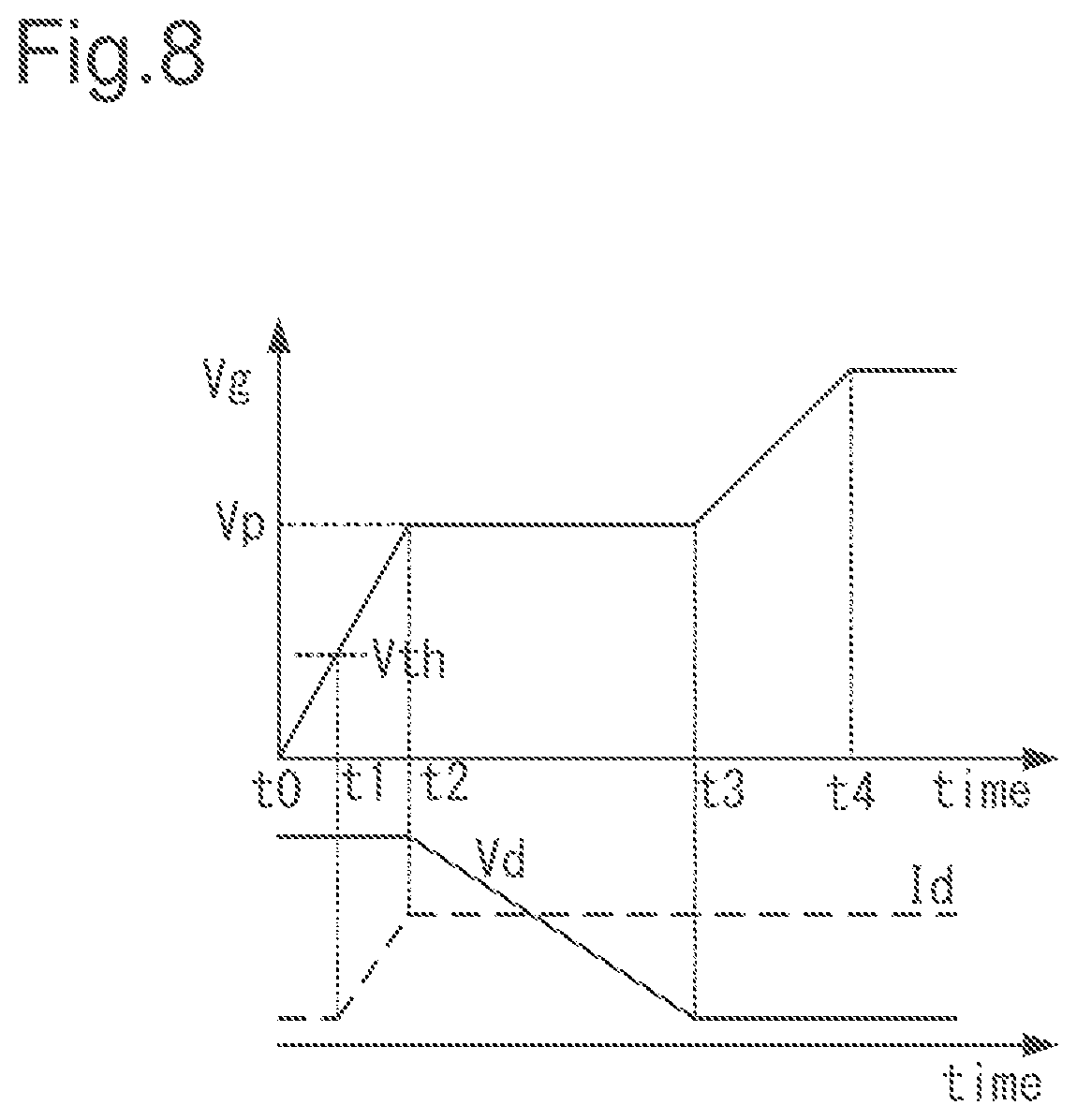

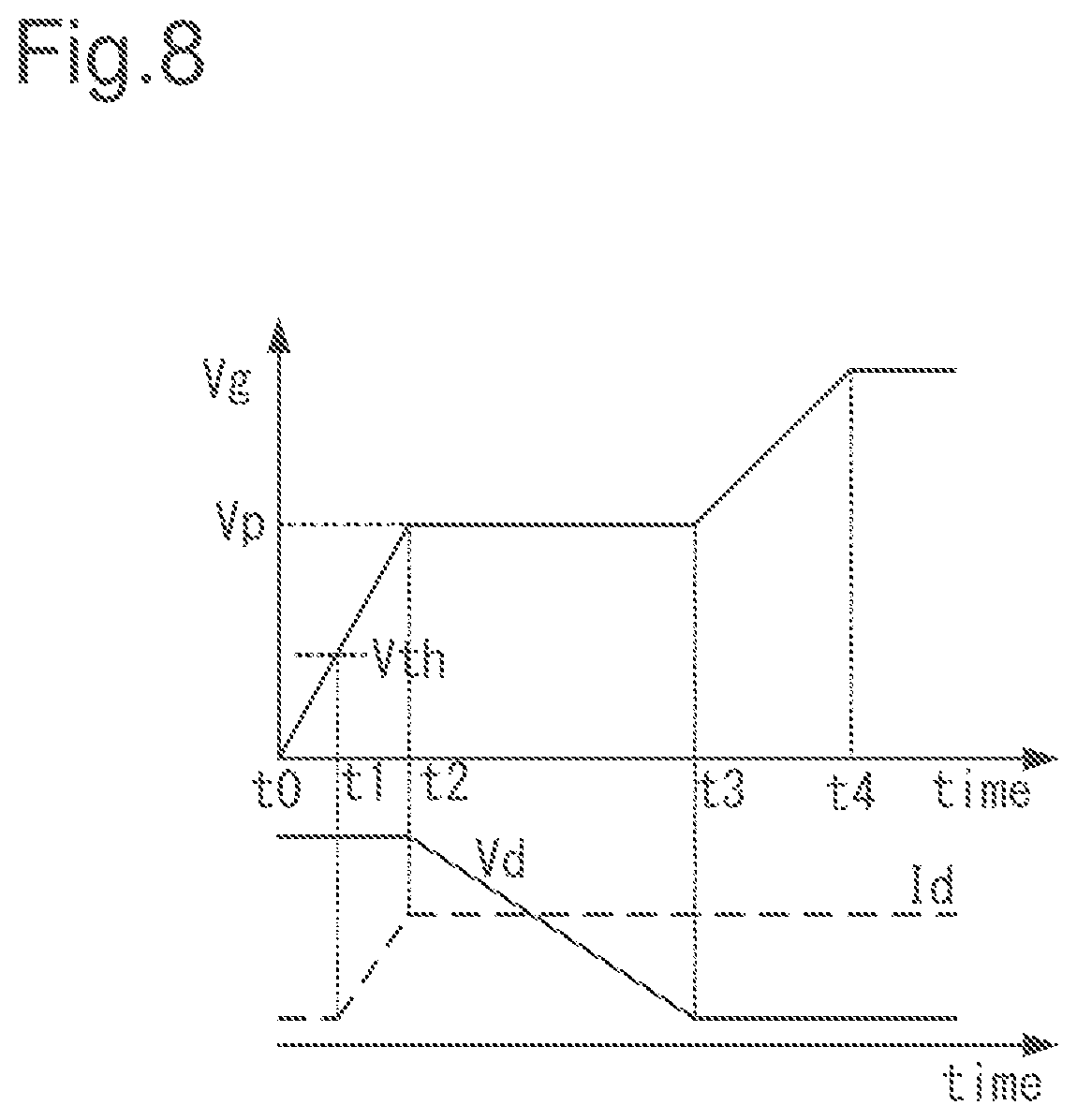

[0035] FIG. 8 is a timing chart showing various waveforms when the transistor is turned on.

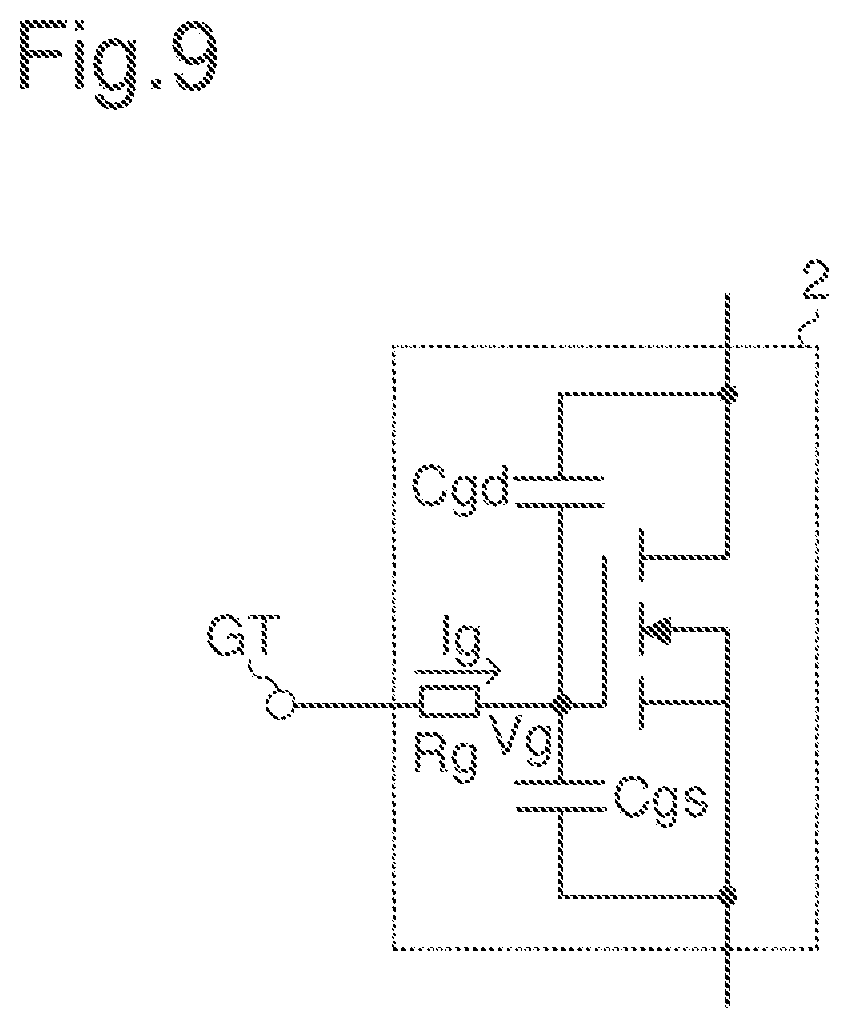

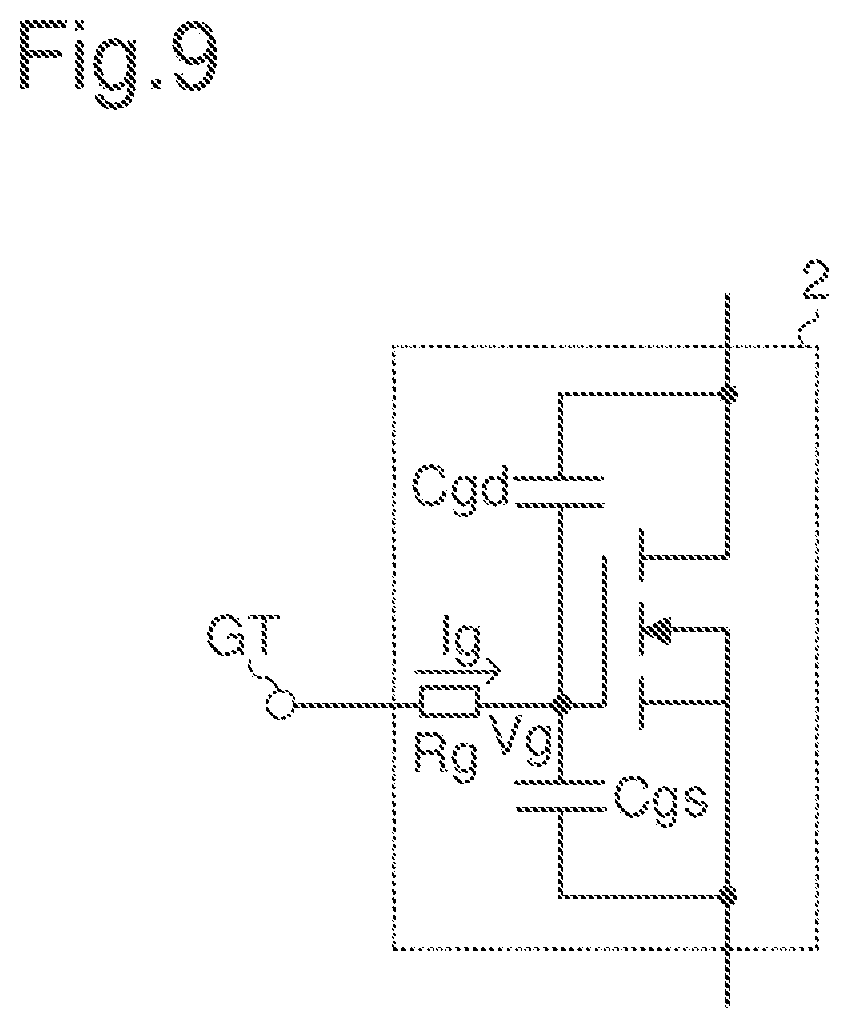

[0036] FIG. 9 is a model diagram of the transistor (MOSFET).

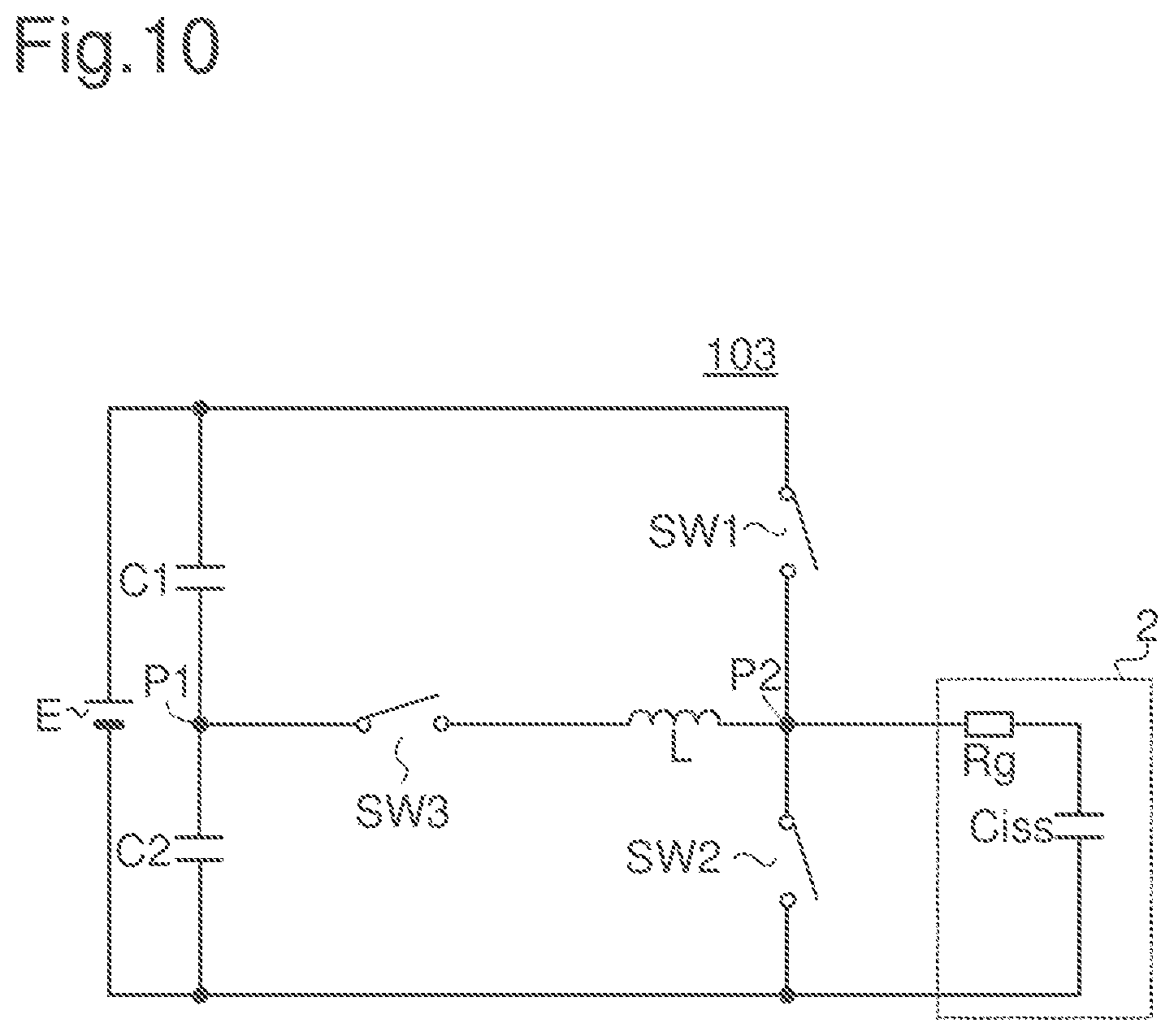

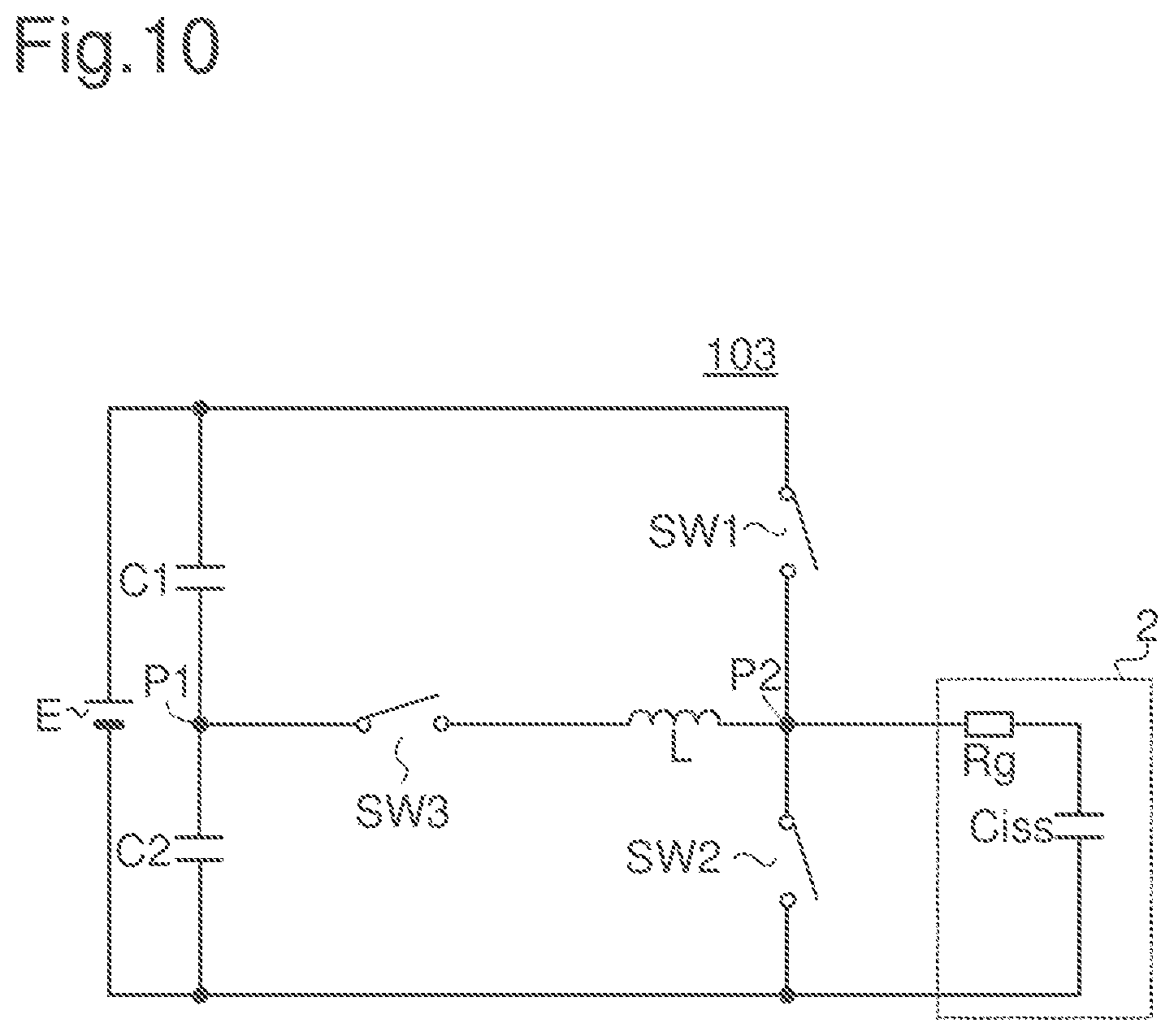

[0037] FIG. 10 is a circuit diagram illustrating a structure of the gate drive circuit according to another variation.

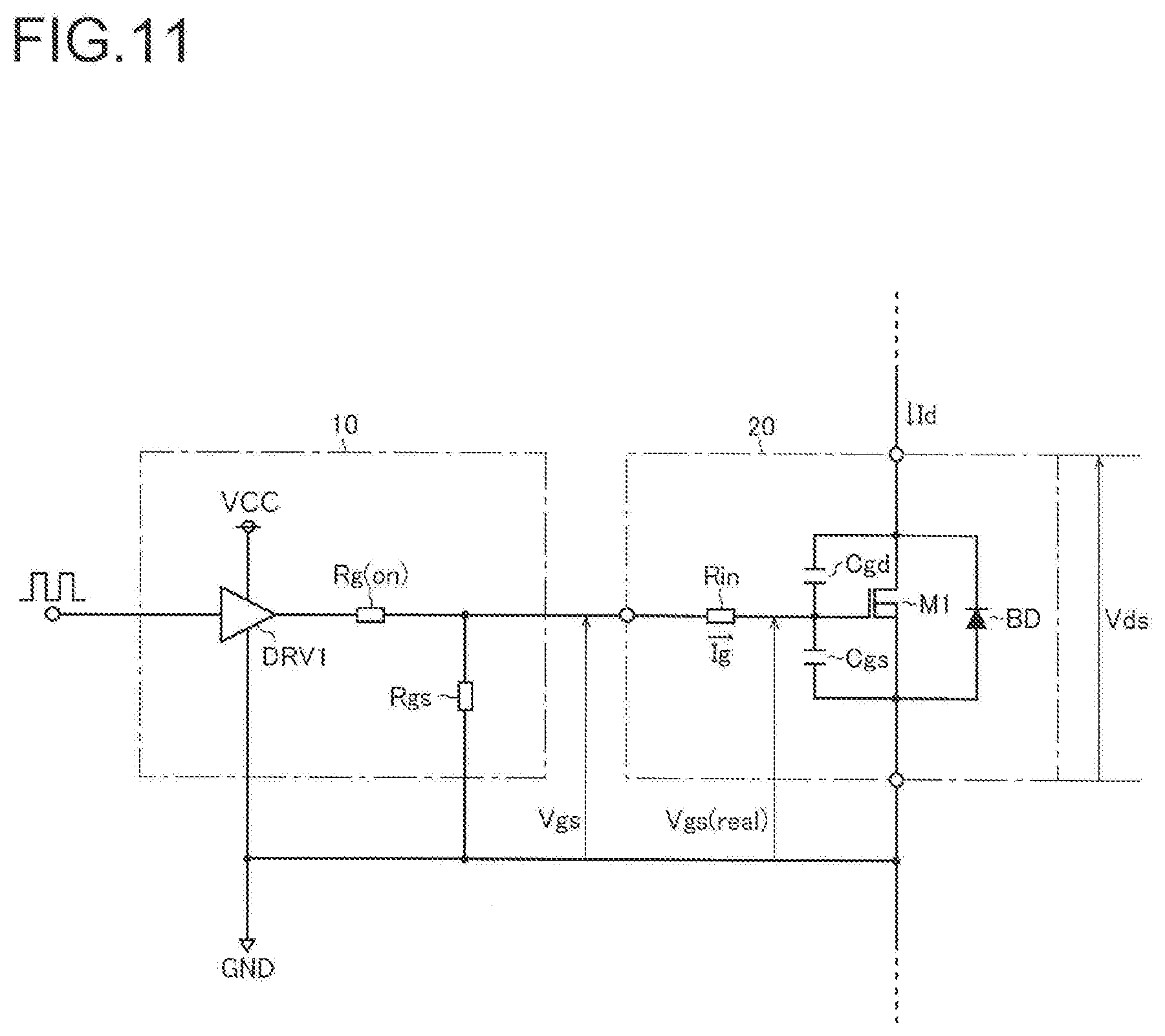

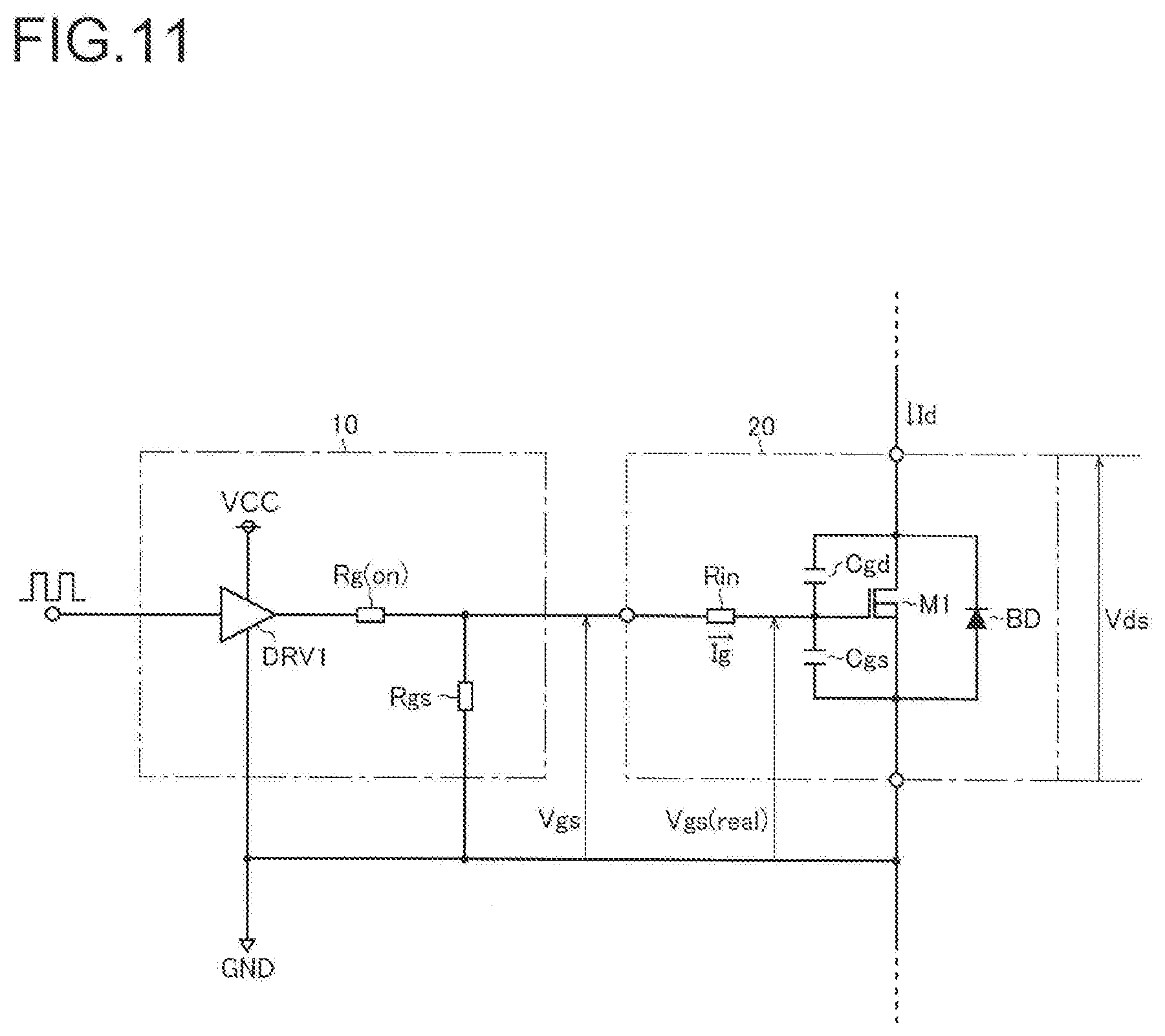

[0038] FIG. 11 is an equivalent circuit diagram illustrating a reference example of the gate drive circuit to be compared with the present invention.

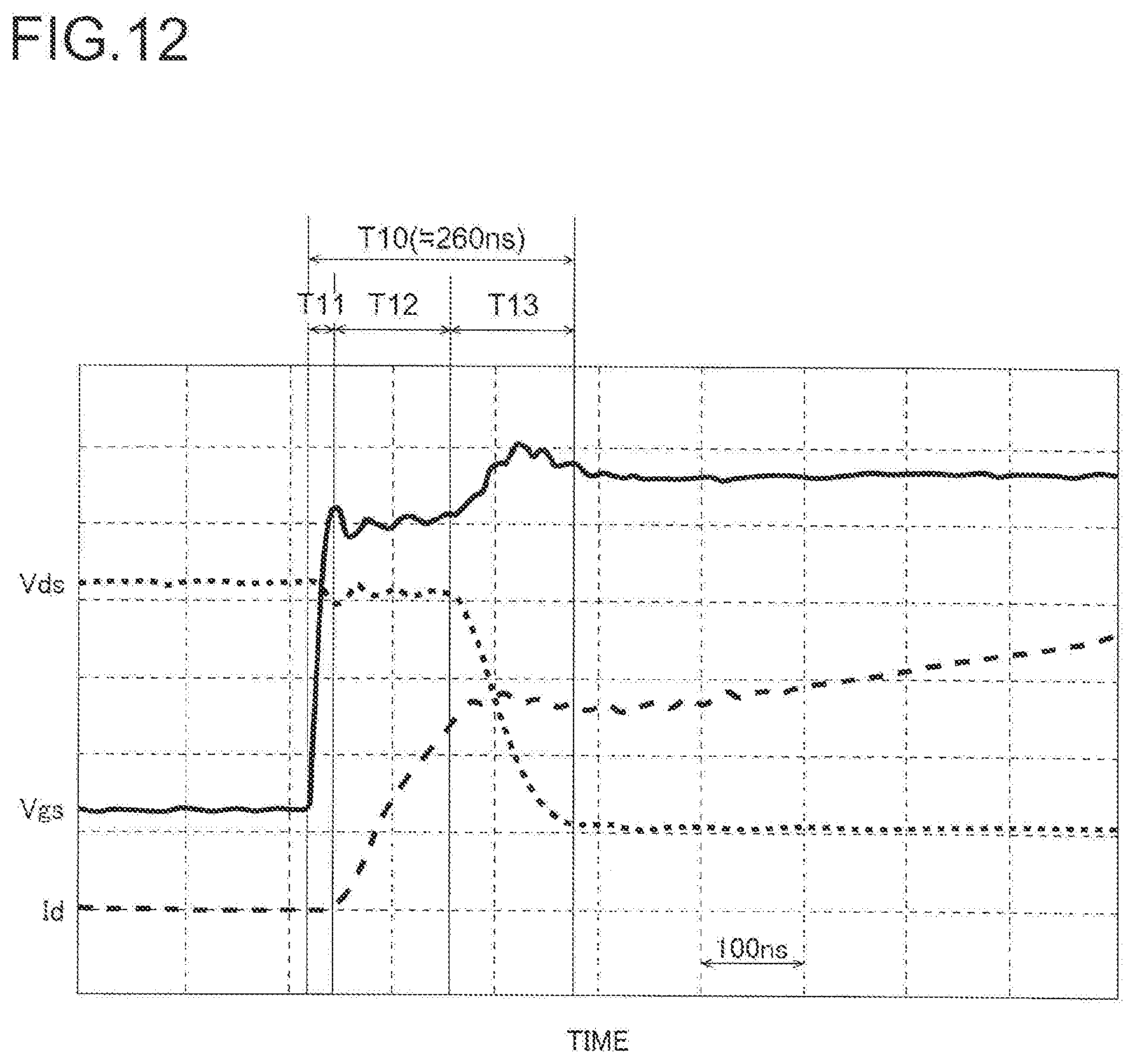

[0039] FIG. 12 is a switching waveform diagram of turn-on transient characteristics in this reference example.

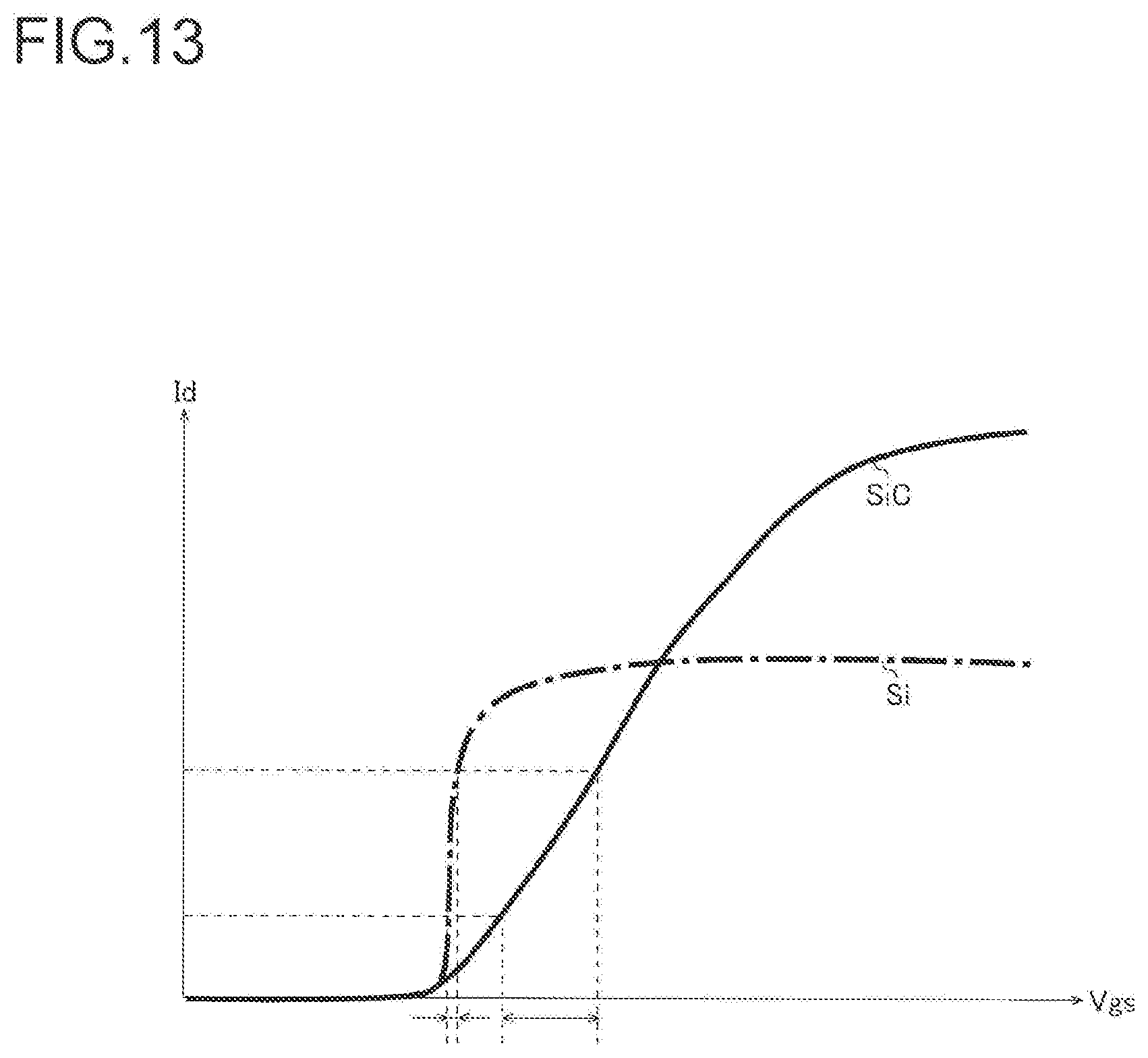

[0040] FIG. 13 is an Id-Vgs characteristic diagram.

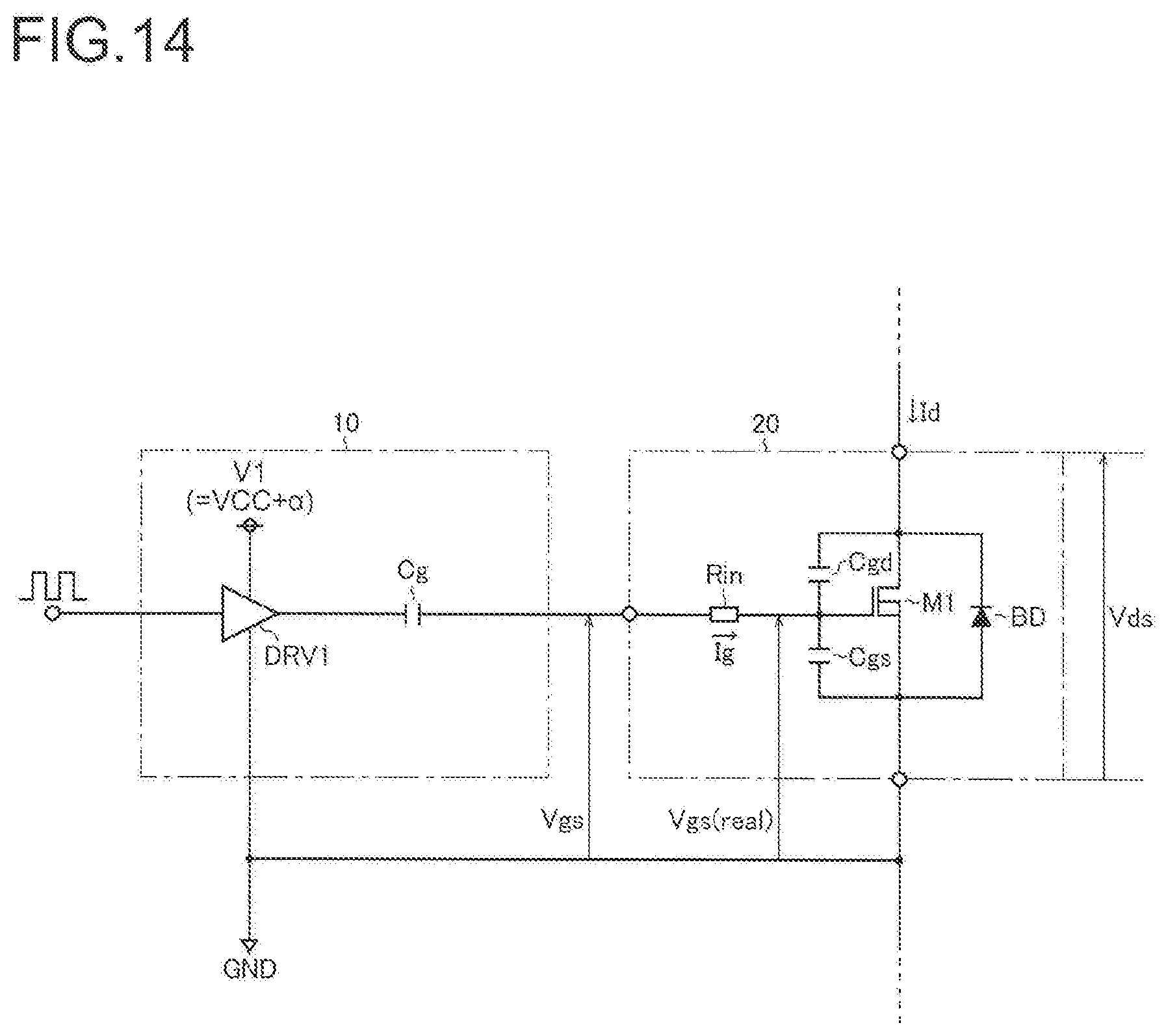

[0041] FIG. 14 is an equivalent circuit diagram illustrating a first embodiment of the gate drive circuit.

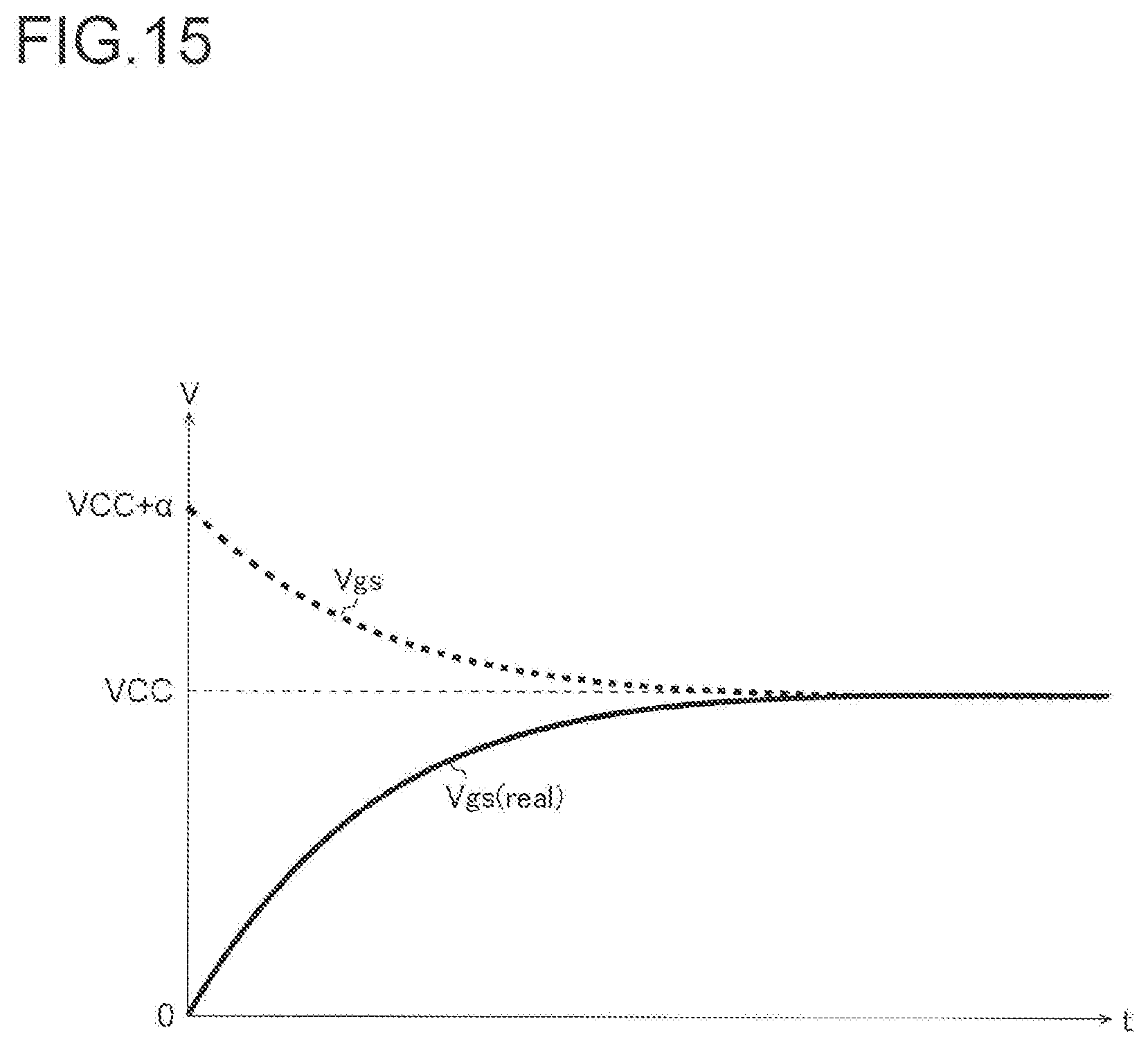

[0042] FIG. 15 is a voltage waveform diagram showing turn-on behaviors of Vgs and Vgs(real).

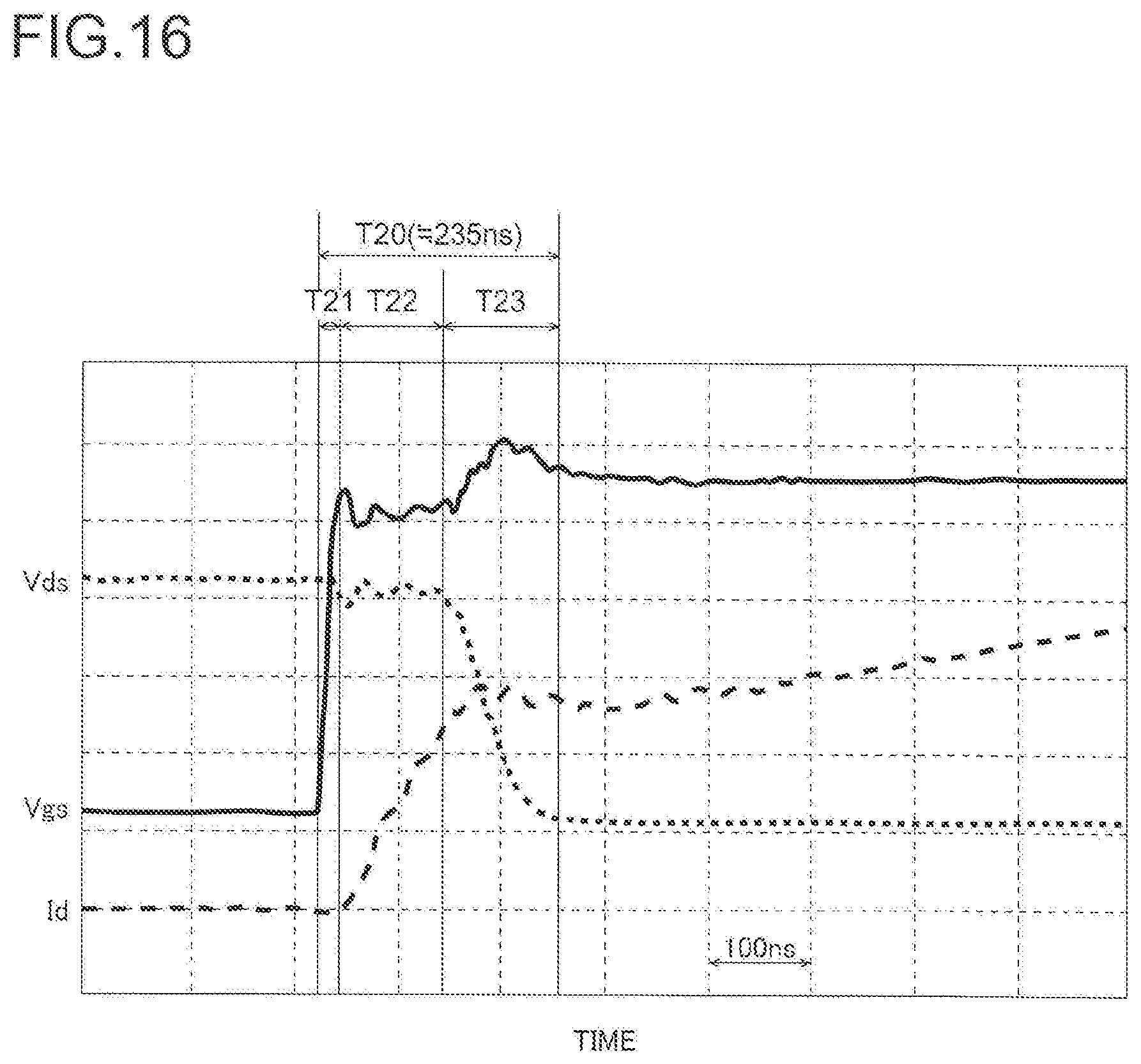

[0043] FIG. 16 is a switching waveform diagram showing turn-on transient characteristics in the first embodiment.

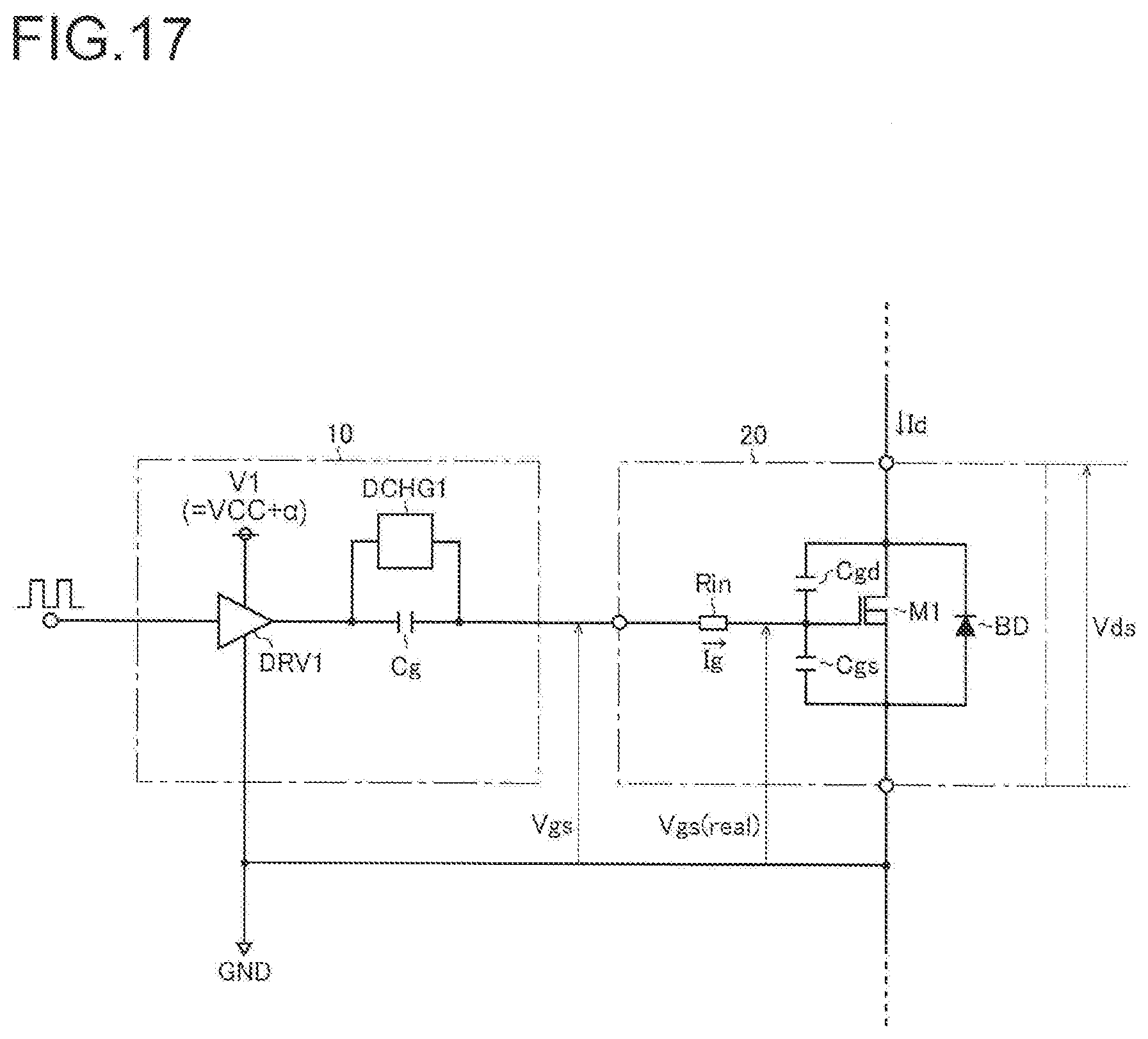

[0044] FIG. 17 is an equivalent circuit diagram illustrating a second embodiment of the gate drive circuit.

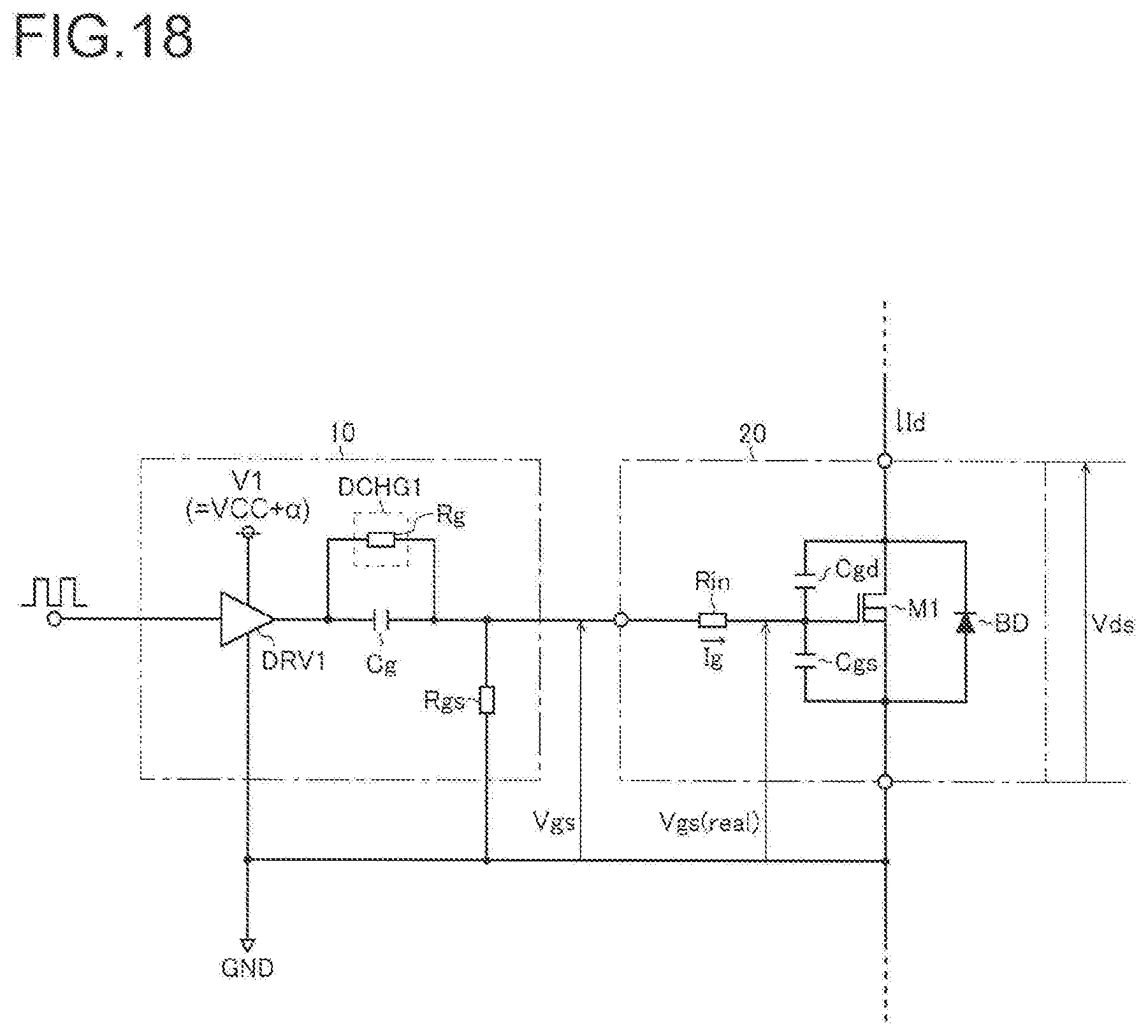

[0045] FIG. 18 is an equivalent circuit diagram illustrating a third embodiment of the gate drive circuit.

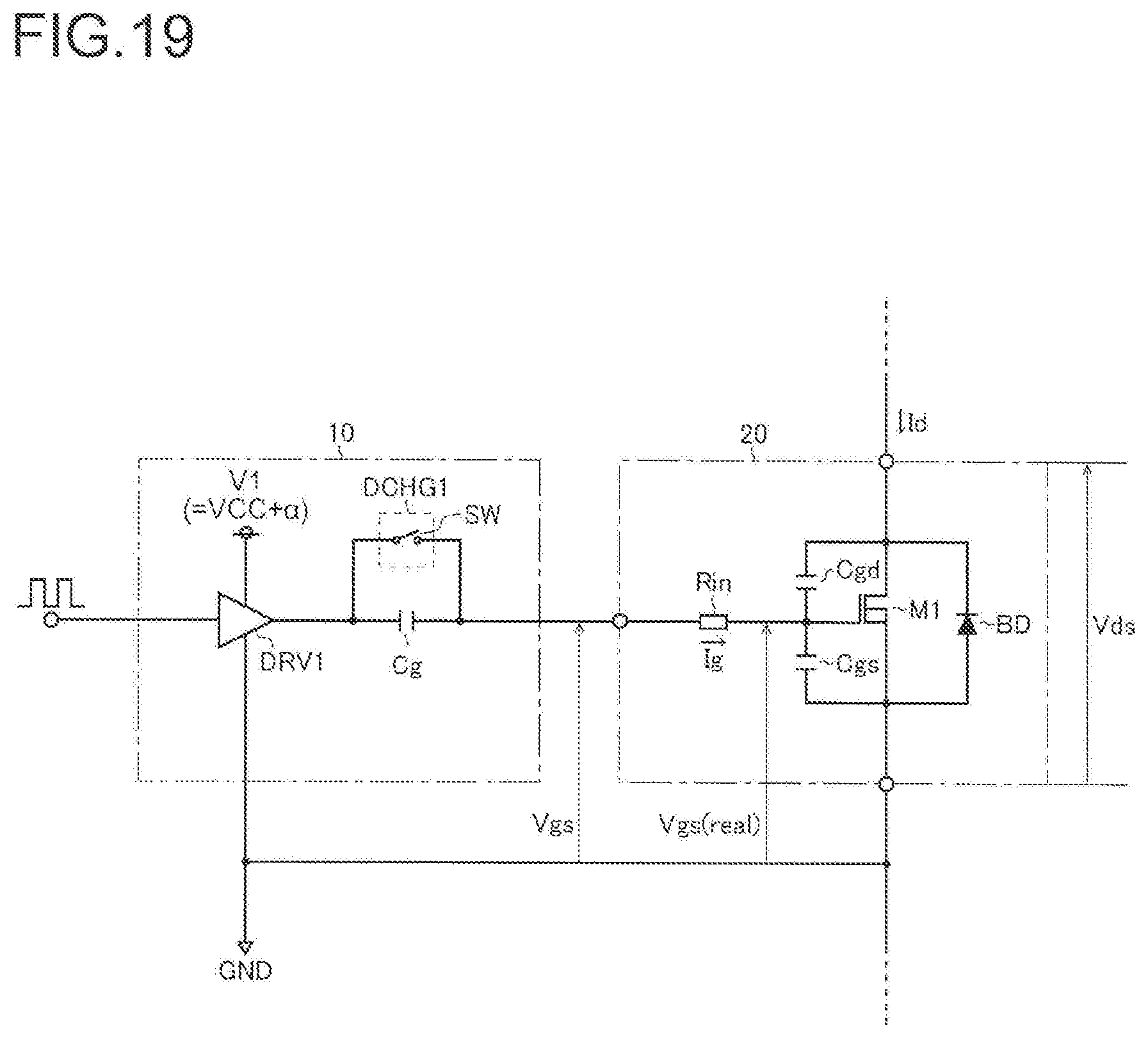

[0046] FIG. 19 is an equivalent circuit diagram illustrating a fourth embodiment of the gate drive circuit.

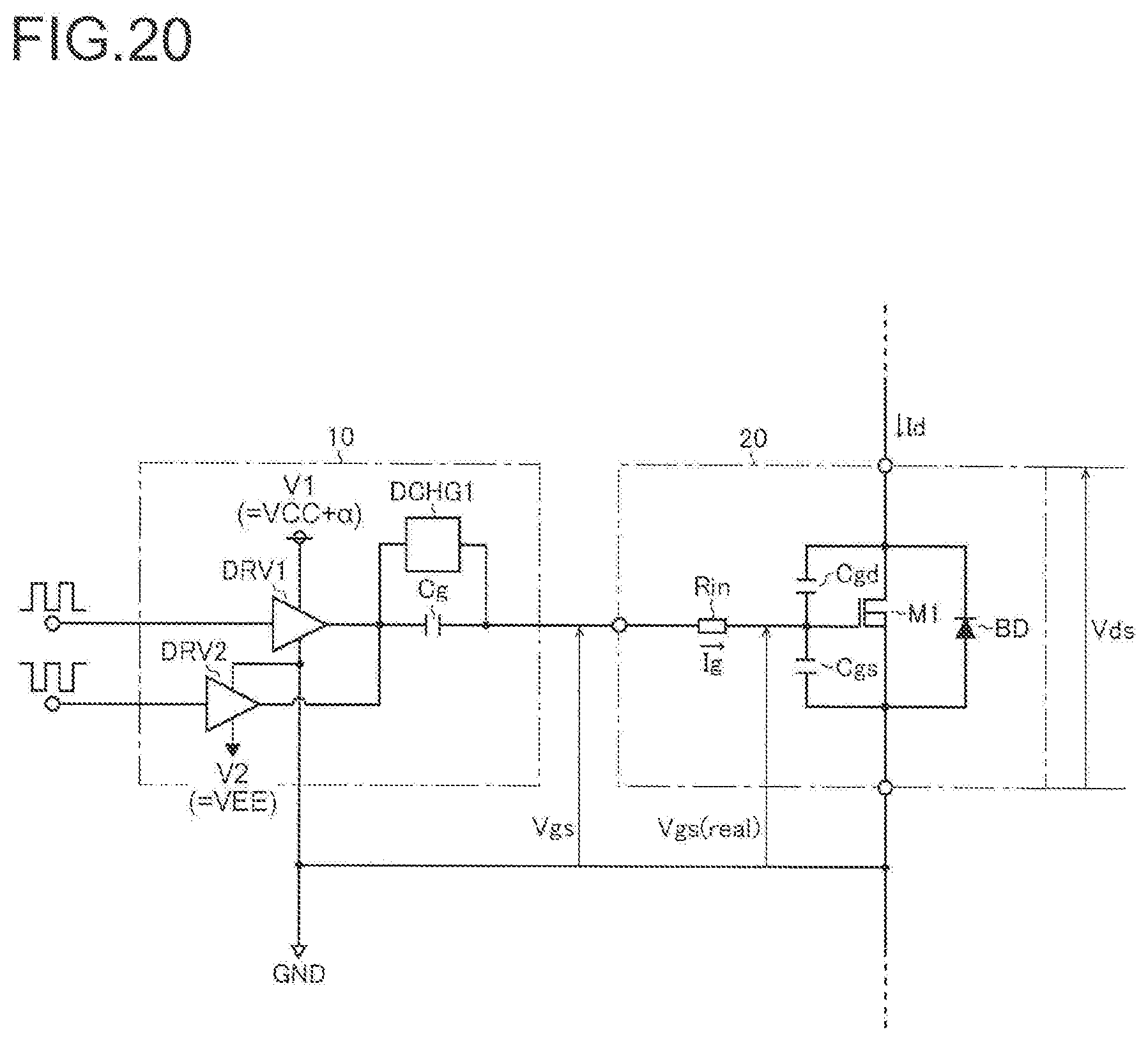

[0047] FIG. 20 is an equivalent circuit diagram illustrating a fifth embodiment of the gate drive circuit.

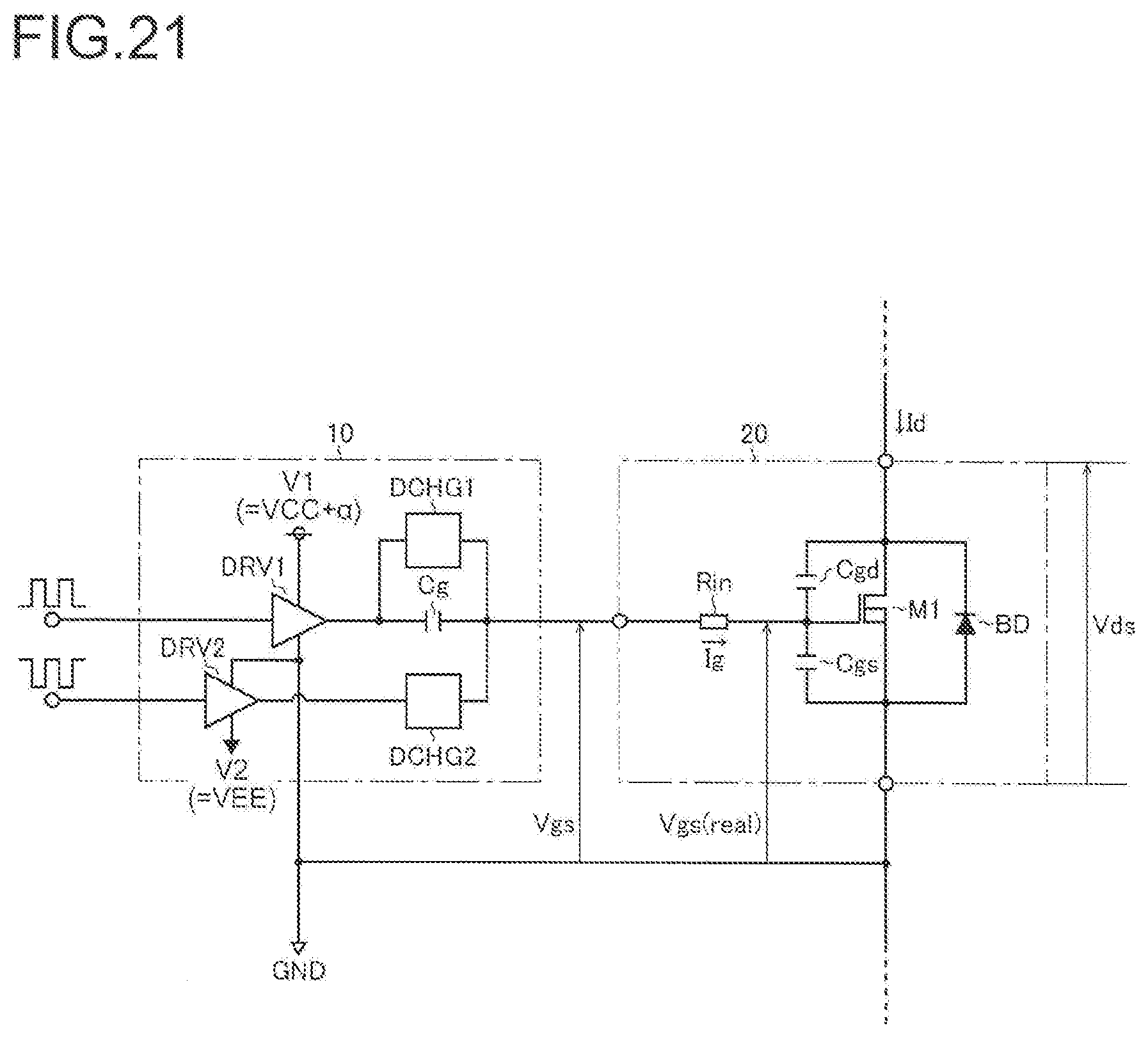

[0048] FIG. 21 is an equivalent circuit diagram illustrating a sixth embodiment of the gate drive circuit.

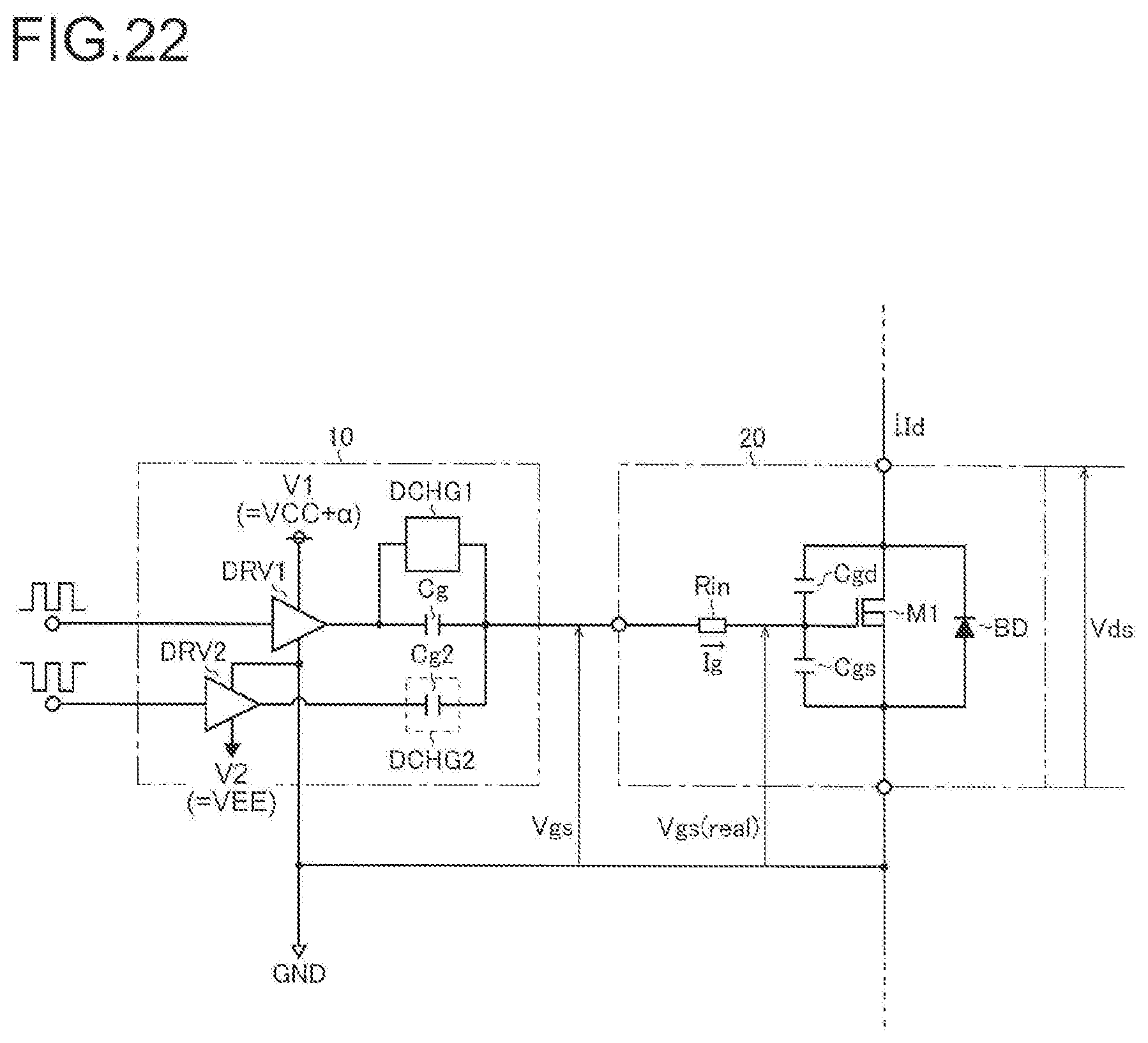

[0049] FIG. 22 is an equivalent circuit diagram illustrating a seventh embodiment of the gate drive circuit.

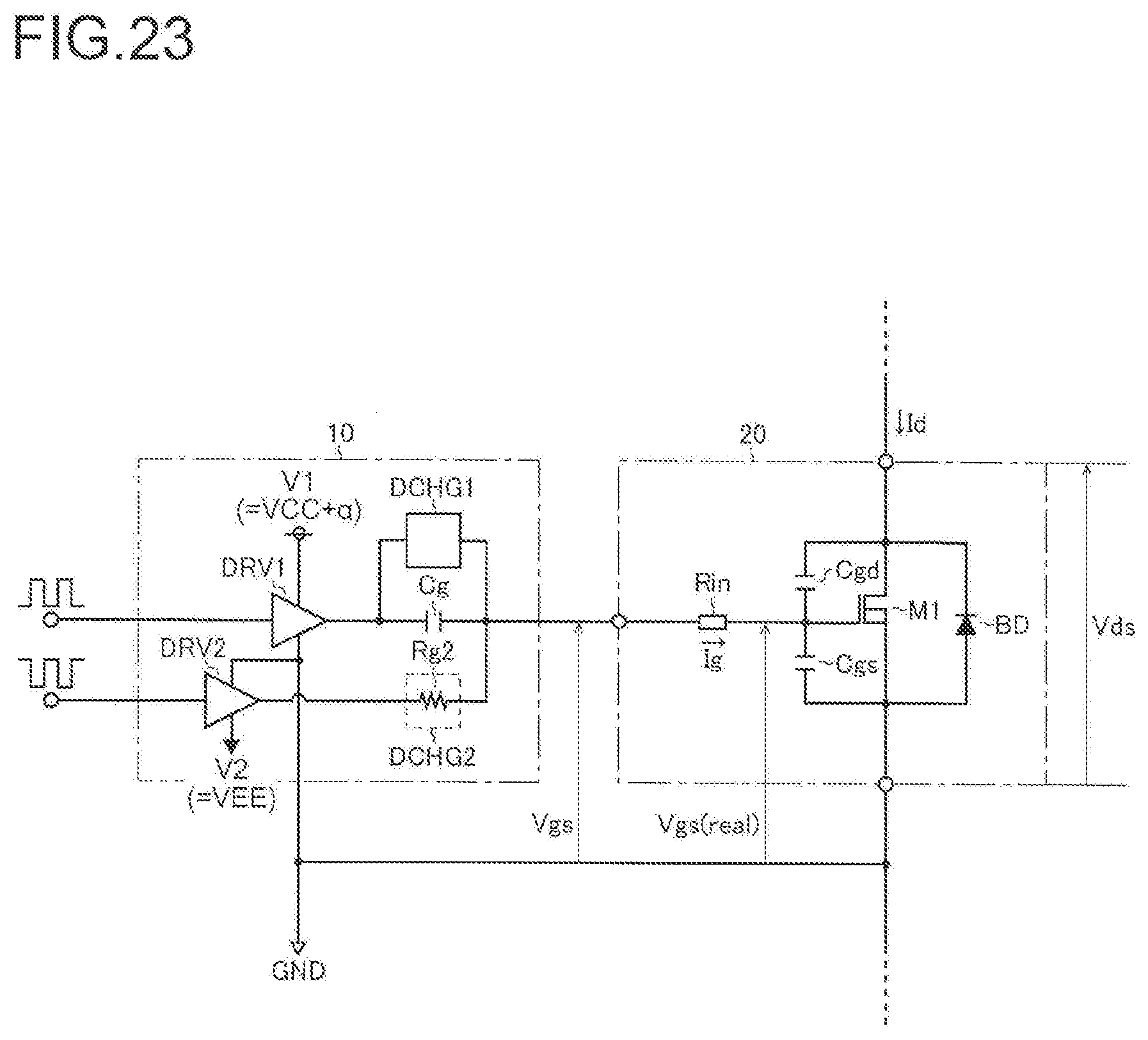

[0050] FIG. 23 is an equivalent circuit diagram illustrating an eighth embodiment of the gate drive circuit.

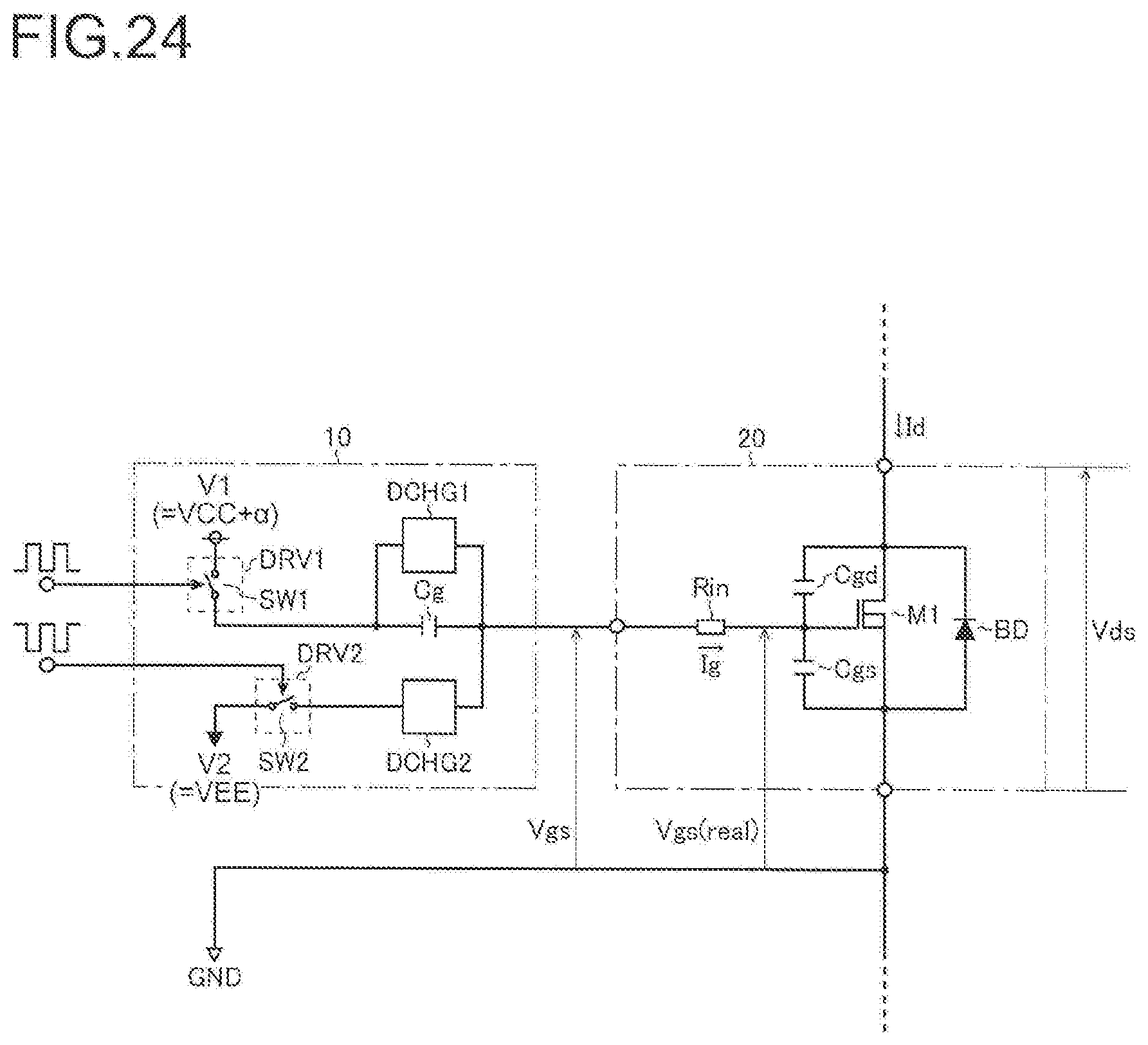

[0051] FIG. 24 is an equivalent circuit diagram illustrating a ninth embodiment of the gate drive circuit.

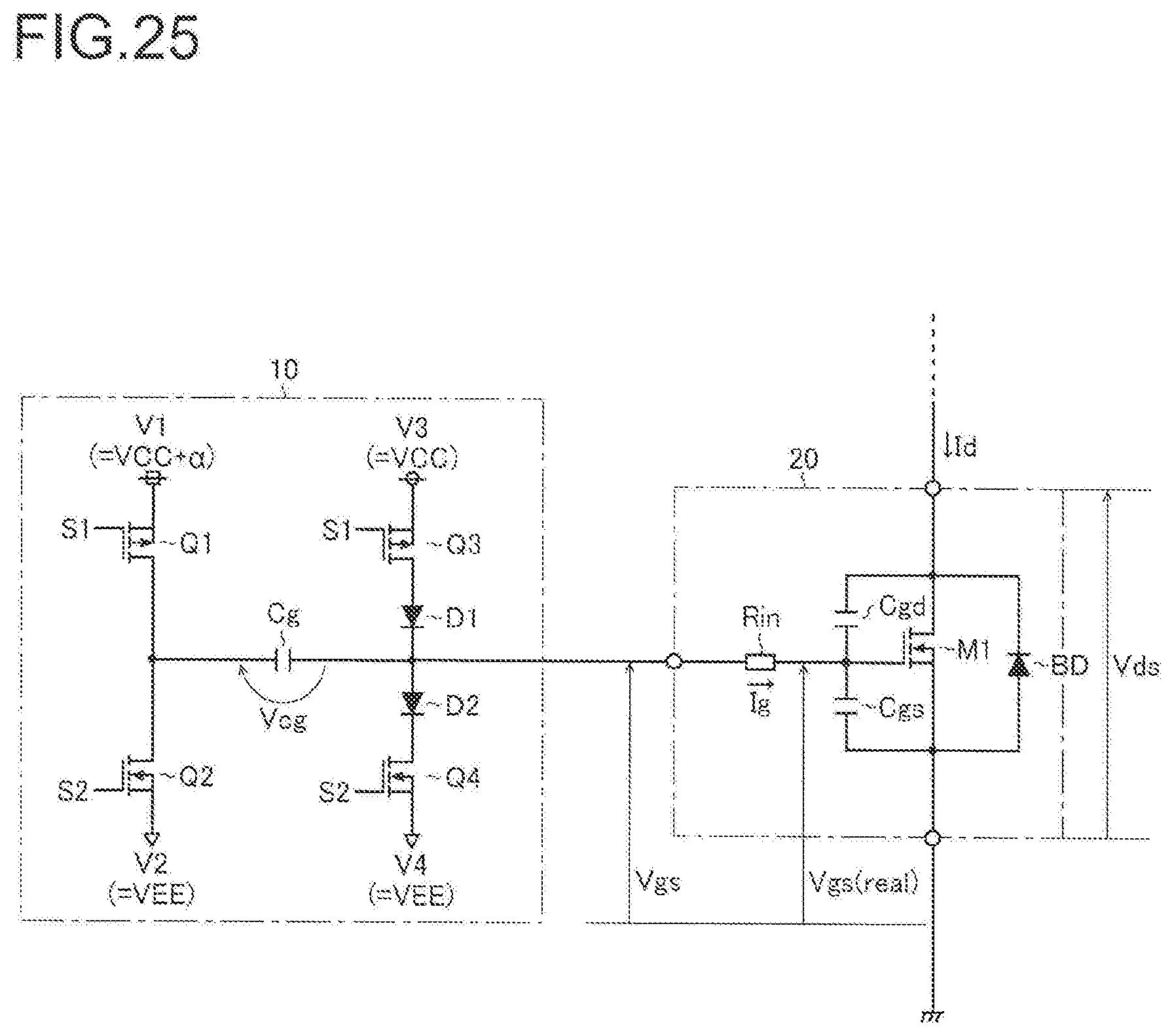

[0052] FIG. 25 is an equivalent circuit diagram illustrating a tenth embodiment of the gate drive circuit.

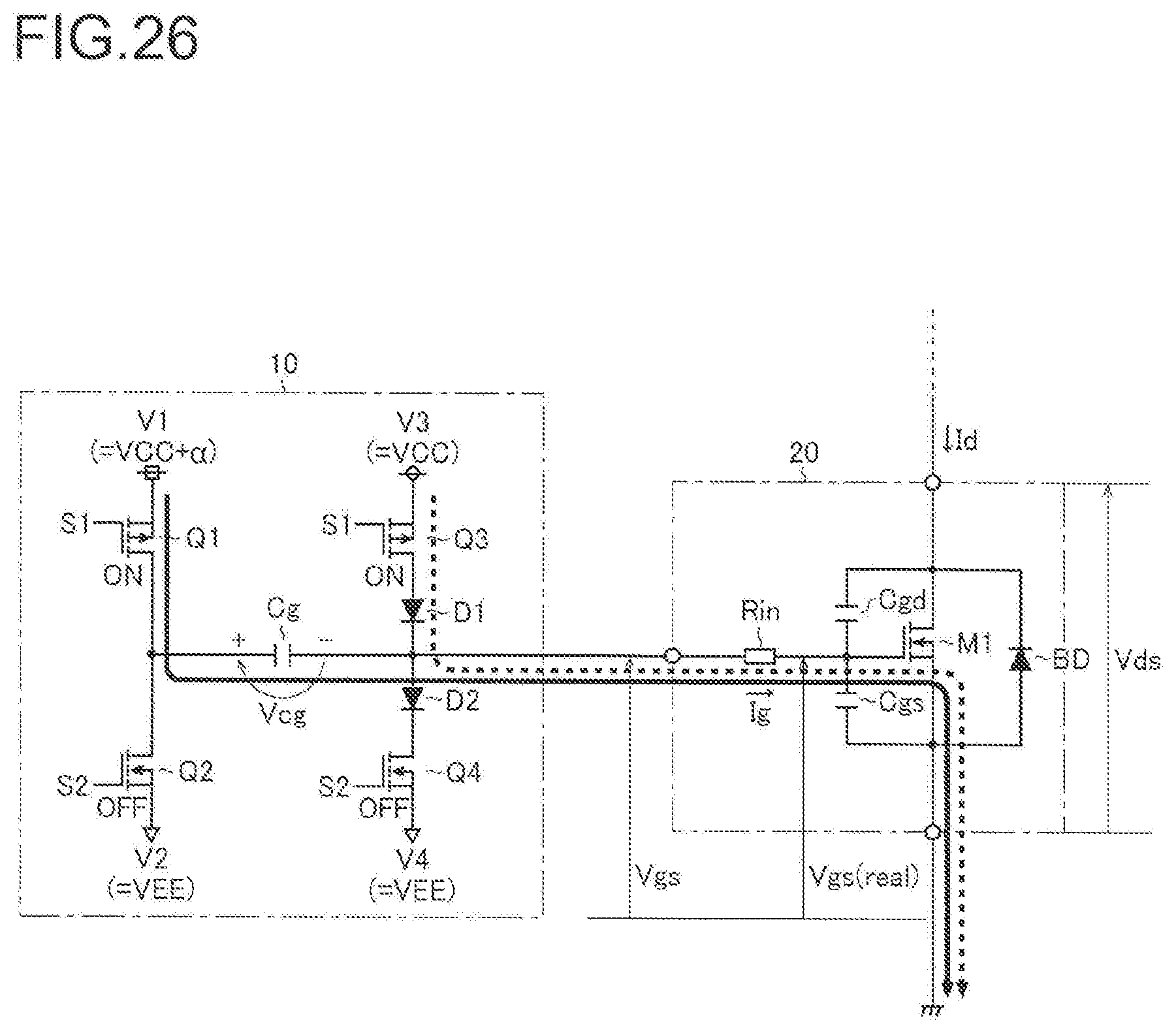

[0053] FIG. 26 is a current path diagram for explaining a principle of operation (when being turned on) of the tenth embodiment.

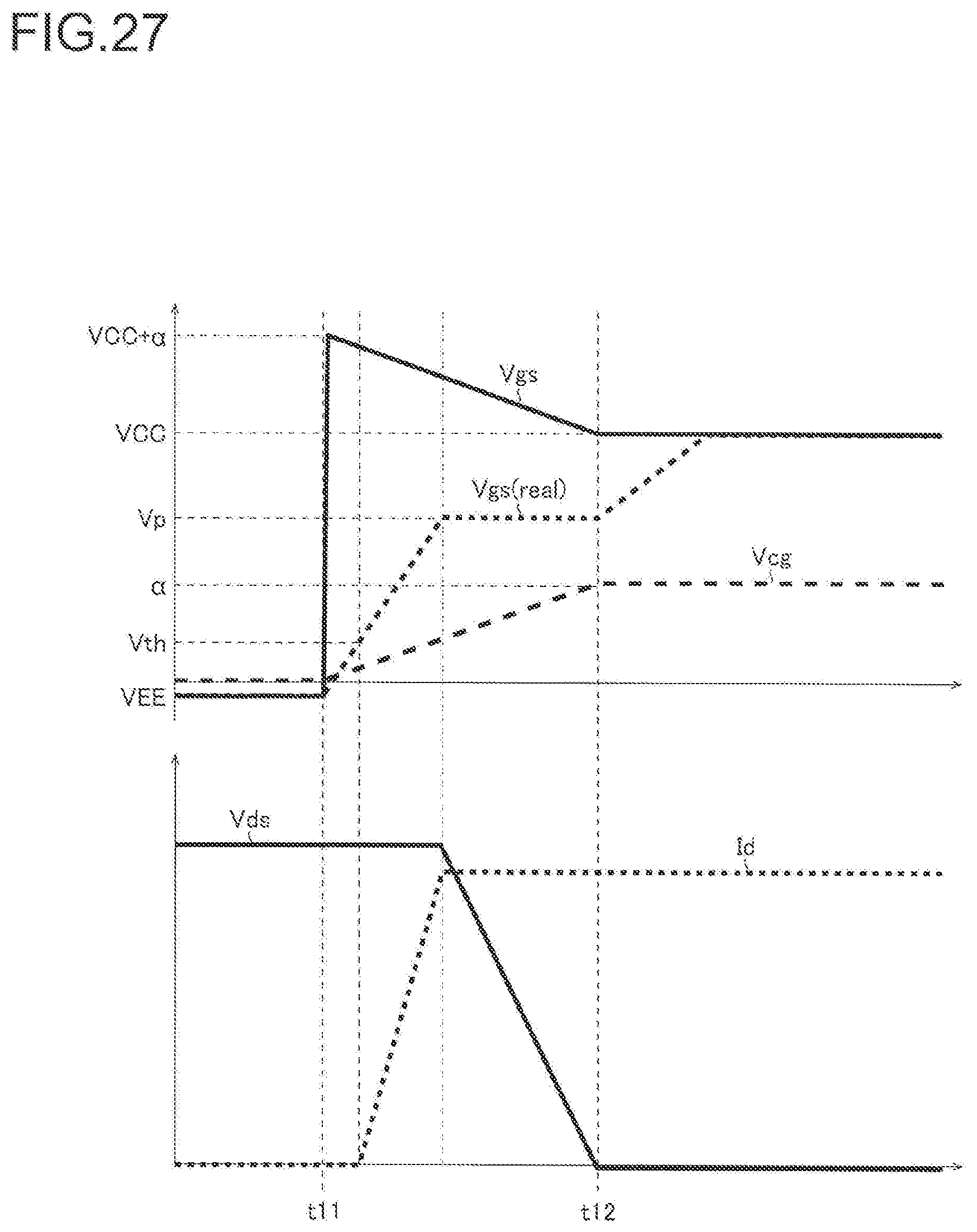

[0054] FIG. 27 is a switching waveform diagram showing turn-on transient characteristics in the tenth embodiment.

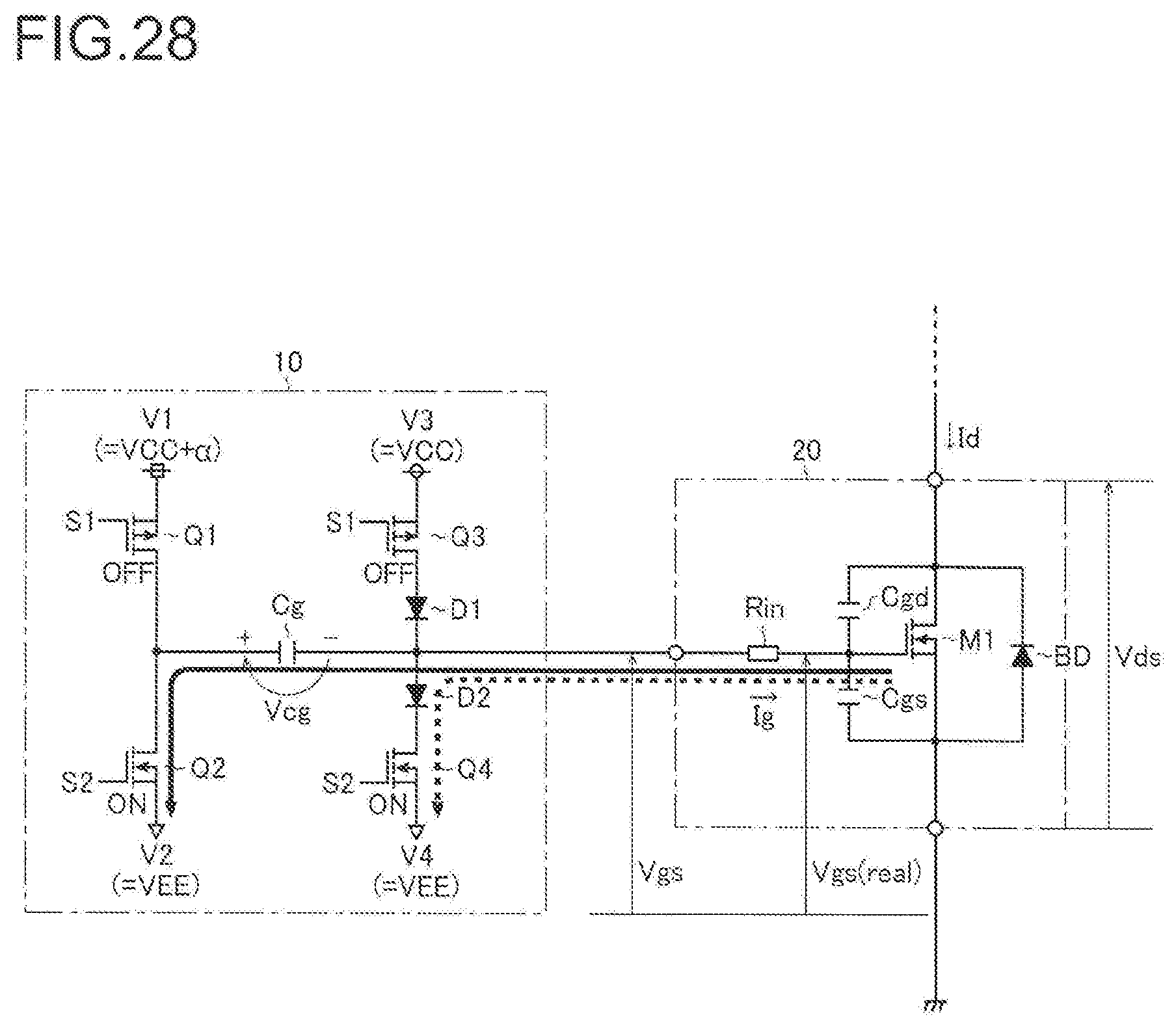

[0055] FIG. 28 is a current path diagram for explaining a principle of operation (when being turned off) of the tenth embodiment.

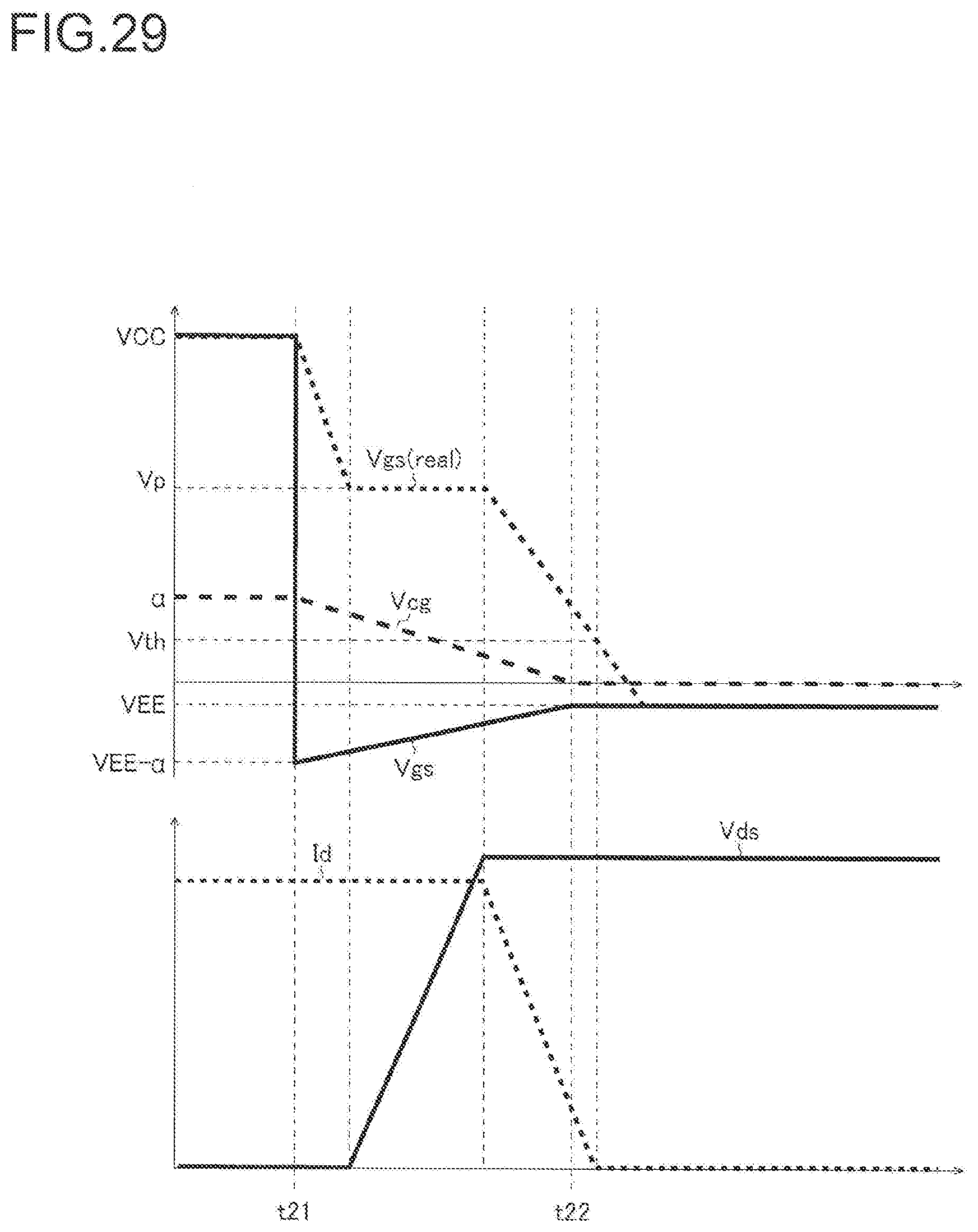

[0056] FIG. 29 is a switching waveform diagram showing turn-off transient characteristics in the tenth embodiment.

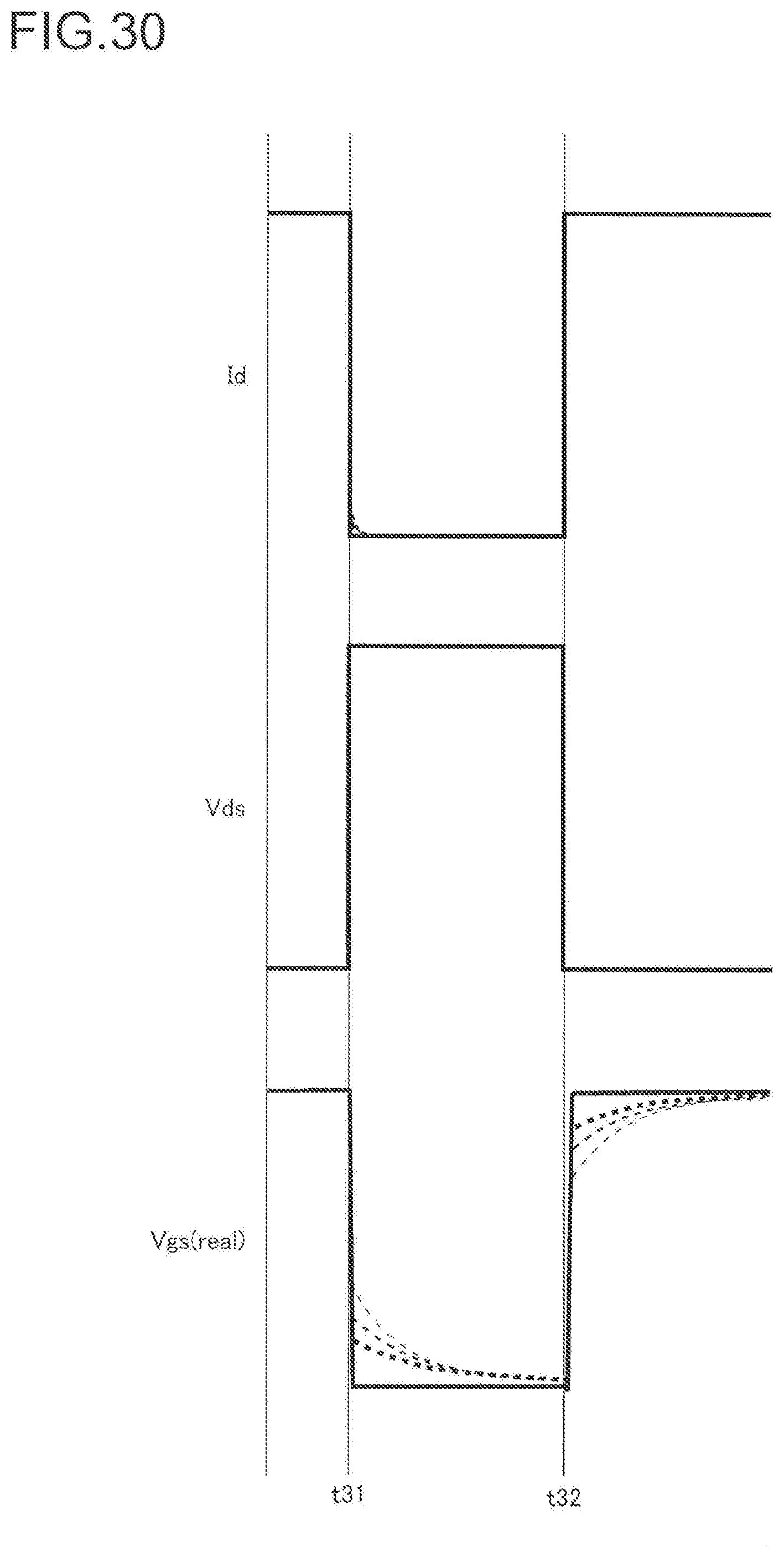

[0057] FIG. 30 is a switching waveform diagram for comparatively explaining an influence of capacitance variation.

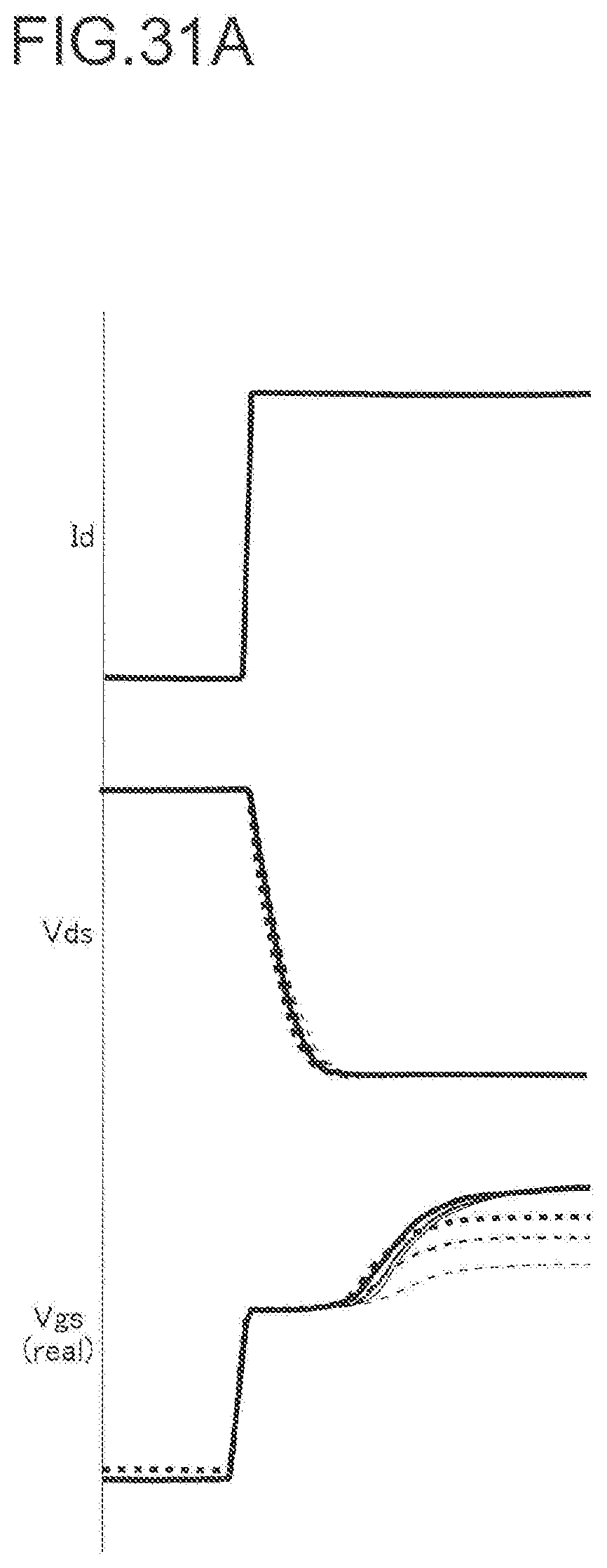

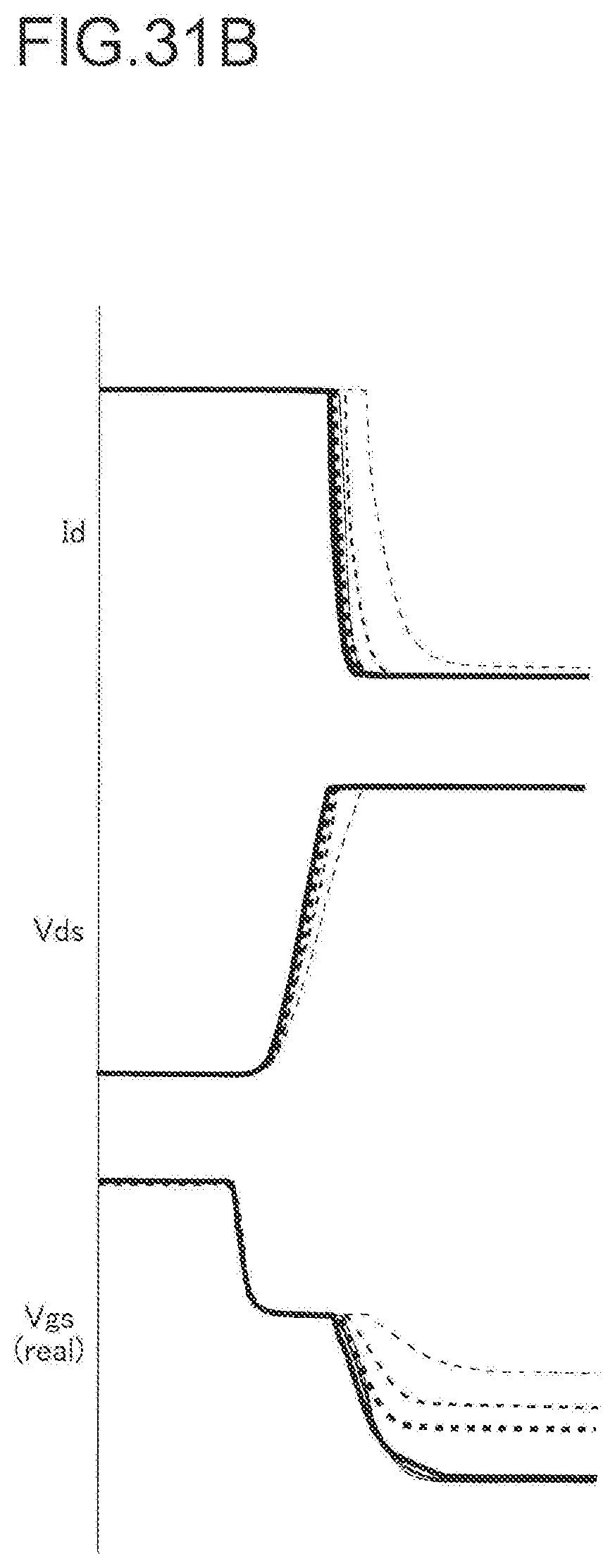

[0058] FIG. 31A is a partial enlarged view (when being turned on) FIG. 20.

[0059] FIG. 31B is a partial enlarged view (when being turned off) of FIG. 20.

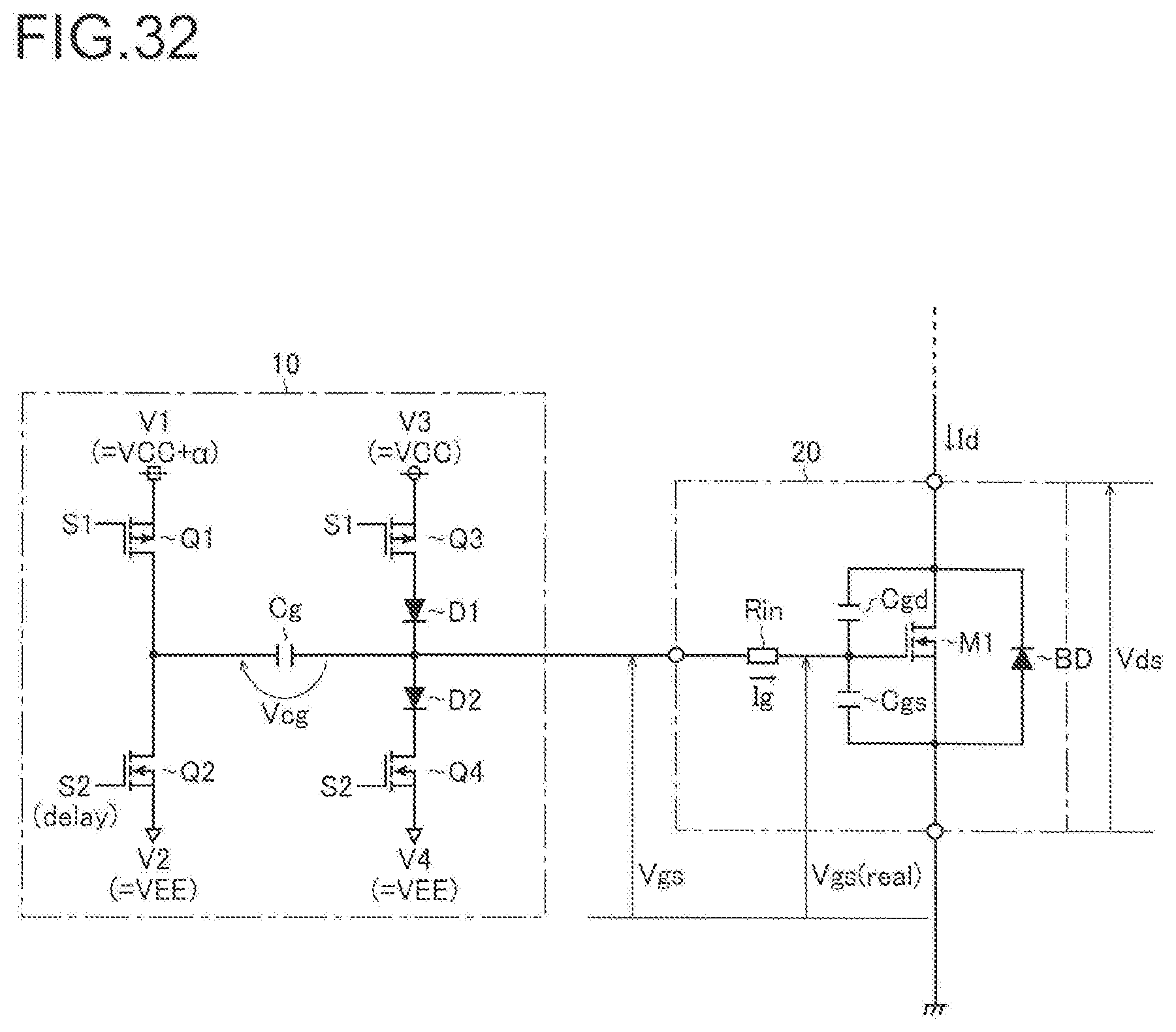

[0060] FIG. 32 is an equivalent circuit diagram illustrating an eleventh embodiment of the gate drive circuit.

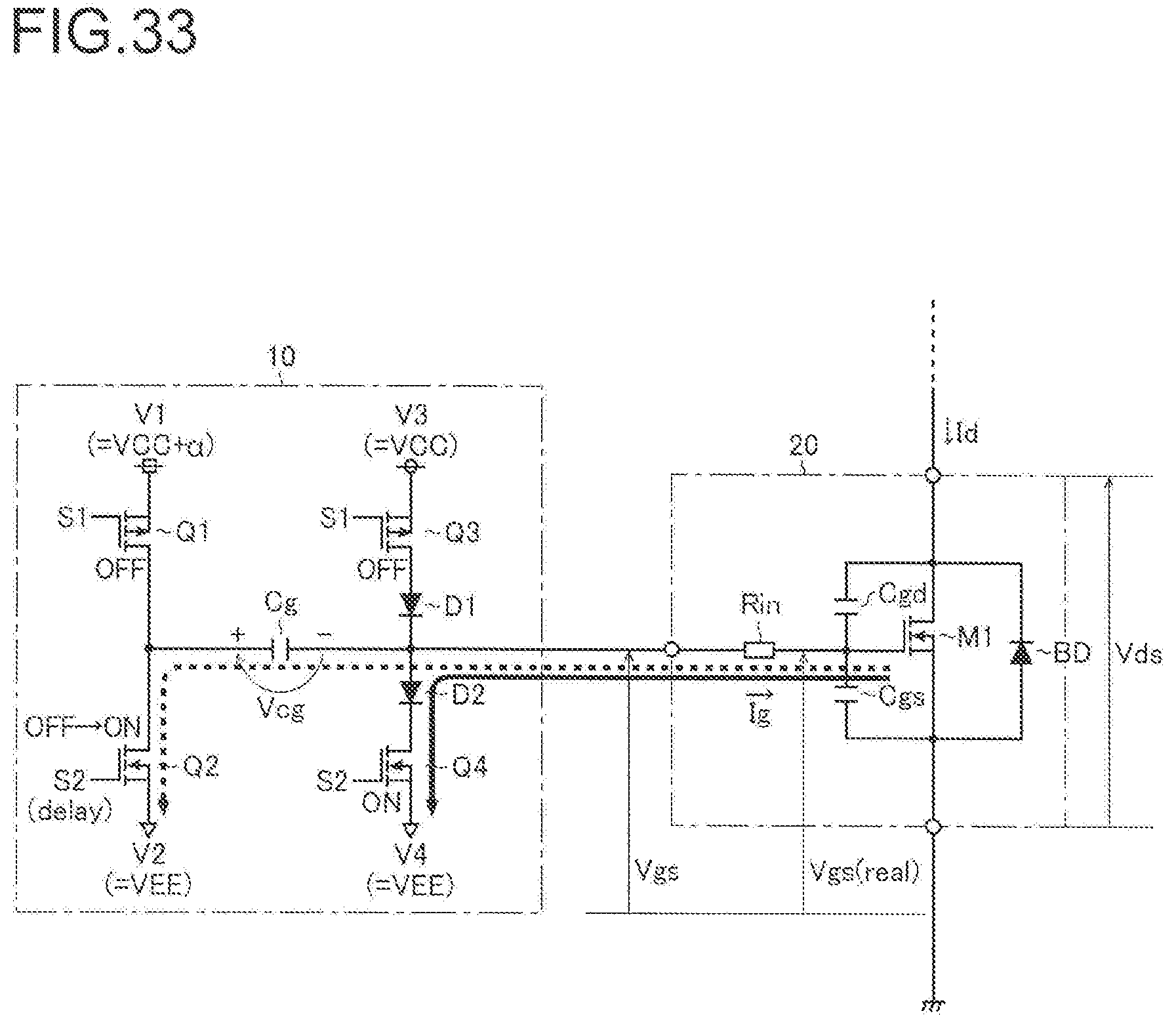

[0061] FIG. 33 is a current path diagram for explaining a principle of operation (when being turned off) in the eleventh embodiment.

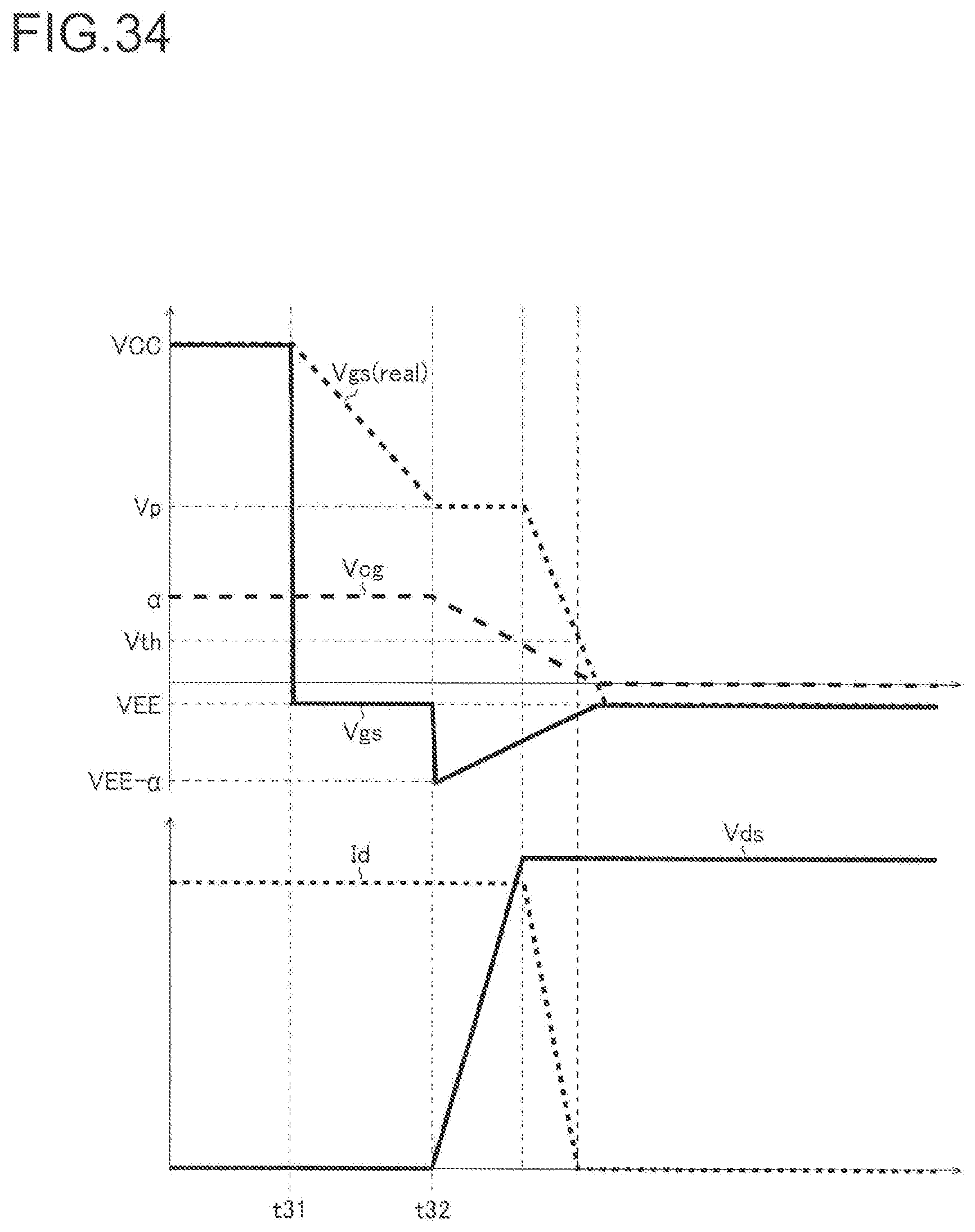

[0062] FIG. 34 is a switching waveform diagram of turn-off transient characteristics in the eleventh embodiment.

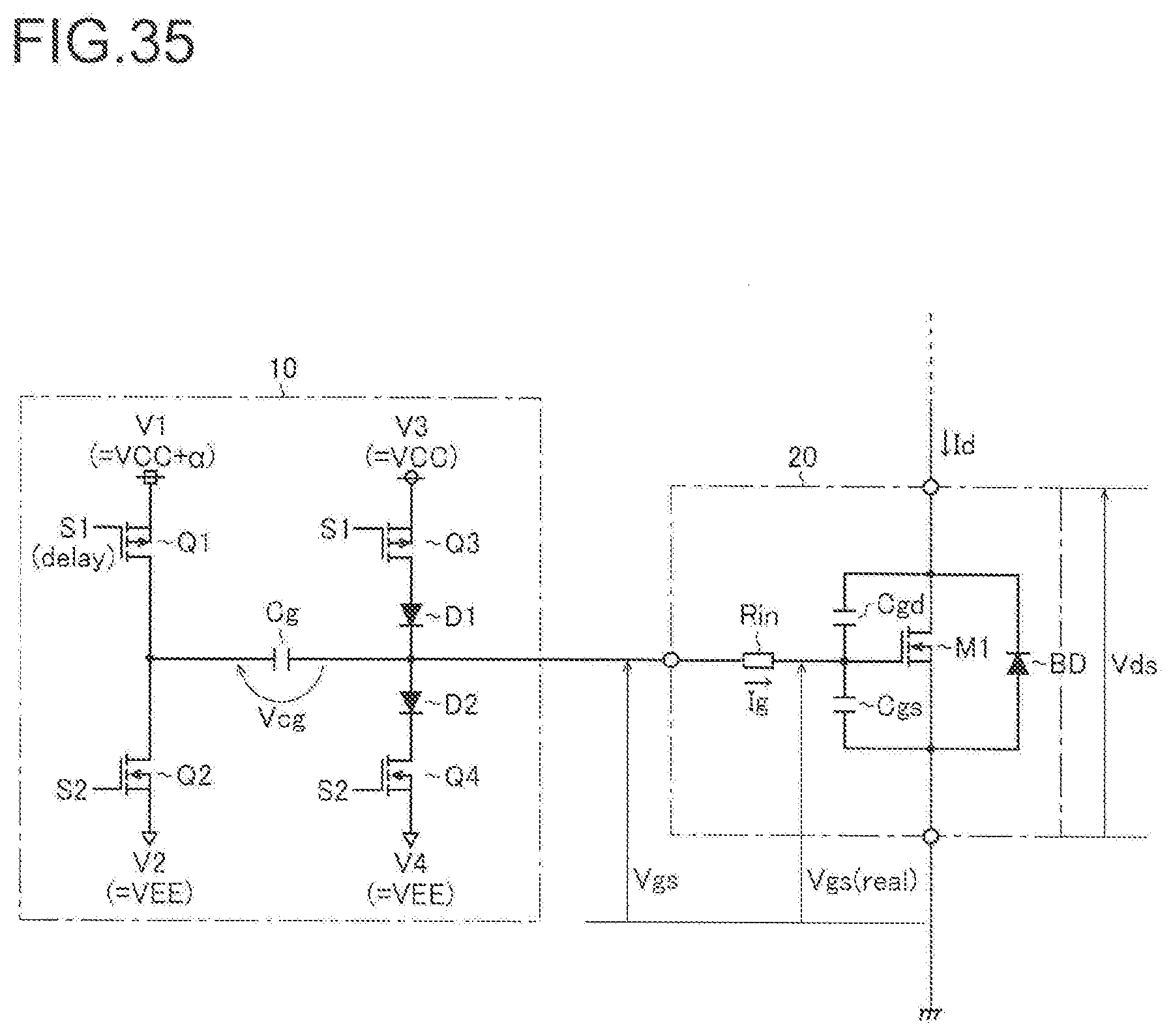

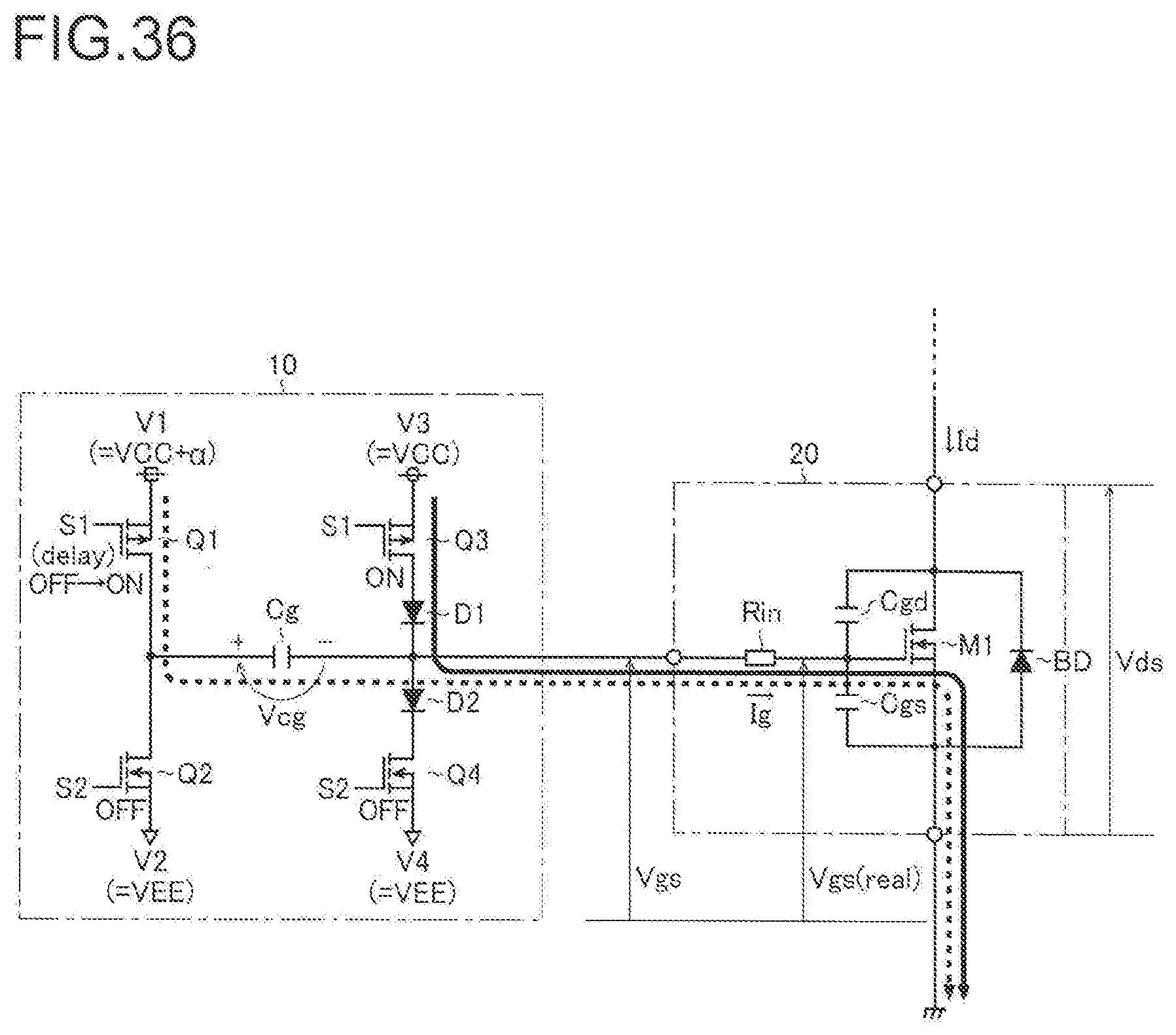

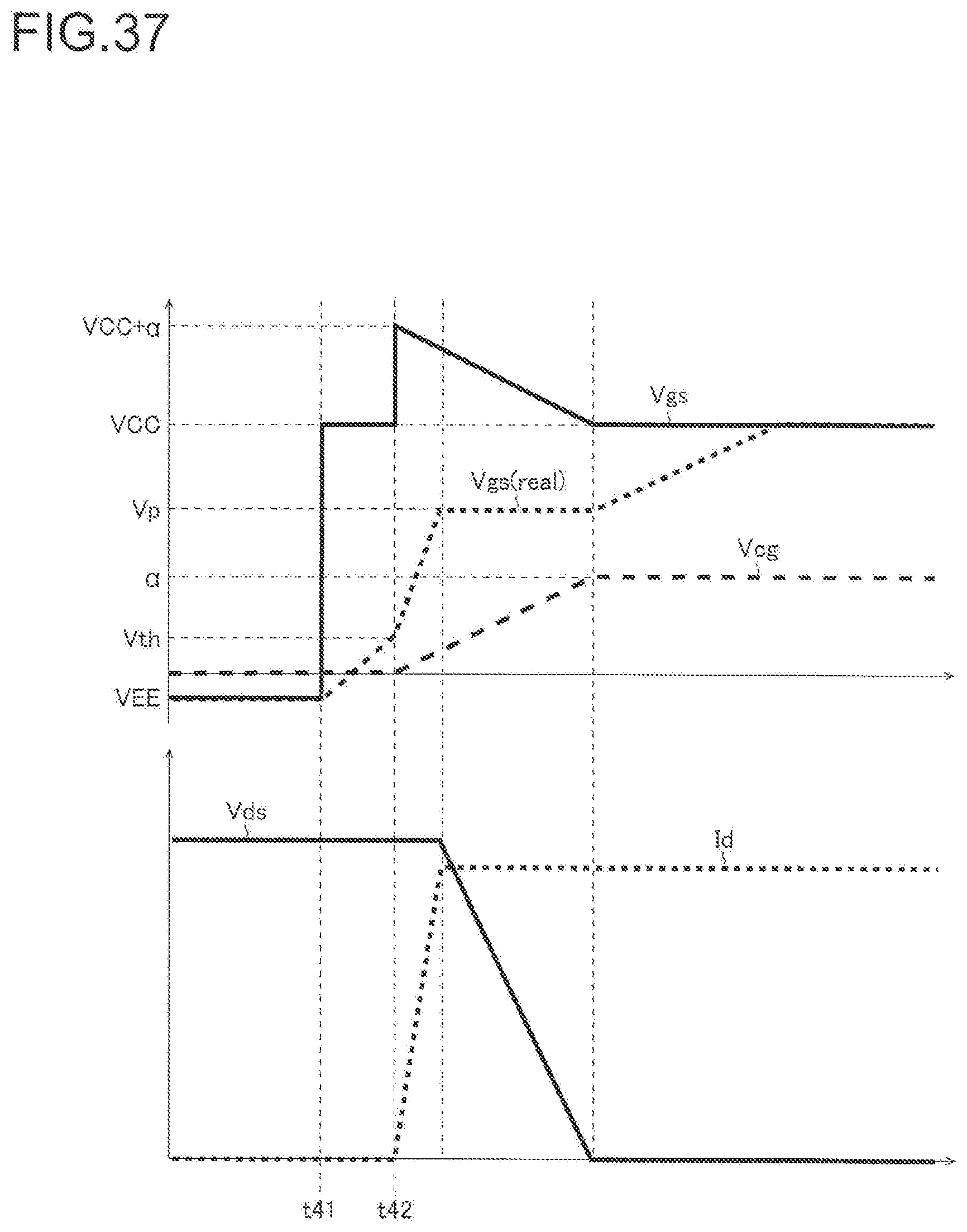

[0063] FIG. 35 is an equivalent circuit diagram illustrating a twelfth embodiment of the gate drive circuit.

[0064] FIG. 36 is a current path diagram for explaining a principle of operation (when being turned on) in the twelfth embodiment.

[0065] FIG. 37 is a switching waveform diagram of turn-on transient characteristics in the twelfth embodiment.

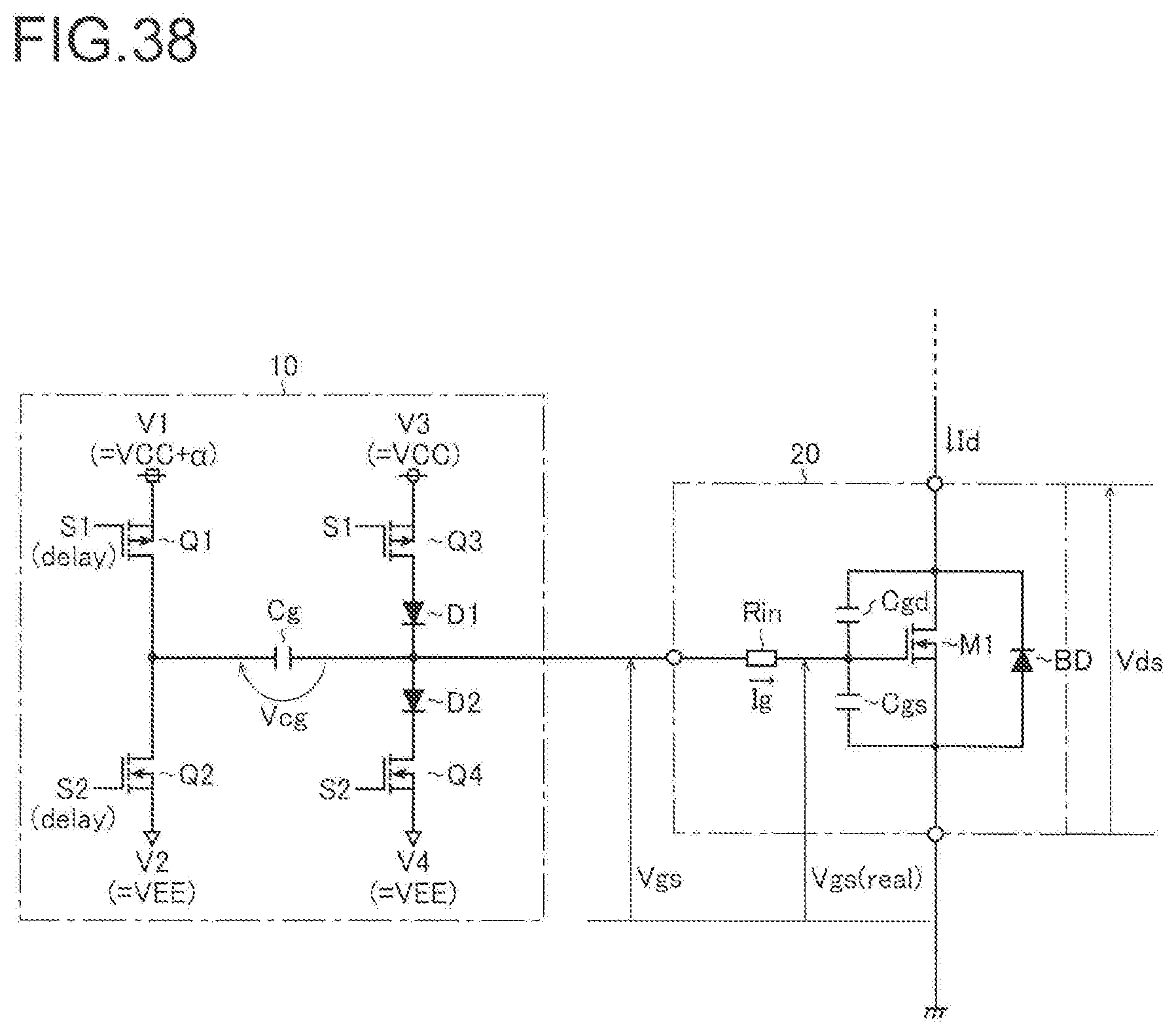

[0066] FIG. 38 is an equivalent circuit diagram illustrating a thirteenth embodiment of the gate drive circuit.

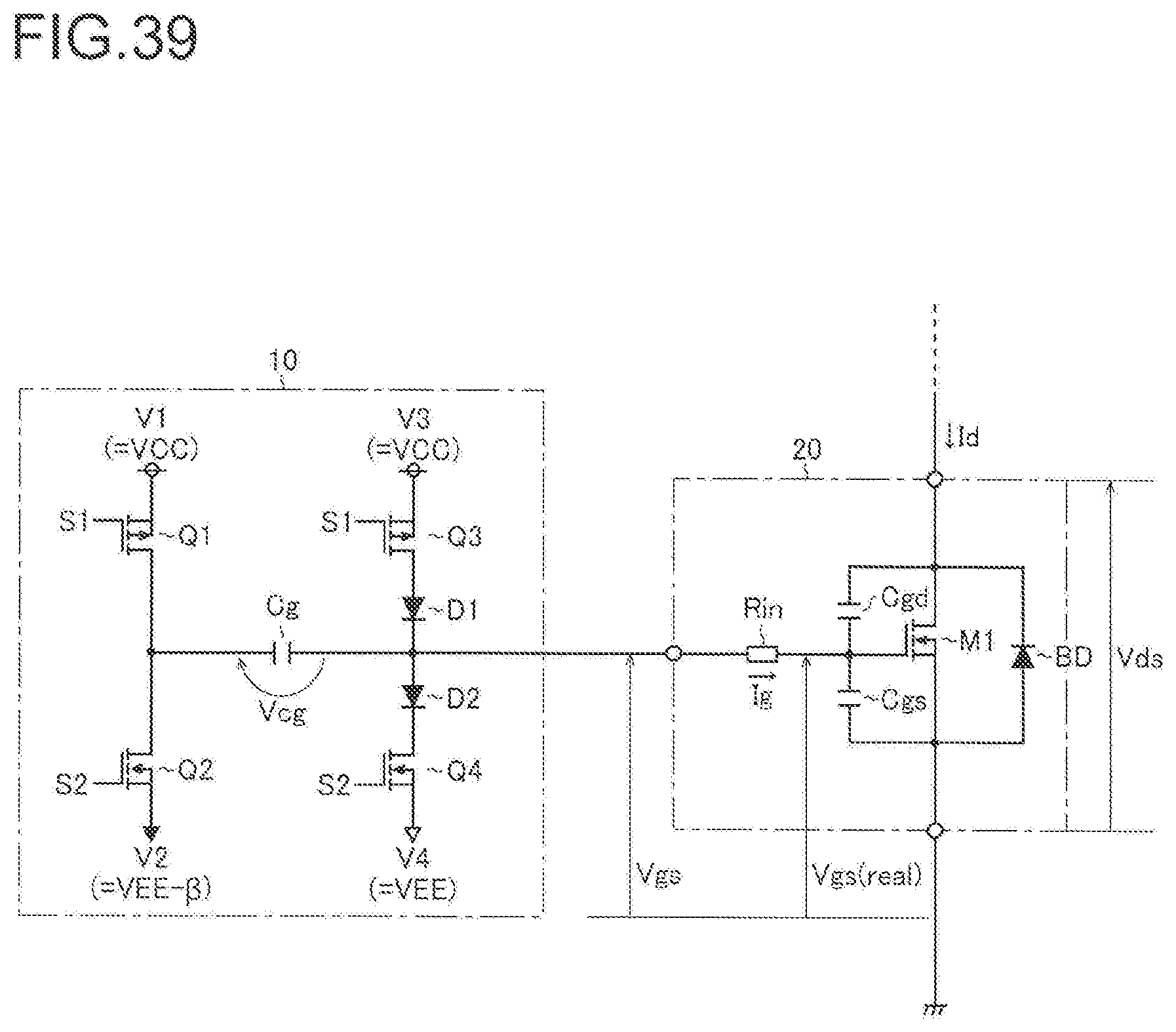

[0067] FIG. 39 is an equivalent circuit diagram illustrating a fourteenth embodiment of the gate drive circuit.

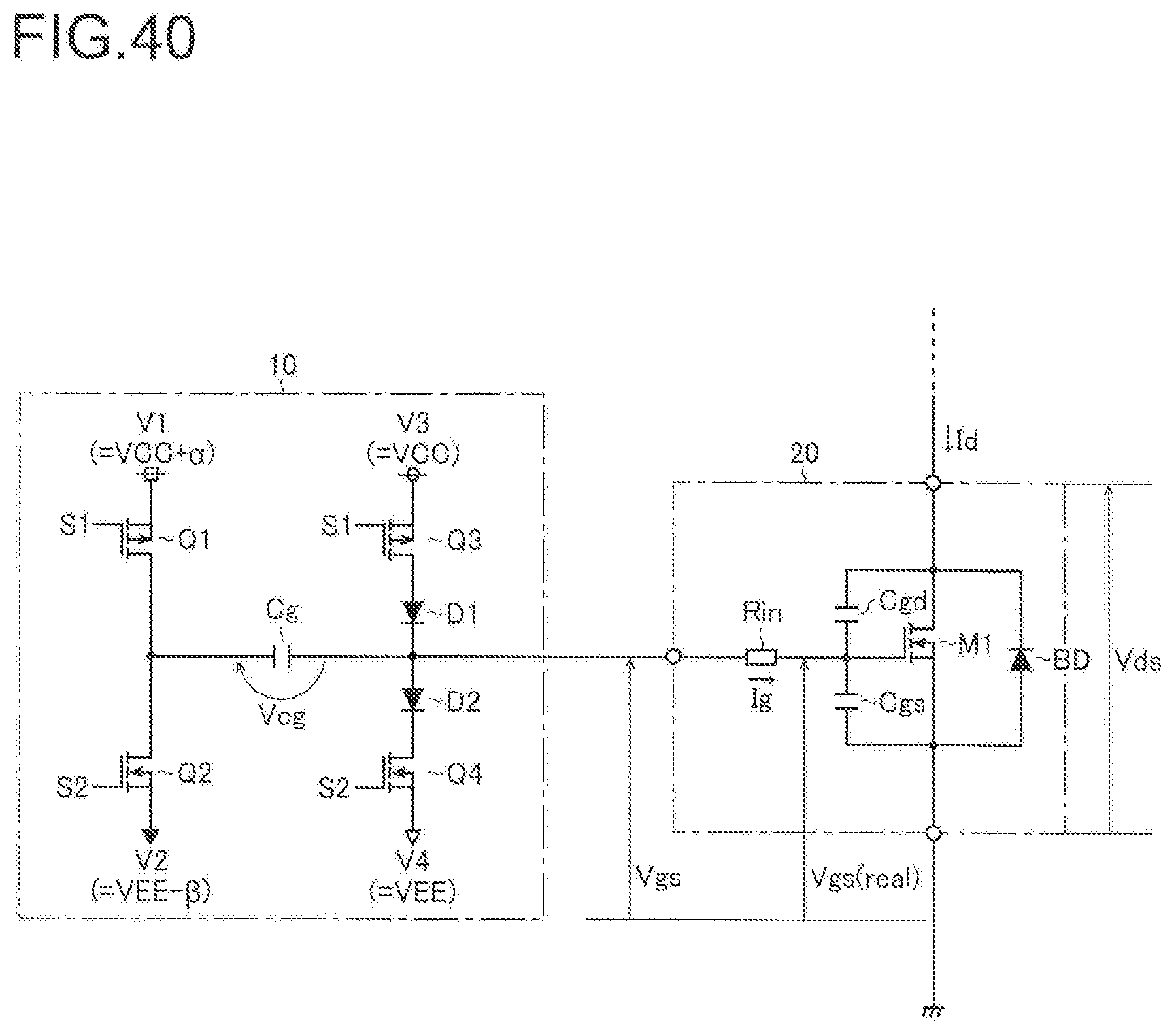

[0068] FIG. 40 is an equivalent circuit diagram illustrating a fifteenth embodiment of the gate drive circuit.

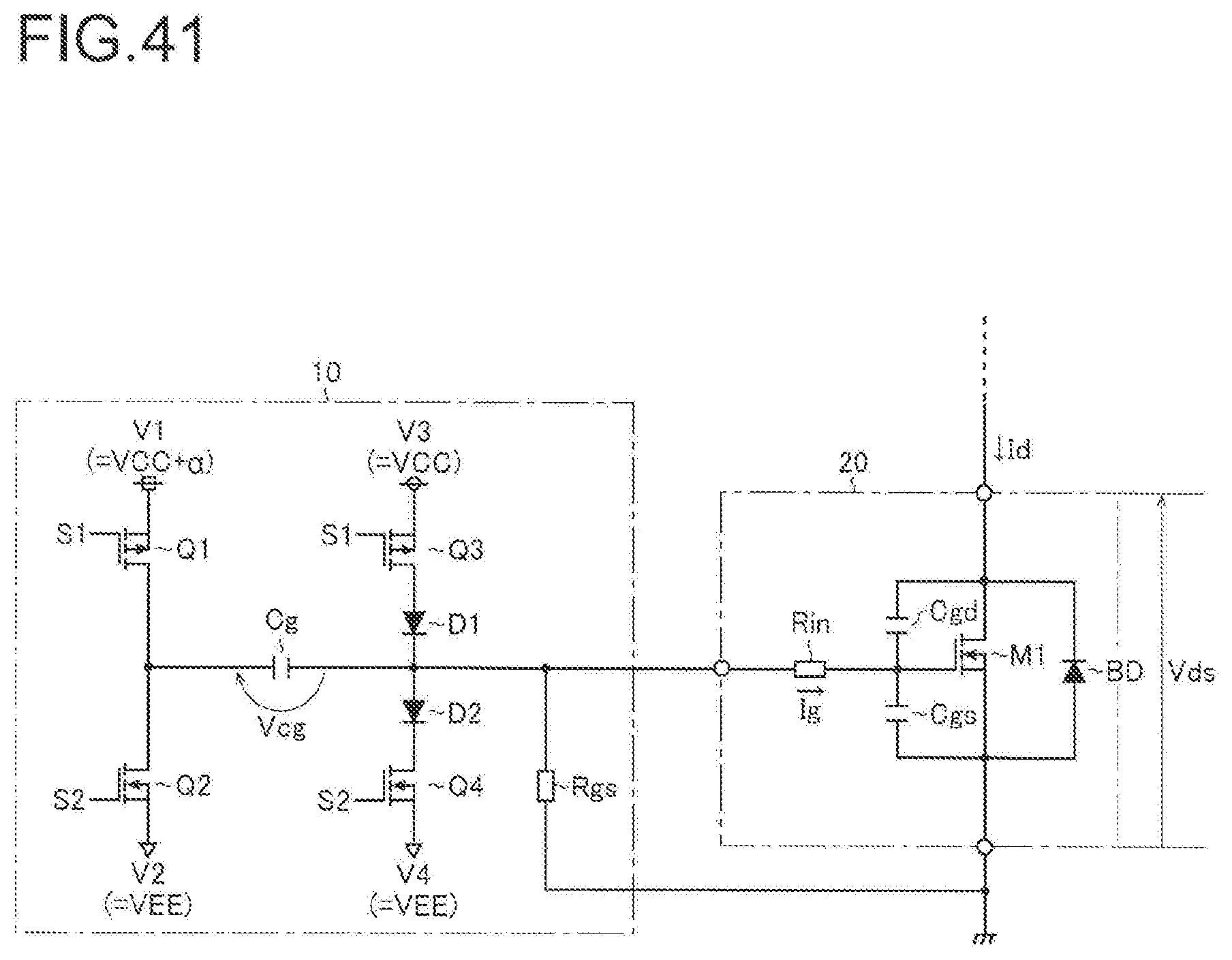

[0069] FIG. 41 is an equivalent circuit diagram illustrating a sixteenth embodiment of the gate drive circuit.

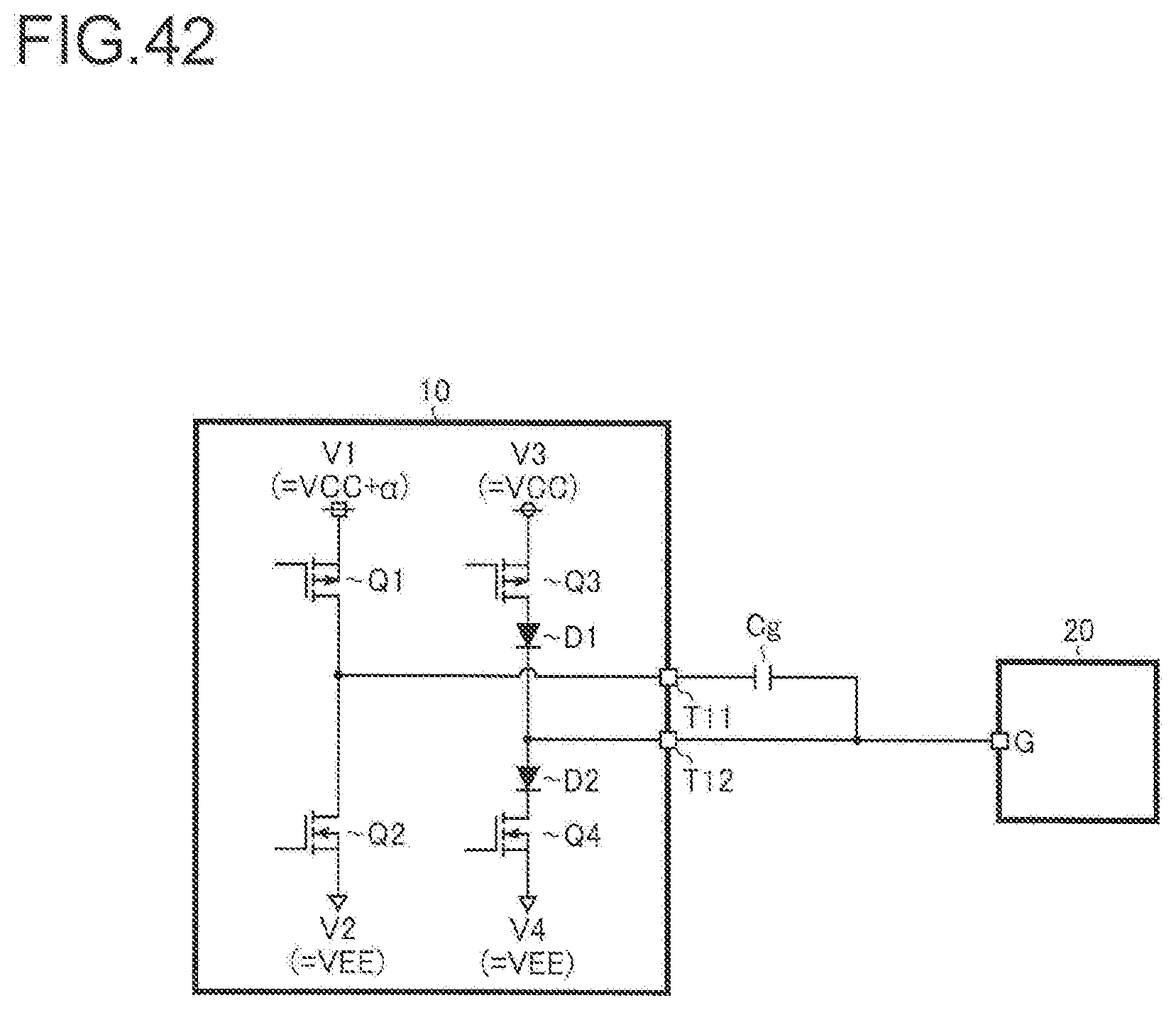

[0070] FIG. 42 is a diagram illustrating a first structural example of a switching module.

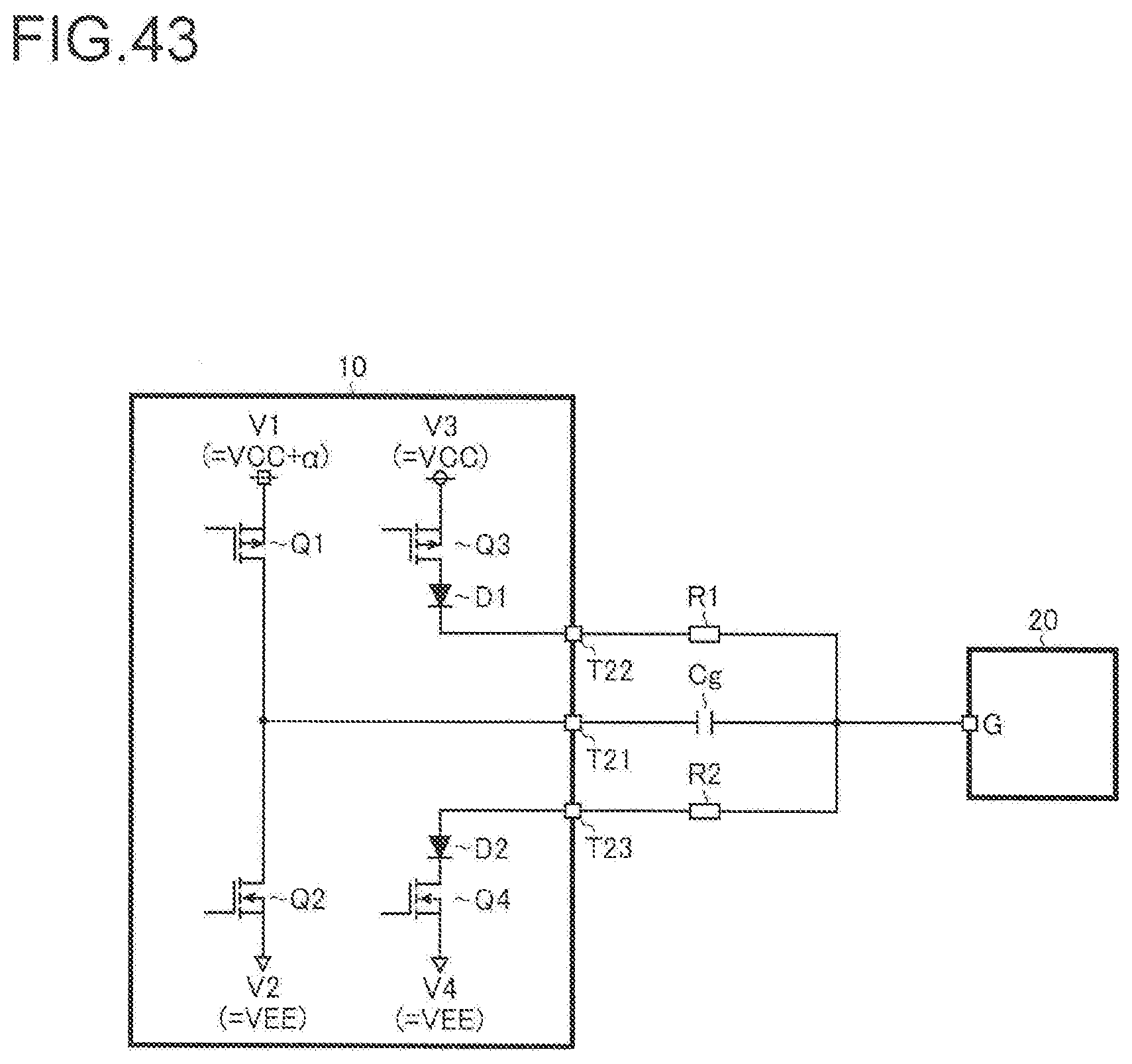

[0071] FIG. 43 is a diagram illustrating a second structural example of a switching module.

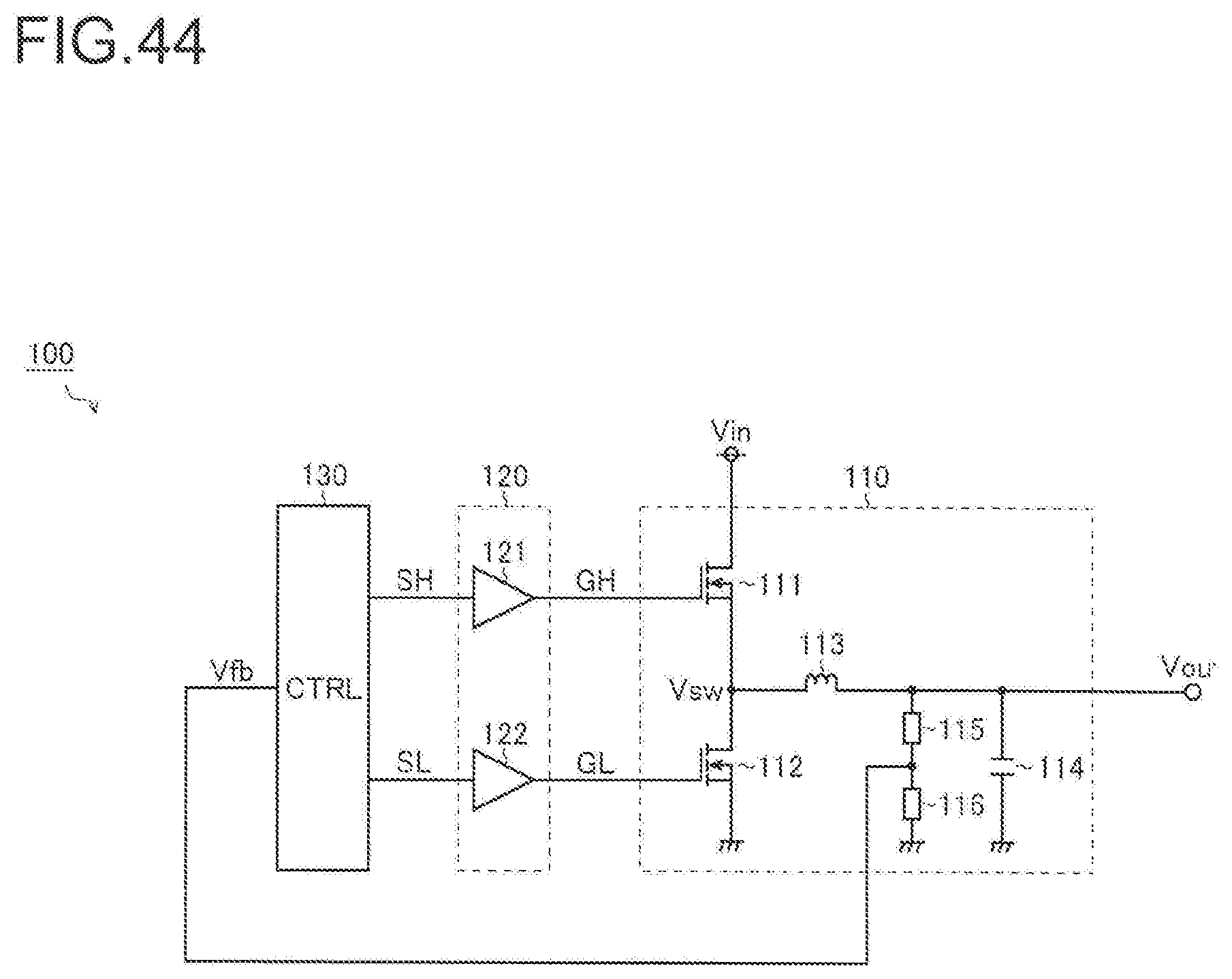

[0072] FIG. 44 is a diagram illustrating an application example to a DC/DC converter.

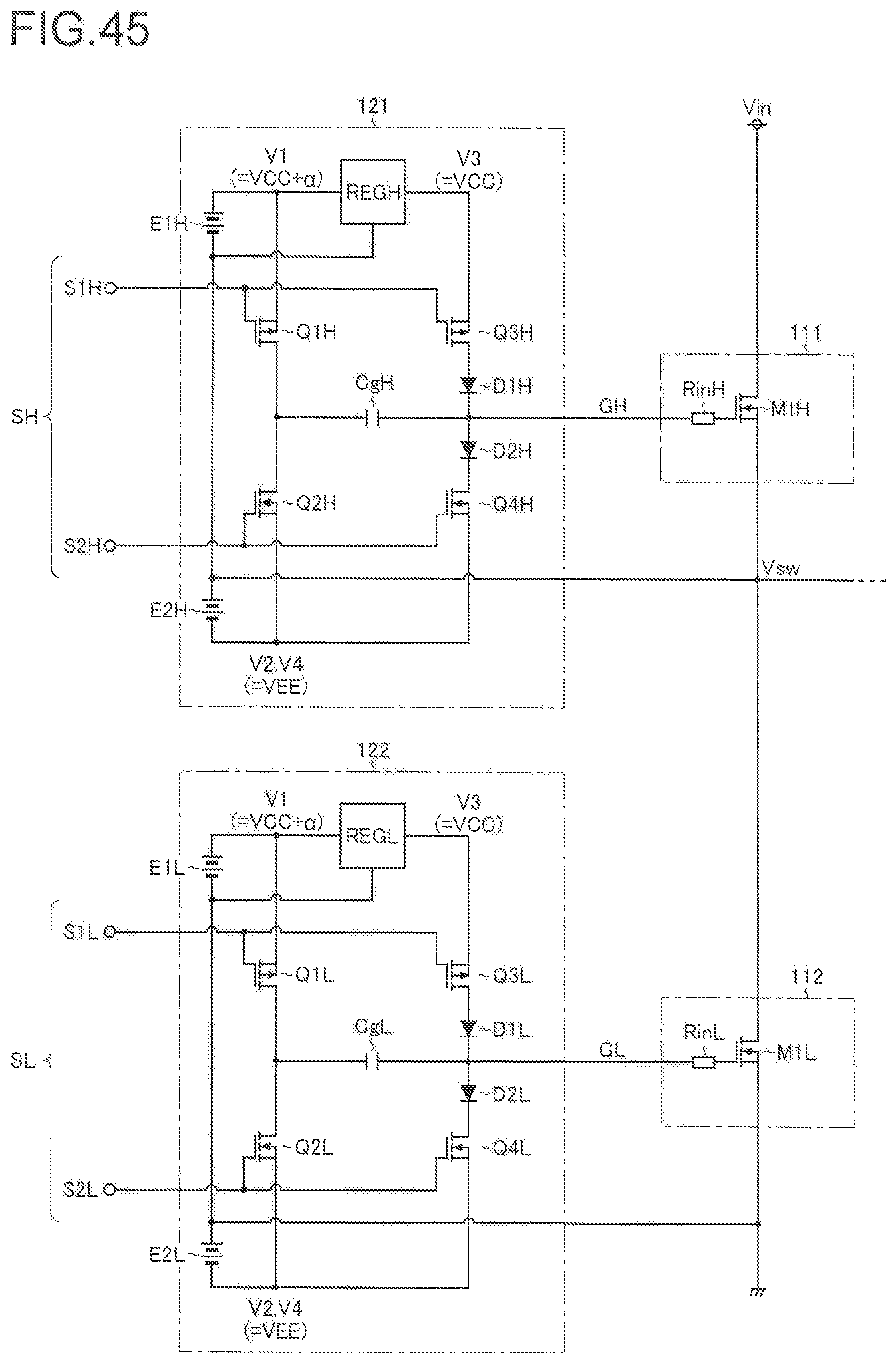

[0073] FIG. 45 is a diagram illustrating a structural example of a driver.

DESCRIPTION OF EMBODIMENTS

[0074] An embodiment of the present invention is described below with reference to the drawings.

[0075] <1. Structure of Gate Drive Circuit>

[0076] FIG. 1 is a circuit diagram illustrating a structure of a gate drive circuit according to one embodiment of the present invention. A gate drive circuit 1 illustrated in FIG. 1 drives a transistor 2. The gate drive circuit 1 and the transistor 2 can constitute various power conversion devices (such as a converter and an inverter). The transistor 2 is, for example, an N-channel type MOSFET using SiC as a semiconductor material. In FIG. 1 and FIGS. 2, 4A to 4D, 5A to 5D, 6, and 7 that are described later, a main equivalent circuit of the transistor 2 is illustrated. Here, FIG. 9 illustrates a model diagram of the transistor 2. As illustrated in FIG. 9, the transistor 2 includes an internal gate resistor Rg, a gate-source capacitance Cgs as a parasitic capacitance, and a gate-drain capacitance Cgd as a parasitic capacitance. The internal gate resistor Rg is connected between a gate terminal GT and a connection node between the gate-source capacitance Cgs and the gate-drain capacitance Cgd. In the transistor 2 illustrated in FIG. 1 and the like, there are shown the internal gate resistor Rg and an input capacitance Ciss, which is a combined capacitance of the gate-source capacitance Cgs and the gate-drain capacitance Cgd. The input capacitance Ciss is a total capacitance of the transistor 2 viewed from the input side.

[0077] The gate drive circuit 1 includes capacitors C1 and C2, transistors Q1a and Q1b, transistors Q2 and Q3, an inductor L, and diodes D20 and D30. The transistors Q1a and Q1b constitute a bidirectional switch. Further, the diodes D20 and D30 function as a current blocking unit.

[0078] The capacitor C1 and the capacitor C2 are connected in series, and a power supply E applies a power supply voltage Vcc across both ends of the series connection structure. In other words, one terminal of the capacitor C1 (high potential end) is connected to an application terminal of the power supply voltage Vcc, and one terminal of the capacitor C2 (low potential end) is connected to an application terminal of a reference potential. The capacitors C1 and C2 function as voltage sources, each of which generates a voltage of Vcc/2. Note that a voltage ratio of the capacitors C1 and C2 is not limited to this, but can be arbitrarily set.

[0079] A connection node P1 of the capacitor C1 and the capacitor C2 (first connection node) is connected to a source of the transistor Q1a constituted of an N-channel type MOSFET. A drain of the transistor Q1a is connected to a drain of the transistor Q1b constituted of an N-channel type MOSFET. A source of the transistor Q1b is connected to one terminal of the inductor L. Note that the transistor Q1a has a body diode Da, and the transistor Q1b has a body diode Db.

[0080] A source of the transistor Q2 (first switch) constituted of a P-channel type MOSFET is connected to the one terminal of the capacitor C1. An anode of the diode D20 (first current blocking unit) is connected to a drain of the transistor Q2. A cathode of the diode 20 is connected to an anode of the diode 030 (second current blocking unit). A cathode of the diode D30 is connected to a drain of the transistor Q3 (second switch) constituted of an N-channel type MOSFET. A source of the transistor Q3 is connected to the one terminal of the capacitor C2. Note that the transistor Q2 has a body diode D2, and the transistor Q3 has a body diode D3.

[0081] The other terminal of the inductor L is connected to a connection node P2 (second connection node) of the diode D20 and the diode D30. In other words, the inductor L and the bidirectional switch (third switch) constituted of the transistors Q1a and Q1b are connected in series between the connection node P1 and the connection node P2.

[0082] The connection node P2 is connected to a gate of the transistor 2. The transistor 2 includes the internal gate resistor Rg and the input capacitance Ciss. One terminal of the internal gate resistor Rg is connected to the connection node P2, and the other terminal of the internal gate resistor Rg is connected to one terminal of the input capacitance Ciss. Note that an additional resistor may be connected between the connection node P2 and the internal gate resistor Rg. In other words, it is sufficient that the gate of the transistor 2 can be electrically connected to the connection node P2.

[0083] The control unit 3 controls driving the gate drive circuit 1. The control unit 3 outputs a gate drive signal Q1a_g to a gate of the transistor Q1a and outputs a gate drive signal Q1b_g to a gate of the transistor Q1b. Further, the control unit 3 outputs a gate drive signal Q2_g to a gate of the transistor Q2 and outputs a gate drive signal Q3_g to a gate of the transistor Q3. The gate drive signal Q2_g and the gate drive signal Q3_g are a pulse-like signal, and the transistors Q2 and Q3 are complementarily driven.

[0084] <2. Operation of Gate Drive Circuit>

[0085] Next, an operation of the gate drive circuit 1 having the above-described structure according to this embodiment is described. Here, the timing chart of FIG. 3 is used for description. FIG. 3 is the timing chart of operations when the transistor 2 is turned on and when it is turned off. In FIG. 3, the gate drive signal Q1a_g, the gate drive signal Q1b_g, the gate drive signal Q2_g, the gate drive signal Q3_g, an inductor current IL, a gate current Ig, an output voltage Vout, and a gate voltage Vg are shown in order from top to bottom.

[0086] As illustrated in FIG. 1, the inductor current IL is current flowing in the inductor L, the gate current Ig is current flowing in the internal gate resistor Rg, the output voltage Vout is a voltage generated at the connection node P2, and the gate voltage Vg is a voltage generated in the input capacitance Ciss.

[0087] <<When Turned On>>

[0088] First, an operation when the transistor 2 is turned on is described with reference to FIGS. 3 and 4A to 4D. In a state where the gate drive signal Q1a_g is low so that the transistor Q1a is OFF, the gate drive signal Q2_g is high so that the transistor Q2 is OFF, and the gate drive signal Q3_g is high so that the transistor Q3 is ON, the gate drive signal Q1b_g is switched from low to high at timing t1, and the transistor Q1b is turned on.

[0089] Then, as illustrated in FIG. 4A, the current begins to flow in the path of the capacitor C2, the body diode of the transistor Q1a, the transistor Q1b, the inductor L, the diode D30, and the transistor Q3 in order (solid line arrow). In this way, the inductor current IL gradually increases from zero to a positive side. In this case, the gradient of increase depends on the inductance of the inductor L.

[0090] At timing t2 when a predetermined period TI elapses from timing t the gate drive signal Q2_g is switched to low, and the gate drive signal Q3_g is switched to low. Then, as shown in FIG. 4B, the current begins to flow in the path of the capacitor C2, the body diode of the transistor Q1a, the transistor Q1b, the inductor L, the internal gate resistor Rg, and the input capacitance Ciss in order (solid line arrow).

[0091] At timing t2, the inductor current IL (a solid line) becomes a peak current value Ip1, and the gate current Ig shown by a broken line increases steeply from zero to the peak current value Ip1. In other words, the gate current Ig begins to flow. Further, at timing t2, the output voltage Vout (a solid line) increases steeply from zero to a peak voltage value Vp1. The peak voltage value Vp1 is higher than the power supply voltage Vcc. However, the diode D20 blocks the current from flowing to the power supply E side through the body diode of the transistor Q2, and hence it is possible to prevent the output voltage Vout from being clamped to the power supply voltage Vcc.

[0092] At timing t2, charging of the input capacitance Ciss is started, and the gate voltage Vg (a solid line) begins to increase from zero.

[0093] After timing t2, the inductor current IL and the gate current Ig are identical to each other and gradually decrease. In accordance with this, the output voltage Vout is gradually decreased. At timing t3 when the output voltage Vout reaches the power supply voltage Vcc, as illustrated in FIG. 4C, the current begins to flow in the path (a solid line arrow in FIG. 4C) in the same manner as the path illustrated in FIG. 4B, and in the path of the capacitor C2, the capacitor C1, the transistor Q2, the diode D20, the internal gate resistor Rg, and the input capacitance Ciss in order (a broken line arrow in FIG. 4C). Therefore, the gate current Ig is a combined current of the inductor current IL and the current supplied from the transistor Q2.

[0094] After timing 13, the inductor current IL decreases and when it reaches zero, the body diode of the transistor Q1a (backflow prevention unit) prevents back flow of the inductor current IL. Then, as illustrated in FIG. 4D, the current flows only in the path (a broken line arrow in FIG. 4D) in the same manner as the path through the transistor Q2 illustrated in FIG. 4C after that. In other words, the gate current Ig flows as the current flowing only in this path, and when the gate voltage Vg reaches the power supply voltage Vcc, the gate current Ig becomes zero. In this way, charging of the input capacitance Ciss is finished.

[0095] <<When Turned Off>>

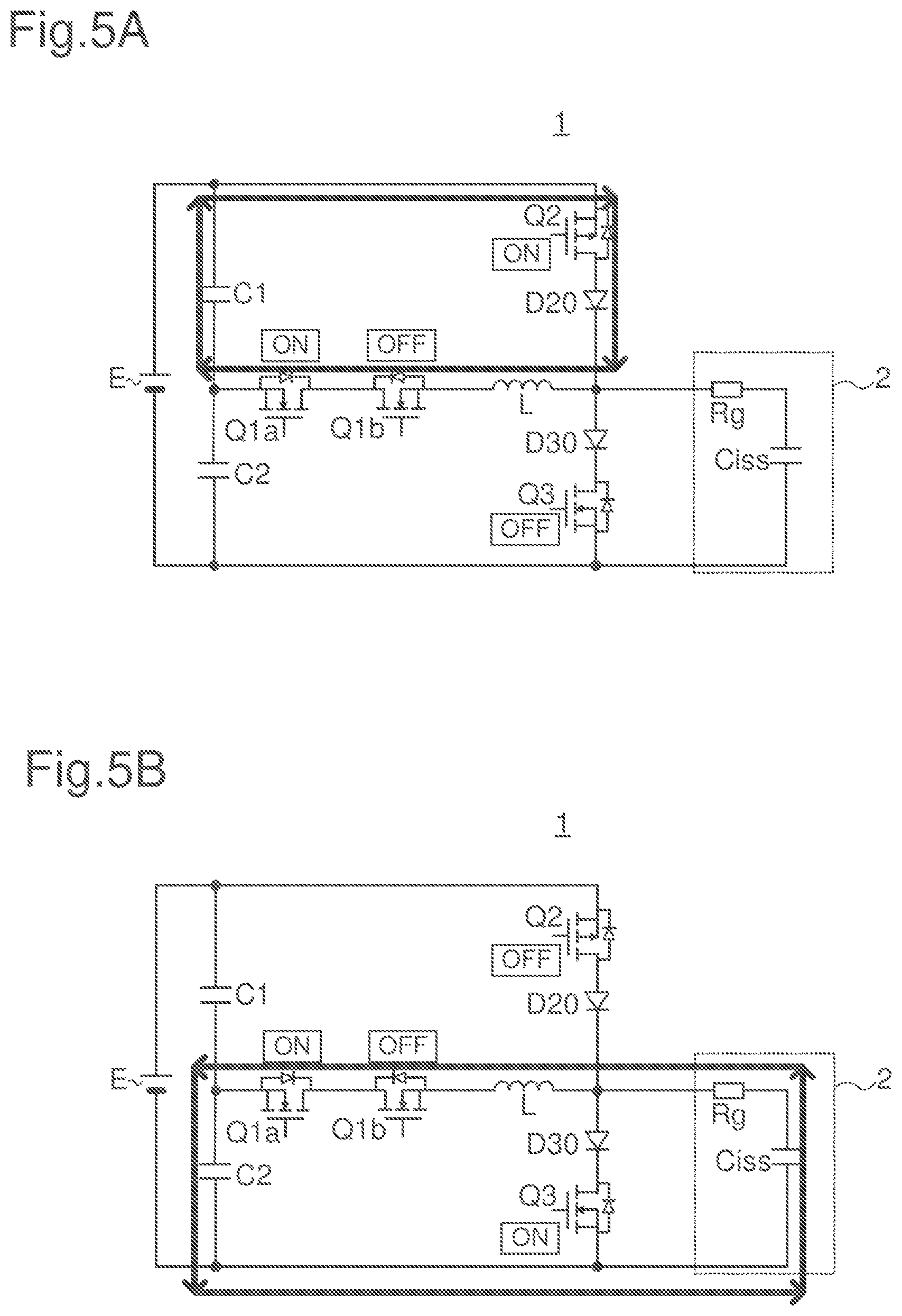

[0096] Next, an operation when the transistor 2 is turned off is described with reference to FIGS. 3 and 5A to SD. In a state where the gate drive signal Q1b_g is low so that the transistor Q1b is OFF, the gate drive signal Q2_g is low so that the transistor Q2 is ON, and the gate drive signal Q3_g is low so that the transistor Q3 is OFF, the gate drive signal Q1a_g is switched from low to high at timing t4, and the transistor Q1a is turned on.

[0097] Then, as illustrated in FIG. 5A, the current begins to flow in the path of the capacitor C1, the transistor Q2, the diode D20, the inductor L, the body diode of the transistor Q1b, and the transistor Q1a in order (solid line arrow). In this way, the inductor current IL (a solid line) gradually increases from zero to a negative side. In this case, the gradient of increase depends on the inductance of the inductor L.

[0098] In FIG. 3, at timing t5 when a predetermined period T2 elapses from timing 14, the gate drive signal Q2_g is switched to high, and the gate drive signal Q3_g is switched to high. Then, as illustrated in FIG. 5B, the current begins to flow in the path of the input capacitance Ciss, the internal gate resistor Rg, the inductor L, the body diode of the transistor Q1b, the transistor Q1a, and the capacitor C2 in order (solid line arrow).

[0099] At timing t5 in FIG. 3, the inductor current IL (a solid line) becomes a peak current value Ip2, and the gate current Ig shown by a broken line increases steeply from zero to the peak current value Ip2. In other words, the gate current Ig begins to flow. Further, at timing t5, the output voltage Vout increases steeply from zero to a peak voltage value Vp2. The peak voltage value Vp2 is lower than 0 V. However, the diode D30 blocks the current from flowing to the connection node P2 side through the body diode of the transistor Q3, and hence it is possible to prevent the output voltage Vout from being clamped to 0 V.

[0100] At timing t5 in FIG. 3, discharge of the input capacitance Ciss is started, and the gate voltage Vg (a solid line) begins to decrease from the power supply voltage Vcc.

[0101] After timing t5 in FIG. 3, the inductor current IL and the gate current Ig are identical to each other and gradually decrease. In accordance with this, the output voltage Vout is gradually decreased toward 0 V. At timing 16 when the output voltage Vout reaches 0 V, as illustrated in FIG. 5C, the current begins to flow in the path (a solid line arrow in FIG. 5C) in the same manner as the path illustrated in FIG. 5B, and in the path of the input capacitance Ciss, the internal gate resistor Rg, the diode D30, and the transistor Q3 in order (a broken line arrow in FIG. 5C). Therefore, the gate current Ig is a combined current of the inductor current IL and the current flowing in the transistor Q3.

[0102] After timing t6, the inductor current IL decreases and when it reaches zero, the body diode of the transistor Q1b (backflow prevention unit) prevents backflow of the inductor current IL. Then, as illustrated in FIG. 5D, the current flows only in the path (a broken line arrow in FIG. 5D) in the same manner as the path through the transistor Q3 illustrated in FIG. 5C after that. In other words, the gate current Ig flows as the current flowing only in this path, and when the gate voltage Vg reaches 0 V, the gate current Ig becomes zero. In this way, discharge of the input capacitance Ciss is finished.

[0103] <3. Comparison with Conventional Structure>

[0104] Here, FIG. 2 is a circuit diagram illustrating a structure of a conventional gate drive circuit that is used for comparison with the present invention. A structure of a conventional gate drive circuit 1' illustrated in FIG. 2 is obtained by eliminating the capacitors C1 and C2, the transistors Q1a and Q1b, the diodes D20 and D30, and the inductor L from the structure of the gate drive circuit 1 illustrated in FIG. 1 according to this embodiment.

[0105] An operation of this conventional gate drive circuit 1' is shown in FIG. 3 together with the operation of this embodiment described above. As an operation when the transistor 2 is turned on, when the transistor Q2 is switched to ON and the transistor Q3 is switched to OFF at timing t2, the output voltage Vout (a broken line) increases steeply from zero to the power supply voltage Vcc, and the gate current Ig (a dashed-dotted line) increases steeply from zero to a predetermined current value I1. Here, the predetermined current value I1 is a value expressed as Vcc/Rg. When the gate current Ig begins to flow, charging of the input capacitance Ciss is started. In this way, the gate voltage Vg (broken line) begins to increase from zero. Then, the charging proceeds and when the gate voltage Vg reaches the power supply voltage Vcc, the gate current Ig becomes zero. In this way, charging of the input capacitance Ciss is finished.

[0106] As an operation when the transistor 2 is turned off, when the transistor Q2 is switched to OFF and the transistor Q3 is switched to ON at timing t5, the output voltage Vout (broken line) decreases steeply to 0 V, and the gate current Ig (dashed-dotted line) increases steeply from zero to a predetermined current value I2. Here, the predetermined current value I2 is a value expressed as Vcc/Rg. When the gate current Ig begins to flow, discharge of the input capacitance Ciss is started. In this way, the gate voltage Vg (broken line) begins to decrease from the power supply voltage Vcc. Then, the discharge proceeds and when the gate voltage Vg reaches 0 V, the gate current Ig becomes zero. In this way, discharge of the input capacitance Ciss is finished.

[0107] In this way, in the conventional gate drive circuit 1', an initial value of the gate current Ig when starting charge and discharge is limited by the current value I1, I2. In particular, if the internal gate resistor Rg is large because the transistor 2 is made of a semiconductor material such as SiC, the current value I1, I2 is limited more. In contrast, according to the gate drive circuit 1 of this embodiment, the initial value of the gate current Ig when starting charge and discharge can be the peak current value Ip1, Ip2 larger than the current value I1, I2. Therefore, the speed of charge and discharge can be higher than the conventional structure. In other words, the switching speed of the transistor 2 can be increased, and a switching loss can be reduced.

[0108] Further, in this embodiment, when being turned on, the period T1 after the transistor Q1b is switched to ON until the transistors Q2 and Q3 are switched is variable, and hence the peak current value lot is adjusted, so that the turn-on speed can be changed. Similarly, when being turned oft, the period T2 after the transistor Q1a is switched to ON until the transistors Q2 and Q3 are switched is variable, and hence the peak current value Ip2 is adjusted, so that the turning off speed can be changed.

[0109] Note that the timing t7 for switching the transistor Q1b from ON to OFF when being turned on can be set with high flexibility, because the body diode of the transistor Q1a can prevent backflow of the inductor current IL even if the transistor Q1b stays ON. However, it is preferred to set the timing t7 to be before the timing t4 at which the inductor current IL is made to flow in the negative direction when being turned off after turning on.

[0110] Further, the timing t8 for switching the transistor Q1a from ON to OFF when being turned oilcan be set with high flexibility, because the body diode of the transistor Q1b can prevent backflow of the inductor current IL even if the transistor Q1a stays ON. However, it is preferred to set the timing t8 to be before the timing t1 at which the inductor current IL is made to flow in the positive direction when being turned on after turning off.

[0111] <4. Variation of Gate Drive Circuit>

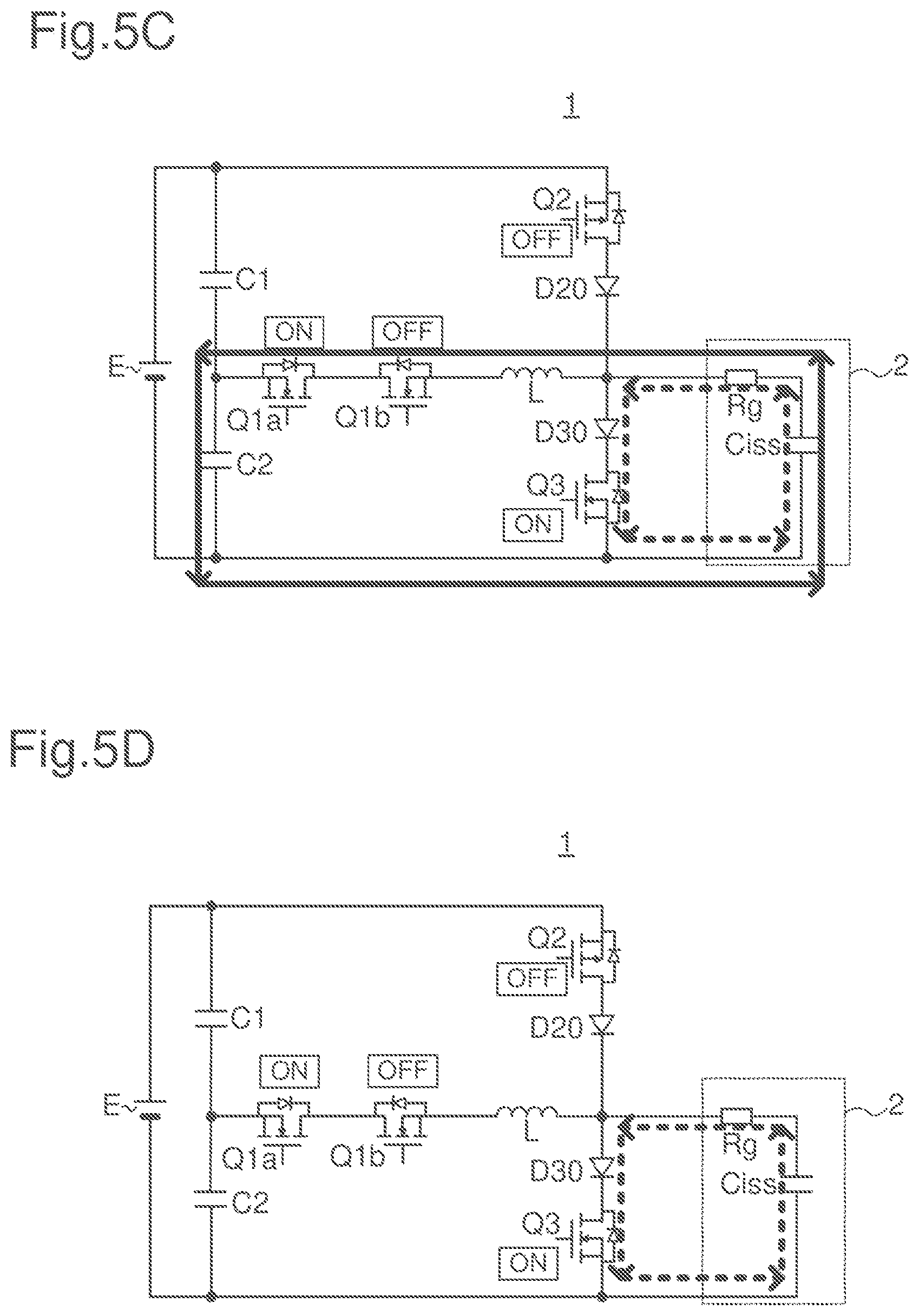

[0112] FIG. 6 is a circuit diagram illustrating a structure of a gate drive circuit 101 according to a variation. The gate drive circuit 101 is different from the structure of FIG. 1 described above in that a diode D40 is substituted for the transistor Q1a, and the diode D30 is not disposed.

[0113] In the gate drive circuit 101, when being turned on, in a state where the transistor Q2 is OFF and the transistor Q3 is ON, the transistor Q1b is switched to ON, and after that the transistors Q2 and Q3 are switched. In this way, with the same operation as the gate drive circuit 1 described above, the input capacitance Ciss can be charged at high speed. Further, when being turned off, the transistor Q3 is ON, and hence discharge of the input capacitance Ciss can be performed in the same manner as the conventional structure. Therefore, according to the gate drive circuit 101, if high speed is required only when being turned on, elements can be made simpler so that cost can be reduced.

[0114] Further, FIG. 7 is a circuit diagram illustrating a structure of a gate drive circuit 102 according to another variation. The gate drive circuit 102 is different from the structure of FIG. 1 described above in that a diode D50 is substituted for the transistor Q1b, and the diode D20 is not disposed.

[0115] In the gate drive circuit 102, when being turned on, the transistor Q2 is ON so that the input capacitance Ciss can be charged in the same manner as the conventional structure. Further, when being turned off, in a state where the transistor Q2 is ON and the transistor Q3 is OFF, the transistor Q1a is switched to ON, and after that the transistors Q2 and Q3 are switched. In this way, with the same operation as the gate drive circuit 1 described above, the input capacitance Ciss can be discharged at high speed. Therefore, according to the gate drive circuit 102, if high speed is required only when being turned off, elements can be made simpler so that cost can be reduced.

[0116] <5. ON Time Control of Transistor According to Load>

[0117] FIG. 8 is a timing chart showing various waveforms when the transistor 2 illustrated in FIG. 9 is turned on. FIG. 8 shows temporal changes of the gate voltage Vg, a drain voltage Vd, and a drain current Id.

[0118] At timing t0, a predetermined voltage is applied to the gate terminal GT of the transistor 2 illustrated in FIG. 9. Then, charging of the gate-source capacitance Cgs is started, and the gate voltage Vg begins to increase. Then, at timing t1 when the gate voltage Vg reaches a threshold voltage Vth, the drain current Id begins to flow. In the period from timing t1 to timing t2, the gate voltage Vg increases, and in proportion to this, the drain current Id increases.

[0119] At timing t2, charging of the gate-source capacitance Cgs is finished, so that the gate voltage Vg becomes constant at a plateau voltage Vp, and the drain current Id becomes constant. Further, at timing t2, charging of the gate-drain capacitance Cgd is started, and the drain voltage Vd begins to decrease.

[0120] The decrease in the drain voltage Vd continues until timing t3 when charging of the gate-drain capacitance Cgd is finished. The gate voltage Vg increases again from timing t3, and the gate voltage Vg reaches the predetermined voltage described above at timing t4.

[0121] After timing t2 when charging of the gate-source capacitance Cgs is finished and the gate voltage Vg reaches the plateau voltage Vp, the gate current Ig when charging the gate-drain capacitance Cgd until timing t3 is expressed by Ig=(VGT-Vp)/Rg, where VGT is a voltage applied to the gate terminal GT. Here, the plateau voltage Vp depends on the drain current Id as a load. A change in the drain current Id causes a change in the gate current Ig, and hence the charging speed of the gate-drain capacitance Cgd is changed.

[0122] Therefore, by changing the voltage VGT to be applied to the gate terminal GT in accordance with the drain current Id, it is possible to suppress a change in the gate current Ig and to suppress a change in the charging speed of the gate-drain capacitance Cgd. In this way, a turning on speed can be stabilized.

[0123] Thus, in the gate drive circuit described above, by changing an ON time Ton_b of the transistor Q1b shown in FIG. 3 in accordance with a load, the output voltage Vout (corresponding to the voltage VGT) can be changed, and the turning on speed can be stabilized.

[0124] Further, when being turned off, the behavior is temporally opposite to that shown in the timing chart of FIG. 8. When the gate voltage Vg reaches the plateau voltage Vp, the gate current Ig when discharging the gate-drain capacitance Cgd after that is expressed by Ig=Vp/Rg. Here, the plateau voltage Vp depends on the drain current Id as a load. A change in the drain current Id causes a change in the gate current Ig, and hence the discharging speed of the gate-drain capacitance Cgd is changed.

[0125] Therefore, by changing the voltage VGT to be applied to the gate terminal GT in accordance with the drain current Id, a is possible to suppress a change in the gate current Ig and to suppress a change in the discharging speed of the gate-drain capacitance Cgd. In this way, the turning off speed can be stabilized.

[0126] Thus, in the gate drive circuit described above, by changing an ON time Ton_a of the transistor Q1a shown in FIG. 3 in accordance with a load, the output voltage Vout (corresponding to the voltage VGT) can be changed, and the turning off speed can be stabilized.

[0127] <6. Others>

[0128] Although the embodiment of the present invention is described above, the embodiment can be variously modified within the spirit of the present invention.

[0129] For instance, like a gate drive circuit 103 illustrated in FIG. 10, if the transistors Q2 and Q3 are ideal switches SW1 and SW2 that can be turned off in a bidirectional manner, the diodes D20 and D30 are not necessary. In this case, each of the switches SW1 and SW2 has both functions of a switch unit and a current blocking unit. Further, as illustrated in FIG. 10, it may be possible to dispose, as a substitute for the transistors Q1a and Q1b, a bidirectional switch SW3 that is turned on and then turned off at the timing when the inductor current IL flows backward. In this case, the bidirectional switch SW3 has both functions of a switch unit and a backflow prevention unit.

[0130] Further, the transistors Q2, Q3, Q1a, and Q1b may be constituted of an N-channel type MOSFET or may be constituted of a P-channel type MOSFET. Furthermore, without limiting to a MOSFET, other transistor may constitute them. For instance, a bipolar transistor (either NPN or PNP) may constitute them. In this case, an external diode should be connected in parallel to a bipolar transistor as each of the transistors Q1a and Q1b, but it is not required to connect a diode in parallel to a bipolar transistor as each of the transistors Q2 and Q3.

[0131] Further, the gate drive circuit of the present invention may be configured as an IC to which the inductor L and the capacitors C1 and C2 can be externally connected.

[0132] Next, an embodiment according to another aspect of the present invention is described.

[0133] <Reference Example>

[0134] Before describing the present invention, a reference example of the gate drive circuit to be compared with the present invention is described. FIG. 11 is an equivalent circuit diagram illustrating a reference example of the gate drive circuit. A gate drive circuit 10 of this reference example is an analog circuit for driving a discrete switching element 20, and includes a drive unit DRV1, an external gate resistor Rg(on), and a discharge resistor Rgs.

[0135] The drive unit DRV1 outputs a binary voltage (a power supply voltage VCC or a ground voltage GND) from its output terminal in accordance with a logic level of the control signal input to the drive unit DRV1, so as to voltage-drive a gate terminal of the switching element 20.

[0136] The external gate resistor Rg(on) is connected between an output terminal of the drive unit DRV1 and the gate terminal of the switching element 20. The discharge resistor Rgs is connected between the gate terminal of the switching element 20 and a ground (GND). Note that the external gate resistor Rg(on) and the discharge resistor Rgs satisfies a relationship of Rg(on)<<Rgs.

[0137] The switching element 20 is a semiconductor switching element that is switched by the gate drive circuit 10, and in this example an N-channel type metal oxide semiconductor (MOS) field-effect transistor M1 is used.

[0138] Note that as illustrated in this diagram in an equivalent manner, a gate-source parasitic capacitance Cgs is added between gate and source of the transistor M1, and the gate-drain parasitic capacitance Cgd is added between gate and drain of the transistor M1. The input capacitance Ciss of the transistor M1 can be expressed as a sum of the gate-source parasitic capacitance Cgs and the gate-drain parasitic capacitance Cgd (=Cgs+Cgd).

[0139] Further, an internal gate resistor Rin is added to a gate of the transistor M1, and a body diode BD is added between drain and source of the transistor M1 in an illustrated polarity. Further, although a parasitic inductance is also added to the transistor M1, it is not shown in the diagram and is not described here for convenience sake of illustration.

[0140] Concerning voltages and the currents of individual portions of the switching element 20, Vgs is a gate-source voltage, Vgs(real) is a voltage across both ends of the gate-source parasitic capacitance Cgs, Vds is a drain-source voltage, Id is a drain current, and Ig is a gate current. Note that when the gate current Ig is flowing, a voltage (=Ig.times.Rin) is generated across both ends of the internal gate resistor Rin, and hence Vgs.noteq. Vgs(real) holds. In contrast, when the gate current Ig is not flowing, the voltage across both ends of the internal gate resistor Rin becomes zero, and hence Vgs=Vgs(real) holds, ignoring the parasitic inductance.

[0141] FIG. 12 is a switching waveform diagram showing turn-on transient characteristics of the switching element 20 in this reference example. In this diagram, a solid line indicates the gate-source voltage Vgs, a short dashed line indicates the drain-source voltage Vds, and a long dashed line indicates the drain current Id. Further, the horizontal axis is scaled by 100 ns/div, and the vertical axis is scaled by 5 V/div for Vgs, 200 V/div for Vds, and 20 A/div for Id.

[0142] Note that this diagram shows transient characteristics when the switching element 20 is turned on in an application where a high-voltage SiC-MOSFET (rating 1200 V) is used as the switching element 20, to which an inductive load (such as a coil) is connected, under a condition of VCC=18 V, Rg(on)=0.01 .OMEGA., and Rgs=4.7 k.OMEGA. (i.e. a condition in which the switching speed is increased by decreasing the Rg(on) to a lower limit).

[0143] Under the conditions described above, it is confirmed by actual measurement that a turn-on period T10 of the switching element 20 (i.e. a period necessary for the switching element 20 to switch from an OFF state to an ON state) is approximately 260 ns. In the following description, this turn-on period T10 is roughly classified into three periods T11 to T13 in a temporal order, and each of them is described in detail.

[0144] First, the period T11 is described. The period T11 corresponds to a period during which Vgs(real)<Vth (where Vth is an on threshold voltage of the transistor M1) is satisfied. During this period T11, the drain current Id is kept at zero while the gate-source voltage Vgs (=Vgs(real)) is being increased at a predetermined time constant .tau. (=(Rg(on)+Rin).times.Ciss).

[0145] Next, the period T12 is described. The period T12 corresponds to a period during which Vth.ltoreq.Vgs(real)<Vp (where Vp is a plateau voltage at a steady state value of the drain current Id in the transistor M1) is satisfied. Here, the steady state value of the drain current Id indicates a current value flowing in the inductive load after switching. During this period T12, the drain-source voltage Vds is maintained while the drain current Id is being increased. Note that the period T12 ends when the drain current Id reaches the steady state value.

[0146] Here, a SiC-MOSFET has a mutual conductance smaller than that of a Si-MOSFET in general, and has a tendency that the plateau voltage Vp is higher as the drain current Id is larger. This point is described in detail with reference to FIG. 13.

[0147] FIG. 13 is an Id-Vgs characteristic diagram in which the vertical axis indicates the drain current Id and the horizontal axis indicates the gate-source voltage Vgs. Note that the solid line indicates Id-Vgs characteristics of the SiC-MOSFET, and the dashed-dotted line indicates Id-Vgs characteristics of the Si-MOSFET.

[0148] As described above, a mutual conductance of a SiC-MOSFET is smaller than that of a Si-MOSFET in general. Therefore, the Id-Vgs characteristics of the SiC-MOSFET (a solid line) has a smaller gradient (=d(Id)/d(Vgs)) than the Si-MOSFET.

[0149] Thus, the gate-source voltage Vgs of the Si-MOSFET (dashed-dotted line) changes little when the drain current Id changes, but the gate-source voltage Vgs of the SiC-MOSFET (a solid line) changes largely when the drain current Id changes.

[0150] In this way, in the SiC-MOSFET, the plateau voltage Vp is higher as the drain current Id is larger. As a result, a transition timing to a plateau region (i.e. a transition timing from the period T12 to the period T13) is delayed, and hence the turn-on period T10 of the switching element 20 is increased.

[0151] With reference to FIG. 12 again, the period T13 (i.e. the plateau region) is described. The period T13 corresponds to a period during which Vgs(real)=Vp is satisfied. During this period T13, the gate-source voltage Vgs is maintained while the drain-source voltage Vds is being decreased.

[0152] Here, in a SiC-MOSFET, the plateau voltage Vp is higher as the drain current Id is larger as described above, and hence a difference between the gate-source voltage Vgs (=VCC) applied to the switching element 20 and the plateau voltage Vp (=Vgs(real)) is smaller. As a result, the gate current Ig (=(Vgs-Vp)/(Rg(on)+Rin)) is decreased, and charging time of the gate-drain parasitic capacitance Cgd is increased, resulting in an increase of the period T13 (therefore the turn-on period T10). In particular, as the internal gate resistor Rin has a larger resistance, the gate current Ig is smaller, and thus the periods T12 and T13 are longer.

[0153] For instance, when applying the switching element 20 to a switching power supply, high frequency driving of the switching element 20 contributes to downsizing of passive elements. However, as the turn-on period T10 of the switching element 20 and a turn-off period thereof (a period after the gate-source voltage Vgs begins to fall until the drain current Id reaches 0 A) are longer, a switching loss is larger or it is necessary to secure a larger dead time. Therefore, in order to perform the high frequency driving of the switching element 20, it is very important to achieve high speed switching of the switching element 20.

[0154] Note that it is possible to decrease the periods T12 and T13 (therefore the turn-on period T10) by increasing the gate-source voltage Vgs that is applied when the switching element 20 is turned on, because the gate current Ig is increased. However, in order to prevent breakdown of the element, a gate-source voltage Vgs higher than a DC rated voltage (e.g. 22 V) cannot be applied to the switching element 20 continuously in the steady on state of the switching element 20.

[0155] Therefore, in the embodiment described below, there is proposed the gate drive circuit 10 that can achieve high speed switching by temporarily increasing the gate-source voltage Vgs of the switching element 20 only for an instant of turning on.

[0156] Note that, among first to sixteenth embodiments described below, the former part, i.e. the first to ninth embodiments have the same structure as Patent Document 5 filed by this applicant, and are understood as comparative examples to be compared with the tenth to sixteenth embodiments (having a structure in which a capacitance variation of a capacitor is taken into account).

First Embodiment

[0157] FIG. 14 is an equivalent circuit diagram illustrating the first embodiment of the gate drive circuit 10. The gate drive circuit 10 of this embodiment is an analog circuit for driving a voltage drive type switching element 20 (such as a SiC-MOSFET) in the same manner as the reference example (FIG. 11) described above, and includes, in addition to the drive unit DRV1 described above, a capacitor Cg connected in series to the gate terminal of the switching element 20, and a gate drive voltage source V1.

[0158] The drive unit DRV1 outputs a binary pulse voltage (a gate drive voltage (VCC+.alpha.) or the ground voltage GND) from its output terminal in accordance with a logic level of a pulse control signal input to the drive unit DRV1, so as to voltage drive the gate terminal of the switching element 20.

[0159] The capacitor Cg is connected between the output terminal of the drive unit DRV1 and the gate terminal of the switching element 20. In particular, a drive target of the gate drive circuit 10 of this embodiment is the voltage drive type switching element 20, and it is not necessary to continuously supply the gate current Ig in the steady ON state of the switching element 20. Therefore, only the capacitor Cg is sufficient as an essential circuit element connected directly to the gate terminal of the switching element 20.

[0160] Note that the voltage applied to the gate-source parasitic capacitance Cgs in the steady ON state is determined by a capacitance ratio between the capacitor Cg and the gate-source parasitic capacitance Cgs. Therefore, concerning the capacitor Cg, it is preferred to design element thereof so that the voltage applied to the gate-source parasitic capacitance Cgs in the steady ON state is the DC rated voltage or lower. Taking an example of SIC-MOSFET, the gate-source parasitic capacitance Cgs thereof has a capacitance value of approximately 2 nF, and hence it is preferred to design so that the capacitor Cg has a capacitance value of approximately 30 nF, for example.

[0161] The gate drive voltage source V1 supplies a gate drive voltage (VCC+.alpha.) (e.g. 23 V) higher than the power supply voltage VCC (e.g. 18 V) to the drive unit DRV1.

[0162] More specific description is as follows. Vx represents a voltage applied across both ends of the gate-source parasitic capacitance Cgs in the steady ON state of the switching element 20. Vy represents a voltage applied to a circuit element other than the capacitor Cg (such as an upper side transistor forming an output stage of the drive unit DRV1) among circuit elements disposed between the gate drive voltage source V1 and the gate terminal of the switching element 20. Then, it is sufficient that the gate drive voltage source V1 supplies a voltage that is substantially higher than the sum of the above two voltages (=Vx+Vy), as the gate drive voltage (VCC+.alpha.).

[0163] In other words, in the gate drive voltage source V1, a voltage value of the gate drive voltage (VCC+.alpha.) should be appropriately set so that a voltage across both ends of the capacitor Cg does not become substantially zero also in the steady ON state of the switching element 20.

[0164] Note that, in the conventional gate drive circuit, a speedup capacitor is connected in parallel to the gate resistor (see Rg(on) in FIG. 11) in many cases. However, in the steady ON state of the switching element, the gate current does not flow in the gate resistor, and hence the voltage across both ends of the speedup capacitor is zero. In this point of view, it can be said that the capacitor Cg and the conventional speedup capacitor are completely different from each other. As a matter of course, the voltage across both ends of the speedup capacitor cannot be completely zero due to an influence of a leak current and the like, but this can be regarded to be substantially zero.

[0165] When performing the switching drive of the switching element 20 using the gate drive circuit 10 having the structure described above, the gate current Ig flows from the gate drive voltage source V1 through the capacitor Cg immediately after turning on of the switching element 20. Here, when the operation begins, no voltage is applied across both ends of the capacitor Cg, and hence the gate drive voltage (VCC+.alpha.) is applied as the gate-source voltage Vgs of the switching element 20 substantially as it is. As a result, the gate input capacitance Ciss is charged using the gate drive voltage (VCC+.alpha.), and thus it is possible to turn on the switching element 20 at high speed.

[0166] After that, when the switching element 20 reaches the steady ON state (i.e. a state where the gate current Ig does not flow), the gate-source voltage Vgs of the switching element 20 (=Vgs(real)) is converged to a voltage value that is determined by the capacitance ratio between the capacitor Cg and the gate-source parasitic capacitance Cgs.

[0167] For instance, the capacitance ratio between the capacitor Cg and the gate-source parasitic capacitance Cgs should be appropriately set, so that the power supply voltage VCC is applied across both ends of the gate-source parasitic capacitance Cgs in the steady ON state of the switching element 20, and that a voltage a is applied across both ends of the capacitor Cg.

[0168] FIG. 15 is a voltage waveform diagram illustrating turn-on behaviors of Vgs and Vgs(real) described above. Note that a broken line in this diagram indicates a turn-on behavior of the gate-source voltage Vgs, and a solid line indicates a turn-on behavior of the voltage Vgs(real) across both ends of the gate-source parasitic capacitance Cgs.

[0169] As described above, the gate drive voltage (VCC+.alpha.) is applied as the gate-source voltage Vgs substantially as it is, immediately after turning on of the switching element 20. In contrast, the voltage Vgs(real) across both ends of the gate-source parasitic capacitance Cgs is being increased from zero. After that, when the switching element 20 reaches the steady ON state, each of the both voltages is converged to the power supply voltage VCC.

[0170] In this way, the gate drive circuit 10 of this embodiment can temporarily increase the gate-source voltage Vgs of the switching element 20 only for an instant of turning on without increasing a circuit scale or needing a complicated control. Thus, high speed switching of the switching element 20 can be realized with a very simple structure.

[0171] Note that, in order to prevent breakdown of the element, a DC rated voltage VA (i.e. a voltage that can be regularly applied) and a rated surge voltage VB (i.e. a voltage that can be instantaneously applied) are defined between gate and source of the switching element 20. In view of this, it is preferred to set the gate drive voltage (VCC+.alpha.) to be a voltage value that is higher than the DC rated voltage VA and lower than the rated surge voltage VB (VA<VCC+.alpha.<VB). For instance, if VA is 22 V and VB is 26 V, VCC+.alpha. should be set to be 23 to 25 V.

[0172] Further, in the steady ON state of the switching element 20, the voltage Vgs(real) across both ends of the gate-source parasitic capacitance Cgs (e.g. Vgs(real)=VCC) should be set to a voltage value that is lower than the DC rated voltage VA and can sufficiently decrease an on-resistance value of the switching element 20 (e.g. 18 V).

[0173] By setting in this way, the switching speed can be increased as much as possible within a rated operating range of the switching element 20.

[0174] FIG. 16 is a switching waveform diagram showing turn-on transient characteristics of the switching element 20 in the first embodiment. In the same manner as in FIG. 12 described above, a solid line in this diagram indicates the gate-source voltage Vgs, a short dashed line indicates the drain-source voltage Vds, and a long dashed line indicates the drain current Id. Further, the horizontal axis is scaled by 100 ns/div, and the vertical axis is scaled by 5 V/div for Vgs, 200 V/div for Vds, and 20 A/div for Id.

[0175] Note that this diagram shows transient characteristics when the switching element 20 is turned on in an application where a high-voltage SiC-MOSFET (rating 1200 V) is used as the switching element 20, to which an inductive load (such as a coil) is connected, under a condition of VCC+.alpha.=23 V and Cg=30 nF.

[0176] Further, a turn-on period T20 in this diagram is roughly classified into three periods T21 to T23 in a temporal order, in the same manner as the turn-on period T10 in FIG. 12, and the periods T21 to T23 in this diagram correspond to the periods T11 to T13 in FIG. 12, respectively.

[0177] Under the conditions described above, it is confirmed by actual measurement that the turn-on period T20 of the switching element 20 is approximately 235 ns. In other words, according to the gate drive circuit 10 of the first embodiment, the turn-on period of the switching element 20 can be decreased by 10% compared with the reference example (see FIGS. 1 and 12) described above (decreased from T10=260 ns to T20=235 ns).

[0178] Note that a SiC-MOSFET is used as the switching element 20 in the example described above, but the effect described above does not depend on a material or a structure of the switching element 20. For instance, using a Si-MOSFET, a Si-IGBT (Insulated Gate Bipolar Transistor), or a SiC-IGBT, improvement of the switching speed can be expected in the same manner, and there are wide applications to general gate drive circuits for a voltage drive type switching element as a drive target. When an IGBT is a drive target, as terminal names of the transistor M1 in the above description, "source" should be replaced with "emitter", and "drain" should be replaced with "collector".

[0179] However, as described above, a SiC-MOSFET has a smaller mutual conductance than a Si-MOSFET, and hence a turn-on period thereof is increased in an application where the drain current Id is large. Therefore, it is considered that the effect of improving the switching speed with the structure described above is high in the SiC-MOSFET. In view of this, it can be said that the structure of this embodiment is suitable particularly for a gate drive circuit that drives SiC-based switching element.

Second Embodiment

[0180] FIG. 17 is an equivalent circuit diagram illustrating a second embodiment of the gate drive circuit. The gate drive circuit 10 of this embodiment is based on the first embodiment (FIG. 14) and further includes a discharge unit DCHG1. The discharge unit DCHG1 is connected in parallel to the capacitor Cg, and discharges the capacitor Cg when the switching element 20 is turned off With this structure, when the switching element 20 is turned off, it is possible to prevent application of a negative voltage to the gate terminal of the switching element 20 or to adjust the voltage applied to the gate terminal of the switching element 20 as necessary.

Third Embodiment

[0181] FIG. 18 is an equivalent circuit diagram illustrating a third embodiment of the gate drive circuit. The gate drive circuit 10 of this embodiment is based on the second embodiment (FIG. 17) with the resistor Rg as the discharge unit DCHG1 and further includes the resistor Rgs connected between gate and source of the switching element 20.

[0182] In this case, a resistance of the resistor Rg and a resistance of the Rgs are adjusted so that Rg<Rgs holds. Then, a most part of the gate-source voltage Vgs that is applied when the switching element 20 is in the steady ON state can be applied across both ends of the gate-source parasitic capacitance Cgs. Further, with this structure, charge stored in the capacitor Cg when being turned on enables to apply a negative bias to the gate when being turned off only for an instant of switching, and hence higher speed switching can be realized not only when turning on but also when turning off. In the plateau region when being turned off, the voltage applied to the gate-source parasitic capacitance Cgs is Vp (>Vth), which cannot be negative, and hence this effect has a large influence on a device in which the DC rated voltage between gate and source on the negative side is close to zero, and a large negative bias cannot be applied regularly.

[0183] In particular, if Rg>>Rin and Rgs>>Rin is satisfied so that Rin can be substantially ignored on the circuit, physical property values of circuit elements are adjusted so that the relationship of Cg:(Cg+Cgs)=(Rg/Rgs):Rg is satisfied. Then, a capacitive division ratio between the capacitor Cg and the gate-source parasitic capacitance Cgs can be constant without depending on a drive condition (such as a drive frequency) of the switching element 20 and without causing an unwanted voltage fluctuation due to an imbalance among circuit constants. Note that even if Rg>>Rin and Rgs>>Rin is not satisfied, the same effect can be obtained by appropriately adjusting Rg, Rgs, and Cg in consideration of Rin and Cgs.

[0184] For instance, if Cgs=2 nF and Cg=30 nF, Rg is set to 1 k.OMEGA., and Rgs is set to 15 k.OMEGA.. Thus, without depending on a drive condition of the switching element 20, in the steady ON state thereof, the power supply voltage VCC is applied across both ends of the gate-source parasitic capacitance Cgs, and the voltage a is applied across both ends of the capacitor Cg.

Fourth Embodiment

[0185] FIG. 19 is an equivalent circuit diagram illustrating a fourth embodiment of the gate drive circuit. The gate drive circuit 10 of this embodiment is based on the second embodiment (FIG. 17) and includes a switch SW as the discharge unit DCHG1. With this structure, by setting the switch SW in OFF state in a period other than a period during which the switching element 20 is turned off, charge stored in the capacitor Cg can be maintained without being discharged, while when the switching element 20 is turned oar, the switch SW is switched to ON state, so that the charge stored in the capacitor Cg can be quickly discharged.

Fifth Embodiment

[0186] FIG. 20 is an equivalent circuit diagram illustrating a fifth embodiment of the gate drive circuit. The gate drive circuit 10 of this embodiment is based on the second embodiment (FIG. 17) and further includes a drive unit DRV2. Further, along with addition of the circuit elements, operation of the drive unit DRV1 is partially changed, too.

[0187] The drive unit DRV1 switches its output state between a first state (i.e. a (VCC+.alpha.) output state) and a second state (i.e. a Hi-Z state) in accordance with a logic level of the input control signal. Further, the drive unit DRV2 switches its output state between a first state (i.e. a Hi-Z state) and a second state (i.e. a VEE output state) in accordance with a logic level of the input inverted control signal (corresponding to a logically inverted signal of the control signal). Note that a 3-state buffer, a 3-state inverter or the like can be used as the drive units DRV1 and DRV2 realizing the above-mentioned operation.

[0188] The gate drive voltage source V2 supplies a negative side gate drive voltage VEE -2 V) to the drive unit DRV2. Note that the negative side gate drive voltage VEE should be higher than a negative side DC rated voltage between gate and source and lower than or equal to GND.

[0189] Adopting this structure, a turn-on driving path and a turn-off driving path can be separated front each other, and hence the gate-source voltage Vgs when the switching element 20 is turned off can be set to a voltage value that does not depend on a positive side gate drive voltage (VCC+.alpha.) (i.e. a voltage value that is not "-.alpha."). In this way, an application of a large reverse bias can be prevented, and hence the gate voltage drive can be performed in consideration of the negative side DC rated voltage.

Sixth Embodiment

[0190] FIG. 21 is an equivalent circuit diagram illustrating a sixth embodiment of the gate drive circuit. The gate drive circuit 10 of this embodiment is based on the filth embodiment (FIG. 20) and further includes a discharge unit DCHG2. The discharge unit DCHG2 is connected between an output terminal of the drive unit DRV2 and the gate terminal of the switching element 20.

[0191] Adopting this structure, a discharge condition when being turned off can be designed separately from that when being turned on.

Seventh Embodiment

[0192] FIG. 22 is an equivalent circuit diagram illustrating a seventh embodiment of the gate drive circuit. The gate drive circuit 10 of this embodiment is bused on the sixth embodiment (FIG. 21) and includes a capacitor Cg2 as the discharge unit DCHG2. In this way, as the discharge unit DCHG2 is the capacitor Cg2, higher speed can be realized also in a turning off operation of the switching element 20.

Eighth Embodiment

[0193] FIG. 23 is an equivalent circuit diagram illustrating an eighth embodiment of the gate drive circuit. The gate drive circuit 10 of this embodiment is based on the sixth embodiment (FIG. 21) and includes a resistor Rg2 as the discharge unit DCHG2. In this way, if it is not necessary to realize higher speed of the turning off operation of the switching element 20, the resistor Rg2 can be used as the discharge unit DCHG2.

Ninth Embodiment

[0194] FIG. 24 is an equivalent circuit diagram illustrating a ninth embodiment of the gate drive circuit. The gate drive circuit 10 of this embodiment is based on the sixth embodiment (FIG. 21) and includes switches SW1 and SW2 as the drive units DRV1 and DRV2.

[0195] As described above, it is sufficient that the drive unit DRV1 can switch its output state between the first state (i.e. the VCC+.alpha. output state) and the second state (i.e. the Hi-Z state) in accordance with the input control signal. Therefore, using the switch SW1 that is turned on and off between the gate drive voltage source V1 and the capacitor Cg as well as the discharge unit DCHG1, the drive unit DRV1 can be easily realized.

[0196] In the same manner, it is sufficient that the drive unit DRV2 can switch its output state between the first state (i.e. the Hi-Z state) and the second state (i.e. the VEE output state) in accordance with the input inverted control signal. Therefore, using the switch SW2 that is turned on and off between the gate drive voltage source V2 and the discharge unit DCHG2, the drive unit DRV2 can be easily realized.

[0197] <Consideration About Capacitance Variation>

[0198] As described above, the gale driving devices 10 of the first to ninth embodiments can easily realize high speed switching of the switching element 20. However, if the capacitance ratio of Cg:Ciss varies, the gate voltage of the switching element 20 (i.e. the voltage Vgs(real) across both ends of the gate-source parasitic capacitance Cgs accompanying the transistor M1) varies, and hence the variation may cause an increase in a switching loss or an excess of the gate voltage over a rated value.

[0199] Therefore, as a countermeasure against capacitance ratio variation, voltage division resistors (see, for example, the resistor Rg and the resistor Rgs in FIG. 18) are necessary. In order to decrease a loss in the voltage division resistors, resistance values of them should be set to high values. However, as resistance values of the voltage division resistors are higher, time until the gate voltage is stabilized is longer, and hence the effect of the countermeasure with the voltage division resistors becomes smaller.

[0200] In the following description, various proposals are given for a novel embodiment that can easily and appropriately realize high speed switching of the switching element 20, even if there is a variation in the capacitor Cg or the input capacitance Ciss.

Tenth Embodiment

[0201] FIG. 25 is an equivalent circuit diagram illustrating a tenth embodiment of the gate drive circuit. The ewe drive circuit 10 of this embodiment includes a P-channel type MOS field-effect transistor Q1, an N-channel type MOS field-effect transistor Q2, a P-channel type MOS field-effect transistor Q3, an N-channel type MOS field-effect transistor Q4, a capacitor Cg, a diode D1, and a diode D2. Note that in this diagram, a MOS field-effect transistor is used for each of the transistors Q1 to Q4, but this is not a limitation.

[0202] A source of the transistor Q (corresponding to a first transistor) is connected to an application terminal of a first voltage V1(=VCC+.alpha., where VCC=18 V and .alpha.=6 V, for example). A drain of the transistor Q1 is connected to a first terminal of the capacitor Cg. A second terminal of the capacitor Cg is connected to a gate of the switching element 20. A gate of the transistor Q1 is connected to an application terminal of a control signal S1. Therefore, the transistor Q1 is ON when the control signal S1 is low level, while it is OFF when the control signal S1 is high level.

[0203] A drain of the transistor Q2 (corresponding to a second transistor) is connected to the first terminal of the capacitor Cg. A source of the transistor Q2 is connected to an application terminal of a second voltage V2 (=VEE, where VEE=0 V, for example). A gate of the transistor Q2 is connected to an application terminal of a control signal S2. Therefore, the transistor Q2 is ON when the control signal S2 is high level, while it is OFF when the control signal S2 is low level.

[0204] Note that the control signals S1 and S2 are pulse signals having basically the same logic level, and the transistor Q2 is driven in anti-phase (complementarily) with respect to the transistor Q1. In other words, the transistor Q2 is OFF when the transistor Q1 is ON, while it is ON when the transistor Q1 is OFF. However, the above "driven in anti-phase" includes a case where a simultaneous OFF period of the transistors Q1 and Q2 (a so-called dead time) is provided to prevent a shoot-through current.

[0205] Further, if each of the transistors Q1 and Q2 is an N-channel type, it is also possible to use a logically inverted signal of the control signal S1 as the control signal S2, for example (the simultaneous OFF period is added separately).

[0206] A source of the transistor Q3 (corresponding to a third transistor) is connected to an application terminal of a third voltage V3 (VCC). The third voltage V3 should be set to a recommended operation voltage of the switching element 20 (i.e. a voltage lower than a maximum rated value of the gate-source voltage Vgs(real), e.g. 18 V). A drain of the transistor Q3 is connected to an anode of the diode D1 (corresponding to a first rectifier element). A cathode of the diode D1 is connected to a second terminal of the capacitor Cg. A gate of the transistor Q3 is connected to an application terminal of the control signal S1. Therefore, the transistor Q3 is ON when the control signal S1 is low level, while it is OFF when the control signal S1 is high level.

[0207] In this way, as the common control signal S1 is input to the transistors Q1 and Q3, the transistor Q3 is driven in the same phase as the transistor Q1. In other words, the transistor Q3 is ON when the transistor Q1 is ON, while it is OFF when the transistor Q1 is OFF. However, the above "driven in the same phase" includes a case where the ON tinting of the transistor Q1 is delayed from the ON timing of the transistor Q3, as shown in a twelfth embodiment (FIG. 35) or a thirteenth embodiment (FIG. 38), which are described later.

[0208] Note that the third voltage V3 (=VCC) should be generated from the first voltage V1 (=VCC+.alpha.). In this case, as the DC voltage conversion means, a regulator (see FIG. 45 described later) may be used, or a simpler voltage division resistor circuit or voltage division capacitor circuit may be used.

[0209] A drain of the transistor Q4 (corresponding to a fourth transistor) is connected to a cathode of the diode D2 (corresponding to a second rectifier element). An anode of the diode D2 is connected to a second terminal of the capacitor Cg. A source of the transistor Q4 is connected to an application terminal of a fourth voltage V4 (=VEE, e.g. VEE=0 V). A gate of the transistor Q4 is connected to an application terminal of the control signal S2. Therefore, the transistor Q4 is ON when the control signal S2 is high level, while it is OFF when the control signal S2 is low level.