Shared Decoder Circuit And Method

YANG; XiuLi ; et al.

U.S. patent application number 16/582514 was filed with the patent office on 2021-03-04 for shared decoder circuit and method. The applicant listed for this patent is TAIWAN SEMICONDUCTOR MANUFACTURING COMPANY, LTD., TSMC CHINA COMPANY, LIMITED, TSMC NANJING COMPANY, LIMITED. Invention is credited to Kuan CHENG, Luping KONG, He-Zhou WAN, Ching-Wei WU, XiuLi YANG.

| Application Number | 20210065759 16/582514 |

| Document ID | / |

| Family ID | 1000005399742 |

| Filed Date | 2021-03-04 |

| United States Patent Application | 20210065759 |

| Kind Code | A1 |

| YANG; XiuLi ; et al. | March 4, 2021 |

SHARED DECODER CIRCUIT AND METHOD

Abstract

A circuit includes a selection circuit configured to receive a first address at a first input and a second address at a second input, pass the first address to an output when a select signal has a first logical state, and pass the second address to the output when the select signal has a second logical state different from the first logical state. The circuit also includes a decoder configured to decode the passed first address or second address.

| Inventors: | YANG; XiuLi; (Shanghai, CN) ; WU; Ching-Wei; (Caotun Town, TW) ; WAN; He-Zhou; (Shanghai, CN) ; CHENG; Kuan; (Shanghai, CN) ; KONG; Luping; (Nanjing, CN) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 1000005399742 | ||||||||||

| Appl. No.: | 16/582514 | ||||||||||

| Filed: | September 25, 2019 |

| Current U.S. Class: | 1/1 |

| Current CPC Class: | G11C 8/10 20130101; G11C 7/1087 20130101; G11C 7/222 20130101; G11C 7/109 20130101; G11C 11/418 20130101; G11C 8/18 20130101; G11C 11/419 20130101; G11C 7/1063 20130101; G11C 7/106 20130101; G11C 8/08 20130101 |

| International Class: | G11C 8/18 20060101 G11C008/18; G11C 8/10 20060101 G11C008/10; G11C 8/08 20060101 G11C008/08; G11C 7/22 20060101 G11C007/22; G11C 7/10 20060101 G11C007/10; G11C 11/418 20060101 G11C011/418; G11C 11/419 20060101 G11C011/419 |

Foreign Application Data

| Date | Code | Application Number |

|---|---|---|

| Aug 29, 2019 | CN | 201910808044.X |

Claims

1. A circuit comprising: a selection circuit configured to receive a first address at a first input and a second address at a second input, pass the first address to an output responsive to a select signal having a first logical state, and pass the second address to the output responsive to the select signal having a second logical state different from the first logical state; and a decoder configured to decode the passed first address or second address.

2. The circuit of claim 1, further comprising: a first latch circuit configured to output the first address to the first input responsive to a first clock pulse signal; and a second latch circuit coupled between the selection circuit and the decoder, the second latch circuit configured to latch the passed first address or second address responsive to a second clock pulse signal.

3. The circuit of claim 2, further comprising a control circuit configured to receive a clock signal, a first enable signal, and a second enable signal, and generate the select signal, the first clock pulse signal, and the second clock pulse signal based on the clock signal, the first enable signal, and the second enable signal.

4. The circuit of claim 3, wherein the second latch circuit is configured to latch the passed first address or second address responsive to a first transition of the second clock pulse signal from a first one of the first logical state or the second logical state to a second one of the first logical state or the second logical state, and the control circuit is further configured to generate the first transition while the select signal has the first logical state.

5. The circuit of claim 4, wherein the second latch circuit is configured to output the passed first address or second address responsive to a second transition of the second clock pulse signal from the second one of the first logical state or the second logical state to the first one of the first logical state or the second logical state, and the control circuit is further configured to generate the second transition while the select signal has the second logical state.

6. The circuit of claim 5, further comprising a pre-decoder coupled between the second latch circuit and the decoder, wherein the control circuit is further configured to activate the pre-decoder for a first interval and a second interval, during the first interval, the second clock pulse signal has the second one of the first logical state or the second logical state and the select signal transitions from the second logical state to the first logical state, and during the second interval, the second clock pulse signal has the second one of the first logical state or the second logical state and the select signal has the first logical state.

7. The circuit of claim 3, wherein the control circuit is further configured to cause the select signal to transition from the second logical state to the first logical state based on the clock signal, and transition from the first logical state to the second logical state based on a tracking signal.

8. The circuit of claim 7, wherein the control circuit is further configured to generate the tracking signal responsive to the first enable signal and responsive to the second enable signal.

9. The circuit of claim 1, wherein the decoder comprises an output coupled to a plurality of word line signal paths, and the decoder is configured to activate a word line signal path of the plurality of word line signal paths corresponding to the decoded passed first address or second address.

10. A method of operating a memory circuit, the method comprising: receiving a select signal, a first address, and a second address at a selection circuit; using the selection circuit to pass the first address to an address decoder in response to the select signal having a first logical state and the second address to the address decoder in response to the select signal having a second logical state different from the first logical state; and using the address decoder to decode the first address or the second address.

11. The method of claim 10, wherein the receiving the first address at the selection circuit comprises receiving the first address from a latch circuit.

12. The method of claim 10, wherein the passing the one of the first address or the second address to the address decoder comprises receiving the one of the first address or the second address from the selection circuit at a latch circuit.

13. The method of claim 10, further comprising: using the selection circuit to pass the other of the first address or the second address to the address decoder; and using the address decoder to decode the other of the first address or the second address.

14. The method of claim 13, further comprising: based on the decoded first address, activating a first word line of a memory array in a write operation; and based on the decoded second address, activating a second word line of the memory array in a read operation.

15. A memory circuit comprising: a memory array; a selection circuit configured to receive a write address at a first input and a read address at a second input, pass the write address to an output when a select signal has a first logical state, and pass the read address to the output when the select signal has a second logical state different from the first logical state; and a decoder configured to decode the passed write address or read address, and activate a word line signal path of the memory array corresponding to the decoded write address or read address.

16. The memory circuit of claim 15, further comprising a control circuit configured to generate a clock pulse signal responsive to a clock signal, wherein the clock pulse signal comprises at least one of a first pulse or a second pulse during a period of the clock signal, and the memory circuit is configured to activate the word line signal path corresponding to the decoded read address during the first pulse, and activate the word line signal path corresponding to the decoded write address during the second pulse.

17. The memory circuit of claim 16, wherein the first pulse has a first pulse width based on a first tracking interval, and the second pulse has a second pulse width based on a second tracking interval.

18. The memory circuit of claim 17, wherein the memory circuit is configured to receive the read address from a first port and the write address from a second port, the first tracking interval is based on a read operation using the first port, and the second tracking interval is based on a write operation using the second port.

19. The memory circuit of claim 16, wherein the control circuit is configured to generate the first pulse responsive to a first enable signal, and generate the second pulse responsive to a second enable signal.

20. The memory circuit of claim 15, wherein the memory array comprises a register file of processor registers, and the memory circuit is configured to control data movement in pseudo two-port register file (2PRF) operations.

Description

PRIORITY CLAIM

[0001] The present application claims priority to the China Patent Application No. 201910808044.X, filed Aug. 29, 2019, which is incorporated herein by reference in its entirety.

BACKGROUND

[0002] Memory arrays are often used to store and access data used for various types of computations such as logic or mathematical operations. To perform these operations, data are moved through data ports between the memory arrays and circuits used to perform the computations. In some cases, the number of data lines in a memory array through which stored data are accessed is less than the number of data ports, and some or all of the data lines are shared for data movement operations.

BRIEF DESCRIPTION OF THE DRAWINGS

[0003] Aspects of the present disclosure are best understood from the following detailed description when read with the accompanying figures. It is noted that, in accordance with the standard practice in the industry, various features are not drawn to scale. In fact, the dimensions of the various features may be arbitrarily increased or reduced for clarity of discussion.

[0004] FIG. 1 is a diagram of a memory circuit, in accordance with some embodiments.

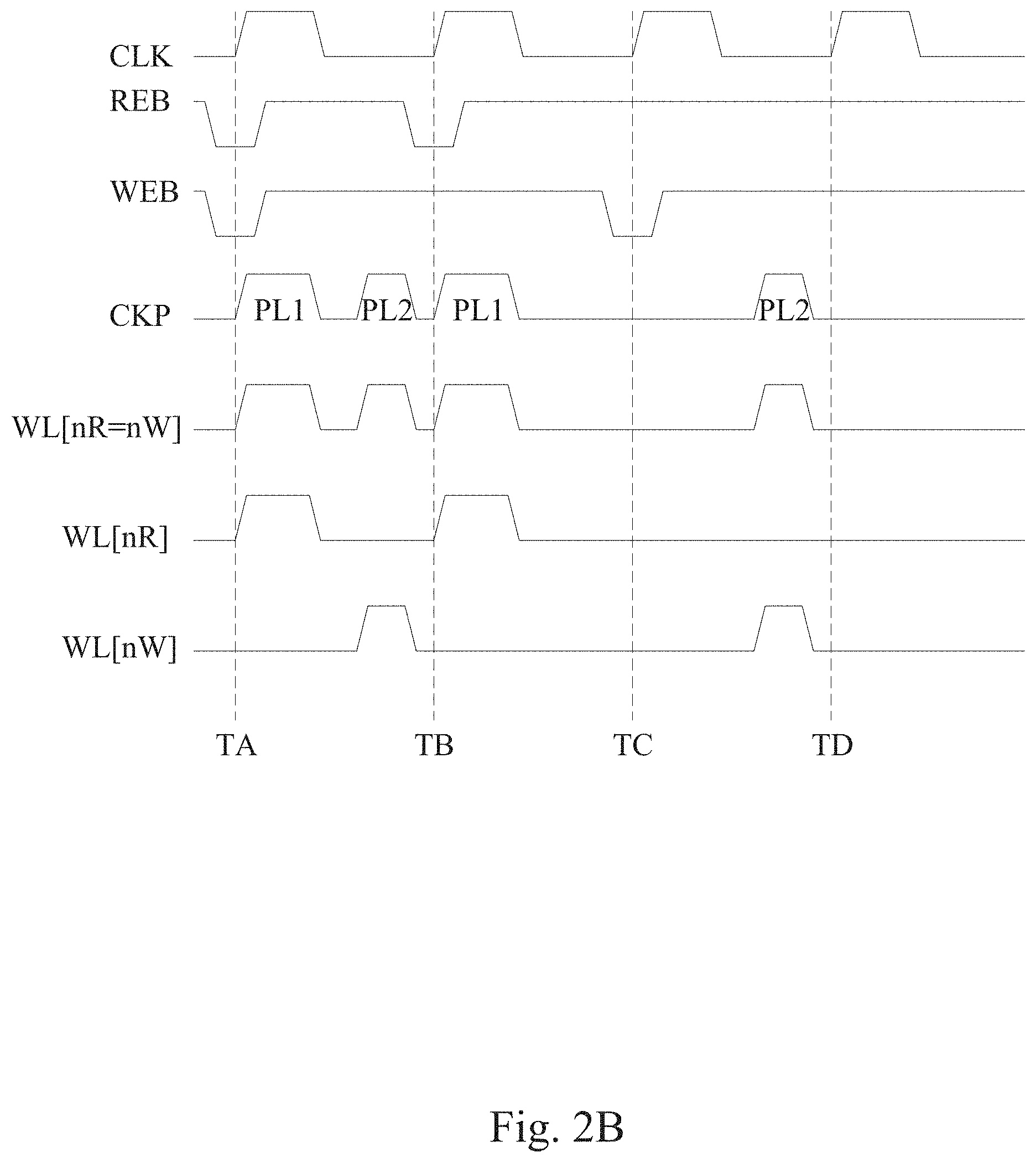

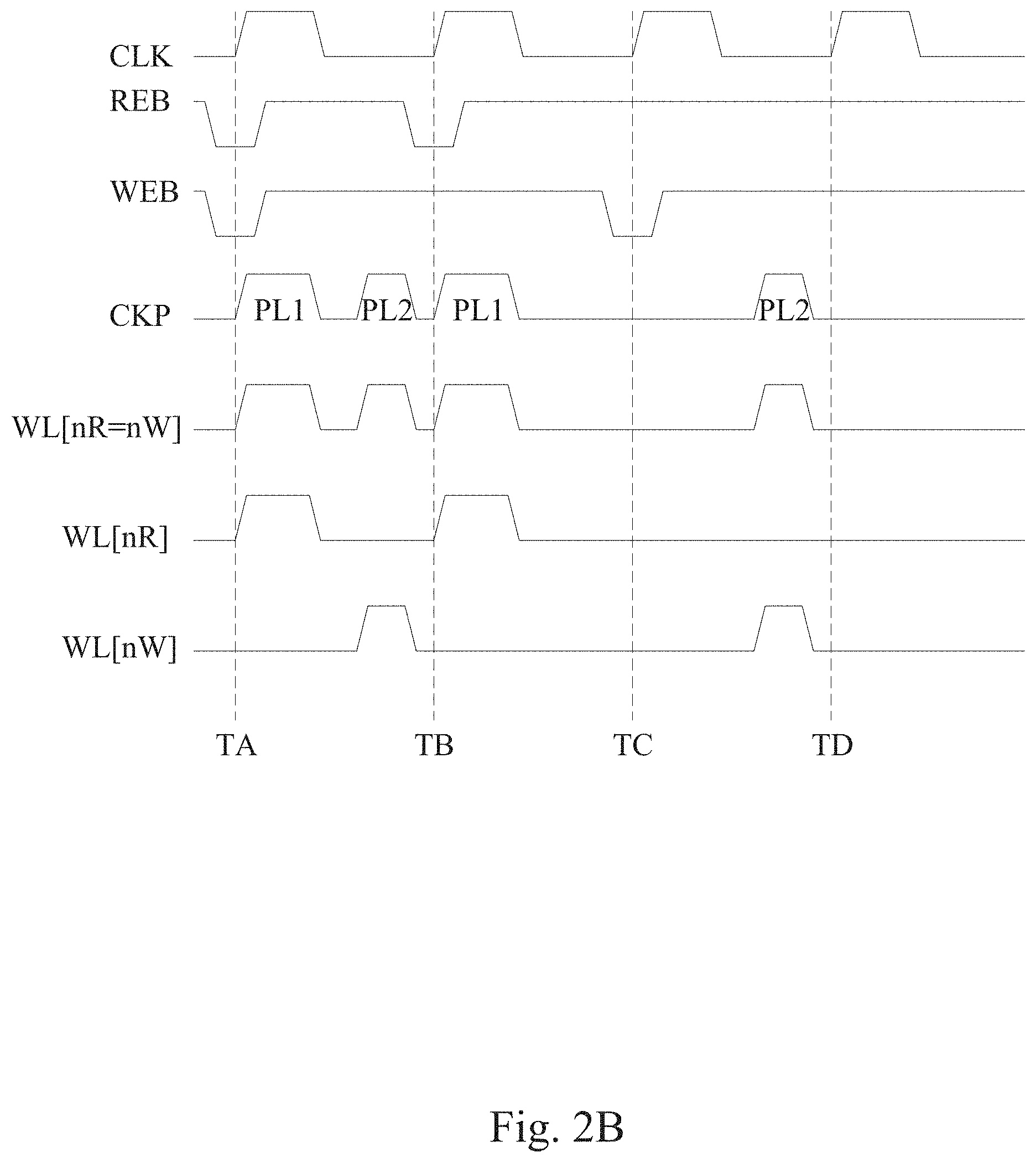

[0005] FIGS. 2A and 2B are plots of memory circuit operating parameters, in accordance with some embodiments.

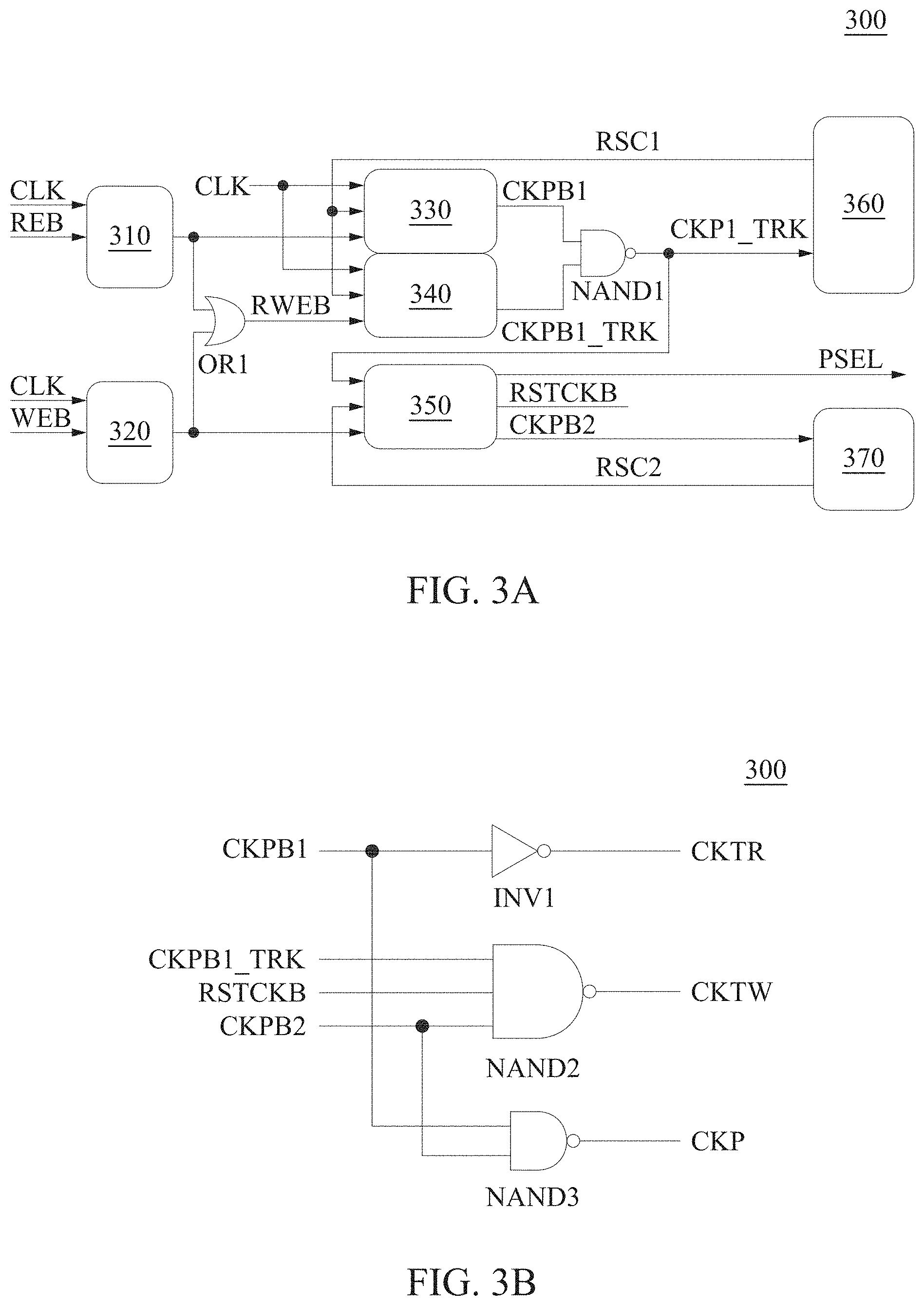

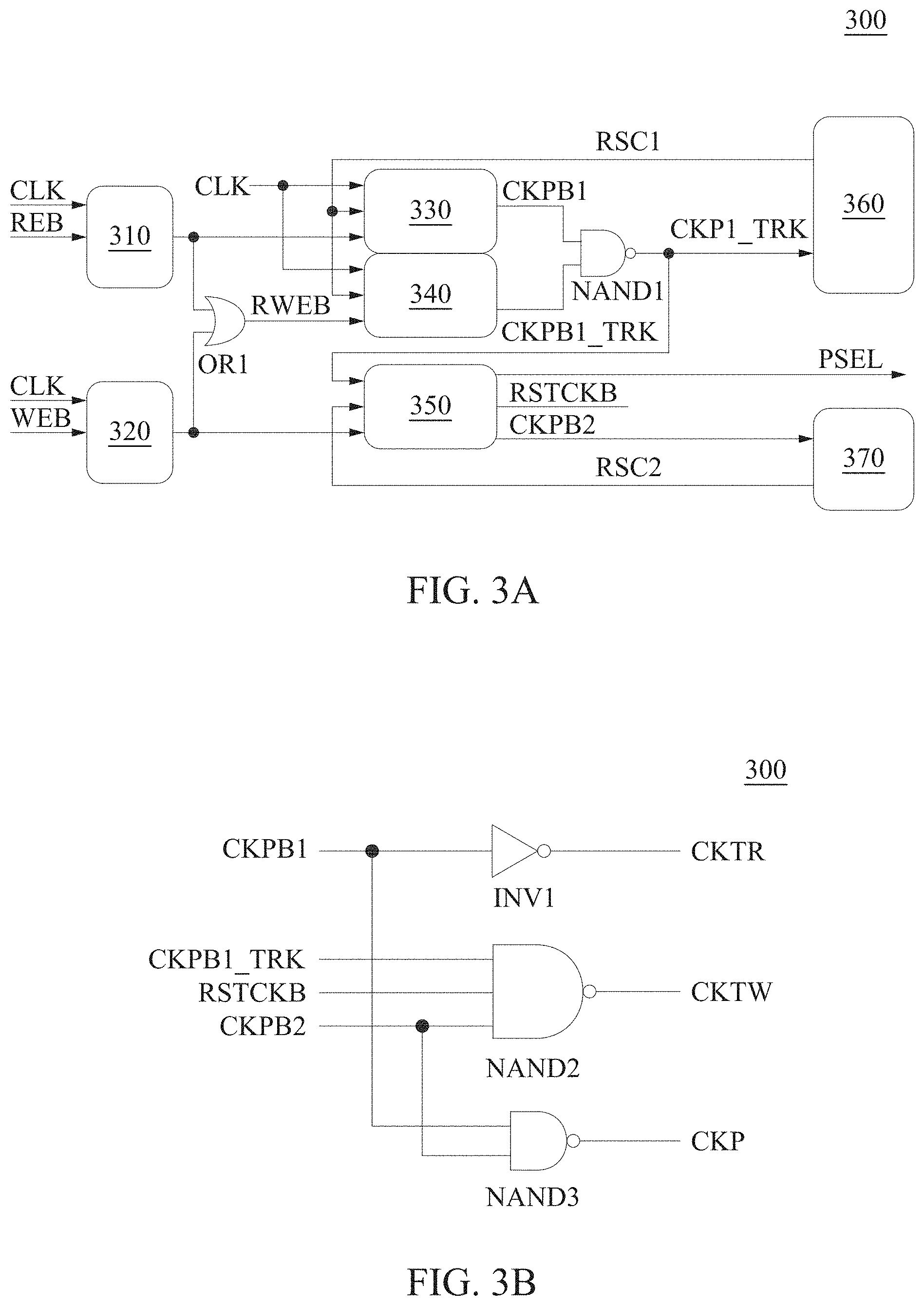

[0006] FIGS. 3A and 3B are diagrams of a control circuit, in accordance with some embodiments.

[0007] FIGS. 4A and 4B are plots of memory circuit operating parameters, in accordance with some embodiments.

[0008] FIG. 5 is a diagram of a signal generation circuit, in accordance with some embodiments.

[0009] FIG. 6 is a diagram of a signal generation circuit, in accordance with some embodiments.

[0010] FIGS. 7A and 7B are plots of memory circuit operating parameters, in accordance with some embodiments.

[0011] FIG. 8 is a flowchart of a method of operating a memory circuit, in accordance with some embodiments.

DETAILED DESCRIPTION

[0012] The following disclosure provides many different embodiments, or examples, for implementing different features of the provided subject matter. Specific examples of components, values, operations, materials, arrangements, or the like, are described below to simplify the present disclosure. These are, of course, merely examples and are not intended to be limiting. Other components, values, operations, materials, arrangements, or the like, are contemplated. For example, the formation of a first feature over or on a second feature in the description that follows may include embodiments in which the first and second features are formed in direct contact, and may also include embodiments in which additional features may be formed between the first and second features, such that the first and second features may not be in direct contact. In addition, the present disclosure may repeat reference numerals and/or letters in the various examples. This repetition is for the purpose of simplicity and clarity and does not in itself dictate a relationship between the various embodiments and/or configurations discussed.

[0013] Further, spatially relative terms, such as "beneath," "below," "lower," "above," "upper" and the like, may be used herein for ease of description to describe one element or feature's relationship to another element(s) or feature(s) as illustrated in the figures. The spatially relative terms are intended to encompass different orientations of the device in use or operation in addition to the orientation depicted in the figures. The apparatus may be otherwise oriented (rotated 90 degrees or at other orientations) and the spatially relative descriptors used herein may likewise be interpreted accordingly.

[0014] In various embodiments, a circuit includes a single decoder and a selection circuit and is configured to select and decode one of two addresses corresponding to data movement, e.g., read and write, operations in a memory array. By using a single decoder to activate control lines during the data movement operations, area requirements are reduced compared to approaches in which separate decoders are used for each of two addresses in memory array data movement operations.

[0015] FIG. 1 is a diagram of a memory circuit 100, in accordance with some embodiments. Memory circuit 100, also referred to as circuit 100, includes a latch circuit 110, a selection circuit 120, a latch circuit 130, a pre-decoder 140, a decoder 150, a memory array 160, and a control circuit 170. As discussed below, control circuit 170 includes a signal generation portion, also referred to as a double pump generator in some embodiments, configured to generate various timing signals, and a clock buffer portion configured to output various control signals based on the timing signals.

[0016] Memory circuit 100 is configured as discussed below to receive an address RX from a port P1, an address WX from a port P2, a clock signal CLK, and enable signals REB and WEB, and, in response to clock signal CLK and enable signals REB and WEB, select and decode one of addresses RX or WX, thereby generating one or more of a number N of word line signals WL[1]-WL[N] on a corresponding one or more of word line signal paths WP[1]-WP[N].

[0017] In some embodiments, memory array 160 is a static random access memory (SRAM) array including single-port memory cells, and memory circuit 100 is configured to facilitate data movement in and out of single-port memory cells identified by addresses RX and WX. In some embodiments, memory circuit 100 is configured to facilitate data movement in and out of single-port memory cells at column locations, also referred to as X locations, identified by addresses RX and WX. In some embodiments, addresses RX and WX are derived from corresponding addresses (not shown) that include additional information, e.g., column identifiers, and addresses RX and WX do not include the additional information.

[0018] In some embodiments, memory array 160 includes a register file of processor registers including single-port memory cells, and memory circuit 100 is configured to control data movement in pseudo two-port register file (2PRF) operations. In pseudo 2PRF operations, in some embodiments, single-port memory cells are used to perform functions of two-port memory cells by using a single clock signal instead of two separate clock signals. A first half of a clock cycle of the single clock signal is used to control a read operation based on a read address received on a read port, and a second half of the clock cycle is used to control a write operation based on a write address received on a write port. In some embodiments, memory circuit 100 is included in an ultra-high density (UHD) pseudo 2PRF circuit. In some embodiments, memory circuit 100 is an integrated circuit (IC).

[0019] In the embodiment depicted in FIG. 1, memory circuit 100 includes memory array 160 coupled to decoder 150 through word line signal paths WP[1]-WP[N]. In various embodiments, memory circuit 100 includes word line signal paths WP[1]-WP[N] and does not include memory array 160, or includes neither memory array 160 nor word line signal paths WP[1]-WP[N].

[0020] Latch circuit 110 is coupled to port P2, selection circuit 120, and control circuit 170; selection circuit 120 is coupled to port P1, each of latch circuits 110 and 130, and control circuit 170; latch circuit 130 is coupled to selection circuit 120, pre-decoder 140, and control circuit 170; pre-decoder 140 is coupled to latch circuit 130, decoder 150, and control circuit 170; and decoder 150 is coupled to pre-decoder 140 and memory array 160.

[0021] Two or more circuit elements are considered to be coupled based on one or more direct signal connections and/or one or more indirect signal connections that include one or more logic devices, e.g., an inverter or logic gate, between the two or more circuit elements. In some embodiments, signal communications between the two or more coupled circuit elements are capable of being modified, e.g., inverted or made conditional, by the one or more logic devices.

[0022] Each of addresses RX and WX includes a combination of logical states configured to identify one or more physical locations in a memory array, e.g., memory array 160, corresponding to a given word. In some embodiments, each word corresponds to a row of memory array 160, address RX is configured to identify a corresponding row of memory array 160 in a read operation, and address WX is configured to identify a corresponding row of memory array 160 in a write operation.

[0023] An address RX or WX includes a number L of logical states corresponding to 2.sup.L words in some or all of a memory, e.g., memory array 160. In some embodiments, L is a number of logical states ranging from two logical states corresponding to four words, to 12 logical states corresponding to 4096 words. In some embodiments, an address RX or WX includes L equal to four logical states corresponding to 16 words. In some embodiments, the 2.sup.L words corresponding to the L logical states in addresses RX and WX is equal to the number N of word line signal paths WP[1]-WP[N].

[0024] In the embodiment depicted in FIG. 1, each of ports P1 and P2, latch circuits 110 and 130, selection circuit 120, and pre-decoder 140 includes one or more electrical paths configured to conduct one or more signals corresponding to the L logical states included in addresses RX and WX. In some embodiments, each of ports P1 and P2, latch circuits 110 and 130, selection circuit 120, and pre-decoder 140 includes a number of electrical paths equal to L.

[0025] In various embodiments, at least one of latch circuits 110 or 130 is one latch circuit of a plurality of latch circuits (not shown) and/or selection circuit 120 is one selection circuit of a plurality of selection circuits (not shown), the at least one plurality of latch circuits and/or selection circuits being configured to collectively conduct the one or more signals corresponding to the L logical states included in addresses RX and WX. In some embodiments, each of latch circuits 110 and 130 includes a single electrical path and is one latch circuit of the number L of latch circuits, selection circuit 120 includes a single electrical path and is one selection circuit of the number L of selection circuits, and circuit 100 is thereby configured to collectively conduct the one or more signals corresponding to the L logical states included in addresses RX and WX.

[0026] Latch circuit 110 is an electronic circuit that includes an input 111 configured to receive address WX from port P2, an input 113 configured to receive a clock pulse signal CKTW from control circuit 170, and an output 112 configured to output address WX, selectively latched responsive to clock pulse signal CKTW.

[0027] Selection circuit 120 is an electronic circuit that includes an input 121 configured to receive address RX from port P1, an input 123 configured to receive address WX from output 112 of latch circuit 110, an input 125 configured to receive a select signal PSEL from control circuit 170, and an output 122 configured to output either of addresses RX or WX responsive to select signal PSEL. Selection circuit 120 is thereby configured to pass the selected address RX or WX to output 122. In some embodiments, selection circuit 120 includes a multiplexer.

[0028] Latch circuit 130 is an electronic circuit that includes an input 131 configured to receive either of addresses RX or WX from output 122 of selection circuit 120, an input 133 configured to receive a clock pulse signal CKTR from control circuit 170, and an output 132 configured to output the received address RX or WX, selectively latched responsive to clock pulse signal CKTR.

[0029] Pre-decoder 140 is a combinational logic circuit that includes an input 141 configured to receive either of addresses RX or WX from output 132 of latch circuit 130, an input 143 configured to receive a clock pulse signal CKP from control circuit 170, and an output 142 configured to output a partially decoded address PD based on the received address RX or WX, selectively enabled responsive to clock pulse signal CKP.

[0030] Decoder 150 is a combinational logic circuit that includes an input 151 configured to receive partially decoded address PD from output 142 of pre-decoder 140, and an output 152 configured to output one or more of word line signals WL[1]-WL[N] on a corresponding one or more of word line signal paths WP[1]-WP[N] based on partially decoded address PD.

[0031] In the embodiment depicted in FIG. 1, pre-decoder 140 and decoder 150 are separate circuits. In some embodiments, pre-decoder 140 and decoder 150 are a single combinational logic circuit configured to output one or more of word line signals WL[1]-WL[N] on a corresponding one or more of word line signal paths WP[1]-WP[N] based on address RX or WX received on input 141 from output 132 of latch circuit 130, selectively enabled responsive to clock pulse signal CKP.

[0032] In some embodiments, memory circuit 100 does not include decoder 150, output 142 of pre-decoder 140 is an output of memory circuit 100, and pre-decoder 140 is configured to output partially decoded address PD as one or more output signals of memory circuit 100.

[0033] Memory array 160 is an array of memory cells (not shown) arranged in rows and columns. A memory cell of memory array 160 includes electrical, electromechanical, electromagnetic, or other devices configured to store bit data represented by logical states. In some embodiments, a logical state corresponds to a voltage level of an electrical charge stored in a given memory cell. In some embodiments, a logical state corresponds to a physical property, e.g., a resistance or magnetic orientation, of a component of a given memory cell.

[0034] In some embodiments, the memory cells of memory array 160 include SRAM cells. In various embodiments, SRAM cells include five-transistor (5T) SRAM cells, six-transistor (6T) SRAM cells, eight-transistor (8T) SRAM cells, nine-transistor (9T) SRAM cells, or SRAM cells having other numbers of transistors. In some embodiments, the memory cells of memory array 160 include dynamic random-access memory (DRAM) cells or other memory cell types capable of storing bit data.

[0035] Some or all of the memory cells of a given row or column of memory array 160 are configured to be activated simultaneously in read and write operations as a word, responsive to a corresponding one or more of word line signals WL[1]-WL[N] received from a corresponding one or more of word line signal paths WP[1]-WP[N]. In some embodiments, each word corresponds to a row of memory cells in memory array 160, and each one of word line signal paths WP[1]-WP[N] is coupled to the memory cells in the row corresponding to a given word.

[0036] Addresses RX and WX, clock pulse signals CKTW, CKTR, and CKP, select signal PSEL, word line signals WL[1]-WL[N], and other signals used by memory circuit 100 discussed below, are configured to have one or more voltage levels corresponding to logical states. A high logical state corresponds to a voltage level at or above a first predetermined threshold, and a low logical state corresponds to a voltage level at or below a second predetermined threshold. In various embodiments, the first predetermined threshold corresponds to a voltage level at or near an operating voltage level, e.g., a voltage level VDD or VDDM, of memory circuit 100, and/or the second predetermined threshold corresponds to a voltage level at or near a reference voltage level, e.g., a voltage level VSS or ground, of memory circuit 100.

[0037] In various embodiments, latch circuit 110 is configured to latch address WX in response to clock pulse signal CKTW having a predetermined one of the high or low logical states, selection circuit 120 is configured to pass a given one of address RX or WX to output 122 in response to select signal PSEL having a corresponding one of the high or low logical states, latch circuit 130 is configured to latch address RX or WX in response to clock pulse signal CKTR having a predetermined one of the high or low logical states, and pre-decoder 140 is configured to output partially decoded address PD in response to clock pulse signal having a predetermined one of the high or low logical states.

[0038] In various embodiments, decoder 150 is configured to activate a given one or more of word line signal paths WP[1]-WP[N], and thereby the corresponding word, by outputting the one or more word line signals WL[1]-WL[N] having a predetermined one of the high or low logical states. Outputting a given one of word line signals WL[1]-WL[N] having the predetermined one of the high or low logical states is also referred to as activating the given one of word line signals WL[1]-WL[N], and outputting the given one of word line signals WL[1]-WL[N] having the other of the high or low logical states is referred to as deactivating the given one of word line signals WL[1]-WL[N], in some embodiments.

[0039] Control circuit 170 is an electronic circuit configured to receive clock signal CLK and enable signals REB and WEB, and generate clock pulse signals CKTW, CKTR, and CKP, and select signal PSEL based on clock signal CLK and enable signals REB and WEB. Control circuit 170 is configured to control operating parameters of memory circuit 100, thereby generating clock pulse signals CKTW, CKTR, and CKP and select signal PSEL having timing relationships as discussed below with respect to FIGS. 2A and 2B. In some embodiments, control circuit 170 includes a control circuit 300 discussed below with respect to FIG. 3.

[0040] FIG. 2A is a plot of memory circuit 100 operating parameters, in accordance with some embodiments. In the non-limiting example depicted in FIG. 2A, signals CLK, CKTW, CKTR, PSEL, and CKP include transitions between the high and low logical states corresponding to memory circuit 100 operation at times t1-t5 as discussed below. FIG. 2A depicts a case in which each of enable signals REB and WEB has a logical state corresponding to an enabled state and is not shown for the purpose of clarity.

[0041] In the embodiment depicted in FIG. 2A, each of latch circuits 110 and 130 is configured to, in response to the corresponding clock pulse signal transitioning to the high logical state, latch the received address and pass the latched address to the corresponding output until the corresponding clock pulse signal transitions to the low logical state, and in response to the corresponding clock pulse signal having the low logical state, pass the received address to the corresponding output without performing the latching operation. Selection circuit 120 is configured to pass each of addresses RX and WX to output 122 in response to select signal PSEL having respective low and high logical states, and pre-decoder 140 is configured to selectively output partially decoded address PD in response to clock pulse signal CKP having the high logical state.

[0042] In various embodiments, memory circuit 100 is configured to operate based on one or more of signals CLK, CKTW, CKTR, PSEL, or CKP having one or more logical states and/or transitions other than those depicted in FIG. 2A.

[0043] Clock signal CLK is generated by a circuit external to memory circuit 100 and includes a series of pulses having a predetermined period T. A rising edge of a pulse corresponds to a transition from the low logical state to the high logical state, and a falling edge of the pulse corresponds to a transition from the high logical state to the low logical state.

[0044] At time t1, control circuit 170 is configured to respond to a rising edge of clock signal CLK by generating a rising edge in each of clock pulse signals CKTW, CKTR, and CKP while select signal PSEL has the low logical state.

[0045] Based on the rising edge of clock pulse signal CKTW, latch circuit 110 latches address WX and passes latched address WX to output 112. Based on the low logical state of select signal PSEL, selection circuit 120 passes address RX to output 122. Based on the rising edge of clock pulse signal CKTR, latch circuit 130 latches address RX and passes latched address RX to output 122. Based on the rising edge of clock pulse signal CKP, pre-decoder 140 becomes enabled, thereby generating partially decoded address PD at output 142 based on latched address RX, and decoder 150 activates the word line signal of word line signals WL[1]-WL[N] corresponding to address RX, as discussed below with respect to FIG. 2B.

[0046] At time t2, subsequent to time t1, control circuit 170 is configured to generate a rising edge in select signal PSEL while each of clock pulse signals CKTW, CKTR, and CKP remains at the high logical state.

[0047] Because clock pulse signal CKTW remains at the high logical state, latch circuit 110 continues to pass latched address WX to output 112. Based on the rising edge of select signal PSEL, selection circuit 120 passes latched address WX to output 122. Because clock pulse signal CKTR remains at the high logical state, latch circuit 130 continues to pass latched address RX to output 132. Because clock pulse signal CKP remains at the high logical state, pre-decoder 140 remains enabled, thereby continuing to generate partially decoded address PD at output 142 based on latched address RX such that decoder 150 continues to activate the word line signal of word line signals WL[1]-WL[N] corresponding to address RX.

[0048] At time t3, subsequent to time t2, control circuit 170 is configured to generate a falling edge in each of clock pulse signals CKTR and CKP while each of clock pulse signal CKTW and select signal PSEL remains at the high logical state.

[0049] Because clock pulse signal CKTW remains at the high logical state, latch circuit 110 continues to pass latched address WX to output 112. Because select signal PSEL remains at the high logical state, selection circuit 120 continues to pass latched address WX to output 122. Based on the falling edge of clock pulse signal CKTR, latch circuit 130 ceases to latch address RX and passes latched address WX to output 122. Based on the falling edge of clock pulse signal CKP, pre-decoder 140 becomes disabled, thereby ceasing to generate partially decoded address PD at output 142 based on latched address RX, and decoder 150 deactivates the word line signal of word line signals WL[1]-WL[N] corresponding to address RX.

[0050] At time t4, subsequent to time t3, control circuit 170 is configured to generate a rising edge in clock pulse signal CKP while each of clock pulse signal CKTW and select signal PSEL remains at the high logical state and clock pulse signal CKTR remains at the low logical state.

[0051] Because clock pulse signal CKTW remains at the high logical state, latch circuit 110 continues to pass latched address WX to output 112. Because select signal PSEL remains at the high logical state, selection circuit 120 continues to pass latched address WX to output 122. Because clock pulse signal CKTR remains at the low logical state, latch circuit 130 continues to pass latched address WX to output 122. Based on the rising edge of clock pulse signal CKP, pre-decoder 140 becomes enabled, thereby generating partially decoded address PD at output 142 based on latched address WX, and decoder 150 activates the word lines signal of word line signals WL[1]-WL[N] corresponding to address WX, as discussed below with respect FIG. 2B.

[0052] At time t5, subsequent to time t4, control circuit 170 is configured to generate a falling edge in each of clock pulse signals CKTW and CKP and select signal PSEL while clock pulse signal CKTR remains at the low logical state.

[0053] Based on the falling edge of clock pulse signal CKTW, latch circuit 110 ceases to pass latched address WX to output 112. Based on the falling edge of select signal PSEL, selection circuit 120 passes address RX to output 122. Because clock pulse signal CKTR continues to have the low logical state, latch circuit 130 passes address RX to output 122. Based on the falling edge of clock pulse signal CKP, pre-decoder 140 becomes disabled, thereby ceasing to generate partially decoded address PD at output 142 based on latched address WX, and decoder 150 deactivates the word line signal of word line signals WL[1]-WL[N] corresponding to address WX.

[0054] The interval from times t1 to t3 corresponds to a pulse PL1 of clock pulse signal CPK during which decoder 150 activates the one of word line signals WL[1]-WL[N] based on latched address RX being passed to pre-decoder 140. In some embodiments, pulse PL1 corresponds to a read operation in memory array 160.

[0055] In the embodiment depicted in FIG. 2A, memory circuit 100 is configured to pass latched address RX to pre-decoder 140 during pulse PL1 by generating the rising edge of each of clock pulse signals CKTW, CKTR, and CKP at time t1 prior to generating the rising edge of select signal PSEL at time t2. In various embodiments, memory circuit 100 is configured to pass latched address RX to pre-decoder 140 during pulse PL1 by generating the rising edges of clock pulse signals CKTW, CKTR, and CKP having timings other than those depicted in FIG. 2A, such timings including causing latched address RX to be passed to pre-decoder 140 prior to generating the rising edge of select signal PSEL at time t2.

[0056] The interval from times t4 to t5 corresponds to a pulse PL2 of clock pulse signal CKP during which decoder 150 activates the one of word line signals WL[1]-WL[N] based on latched address WX being passed to pre-decoder 140. In some embodiments, pulse PL2 corresponds to a write operation in memory array 160.

[0057] In the embodiment depicted in FIG. 2A, memory circuit 100 is configured to pass latched address WX to pre-decoder 140 during pulse PL2 by generating the rising edge of clock pulse signal CKTW at time t1 and the rising edge of select signal PSEL at time t2 prior to generating the rising edge of pulse PL2 at time t4. In various embodiments, memory circuit 100 is configured to pass latched address WX to pre-decoder 140 during pulse PL2 by generating the rising edges of clock pulse signal CKTW and select signal PSEL having timings other than those depicted in FIG. 2A, such timings including causing latched address WX to be passed to pre-decoder 140 prior to or simultaneously with generating the rising edge of clock pulse signal CKP at time t4.

[0058] As indicated above, FIG. 2A depicts a case in which each of enable signals REB and WEB has a logical state corresponding to an enabled state. In some embodiments, memory circuit 100 is configured to respond to a case in which enable signal REB has a logical state corresponding to a disabled state by generating clock pulse signal CKP without pulse PL1 and/or to respond to a case in which enable signal WEB has a logical state corresponding to a disabled state by generating clock pulse signal CKP without pulse PL2.

[0059] As depicted in the non-limiting example of FIG. 2A, memory circuit 100 is configured to generate pulses PL1 and PL2 in the interval from times t1 to t5 less than period T of clock signal CLK. Memory circuit 100 is thereby capable of enabling a read operation and a write operation in memory array 160 during a single period T of clock signal CLK.

[0060] FIG. 2B is a plot of memory circuit 100 operating parameters, in accordance with some embodiments. FIG. 2B depicts non-limiting examples of word line signals WL[1]-WL[N] generated in response to received addresses RX and WX, clock signal CLK, and enable signals REB and WEB. The non-limiting example of FIG. 2B illustrates four clock signal periods, TA, TB, TC, and TD, and includes each of enable signals REB and WEB having the low logical state corresponding to the enabled state, and word line signals WL[1]-WL[N] having the high logical state corresponding to the activated state. An address nR is a non-limiting example of received address RX and an address nW is a non-limiting example of received address WX.

[0061] At the start of clock signal period TA, enable signal REB has the low logical state corresponding to an enabled read operation, and enable signal WEB has the low logical state corresponding to an enabled write operation. At the start of clock signal period TB, enable signal REB has the low logical state corresponding to an enabled read operation, and enable signal WEB has the high logical state corresponding to a disabled write operation. At the start of clock signal period TC, enable signal REB has the high logical state corresponding to a disabled read operation, and enable signal WEB has the low logical state corresponding to an enabled write operation. At the start of clock signal period TD, enable signal REB has the high logical state corresponding to a disabled read operation, and enable signal WEB has the high logical state corresponding to a disabled write operation.

[0062] Accordingly, circuit 100 generates clock pulse signal CKP including each of pulses PL1 and PL2 during clock signal period TA, pulse PL1 and not pulse PL2 during clock signal period TB, pulse PL2 and not pulse PL1 during clock signal period TC, and neither one of pulses PL1 and PL2 during clock signal period TD.

[0063] FIG. 2B depicts non-limiting examples of word line signals WL[1]-WL[N] for two cases: a first case in which a single word line signal WL[nR=nW] corresponds to address nR being the same as address nW; and a second case in which a word line signal WL[nR] corresponds to address nR and a word line signal WL[nW] corresponds to address nW different from address nR. In various embodiments, each of addresses nR and nW has the number L equal to 4, and one or both of addresses nR or nW is equal to 0000 and/or 1111.

[0064] In the first case, during clock signal period TA, decoder 150 generates word line signal WL[nR=nW] including the activated read state in response to address nR and pulse PL1, and the activated write state in response to address nW and pulse PL2. During clock signal period TB, decoder 150 generates word line signal WL[nR=nW] including the activated read state in response to address nR and pulse PL1, and not including the activated write state. During clock signal period TC, decoder 150 generates word line signal WL[nR=nW] not including the activated read state and including the activated write state in response to address nW and pulse PL2. During clock signal period TD, decoder 150 generates word line signal WL[nR=nW] not including the activated read state and not including the activated write state.

[0065] In the second case, during clock signal period TA, decoder 150 generates word line signal WL[nR] including the activated read state in response to address nR and pulse PL1 and not including the activated write state, and generates word line signal WL[nW] not including the activated read state and including the activated write state in response to address nW and pulse PL2. During clock signal period TB, decoder 150 generates word line signal WL[nR] including the activated read state in response to address nR and pulse PL1 and not including the activated write state, and generates word line signal WL[nW] not including the activated read state and not including the activated write state. During clock signal period TC, decoder 150 generates word line signal WL[nR] not including the activated read state and not including the activated write state, and generates word line signal WL[nW] not including the activated read state and including the activated write state in response to address nW and pulse PL2. During clock signal period TD, decoder 150 generates word line signal WL[nR] not including the activated read state and not including the activated write state, and generates word line signal WL[nW] not including the activated read state and not including the activated write state.

[0066] By the configuration discussed above, memory circuit 100 is capable of selecting and decoding one of two addresses corresponding to data movement operations in memory array 160 using decoder 150 and selection circuit 120 during a single clock period. Memory circuit 100 thereby has reduced area requirements compared to approaches in which separate decoders are used during a single clock period for each of two addresses in memory array data movement operations.

[0067] Significant area reduction is achieved by reducing a number of data lines used to activate a given word in a memory array. By reducing the number of decoders from two to one, the number of data lines that carry the enable signal used to activate the given word is similarly reduced from two to one.

[0068] FIGS. 3A and 3B are diagrams of control circuit 300, in accordance with some embodiments. Control circuit 300 is usable as control circuit 170 discussed above with respect to memory circuit 100 and FIGS. 1-2B.

[0069] FIG. 3A depicts a signal generation portion of control circuit 300 configured to generate various signals including select signal PSEL based on clock signal CLK and enable signals REB and WEB, and FIG. 3B depicts a clock buffer portion of control circuit 300 configured to generate clock pulse signals CKTW, CKTR, and CKP based on the various signals, as discussed below.

[0070] The signal generation portion of control circuit 300 includes latch circuits 310 and 320, signal generation circuits 330, 340, and 350, port tracking circuits 360 and 370, OR gate OR1, and NAND gate NAND1. The clock buffer portion of control circuit 300 includes inverter INV1 and NAND gates NAND2 and NAND3.

[0071] An output of latch circuit 310 is coupled to an input of signal generation circuit 330 and to an input of OR gate OR. An output of latch circuit 320 is coupled to an input of signal generation circuit 350 and to an input of OR gate OR1. An output of OR gate OR1 is coupled to an input of signal generation circuit 340.

[0072] An output of signal generation circuit 330 is coupled to an input of NAND gate NAND1, an output of signal generation circuit 340 is coupled to the other input of NAND gate NAND1, and an output of signal generation circuit 350 is coupled to an input of port tracking circuit 370. An output of NAND gate NAND1 is coupled to an input of port tracking circuit 360.

[0073] An output of port tracking circuit 360 is coupled to an input of signal generation circuit 330 and to an input of signal generation circuit 340. An output of port tracking circuit 370 is coupled to an input of signal generation circuit 350.

[0074] Latch circuit 310 is an electronic circuit configured to receive enable signal REB and clock signal CLK and, responsive to clock signal CLK, latch and output enable signal REB to signal generation circuit 330 and OR gate OR1.

[0075] Latch circuit 320 is an electronic circuit configured to receive enable signal WEB and clock signal CLK and, responsive to clock signal CLK, latch and output enable signal WEB to signal generation circuit 350 and OR gate OR1.

[0076] OR gate OR1 is a logic gate configured to receive latched enable signals REB and WEB and, responsive to latched enable signals REB and WEB, output an enable signal RWEB to signal generation circuit 340.

[0077] Signal generation circuit 330 is an electronic circuit configured to receive clock signal CLK, latched enable signal REB, and a reset signal RSC1, and responsive to clock signal CLK, latched enable signal REB, and reset signal RSC1, output a clock pulse signal CKPB1 to NAND gates NAND1 and NAND3 and inverter INV1. Signal generation circuit 330 is configured to generate clock pulse signal CKPB1 including logical state transitions discussed below with respect to FIGS. 4A and 4B. In some embodiments, signal generation circuit 330 is a signal generation circuit 500 discussed below with respect to FIG. 5.

[0078] Signal generation circuit 340 is an electronic circuit configured to receive clock signal CLK, enable signal RWEB, and reset signal RSC1, and responsive to clock signal CLK, enable signal RWEB, and reset signal RSC1, output a clock pulse signal CKPB1_TRK to NAND gates NAND1 and NAND2. Signal generation circuit 340 is configured to generate clock pulse signal CKPB1_TRK including logical state transitions discussed below with respect to FIGS. 4A and 4B. In some embodiments, signal generation circuit 340 is signal generation circuit 500 discussed below with respect to FIG. 5.

[0079] Signal generation circuit 350 is an electronic circuit configured to receive a clock pulse signal CKP1_TRK, latched enable signal WEB, and a reset signal RSC2, and responsive to clock pulse signal CKP1_TRK, latched enable signal WEB, and reset signal RSC2, output a clock pulse signal CKPB2 to port tracking circuit 370 and NAND gates NAND2 and NAND3, a reset signal RSTCKB to NAND gate NAND2, and select signal PSEL discussed above with respect to FIGS. 1 and 2A. Signal generation circuit 330 is configured to generate clock pulse signal CKPB2, reset signal RSTCKB, and select signal PSEL including logical state transitions discussed below with respect to FIG. 4A. In some embodiments, signal generation circuit 350 is a signal generation circuit 600 discussed below with respect to FIG. 6.

[0080] NAND gate NAND1 is a logic gate configured to receive clock pulse signals CKPB1 and CKPB1_TRK and, responsive to clock pulse signals CKPB1 and CKPB1_TRK, output a clock pulse signal CKP1_TRK to port tracking circuit 360.

[0081] Port tracking circuit 360 is an electronic circuit configured to receive clock pulse signal CKP1_TRK and generate reset signal RSC1 responsive to a timing of a tracking circuit (not shown) configured to replicate a read operation using port P1 and initiated by clock pulse signal CKP1_TRK, thereby generating reset signal RSC1 including a logical state transition after a tracking interval sufficiently long to ensure completion of a read operation on port P1.

[0082] Port tracking circuit 370 is an electronic circuit configured to receive clock pulse signal CKPB2 and generate reset signal RSC2 responsive to a timing of a tracking circuit (not shown) configured to replicate a write operation using port P2 and initiated by clock pulse signal CKPB2, thereby generating reset signal RSC2 including a logical state transition after a tracking interval sufficiently long to ensure completion of a write operation on port P2.

[0083] Inverter INV1 is a logic gate configured to receive clock pulse signal CKPB1 and output inverted clock pulse signal CKPB1 as clock pulse signal CKTR discussed above with respect to FIGS. 1 and 2A and discussed below with respect to FIG. 4B.

[0084] NAND gate NAND2 is a logic gate configured to receive clock pulse signals CKPB1_TRK and CKPB2 and reset signal RSTCKB and, responsive to clock pulse signals CKPB1_TRK and CKPB2 and reset signal RSTCKB, output clock pulse signal CKTW discussed above with respect to FIGS. 1 and 2A and discussed below with respect to FIG. 4B.

[0085] NAND gate NAND3 is a logic gate configured to receive clock pulse signals CKPB1 and CKPB2 and, responsive to clock pulse signals CKPB1 and CKPB2, output clock pulse signal CKP discussed above with respect to FIGS. 1-2B and discussed below with respect to FIG. 4B.

[0086] FIGS. 4A and 4B are plots of memory circuit 100 and control circuit 300 operating parameters, in accordance with some embodiments. In the non-limiting example depicted in FIGS. 4A and 4B, signals CLK, CKPB1, CKPB1_TRK, CKP1_TRK, RSC1, RSTCKB, CKPB2, RSC2, PSEL, CKP, CKTR, and CKTW include transitions T1-T24 between the high and low logical states corresponding to control circuit 300 operation as discussed below. FIGS. 4A and 4B depict a case in which enable signals REB, WEB, and thereby RWEB, have logical states corresponding to an enabled state and are not shown for the purpose of clarity.

[0087] As depicted in FIG. 4A, transition T1 is a rising edge of clock signal CLK. In response to transition T1, signal generation circuit 330 generates transition T2, a falling edge of clock pulse signal CKPB1, and signal generation circuit 340 generates transition T3, a falling edge of clock pulse signal CKPB1_TRK. In the case depicted in FIGS. 4A and 4B in which signal generation circuits 330 and 340 are both enabled, transitions T2 and T3 are generated simultaneously. In response to either of transitions T2 or T3, NAND gate NAND1 generates transition T4, a rising edge of clock pulse signal CKP1_TRK.

[0088] In response to transition T4, signal generation circuit 350 generates transition T5, a falling edge of reset signal RSTCKB, and, in response to transition T5, generates transition T6, a rising edge of select signal PSEL. In response to transition T4, and after the tracking interval discussed above, port tracking circuit 360 generates transition T7, a falling edge of reset signal RSC1.

[0089] In response to transition T7, signal generation circuit 330 generates transition T8, a rising edge of clock pulse signal CKPB1, and signal generation circuit 340 generates transition T9, a rising edge of clock pulse signal CKPB1_TRK. In response to transitions T8 and T9, NAND gate NAND1 generates transition T10, a falling edge of clock pulse signal CKP1_TRK.

[0090] In response to transition T10, signal generation circuit 350 generates transition T11, a falling edge of clock pulse signal CPKB2. In response to transition T11, and after the tracking interval discussed above, port tracking circuit 370 generates transition T12, a falling edge of reset signal RSC2.

[0091] In response to transition T12, signal generation circuit 350 generates transition T13, a rising edge of reset signal RSTCKB, and transition T14, a rising edge of clock pulse signal CKPB2.

[0092] In response to transition T14, port tracking circuit 370 generates transition T15, a rising edge of reset signal RSC2, and signal generation circuit 350 generates transition T16, a falling edge of select signal PSEL.

[0093] As depicted in FIG. 4B, in response to transitions T2 and T8, the respective falling and rising edges of clock pulse signal CKPB1, NAND gate NAND3 generates transitions T17 and T18. Transitions T17 and T18, the respective rising and falling edges of pulse PL1 of clock pulse signal CKP, thereby correspond to a pulse width of pulse PL1 based on clock pulse signal CKPB1.

[0094] In response to transitions T11 and T14, the respective falling and rising edges of clock pulse signal CKPB2, NAND gate NAND3 generates transitions T19 and T20. Transitions T19 and T20, the respective rising and falling edges of pulse PL2 of clock pulse signal CKP, thereby correspond to a pulse width of pulse PL2 based on clock pulse signal CKPB2.

[0095] In response to transitions T2 and T8, the respective falling and rising edges of clock pulse signal CKPB1, inverter INV1 generates transitions T21 and T22, respective rising and falling edges of clock pulse signal CKTR.

[0096] In response to transitions T3 and T14, the respective falling edge of clock pulse signal CKPB1_TRK and rising edge of clock pulse signal CKPB2, NAND gate NAND2 generates transitions T23 and T24, respective rising and falling edges of clock pulse signal CKTW.

[0097] Transition T17 is generated by NAND gate NAND3 in response to transition T2, and thereby follows transition T2 by a single gate delay, a time interval corresponding to a logical state transition in a logic gate. Transition T21 is generated by inverter INV1 in response to transition T2, and thereby follows transition T2 by a single gate delay. Transition T23 is generated by NAND gate NAND2 in response to transition T3, simultaneous with transition T2, and thereby follows transition T2 by a single gate delay.

[0098] By causing each of transitions T17, T21, and T23, the rising edges of respective clock pulse signals CKP, CKTR, and CKTW, to follow transition T2 by a single gate delay, control circuit 300 is configured to generate the rising edges of respective clock pulse signals CKP, CKTR, and CKTW at or near time t1 as discussed above with respect to FIG. 2A.

[0099] Transition T4 is generated by NAND gate NAND1 in response to either of simultaneous transitions T2 or T3, and thereby follows transition T2 by a single gate delay. Transition T6 is generated by signal generation circuit 350 in response to transition T4, and thereby follows transition T4 by at least one gate delay and follows transition T2 by at least two gate delays.

[0100] By causing transition T6, the rising edge of select signal PSEL, to follow transition T2 by at least two gate delays, control circuit 300 is configured to generate the rising edge of select signal PSEL at time t2 subsequent to time t1 as discussed above with respect to FIG. 2A, thereby ensuring that latch circuit 130 has latched address RX based on transition T21 of clock pulse signal CKTR prior to selection circuit 120 ceasing to pass address RX to latch circuit 130 based on the rising edge of select signal PSEL.

[0101] Because transition T18, the falling edge of pulse PL1 of clock pulse signal CKP, and transition T22, the falling edge of clock pulse signal CKTR, follow transition T7, the falling edge of reset signal RSC1, after the corresponding tracking interval has elapsed, control circuit 300 is configured to cause partially decoded address PD to be output from pre-decoder 140 based on latched address RX until time t3, discussed above with respect to FIG. 2A, thereby ensuring completion of the corresponding read operation prior to signal transitions T18 and T22.

[0102] By causing transition T16, the falling edge of select signal PSEL, to follow transitions T18 and T22, control circuit 300 is configured to cause selection circuit 120 and latch circuit 130 to pass latched address WX to pre-decoder 140 after completion of the corresponding read operation.

[0103] By causing transition T19, the rising edge of pulse PL2 of clock pulse signal CKP, to follow transition T18, the falling edge of pulse PL1 of clock pulse signal CKP, control circuit 300 is configured to provide the interval from time t3 to time t4, discussed above with respect to FIG. 2A, thereby ensuring that latched address WX is being passed to pre-decoder 140 prior to the start of a subsequent write operation.

[0104] By including OR gate OR1, signal generation circuits 330 and 340, and NAND gate NAND1, control circuit 300 is configured to generate transition T10 in clock pulse signal CKP1_TRK in response to either of enable signals REB or WEB having the logical state corresponding to an enabled state, thereby causing pulse PL2 of clock pulse signal CKP to start at time t4 so that a write operation has a timing relative to clock signal CLK independent of the execution of a read operation.

[0105] As discussed above, transition T12, the falling edge of reset signal RSC2, occurs after the tracking interval corresponding to a write operation has elapsed. Transition T14, the rising edge of clock pulse signal CKPB2, follows transition T12. Because transition T20, the falling edge of pulse PL2 of clock pulse signal CKP, and transition T24, the falling edge of clock pulse signal CKTW, follow transition T14, control circuit 300 is configured to cause partially decoded address PD to be output from pre-decoder 140 based on latched address WX until time t5, discussed above with respect to FIG. 2A, thereby ensuring completion of the corresponding write operation prior to signal transitions T20 and T24.

[0106] As indicated above, FIGS. 4A and 4B depict a case in which each of enable signals REB and WEB has a logical state corresponding to an enabled state. In a case in which enable signal REB has a logical state corresponding to a disabled state, signal generation circuit 330 is configured so that transitions T2 and T8 in clock pulse signal CKPB1 are not generated, and control circuit 300 is thereby configured to respond to the disabled state by generating clock pulse signal CKP without pulse PL1, as discussed above with respect to FIG. 2B, so that pre-decoder 140 does not output partially decoded address PD during the interval from time t1 to time t3.

[0107] In a case in which enable signal WEB has a logical state corresponding to a disabled state, signal generation circuit 350 is configured so that transitions T11 and T14 in clock pulse signal CKPB2 are not generated, and control circuit 300 is thereby configured to respond to the disabled state by generating clock pulse signal CKP without pulse PL2, as discussed above with respect to FIG. 2B, so that pre-decoder 140 does not output partially decoded address PD during the interval from time t4 to time t5.

[0108] In addition to the timing features discussed above with respect to the configuration depicted in FIGS. 3A and 3B, control circuit 300 is capable of generating clock pulse signals CKTW, CKTR, and CKP, and select signal PSEL based on clock signal CLK and enable signals REB and WEB having the timing control and benefits discussed above with respect to memory circuit 100 and FIGS. 1-2B.

[0109] FIG. 5 is a diagram of signal generation circuit 500, in accordance with some embodiments. Signal generation circuit 500 is usable as one or both of signal generation circuits 330 or 340 discussed above with respect to control circuit 300 and FIGS. 3A-4B.

[0110] Signal generation circuit 500 includes p-type metal-oxide-semiconductor (PMOS) transistors P1-P7, n-type metal-oxide-semiconductor (NMOS) transistors N1-N7, and logic gates inverters INV2-INV4 and NOR gate NOR1.

[0111] Transistors P1, N1, and N2 are coupled in series between a power supply node VDD and a reference node VSS. A source terminal of transistor P1 is coupled to power supply node VDD, a drain terminal of transistor P1 is coupled to a drain terminal of transistor N1, a source terminal of transistor N1 is coupled to a drain terminal of transistor N2, and a source terminal of transistor N2 is coupled to reference node VSS.

[0112] Transistors P2 and P3 are coupled in series with each other and parallel to transistor P1. A source terminal of transistor P2 is coupled to power supply node VDD, a drain terminal of transistor P2 is coupled to a source terminal of transistor P3, and a drain terminal of transistor P3 is coupled to the drain terminals of transistors P1 and N1.

[0113] Transistor N3 is coupled in parallel with transistor N2. A drain terminal of transistor N3 is coupled to the drain terminal of transistor N2, and a source terminal of transistor N3 is coupled to reference node VSS.

[0114] Transistors P4, P5, N4, and N5 are coupled in series between power supply node VDD and reference node VSS. A source terminal of transistor P4 is coupled to power supply node VDD, a drain terminal of transistor P4 is coupled to a source terminal of transistor P5, a drain terminal of transistor P5 is coupled to a drain terminal of transistor N4, a source terminal of transistor N4 is coupled to a drain terminal of transistor N5, and a source terminal of transistor N5 is coupled to reference node VSS.

[0115] Transistors P6, P7, N6, and N7 are coupled in series between power supply node VDD and reference node VSS. A source terminal of transistor P6 is coupled to power supply node VDD, a drain terminal of transistor P6 is coupled to a source terminal of transistor P7, a drain terminal of transistor P7 is coupled to a drain terminal of transistor N6, a source terminal of transistor N6 is coupled to a drain terminal of transistor N7, and a source terminal of transistor N7 is coupled to reference node VSS.

[0116] The drain terminals of transistors P4 and P6 and the source terminals of transistors P5 and P7 are coupled to each other, gates of transistors P5 and N7 are configured to receive reset signal RSC1, discussed above with respect to control circuit 300 and FIGS. 3A-4B, and gates of transistors P6 and N4 are configured to receive clock signal CLK.

[0117] The drain terminals of transistors P5, P7, N4, and N6 are coupled to each other and to an output OUT1, and are thereby configured to output one of clock pulse signals CKPB1 or CKPB1_TRK discussed above with respect to control circuit 300 and FIGS. 3A-4B.

[0118] Inverter INV2 is coupled to gates of transistors P2 and N2, and is thereby configured to receive clock signal CLK and output inverted clock signal CLK as clock signal CLKB to the gates of transistors P2 and N2.

[0119] Inverter INV3 is coupled between inverter INV4 and gates of transistors P1 and N1, and is thereby configured to output signal CKP1B to the gates of transistors P1 and N1.

[0120] Inverter INV4 is coupled between output OUT1 and inverter INV3 and gates of transistors P7 and N6, and is thereby configured to output inverted clock pulse signal CKPB1 or CKPB1_TRK to inverter INV3 and the gates of transistors P7 and N6.

[0121] NOR gate NOR1 is coupled to the drains of transistors P1, P3, and N1 and to gates of transistors P3, P4, N3, and N5, and is thereby configured to receive signal CEB, the complement of one of latched enable signals REB or RWEB, discussed above with respect to memory circuit 100, control circuit 300, and FIGS. 1-4B, and output signal CLK_EN to the gates of transistors P3, P4, N3, and N5.

[0122] In operation, an initial state of signal generation circuit 500 includes clock signal CLK having the low logical state, signal CEB having the low logical state corresponding to activation of signal generation circuit 500, reset signal RSC1 having the high logical state, and the clock pulse signal CKPB1 or CKPB1_TRK having the high logical state.

[0123] In response to clock signal CLK having the low logical state, inverter INV2 outputs signal CLKB having the high logical state, thereby turning off transistor P2 and turning on transistor N2 and configuring transistors P1 and N1 as an inverter.

[0124] Reset signal RSC1 having the high logical state turns off transistor P5, and clock signal CLK having the low logical state turns off transistor N4, thereby decoupling output OUT1 from transistors P4 and N5.

[0125] Clock signal CLK having the low logical state turns on transistor P6, and reset signal RSC1 having the high logical state turns on transistor N7, thereby configuring transistors P7 and N6 as an inverter cross-coupled with inverter INV4.

[0126] In response to signal CEB having the low logical state, NOR gate NOR1 outputs signal CLK_EN responsive to the logical state of the drains of transistors P1, P3, and N.

[0127] In response to the clock pulse signal CKPB1 or CKPB1_TRK having the high logical state, inverter INV4 outputs the low logical state, and inverter INV3 outputs signal CKP1B having the high logical state, turning off transistor P1 and turning on transistor N1. The drains of transistors P1, P3, and N1 have the low logical state, and NOR gate NOR1 outputs signal CLK_EN having the high logical state, thereby turning off transistors P3 and P4 and turning on transistors N3 and N5.

[0128] In response to transition T1 of clock signal CLK, discussed above with respect to control circuit 300 and FIGS. 3A-4B, clock signal CLK having the high logical state turns off transistor P6 and turns on transistor N4, thereby decoupling output OUT1 from power supply node VDD, coupling output OUT1 to reference node VSS through transistors N4 and N5, and causing the clock pulse signal CKPB1 or CKPB1_TRK to have the low logical state. The clock pulse signal CKPB1 or CKPB1_TRK changing from the high logical state to the low logical state corresponds to the respective transition T2 or T3 discussed above with respect to control circuit 300 and FIGS. 3A-4B.

[0129] In response to clock signal CLK having the high logical state, inverter INV2 outputs signal CLKB having the low logical state, thereby turning on transistor P2 and turning off transistor N2.

[0130] In response to the clock pulse signal CKPB1 or CKPB1_TRK having the low logical state, inverter INV4 outputs the high logical state, and inverter INV3 outputs signal CKP1B having the low logical state, turning on transistor P1 and turning off transistor N1. The drains of transistors P1, P3, and N1 have the high logical state, and NOR gate NOR1 outputs signal CLK_EN having the low logical state, thereby turning on transistors P3 and P4 and turning off transistors N3 and N5.

[0131] Because of gate delays introduced by inverter INV3, transistors P1 and N1, and NOR gate NOR1, transistor N5 is turned off after transistor N7 is turned on, and output OUT1 is coupled to reference node VSS through transistors N6 and N7.

[0132] In response to transition T7 of reset signal RSC1, discussed above with respect to control circuit 300 and FIGS. 3A-4B, reset signal RSC1 having the low logical state turns on transistor P5 and turns off transistor N7, thereby decoupling output OUT1 from reference node VSS, coupling output OUT1 to power supply node VDD through transistors P4 and P5, and causing the clock pulse signal CKPB1 or CKPB1_TRK to have the high logical state. The clock pulse signal CKPB1 or CKPB1_TRK changing from the low logical state to the high logical state corresponds to the respective transition T8 or T9 discussed above with respect to control circuit 300 and FIGS. 3A-4B.

[0133] By the configuration depicted in FIG. 5 and discussed above, signal generation circuit 500 is capable of generating each of clock pulse signals CKPB1 or CKPB1_TRK responsive to clock signal CLK, the corresponding enable signal REB or RWEB, and reset signal RSC1 having the timing control and benefits discussed above with respect to memory circuit 100, control circuit 300, and FIGS. 1-4B.

[0134] FIG. 6 is a diagram of signal generation circuit 600, in accordance with some embodiments. Signal generation circuit 600 is usable as signal generation circuit 350 discussed above with respect to control circuit 300 and FIGS. 3A-4B.

[0135] Signal generation circuit 600 includes logic gates NAND gates NAND4-NAND8, inverters INV5-INV7, and NOR gates NOR2 and NOR3, a delay circuit 610, and word tracking circuits 620 and 630.

[0136] NAND gate NAND4 includes inputs configured to receive clock pulse signal CKP1_TRK, enable signal WEB, and reset signal RSC2, and an output coupled to an input of NAND gate NAND5.

[0137] NAND gate NAND5 includes an input coupled to an output of NAND gate NAND6 and an output coupled to an input of NAND gate NAND6 and an input of inverter INV5. NAND gate NAND6 includes an input configured to receive reset signal RSC2.

[0138] Inverter INV5 includes an output coupled to an input of NOR gate NOR2 and an input of NAND gate NAND8, and is thereby configured to output reset signal RSTCKB. NOR gate NOR2 includes an input configured to receive clock pulse signal CKP1_TRK, and an output coupled to delay circuit 610 and an input of NAND gate NAND7, and is thereby configured to output signal TRK_EN.

[0139] Inverter INV6 includes an input coupled to delay circuit 610 and an output coupled to word tracking circuit 620. Inverter INV7 includes an input coupled to delay circuit 610 and an output coupled to word tracking circuit 630. NOR gate NOR3 includes inputs coupled to each of word tracking circuits 620 and 630, and an output coupled to an input of NAND gate NAND7, and is thereby configured to output signal CKP2_PRE to NAND gate NAND7.

[0140] NAND gate NAND7 includes an output coupled to an input of NAND gate NAND8 and configured to output clock pulse signal CKPB2, discussed above with respect to control circuit 300 and FIGS. 3A-4B. NAND gate NAND8 is configured to output select signal PSEL, discussed above with respect to memory circuit 100, control circuit 300, and FIGS. 1-4B.

[0141] Delay circuit 610 is a configurable electronic circuit configured to delay signal TRK_EN outputted from NOR gate NOR2 by an interval determined by signal PTSEL[1:0], and to output the delayed signal TRK_EN. In the embodiment depicted in FIG. 6, delay circuit 610 is configured to receive signal PTSEL[1:0] having one of four logical state combinations, and to output signal TRK_EN having a corresponding delay equivalent to zero, two, four, or six gate delays. In various embodiments, delay circuit 610 is configured to receive signal PTSEL[1:0] having fewer or greater than four logical state combinations, and to output signal TRK_EN having a corresponding delay equivalent to a set of gate delays other than zero, two, four, or six gate delays.

[0142] In various embodiments, signal PTSEL[1:0] includes logical states corresponding to either voltage levels or short and open circuits configured by jumpers, pins, or other suitable conductive elements.

[0143] In operation, the configurable delay introduced by delay circuit 610 in response to signal PTSEL[1:0] is included in the timing of clock pulse signal CKPB2 and select signal PSEL, as discussed below. The timing of clock pulse signal CKPB2 and select signal PSEL thereby includes an overall delay that includes a predetermined delay component based on the configuration of delay circuit 610. Because the predetermined delay component is based on signal PTSEL[1:0], delay circuit 610 enables timing control to be adjusted based on user input reflecting timing requirements of the application in which signal generation circuit 600 is being used.

[0144] Each of word tracking circuits 620 and 630 is an electronic circuit configured to receive signal TRK_EN delayed by delay circuit 610 and inverted by respective inverter INV6 or INV7, and generate an output signal responsive to a timing of a tracking circuit (not shown) configured to replicate a write operation using port P2 and initiated by delayed and inverted signal TRK_EN. Each of word tracking circuits 620 and 630 is thereby configured to generate the output signal including a logical state transition after a tracking interval sufficiently long to ensure completion of a write operation on port P2.

[0145] Word tracking circuits 620 and 630 include tracking circuits configured to track separate aspects of the write operation such that the output signals generated by tracking circuits 620 and 630 include separate timing information. In some embodiments, word tracking circuit 620 includes tracking circuits configured to track timing based on a depth of a word line within a column of a memory array, e.g., memory array 160 discussed above with respect to memory circuit 100 and FIGS. 1-2B. In some embodiments, word tracking circuit 630 includes tracking circuits configured to track timing based on a width of a column of a memory array, e.g., memory array 160 discussed above with respect to memory circuit 100 and FIGS. 1-2B.

[0146] In operation, an initial state of signal generation circuit 600 includes clock pulse signal CKP1_TRK having the low logical state, enable signal WEB having the high logical state corresponding to activation of signal generation circuit 600, reset signal RSC2 having the high logical state, and NAND gate NAND5 outputting the low logical state latched to NAND gate NAND6 outputting the high logical state.

[0147] In response to clock pulse signal CKP1_TRK having the low logical state, NAND gate NAND4 outputs the high logical state to NAND gate NAND5. In response to NAND gate NAND5 having the low logical state, inverter INV5 outputs reset signal RSTCKB having the high logical state.

[0148] In response to clock pulse signal CKP1_TRK having the low logical state and reset signal RSTCKB having the high logical state, NOR gate NOR2 outputs signal TRK_EN having the low logical state. In response to signal TRK_EN having the low logical state, delay circuit 610 outputs the low logical state to each of inverters INV6 and INV7, each of inverters INV6 and INV7 outputs the high logical state to corresponding word tracking circuit 620 or 630, each of word tracking circuits 620 and 630 outputs the high logical state to NOR gate NOR3, and NOR gate NOR3 outputs signal CKP2_PRE having the low logical state.

[0149] In response to signal CKP2_PRE having the high logical state and signal TRK_EN having the low logical state, NAND gate NAND7 outputs clock pulse signal CKPB2 having the high logical state.

[0150] In response to clock pulse signal CKPB2 having the high logical state and reset signal RSTCKB having the high logical state, NAND gate NAND8 outputs select signal PSEL having the low logical state.

[0151] As a result of transition T4 of clock pulse signal CKP1_TRK, discussed above with respect to control circuit 300 and FIGS. 3A-4B, clock pulse signal CKP1_TRK has the high logical state. In response to clock pulse signal CKP1_TRK having the high logical state, NAND gate NAND4 outputs the low logical state, NAND gate NAND5 outputs the high logical state, and inverter INV5 outputs reset signal RSTCKB having the low logical state. Reset signal RSTCKB changing from the high logical state to the low logical state corresponds to transition T5 discussed above with respect to control circuit 300 and FIGS. 3A-4B.

[0152] In response to clock pulse signal CKP1_TRK having the high logical state and reset signal RSTCKB having the low logical state, NOR gate NOR2 continues to output signal TRK_EN having the low logical state, NOR gate NOR3 continues to output signal CKP2_PRE having the high logical state, and NAND gate NAND7 continues to output clock pulse signal CKPB2 having the high logical state.

[0153] In response to clock pulse signal CKPB2 having the high logical state and reset signal RSTCKB having the low logical state, NAND gate NAND8 outputs select signal PSEL having the high logical state. Select signal PSEL changing from the low logical state to the high logical state corresponds to transition T6 discussed above with respect to control circuit 300 and FIGS. 3A-4B.

[0154] As a result of transition T10 of clock pulse signal CKP1_TRK, discussed above with respect to control circuit 300 and FIGS. 3A-4B, clock pulse signal CKP1_TRK has the low logical state. In response to clock pulse signal CKP1_TRK having the low logical state, NAND gate NAND4 outputs the high logical state, and NAND gate NAND5 continues to output the high logical state in response to NAND gate NAND6 outputting the low logical state. Inverter INV5 therefore continues to output reset signal RSTCKB having the low logical state.

[0155] In response to each of clock pulse signal CKP1_TRK and reset signal RSTCKB having the low logical state, NOR gate NOR2 outputs signal TRK_EN having the high logical state. In response to signal TRK_EN having the high logical state, delay circuit 610 initially continues to output the low logical state, NOR gate NOR3 continues to output signal CKP2_PRE having the low logical state, and NAND gate NAND7 continues to output clock pulse signal CKPB2 having the high logical state.

[0156] After the configurable delay discussed above, delay circuit 610 outputs the high logical state to each of inverters INV6 and INV7, and each of inverters INV6 and INV7 outputs the low logical state to corresponding word tracking circuits 620 and 630.

[0157] Based on the timing discussed above, each of word tracking circuits 620 and 630 responds to the received low logical state by outputting the low logical state after a corresponding tracking delay. Until both of word tracking circuits 620 and 630 output the low logical state, NOR gate NOR3 continues to output signal CKP2_PRE having the low logical state. In response to both of word tracking circuits 620 and 630 outputting the low logical state, NOR gate NOR3 outputs signal CKP2_PRE having the high logical state.

[0158] In response to both output signal CKP2_PRE and signal TRK_EN having the high logical state, NAND gate NAND7 outputs clock pulse signal CKPB2 having the low logical state. Clock pulse signal CKPB2 changing from the high logical state to the low logical state corresponds to transition T11 discussed above with respect to control circuit 300 and FIGS. 3A-4B.

[0159] In response to each of clock pulse signal CKPB2 and reset signal RSTCKB having the low logical state, NAND gate NAND8 continues to output select signal PSEL having the high logical state.

[0160] In response to transition T12 of reset signal RSC2, discussed above with respect to control circuit 300 and FIGS. 3A-4B, reset signal RSC2 has the low logical state. In response to reset signal RSC2 having the low logical state, NAND gate NAND6 outputs the high logical state, NAND gate NAND5 outputs the low logical state, and inverter INV5 outputs reset signal RSTCKB having the high logical state. Reset signal RSTCKB changing from the low logical state to the high logical state corresponds to transition T13 discussed above with respect to control circuit 300 and FIGS. 3A-4B.

[0161] In response to clock pulse signal CKP1_TRK having the low logical state and reset signal RSTCKB having the high logical state, NOR gate NOR2 outputs signal TRK_EN having the low logical state. In response to signal TRK_EN having the low logical state and signal CKP2_PRE having either the low or high logical state, NAND gate NAND7 outputs clock pulse signal CKPB2 having the high logical state. Clock pulse signal CKPB2 changing from the low logical state to the high logical state corresponds to transition T14 discussed above with respect to control circuit 300 and FIGS. 3A-4B.

[0162] In response to each of clock pulse signal CKPB2 and reset signal RSTCKB having the high logical state, NAND gate NAND8 outputs select signal PSEL having the low logical state. Select signal PSEL changing from the high logical state to the low logical state corresponds to transition T16 discussed above with respect to control circuit 300 and FIGS. 3A-4B.