Systems And Methods For Addressing Devices In A Superconducting Circuit

Swenson; Loren J. ; et al.

U.S. patent application number 16/996595 was filed with the patent office on 2021-02-25 for systems and methods for addressing devices in a superconducting circuit. The applicant listed for this patent is D-WAVE SYSTEMS INC.. Invention is credited to Christopher B. Rich, George E.G. Sterling, Loren J. Swenson.

| Application Number | 20210057631 16/996595 |

| Document ID | / |

| Family ID | 1000005121331 |

| Filed Date | 2021-02-25 |

View All Diagrams

| United States Patent Application | 20210057631 |

| Kind Code | A1 |

| Swenson; Loren J. ; et al. | February 25, 2021 |

SYSTEMS AND METHODS FOR ADDRESSING DEVICES IN A SUPERCONDUCTING CIRCUIT

Abstract

Addressing a superconducting flux storage device may include applying a bias current, a low-frequency flux bias, and a high-frequency flux bias in combination to cause a combined address signal level to exceed a defined address signal latching level for the superconducting flux storage device. A bias current that, in combination with a low-frequency flux bias and a high-frequency flux bias, causes a combined address signal level to exceed a defined address signal latching level for a superconducting flux storage device is at least reduced by an asymmetry in the Josephson junctions of the CJJ. A low-frequency flux bias that, in combination with a bias current and a high-frequency flux bias, causes a combined address signal level to exceed a defined address signal latching level for a superconducting flux storage device is at least reduced by an asymmetry in the Josephson junctions of the CJJ.

| Inventors: | Swenson; Loren J.; (San Jose, CA) ; Sterling; George E.G.; (Vancouver, CA) ; Rich; Christopher B.; (Vancouver, CA) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 1000005121331 | ||||||||||

| Appl. No.: | 16/996595 | ||||||||||

| Filed: | August 18, 2020 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 62888605 | Aug 19, 2019 | |||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H03K 3/38 20130101; H01L 39/223 20130101; H01L 27/18 20130101; H03K 17/92 20130101; H01L 39/025 20130101; G11C 11/44 20130101 |

| International Class: | H01L 39/22 20060101 H01L039/22; H01L 39/02 20060101 H01L039/02; H01L 27/18 20060101 H01L027/18; H03K 3/38 20060101 H03K003/38; H03K 17/92 20060101 H03K017/92; G11C 11/44 20060101 G11C011/44 |

Claims

1. A superconducting integrated circuit comprising: a microwave transmission line; a superconducting flux storage device comprising a loop of material that is superconductive below a critical temperature interrupted by an asymmetric compound Josephson junction (CJJ), the asymmetric CJJ comprising: a first parallel current path interrupted by a first Josephson junction, the first Josephson junction characterized by a first critical current; and a second parallel current path interrupted by a second Josephson junction, the second parallel current path electrically in parallel with the first parallel current path, the second Josephson junction characterized by a second critical current, the second critical current of the second Josephson junction different from the first critical current of the first Josephson junction; a first superconducting resonator communicatively coupled to the microwave transmission line; and a first signal interface that inductively communicatively couples the first superconducting resonator to the superconducting flux storage device, wherein the first signal interface is operable to provide a first flux bias to the superconducting flux storage device.

2. The superconducting integrated circuit of claim 1 further comprising: a low-frequency address bias line; and an address interface that inductively communicatively couples the low-frequency bias address line to the superconducting flux storage device, wherein the address interface is operable to provide a second flux bias to the superconducting flux storage device.

3. The superconducting integrated circuit of claim 2, wherein the superconducting flux storage device comprises a superconducting digital-to-analog converter (DAC), the superconducting DAC which is operable to perform latching, and the superconducting DAC is programmed by a low-frequency bias signal carried by the low-frequency address bias line and by a microwave signal carried by the first superconducting resonator, which combine constructively to exceed a threshold address latching level, the low-frequency bias signal carried by the low-frequency address bias line which is at least reduced by a factor that depends on a difference between the first critical current of the first Josephson junction of the CJJ and the second critical current of the second Josephson junction of the CJJ.

4. The superconducting integrated circuit of claim 1, further comprising a current bias line, wherein a current in the current bias line is an alternating current.

5. The superconducting integrated circuit of claim 4, wherein the alternating current has no DC component.

6. The superconducting integrated circuit of claim 1, further comprising: a second superconducting resonator communicatively coupled to the microwave transmission line; and a second signal interface that inductively communicatively couples the second superconducting resonator to the superconducting flux storage device, wherein the second signal interface is operable to provide a second flux bias to the superconducting flux storage device.

7. The superconducting integrated circuit of claim 6, wherein the first superconducting resonator extends along a first axis and the second superconducting resonator extends along a second axis, the second axis perpendicular to the first axis.

8. The superconducting integrated circuit of claim 6, wherein the superconducting flux storage device is XY-addressed by two microwave signals, a first one of the two microwave signals carried by the first superconducting resonator, and a second one of the two microwave signals carried by the second superconducting resonator, each of the first and the second superconducting resonator having a respective resonant frequency, the respective resonant frequencies of the first and the second superconducting resonators which in operation add constructively at the superconducting flux storage device.

9. The superconducting integrated circuit of claim 8, wherein the respective resonant frequencies of the first and the second superconducting resonators add constructively at the superconducting flux storage device to provide a beat signal, a frequency of the beat signal which is matched to a linewidth of at least one of the first and the second superconducting resonators.

10. The superconducting integrated circuit of claim 6, wherein the superconducting flux storage device comprises a superconducting digital-to-analog converter (DAC), the superconducting DAC which is operable to perform latching, and the superconducting DAC is programmed by a low-frequency bias signal carried by a low-frequency address bias line and by two microwave signals, which combine constructively to exceed a threshold address latching level, the low-frequency bias signal carried by the low-frequency address bias line which is at least reduced by a factor that depends on a difference between the first critical current of the first Josephson junction of the CJJ and the second critical current of the second Josephson junction of the CJJ.

11. The superconducting integrated circuit of claim 1, wherein a size of the second Josephson junction is different from a size of the first Josephson junction.

12. A method of loading a superconducting flux storage device with a magnetic flux quantum, the superconducting flux storage device comprising a superconducting flux storage loop interrupted by an asymmetric compound Josephson junction (CJJ), the asymmetric CJJ comprising: a first parallel current path interrupted by a first Josephson junction, the first Josephson junction characterized by a first critical current; and a second parallel current path interrupted by a second Josephson junction, the second parallel current path electrically in parallel with the first parallel current path, the second Josephson junction characterized by a second critical current, the second critical current of the second Josephson junction different than the first critical current of the first Josephson junction, the superconducting flux storage devices, the method comprising: applying a first high-frequency pulse to at least a first superconducting resonator by a microwave transmission line, the microwave transmission line communicatively coupled to the at least a first superconducting resonator; and applying the first high-frequency pulse to the superconducting flux storage device by the at least a first superconducting resonator, the at least a first superconducting resonator communicatively coupled to the superconducting flux storage device, to cause a flux quantum to be added to the asymmetric CJJ of the superconducting flux storage device.

13. The method of claim 12, further comprising: setting a current bias line to a first current bias value; setting a low-frequency address line to a first address line value; setting the current bias line to a second current bias line value to cause a current bias to be applied to the superconducting flux storage device; setting the low-frequency address line to a second address line value to cause a flux bias to be applied to the asymmetric CJJ of the superconducting flux storage device; after the applying a first high-frequency pulse to the superconducting flux storage device, setting the low-frequency address line to a third address line value to cause the flux quantum to be loaded into the superconducting flux storage loop of the superconducting flux storage device; returning the current bias line to the first current bias line value; and returning the low-frequency address line to the first address line value, wherein applying a first high-frequency pulse to the superconducting flux storage device by a microwave transmission line and a first superconducting resonator includes causing a combined low-frequency and high-frequency signal level applied to the superconducting flux storage device to exceed a predetermined upper threshold, and wherein at least one of the second current bias line value and the second address line value is at least reduced by a factor that depends on a difference between the first critical current of the first Josephson junction of the asymmetric CJJ and the second critical current of the second Josephson junction of the asymmetric CJJ.

14. The method of claim 13, wherein setting the low-frequency address line to a third address line value to cause the flux quantum to be loaded into the superconducting flux storage loop of the superconducting flux storage device includes setting the low-frequency address line to a third address line value to cause the flux quantum to be loaded into a superconducting digital-to-analog converter (DAC).

15. The method of claim 12, wherein applying a first high-frequency pulse to the superconducting flux storage device by a microwave transmission line and at least a first superconducting resonator includes applying a set of frequency-domain multiplex signals to each of the first superconducting resonator and at least a second superconducting resonator.

16. The method of claim 12, further comprising: applying the first high-frequency pulse to a second superconducting flux storage device by the microwave transmission line and the at least a first superconducting resonator.

17. The method of claim 12, wherein applying a first high-frequency pulse to the superconducting flux storage device by a microwave transmission line and at least a first superconducting resonator includes applying a first high-frequency pulse to a superconducting digital-to-analog converter (DAC) by the microwave transmission line and a first and at least a second superconducting resonator, the superconducting DAC operable to perform latching.

18. The method of claim 17, further comprising programming the superconducting DAC by a low-frequency bias signal carried by a first low-frequency address bias line and by two microwave signals, the low-frequency bias signal and the two microwave signals which combine constructively to exceed a threshold address latching level.

19. The method of claim 12, further comprising applying an alternating current on a current bias line.

20. The method of claim 19, wherein applying an alternating current on a current bias line includes applying an alternating current having no DC component.

21. A superconducting integrated circuit comprising: a superconducting flux storage device, the superconducting flux storage device which comprises a loop of material that is superconductive in a range of temperatures, the loop of material which is interrupted by at least one Josephson junction; and a first addressing line communicatively coupled to the superconducting flux storage device, wherein a current in the first addressing line is an alternating current.

22. The superconducting integrated circuit of claim 21, wherein the at least one Josephson junction is a compound Josephson junction (CJJ), the CJJ comprising: a first parallel current path which is interrupted by a first Josephson junction; and a second parallel current path which is interrupted by a second Josephson junction, the second parallel current path which is electrically in parallel with the first parallel current path.

23. The superconducting integrated circuit of claim 22, the first parallel current path which is further interrupted by a first inductance and the second parallel current path which is further interrupted by a second inductance, the superconducting integrated circuit further comprising: a second addressing line which is inductively coupled to the first inductance; and a third addressing line which is inductively coupled to the second inductance.

24. The superconducting integrated circuit of claim 23, the loop of material which includes a third inductance, the superconducting integrated circuit further comprising a device inductively communicatively coupled to the superconducting flux storage device by the third inductance.

Description

TECHNICAL FIELD

[0001] This disclosure generally relates to systems and methods for addressing devices in a superconducting circuit, and, more specifically, to systems and methods for resonator-addressing of superconducting flux storage devices and digital-to-analog converters (DAC) in superconducting integrated circuits.

BACKGROUND

[0002] Frequency Multiplexed Resonant (FMR) Readout

[0003] Superconducting microwave resonators can be used in a variety of fields including, but not limited to, quantum computation and astronomy. In quantum computation, superconducting resonators can be used to detect the state of qubits, for example the state of superconducting qubits in a superconducting quantum processor. In astronomy, superconducting microwave resonators can be used in Microwave Kinetic Inductance Detectors (MKIDs).

[0004] Multiple resonators (detectors) can be coupled to a common transmission line and integrated through frequency domain multiplexing. Frequency-domain multiplexing (FDM) is a technique in which a communication bandwidth is divided into a number of non-overlapping sub-bands, and each sub-band used to carry a separate signal. Frequency-domain multiplexing is also referred to in the present application as frequency multiplexing and frequency-division multiplexing.

[0005] Using FMR technology, superconducting resonators of different resonant frequencies can be used for readout of multiple qubits, for example. The resonators can share a common microwave transmission line by using frequency-domain multiplexing.

BRIEF SUMMARY

[0006] A superconducting integrated circuit may be summarized as comprising a microwave transmission line; a superconducting flux storage device comprising a loop of material that is superconductive below a critical temperature interrupted by an asymmetric compound Josephson junction (CJJ), the asymmetric CJJ comprising a first parallel current path interrupted by a first Josephson junction, the first Josephson junction characterized by a first critical current; and a second parallel current path interrupted by a second Josephson junction, the second parallel current path electrically in parallel with the first parallel current path, the second Josephson junction characterized by a second critical current, the second critical current of the second Josephson junction different from the first critical current of the first Josephson junction; a first superconducting resonator communicatively coupled to the microwave transmission line; and a first signal interface that inductively communicatively couples the first superconducting resonator to the superconducting flux storage device, wherein the first signal interface is operable to provide a first flux bias to the superconducting flux storage device.

[0007] The superconducting integrated circuit may further comprise a low-frequency address bias line; and an address interface that inductively communicatively couples the low-frequency bias address line to the superconducting flux storage device, wherein the address interface is operable to provide a second flux bias to the superconducting flux storage device. The superconducting flux storage device may comprise a superconducting digital-to-analog converter (DAC), the superconducting DAC which is operable to perform latching, and the superconducting DAC is programmed by a low-frequency bias signal carried by the low-frequency address bias line and by a microwave signal carried by the first superconducting resonator, which combine constructively to exceed a threshold address latching level, the low-frequency bias signal carried by the low-frequency address bias line which is at least reduced by a factor that depends on a difference between the first critical current of the first Josephson junction of the CJJ and the second critical current of the second Josephson junction of the CJJ.

[0008] The superconducting integrated circuit may further comprise a current bias line, wherein a current in the current bias line is an alternating current. The alternating current may have no DC component.

[0009] The superconducting integrated circuit may further comprise a second superconducting resonator communicatively coupled to the microwave transmission line; and a second signal interface that inductively communicatively couples the second superconducting resonator to the superconducting flux storage device, wherein the second signal interface is operable to provide a second flux bias to the superconducting flux storage device. The first superconducting resonator may extend along a first axis and the second superconducting resonator may extend along a second axis, the second axis perpendicular to the first axis. The superconducting flux storage device may be XY-addressed by two microwave signals, a first one of the two microwave signals carried by the first superconducting resonator, and a second one of the two microwave signals carried by the second superconducting resonator, each of the first and the second superconducting resonator having a respective resonant frequency, the respective resonant frequencies of the first and the second superconducting resonators which in operation add constructively at the superconducting flux storage device. The respective resonant frequencies of the first and the second superconducting resonators may add constructively at the superconducting flux storage device to provide a beat signal, a frequency of the beat signal which is matched to a linewidth of at least one of the first and the second superconducting resonators. The superconducting flux storage device may comprise a superconducting digital-to-analog converter (DAC), the superconducting DAC which is operable to perform latching, and the superconducting DAC may be programmed by a low-frequency bias signal carried by a low-frequency address bias line and by two microwave signals, which combine constructively to exceed a threshold address latching level, the low-frequency bias signal carried by the low-frequency address bias line which is at least reduced by a factor that depends on a difference between the first critical current of the first Josephson junction of the CJJ and the second critical current of the second Josephson junction of the CJJ.

[0010] A size of the second Josephson junction may be different from a size of the first Josephson junction.

[0011] A method of loading a superconducting flux storage device with a magnetic flux quantum, the superconducting flux storage device comprising a superconducting flux storage loop interrupted by an asymmetric compound Josephson junction (CJJ), the asymmetric CJJ comprising a first parallel current path interrupted by a first Josephson junction, the first Josephson junction characterized by a first critical current; and a second parallel current path interrupted by a second Josephson junction, the second parallel current path electrically in parallel with the first parallel current path, the second Josephson junction characterized by a second critical current, the second critical current of the second Josephson junction different than the first critical current of the first Josephson junction, the superconducting flux storage devices, may be summarized as comprising applying a first high-frequency pulse to at least a first superconducting resonator by a microwave transmission line, the microwave transmission line communicatively coupled to the at least a first superconducting resonator; and applying the first high-frequency pulse to the superconducting flux storage device by the at least a first superconducting resonator, the at least a first superconducting resonator communicatively coupled to the superconducting flux storage device to cause a flux quantum to be added to the asymmetric CJJ of the superconducting flux storage device.

[0012] The method may further comprise setting a current bias line to a first current bias value; setting a low-frequency address line to a first address line value; setting the current bias line to a second current bias line value to cause a current bias to be applied to the superconducting flux storage device; setting the low-frequency address line to a second address line value to cause a flux bias to be applied to the asymmetric CJJ of the superconducting flux storage device; after the applying a first high-frequency pulse to the superconducting flux storage device, setting the low-frequency address line to a third address line value to cause the flux quantum to be loaded into the superconducting flux storage loop of the superconducting flux storage device; returning the current bias line to the first current bias line value; and returning the low-frequency address line to the first address line value, wherein applying a first high-frequency pulse to the superconducting flux storage device by a microwave transmission line and a first superconducting resonator includes causing a combined low-frequency and high-frequency signal level applied to the superconducting flux storage device to exceed a predetermined upper threshold, and wherein at least one of the second current bias line value and the second address line value is at least reduced by a factor that depends on a difference between the first critical current of the first Josephson junction of the asymmetric CJJ and the second critical current of the second Josephson junction of the asymmetric CJJ. Setting the low-frequency address line to a third address line value to cause the flux quantum to be loaded into the superconducting flux storage loop of the superconducting flux storage device may include setting the low-frequency address line to a third address line value to cause the flux quantum to be loaded into a superconducting digital-to-analog converter (DAC).

[0013] Applying a first high-frequency pulse to the superconducting flux storage device by a microwave transmission line and at least a first superconducting resonator may include applying a set of frequency-domain multiplex signals to each of the first superconducting resonator and at least a second superconducting resonator.

[0014] The method may further comprise applying the first high-frequency pulse to a second superconducting flux storage device by the microwave transmission line and the at least a first superconducting resonator.

[0015] Applying a first high-frequency pulse to the superconducting flux storage device by a microwave transmission line and at least a first superconducting resonator may include applying a first high-frequency pulse to a superconducting digital-to-analog converter (DAC) by the microwave transmission line and a first and at least a second superconducting resonator, the superconducting DAC operable to perform latching. The method may further comprise programming the superconducting DAC by a low-frequency bias signal carried by a first low-frequency address bias line and by two microwave signals, the low-frequency bias signal and the two microwave signals which combine constructively to exceed a threshold address latching level.

[0016] The method may further comprise applying an alternating current on a current bias line. Applying an alternating current on a current bias line may include applying an alternating current having no DC component.

[0017] A superconducting integrated circuit may be summarized as comprising a superconducting flux storage device, the superconducting flux storage device which comprises a loop of material that is superconductive in a range of temperatures, the loop of material which is interrupted by at least one Josephson junction; and a first addressing line communicatively coupled to the superconducting flux storage device, wherein a current in the first addressing line is an alternating current. The at least one Josephson junction may be a compound Josephson junction (CJJ), the CJJ comprising a first parallel current path which is interrupted by a first Josephson junction; and a second parallel current path which is interrupted by a second Josephson junction, the second parallel current path which is electrically in parallel with the first parallel current path. Where the first parallel current path is further interrupted by a first inductance and the second parallel current path is further interrupted by a second inductance, the superconducting integrated circuit may further comprise a second addressing line which is inductively coupled to the first inductance; and a third addressing line which is inductively coupled to the second inductance. Where the loop of material includes a third inductance, the superconducting integrated circuit may further comprise a device inductively communicatively coupled to the superconducting flux storage device by the third inductance.

BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWINGS

[0018] In the drawings, identical reference numbers identify similar elements or acts. The sizes and relative positions of elements in the drawings are not necessarily drawn to scale. For example, the shapes of various elements and angles are not necessarily drawn to scale, and some of these elements are arbitrarily enlarged and positioned to improve drawing legibility. Further, the particular shapes of the elements as drawn, are not necessarily intended to convey any information regarding the actual shape of the particular elements, and have been solely selected for ease of recognition in the drawings.

[0019] FIG. 1 is a schematic diagram illustrating an example implementation of a microwave path to a superconducting circuit, according to the present disclosure.

[0020] FIG. 2 is a schematic diagram illustrating another example implementation of a microwave path to a superconducting circuit, according to the present disclosure.

[0021] FIG. 3A is a schematic layout of a portion of an example implementation of a superconducting circuit that includes a superconducting half-wave resonator and a transmission line, according to the present disclosure.

[0022] FIG. 3B is an enlarged view of a coupling region of the superconducting half-wave resonator of FIG. 3A.

[0023] FIG. 4A is a schematic layout of a portion of an example implementation of a superconducting circuit that includes a superconducting lumped-element resonator and a transmission line, according to the present disclosure.

[0024] FIG. 4B is an enlarged view of a coupling region of the superconducting lumped-element resonator of FIG. 4A.

[0025] FIG. 4C is a cross-section of a portion of an example implementation of a superconducting circuit that includes a superconducting lumped-element resonator and a transmission line, according to the present disclosure.

[0026] FIG. 5A is a schematic diagram illustrating an example implementation of a superconducting circuit that includes a resonator-addressed digital-to-analog converter (DAC), according to the present disclosure.

[0027] FIG. 5B is a schematic diagram illustrating another example implementation of a superconducting circuit that includes a resonator-addressed digital-to-analog converter (DAC), according to the present disclosure.

[0028] FIG. 5C is a schematic diagram illustrating an example implementation of a superconducting circuit that includes a pair of resonator-addressed digital-to-analog converters (DACs), according to the present disclosure.

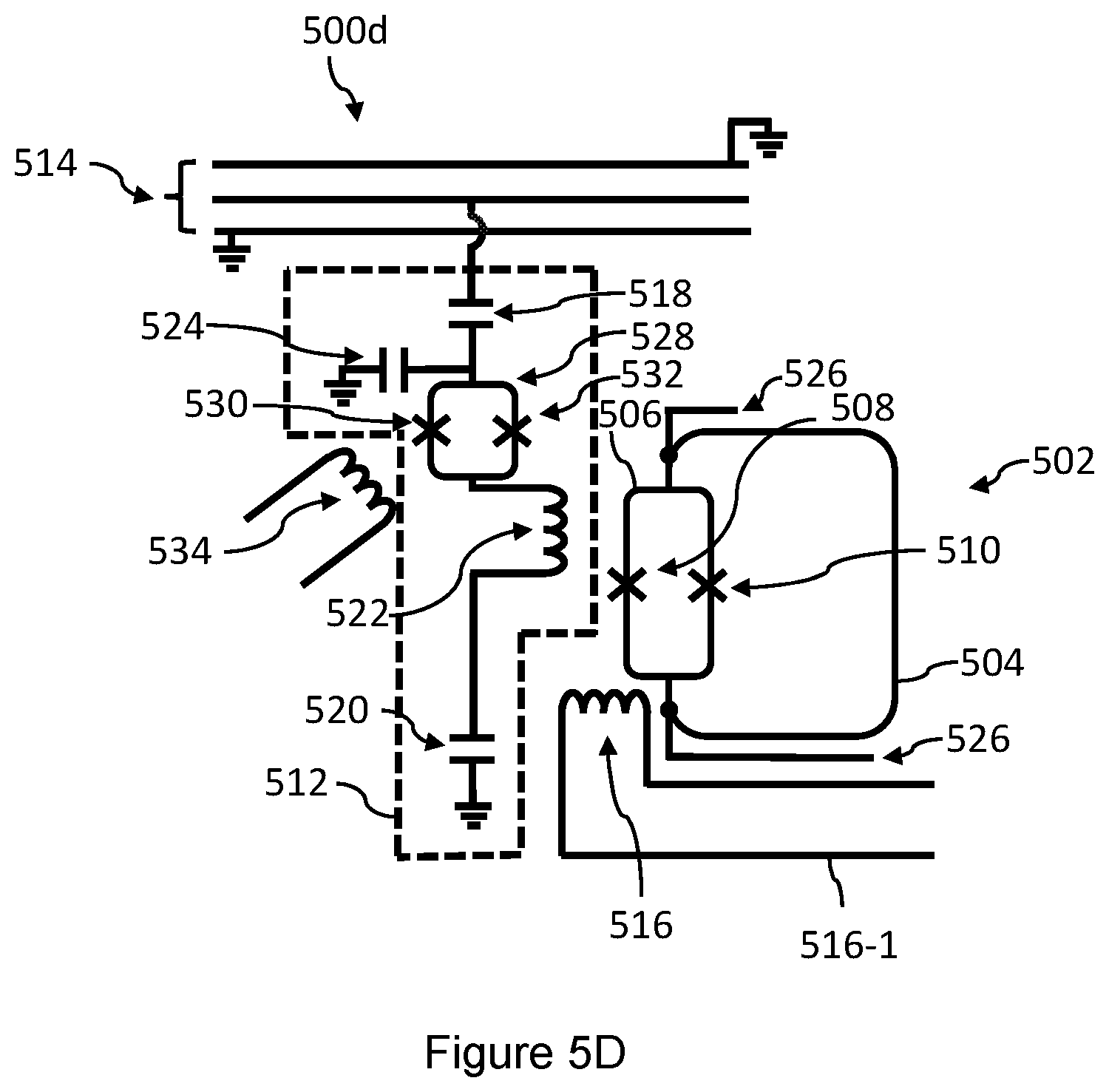

[0029] FIG. 5D is a schematic diagram illustrating another example implementation of a superconducting circuit that includes a resonator-addressed digital-to-analog converter (DAC), according to the present disclosure.

[0030] FIG. 5E is a schematic diagram illustrating an example implementation of a superconducting circuit that includes a resonator-addressed digital-to-analog converter (DAC), and a resonator that is inductively coupled to a transmission line, according to the present disclosure.

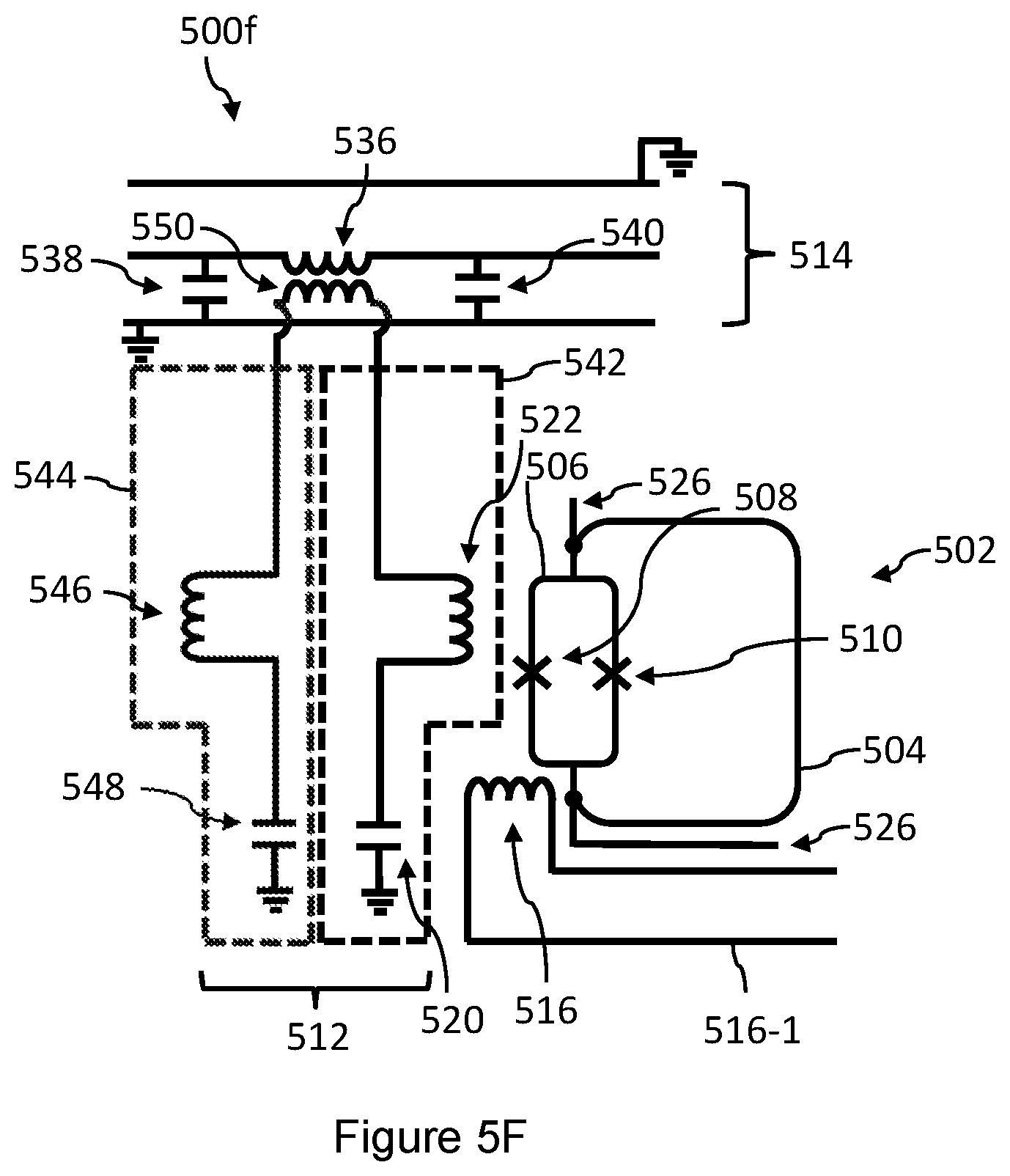

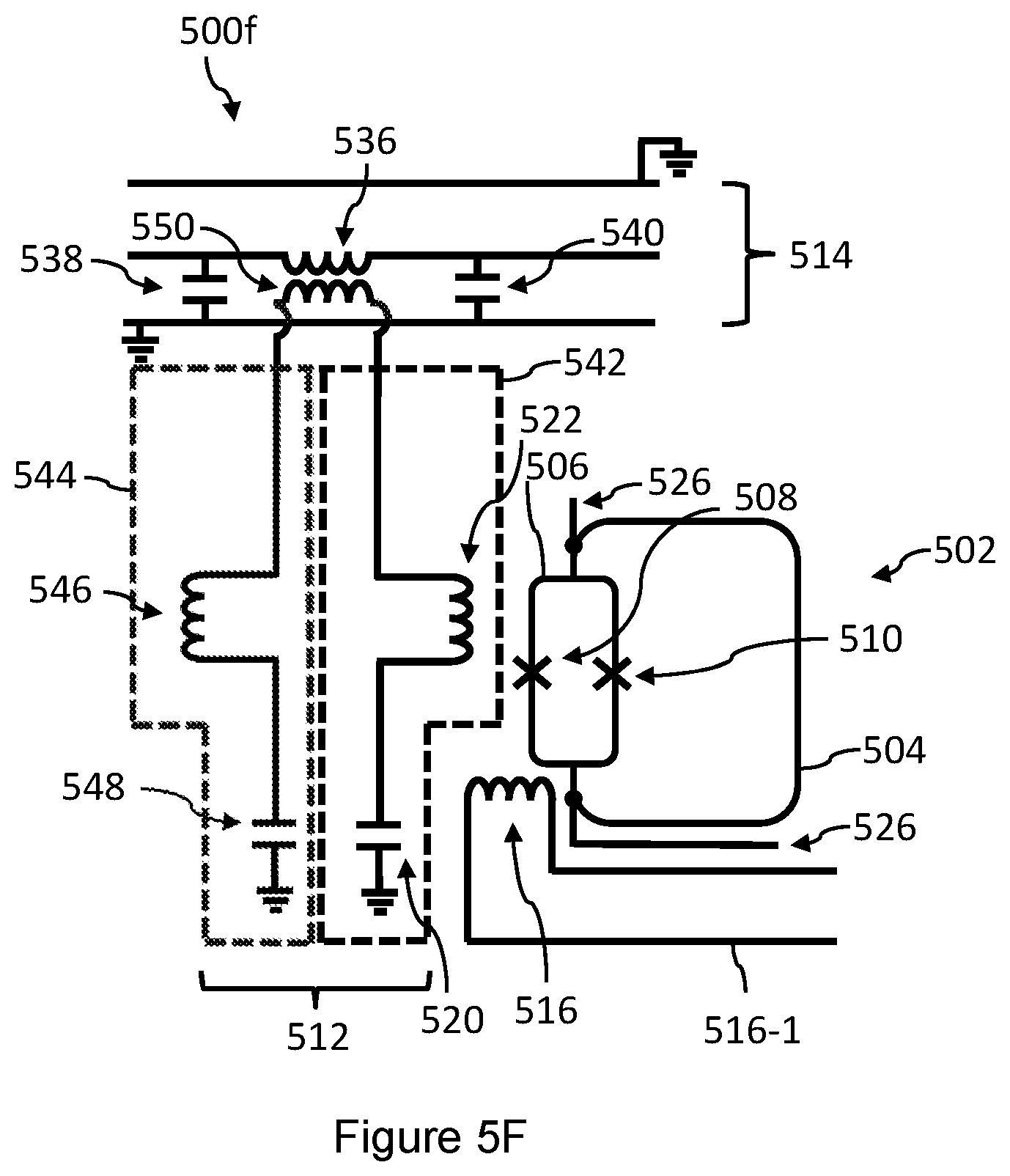

[0031] FIG. 5F is a schematic diagram illustrating another example implementation of a superconducting circuit that includes a resonator-addressed digital-to-analog converter (DAC), and a resonator that is inductively coupled to a transmission line, according to the present disclosure.

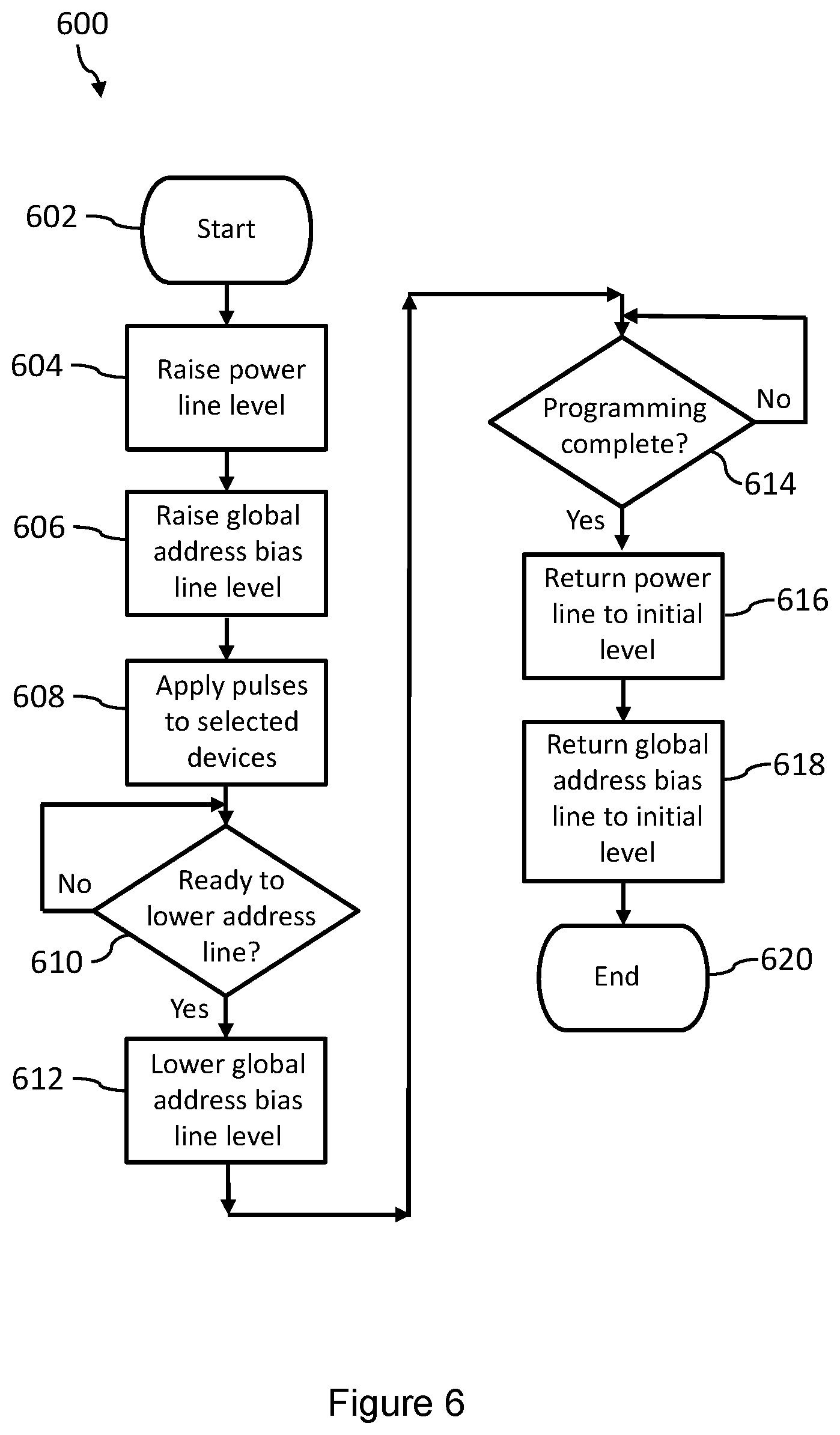

[0032] FIG. 6 is a flow chart illustrating an example method for programming a superconducting DAC, according to the present disclosure.

[0033] FIGS. 7A, 7B and 7C are schematic plots illustrating an example time series for loading of a single flux quantum, according to the present disclosure, and in particular FIG. 7A is a graph showing a plot of an address signal current as a function of time; FIG. 7B is a graph showing a plot of a power signal current as a function of time; and FIG. 7C is a graph showing a plot of a persistent current in a compound Josephson junction (CJJ) loop of the superconducting DAC as a function of time.

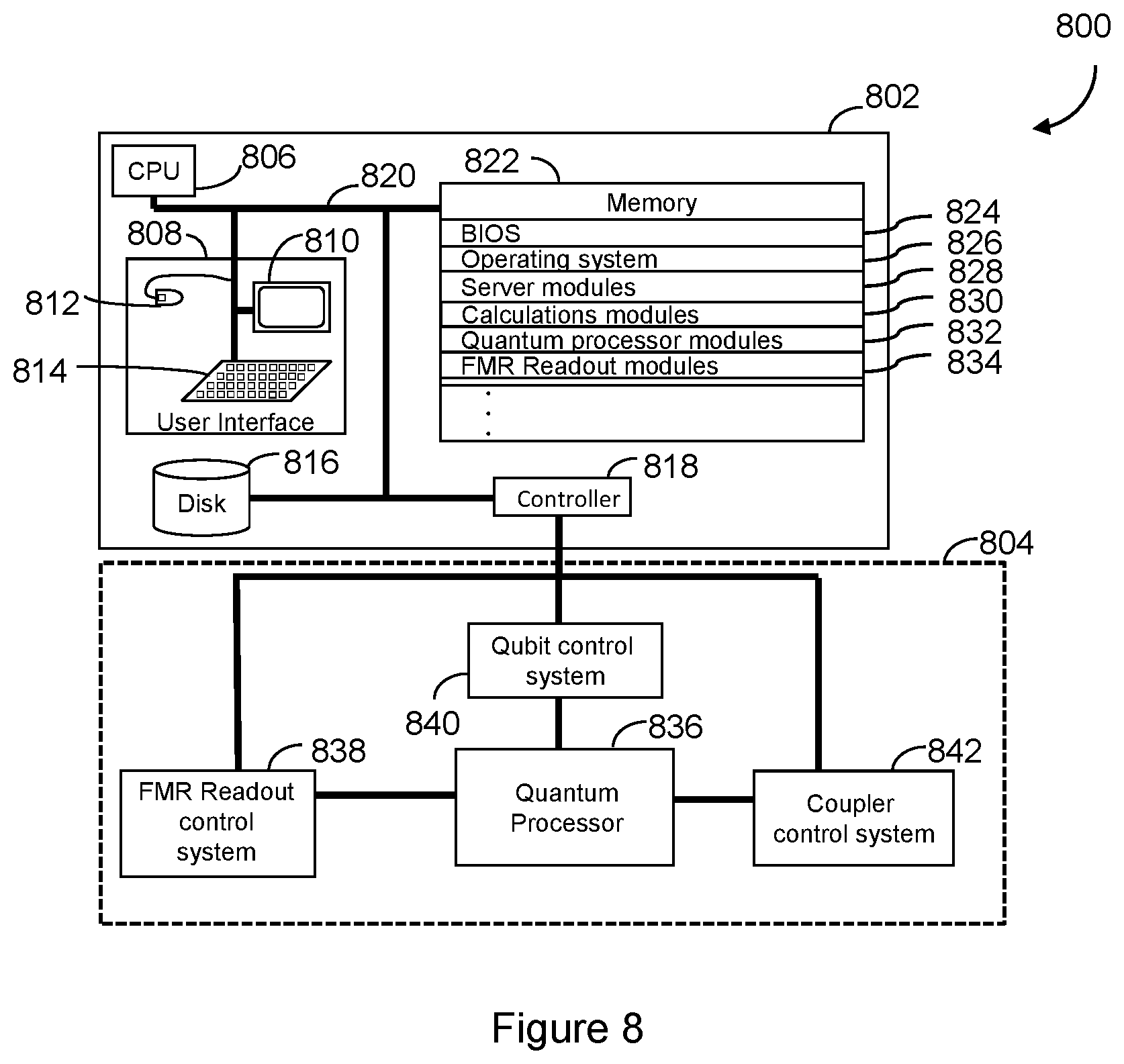

[0034] FIG. 8 is a schematic diagram of an exemplary computing system including a digital computer and an analog computer, in accordance with the present disclosure.

[0035] FIG. 9A is a schematic diagram illustrating an example implementation of a superconducting circuit, according to the present disclosure.

[0036] FIG. 9B is a schematic diagram illustrating another example implementation of a superconducting circuit, according to the present disclosure.

[0037] FIG. 9C is a schematic diagram illustrating an example implementation of a superconducting circuit with asymmetric Josephson junctions in a compound Josephson junction of a superconducting flux storage device, according to the present disclosure.

[0038] FIG. 10 is a schematic diagram illustrating an example implementation of a superconducting circuit that includes an array of resonators, according to the present disclosure.

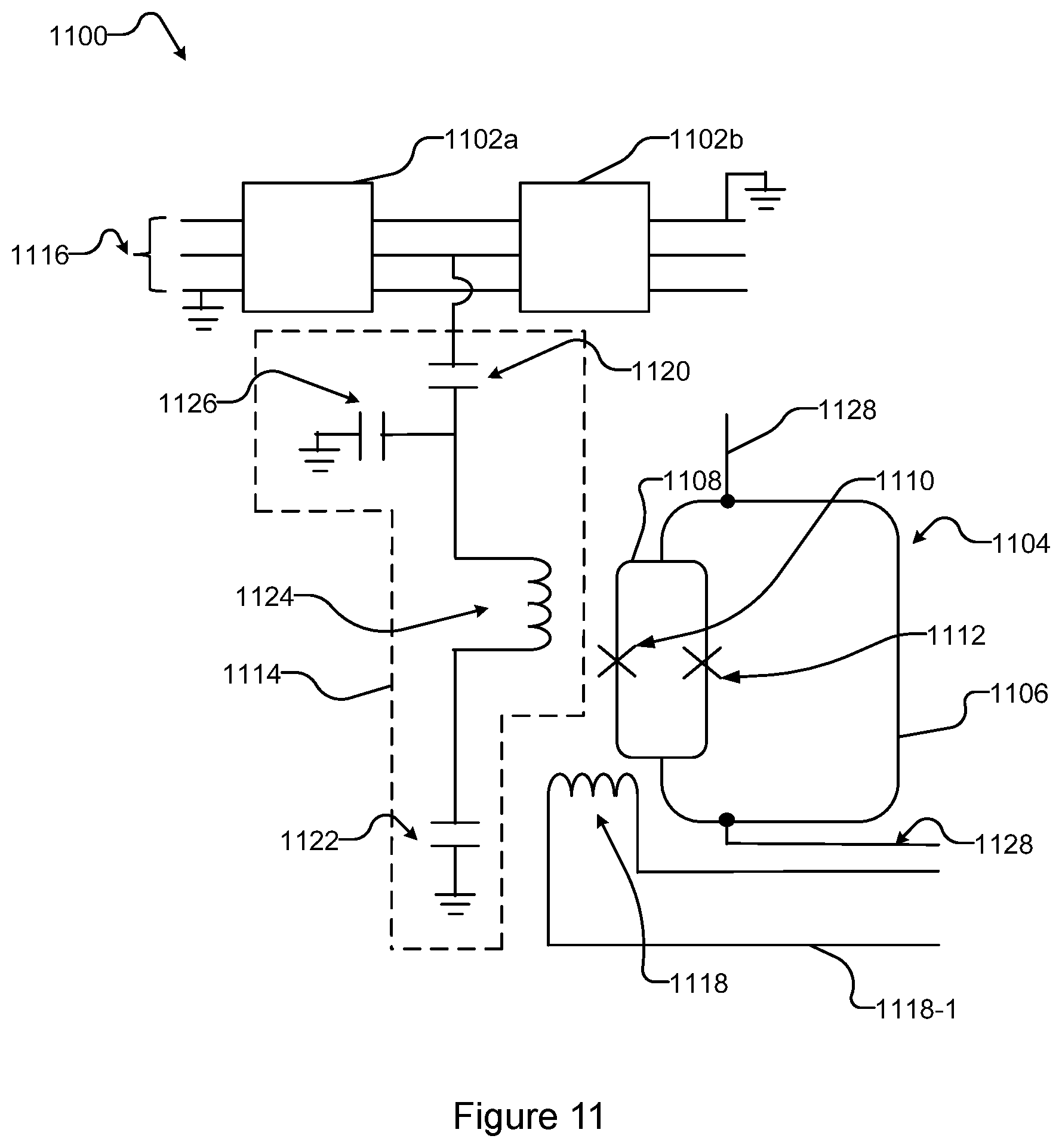

[0039] FIG. 11 is a schematic diagram illustrating an example implementation of a superconducting circuit that includes a switch, according to the present disclosure.

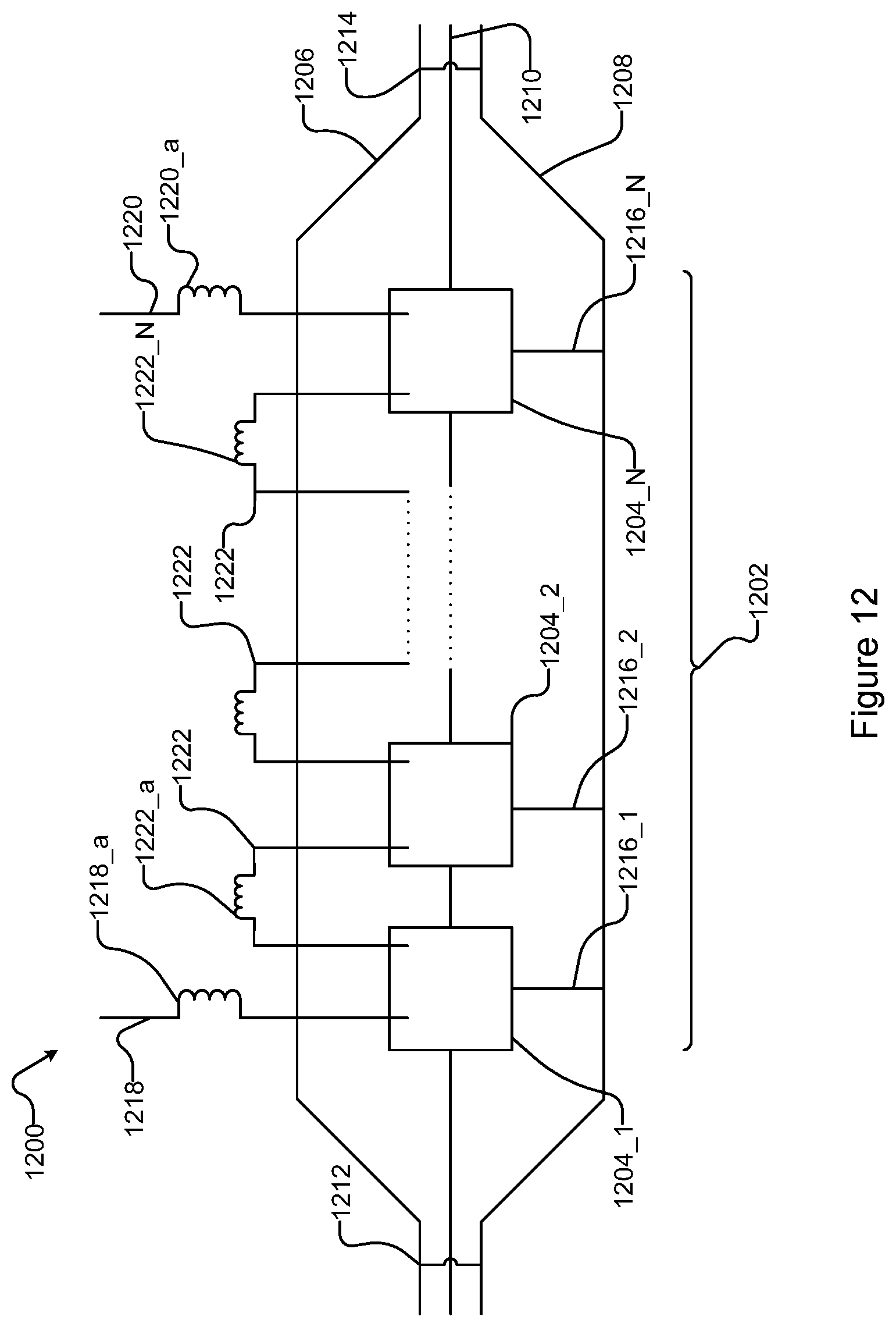

[0040] FIG. 12 is a schematic diagram of an example implementation of a transmission line layout with N cascade elements, according to the present disclosure.

[0041] FIG. 13 is a schematic diagram of an example implementation of a single cascade element, according to the present disclosure.

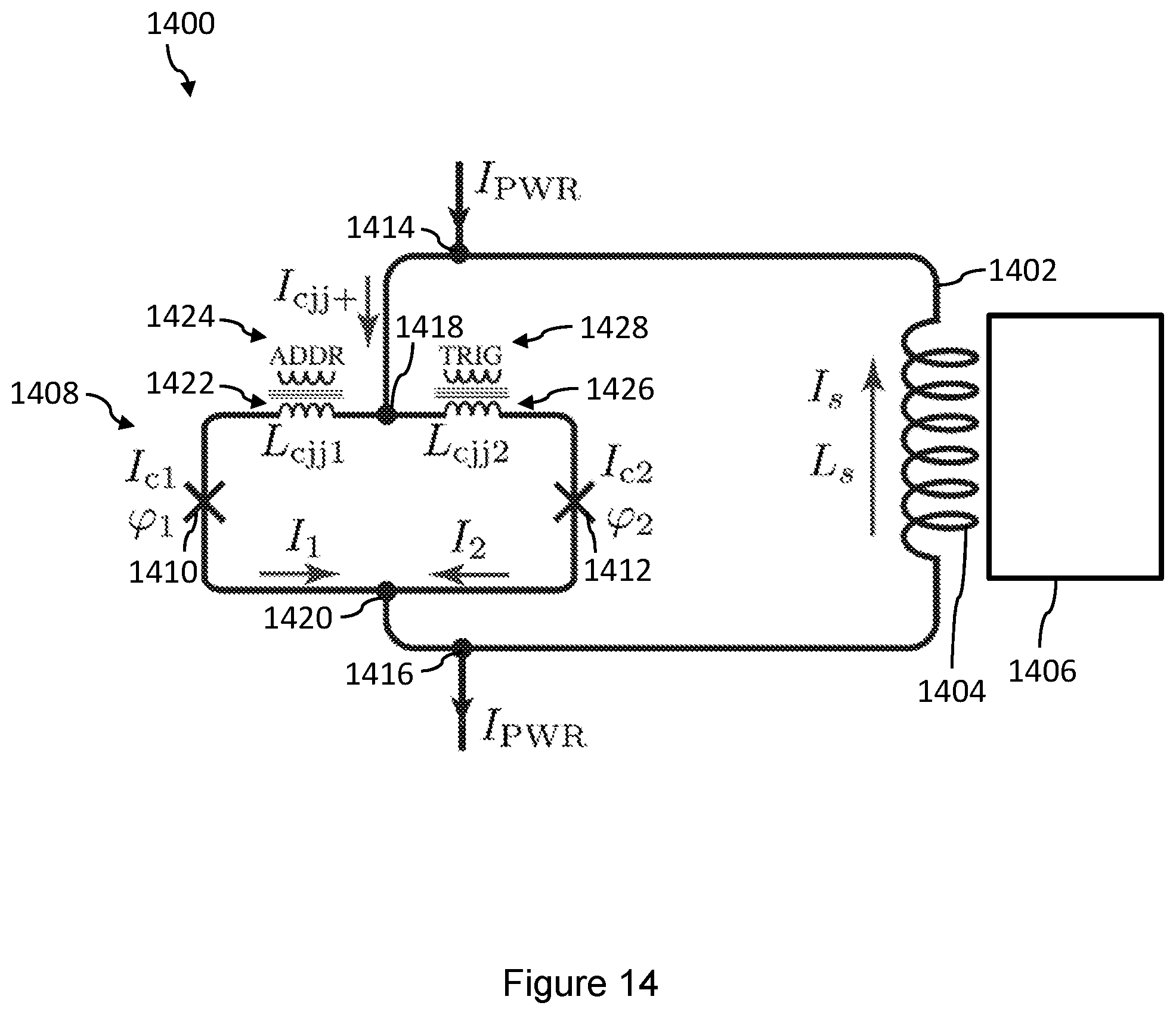

[0042] FIG. 14 is a schematic diagram of a superconducting DAC, according to the present disclosure.

DETAILED DESCRIPTION

Preamble

[0043] In the following description, some specific details are included to provide a thorough understanding of various disclosed implementations and embodiments. One skilled in the relevant art, however, will recognize that embodiments may be practiced without one or more of these specific details, or with other methods, components, materials, etc. In other instances, well-known structures associated with superconductive devices and integrated superconductive circuits have not been shown or described in detail to avoid unnecessarily obscuring descriptions of the implementations or embodiments of the present methods. Throughout this specification and the appended claims, the words "element" and "elements" are used to encompass, but are not limited to, all such structures, systems, and devices associated with superconductive circuits and integrated superconductive circuits.

[0044] Unless the context requires otherwise, throughout the specification and claims which follow, the word "comprise" is synonymous with "including," and is inclusive or open-ended (i.e., does not exclude additional, unrecited elements or acts).

[0045] Reference throughout this specification to "one embodiment" "an embodiment", "another embodiment", "one example", "an example", "another example", "one implementation", "another implementation", or the like means that a particular referent feature, structure, or characteristic described in connection with the embodiment, example, or implementation is included in at least one embodiment, example, or implementation. Thus, the appearances of the phrases "in one embodiment", "in an embodiment", "another embodiment" or the like in various places throughout this specification are not necessarily all referring to the same embodiment, example, or implementation. Furthermore, the particular features, structures, or characteristics may be combined in any suitable manner in one or more embodiments, examples, or implementations.

[0046] It should be noted that, as used in this specification and the appended claims, the singular forms "a," "an," and "the" include plural referents unless the content clearly dictates otherwise. Thus, for example, reference to a readout system including "a superconducting resonator" includes a single superconducting resonator, or two or more superconducting resonators. It should also be noted that the term "or" is generally employed in its sense including "and/or" unless the content clearly dictates otherwise.

[0047] The headings provided herein are for convenience only and do not interpret the scope or meaning of the embodiments.

Superconducting Flux Storage Devices

[0048] Superconducting flux storage devices are also referred to in the present application as superconducting digital-to-analog converters (DACs) and flux DACs.

[0049] While a single qubit, or a handful of them, can be precisely controlled using dedicated analog lines driven by room-temperature electronics, integrating more than a few dozen qubits on a single chip can preferably be implemented using on-chip control circuitry. In one implementation of a quantum processor that includes superconducting qubits and couplers, there can be six control parameters per qubit, and one control parameter per coupler. Static flux biases can be selectively applied to superconducting loops in order to realize at least some of the control parameters. The desired values of flux biases can be programmed into control devices using a relatively small number of control lines that carry signals generated at room temperature.

[0050] In some implementations, control devices can combine the functions of persistent memory and digital-to-analog conversion, and are referred to in the present application as flux DACs. In an example implementation, each flux DAC has a size of about 10 .mu.m. Having several of them attached to a single qubit can set a lower bound on qubit size, and can influence possible qubit shapes, hardware graph topologies, and processor architecture.

[0051] XYZ-Addressing of Flux DACs In an example implementation of a quantum processor, 512 qubits and associated coupling devices can be controlled by 4608 flux DACs. An XYZ-addressing approach can control the quantum processor using only 56 lines. The processor can be arranged as an 8.times.8 array of tiles, each tile having 72 flux DACs. The flux DACs of each tile can be arranged in a respective 3-DAC plaquette. One of each set of three DACs in a 3-DAC plaquette can be selected using one of three lines (referred to in the present application as address (ADDR) lines), all three sharing another line (referred to in the present application as a trigger (TRIG) line), in an arrangement that uses 15 ADDR lines and 5 TRIG lines to address DACs in the tile. The 8.times.8 array of tiles can be divided into 16 domains (referred to in the present application as power (PWR) domains), and arranged such that 4608 flux DACs can be addressed using 30 ADDR lines, 10 TRIG lines, and 16 PWR lines in total. See for example Bunyk P. et al., "ARCHITECTURAL CONSIDERATIONS IN THE DESIGN OF A SUPERCONDUCTING QUANTUM ANNEALING PROCESSOR", arXiv:1401.5504v1, 21 Jan. 2014.

[0052] A shortcoming of the DAC addressing scheme described above can be that implementation can include a large number of wires and superconducting low-pass filters which can be costly to produce, vulnerable to failure, and a source of high-energy photons from internal filter heating. In some implementations, the wires are twisted-pairs and the low-pass filters are custom-made superconducting low-pass filters. The systems and methods described in the present application include replacing wires by coaxial cable which can provide greater bandwidth and reduced complexity. A benefit of greater bandwidth can be improved processor input/output (I/O) speed.

Superconducting Resonators

[0053] When high-bandwidth lines are available for communicating with the processor, more efficient use of the bandwidth can be made by coupling the high-bandwidth line to a suitable on-chip element. An example on-chip element suitable for coupling to a high-bandwidth transmission line is a superconducting resonator. An advantage of using a superconducting resonator is that, similar to FMR readout or microwave kinetic-inductance detectors (MKIDs), these devices can be compatible with frequency-domain multiplexing. An array of resonators can be coupled to a single transmission line using frequency-domain multiplexing by tuning a resonant frequency of each resonator. The resonant frequency can be tuned, for example, by adjusting a length of the resonator, and/or by adding additional capacitance. In one implementation, the resonator is a half-wave superconducting resonator. Microwave current can be excited when the resonator is driven near its resonant frequency. Addressing can be achieved by selectively transmitting a set of tones corresponding to a set of resonators in the array of resonators.

Distributed Superconducting Resonators

[0054] One implementation of a superconducting resonator is a distributed superconducting resonator. An example of a distributed superconducting resonator is half-wavelength (.lamda./2) resonator. A half-wavelength resonator can generally provide sufficient usable wiring length for coupling to another device. A shortcoming of a half-wavelength resonator can be that the presence of harmonics at integer multiples of the fundamental resonant frequency can constrain an array of superconducting resonators to one octave of bandwidth.

[0055] An additional shortcoming can be that the current distribution can vary sinusoidally along the wiring length, with a peak value occurring at the center of the device. One approach to mitigating the variation in current is to use only a section of the length of the resonator, for example a section in which the variation in current remains within, say, 90% of the peak value. Another approach is to vary the strength of coupling of the resonator to devices coupled along the length of the resonator. Yet another approach is to adjust the driving amplitudes of intersecting resonators to compensate for the resonator current distribution. The latter approach can be used in the XY-addressing scheme described below, for example. In some implementations, resonators are operated individually. In some implementations, resonators are operated in groups of resonators.

[0056] Another example of a distributed superconducting resonator is a quarter-wavelength (.lamda./4) resonator. The peak current for a quarter-wavelength resonator is at one end of the resonator. Variation in current along the body of the resonator can be mitigated by using only a section of the length of the resonator, specifically a section at or near the end where the current is within, say 90% of the peak value.

Lumped-Element Resonators

[0057] Another implementation of a superconducting resonator is a lumped-element resonator. An advantage of a lumped-element resonator is that the current distribution can be substantially uniform along an inductive portion of the lumped-element resonator. Furthermore, a lumped-element resonator can be compact and, in at least some implementations, is not constrained to one octave of bandwidth. In an example implementation, a lumped element resonator can operate from 5 GHz to 15 GHz, and yield 10 GHz of bandwidth.

[0058] There are several constraints that can influence achievable electronic bandwidth utilization of a resonator-multiplexed programming system (also referred to in the present application as system bandwidth). The same or similar constraints can also influence the system bandwidth of implementations of superconducting resonators other than lumped-element resonators.

[0059] Firstly, system bandwidth can be constrained by cross-talk. The effective system bandwidth can be limited by as much as 30% in some implementations where resonances are spaced apart from each other to reduce cross-talk. The spacing between resonances can be several linewidths. In an example implementation, the system bandwidth is 4-8 GHz, and the per-resonator bandwidth is approximately 30 MHz centered on a resonant frequency within the system bandwidth.

[0060] Secondly, variations in fabrication, such as variations in layer thickness, can shift a resonant frequency by as much as 10% in some implementations.

[0061] Thirdly, layout of resonators and associated wiring can cause resonator-to-resonator frequency shifts. In some implementations, resonator bodies are routed in a single wiring layer to reduce resonator-to-resonator frequency shifts. In some implementations, where vias are used, an array of resonators can use the same number of vias with approximately the same distribution along the resonator length for every resonator in the array, to avoid or at least reduce differential changes in resonator lengths, resonator-to-resonator frequency shifts, and contaminant electronic cross-talk.

[0062] Fourthly, a higher-frequency resonator can be shorter than a lower-frequency resonator, and, in some instances, can become too short to span a width of a processor in which an array of resonators is used for DAC addressing. The constraint can be mitigated in some implementations by using a thin dielectric layer in the fabrication of parallel-plate capacitors in the resonators to reduce the footprint of the capacitors. See for example U.S. Provisional Patent Application Ser. No. 62/660,719, "SYSTEMS AND METHODS FOR FABRICATION OF SUPERCONDUCTING DEVICES", filed Apr. 20, 2018, and U.S. patent application Ser. No. 16/389,669, "SYSTEMS AND METHODS FOR FABRICATION OF SUPERCONDUCTING DEVICES".

[0063] A superconducting integrated circuit may include a substrate; a base electrode overlying at least a portion of the substrate, the base electrode superconductive in a range of temperatures; a parallel-plate capacitor overlying at least a portion of the base electrode, the parallel-plate capacitor comprising: a first capacitor plate that is superconductive in a range of temperatures; a metal-oxide layer overlying the first capacitor plate; a second capacitor plate overlying the metal-oxide layer, the second capacitor plate superconductive in a range of temperatures, wherein the base electrode is superconductingly electrically coupled to the first capacitor plate.

[0064] A method of fabricating a parallel-plate capacitor in a superconducting integrated circuit may include forming a metal-oxide layer to overlie at least a portion of a first capacitor plate, the first capacitor plate comprising a material that is superconductive in a range of temperatures; depositing a second capacitor plate to overlie at least a portion of the metal-oxide layer, the second capacitor plate comprising a material that is superconductive in a range of temperatures; depositing a base electrode to overlie at least a portion of a substrate, the base electrode comprising a material that is superconductive in a range of temperatures; depositing the first capacitor plate to overlie at least a portion of the base electrode, the first capacitor plate superconductingly electrically coupled to the base electrode; and depositing a counter electrode to overlie at least a portion of the second capacitor plate, the counter electrode comprising a material that is superconductive in a range of temperatures, wherein the counter electrode is superconductingly electrically coupled to the second capacitor plate.

[0065] In some implementations, a kinetic-inductance transmission line is used to route microwave signals with high isolation within the processor fabric using three layers or less. See, for example, PCT Patent Application No. WO2018US016237, SYSTEMS AND METHODS FOR FABRICATION OF SUPERCONDUCTING INTEGRATED CIRCUITS, filed Jan. 31, 2018. On-chip transmission lines are ideally designed to be fully enclosed (except at the point of coupling) and 50 ohm matched. Impedance matching ensures that minimal, or at least reduced, signal distortion occurs. Enclosing the transmission line ensures minimal, or at least reduced, coupling to box modes or on-chip structures. Additionally, the shield enclosing the transmission line can at least partially isolate an on-chip device (for example, a qubit) from high-frequency noise propagating on the line.

[0066] There can be challenges in implementing a 50 ohm transmission line in a 3-layer (or higher) superconducting integrated circuit. For example, there can be an undesirably large capacitance between the center line and the ground in a fabrication stack, in particular where the dielectric thickness is low and the wire width is too large. A higher capacitance can result in a lower characteristic impedance.

[0067] Some implementations include a transmission line with a center conductor having a large kinetic inductance. For example, the center conductor of the transmission line can include titanium nitride (TiN). A higher inductance of the center line can compensate for a higher capacitance between the center line and ground. This approach can be used to form a fully-enclosed, 50 ohm transmission line in as few as three metal layers in the fabrication stack.

[0068] A method for fabricating a superconducting integrated circuit may include depositing a first superconducting metal layer to overlie at least a portion of a substrate; depositing a first dielectric layer to overlie at least a portion of the first superconducting metal layer; and depositing a kinetic inductance layer to overlie at least a portion of the first dielectric layer, wherein the kinetic inductance layer forms a center conductor for an on-chip transmission line. The method may further include depositing a passivation layer to overlie at least a portion of the kinetic inductance layer. In some implementations, the method further includes depositing a second superconducting metal layer to overlie at least a portion of the passivation layer; depositing a second dielectric layer to overlie at least a portion of the second superconducting metal layer; and depositing a third superconducting metal layer to overlie at least a portion of the second dielectric layer, wherein the first and the third superconducting metal layers form an outer conductor of the on-chip transmission line. In some implementations, the method further includes depositing a second dielectric layer to overlie at least a portion of the passivation layer; and depositing a second superconducting metal layer to overlie at least a portion of the second dielectric layer, wherein the first and the second superconducting metal layers form an outer conductor of the on-chip transmission line.

High-Bandwidth Lines

[0069] FIG. 1 is a schematic diagram illustrating an example implementation of a microwave path 100 to a superconducting circuit, according to the present disclosure. Microwave path 100 is positioned in a cryogenic refrigeration system. The cryogenic refrigeration system includes a still 102, a sample holder 104, and mixing chamber 106. Microwave path 100 travels between still 102 and sample holder 104. Microwave path 100 is a microwave path through the cryogenic refrigeration system. Still 102, sample holder 104, and mixing chamber 106 are shown as dashed lines in FIG. 1 to provide context for microwave path 100.

[0070] Sample holder 104 can contain or hold the superconducting circuit. In some implementations, the superconducting circuit is an integrated superconducting circuit. In some implementations, the integrated superconducting circuit includes a quantum processor. In some implementations, the quantum processor includes a plurality of superconducting flux qubits. See, for example, PCT Patent Application No. PCT/US2009/055939 (published as International patent application publication WO 2010/028183A2), SYSTEMS, METHODS AND APPARATUS FOR ACTIVE COMPENSATION OF QUANTUM PROCESSOR ELEMENTS, filed Sep. 3, 2009.

[0071] Microwave path 100 traverses mixing chamber 106. Microwave path 100 includes a superconducting coaxial cable 108 between still 102 and mixing chamber 106. In some implementations, superconducting cable 108 is superconducting NbTi (niobium titanium) coaxial cable.

[0072] Microwave path 100 includes a bandpass filter 110, a powder filter 112, and a switch 114 for the operating band. In some implementations, powder filter 112 is a superconducting powder filter. Bandpass filter 110 is communicatively coupled to powder filter 112 by a coaxial cable 116. In some implementations, bandpass filter 110 is a GHz bandpass filter with greater than 90 dB out-of-band suppression of frequencies below 60 GHz. Bandpass filter 110 and powder filter 112 in combination can determine at least in part the filtering of signals on microwave path 100. The use of one or both of bandpass filter 110 and powder filter 112 can be optional in some implementations. One reason for including filters is to reduce noise on high-bandwidth lines used for programming devices such as devices in a quantum processor.

[0073] In some implementations operating at a temperature of approximately 4 K (Kelvin), switch 114 is a CMOS (Complementary Metal-Oxide-Semiconductor) switch. In other implementations operating at a temperature of approximately 4 K, switch 114 is a superconducting switch, e.g., a cryotron. In some implementations operating at a temperature of approximately 10 mK, switch 114 is a superconducting switch, e.g., a cryotron. In yet other implementations, switch 114 is a broadband switch as described in the present application with reference to FIGS. 11, 12, and 13. The broadband switch of FIGS. 11, 12, and 13 is further described in U.S. patent application Ser. No. 16/397,790, DYNAMICAL ISOLATION OF A CRYOGENIC PROCESSOR, filed Apr. 29, 2019.

[0074] In some implementations, coaxial cable 116 is a copper coaxial cable. Powder filter 112 is communicatively coupled to switch 114 by coaxial cable 118. In some implementations, coaxial cable 118 is a copper coaxial cable. Switch 114 is communicatively coupled to sample holder 104 by coaxial cable 120. In some implementations, coaxial cable 120 is a copper coaxial cable.

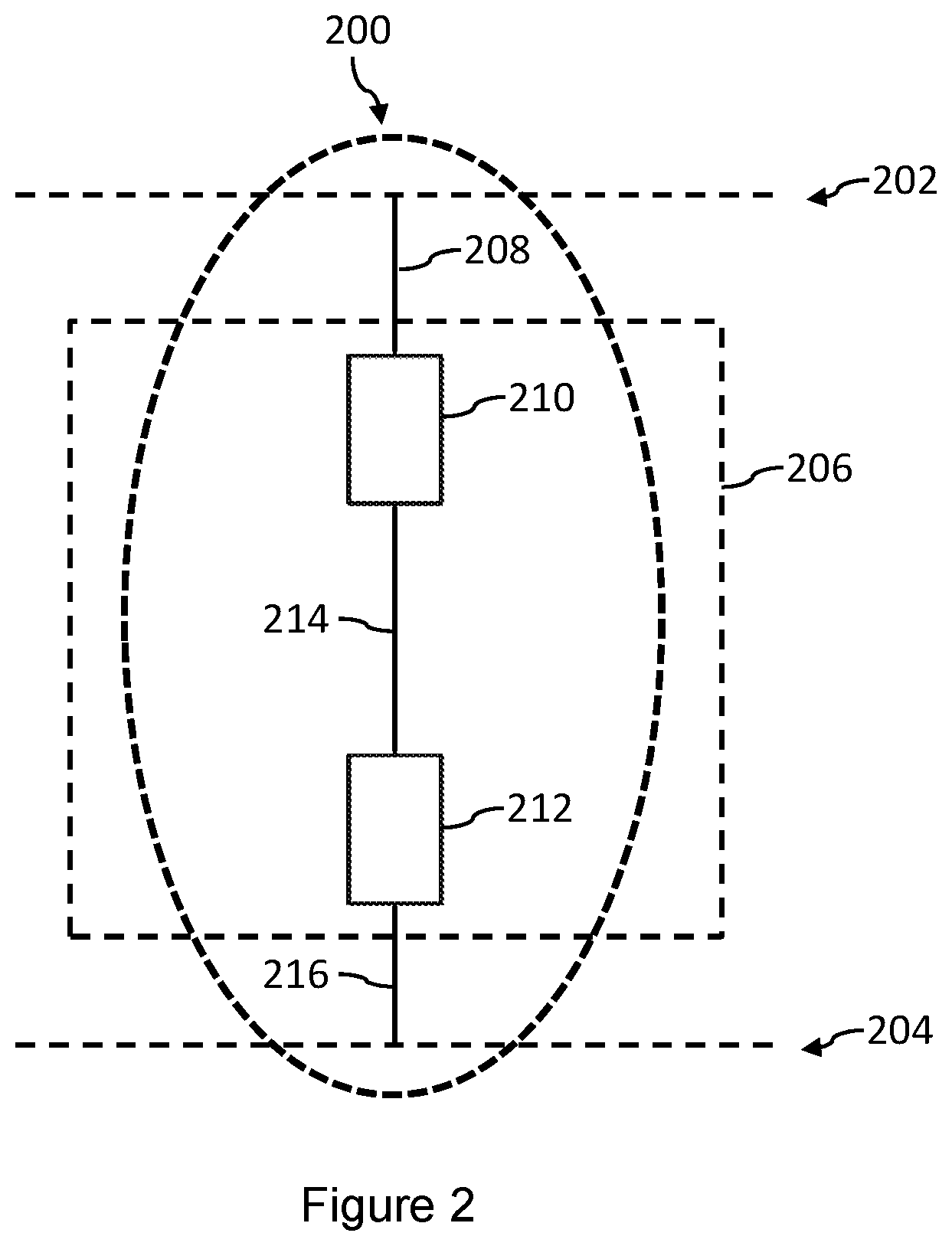

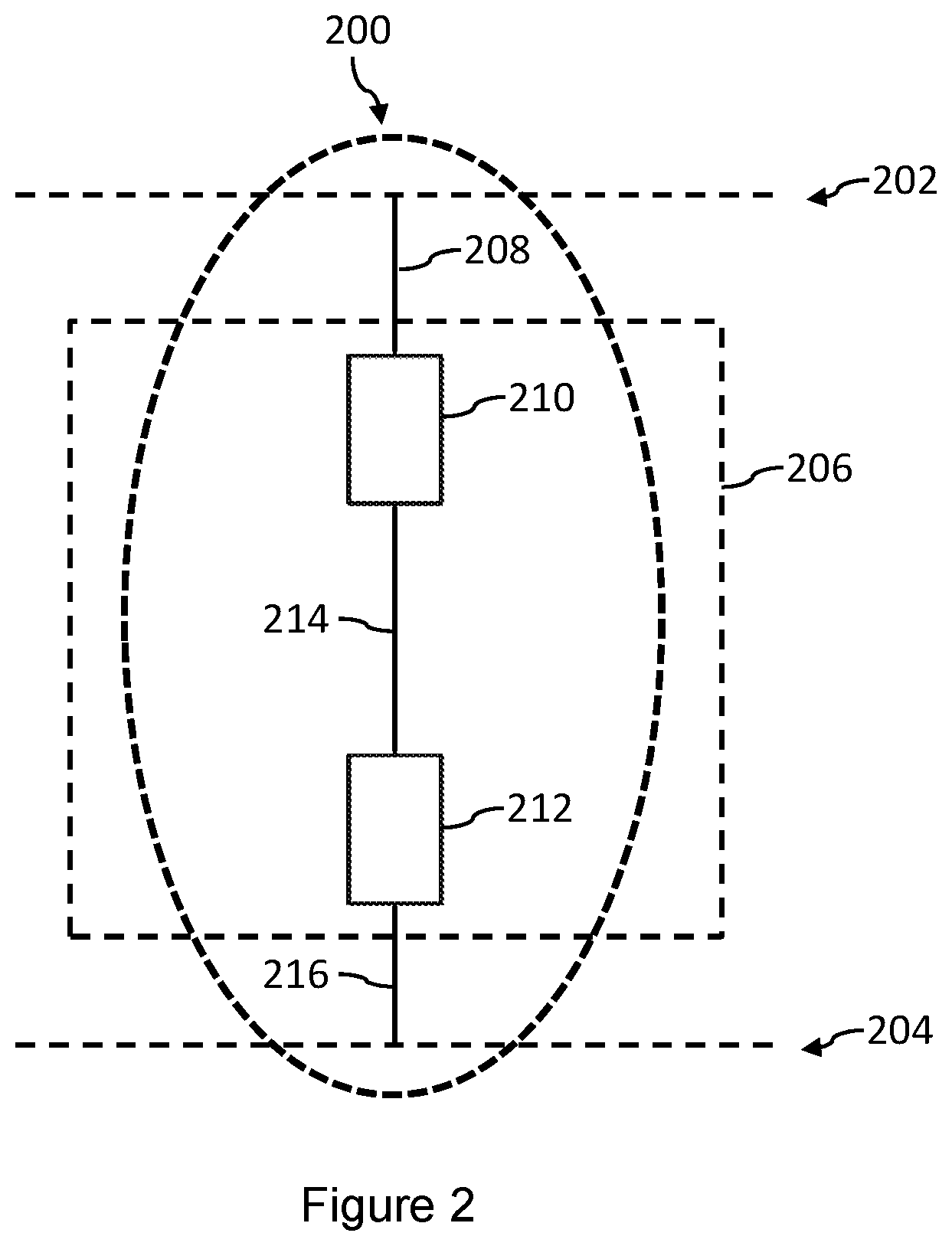

[0075] FIG. 2 is a schematic diagram illustrating another example implementation of a microwave path to a superconducting circuit, according to the present disclosure. Microwave path 200 is positioned in a cryogenic refrigeration system. The cryogenic refrigeration system includes a still 202, a sample holder 204, and a mixing chamber 206. Microwave path 200 travels between still 202 and sample holder 204. Microwave path 200 is a microwave path through the cryogenic refrigeration system. Still 202, sample holder 204, and mixing chamber 206 are shown as dashed lines in FIG. 2 to provide context for microwave path 200.

[0076] Sample holder 204 can contain or hold the superconducting circuit. In some implementations, the superconducting circuit is an integrated superconducting circuit. The integrated superconducting circuit may comprise or include a quantum processor with one or more other superconducting processors or devices, or may consist of a quantum processor. In some implementations, the quantum processor includes a plurality of superconducting flux qubits.

[0077] Microwave path 200 traverses mixing chamber 206. Microwave path 200 includes a coaxial cable 208 between still 202 and mixing chamber 206. In some implementations, coaxial cable 208 is a superconducting coaxial cable. In some implementations, coaxial cable is a stainless steel coaxial cable.

[0078] Microwave path 200 includes a bandpass filter 210 and a switch 212. Bandpass filter 210 is communicatively coupled to switch 212 by a coaxial cable 214. In some implementations, bandpass filter 210 is a GHz bandpass filter with greater than 90 dB out-of-band suppression of frequencies below 60 GHz. In some implementations, coaxial cable 214 is a copper coaxial cable. Switch 212 is communicatively coupled to sample holder 204 by coaxial cable 216. In some implementations, coaxial cable 216 is a copper coaxial cable.

[0079] In some implementations operating at a temperature of approximately 4 K, switch 212 is a CMOS switch. In other implementations operating at a temperature of approximately 4 K, switch 212 is a superconducting switch, e.g., a cryotron. In some implementations operating at a temperature of approximately 10 mK, switch 212 is a superconducting switch, e.g., a cryotron. In yet other implementations, switch 212 is a broadband switch as described in the present application with reference to FIGS. 11, 12, and 13.

Example Lumped-Element Resonators

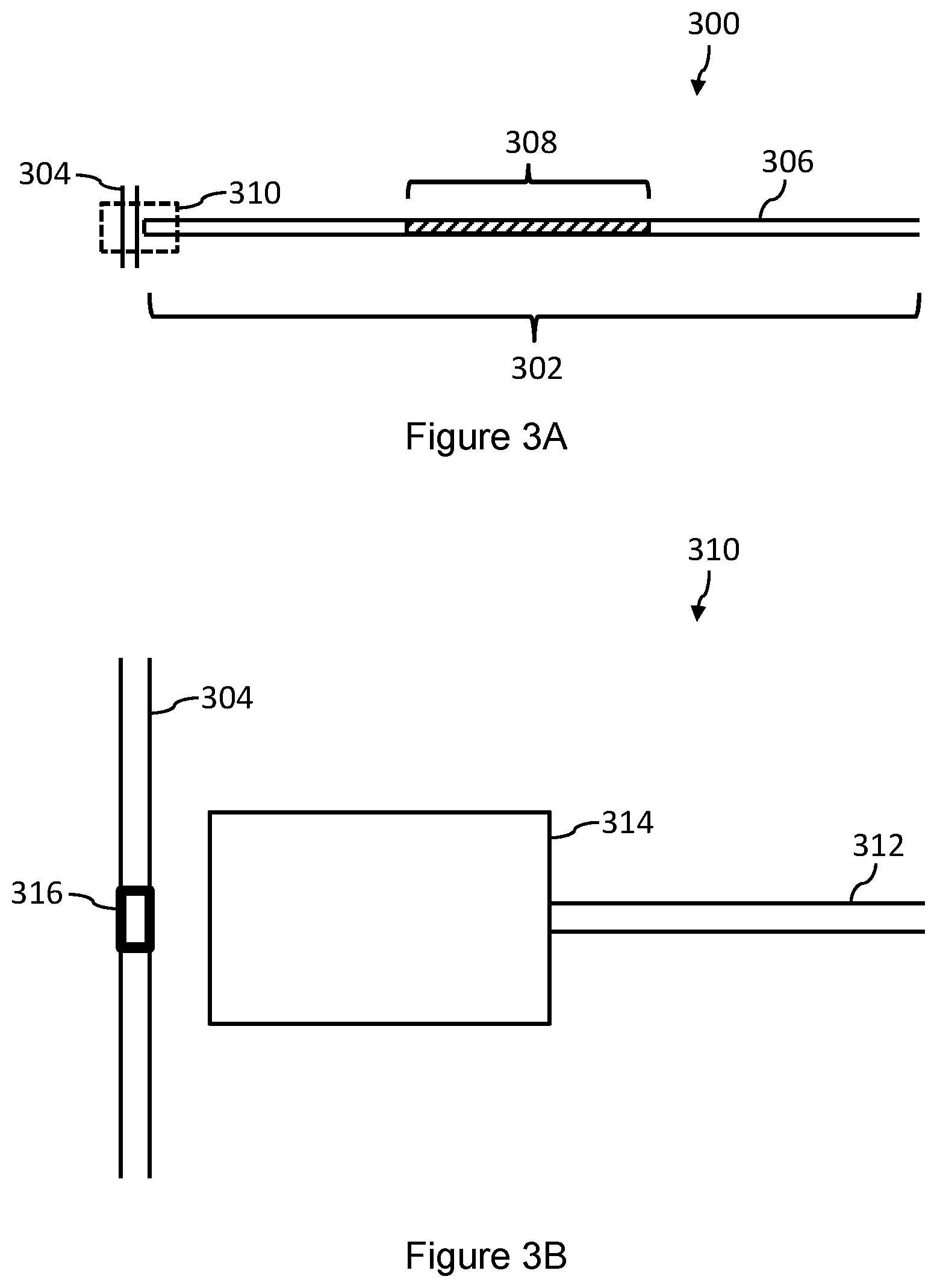

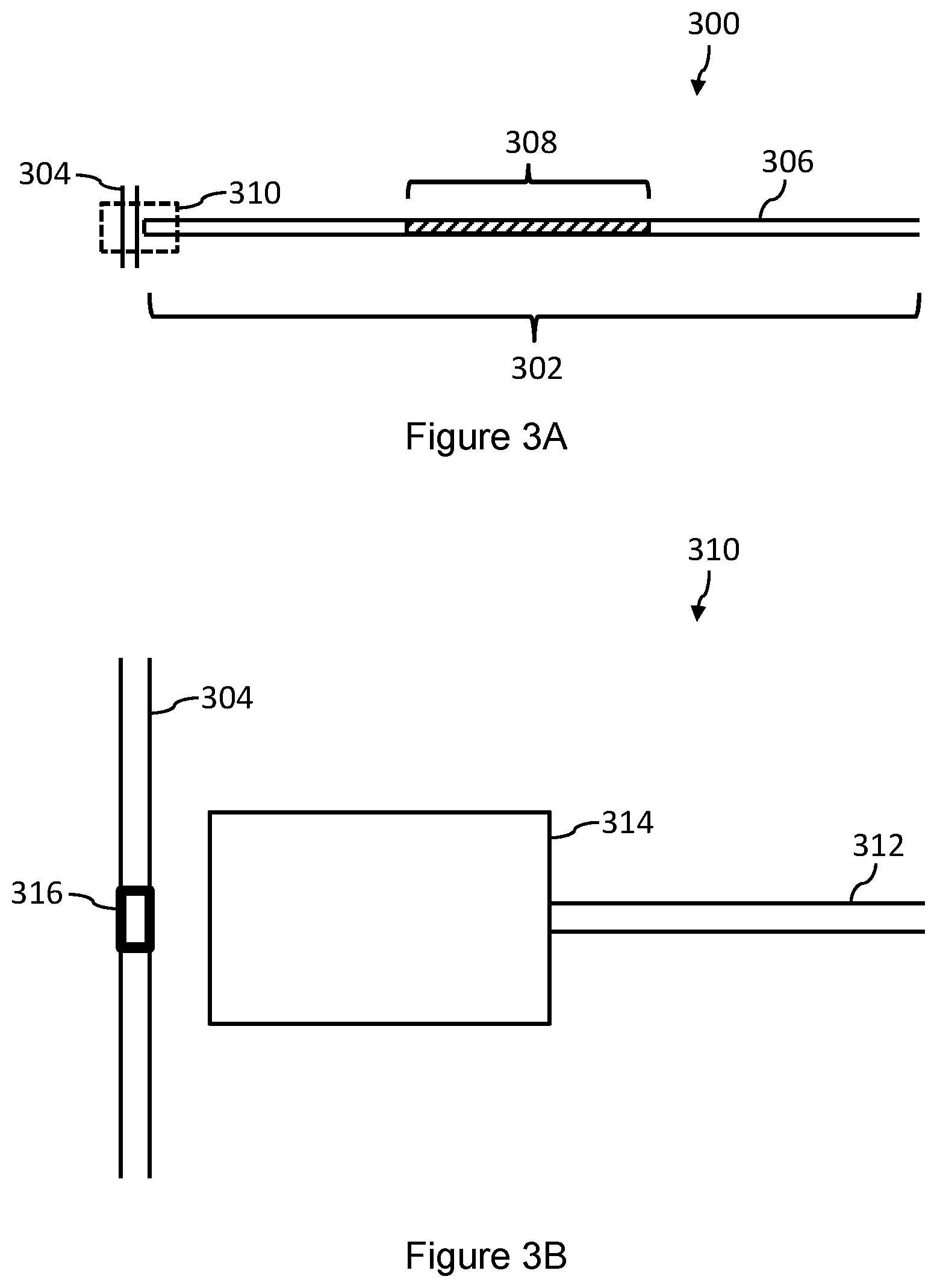

[0080] FIG. 3A is a schematic layout of a portion of an example implementation of a superconducting circuit 300 that includes a superconducting half-wave resonator 302 and a transmission line 304, according to the present disclosure. For example, superconducting half-wave resonator 302 can be a microstrip resonator, a coplanar waveguide (CPW) resonator, or a lumped-element resonator. For example, transmission line 304 can be a microstrip transmission line, a CPW transmission line, or a coaxial transmission line.

[0081] Superconducting half-wave resonator 302 includes a resonator body 306. FIG. 3A illustrates a portion of resonator body 306. In one implementation, resonator body 306 is 7 mm in length.

[0082] Region 308 (shown in FIG. 3A by hatching) is a region over which a current in resonator body 306 is within a suitable threshold of a maximum current. In some implementations, the suitable threshold is 90% of the maximum current. In some implementations, one portion of a length of resonator body 306 is used for coupling to a DAC, and another portion of the length is serpentine, e.g., to increase compactness of superconducting half-wave resonator 302.

[0083] FIG. 3B is an enlarged view of a coupling region 310 of superconducting half-wave resonator 302 of FIG. 3A. Superconducting half-wave resonator 302 includes wiring 312 and a coupling capacitor 314. In some implementations, coupling capacitor 314 is a parallel-plate capacitor. In some implementations, coupling capacitor 314 includes a thin-film metal-oxide layer as a dielectric in the parallel-plate capacitor. See for example U.S. Provisional Patent Application Ser. No. 62/660,719, "SYSTEMS AND METHODS FOR FABRICATION OF SUPERCONDUCTING DEVICES", filed Apr. 20, 2018, and U.S. patent application Ser. No. 16/389,669, "SYSTEMS AND METHODS FOR FABRICATION OF SUPERCONDUCTING DEVICES". In one implementation, coupling capacitor 314 has dimensions of 30 .mu.m.times.20 .mu.m.

[0084] Superconducting circuit 300 includes a via 316, for example to provide a superconducting communicative coupling between transmission line 304 and a lower capacitor plate of coupling capacitor 314. The lower capacitor plate of coupling capacitor 314 is not shown in FIG. 3B. A via is also referred to in the present application as a VIA and a vertical interconnect access. A via is an electrical communicative coupling between layers in an electronic circuit. The via may pass through a plane of one or more adjacent layers. The electronic circuit may be an integrated circuit. The electronic circuit may be a printed circuit board. A superconducting via is a superconducting electrical communicative coupling between layers in a superconducting electronic circuit.

[0085] Superconducting half-wave resonator 302 can have a symmetric coupling to ground at the other end. The ground is also referred to in the present application as an electrical ground. The ground is not shown in FIGS. 3A and 3B. In some implementations, wiring 312 and/or transmission line 304 include 2 .mu.m lines over a 1 .mu.m silicon dioxide (SiO2) dielectric, which can provide an impedance close to 50.OMEGA.. In one implementation, superconducting half-wave resonator 302 has a resonance at 9.58 GHz with approximately 35 MHz of bandwidth.

[0086] FIG. 4A is a schematic layout of a portion of an example implementation of a superconducting circuit 400a that includes a superconducting lumped-element resonator 402 and a transmission line 404, according to the present disclosure. Superconducting lumped-element resonator 402 includes a resonator body 406.

[0087] Region 408 (shown in FIG. 4A by hatching) is a region over which a current in resonator body 406 is within a suitable threshold of a maximum current. In some implementations, the suitable threshold is 90% of the maximum current.

[0088] FIG. 4B is an enlarged view of a coupling region 410 of superconducting lumped-element resonator 402 of FIG. 4A. Superconducting lumped-element resonator 402 includes wiring 412, a coupling capacitor 414, and a shunting capacitor 416. In some implementations, coupling capacitor 414 is a parallel-plate capacitor. In some implementations, coupling capacitor 414 includes a thin-film metal-oxide layer for a dielectric in the parallel-plate capacitor. In one implementation, coupling capacitor 414 has dimensions of 30 .mu.m.times.30 .mu.m. In one implementation, shunting capacitor 416 has dimensions 100 .mu.m.times.120 .mu.m.

[0089] Superconducting lumped-element resonator 402 can have a symmetric coupling to ground at the other end. In some implementations, wiring 412 and/or transmission line 404 include 2 .mu.m lines over a 1 .mu.m silicon dioxide (SiO2) dielectric, which can provide an impedance close to 50.OMEGA.. In one implementation, superconducting lumped-element resonator 402 has a resonance at 9.62 GHz with approximately 30 MHz of bandwidth.

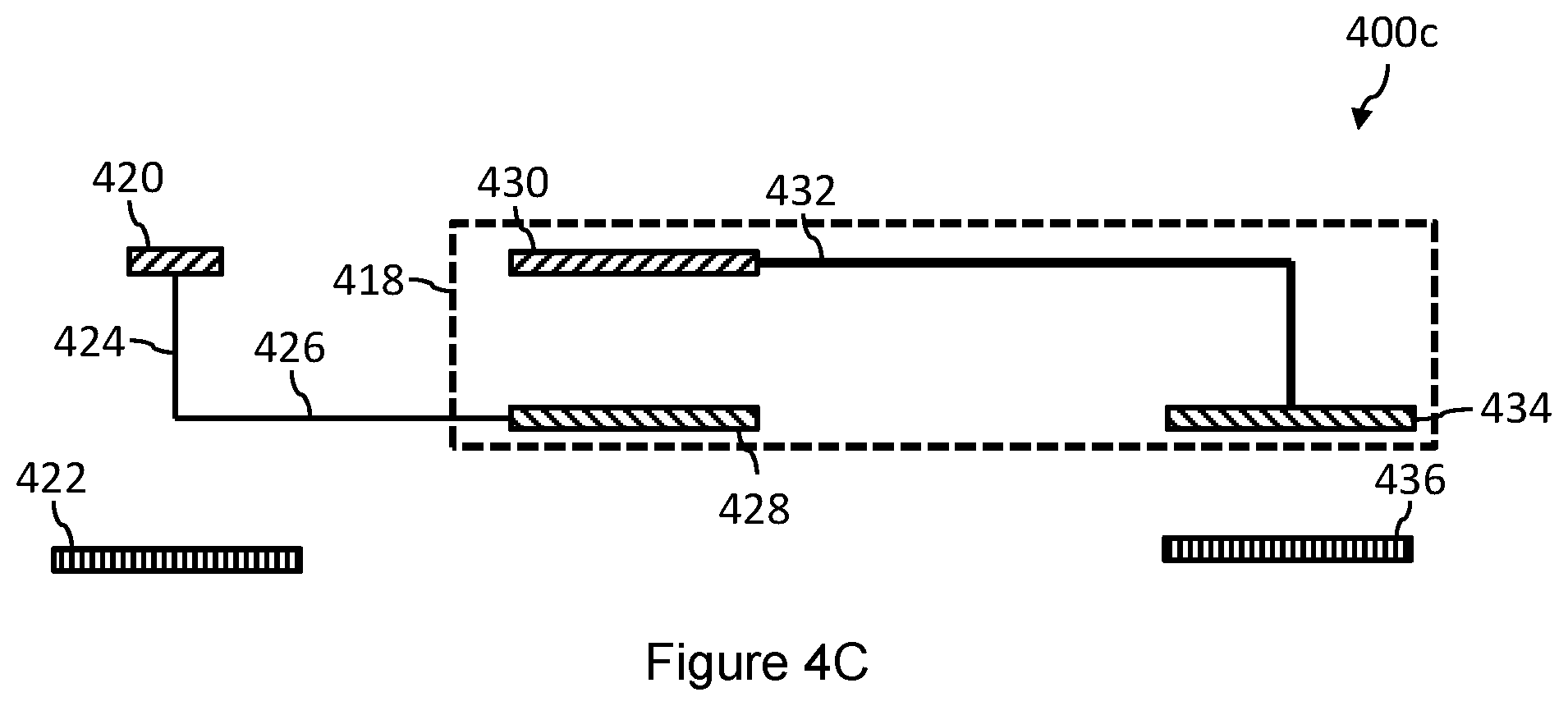

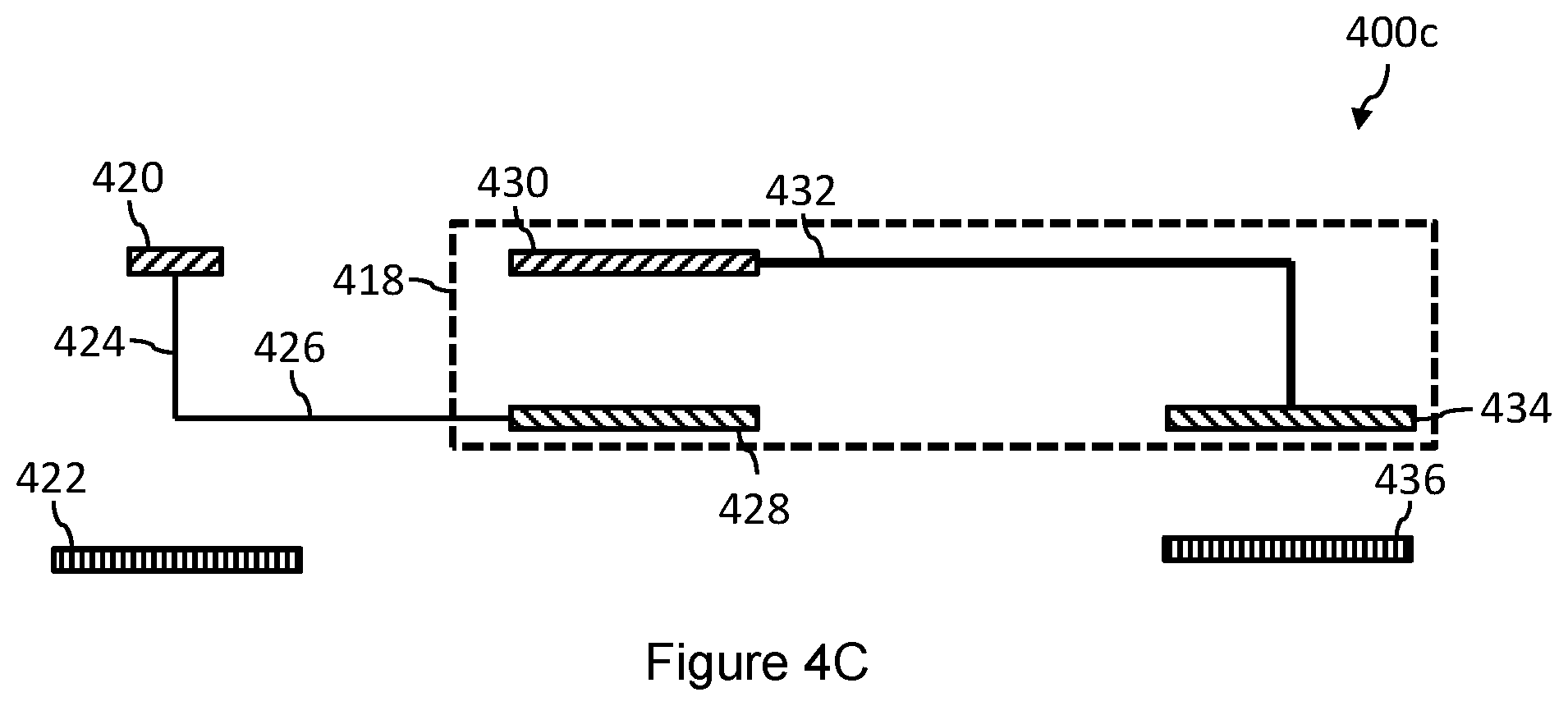

[0090] FIG. 4C is a schematic drawing of a cross-section of a portion of an example implementation of a superconducting circuit 400c that includes a superconducting lumped-element resonator 418 and a transmission line 420, according to the present disclosure.

[0091] Superconducting circuit 400c is implemented in a multilayer superconducting integrated circuit. Transmission line 420 is coupled to a ground plane 422. Transmission line 420 is superconductingly communicatively coupled by a superconducting via 424 and superconducting wiring 426 to a lower plate 428 of a coupling capacitor (such as coupling capacitor 414 of FIG. 4B).

[0092] An upper plate 430 of the coupling capacitor is superconductingly communicatively coupled to a resonator body 432 and an upper plate 434 of a capacitor coupling superconducting lumped-element resonator 418 to a ground plane 436.

Resonator-Addressed DAC

[0093] Resonator-addressing of a superconducting digital-to-analog converter (DAC) can use the DAC in operation to perform latching. Resonator-addressing is also referred to in the present application as resonator-loading of a DAC. A resonator can be integrated with a DAC, and can, for example, be used to replace an ADDR line and/or a TRIG line.

[0094] The superconducting DAC is a flux memory or flux storage device. The DAC can convert a digital amount of flux into flux stored in an analog device.

[0095] In some implementations, the DAC includes a loop of material that is superconducting in a range of temperatures, the loop interrupted by one or more Josephson junctions. In one implementation, the DAC is an rf-SQUID (radio-frequency superconducting quantum interference device) and includes a superconducting loop interrupted by a single Josephson junction. In another implementation, the DAC is a superconducting loop interrupted by a compound Josephson junction (CJJ). A CJJ includes two parallel current paths each interrupted by a Josephson junction. The DAC CJJ loop can behave as a summing element for magnetic flux. The loop can combine a direct current (DC) provided by a wire (e.g., a twisted-pair) with a current induced by a resonator. In some implementations, the wire is shared globally, i.e., shared by multiple DACs in the processor, and the wire can provide a global bias signal.

[0096] Storing flux in the DAC includes adding flux to the CJJ loop of the DAC, and moving flux in the CJJ loop of the DAC into the storage loop of the DAC (i.e., into the superconducting loop of the DAC). Flux can be added to the CJJ loop of the superconducting DAC by suppressing a Josephson junction in the CJJ using one or more control signals or biases. Flux can be moved into the DAC storage loop by suppressing another Josephson junction in the CJJ loop using one or more control signals or biases. Multiple flux quanta can be stored in a superconducting DAC implemented using a CJJ loop.

[0097] See, for example, Johnson M. W. et al. "A scalable control system for a superconducting adiabatic quantum optimization processor", arXiv:0907.3757v2, 24 Mar. 2010 for a description of an example implementation of flux DACs operable to control superconducting devices in an integrated circuit.

[0098] An array of resonators can be used to provide one or more signals that can be combined with the global bias signal to enable addressing of DACs.

[0099] FIG. 5A is a schematic diagram illustrating an example implementation of a superconducting circuit 500a that includes a resonator-addressed DAC 502, according to the present disclosure.

[0100] In superconducting circuit 500a, resonator-addressed DAC 502 includes a loop 504 of material that is superconductive in a range of temperatures, and a CJJ 506. CJJ 506 includes two parallel current paths each interrupted by a Josephson junction, Josephson junctions 508 and 510, respectively.

[0101] Superconducting circuit 500a further includes a resonator 512, a transmission line 514, and interface 516 operable to provide a global flux bias by a global flux bias line 516-1. Resonator 512 includes coupling capacitors 518 and 520, an inductive interface 522 to resonator-addressed DAC 502, and an optional shunting capacitor 524. The term "inductive interface" is also referred to in the present application as a coupling inductance. Coupling inductance 522, for example, inductively communicatively couples resonator 512 and resonator-addressed DAC 502.

[0102] Superconducting circuit 500a further includes a current bias line 526 operable to provide a current bias to resonator-addressed DAC 502.

[0103] In some implementations, multiple resonators are coupled to a single DAC CJJ loop. FIG. 5B is a schematic diagram illustrating another example implementation of a superconducting circuit 500b that includes a resonator-addressed digital-to-analog converter (DAC) 502, according to the present disclosure.

[0104] In FIG. 5B, the same reference numbers as used in FIG. 5A are used in FIG. 5B to denote the same or similar elements. In instances where there is more than one of a given element in the implementation of FIG. 5B, the reference number has a suffix, for example "a" or "b".

[0105] In superconducting circuit 500b, resonator-addressed DAC 502 includes a loop 504 of material that is superconductive in a range of temperatures, and a CJJ 506. CJJ 506 includes two parallel current paths each interrupted by a Josephson junction, Josephson junctions 508 and 510, respectively.

[0106] Superconducting circuit 500b further includes a pair of resonators 512a and 512b, a transmission line 514, and interface 516 operable to provide a global flux bias by a global flux bias line 516-1. Resonator 512a includes coupling capacitors 518a and 520a, an inductive interface 522a to resonator-addressed DAC 502, and an optional shunting capacitor (not shown in FIG. 5B for clarity) like optional shunt capacitor 524 of FIG. 5A. Resonator 512b includes coupling capacitors 518b and 520b, an inductive interface 522b to resonator-addressed DAC 502, and an optional shunting capacitor (not shown in FIG. 5B for clarity) like optional shunt capacitor 524 of FIG. 5A.

[0107] Superconducting circuit 500b further includes a current bias line 526 operable to provide a current bias to resonator-addressed DAC 502.

[0108] In one implementation, resonators 512a and 512b are both coupled to transmission line 514. In another implementation, resonator 512a is coupled to transmission line 514, and resonator 512b is coupled to another transmission line (not shown in FIG. 5B).

[0109] In an example where two resonators are coupled to the same DAC CJJ loop, programming of the DAC can be achieved by having a low-frequency bias signal and two microwave signals combine constructively to exceed a determined address latching level. The arrangement can be used to construct an XY-addressing scheme for a set of DACs, for example as follows. Firstly, a DC current bias is applied to the DAC by a line referred to in the present application as a power line (PWR). Next, a global low-frequency bias address line (such global flux bias line 516-1 of FIGS. 5A and 5B) is coupled to each DAC CJJ loop of the set of DAC CJJ loops. Then, an array of resonators is laid out across the processor in a two-dimensional X-Y grid. Programming a selected DAC can be achieved by pre-biasing the set of DAC CJJ loops, and activating the two resonators (also referred to in the present application as the address and trigger resonators) that intersect at the selected DAC.

[0110] The selected DAC can be programmed when the two microwave tones (at frequencies f.sub.lo and f.sub.hi respectively) add constructively at the selected DAC. A relative phase between the two microwave tones can evolve at an angular frequency co given by the following expression:

.omega.=2.pi./(f.sub.hi-f.sub.lo)

The higher frequency tone can advance by .delta..theta.=.omega./f.sub.lo radians per cycle relative to the low frequency tone. Each time the low frequency tone is at a maximum, the high frequency tone can have advanced by an angle of dB. The angle .delta..theta. can represent the closest the maxima can approach within a cycle at the beat frequency, and, since the angle .delta..theta. can be linearly proportional to the beat frequency .omega., it can be desirable to select a smaller beat frequency .omega.. On the other hand, the smaller the beat frequency .omega., the longer it will take to complete a full 2.pi. rotation.

[0111] It can be desirable to leave the resonator charged no more than a few multiples of .tau.=1/(2.pi..DELTA.f) where .DELTA.f is the bandwidth per tone (also referred to in the present application as a linewidth of the resonator). It can typically take a few multiples of .tau. to charge and discharge the resonator. Programming can be completed roughly on the same timescale for efficient bandwidth utilization. This suggests that it can be desirable to match the beat frequency to the linewidth of the resonator.

[0112] This leads to a criterion for completing the programming in a reasonable time--that the beat frequency should be approximately matched to a resonator linewidth (.omega..about.2.pi..DELTA.f). This is consistent with a preference for resonances within a single array to be separated by a few linewidths .DELTA.f to avoid, or at least reduce, cross-talk between channels. With the beat frequency determined, the resonant frequencies can, in general, be selected to be at higher frequencies consistent with the determined beat frequency.

[0113] FIG. 5C is a schematic diagram illustrating an example implementation of a superconducting circuit 500c that includes a pair of resonator-addressed digital-to-analog converters (DACs) 502a and 502b, according to the present disclosure.

[0114] The same reference numbers as used in FIG. 5A are used in FIG. 5C to denote the same or similar elements. In instances where there is more than one of a given element in the implementation of FIG. 5C, the reference number has a suffix, for example "a" or "b".

[0115] In superconducting circuit 500c, resonator-addressed DAC 502a includes a loop 504a of material that is superconductive in a range of temperatures, and a CJJ 506a. CJJ 506a includes two parallel current paths each interrupted by a Josephson junction, Josephson junctions 508a and 510a, respectively. Resonator-addressed DAC 502b includes a loop 504b of material that is superconductive in a range of temperatures, and a CJJ 506b. CJJ 506b includes two parallel current paths each interrupted by a Josephson junction, Josephson junctions 508b and 510b, respectively.

[0116] Superconducting circuit 500c further includes a resonator 512, a transmission line 514, and interfaces 516a, 516b operable to provide a global flux bias by a global flux bias line 516-1. Resonator 512 includes coupling capacitors 518 and 520, an inductive interface 522c to resonator-addressed DAC 502a, an inductive interface 522d to resonator-addressed DAC 502b, and an optional shunting capacitor 524.

[0117] Superconducting circuit 500c further includes a current bias line 526a operable to provide a current bias to resonator-addressed DAC 502a, and a current bias line 526b operable to provide a current bias to resonator-addressed DAC 502b.

[0118] A variation in current along the body of resonator 512 of FIG. 5C can be at least partially compensated for by tuning each coupling of resonator 512 to DAC CJJ loops 502a and 502b. In some implementations, resonator 512 can be coupled to more than two DAC CJJ loops (only two DAC CJJ loops are shown in FIG. 5C), and a variation in current along the body of resonator 512 can be at least partially compensated for by tuning each coupling of resonator 512 to a respective DAC CJJ loop.

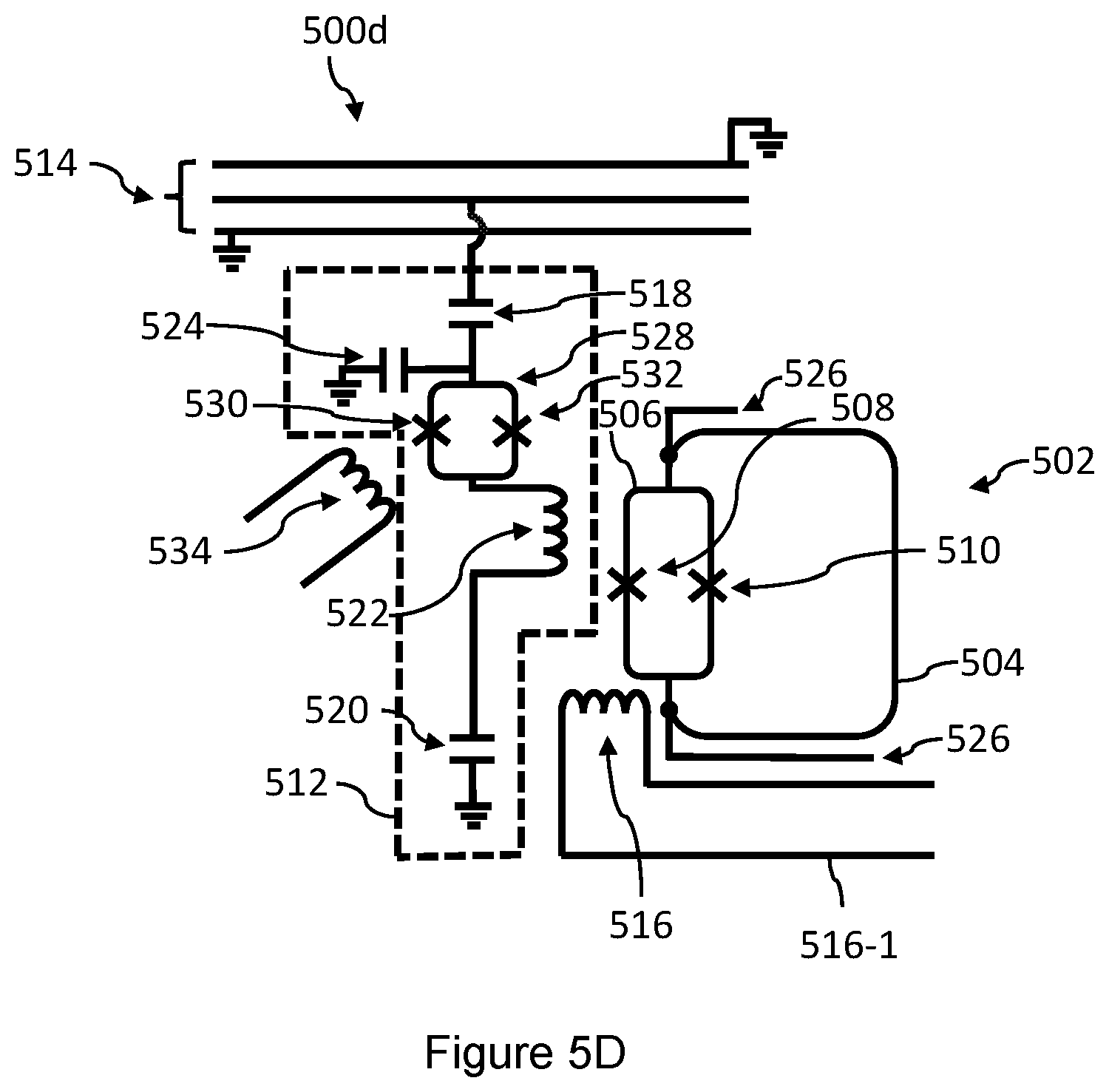

[0119] FIG. 5D is a schematic diagram illustrating another example implementation of a superconducting circuit 500d that includes a resonator-addressed digital-to-analog converter (DAC) 502, according to the present disclosure. Resonator 512 of FIG. 5D includes a DC-SQUID (direct current superconducting quantum interference device) 528. DC-SQUID 528 includes a pair of Josephson junctions 530 and 532. Superconducting circuit 500d includes an interface 534. Interface 534 can be provided by a DAC or an analog line, for example. A resonant frequency of resonator 512 of FIG. 5D can be tuned by applying a flux bias to DC-SQUID 532 by interface 534.

[0120] In some implementations, a critical current of at least one of Josephson junctions 530 and 532 is comparable in magnitude to a current in resonator 512.

[0121] Instead of capacitively communicatively coupling resonator 512 of FIGS. 5A, 5C, and 5D to transmission line 514 by coupling capacitor 518, resonator 512 can be communicatively coupled to transmission line 514 by an inductive coupling. For example, resonator 512 can be inductively communicatively coupled to transmission line 514 by an inductive coupling to a portion of the body of resonator 512.

[0122] Similarly, instead of capacitively communicatively coupling each of resonators 512a and 512b of FIG. 5B to a respective transmission line by a respective coupling capacitor, at least one of resonators 512a and 512b can be inductively communicatively coupled to the respective transmission line by an inductive coupling to a portion of the body of the resonator.

[0123] FIG. 5E is a schematic diagram illustrating an example implementation of a superconducting circuit 500e that includes a resonator-addressed digital-to-analog converter (DAC) 502, and a resonator 512 that is inductively coupled to transmission line 514, according to the present disclosure. The same reference numbers as used in FIG. 5A are used in FIG. 5E to denote the same or similar elements.

[0124] Superconducting circuit 500e includes a transmission line inductance 536, and matching capacitors 538 and 540. Matching capacitors 538 and 540 can at least partially tune an impedance of transmission line 514 (e.g. to cause the impedance of transmission line 514 to be approximately 50.OMEGA.).

[0125] Resonator 512 can be inductively communicatively coupled to transmission line 514 by a shared galvanic inductance 536. Resonator 512 can be used to address one or more DACs or other superconducting devices. Resonator 512 includes a first part 542 that includes an inductive interface 522 to resonator-addressed DAC 502, and a second part 544 that includes an inductive interface 546 to another resonator-addressed DAC (not shown in FIG. 5E). First part 542 includes a capacitor 520, and second part 544 includes a capacitor 548.

[0126] FIG. 5F is a schematic diagram illustrating another example implementation of a superconducting circuit 500f that includes a resonator-addressed digital-to-analog converter (DAC) 502, and a resonator 512 that is inductively coupled to transmission line 514, according to the present disclosure. The same reference numbers as used in FIG. 5A are used in FIG. 5F to denote the same or similar elements. Superconducting circuit 500f includes a coupling inductance 550 that can inductively communicatively couple resonator 512 to transmission line 514 by transmission line inductance 536. Coupling inductance 550 and transmission line inductance 536 form a magnetic transformer by which resonator 512 is inductively coupled to transmission line 514.

[0127] FIG. 6 is a flow chart illustrating an example method 600 for programming a DAC according to the present disclosure. FIG. 6 illustrates a sequence of currents used to load a single flux quantum into a DAC storage loop using standard 30 MHz lines, for example. Method 600 may be implemented by a programming system. For example, method 600 may be implemented by electronics, for example electronics operating at room temperature. In some implementations, the phases and amplitudes of the high-frequency tones are controllable, for example, by electronics operating at room temperature.

[0128] Method 600 includes acts 602 to 620, though those of skill in the art will appreciate that in alternative embodiments certain acts may be omitted and/or additional acts may be added. Those of skill in the art will appreciate that the illustrated order of the acts is shown for exemplary purposes only and may change in alterative embodiments.

[0129] Method 600 starts at 602, for example in response to an initiation of a programming of a DAC. At 604, the DAC power level in the current line to the resonator-addressed DAC (such as resonator-addressed DAC 502 of FIG. 5A) is raised to a pre-calibrated level or defined calibration level. At 606, the global address bias line is raised to a pre-calibrated level or defined calibration level, thereby applying a flux bias to one or more resonator-addressed DACs. The level can be calibrated to cause the level to cross a predetermined or defined upper threshold when high-frequency microwave pulses are applied by a transmission line (such as transmission line 514 of FIG. 5A) and a resonator (such as resonator 512 of FIG. 5A). The upper threshold can be selected to cause a flux quantum to be added to the CJJ loop when the upper threshold is exceeded by applying and combining the global bias and the high-frequency microwave pulses.

[0130] At 608, the high-frequency ADDR and/or TRIG (e.g., X and/or Y) microwave pulses are applied to selected devices, e.g., to selected resonator-addressed DACs. In an XY-addressing scheme, the flux bias injected into the DAC by the ADDR (or X) line can be one-half of the flux needed to cause the combined address signal current (see, for example, FIG. 7A) to exceed a threshold for programming the DAC, and the flux bias injected into the DAC by the TRIG (or Y) line can similarly be one-half of the flux needed to cause the combined address signal current to exceed a threshold for programming the DAC. The DAC is programmed only when a threshold is exceeded in the combined address signal current (see, for example, FIGS. 7A-7C and accompanying description). The systems and methods described in the present application can cause the threshold to be exceeded when a) a sufficient flux bias is applied by a global address bias line, and b) there are pulses on the ADDR (X) and TRIG (Y) address lines.