Apparatuses And Methods For Analog Row Access Tracking

Wu; Jun ; et al.

U.S. patent application number 16/546152 was filed with the patent office on 2021-02-25 for apparatuses and methods for analog row access tracking. This patent application is currently assigned to MICRON TECHNOLOGY, INC.. The applicant listed for this patent is MICRON TECHNOLOGY, INC.. Invention is credited to Liang Li, Dong Pan, Jun Wu, Yu Zhang.

| Application Number | 20210057021 16/546152 |

| Document ID | / |

| Family ID | 1000004319880 |

| Filed Date | 2021-02-25 |

| United States Patent Application | 20210057021 |

| Kind Code | A1 |

| Wu; Jun ; et al. | February 25, 2021 |

APPARATUSES AND METHODS FOR ANALOG ROW ACCESS TRACKING

Abstract

Embodiments of the disclosure are drawn to apparatuses and methods for analog row access hacking. A plurality of unit cells are provided, each of which contains one or more analog circuits used to track accesses to a portion of the wordlines of a memory device. When a wordline in the portion is accessed, the unit cell may update an accumulator voltage, for example by adding charge to a capacitor. A comparator circuit may determine when one or more accumulator voltages cross a threshold (e.g., a reference voltage). Responsive to the accumulator voltage crossing the threshold, an aggressor address may be loaded in a targeted refresh queue, or if the aggressor address is already in the queue, a priority flag associated with that address may be set. Aggressor addresses may be provided to have their victims refreshed in an order based on the number of set priority flags.

| Inventors: | Wu; Jun; (Su Zhou, CN) ; Li; Liang; (Shanghai, CN) ; Zhang; Yu; (Shanghai, CN) ; Pan; Dong; (Boise, ID) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Assignee: | MICRON TECHNOLOGY, INC. BOISE ID |

||||||||||

| Family ID: | 1000004319880 | ||||||||||

| Appl. No.: | 16/546152 | ||||||||||

| Filed: | August 20, 2019 |

| Current U.S. Class: | 1/1 |

| Current CPC Class: | G11C 11/40611 20130101; G11C 11/4087 20130101; G11C 11/4085 20130101; G11C 11/40603 20130101 |

| International Class: | G11C 11/406 20060101 G11C011/406; G11C 11/408 20060101 G11C011/408 |

Claims

1. An apparatus comprising: a plurality of unit cells, each of the unit cells configured to store one of a plurality of voltages and compare the stored one of the plurality of voltages to a reference voltage, wherein responsive to a select signal indicating one of the plurality of unit cells, the selected one of the plurality of unit cells is configured to update the stored one of the plurality of voltages; and a stack control circuit, the stack control circuit comprising a decoder circuit configured to receive a row address and provide the select signal to one of the plurality of unit cells based on the row address, wherein the stack control circuit comprises a comparator circuit configured to provide a trigger signal responsive to the stored one of the plurality of voltages crossing the reference voltage.

2. The apparatus of claim 1, wherein the decoder circuit is further configured to provide the select signal based on a subset of bits of the row address.

3. The apparatus of claim 2, wherein the plurality of unit cells each represent a different value of the subset of bits of the row address, and wherein the plurality of unit cells together represent all values of the subset of bits of the row address.

4. The apparatus of claim 1, wherein each unit cell comprises an accumulator circuit including a capacitor and wherein the stored voltage is based on a charge on the capacitor, and wherein responsive to the select signal the unit cell is configured to update the charge on the capacitor.

5. The apparatus of claim 1, wherein each of the plurality of unit cells comprises a comparator portion and wherein the comparator circuit is coupled in common to the comparator portion in each of the plurality of unit cells, wherein responsive to the select signal indicating one of the plurality of unit cells the comparator circuit and the comparator portion in the one of the plurality of unit cells compare the stored one of the plurality of voltages to the reference voltage.

6. The apparatus of claim 1, further comprising: a targeted refresh queue configured to store a plurality of row addresses; and a steal address circuit configured to selectively store a queue address based on the received row address in the targeted refresh queue based, in part, on the trigger signal.

7. The apparatus of claim 6, wherein one or more victim addresses based on the queue address stored in the targeted refresh queue are refreshed.

8. An apparatus comprising: an accumulator circuit comprising a capacitor, the accumulator circuit configured to provide an accumulator voltage based on a charge of the capacitor, the accumulator circuit further configured to add an amount of charge to the capacitor responsive to a select signal; a comparator circuit configured to compare the accumulator voltage to a reference voltage and provide a trigger signal responsive to the accumulator voltage being higher than the reference voltage; and a flag logic circuit configured to set a logical level of a plurality of flag signals based, in part, on the trigger signal.

9. The apparatus of claim 8, further comprising a decoder circuit configured to receive a row address and provide the select signal based on the row address.

10. The apparatus of claim 8, wherein the amount of charge added to the capacitor is based, in part, on a bias voltage, and wherein the bias voltage is adjustable.

11. The apparatus of claim 8, wherein the capacitor is a crown capacitor or a switched capacitor.

12. The apparatus of claim 8, further comprising a pulse generator circuit configured to provide an activation signal with a pulse width, wherein the amount of charge added to the capacitor is based, in part, on the pulse width.

13. The apparatus of claim 8, wherein the flag logic circuit configured to change the logical level of one of the plurality of flag signals from a low logical level to a high logical level responsive to the trigger signal.

14. The apparatus of claim 13, further comprising a discharge logic circuit configured to discharge the capacitor responsive to the flag logic circuit changing the logic level of one of the plurality of flag signals.

15. An apparatus comprising: a memory array comprising a plurality of word lines each associated with a row address; a row access tracking stack configured to store a plurality of voltages in one of a plurality of unit cells, wherein each of the plurality of voltages is associated with a portion of the plurality of word lines, wherein the row access tracking stack includes a stack control circuit configured to change a selected one of the plurality of voltages in an associated one of the plurality of unit cells responsive to receiving a row address associated with the portion of the plurality of wordlines associated with the selected one of the plurality of voltages, and wherein the row access tracking stack further includes a comparator circuit configured to provide a trigger signal if the selected one of the plurality of voltages crosses a threshold represented by a reference voltage; and a targeted refresh queue configured to store a queue addresses based on the row address responsive to the trigger signal.

16. The apparatus of claim 15, wherein the queue address represents a same portion of the plurality of word lines as the portion of the plurality of wordlines associated with the selected one of the plurality of voltages.

17. The apparatus of claim 15, wherein each stored queue address in the targeted refresh queue is associated with a first priority flag and a second priority flag.

18. The apparatus of claim 17, wherein when a first queue address is stored in the targeted refresh queue, the first priority flag is set, and wherein the second priority flag is set responsive to a second queue address provided to the targeted refresh queue matching the first queue address.

19. The apparatus of claim 17, wherein the targeted refresh queue is configured to provide one of the stored queue addresses, and wherein one or more of the plurality of wordlines are refreshed based on the provided one of the stored queue addresses.

20. The apparatus of claim 19, wherein stored queue addresses where the first priority flag and the second priority flag are in an active state are provided before the stored queue addresses where the first priority flag is in the active state and the second priority flag is in an inactive state.

Description

BACKGROUND

[0001] Information may be stored on individual memory cells of the memory as a physical signal (e.g., a charge on a capacitive element). The memory may be a volatile memory, and the physical signal may decay over time (which may degrade or destroy the information stored in the memory cells). It may be necessary to periodically refresh the information in the memory cells by, for example, rewriting the information to restore the physical signal to an initial value.

[0002] As memory components have decreased in size, the density of memory cells has greatly increased. An auto-refresh operation may be carried out where a sequence of memory cells are periodically refreshed. Repeated access to a particular memory cell or group of memory cells (often referred to as a `row hammer`) may cause an increased rate of data degradation in nearby memory cells. In addition to the auto-refresh operations, it may be desirable to identify and refresh memory cells affected by the row hammer in a targeted refresh operation.

BRIEF DESCRIPTION OF THE DRAWINGS

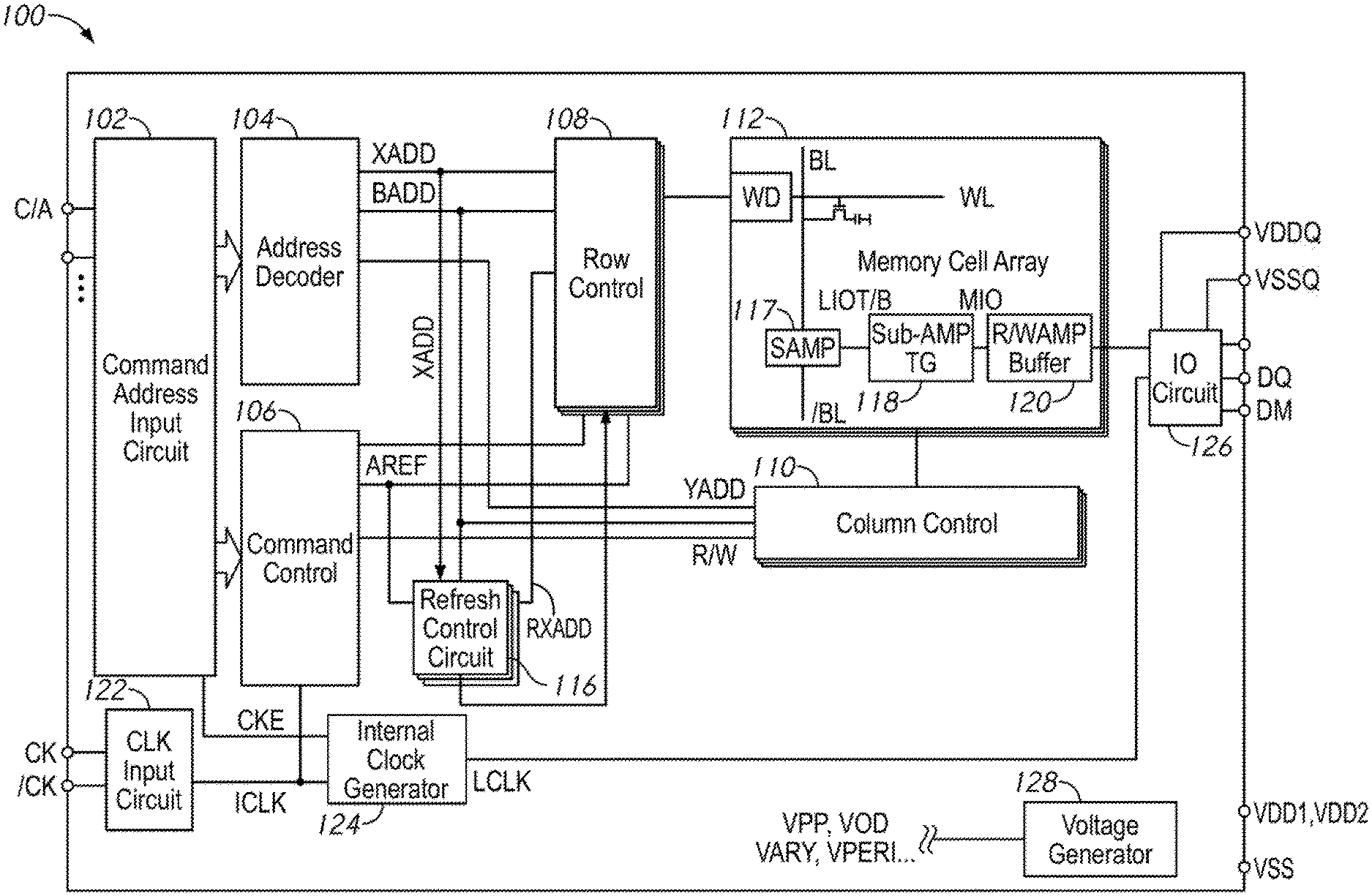

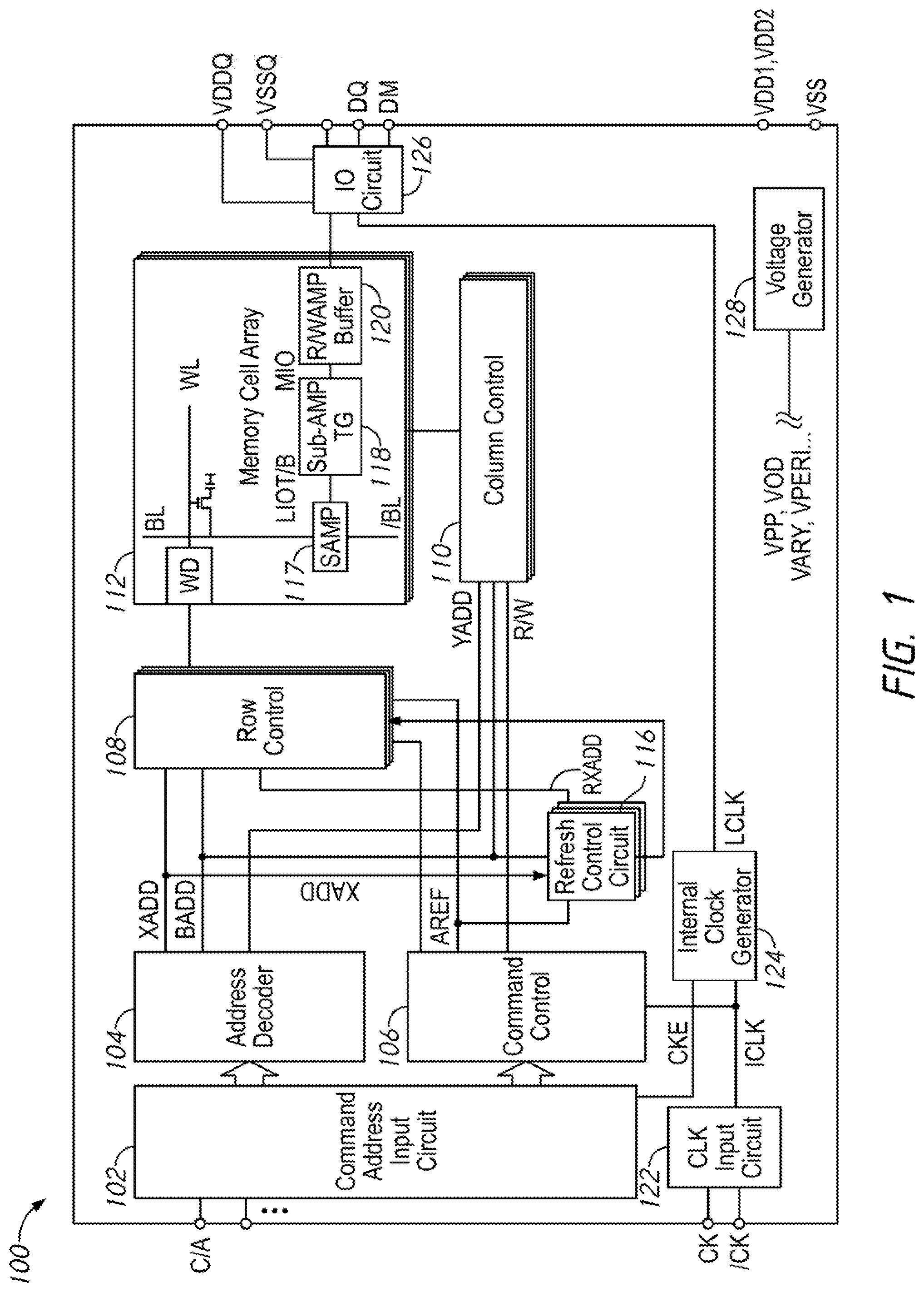

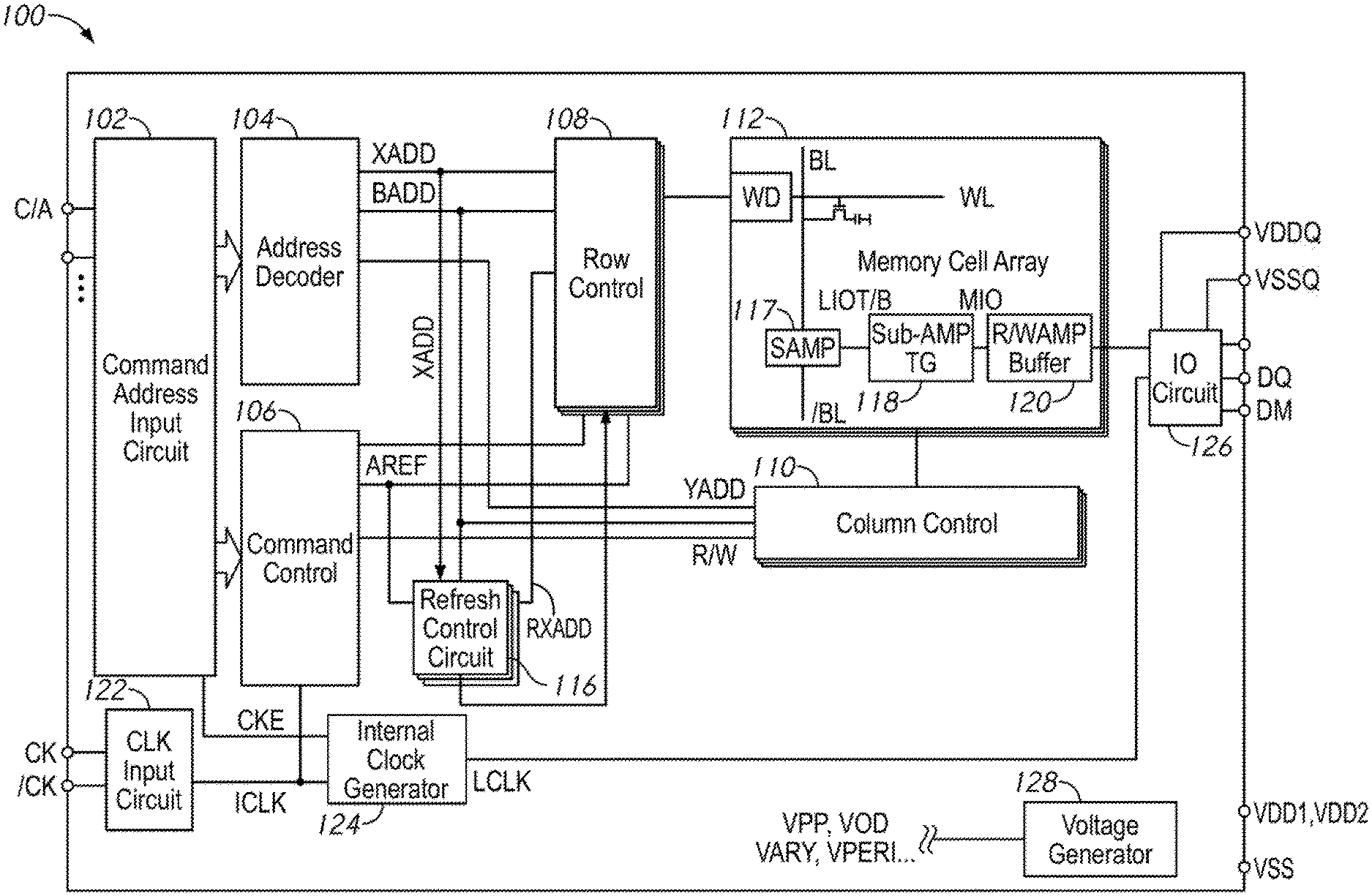

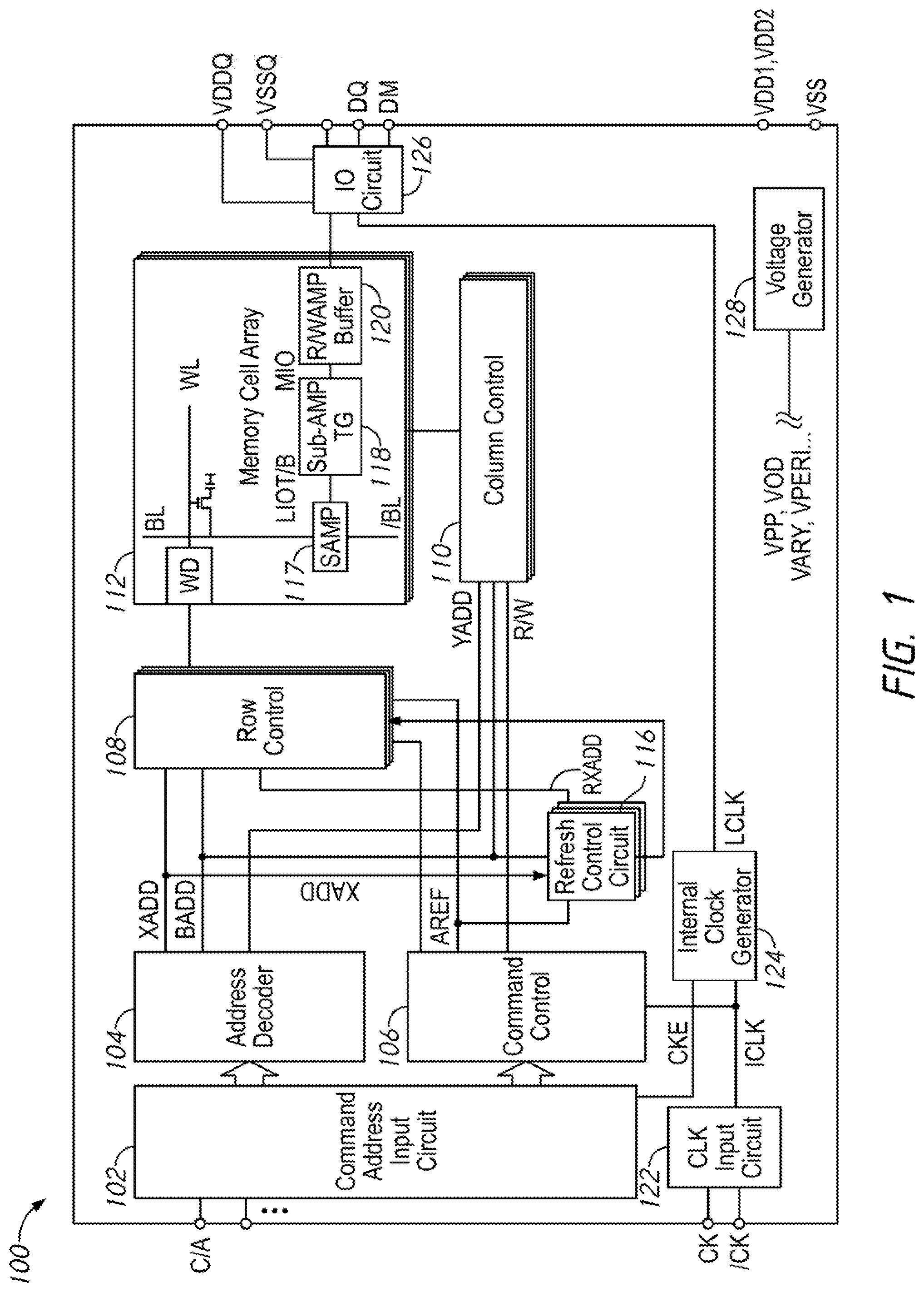

[0003] FIG. 1 is a block diagram of a semiconductor device according to an embodiment of the present disclosure.

[0004] FIG. 2 is a block diagram of a refresh control circuit according to an embodiment of the present disclosure.

[0005] FIG. 3 is a block diagram of a row access tracking stack according to an embodiment of the present disclosure.

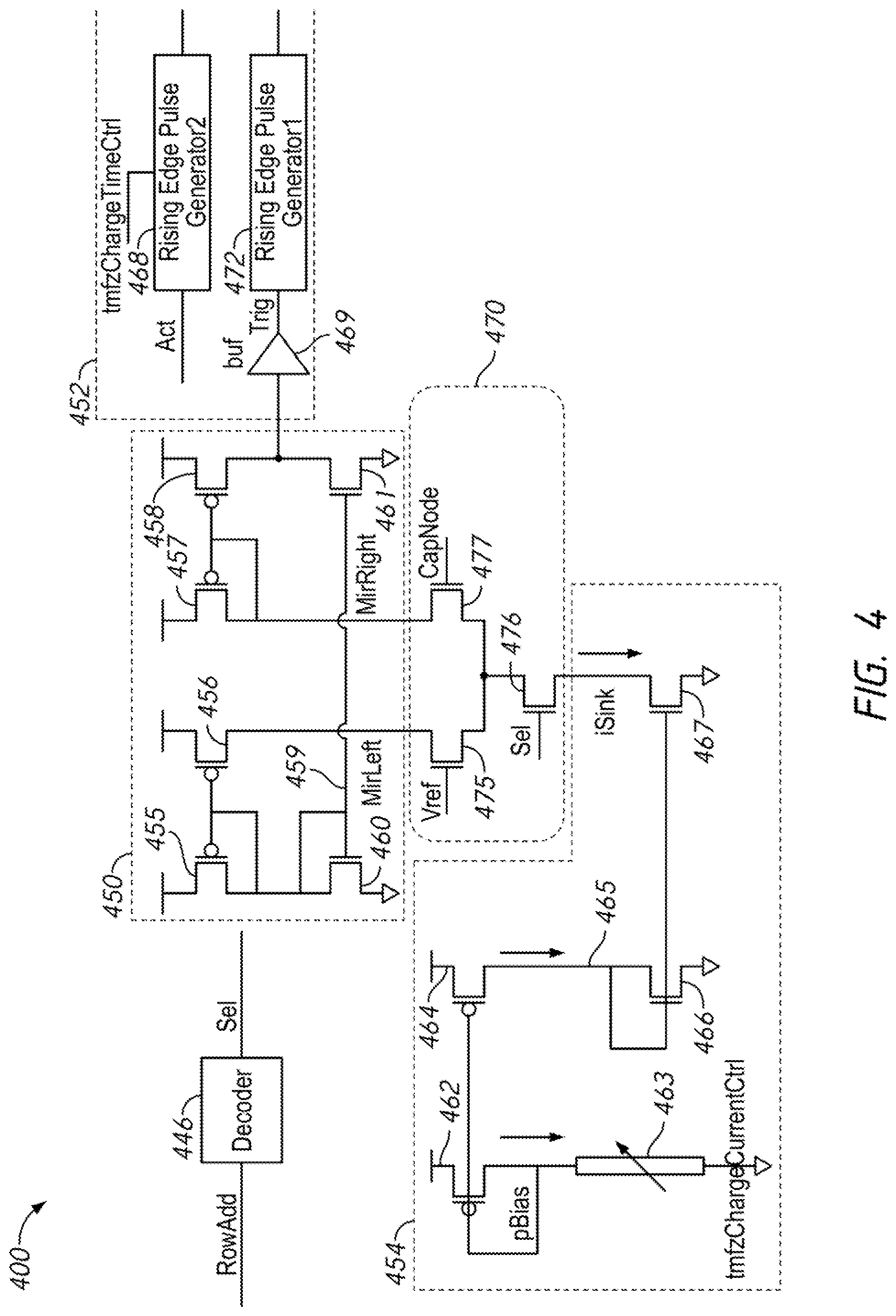

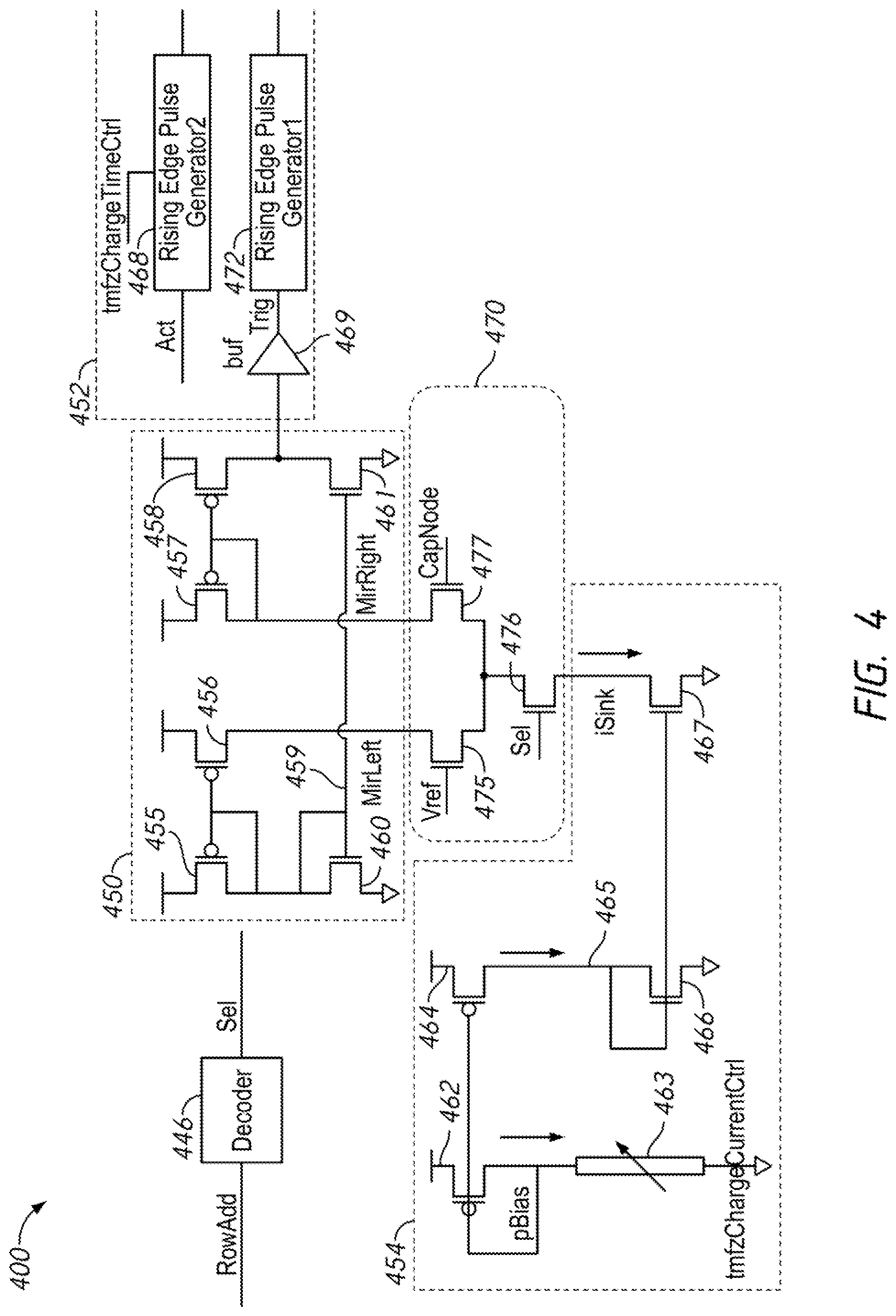

[0006] FIG. 4 is a schematic diagram showing a stack control circuit according to an embodiment of the present disclosure.

[0007] FIG. 5 is a schematic diagram of a unit cell according to an embodiment of the present disclosure.

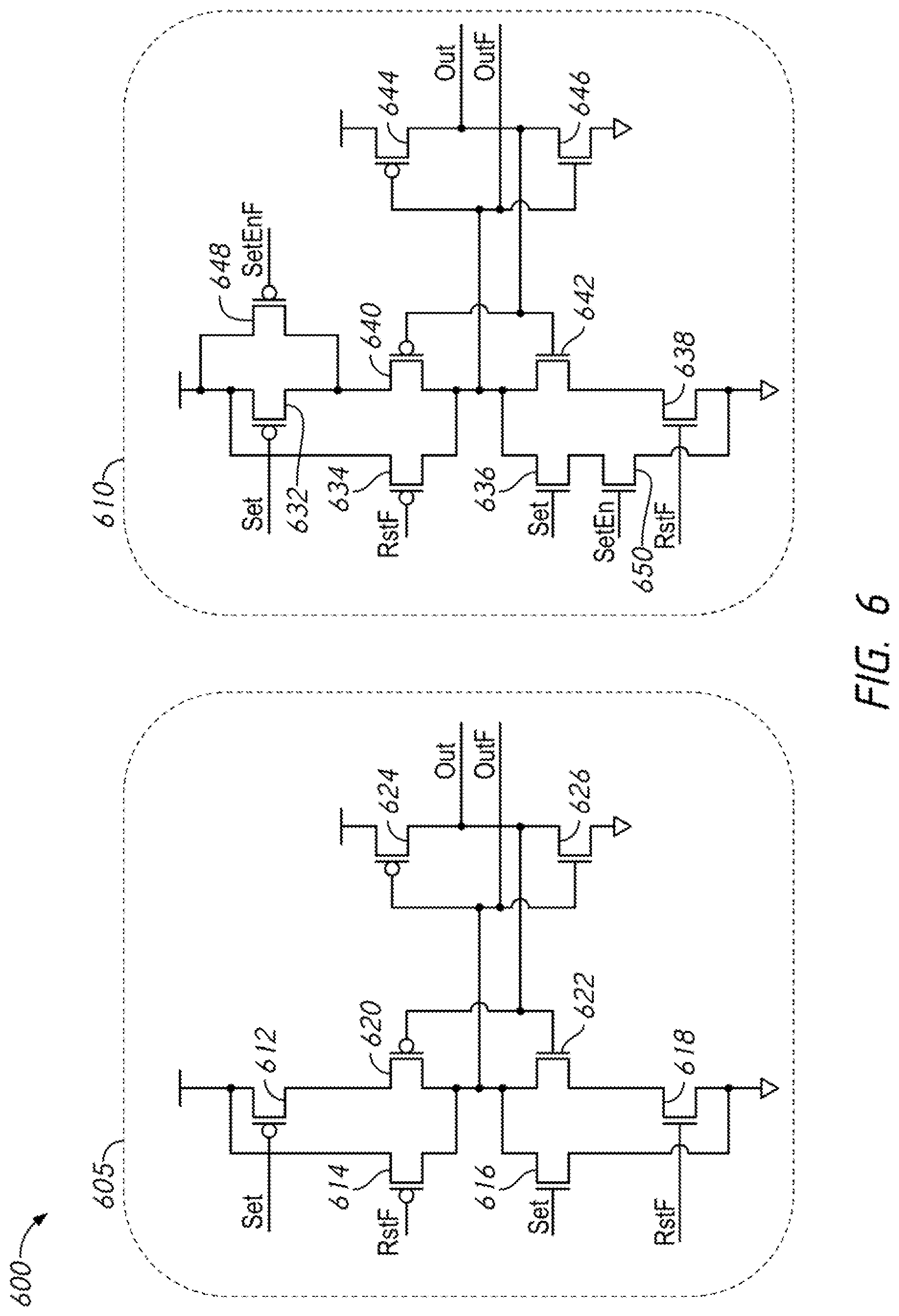

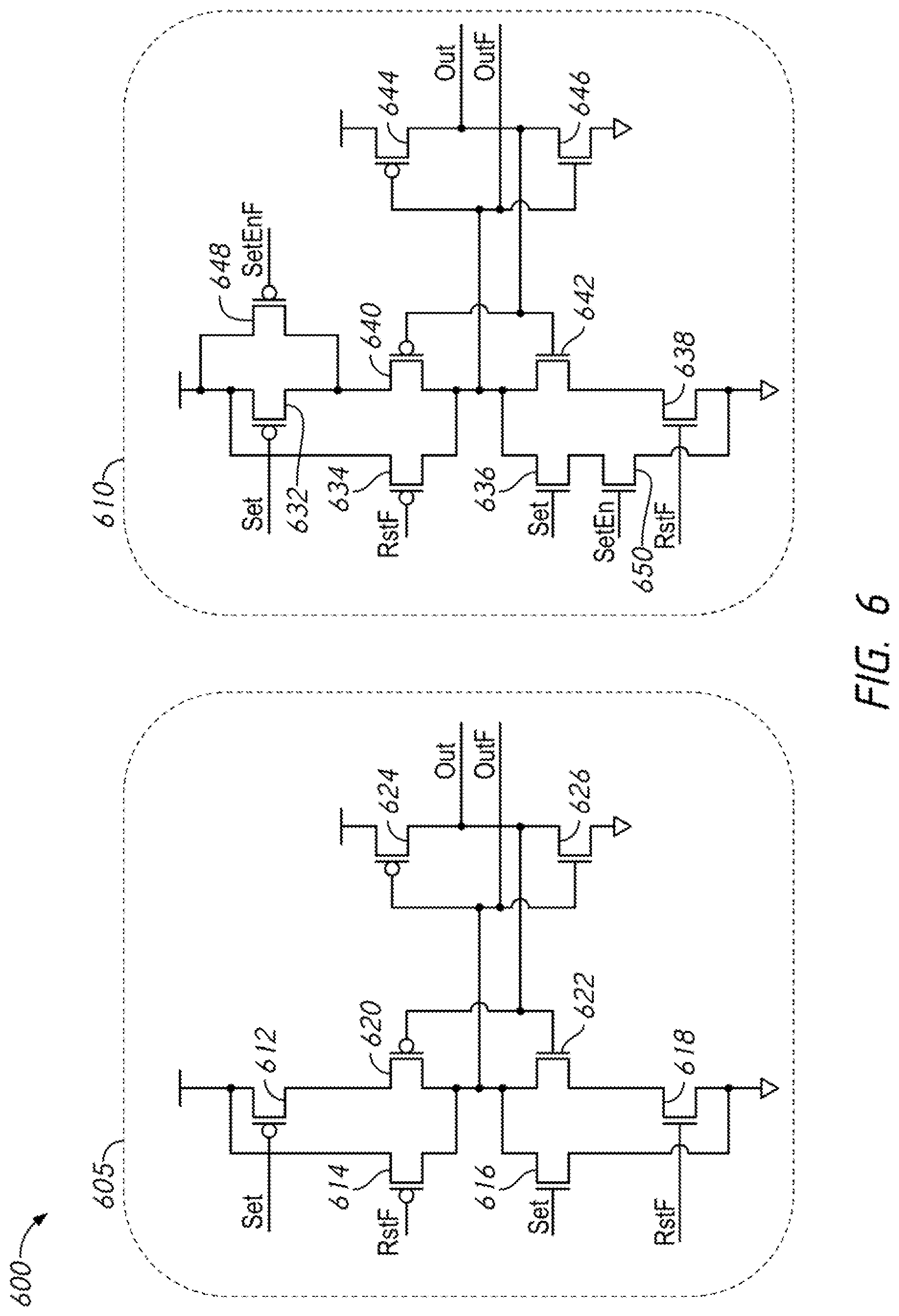

[0008] FIG. 6 is a schematic diagram of a first and second flag latch according to an embodiment of the present disclosure.

[0009] FIGS. 7A-7B are block diagrams of a memory array according to an embodiment of the present disclosure.

[0010] FIG. 8 is a block diagram of a memory array according to an embodiment of the present disclosure.

DETAILED DESCRIPTION

[0011] The following description of certain embodiments is merely exemplary in nature and is in no way intended to limit the scope of the disclosure or its applications or uses. In the following detailed description of embodiments of the present systems and methods, reference is made to the accompanying drawings which form a part hereof and which are shown by way of illustration specific embodiments in which the described systems and methods may be practiced. These embodiments are described in sufficient detail to enable those skilled in the art to practice presently disclosed systems and methods, and it is to be understood that other embodiments may be utilized and that structural and logical changes may be made without departing from the spirit and scope of the disclosure. Moreover, for the purpose of clarity, detailed descriptions of certain features will not be discussed when they would be apparent to those with skill in the art so as not to obscure the description of embodiments of the disclosure. The following detailed description is therefore not to be taken in a limiting sense, and the scope of the disclosure is defined only by the appended claims.

[0012] A memory device may include a plurality of memory cells. The memory cells may store information (e.g., as one or more bits), and may be organized at the intersection of wordlines (rows) and bit lines (columns). A number of wordlines and bit lines may be organized into a memory bank. A memory device may include a number of different memory banks. The memory device may receive one or more command signals which may indicate operations in one or more of the banks of one or more memory packages. The memory device may enter a refresh mode, in which wordlines in one or more of the memory banks are refreshed.

[0013] Information in the memory cells may decay over time. The memory cells may be refreshed on a row-by-row basis to preserve information in the memory cells. During a refresh operation, the information in one or more rows may be rewritten back to the respective rows to restore an initial value of the in information. Repeated access to a given row (e.g., an aggressor row) may cause an increased rate of information decay in one or more neighboring rows (e.g., victim rows). Accesses to different rows of the memory may be tracked in order to determine likely victim rows and refresh them as part of a targeted (or `row hammer`) refresh operation. However, individually tracking every row access with digital counters may be difficult due to space and/or power limitations of the device.

[0014] The present disclosure is drawn to apparatuses, systems, and methods for analog row access tracking. A refresh control circuit may include a number of analog unit cells, each of which includes a number of circuits which are used to track accesses to one or more wordlines of the memory device. Each unit cell may track accesses to a portion of the wordlines, and together the unit cells may track accesses to all wordlines of the memory. When a given wordline is accessed, a stack control circuit may send signals to the unit cell which tracks that wordline. Responsive to those signals, the unit cell may update a voltage (e.g., by increasing an amount of charge on a capacitor). Based on that voltage (e.g., when the voltage crosses a reference voltage), one or more wordlines associated with the unit cell may be flagged for a targeted refresh operation.

[0015] In some embodiments, the refresh control circuit may also include a targeted refresh queue, which may store addresses for refreshing as part of a targeted refresh operation after they have been flagged for refresh by a unit cell. When the voltage in one of the unit cells crosses a threshold level (e.g., a reference voltage), one or more addresses associated with the unit cell may be added to the targeted refresh queue, and the voltage in the unit cell may be reset. In some embodiments, each address in the targeted refresh queue may include one or more priority flags. When the voltage in the unit cell crosses the threshold, if the addresses associated with the unit cell are already in the targeted refresh queue (e.g., when a queue address to be stored matches one of the stored queue addresses), one or more of the priority flags may be set (e.g., the level of the flag may be switched). Addresses in the targeted refresh queue may be refreshed in an order based on the number of priority flags which are set.

[0016] FIG. 1 is a block diagram of a semiconductor device according to an embodiment of the disclosure. The semiconductor device 100 may be a semiconductor memory device, such as a DXADDM device integrated on a single semiconductor chip.

[0017] The semiconductor device 100 includes a memory array 112. In some embodiments, the memory array 112 may include of a plurality of memory banks. Each memory bank includes a plurality of wordlines WL, a plurality of bit lines BL and /BL, and a plurality of memory cells MC arranged at intersections of the plurality of wordlines WL and the plurality of bit lines BL and /BL. The selection of the wordline WL is performed by a row control 108 and the selection of the bit lines BL and /BL is performed by a column control 110. In some embodiments, there may be a row control 108 and column control 110 for each of the memory banks.

[0018] The bit lines BL and /BL are coupled to a respective sense amplifier (SAMP) 117, Read data from the bit line BL or /BL is amplified by the sense amplifier SAMP 117, and transferred to read/write amplifiers 120 over complementary local data lines (LIOT/B), transfer gate (TG) 118, and complementary main data lines (MIO). Conversely, write data outputted from the read/write amplifiers 120 is transferred to the sense amplifier 117 over the complementary main data lines MIO, the transfer gate 118, and the complementary local data lines LIOT/B, and written in the memory cell MC coupled to the bit line BL or /BL.

[0019] The semiconductor device 100 may employ a plurality of external terminals that include command and address (C/A) terminals coupled to a command and address bus to receive commands and addresses, clock terminals to receive clocks CK and /CK, data terminals DQ to provide data, and power supply terminals to receive power supply potentials VDD, VSS, VDDQ, and VSSQ.

[0020] The clock terminals are supplied with external clocks CK and /CK that are provided to a clock input circuit 122. The external clocks may be complementary. The clock input circuit 122 generates an internal clock ICLK based on the CK and /CK clocks. The ICLK clock is provided to the command control 106 and to an internal clock generator 124. The internal clock generator 124 provides various internal clocks LCLK based on the ICLK clock. The LCLK clocks may be used for timing operation of various internal circuits. The internal data clocks LCLK are provided to the input/output circuit 126 to time operation of circuits included in the input/output circuit 126, for example, to data receivers to time the receipt of write data.

[0021] The C/A terminals may be supplied with memory addresses. The memory addresses supplied to the C/A terminals are transferred, via a command/address input circuit 102, to an address decoder 104. The address decoder 104 receives the address and supplies a decoded row address XADD to the row control 108 and supplies a decoded column address YADD to the column control 110. The row address XADD may be used to specify one or more wordlines WL of the memory array 112 and the column address YADD may specify one or more bit lines BL of the memory array 112. The address decoder 104 may also provide a bank address BADD, which specifies a particular bank of the memory. The bank address BADD may be provided to the row control 108 and/or column control 110 to direct access operations to one or more of the banks.

[0022] The row address XADD may include multiple bits. As used herein, the different bits of the row address XADD may be labeled as XADDO-XADDn, where n is the total number of bits of the row address. Accordingly, XADDi may refer to an ith bit of the row address XADD.

[0023] Different subsets of the bits of the row address XADD may be associated with different levels of organization of the memory array 112. For example, a subset of the bits of the row address XADD may be a section address which refers to a section of the memory array 112 containing a number of wordlines and a different subset of the bits of the row address XADD may be a wordline address which refers to a particular wordline within that section. Different arrangements of the row address and wordlines may be used in other embodiments. Although properties and uses of the row address are generally described herein, it should be understood that the column addresses may be organized and used in a similar way in some embodiments.

[0024] The C/A terminals may be supplied with commands. Examples of commands include timing commands for controlling the timing of various operations, access commands for accessing the memory, such as read commands for performing read operations and write commands for performing write operations, as well as other commands and operations. The access commands may be associated with one or more row address XADD, column address YADD, and/or bank address BADD to indicate the memory cell(s) to be accessed.

[0025] The commands may be provided as internal command signals to a command control 106 via the command/address input circuit 102. The command control 106 includes circuits to decode the internal command signals to generate various internal signals and commands for performing operations. For example, the command control 106 may provide a row command signal to select a wordline and a column command signal to select a bit line.

[0026] The device 100 may receive an access command which is a row activation command ACT. When the row activation command ACT is received, a row address XADD is supplied with the row activation command ACT.

[0027] The device 100 may receive an access command which is a read command. When a read command is received, a bank address BADID and a column YADD address are timely supplied with the read command, read data is read from memory cells in the memory array 112 corresponding to the row address XADD and column address YADD. The read command is received by the command control 106, which provides internal commands so that read data from the memory array 112 is provided to the read/write amplifiers 120. The read data is output to outside from the data terminals DQ via the input/output circuit 126.

[0028] The device 100 may receive an access command which is a write command. When the write command is received, a bank address and a column address are timely supplied with the write command, write data supplied to the data terminals DQ is written to a memory cells in the memory array 112 corresponding to the row address and column address. The write command is received by the command control 106, which provides internal commands so that the write data is received by data receivers in the input/output circuit 126. Write clocks may also be provided to the external clock terminals for timing the receipt of the write data by the data receivers of the input/output circuit 126. The write data is supplied via the input/output circuit 126 to the read/write amplifiers 120, and by the read/write amplifiers 120 to the memory array 112 to be written into the memory cell MC.

[0029] The device 100 may also receive commands causing it to carry out refresh operations. A refresh signal AREF may be a pulse signal which is activated when the command control 106 receives a signal which indicates a refresh mode. In some embodiments, the refresh command may be externally issued to the memory device 100. In some embodiments, the refresh command may be periodically generated by a component of the device. In some embodiments, when an external signal indicates a refresh entry command, the refresh signal AREF may also he activated. The refresh signal AREF may he activated once immediately after command input, and thereafter may be cyclically activated at desired internal timing. Thus, refresh operations may continue automatically. A self-refresh exit command may cause the automatic activation of the refresh signal AREF to stop and return to an IDLE state.

[0030] The refresh signal AREF is supplied to a refresh control circuit 116. In some embodiments, there may be a refresh control circuit 116 associated with each bank. The bank address BADD may indicate one or more of the refresh control circuits 116 to be activated. The refresh control circuits 116 may receive the refresh signal AREF in common, and may generate and provide one or more refresh row address(es) RXADD in order to perform one or more refresh operations in the associated memory bank. In some embodiments, a subset of die memory banks may be given refresh commands. For example, one or more additional signals may indicate which of the refresh control circuits 116 should provide refresh address(es) responsive to AREF. In another example, AREF may only be provided to refresh control circuits 116 which are associated with the subset of memory banks which are refreshing.

[0031] Focusing on the operation of a given refresh control circuit, the refresh control circuit 116 supplies a refresh row address RXADD to the row control 108, which may refresh one or more wordlines WL indicated by the refresh row address RXADD. The refresh control circuit 116 may control a timing of the refresh operation based on the refresh signal AREF. In some embodiments, responsive to an activation of AREF, the refresh control circuit 116 may generate one or more activations of a pump signal, and may generate and provide a refresh address RXADD for each activation of the pump signal (e.g., each pump).

[0032] One type of refresh operation may be an auto-refresh operation. Responsive to an auto-refresh operation the memory bank may refresh a group of rows of the memory, and then may refresh a next group of rows of the memory bank responsive to a next auto-refresh operation. The refresh control circuit 116 may provide a refresh address RXADD which indicates a group of wordlines in the memory bank. The refresh control circuit 116 may generate a sequence of refresh addresses RXADD such that over time the auto-refresh operation may cycle through all the wordlines WL of the memory bank. The timing of refresh operations may be such that each wordline is refreshed with a frequency based on a normal rate of data degradation in the memory cells.

[0033] Another type of refresh operation may be a targeted refresh operation. Repeated access to a particular row of memory (e.g., an aggressor row) may cause an increased rate of decay in neighboring rows (e.g., victim rows) due, for example, to electromagnetic coupling between the rows. In some embodiments, the victim rows may include rows which are physically adjacent to the aggressor row. In some embodiments, the victim rows may include rows further away from the aggressor row. Information in the victim rows may decay at a rate such that data may be lost if they aren't refreshed before the next auto-refresh operation of that row. In order to prevent information from being lost, it may be necessary to identify aggressor rows and then carry out a targeted refresh operation where a refresh address RXADD associated with one or more associated victim rows is refreshed.

[0034] In some embodiments, the identified rows may be potential aggressor rows (and/or rows with a higher likelihood of being aggressors) and the targeted refresh operations may be carried out on potential victim rows (and/or rows with a higher likelihood of being victims). For purposes of clarity, the identified rows will be referred to as aggressors and the rows which are refreshed will be referred to as victims, even though the memory may identify aggressor wordlines which are not necessarily being accessed enough to cause an increased rate of data degradation in neighboring rows, and may refresh victim wordlines where an increased rate of data degradation is not necessarily taking place.

[0035] The refresh control circuit 116 may receive the row addresses XADD provided by the address decoder 104 and may determine which wordlines are aggressors based on the row addresses XADD. The refresh control circuit 116 may track accesses to the wordlines based on the row address XADD and may determine which wordlines are aggressors based on an amount of the accesses. The refresh control circuit may divide the total number of wordlines into portions and have an accumulator voltage for each of the portions. For example, a first portion of the wordlines may be associated with a first accumulator voltage, a second portion of the wordlines may be associated with a second accumulator voltage, etc. In some embodiments, the portion of the wordlines associated with the accumulator voltage may be organized into one or more sections of wordlines each of which contain one or more wordlines which are physically adjacent to each other. Each accumulator voltage may be updated any time any of the wordlines in the portion represented by the accumulator voltage is accessed. For example, the accumulator voltage may be increased by increasing the charge on a capacitor in some embodiments. In some embodiments, the accumulator voltage may be decreased by decreasing a charge on the capacitor. In this manner all accesses to all wordlines may be tracked by the accumulator voltages, but there may be fewer count values than the number of total wordlines.

[0036] In some embodiments, wordlines may be grouped together based on the row addresses associated with those wordlines. If only a particular subset of the row address is specified (e.g., a particular value of that subset of bits) then all wordlines which share the specified value of that subset as part of their row address may be identified. For example, each portion of the wordlines tracked by an accumulator voltage may be specified by a particular value of a subset of the row address XADD. If a row address contains a first subset (e.g., a section address) specifying a section of wordlines and a second subset (e.g., a wordline address) specifying a particular wordline within that section, then the wordline address subset of the row address may be ignored, and the refresh control circuit 116 may have an accumulator voltage associated with the value of the section address. Accordingly, the accumulator voltage may be updated anytime any wordline within the section(s) associated with the section address. In some embodiments, the section address may be truncated (e.g., some of the bits of the section address may be ignored) into a multi-section address, which represents all of the wordlines in a number of different sections. Each count value may be specified by a particular value of the grouped section address and may represent accesses to any wordline in any of the sections associated with the multi-section address. It should be understood that a row address XADD may include many subsets describing many different levels of organization, and that examples of a particular way of apportioning the wordlines of the memory array 112 based on the row address are only meant to aid in understanding of the concept. Other methods associating groups of wordlines with a counter value may be used in other embodiments.

[0037] When the refresh control circuit 116 determines that at least one wordline of a portion of the wordlines tracked by an accumulator voltage is an aggressor (e.g., when the accumulator voltage crosses a threshold, such as a reference voltage), one or more victim addresses associated with the portion of the wordlines represented by that accumulator voltage may be provided. In some embodiments where each access increases an accumulator voltage, the refresh control circuit 116 may determine when the accumulator voltage is greater than the reference voltage. In some embodiments, where each access decreases an accumulator voltage, the refresh control circuit 116 may determine when the accumulator voltage is less than the reference voltage. Since each accumulator voltage may represent a number of different wordlines, victim addresses may be provided for each of the wordlines in the group associated with a given accumulator voltage. In addition, victim addresses may be provided for wordlines which are physically nearby (e.g., adjacent to) one of more of the wordlines in the group of wordlines associated with the accumulator voltage. For example, if the group of wordlines is arranged into one or more sections, the victim addresses may be associated with each wordline in the section(s) as well as the wordlines which are nearby to the wordlines at either end of the section(s).

[0038] The refresh control circuit 116 may have a number of accumulator voltages which between them represent accesses to every wordline of the memory array 112. In some embodiments, the refresh control circuit 116 may include a targeted refresh queue which may store addresses for targeted refresh operations. In some embodiments, the targeted refresh queue may store victim addresses. In some embodiments, the targeted refresh queue may store an aggressor address (or a portion of an aggressor address) associated with the portion of the wordlines represented by the accumulator voltage. When an accumulator voltage crosses the threshold (e.g., a reference voltage) an address associated with that accumulator voltage may be added to the targeted refresh queue, and the accumulator voltage may be reset to an initial voltage (e.g., a ground voltage, a system voltage such as VDD, etc.). When there is a refresh command (e.g., AREF, a refresh pump) an address stored in the targeted refresh queue may be selected and one or more victim addresses based on the address in the queue maybe provided as the refresh address RXADD.

[0039] In some embodiments, the memory may perform targeted refresh operations on the victim addresses (e.g., by providing victim addresses based on the targeted refresh queue as the refresh address RXADD) as long as the targeted refresh queue contains at least one unrefreshed address. In some embodiments, if a refresh operation is indicated, but the targeted refresh queue is empty (e.g., contains no addresses and/or contains only addresses which have already had their victims refreshed), an auto-refresh operation may be performed instead. In some embodiments, certain refresh operations may be reserved for targeted refresh operations, and if the targeted refresh queue is empty, no refresh operation may be performed during those reserved operations.

[0040] The targeted refresh queue may include one or more priority flags associated with the addresses stored therein. Each time the accumulator voltage crosses the threshold, if the address(es) associated with that accumulator voltage are already stored in the targeted refresh queue, another priority flag may be set and the accumulator voltage may be reset to an initial level. For example, when a queue address is added to the targeted refresh queue, if the queue address is already in the targeted refresh queue instead of being stored, another priority flag associated with the stored queue address is set. The device 100 may prioritize refreshing addresses in the targeted refresh queue based on the number of priority flags which are set. For example, addresses where more priority flags may be selected for refreshing before addresses where less priority flags are set.

[0041] The power supply terminals are supplied with power supply potentials VDD and VSS. The power supply potentials VDD and VSS are supplied to an internal voltage generator circuit 128. The internal voltage generator circuit 128 generates various internal potentials VPP, VOD, VARY, VPERI, and the like based on the power supply potentials VDD and VSS supplied to the power supply terminals. The internal potential VIPP is mainly used in the row control 108, the internal potentials VOD and VARY are mainly used in the sense amplifiers SAMP included in the memory array 112, and the internal potential VPERI is used in many peripheral circuit blocks.

[0042] The power supply terminals are also supplied with power supply potentials VDDQ and VSSQ. The power supply potentials VDDQ and VSSQ are supplied to the input/output circuit 126. The power supply potentials VDDQ and VSSQ supplied to the power supply terminals may be the same potentials as the power supply potentials VDD and VSS supplied to the power supply terminals in an embodiment of the disclosure. The power supply potentials VDDQ and VSSQ supplied to the power supply terminals may be different potentials from the power supply potentials VDD and VSS supplied to the power supply terminals in another embodiment of the disclosure. The power supply potentials VDDQ and VSSQ supplied to the power supply terminals are used for the input/output circuit 126 so that power supply noise generated by the input/output circuit 126 does not propagate to the other circuit blocks.

[0043] FIG. 2 is a block diagram of a refresh control circuit according to an embodiment of the present disclosure. The refresh control circuit 200 may implement the refresh control circuit 116 of FIG. 1 in some embodiments. The refresh control circuit 200 receives a row address XADD (e.g., from the address decoder 104 of FIG. 1) and the refresh signal AREF, and provides a refresh address RXADD with a timing based on AREF. The refresh address RXADD may either be an auto-refresh address RXADD1 as part of an auto-refresh operation, or a targeted refresh address RXADD2 as part of a targeted refresh operation. The targeted refresh addresses RXADD2 may be determined based on tracking the row addresses XADD over time.

[0044] The refresh control circuit 200 includes a row access tracking stack 230a (and its associated stack control circuit 231a) and a redundant row access tracking stack 230b (and its associated stack control circuit 231b). The row access tracking stack 230a and the redundant row access tracking stack 230b each include a number of unit cells 232 each of which includes a number of circuits which store and update one of the accumulator voltages. While the term stack is used in this disclosure, it should be understood that the stacks 230a-b may represent any form of data storage unit including the unit cells 232 as described herein.

[0045] The redundant row access tracking stack 230b includes unit cells 232 which track accesses to redundant rows of the memory (e.g., rows used in repair operations). Row access tracking stack 230a includes unit cells 232 which track accesses to non-redundant rows of the memory. Since there may generally be more non-redundant rows than redundant rows of memory, the stack 230a may include more unit cells 232 than the stack 230b. The stacks 230a and 230b may generally include similar components and may function in a similar fashion. For the sake of brevity, operation will be described with respect to a generic row access tracking stack 230 and stack control circuit 231.

[0046] The row access tracking stack 230 includes a number of unit cells 232, each of which tracks accesses to a portion of the wordlines of the memory. The row access tracking stack 230 also includes a stack control circuit 231, which includes a number of circuits which are coupled in common to the different unit cells 232. The stack control circuit 231 may be used to provide signals in common to all of the unit cells 232 or to one or more specified unit cells 232. An example stack control circuit, which may be used as the stack control circuit 231 is described in more detail in FIGS. 3-4. An example unit cell which may be used as the unit cell 232 is described in more detail in FIGS. 5-6.

[0047] Each time a row address XADD is received, the stack control circuit 231 may selectively activate one of the unit cells 232 associated with the portion of the wordlines including the wordline represented by the row address XADD. In the embodiment of FIG. 2, the activated unit cell 232 may increase the stored accumulator voltage and the unit cell 232 and stack control circuit 231 may compare the updated accumulator voltage to a reference voltage. Based on that comparison (e.g., when the accumulator voltage is greater than a reference voltage), the row access tracking stack 230 may change the state of a flag signal Flag provided by the unit cell 232. It should be understood that while the embodiments discussed herein may generally refer to increasing the accumulator voltage, in some embodiments, the activated unit cell 232 may decrease the voltage and the stack control circuit 231 may determine if the updated accumulator voltage is less than the reference voltage.

[0048] Responsive to the flag signal Flag of one of the unit cells 232 changing states, a steal address circuit 234 may store addresses in a targeted refresh queue 236 based on the row address XADD. The targeted refresh queue 236 includes a number of files, each of which stores a victim address and one or more priority flags. The steal address circuit 234 may use logic to direct a sampler pointer 235 which indicates which tile of the targeted refresh queue 236 the next address is inserted into. In some embodiments, the steal address circuit 234 may determine victim addresses based on XADD, and the victim addresses may be stored in targeted refresh queue 236. In some embodiments, the steal address circuit 234 may add the row address XADD (or a portion of the bits of the row address XADD) to the targeted refresh queue 236. In embodiments where XADD (or a portion of XADD) is stored in the targeted refresh queue 236, the refresh logic circuit 244 may calculate the victim addresses after receiving the address RXADD2 stored in the targeted refresh queue 236. Details of determining victim addresses are discussed in more detail in FIGS. 7-8.

[0049] In the embodiment of FIG. 2, the targeted refresh queue 236 includes a first priority flag 237 and a second priority flag 238. More or fewer priority flags may be used in other embodiments. When the accumulator voltage in a unit cell 232 rises above the threshold, the unit cell 232 may check the state of the first and the second priority flags 237 and 238. If neither of the priority flags 237, 238 is at a high level (e.g., neither is set), then the steal address circuit 234 may store an address based on the address XADD in the targeted refresh queue 236 at a location (e.g., a file) based on the sample pointer 235. The accumulator voltage may then be reset to an initial level. If the first flag 237 is already at a high level (e.g., indicating that the accumulator voltage previously rose above the reference voltage), the second priority flag 238 may be changed to a high level, and the first priority flag 237 may be kept at a high level. The steal address circuit 234 may only store the address in the targeted refresh queue 236 responsive to the first priority flag 237 changing from a lint state to a second state. Thus, if an address is already located in the targeted refresh queue 236, it will not be loaded a second time.

[0050] A refresh logic circuit 244 provides the refresh address RXADD with a timing based on the refresh signal AREF. The refresh address RXADD may either be an auto-refresh address RXADD1 provided by an auto-refresh address circuit 242 or a targeted refresh address (e.g., one or more victim addresses) based on the address RXADD2 provided by the targeted refresh queue 236. The queue address in the targeted refresh queue 236 to be provided as the address RXADD2 is indicated by a flush pointer 241 which is directed by a flush control circuit 240. The flush control circuit 240 may cause the flush pointer 241 to prioritize files of the targeted refresh queue 236 based on the number of priority flags 237, 238 which are set. Addresses where the first and the second priority flags 237 and 238 are both at the high level may be provided as the targeted refresh address RXADD2 before address where only the first priority flag 237 is at the high level.

[0051] The stack control circuit 231 may receive the row address XADD and provide one of the count values from the row counter stack 230 to the counter logic circuit 234 based on a value of a subset of the bits of the row address XADD. Each of the count values of the row counter stack 230 may be associated with a portion of the wordlines of the memory. Each portion of the wordlines may be specified by a value of the subset of the bits of the row address XADD. Each of the count values may be associated with a particular value of the subset of the bits of the row address. Thus, there may be a first count value for a first value of the subset of the row address, a second count value for a second value of the subset of the row address, etc. If the subset of the row address has N possible values, then the row count stack 230 may be N registers deep.

[0052] The decoder in the stack control circuit 231 may only receive (and/or only pay attention to) a subset of the bits of the row address XADD. In some embodiments, the targeted refresh queue may store the same subset of the row address as the stack 230. In turn, the refresh logic 244 may determine victim addresses based off of that subset of row address. For example, the refresh logic 244 may determine the victim addresses based on a multi-section address including the fourth through thirteenth bits of the row address (e.g., XADD3-XADD12). The refresh logic 244 may provide a number of victim addresses which include victim addresses associated with all of the wordlines represented by the subset of the row address. In some embodiments, each victim address may represent multiple wordlines of the memory, and all of the wordlines represented by a given victim address may be refreshed simultaneously. In some embodiments, the refresh logic 244 may also provide victim addresses which represent wordlines not associated with the portion of the row address. The determination of the victim addresses is discussed in more detail in FIGS. 7-8.

[0053] The targeted refresh queue 236 may be a register stack which stores the queue addresses provided by the steal address circuit 234. Each register of the targeted refresh queue 236 may include a number of bits to store a queue address provided by steal address circuit 234. For example, each register may store a same number of bits as are used by the decoder in the stack control circuit 231 to activate a unit cell 232. In one example, where the decoder is responsive to 10 bits (e.g., XADD3-XADD12), each register of the targeted refresh queue 236 may store 10 bits worth of the row address XADD. In some embodiments, the targeted refresh queue 236 may be, for example, 64 registers deep. Other depths of the targeted refresh queue 236, such as 50 or 100, may be used in other examples.

[0054] Each register of the targeted refresh queue 236 may include a number of priority flags (e.g., first priority flag 237 and second priority flag 238). Each register may include some number of extra bits of storage to contain the priority flags. For example, the priority flags 237-238 may each be single bit, and thus each register may include a bit for the first priority flag 237 and a bit for the second priority flag 238. The flags 237 and 238 may be set (e.g., active) when they are at a high logical level, and not set (e.g., inactive) when at a low logical level. Once a priority flag 237/238 is set, it may generally remain set, until the address in that register is refreshed at which point both of the priority flags 237 and 238 may be reset to an inactive state.

[0055] When a unit cell 232 indicates that a current address XADD should be added to the targeted refresh queue 236, the address (or a portion thereof) may be inserted into the targeted refresh queue 236 at a register indicated by the sample pointer 235. The steal address circuit 234 may monitor the state of the priority flags 237 and 238 and move the sample pointer 235, in part based on the states of the priority flags. In general, the sample pointer 235 may progress through a sequence of the registers (e.g., register(0), register(1), . . . , register(n), register(0), . . . , etc.), but may skip certain registers in the sequence based on the state of their flags.

[0056] In general, the steal address circuit will direct the sample pointer 235 towards registers with less priority flags active. After an address is added to the current location of the sample pointer 235, the sample pointer 235 may move to a next register in the sequence. If the first and the second priority flags 237 and 238 are both at a low level (e.g., inactive), the sample pointer 235 may remain at that location. If the first priority flag 237 is set, but the second priority flag 238 is not set, the sample pointer 235 may skip that register and move to a next register in the sequence. If all of the registers in the targeted refresh queue 236 have the first priority flag 237 set (e.g., after the sample pointer 235 has looped back around), then the sample pointer 235 may remain at the next register with the first priority flag 237 set but not the second priority flag 238. In some embodiments, the steal address circuit 234 may not point to any register which has the second priority flag 238 at a high level. Accordingly, if the sample pointer 235 moves to a register which has the second priority flag 238 at a high level, it may move to the next register. If all of the registers have the second priority flag 238 at a high level, the steal address circuit 234 may not add the address to the targeted refresh queue 236, and may not add any address to the targeted refresh queue 236 until at least one register is refreshed causing its priority flags to be reset to an inactive level.

[0057] The refresh logic circuit 244 provides the refresh address RXADD with a timing based on the signal AREF. In some embodiments, the refresh logic circuit 244 may provide a refresh address RXADD each time there is an occurrence of AREF. In some embodiments, the refresh logic circuit 244 may provide multiple refresh addresses RXADD responsive to each occurrence of AREF. For example, the refresh logic circuit 244 may provide a set number of `pumps` responsive to receiving an occurrence of AREF, and a refresh address RXADD may be provided for each pump.

[0058] Each time the refresh logic circuit 244 provides a refresh address RXADD, either an auto-refresh address RXADD1 or a victim address based on the queue address RXADD2 may be provided as the refresh address RXADD. The auto-refresh address RXADD1 may be provided by an auto-refresh address circuit 242. Each auto-refresh address RXADD1 may be associated with a number of wordlines of the memory. After an auto-refresh address RXADD1 is provided, the auto-refresh address circuit 242 may provide a next auto-refresh address RXADD1 associated with a next group of wordlines in a sequence. The auto-refresh address circuit 242 may provide the auto-refresh addresses RXADD1 in a sequence such that over time all the wordlines of the memory array are refreshed by the auto-refresh addresses RXADD1. After a last auto-refresh address RXADD1 in the sequence is provided, the first auto-refresh address RXADD1 in the sequence may be provided again. In some embodiments, the auto-refresh address circuit 242 may determine the sequence of auto-refresh addresses with internal logic. For example, one or more portions of the auto-refresh address RXADD1 may be incremented after each auto-refresh address RXADD1 is provided to determine a next auto-refresh address RXADD1.

[0059] The flush control circuit 240 may direct a flush pointer 241 which may indicate which register of the targeted refresh queue 236 provides the address stored in the indicated register as the queue address RXADD2. In a manner similar to the sample pointer 235, the flush pointer 241 may generally proceed through a sequence of the registers (e.g., register(0), register(1), . . . , register(n), register(0), . . . , etc.), but may skip certain registers based on the number of priority flags 237 and 238 which are set. In general, the flush control circuit 240 may prioritize directing the flush pointer 241 towards registers with more priority flags 237 and 238 set. It should be noted that the sample pointer 235 and flush pointer 241 may generally move independently of each other.

[0060] The flush control 240 may move at a rate based on a steal rate control signal, which may indicate the rate of targeted refresh operations. In some embodiments, the refresh logic 244 may provide the steal rate control signal. In some embodiments, the refresh logic circuit 244 and the flush control circuit 240 may both receive the steal rate cont ml signal from an external source. In an example operation, when flush pointer 241 moves to a next register, the flush control circuit 240 may check the status of the priority flags 237 and 238. If the second priority flag 238 is active, the flush pointer 241 may remain at that register. If the second priority flag 238 is not active, the flush pointer 241 may move on to a next register, unless none of the registers have the second priority flag 238 active, in which case the flush pointer 241 may stop at the next register where the first priority flag 237 is active but the second priority flag 238 is not. If none of the registers in the targeted refresh queue 236 have either of the priority flags 237-238 active, then no address may be provided as the queue address RXADD2.

[0061] In some embodiments, the refresh logic circuit 244 may determine whether to provide an auto-refresh address RXADD1 of an address based off a queue address RXADD2 based on the state of the targeted refresh queue 236. For example, the refresh logic circuit 211 may provide targeted refresh addresses (e.g., victim addresses) as long as an address RXAOD2 is being provided by the targeted refresh queue 236 and may provide the auto-refresh address RXADD1 as the refresh address RXADD if no address RXADD2 is being provided. In some embodiments, the refresh logic circuit 244 may provide victim addresses based on the address RXADD2 at a rate determined by the steal rate control signal, and if no address RXADD2 is available, those refresh operations may be skipped.

[0062] FIG. 3 is a block diagram of a row access tracking stack according to an embodiment of the present disclosure. The row access tracking stack 300 may, in some embodiments, be included in the row access tracking stack 230 of FIG. 2. The row access tracking stack 300 includes a number of different unit cells 348, which may, in some embodiments, implement the unit cells 232 of FIG. 2. The row access tracking stack 300 also includes various components, such as the decoder circuit 346, comparator circuit 350, pulse generator circuit 352, and sink circuit 354 which may, in some embodiments, be included in the stack control circuit 231 of FIG. 2.

[0063] The decoder circuit 346 receives a row address XADD and provides a select signal Sel to one of the unit cells 348. The stack 300 includes a number of different unit cells 348, each of which may be numbered from unit cell(0) to unit cell(n). Each unit cell 348 may be activated by a select signal Sel(0) to Sel(n). The decoder circuit 346 may provide a select signal Sel(i) to the unit cell(i) based on the value of the received row address XADD. The select signal Sel(i) may be provided at a high voltage (e.g., a system voltage such as VDD or VPERI) and the other select signals (e.g., Sel(0 to i-1) and Sel(i+1 to n)) may be provided at a low voltage (e.g., a ground voltage such as VSS).

[0064] For example, in some embodiments the row address XADD may be 17 bits long to represent 2{circumflex over ( )}17 total wordlines in a bank (not including the redundant wordlines). The fourth through sixteenth bits (e.g., XADD3-16) may be a section address which represents a particular section of the memory, with each section containing 8 wordlines, which are addressed by the first through third bits (e.g., XADD0-XADD2) as a wordline address. The decoder circuit 346 may group some of the sections together by ignoring some of the bits of the section address, which may be considered to be a multi-section address. For example the decoder circuit 346 may only pay attention to a multi-section address including the fourth through thirteenth bits of the row address (e.g., XADD3-XADD12) such that each multi-section address represents sixteen of the sections. Each unit cell 348 may therefore be associated with a value of the multi-section address (e.g., XADD3-XADD12). Thus the row access tracking stack 300 may include 1024 unit cells (e.g., n=1023), one for each of the values of the multi-section address XADD3-XADDI2 (e.g., 2{circumflex over ( )}10 total values). Each unit cell 348 in such a stack 300 may represent eight wordlines (since the wordline address is ignored) in each of 16 different sections of the memory (since the section address is truncated into a multi-section address). Thus, in this example embodiment, each unit cell is tracking accesses to 128 total wordlines. Different organizations of the memory and the row address may be used in other examples. In other embodiments, the row address may have more (or fewer) bits to represent more or fewer wordlines of a memory.

[0065] When a unit cell 348 receives its associated select signal Sel at a high level, the unit cell 348 may be activated. When a given unit cell 348 is activated, it may increase an accumulator voltage on a capacitor in the unit cell 348.

[0066] Each of the unit cells 348 may be coupled in common to a comparator circuit 350. Each of the unit cells 348 may include a comparator portion which is coupled to voltages MirLeft and MirRight provided by the comparator circuit 350. The voltages MirLeft and MirRight may be coupled in common to the comparator portions in each of the unit cells 348. Each unit cell 342 is also coupled in common to a sink circuit 354, which may generate a sink current iSink, which drains from the unit cell 348 to the sink circuit 354. When a unit cell 348 is activated by the select signal Sel it may couple the comparator portion in that unit cell 348 between the voltages MirLeft and MirRight and the sink current iSink. A first current may flow from the voltage MirLeft to the sink, and the magnitude of the first current may be based on the reference voltage, and a second current may flow from MirRight to the sink, with the second current having a magnitude based on the accumulator voltage in that unit cell 348. The comparator circuit 350 may provide a trigger signal Trig based on the relative levels of the first and the second currents.

[0067] The pulse generator circuit 352 receives the signal Trig from the comparator circuit 350 and provides trigger signals TrigPulse0 and TrigPulse1. The lust trigger signal TrigPulse0 may be provided at a first time, and the second trigger signal TrigPulse1 may be provided at a second time. The first and second trigger signals TrigPulse0 and TrigPulse1 may be provided to the unit cells 348.

[0068] The unit cell 348 which is receiving the select signal Sel (e.g., the unit cell 348 which is active) may send one or more flag signals (e.g., signal Flag of FIG. 2) based on the current states of the flag signals, and the first and the second trigger signals TrigPulse0 and TrigPulse1. The unit cell 348 may include a flag logic circuit which determines when to change the states of the flag signals.

[0069] Each unit cell may also be coupled in common to a number of control signals Control, which may be used to manage the operation of the different components of the stack 300. For example, the control signals may include signals such as a bias voltage pBias, a reference voltage VRef, a flag reset signal FlushEn, and a voltage reset signal DisChgEn. In some embodiments, the bias voltage pBias may be provided by the sink circuit 354, and may be an adjustable voltage. The pulse generator circuit 352 may receive an activation signal (e.g., Act of FIG. 1) and provide a signal ActPulse responsive to the activation signal. The pulse generator circuit 352 may provide additional control signals such as ActPulse, TrigPulse0, and TrigPulse1. In general, the different control signals may be provided in common to each of the unit cells 348, and the select signal Sel may determine which unit cell 348 is active and responds to the various control signals.

[0070] The voltage reset signal DisChgEn may be provided by a discharge logic circuit 353. The voltage reset signal DisChgEn may be provided at a high logical level to cause the accumulator voltages in the unit cell(s) 348 specified by the select signal Sel to reset to an initial level (e.g., a ground voltage). The voltage reset signal DisChgEn may be provided in common to all of the unit cells 348. In the embodiment of FIG. 3, the discharge logic circuit 353 may work with the decoder 346 to provide the select signals to determine which of the unit cells 348 are reset. In some embodiments (not shown), the discharge logic circuit 353 may also provide the select signal Sel (e.g., in addition to the decoder 346), and use one or more signals along with internal logic to determine when to provide the signal DisChgEn, and what value of the select signal Sel to provide.

[0071] The discharge logic circuit 353 may provide the signals DisChgEn to the unit cells 348 specified by the select signal Sel responsive to several different conditions. For example, each time the signal FlushEn is received at a high level, the discharge logic circuit 353 may provide the signal DisChgEn at a high level. Since the signal FlushEn may generally indicate that a wordline associated with a unit cell 348 has been refreshed, and since the signal Sel may still indicate which unit cell 348 has been refreshed, the discharge logic circuit 353 may cause the accumulator voltage in the unit cell 348 to reset when the wordlines associated with that unit cell are refreshed. The discharge logic circuit may also reset a unit cells 348, each time a new priority flag associated with that unit cell is set (e.g., as indicated by the signals TrigPulse0 or TrigPulse1). In other words, each time a given unit cells 348 accumulator voltage rises above the threshold (e.g., reference voltage Vref), the discharge logic circuit 353 may reset the accumulator voltage in that unit cell 348. Accordingly, responsive to receiving TrigPulse0 or TrigPulse1 at a high logical level, the discharge logic circuit 353 may provide the signals DisChgEn at a high logical level. The discharge logic circuit 348 may also provide the signal DisChgEn at a high logical level each time the refresh signal AREF is received.

[0072] In some situations, the discharge logic circuit 353 may cause all of the unit cells 348 to reset (e.g., by providing the signal DisChgEn at the same time a select signal is provided to all of the unit cells 348). For example, when the system is initialized (e.g., in response to a power up, responsive to a system reset, etc.). For example, the discharge logic circuit 353 may receive a signal PwrUp which indicates if the system is powered up or not. If the system is not powered up, the signal PwrUp may be at a low logical level, and the discharge logic circuit 353 may provide the signal DisChgEn at a high logical level which indicates if the system is powered up or not. If the system is not powered up, the signal PwrUp may be at a low logical level, and the discharge logic circuit 353 may provide the signal DisChgEn at a high logical level.

[0073] FIG. 4 is a schematic diagram showing a stack control circuit according to an embodiment of the present disclosure. The stack control circuit 400 includes a decoder 446, a comparator circuit 450, a pulse generator circuit 452, and a sink circuit 454. These may, in some embodiments, be included in the decoder 346, comparator circuit 350, pulse generator circuit 352, and sink circuit 354, respectively, of FIG. 3. Also shown in FIG. 4 is a comparator portion 470 of a unit cell (e.g., unit cell 348 of FIG. 3) to help demonstrate the operation of the comparator circuit 450 and sink circuit 454. The comparator portion 470 may be repeated in each of the unit cells (e.g., the unit cells 232 of FIG. 2 and/or 348 of FIG. 3).

[0074] The decoder 446 receives the row address XADD and provides a select signal Sel. In some embodiments, the signal Sel may be a multi-bit signal, with each of the bits of the signal Sel provided to a different one of the unit cells. Each bit of the signal Sel may be associated with a value of a subset of bits of the row address XADD. There may be a unit cell for each value of the subset of bits of the row address, and together the unit cells may represent all values of the subset of bits. For example, the decoder 446 may monitor the fourth through thirteenth bits of the row address XADD (e.g., XADD<12:3> which may have 1024 different values. Accordingly, there may be 1024 different unit cells and 1024 different select bits (e.g., Sel<1023:0>).

[0075] When a row address XADD is received, the bit of the select signal Sel associated with that row address XADD may be provided at a high level (e.g., a system voltage such as VPERI). In some embodiments, the bit of the select signal Sel may be provided at a high level for a set period of time after the row address XADD is received. In some embodiments, the bit of the select signal Sel may be provided at a high level as long as the current row address XADD is received.

[0076] Responsive to an associated bit of the select signal Sel being at a high level, the comparator circuit 450 and sink circuit 454 may work together with the comparator portion 470 of the unit cell activated by the bit of the select signal Sel to compare an accumulator voltage CapNode of that unit cell to a reference voltage Vref.

[0077] The sink circuit 454 includes a first transistor 462 with a source coupled to a system voltage (e.g., VPERI or VSS) and a gate and sink coupled to a bias voltage pBias. The first transistor 462 may be a p-type transistor. The bias voltage pBias is also coupled to a ground voltage (e.g., VSS) through a resistor 463. A current I may flow from the first transistor 462 through the resistor 463. The resistor 463 may be an adjustable resistor in some embodiments and may be used to adjust a size of the current I and a level of the bias voltage pBias. In some embodiments, the current I may be about 0.5 .mu.A. Other values for the current I may be used in other examples.

[0078] The sink circuit 454 also includes a second transistor 464, which has a gate coupled to the bias voltage pBias, a source coupled to a system voltage, and a drain coupled to a node 465. The second transistor 464 may be a p-type transistor. The sink circuit 454 also includes a third transistor, with a drain and gate coupled in common to the node 465 and a source coupled to a ground voltage (e.g., VSS). The third transistor 466 may be an n-type transistor. The first, second, and third transistors, 462, 464, and 465, along with the resistor 463 may act as a current mirror, and the current I may also flow fro n the second transistor 464 towards the third transistor 466.

[0079] The sink circuit 454 also includes a fourth transistor 467, which is has a drain coupled to an output of the comparator portion 470, a source coupled to a ground voltage, and a gate coupled to the node 465. The fourth transistor 467 may cause a current iSink to flow through the fourth transistor 467 to the ground voltage when one of the coupled comparator portions 470 is active. The sink current iSink may have a larger magnitude than the current I. In some embodiments, the sink current iSink may be about 8 .mu.A.

[0080] The comparator circuit 450 includes a first transistor 455 with a source coupled to a system voltage (e.g., VSS or VPERI) and a gate and drain coupled in common to a node 459. The first transistor 455 may be a p-type transistor. The comparator circuit 450 also includes a second transistor 456 with a source coupled to the system voltage, a gate coupled to the node 459, and a drain coupled to a voltage MirLeft. The second transistor 456 may be a p-type transistor. The comparator circuit 450 also includes a third transistor 457 and a fourth transistor 458. The third transistor 457 has a source coupled to the system voltage and a gate and source coupled in common to a voltage MirRight. The fourth transistor 458 has a source coupled to a system voltage, a gate coupled to the voltage MirRight, and a drain coupled to an output of the comparator 450. The third and fourth transistor 457 and 458 may be p-type transistors. The comparator circuit 450 also includes a fifth transistor 460 and a sixth transistor 461. The fifth transistor 460 has a drain and gate coupled in common to the node 459 and a source coupled to a ground voltage (e.g., VSS). The sixth transistor 461 has a gate coupled to the node 459, a source coupled to the ground voltage, and a drain coupled to the output of the comparator circuit 450. The fifth and sixth transistors 460 and 461 may be n-type transistors.

[0081] The first, second, and fifth transistors, 455, 456, and 460 may work together as a first current mirror, and the third, fourth, and sixth transistors 457, 458, and 461 may work together as a second current mirror. In general, the more current is allowed to flow from the voltage MirLeft through the comparator portion 470 to the sink circuit 454, the lower the voltage on the sixth transistor 461, and the more active the sixth transistor 461 is. The more current is allowed to flow from the voltage MirRight through the comparator portion 470 to the sink circuit 454, the more active the fourth transistor 458 is. Depending on which of the fourth or sixth transistors 458 and 461 are more active, the output of the comparator circuit 450 may be more strongly coupled to a system voltage through the fourth transistor 458 or more strongly coupled to the ground voltage through the sixth transistor 461. Accordingly, if more current flows from the voltage MirLeft, than from the voltage MirRight, then the output of the comparator portion 450 may be a around voltage. If more current flows from the voltage MirRight than from the voltage MirLeft then the output of the comparator portion 450 may be a system voltage (e.g., a high voltage).

[0082] The comparator portion 470 may control how much current flows from the voltages MirLeft and MirRight to the sink circuit 454. Only a single comparator portion 470 is shown, however there may be a comparator portion 470 for each unit cell, all coupled in common to the voltage MirLeft and MirRight and also the sink current iSink. The comparator portion 470 includes a first transistor 475, a second transistor 477 and a third transistor 476. All three of the transistors 475-477 may be n-type transistors. The first transistor 475 has a drain coupled to the voltage MirLeft and a gate coupled to the reference voltage Vref. The second transistor 477 has a drain coupled to the voltage MirRight and a gate coupled to the accumulator voltage CapNode<i> for the unit cell(i). The first and second transistors 475 and 477 have sources coupled in common to the drain of the third transistor 476. The third transistor 476 has a source coupled to the sink current iSink provided by the sink circuit 454 and a gate coupled to a bit of the select signal Sel<i> associated with the unit cell(i) including the comparator portion 470.

[0083] When the bit of the select signal Sel<i> is at a high level, the third transistor 476 may be active, and may couple the sources of both the first transistor 475 and the second transistor 477 to the current iSink. A current may flow from the voltage MirLeft through the first transistor 475 to the current iSink proportional to how high the reference voltage Vref is. A current may flow from the voltage MirRight through the second transistor 477 to the current iSink proportional to how high the accumulator voltage CapNode<i> is. Accordingly, if the accumulator voltage CapNode<i> is higher than the reference voltage Vref, then more current may flow from MirRight than MirLeft, and the output of the comparator circuit 450 may be a high level (e.g., a system voltage).

[0084] The pulse generator circuit 452 includes a buffer circuit 469 with an input terminal coupled to the output of the comparator circuit 450 and an output terminal which provides a trigger signal Trig. When the input of the buffer circuit 469 rises to a high level (e.g., because the voltage CapNode rises above the voltage Vref), the signal Trig may switch from a low level to a high level. The first rising pulse generator 472 has an input terminal coupled to the signal Trig, and an output terminal which provides the signal TrigPulse0. Responsive to a rising edge of the signal Trig (e.g., when the signal Trig transitions from a low level to a high level), the first rising pulse generator 472 may provide a first trigger pulse TrigPulse0. The first trigger pulse Triguise0 may be a pulse, where a signal transitions from a low level to a high level, remains at the high level for a set length of time (generally short relative to the time between pulses) and then transitions back to a low level. The pulse generator circuit 452 also includes a delay circuit 473 with an input terminal coupled to the signal TrigPulse0. The delay circuit 473 receives the signal TrigPulse0 at a first time, and then provides the signal TrigPulse1 at a second time after the first time.

[0085] The pulse generator circuit 452 may also include a second rising pulse generator 468 which has an input terminal coupled to the activation signal Act. When there is a rising edge of the activation signal Act, the second rising pulse generator 468 may provide a pulse of the signal ActPulse. The width of each pulse of ActPulse (e.g., how long ActPulse is at a high level) may be adjustable. The signals TrigPulse0, TrigPulse1 and ActPulse may be provided in common to the unit cells.

[0086] FIG. 5 is a schematic diagram of a unit cell according to an embodiment of the present disclosure. The unit cell 500 may, in some embodiments, be included in the unit cell 232 of FIG. 2 and/or the unit cell 348 of FIG. 3. The unit cell 500 includes an accumulator circuit 505, a comparator portion 510, and a flag logic circuit 515. The comparator portion 510 may generally be similar to the comparator portion 470 of FIG. 4, and the transistors 540-544 may generally be similar to the transistors 475-477 of FIG. 4. For the sake of brevity, the comparator portion 510 will not be described in detail again.

[0087] The accumulator circuit 505 stores a voltage CapNode based on the charge on a capacitor 530. Responsive to a select signal and an activation signal, the Voltage CapNode may be increased by adding charge to the capacitor 530. The accumulator circuit includes a NAND gate 516, which has an input terminal coupled to the signal ActPulse (e.g., from the pulse generator 468) based on the signal Act, indicating an access operation. The other input terminal of the NAND gate 516 is coupled to the bit of the select signal Sel associated with the unit cell 500. Accordingly, when both ActPulse and Sel are at a high level, it indicates that as part of an access operation, an address was received associated with the portion of the wordlines associated with the unit cell 500. The NAND gate 516 provides a signal Act1F to an inverter circuit 518, which provides a signal Act1. The signals Act1F and Art1 may be complimentary to each other and have opposite logical levels.

[0088] The accumulator circuit 505 includes a first transistor 520, which has a source coupled to a system voltage (e.g., VDD, VPERI) and a drain coupled to a voltage chargeLine. The gate of the first transistor 520 is coupled to the bias voltage pBias, which is provided by the sink circuit (e.g., sink circuit 454 of FIG. 4). The first transistor 520 may be a p-type transistor. The bias voltage pBias may be adjustable (e.g., by adjusting the resistance of resistor 463 of FIG. 4), which may control how much charge is added to the capacitor 530 (e.g., by controlling how much current flows through the first transistor 520) each time the signals Sel and ActPulse are received at a high level.

[0089] The accumulator circuit 505 includes a second transistor 522 and a third transistor 524 which are activated to couple the voltage chargeLine to the voltage CapNode, increasing the charge on the capacitor. The second transistor 522 has a source coupled to the voltage charge line and a drain coupled to the voltage CapNode. The gate of the second transistor 522 is coupled to the signal Act1F, which is at a low level when the signals ActPulse and Sel are both high. The second transistor 522 may be a p-type transistor. The third transistor 524 has a source coupled to the voltage chargeLine, a drain coupled to the voltage CapNode, and a gate coupled to the signal Act1, which is at a high level when Act1F is at a low level. The third transistor 524 may be an n-type transistor.

[0090] The voltage CapNode is coupled to ground through a capacitor 530. Accordingly, when the signal Act1F is at a low level and the signal Act1 is at a high level, then the second and the third transistors 522, 524 may be active and current may flow from the voltage chargeLine to the voltage CapNode, which may add charge to the capacitor 530, increasing the voltage CapNode. The amount that the voltage CapNode is increased responsive the signals ActPulse and Sel (e.g., the step size) may be based, in part, on the voltage pBias and the width of the signal ActPulse. In some embodiments, the voltage pBias may be adjusted by adjusting the resistance of the resistor 463 of FIG. 4. In some embodiments, the width of the signal ActPulse may be adjusted by changing a setting of the pulse generator circuit (e.g., by changing a control signal of the rising pulse generator 468 of FIG. 4). The step size may also depend, in part, on a capacitance of the capacitor 530. In some embodiments, it may be desirable to use a capacitor 530 with a relatively large capacitance. For example, in some embodiments, the capacitor 530 may be an switched capacitor or a crown capacitor to achieve a high capacitance in a relatively small layout area. In some embodiments, the step size may be kept small, to limit unintended couplings, such as a parasitic capacitance on the voltage chargeLine. For example, in some embodiments, the step size may be about 1 mV. Other step sizes may be used in other examples. In some embodiments, additional steps may be taken, such as minimizing the length of the conductive element carrying the voltage chargeLine.

[0091] In some embodiments, the accumulator circuit 505 may also include an optional fourth transistor 526 and fifth transistor 528. The fourth transistor 526 may have a drain coupled to the voltage CapNode, a gate coupled to the signal Act1 and a source which is floating (e.g., not coupled to any component or signal of the accumulator circuit 505). The fourth transistor 526 may be a p-type transistor. The fifth transistor 528 may have a drain coupled to the voltage CapNode, a gate coupled to the signal Act1F, and a source which is floating. The fifth transistor 528 may be an n-type transistor. The fourth and fifth transistors 526, 528 may activate at the same time as the second and third transistors 522, and 524 and may help to limit the decoupling impact of the transistors 522 and 524 switching on the voltage CapNode.