Transversely-excited Film Bulk Acoustic Resonator

Turner; Patrick ; et al.

U.S. patent application number 16/998300 was filed with the patent office on 2020-12-03 for transversely-excited film bulk acoustic resonator. The applicant listed for this patent is Resonant Inc.. Invention is credited to Charles Chung, Mike Eddy, Andrew Kay, Patrick Turner, Ventsislav Yantchev.

| Application Number | 20200382101 16/998300 |

| Document ID | / |

| Family ID | 1000005030802 |

| Filed Date | 2020-12-03 |

View All Diagrams

| United States Patent Application | 20200382101 |

| Kind Code | A1 |

| Turner; Patrick ; et al. | December 3, 2020 |

TRANSVERSELY-EXCITED FILM BULK ACOUSTIC RESONATOR

Abstract

Acoustic resonator devices and filters are disclosed. A piezoelectric plate is attached to a substrate, a portion of the piezoelectric plate forming a diaphragm spanning a cavity in the substrate. A first conductor pattern is formed on a surface of the piezoelectric plate. The first conductor pattern includes interleaved fingers of an interdigital transducer disposed on the diaphragm, and a first plurality of contact pads. A second conductor pattern is formed on a surface of a base, the second conductor pattern including a second plurality of contact pads. Each pad of the first plurality of contact pads is directly bonded to a respective pad of the second plurality of contact pads. A ring-shaped seal is form between a perimeter of the piezoelectric plate and a perimeter of the base.

| Inventors: | Turner; Patrick; (San Bruno, CA) ; Eddy; Mike; (Santa Barbara, CA) ; Kay; Andrew; (Irvine, CA) ; Yantchev; Ventsislav; (Sofia, BG) ; Chung; Charles; (San Francisco, CA) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 1000005030802 | ||||||||||

| Appl. No.: | 16/998300 | ||||||||||

| Filed: | August 20, 2020 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 16841134 | Apr 6, 2020 | |||

| 16998300 | ||||

| 62830258 | Apr 5, 2019 | |||

| 62881749 | Aug 1, 2019 | |||

| 62904416 | Sep 23, 2019 | |||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H03H 9/1085 20130101; H03H 9/02228 20130101; H03H 9/6406 20130101; H03H 9/105 20130101; H03H 9/02992 20130101; H03H 9/25 20130101; H03H 9/586 20130101 |

| International Class: | H03H 9/25 20060101 H03H009/25; H03H 9/58 20060101 H03H009/58; H03H 9/10 20060101 H03H009/10; H03H 9/64 20060101 H03H009/64; H03H 9/02 20060101 H03H009/02 |

Claims

1. A method of fabricating an acoustic resonator device, comprising: fabricating an acoustic resonator chip, comprising: bonding a back surface of a piezoelectric plate to a substrate; forming a cavity in the substrate such that a portion of the piezoelectric plate forms a diaphragm spanning the cavity; and forming a first conductor pattern as one or more conductor layers on a front surface of the single-crystal piezoelectric plate, the first conductor pattern including: an interdigital transducer (IDT), interleaved fingers of the IDT are disposed on the diaphragm, and a first plurality of contact pads; forming a second conductor pattern on a back surface of a base, the second conductor pattern including: a second plurality of contact pads; attaching the back surface of the base to the front surface of the piezoelectric plate by directly bonding each contact pad of the first plurality of contact pads to a respective contact pads of the second plurality of contact pads; and forming a ring-shaped seal between a perimeter of the piezoelectric plate and a perimeter of the base.

2. The method of claim 1, wherein the cavity is a hole passing through a thickness of the substrate, and the method further comprises bonding a cap to a back surface of the substrate.

3. The method of claim 1, wherein the first conductor pattern further includes a first conductor ring about the perimeter of the piezoelectric plate, the second conductor pattern further includes a second conductor ring about the perimeter of the base, and forming a ring-shaped seal comprises directly bonding the first conductor ring to the second conductor ring.

4. The method of claim 1, wherein forming a ring-shaped seal further comprises: applying a ring of adhesive material around one or both of a perimeter of the piezoelectric plate and a perimeter of the base; and curing the adhesive material after or concurrent with directly bonding the first plurality of contact pads to the second plurality of contact pads.

5. The method of claim 1, wherein the method further comprises forming vias to connect the second plurality of contact pads to a third plurality of contact pads formed on the front surface of the base.

6. The method of claim 1, further comprising: prior to attaching the base to the piezoelectric plate, forming a recess in the back surface of the base, the recess located in an area of the back surface of the base that will face the diaphragm.

7. The method of claim 6, wherein forming a recess in the back surface of the base further comprises: forming a recess having a depth such that, after attaching the base to the piezoelectric plate, a distance from a bottom of the recess to the diaphragm is greater than or equal to 15 microns and less than or equal to 100 microns.

8. The method of claim 1, wherein the acoustic resonator device is a bandpass filter; forming a cavity in the substrate comprises forming a plurality of cavities such that a plurality of portions of the piezoelectric plate form a corresponding plurality of diaphragms spanning respective cavities of the plurality of cavities; and the first conductor pattern includes a plurality of IDTs, interleaved fingers of each IDT disposed on a respective diaphragm of the plurality of diaphragms.

9. The method of claim 1, wherein the method further comprises forming vias to connect the second plurality of contact pads to a third plurality of contact pads formed on the front surface of the base; and wherein the base is silicon and the vias are through-silicon-vias (TSVs).

10. The method of claim 1, wherein the IDT and piezoelectric plate are configured such that a radio frequency signal applied to the IDT excites a bulk shear acoustic wave in the diaphragm.

11. A method of fabricating an acoustic resonator device, comprising: fabricating an acoustic resonator chip, comprising: bonding a back surface of a piezoelectric plate to a substrate; forming a cavity in the substrate such that a portion of the piezoelectric plate forms a diaphragm spanning the cavity; and forming a first conductor pattern as one or more conductor layers on a front surface of the single-crystal piezoelectric plate, the first conductor pattern including: an interdigitated transducer (IDT) comprising two bus bars and interleaved fingers, the interleaved fingers of the IDT disposed on the diaphragm, the piezoelectric plate and IDT configured so that a radio frequency or microwave signal applied between the two busbars excites a bulk shear acoustic wave within the diaphragm; and a first plurality of contact pads; forming a second conductor pattern on a back surface of a base of an interposer, the second conductor pattern including: a second plurality of contact pads; attaching the back surface of the base to the front surface of the piezoelectric plate by directly bonding each contact pad of the first plurality of contact pads to a respective contact pads of the second plurality of contact pads; and forming a ring-shaped seal between a perimeter of the piezoelectric plate and a perimeter of the base.

12. The method of claim 11, wherein the first conductor pattern further includes a first conductor ring about the perimeter of the piezoelectric plate, the second conductor pattern further includes a second conductor ring about the perimeter of the base, and forming a ring-shaped seal comprises directly bonding the first conductor ring to the second conductor ring.

13. The method of claim 11, wherein the interposer further comprises through-silicon-vias (TSVs) connecting the second plurality of contact pads to a third plurality of contact pads formed on the front surface of the base; and the base is silicon.

14. The method of claim 11, further comprising: prior to attaching the base to the piezoelectric plate, forming a recess in the back surface of the base, the recess located in an area of the back surface of the base that will face the diaphragm; and wherein forming a recess in the back surface of the base further comprises forming a recess having a depth such that, after attaching the base to the piezoelectric plate, a distance from a bottom of the recess to the diaphragm is greater than or equal to 15 microns and less than or equal to 100 microns.

15. The method of claim 11, wherein the acoustic resonator device is a bandpass filter; forming a cavity in the substrate comprises forming a plurality of cavities such that a plurality of portions of the piezoelectric plate form a corresponding plurality of diaphragms spanning respective cavities of the plurality of cavities; and the first conductor pattern includes a plurality of IDTs, interleaved fingers of each IDT disposed on a respective diaphragm of the plurality of diaphragms.

16. A method of fabricating a filter device, comprising: fabricating an acoustic resonator chip, comprising: bonding a back surface of a piezoelectric plate to a substrate; forming one or more cavities in the substrate such that a portion of the piezoelectric plate forms a diaphragm spanning the cavities; and forming a conductor pattern on a front surface of the single-crystal piezoelectric plate, the conductor pattern including: a plurality of interdigitated transducer (IDTs) of a respective plurality of resonators and a first plurality of contact pads; wherein interleaved fingers of each of the plurality of IDTs are disposed on respective portions of the piezoelectric plate suspended over the one or more cavities; depositing a first thickness of a first dielectric layer between the fingers of the IDT of a first resonator of a respective plurality of resonators; and depositing a second thickness of a second dielectric layer between the fingers of the IDT of a second resonator of a respective plurality of resonators; and forming a second conductor pattern on a back surface of a base of an interposer, the second conductor pattern including: a second plurality of contact pads; and attaching the back surface of the base to the front surface of the piezoelectric plate by directly bonding each contact pad of the first plurality of contact pads to a respective contact pads of the second plurality of contact pads; and forming a ring-shaped seal between a perimeter of the piezoelectric plate and a perimeter of the base.

17. The method of claim 16, wherein the plurality of resonators includes at least five resonators, each resonator having: a recess in the base facing the diaphragm; and a distance from a bottom of the recess to the diaphragm is greater than or equal to 15 microns and less than or equal to 100 microns.

18. The method of claim 16, wherein all of the plurality of IDTs are configured to excite shear acoustic waves in the piezoelectric plate in response to respective radio frequency signals applied to each IDT; the interposer further comprises through-silicon-vias (TSVs) connecting the second plurality of contact pads to a third plurality of contact pads formed on the front surface of the base; and the base is silicon.

Description

NOTICE OF COPYRIGHTS AND TRADE DRESS

[0001] A portion of the disclosure of this patent document contains material which is subject to copyright protection. This patent document may show and/or describe matter which is or may become trade dress of the owner. The copyright and trade dress owner has no objection to the facsimile reproduction by anyone of the patent disclosure as it appears in the Patent and Trademark Office patent files or records, but otherwise reserves all copyright and trade dress rights whatsoever.

RELATED APPLICATION INFORMATION

[0002] This patent application is a divisional of copending U.S. application Ser. No. 16/841,134 titled TRANSVERSELY-EXCITED FILM BULK ACOUSTIC RESONATOR PACKAGE AND METHOD, filed Apr. 6, 2020, which claims priority to the following provisional patent applications: application 62/830,258, titled XBAR PACKAGING, filed Apr. 5, 2019; application 62/881,749, titled XBAR PACKAGING INCLUDING CAP PLATE, filed Aug. 1, 2019; and application 62/904,416, titled XBAR WAFER-LEVEL PACKAGING, filed Sep. 23, 2019, all of which are incorporated herein by reference in their entirety.

[0003] This patent is related to application Ser. No. 16/230,443, filed Dec. 21, 2018, entitled TRANSVERSELY-EXCITED FILM BULK ACOUSTIC RESONATOR, now U.S. Pat. No. 10,491,192.

BACKGROUND

Field

[0004] This disclosure relates to radio frequency filters using acoustic wave resonators, and specifically to filters for use in communications equipment.

Description of the Related Art

[0005] A radio frequency (RF) filter is a two-port device configured to pass some frequencies and to stop other frequencies, where "pass" means transmit with relatively low signal loss and "stop" means block or substantially attenuate. The range of frequencies passed by a filter is referred to as the "pass-band" of the filter. The range of frequencies stopped by such a filter is referred to as the "stop-band" of the filter. A typical RF filter has at least one pass-band and at least one stop-band. Specific requirements on a pass-band or stop-band depend on the specific application. For example, a "pass-band" may be defined as a frequency range where the insertion loss of a filter is better than a defined value such as 1 dB, 2 dB, or 3 dB. A "stop-band" may be defined as a frequency range where the rejection of a filter is greater than a defined value such as 20 dB, 30 dB, 40 dB, or greater depending on application.

[0006] RF filters are used in communications systems where information is transmitted over wireless links. For example, RF filters may be found in the RF front-ends of cellular base stations, mobile telephone and computing devices, satellite transceivers and ground stations, IoT (Internet of Things) devices, laptop computers and tablets, fixed point radio links, and other communications systems. RF filters are also used in radar and electronic and information warfare systems.

[0007] RF filters typically require many design trade-offs to achieve, for each specific application, the best compromise between performance parameters such as insertion loss, rejection, isolation, power handling, linearity, size and cost. Specific design and manufacturing methods and enhancements can benefit simultaneously one or several of these requirements.

[0008] Performance enhancements to the RF filters in a wireless system can have broad impact to system performance. Improvements in RF filters can be leveraged to provide system performance improvements such as larger cell size, longer battery life, higher data rates, greater network capacity, lower cost, enhanced security, higher reliability, etc. These improvements can be realized at many levels of the wireless system both separately and in combination, for example at the RF module, RF transceiver, mobile or fixed sub-system, or network levels.

[0009] The desire for wider communication channel bandwidths will inevitably lead to the use of higher frequency communications bands. The current LTE.TM. (Long Term Evolution) specification defines frequency bands from 3.3 GHz to 5.9 GHz. These bands are not presently used. Future proposals for wireless communications include millimeter wave communication bands with frequencies up to 28 GHz.

[0010] High performance RF filters for present communication systems commonly incorporate acoustic wave resonators including surface acoustic wave (SAW) resonators, bulk acoustic wave (BAW) resonators, film bulk acoustic wave resonators (FBAR), and other types of acoustic resonators. However, these existing technologies are not well-suited for use at the higher frequencies proposed for future communications networks.

DESCRIPTION OF THE DRAWINGS

[0011] FIG. 1 includes a schematic plan view and two schematic cross-sectional views of a transversely-excited film bulk acoustic resonator (XBAR).

[0012] FIG. 2 is an expanded schematic cross-sectional view of a portion of the XBAR of FIG. 1.

[0013] FIG. 3 is an alternative schematic cross-sectional view of the XBAR of FIG. 1.

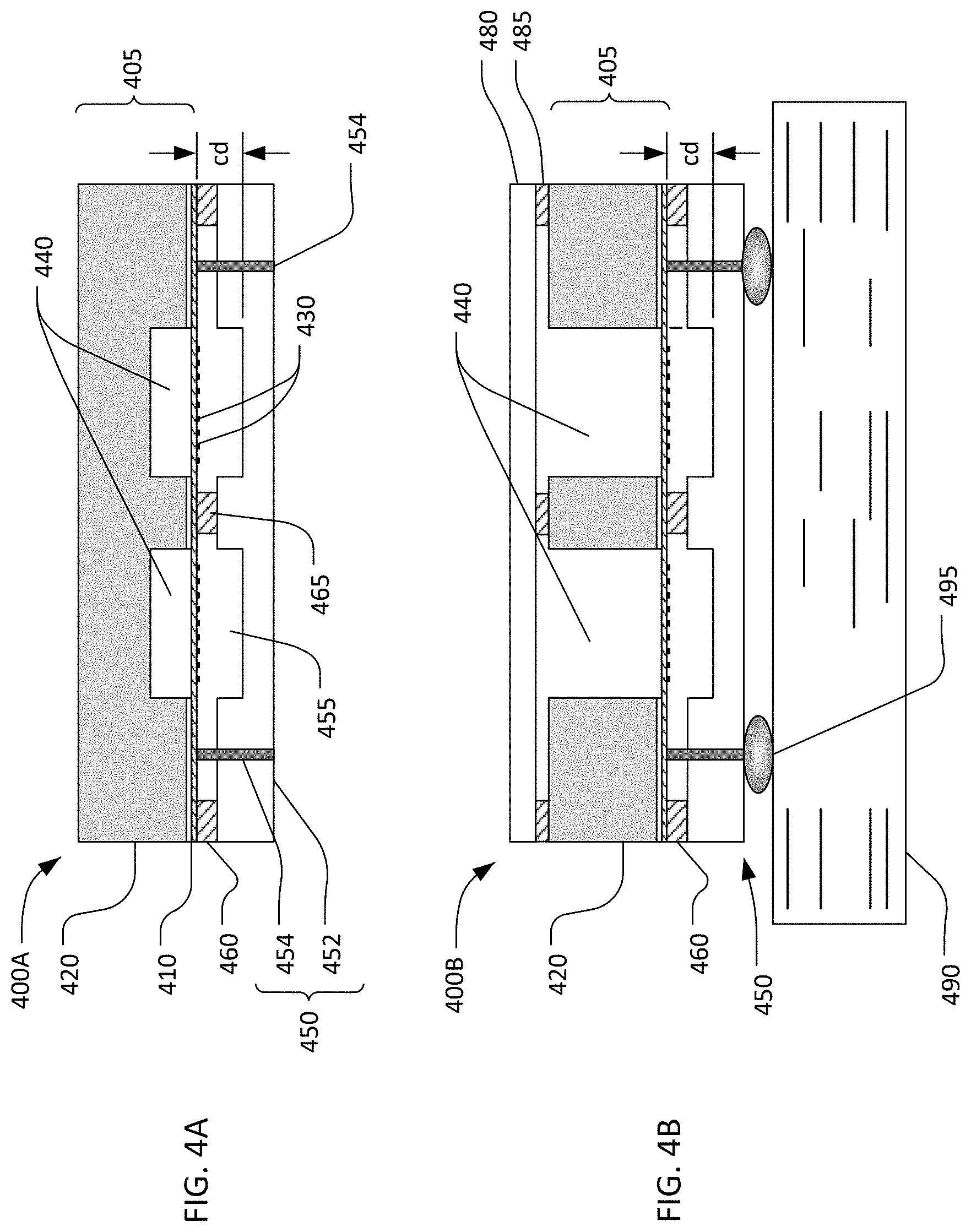

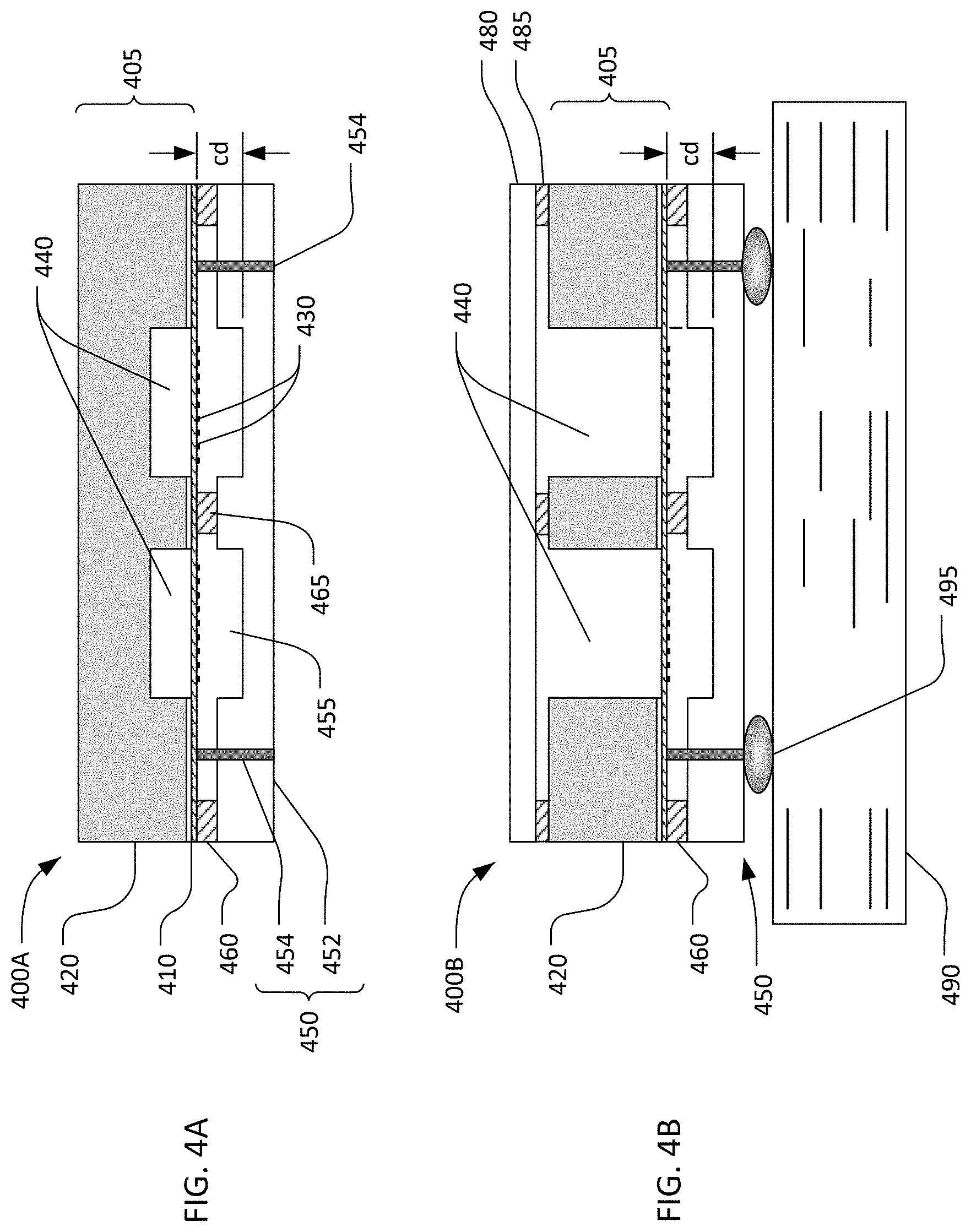

[0014] FIG. 4A is a schematic cross-sectional view of a packaged XBAR.

[0015] FIG. 4B is a schematic cross-sectional view of another packaged XBAR.

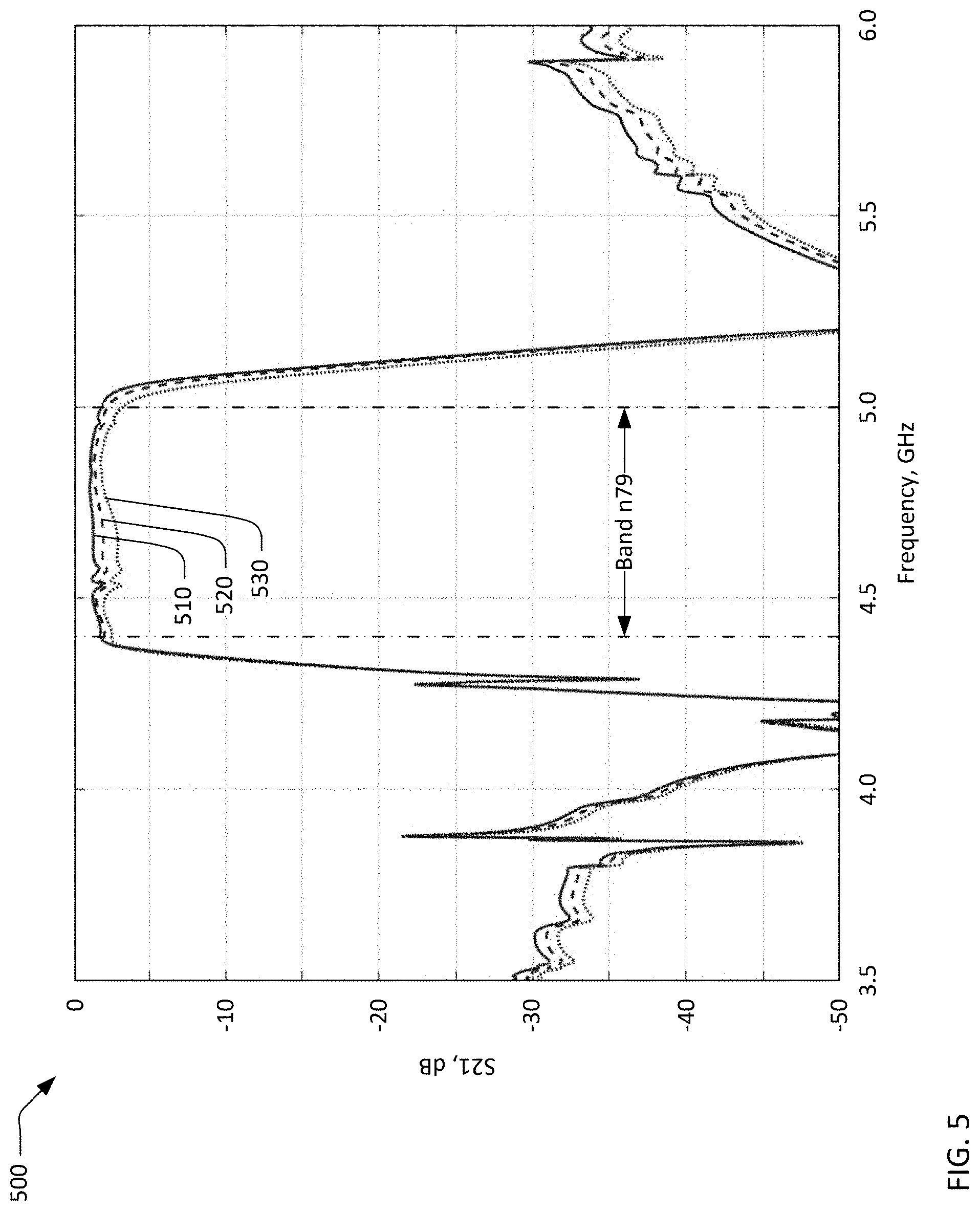

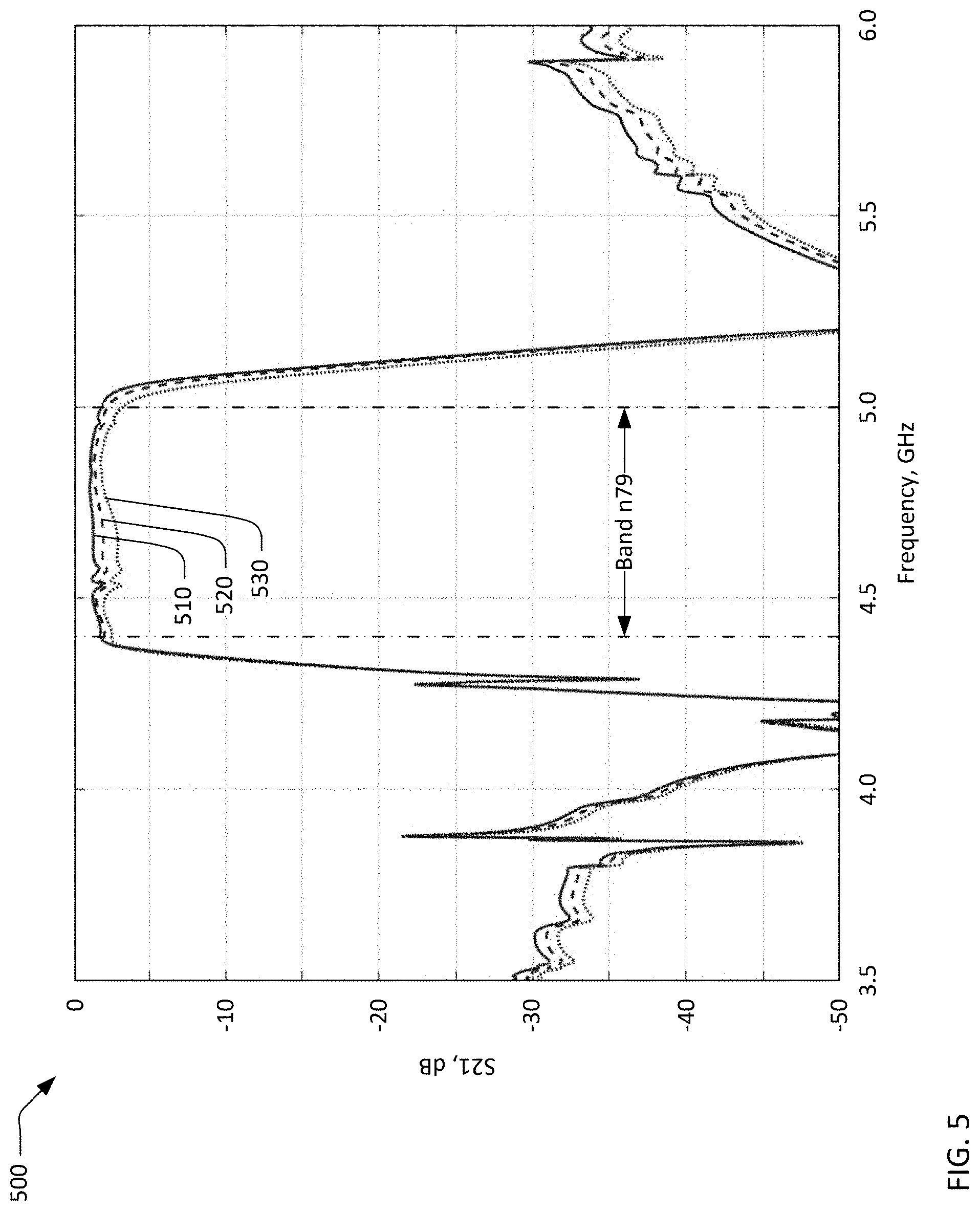

[0016] FIG. 5 is a graph of the transmission S21 through a bandpass filter using XBARs with a distance between the XBARs and a silicon cover as a parameter.

[0017] FIG. 6A is a schematic cross-sectional view of an XBAR filter chip and an interposer prior to bonding.

[0018] FIG. 6B is a schematic cross-sectional view of a packaged XBAR filter.

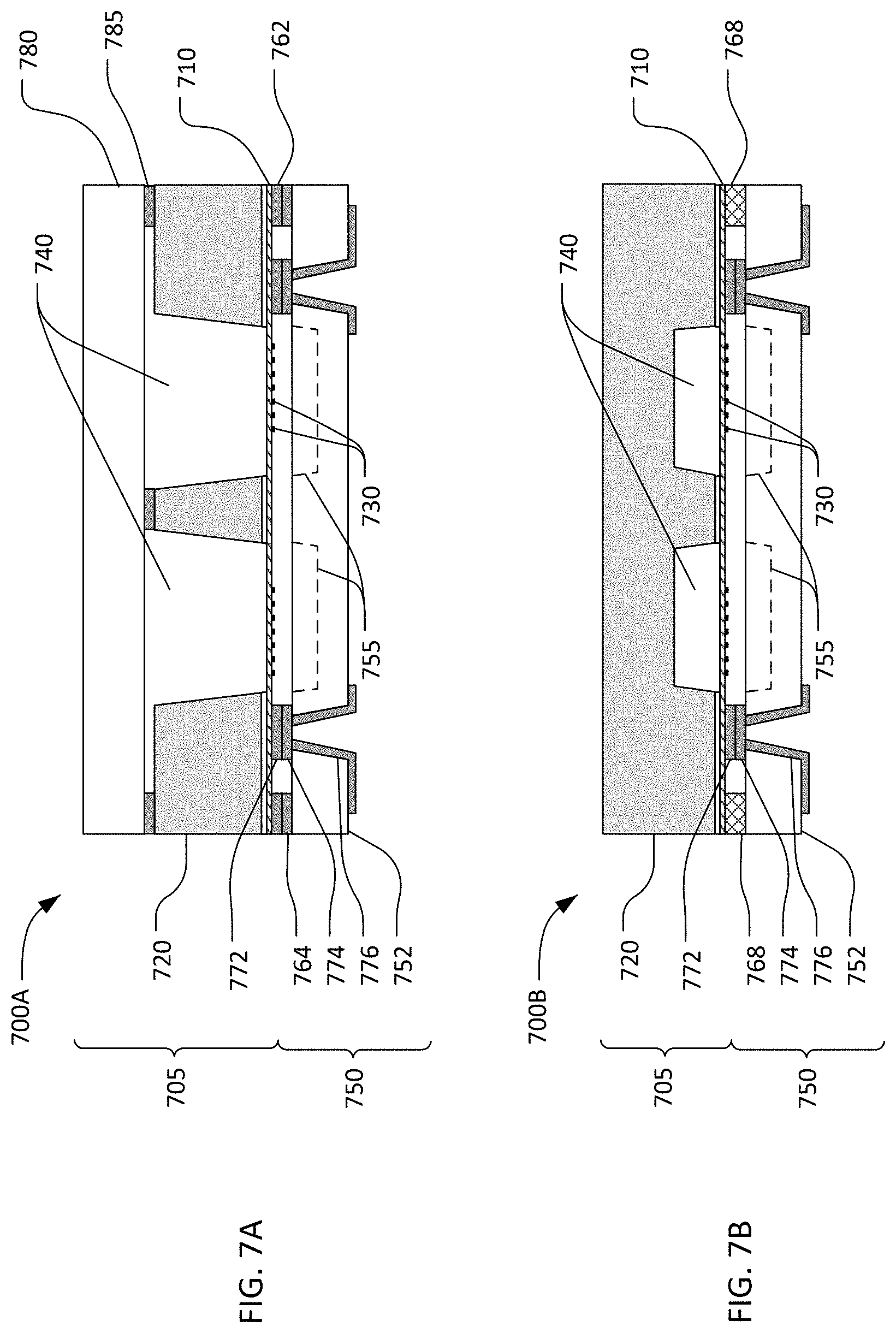

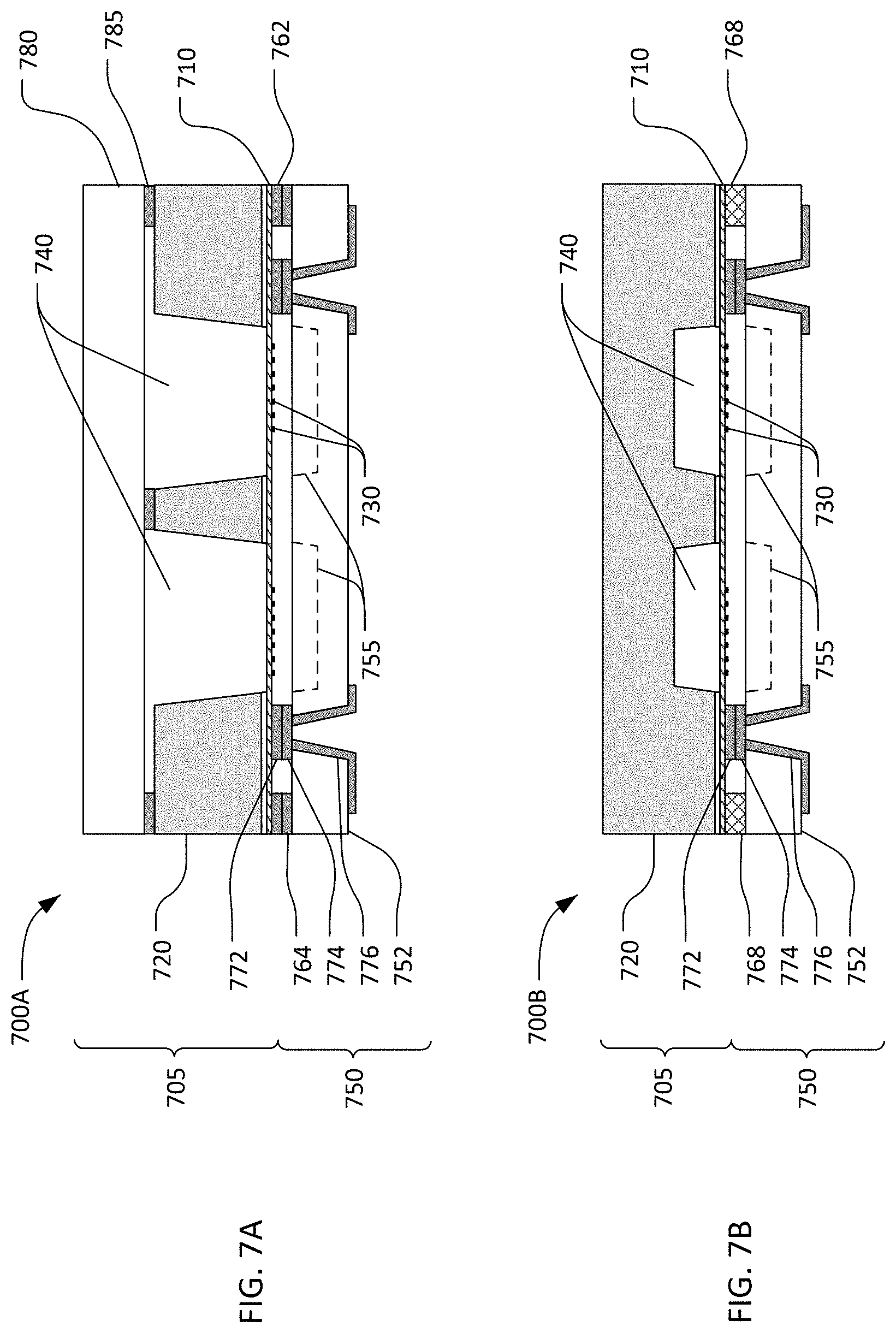

[0019] FIG. 7A is a schematic cross-sectional view of another packaged XBAR filter.

[0020] FIG. 7B is a schematic cross-sectional view of another packaged XBAR filter.

[0021] FIG. 8 is a schematic cross-sectional view of another packaged XBAR filter.

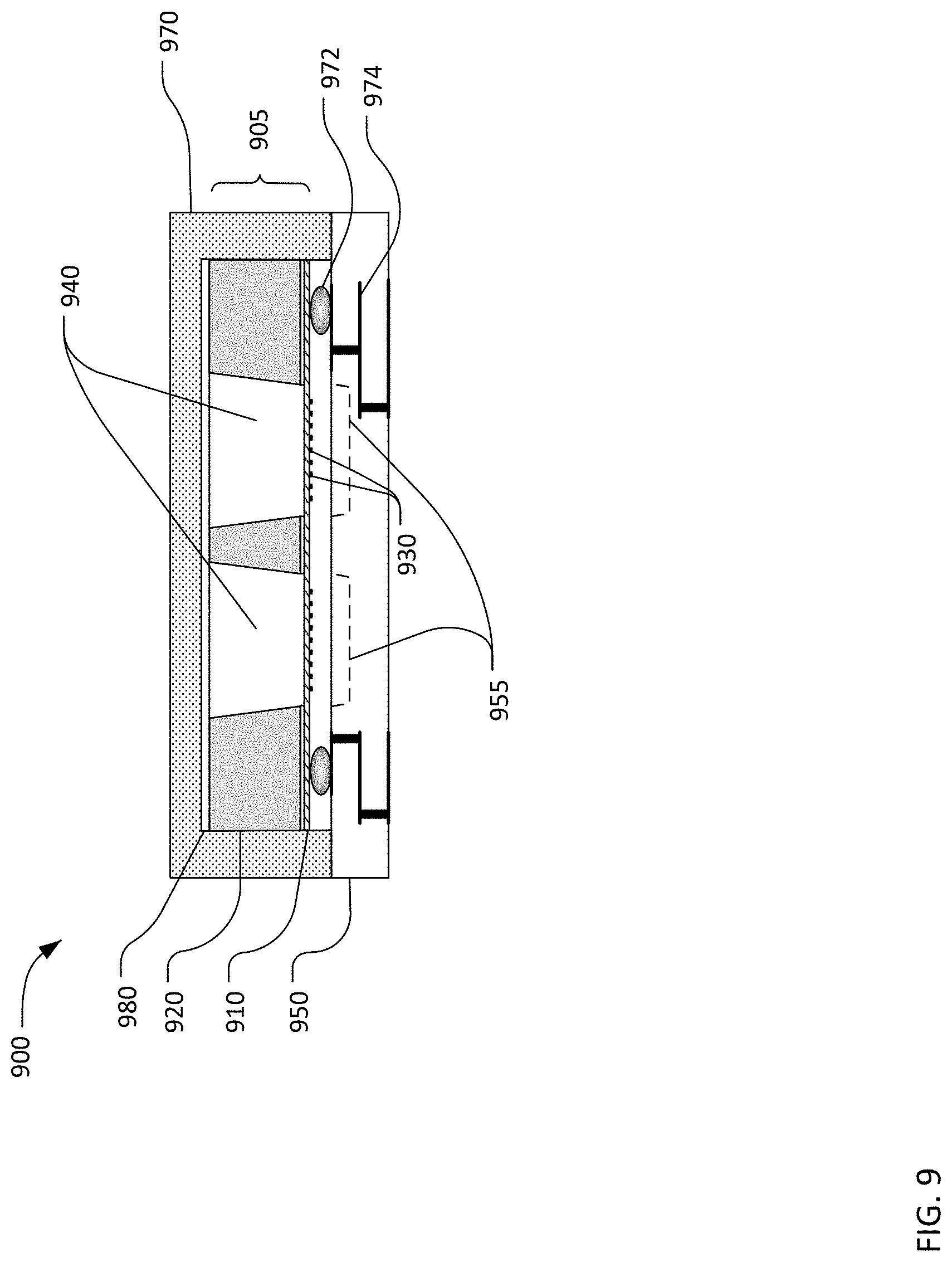

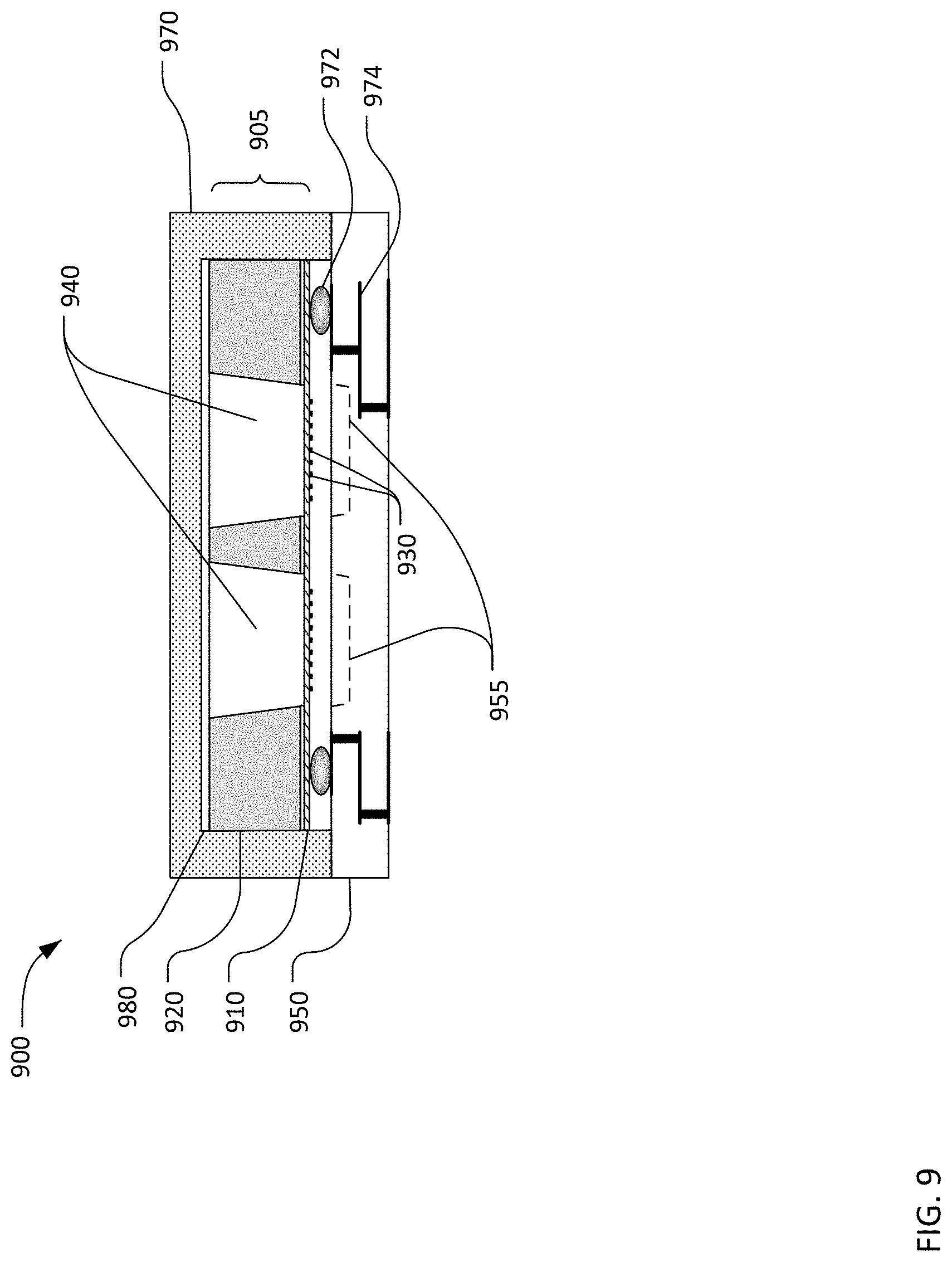

[0022] FIG. 9 is a schematic cross-sectional view of another packaged XBAR filter.

[0023] FIG. 10 is a schematic cross-sectional view of another packaged XBAR filter.

[0024] FIG. 11 is a flow chart of a process for fabricating an XBAR chip.

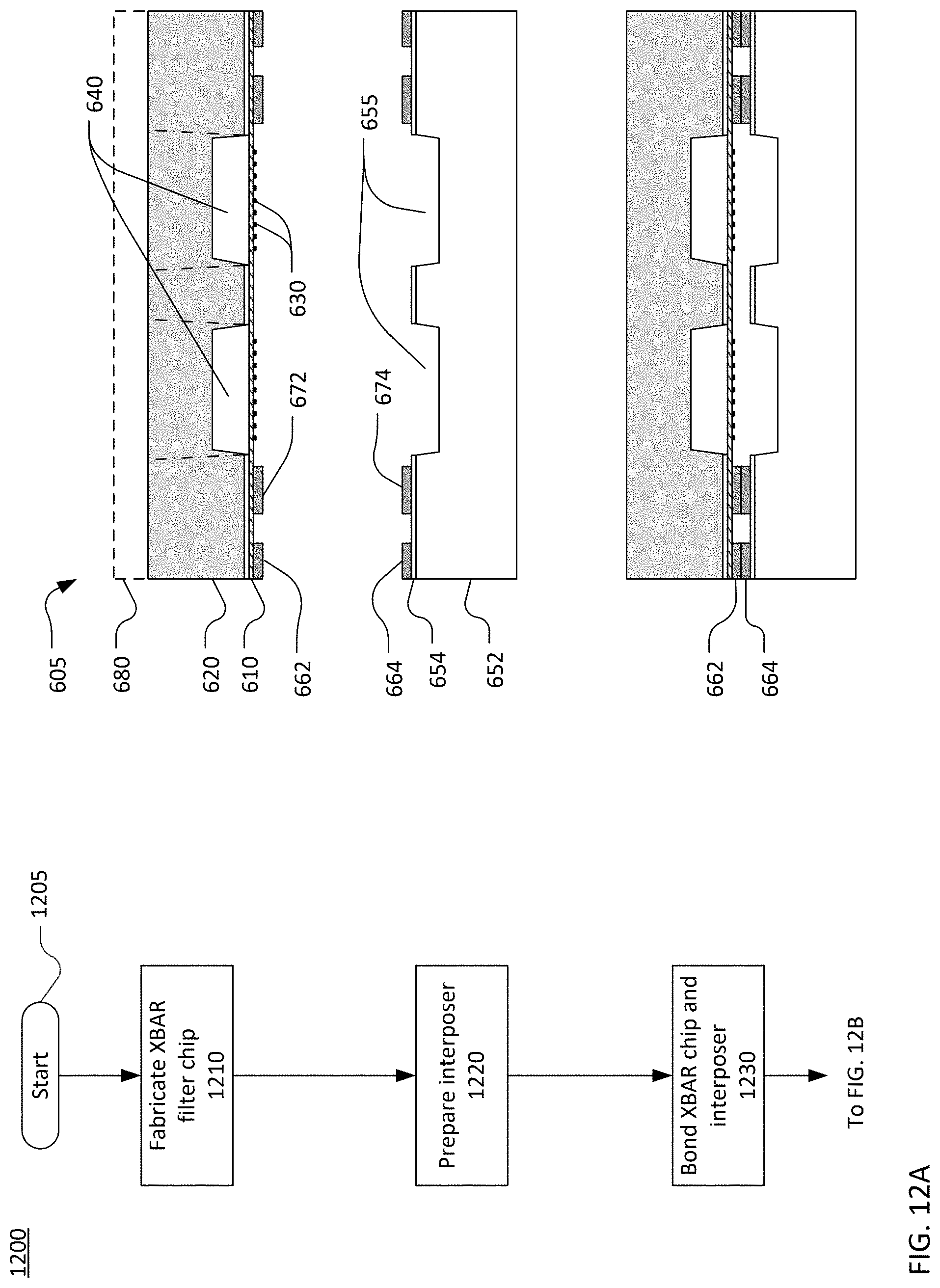

[0025] FIG. 12A, FIG. 12B, and FIG. 12C are, in combination, a flow chart of process for packaging an XBAR filter.

[0026] FIG. 13 is a flow chart of another process for packaging an XBAR filter.

[0027] FIG. 14 is a flow chart of another process for packaging an XBAR filter.

[0028] Throughout this description, elements appearing in figures are assigned three-digit or four-digit reference designators, where the two least significant digits are specific to the element and the one or two most significant digit is the figure number where the element is first introduced. An element that is not described in conjunction with a figure may be presumed to have the same characteristics and function as a previously-described element having the same reference designator.

DETAILED DESCRIPTION

[0029] Description of Apparatus

[0030] FIG. 1 shows a simplified schematic top view and orthogonal cross-sectional views of a transversely-excited film bulk acoustic resonator (XBAR) 100. XBAR resonators such as the resonator 100 may be used in a variety of RF filters including band-reject filters, band-pass filters, duplexers, and multiplexers. XBARs are particularly suited for use in filters for communications bands with frequencies above 3 GHz.

[0031] The XBAR 100 is made up of a thin film conductor pattern formed on a surface of a piezoelectric plate 110 having parallel front and back surfaces 112, 114, respectively. The piezoelectric plate is a thin single-crystal layer of a piezoelectric material such as lithium niobate, lithium tantalate, lanthanum gallium silicate, gallium nitride, or aluminum nitride. The piezoelectric plate is cut such that the orientation of the X, Y, and Z crystalline axes with respect to the front and back surfaces is known and consistent. In the examples presented in this patent, the piezoelectric plates are Z-cut, which is to say the Z axis is normal to the surfaces. However, XBARs may be fabricated on piezoelectric plates with other crystallographic orientations.

[0032] The back surface 114 of the piezoelectric plate 110 is attached to a substrate 120 that provides mechanical support to the piezoelectric plate 110. The substrate 120 may be, for example, silicon, sapphire, quartz, or some other material. The piezoelectric plate 110 may be bonded to the substrate 120 using a wafer bonding process, or grown on the substrate 120, or attached to the substrate in some other manner. The piezoelectric plate may be attached directly to the substrate, or may be attached to the substrate via one or more intermediate material layers.

[0033] The conductor pattern of the XBAR 100 includes an interdigital transducer (IDT) 130. The IDT 130 includes a first plurality of parallel fingers, such as finger 136, extending from a first busbar 132 and a second plurality of fingers extending from a second busbar 134. The first and second pluralities of parallel fingers are interleaved. The interleaved fingers overlap for a distance AP, commonly referred to as the "aperture" of the IDT. The center-to-center distance L between the outermost fingers of the IDT 130 is the "length" of the IDT.

[0034] The first and second busbars 132, 134 serve as the terminals of the XBAR 100. A radio frequency or microwave signal applied between the two busbars 132, 134 of the IDT 130 excites an acoustic wave within the piezoelectric plate 110. As will be discussed in further detail, the excited acoustic wave is a bulk shear wave that propagates in the direction normal to the surface of the piezoelectric plate 110, which is also normal, or transverse, to the direction of the electric field created by the IDT fingers. Thus, the XBAR is considered a transversely-excited film bulk wave resonator.

[0035] A cavity 140 is formed in the substrate 120 such that a portion 115 of the piezoelectric plate 110 containing the IDT 130 is suspended over the cavity 140 without contacting the substrate 120. "Cavity" has its conventional meaning of "an empty space within a solid body." The cavity 140 may be a hole completely through the substrate 120 (as shown in Section A-A and Section B-B) or a recess in the substrate 120 (as shown subsequently in FIG. 3). The cavity 140 may be formed, for example, by selective etching of the substrate 120 before or after the piezoelectric plate 110 and the substrate 120 are attached. As shown in FIG. 1, the cavity 140 has a rectangular shape with an extent greater than the aperture AP and length L of the IDT 130. A cavity of an XBAR may have a different shape, such as a regular or irregular polygon. The cavity of an XBAR may more or fewer than four sides, which may be straight or curved.

[0036] The portion 115 of the piezoelectric plate suspended over the cavity 140 will be referred to herein as the "diaphragm" (for lack of a better term) due to its physical resemblance to the diaphragm of a microphone. The diaphragm may be continuously and seamlessly connected to the rest of the piezoelectric plate 110 around all, or nearly all, of perimeter of the cavity 140.

[0037] For ease of presentation in FIG. 1, the geometric pitch and width of the IDT fingers is greatly exaggerated with respect to the length (dimension L) and aperture (dimension AP) of the XBAR. A typical XBAR has more than ten parallel fingers in the IDT 110. An XBAR may have hundreds, possibly thousands, of parallel fingers in the IDT 110. Similarly, the thickness of the fingers in the cross-sectional views is greatly exaggerated.

[0038] FIG. 2 shows a detailed schematic cross-sectional view of the XBAR 100 of FIG. 1. The piezoelectric plate 110 is a single-crystal layer of piezoelectrical material having a thickness ts. ts may be, for example, 100 nm to 1500 nm. When used in filters for LTE.TM. bands from 3.4 GHZ to 6 GHz (e.g. bands 42, 43, 46), the thickness ts may be, for example, 200 nm to 1000 nm.

[0039] A front-side dielectric layer 214 may optionally be formed on the front side of the piezoelectric plate 110. The "front side" of the XBAR is, by definition, the surface facing away from the substrate. The front-side dielectric layer 214 has a thickness tfd. The front-side dielectric layer 214 is formed between the IDT fingers 238. Although not shown in FIG. 2, the front side dielectric layer 214 may also be deposited over the IDT fingers 238. A back-side dielectric layer 216 may optionally be formed on the back side of the piezoelectric plate 110. The back-side dielectric layer 216 has a thickness tbd. The front-side and back-side dielectric layers 214, 216 may be a non-piezoelectric dielectric material, such as silicon dioxide or silicon nitride. tfd and tbd may be, for example, 0 to 500 nm. tfd and tbd are typically less than the thickness is of the piezoelectric plate. tfd and tbd are not necessarily equal, and the front-side and back-side dielectric layers 214, 216 are not necessarily the same material. Either or both of the front-side and back-side dielectric layers 214, 216 may be formed of multiple layers of two or more materials.

[0040] The IDT fingers 238 may be aluminum or a substantially aluminum alloy, copper or a substantially copper alloy, beryllium, gold, or some other conductive material. Thin (relative to the total thickness of the conductors) layers of other metals, such as chromium or titanium, may be formed under and/or over the fingers to improve adhesion between the fingers and the piezoelectric plate 110 and/or to passivate or encapsulate the fingers. The busbars (132, 134 in FIG. 1) of the IDT may be made of the same or different materials as the fingers.

[0041] Dimension p is the center-to-center spacing or "pitch" of the IDT fingers, which may be referred to as the pitch of the IDT and/or the pitch of the XBAR. Dimension w is the width or "mark" of the IDT fingers. The IDT of an XBAR differs substantially from the IDTs used in surface acoustic wave (SAW) resonators. In a SAW resonator, the pitch of the IDT is one-half of the acoustic wavelength at the resonance frequency. Additionally, the mark-to-pitch ratio of a SAW resonator IDT is typically close to 0.5 (i.e. the mark or finger width is about one-fourth of the acoustic wavelength at resonance). In an XBAR, the pitch p of the IDT is typically 2 to 20 times the width w of the fingers. In addition, the pitch p of the IDT is typically 2 to 20 times the thickness is of the piezoelectric slab 212. The width of the IDT fingers in an XBAR is not constrained to one-fourth of the acoustic wavelength at resonance. For example, the width of XBAR IDT fingers may be 500 nm or greater, such that the IDT can be fabricated using optical lithography. The thickness tm of the IDT fingers may be from 100 nm to about equal to the width w. The thickness of the busbars (132, 134 in FIG. 1) of the IDT may be the same as, or greater than, the thickness tm of the IDT fingers.

[0042] FIG. 3 is an alternative cross-sectional view along the section plane A-A defined in FIG. 1. In FIG. 3, a piezoelectric plate 310 is attached to a substrate 320. A cavity 340, which does not fully penetrate the substrate 320, is formed in the substrate under the portion of the piezoelectric plate 310 containing the IDT of an XBAR. The cavity 340 may be formed, for example, by etching the substrate 320 before attaching the piezoelectric plate 310. Alternatively, the cavity 340 may be formed by etching the substrate 320 with a selective etchant that reaches the substrate through one or more openings 342 provided in the piezoelectric plate 310.

[0043] The XBAR 300 shown in FIG. 3 will be referred to herein as a "front-side etch" configuration since the cavity 340 is etched from the front side of the substrate 320 (before or after attaching the piezoelectric plate 310). The XBAR 100 of FIG. 1 will be referred to herein as a "back-side etch" configuration since the cavity 140 is etched from the back side of the substrate 120 after attaching the piezoelectric plate 110.

[0044] The XBARs of FIG. 1 and FIG. 3 and filter devices using XBARs must be encased in a package. The package for an XBAR must perform the following functions: [0045] Provide mechanical protection for the diaphragms and conductor patterns; [0046] Provide cavities facing the diaphragms comparable to the cavity 340 in the substrate 320; [0047] Provide a seal to prevent intrusion of humidity and/or fluids that may be encountered during subsequent assembly of the packaged filter into an electronic device; and [0048] Provide means for connecting the conductor patterns of the XBARs to circuitry external to the packaged filter device.

[0049] FIG. 4A and FIG. 4B are schematic cross-sectional views of packaged XBAR filters, each of which comprises an XBAR filter chip 405 and an interposer 450. While the cross-sectional views of FIG. 4A and FIG. 4B show the XBAR filter chips 405 containing two XBARs, filters may commonly include five to nine XBARs. Specifically, FIG. 4A is a schematic cross-sectional view of a packaged filter 400A using front-side etched XBARs, and FIG. 4B is a schematic cross-section view of a packaged XBAR filter 400B using back-side etched XBARs. FIG. 4A and FIG. 4B are intended to illustrate the requirements on the package for an XBAR filter but do not necessarily represent practical package structures.

[0050] Referring to FIG. 4A, the XBAR filter chip 405 includes a piezoelectric plate 410 attached to a substrate 420. Portions of the piezoelectric plate form diaphragms spanning respective cavities 440 in the substrate 420. Commonly, one or more intermediate layers, which are shown in FIG. 4A but not identified, may be disposed between the piezoelectric plate 410 and the substrate 420. Conductor patterns including IDTs are formed on the surface of the piezoelectric plate 410 such that interleaved IDT fingers, such as fingers 430, are disposed on the diaphragms.

[0051] The interposer 450 also includes a base 452 and conductive vias 454 to provide electrical connections between the conductor patters on the piezoelectric plate 410 and circuitry external to the filter (not shown). The term "interposer" is generally used to describe a passive circuit device that provides electrical connections between two different interfaces. The interposer 450 fulfills this function but also forms a structural part of the package of the packaged XBAR filter 400A. The interposer may be, for example, a printed circuit board (PCB), a low temperature cofired ceramic (LTCC) circuit card, a silicon wafer, or some other structure that provides mechanical protection to the diaphragms of the XBARs.

[0052] In FIG. 4A, the conductive vias 454 are illustrated schematically as simple pins extending though the base to the piezoelectric plate. As will be discuss subsequently, physically realizable vias have more complex structures.

[0053] As shown in FIG. 4A, the interposer 450 includes recesses 455 facing the diaphragms of the XBARs. Such recesses may be required to ensure sufficient spacing between the diaphragms and the surfaces of the interposer facing the diaphragms (i.e. the bottom surfaces of the cavities 440). The required spacing (dimension cd in the FIG. 4A) depends on the material of the interposer.

[0054] FIG. 5 is a plot of the transmission (S21) through a bandpass filter including five XBARs in a package including a base made from a high resistivity silicon wafer. The silicon wafer has high dielectric permittivity and finite conductivity that can distort the electric fields created by the IDTs within the XBARs and introduce electrical losses, and thus impact the filter performance. The solid line 510 is a plot of S12 for a filter where the dimension cd is 50 microns. The dashed line 520 is a plot of S12 for the same filter where the dimension cd is 15 microns. The dotted line 530 is a plot of S12 for the same filter where the dimension cd is 5 microns. Reducing the spacing between the surface of the interposer and the diaphragms from 50 microns to 15 microns reduces the transmission of the filter in the passband by about 0.5 dB. Further reducing the spacing between the surface of the interposer and the diaphragms to 5 microns results in an addition reduction in transmission by about 1.0 dB. 15 microns may be a practical minimum for the dimension cd. Increasing the spacing between the surface of the interposer beyond 50 microns, for example to 100 microns, may offer a small addition improvement in transmission. All transmission plots are based on simulations of packaged filters using finite element methods.

[0055] Referring back to FIG. 4A, the interposer 450 is attached to the piezoelectric plate 410 by a seal 460. The seal 460 provides mechanical attachment and prevents intrusion of humidity and other fluids into the interior of the packaged XBAR filter 400A. As shown in FIG. 4A, the seal 460 is a distinct structure having a finite thickness which contributes to the total spacing cd between the diaphragms and the facing surfaces of the interposer 450. The seal 460 may be, for example, a thermocompression or ultrasonic bond between metal layers deposited on the piezoelectric plate and the interposer, a polymer or adhesive bond, a eutectic or solder bond, a glass frit bond, or some other bonding method and structure. Alternatively, the seal may be a bond, such as a plasma activated or surface activated wafer bond, directly between the interposer 450 and the piezoelectric plate 410. In this case (not shown in FIG. 4A), the thickness of the seal 460 may be negligible. In all cases, the seal 460 is present around the entire perimeter of the packaged XBAR filter 400A. In addition, the same sealing mechanism may attach the piezoelectric plate 410 to the interposer 450 at locations, such as location 465, in the interior of the packaged XBAR filter 400A.

[0056] FIG. 4B is a schematic cross-section view of a packaged XBAR filter 400B using back-side etched XBARs. Except for the depth of the cavities 440, the structure of the XBAR filter chip 405, the interposer 450, and the seal 460 between the interposer and the piezoelectric plate are identical to the comparable elements in FIG. 4A. The descriptions of these elements will not be repeated.

[0057] In addition, the package XBAR filter 400B includes a cap 480 attached to the substrate 420 by a cap seal 485. The cap 480 may be any material suitable to cover the openings where the cavities 440 intersect the surface of the substrate 420. For example, the cap 480 may be silicon, glass, quartz, or a polymer plate or film. The cap seal 485 may be any of the materials and sealing methods previously described with respect to the seal 460.

[0058] FIG. 4B also illustrates the packaged XBAR filter 400B attached and electrically connected to a radio module circuit board 490 by means of solder balls 495. This is an example of the use of the packaged filter device. The radio module circuit board 490 and the solder balls 495 are not part of the filter device 400B.

[0059] FIG. 6A is an exploded schematic cross-sectional view of a packaged XBAR filter 600. More specifically, FIG. 6A shows schematic cross-sectional views of an XBAR filter chip 605 including front-side etched XBARs and an interposer 650 prior to bonding.

[0060] The XBAR filter chip 605 includes a piezoelectric plate 610 attached to a substrate 620. The substrate 620 may be high resistivity silicon or some other material. Portions of the piezoelectric plate 610 form diaphragms spanning respective cavities 640 in the substrate 620. Commonly, one or more intermediate layers, which are shown in FIG. 6A but not identified, may be disposed between the piezoelectric plate 610 and the substrate 620. A first conductor pattern is formed on the surface of the piezoelectric plate 610. The first conductor pattern includes IDTs with interleaved IDT fingers, such as fingers 630, disposed on the diaphragms. The first conductor pattern may be aluminum, copper, molybdenum, or some other metal with a thickness of about 100 nm to 1000 nm.

[0061] A second conductor pattern is formed on the surface of the piezoelectric plate 610. The second conductor pattern, which may overlay portions of the first conductor pattern, may be gold, aluminum, copper or some other metal. The second conductor pattern includes a continuous metal ring 662 around the perimeter of the XBAR filter chip 605. The second conductor pattern also includes pads, such as pad 672, in locations where portions of the first conductor pattern must be connected to circuitry external to the packaged XBAR filter.

[0062] The interposer 650 includes a base 652, which may be high resistivity silicon or some other material. The base 652 may have recesses 655 so that the surfaces of the base 652 facing the diaphragms (i.e. the bottoms of the recesses 655) are sufficiently far from the diaphragms. A third conductor pattern is formed on the surface of the base 652 facing the XBAR filter chip 605. The third conductor pattern may be the same material as the second conductor pattern. The third conductor pattern includes a continuous metal ring 664 around the perimeter of the base 652. The third conductor pattern also includes pads, such as pad 674, in locations where portions of the first conductor pattern must be connected to circuitry external to the packaged XBAR filter. The arrangement of ring 664 and pads 674 of third conductor pattern is typically a mirror image of the arrangement of the ring 662 and pads 672 of the second conductor pattern.

[0063] The interposer 650 also includes vias such as via 676. When the base is silicon, such vias are commonly referred to as "through silicon vias" (TSVs). Vias consist of a metal-coated or metal-filled hole through the base 652. Each via provides an electrical connection between one of the pads, such as pad 674, of the third conductor pattern and a corresponding pad on the external surface (i.e. the lower surface as shown in the figure) of the base 652. While FIG. 6A, which is intended to illustrate the structure of the packaged XBAR filter 600, shows the TSVs formed prior to bonding the XBAR filter chip 605 and the interposer 650, the vias may be formed after bonding.

[0064] FIG. 6B is a schematic cross-sectional view of the packaged XBAR filter 600 after the XBAR filter chip 605 and the interposer 650 of FIG. 6A are bonded to each other. Descriptions of all of the identified elements in FIG. 6B were previously provided in the discussion of FIG. 6A and will not be repeated.

[0065] As shown in FIG. 6B, the ring 662 around the perimeter of the XBAR filter chip 605 has been directly bonded to the ring 664 around the perimeter of the interposer 650 to create a hermetic seal around the perimeter of the package XBAR filter 600. In this context, the term "directly bonded" means bonded without any intervening adhesive. Simultaneously, the pads, such as pad 672, of the second conductor pattern have been directly bonded to the pads, such as pad 674, of the third conductor pattern to create electrical connections between the XBAR filter chip 605 and the interposer 650. The bonds between the rings and pads of the second and third conductor patterns may be accomplished by, for example, thermocompression bonding or ultrasonic bonding.

[0066] FIG. 7A is a schematic cross-sectional view of a packaged XBAR filter 700A including an XBAR filter chip 705 bonded to an interposer 750. With the exception of elements 780 and 785, the identified elements in FIG. 7A have the structure and function as the corresponding elements of FIG. 6A and FIG. 6B. Descriptions of these elements will not be repeated.

[0067] A cap 780 is sealed to the substrate 720 by a cap seal 785. When the substrate 720 of the XBAR filter chip 705 and the base 752 of the interposer 750 are both silicon, the cap 780 may also be silicon to maintain consistency of thermal expansion coefficients. In other cases, the cap 780 may be silicon, borosilicate or other glass, plastic, or some other material. The cap 780 may be attached to the substrate 720 using any of the previously described sealing methods and materials. Typically, the cap 780 will be attached to the substrate 720 immediately after forming the cavities 740 in the substrate. The cap 780 may be attached to the substrate 720 before bonding the XBAR filter chip 705 to the interposer 750.

[0068] FIG. 7B is a schematic cross-sectional view of a packaged XBAR filter 700B including an XBAR filter chip 705 bonded to an interposer 750. With the exception of element 768, the identified elements in FIG. 7B have the structure and function as the corresponding elements of FIG. 6A and FIG. 6B. Descriptions of these elements will not be repeated.

[0069] In the packaged XBAR filter 700B, a perimeter seal between the piezoelectric plate 710 and the base 752 is not made by bonding conductor rings (i.e. conductor rings 762, 772 in FIG. 7A). Instead, a ring of cured adhesive material 768 forms a perimeter seal between the piezoelectric plate 710 and the base 752. The cured adhesive material 768 may be, for example, an epoxy resin or other thermosetting adhesive. The adhesive material (in an uncured state) may be applied to either or both of the piezoelectric plate 710 and the base 752 before the piezoelectric plate 710 and the base 752 are assembled. The adhesive material may be cured after or concurrent with bonding the pads 772 to the pads 774.

[0070] The XBAR filter chips 605 and 705 shown in FIG. 6B, FIG. 7A, and FIG. 7B may be portions of large wafers containing many filter chips. Similarly, the interposers 650 and 750 may be portions of large wafers containing a corresponding number on interposers. An XBAR wafer and an interposer wafer may be bonded and individual packaged XBAR filters may be excised from the bonded wafers.

[0071] FIG. 8 is a schematic cross-sectional view of another packaged XBAR filter 800 including an XBAR filter chip 805 with front-side etched cavities 840 and a low temperature cofired ceramic (LTCC) interposer 850. As in the previous examples, the XBAR filter chip 805 includes a piezoelectric plate 810 attached to a substrate 820. The substrate 820 may be high resistivity silicon or some other material. Portions of the piezoelectric plate 810 form diaphragms spanning respective cavities 840 in the substrate 820. Commonly, one or more intermediate layers, which are shown in FIG. 8 but not identified, may be disposed between the piezoelectric plate 810 and the substrate 820. A conductor pattern is formed on the surface of the piezoelectric plate 810. The conductor pattern includes IDTs with interleaved IDT fingers, such as fingers 830, disposed on the diaphragms.

[0072] The LTCC interposer 850 comprises layers of thin ceramic tape, some or all of which bear printed conductors, that are assembled and then fired to form a rigid multilayer circuit board. In the example of FIG. 8, the interposer has three conductor layers 874, 876, 878. An LTCC interposer for an XBAR filter may have more than three layers. The availability of multiple conductor layers allows incorporation of passive components, such as inductors, into the interposer.

[0073] The LTCC interposer 850 may have recesses 855 to ensure sufficient spacing between the diaphragms and the surfaces of the interposer facing the diaphragms. Such recess may be formed, for example, by punching openings in one or more of the ceramic layers prior to cofiring the layers of the interposer.

[0074] The XBAR filter chip 805 is flip-chip mounted to the interposer 850. Flip-chip mounting establishes physical and electric connections between the XBAR filter chip 805 and the interposer 850. As shown in FIG. 8, the connections are made by means of solder balls such as solder ball 872. Alternatively, the connections made be made by thermocompression or ultrasonic bonding of gold bumps on the XBAR filter chip 805 and the interposer 850 (not shown).

[0075] Since flip-chip mounting does not establish a seal between the XBAR filter chip 805 and the interposer 850, a polymer cover 860 is molded over the assembly to provide a near-hermetic seal.

[0076] FIG. 9 is a schematic cross-sectional view of another packaged XBAR filter 900 including an XBAR filter chip 905 with back-side etched cavities and a low temperature cofired ceramic (LTCC) interposer 950. With the exception of element 980, the identified elements in FIG. 9 have the structure and function as the corresponding elements of FIG. 8. Descriptions of these elements will not be repeated.

[0077] A cap 980 is sealed to the substrate 920. Since the cap 980 is eventually enclosed by the molded cover 970, the cap's primary function is to prevent intrusion of materials, including the molding compound used for the cover 970, into the cavities 940. This function may be satisfied by a very thin cap, such as a plastic film.

[0078] FIG. 10 is a schematic cross-sectional view of another packaged XBAR filter 1000 including an XBAR filter chip 1005 with back-side etched cavities and an interposer 1050 formed by layers built up on the surface of the XBAR filter chip. The XBAR filter chip 1005 is a portion of a wafer (not shown) containing multiple XBAR filter chips. The build up of the interposer layers is done on all of the XBAR filter chips simultaneously. Individual packaged XBAR filters are then excised from the wafer.

[0079] As in previous examples, the XBAR filter chip 1005 includes a piezoelectric plate 1010 attached to a substrate 1020. The substrate 1020 may be high resistivity silicon or some other material. Portions of the piezoelectric plate 1010 form diaphragms spanning respective cavities 1040 in the substrate 1020. Commonly, one or more intermediate layers, which are shown in FIG. 10 but not identified, may be disposed between the piezoelectric plate 1010 and the substrate 1020. A conductor pattern is formed on the surface of the piezoelectric plate 1010. The conductor pattern includes IDTs with interleaved IDT fingers, such as fingers 1030, disposed on the diaphragms. A cap 1080 is sealed to the substrate 1020 by a cap seal 1085 as previously described.

[0080] The interposer 1050 includes at least three layers sequentially formed on the piezoelectric plate 1010. Walls 1052 surround the diaphragms of the XBAR devices. The thickness of the walls 1052 defines the distance between the diaphragms and a cover layer 1054 that spans the walls creating an enclosed cavity 1055 over each diaphragm. Both the walls 1052 and the cover layer 1054 may be polymer materials. An interposer conductor pattern 1070 includes pads 1072 on the external surface of the cover layer 1054 for connection to circuitry external to the packaged XBAR filter. The conductor pattern 1070 connects the pads 1072 to connection points 1074 on the XBAR filer chip 1005. The conductor pattern 1070 may be aluminum, copper, gold, or a combination of materials.

[0081] Description of Methods

[0082] FIG. 11 is a simplified flow chart showing a process 1100 for making an XBAR filter chip. The process 1100 starts at 1105 with a substrate and a plate of piezoelectric material and ends at 1195 with a completed XBAR filter chip. The flow chart of FIG. 11 includes only major process steps. Various conventional process steps (e.g. surface preparation, cleaning, inspection, baking, annealing, monitoring, testing, etc.) may be performed before, between, after, and during the steps shown in FIG. 11.

[0083] The flow chart of FIG. 11 captures three variations of the process 1100 for making an XBAR filter chip which differ in when and how cavities are formed in the substrate. The cavities may be formed at steps 1110A, 1110B, or 1110C. Only one of these steps is performed in each of the three variations of the process 1100.

[0084] The piezoelectric plate may be, for example, Z-cut lithium niobate or lithium tantalate as used in the previously presented examples. The piezoelectric plate may be some other material and/or some other cut. The substrate may preferably be silicon. The substrate may be some other material that allows formation of deep cavities by etching or other processing.

[0085] In one variation of the process 1100, one or more cavities are formed in the substrate at 1110A, before the piezoelectric plate is bonded to the substrate at 1120. A separate cavity may be formed for each resonator in a filter device. The one or more cavities may be formed using conventional photolithographic and etching techniques. Typically, the cavities formed at 1110A will not penetrate through the substrate, and the resulting resonator devices will have a cross-section as shown in FIG. 3A or FIG. 3B.

[0086] At 1120, the piezoelectric plate is bonded to the substrate. The piezoelectric plate and the substrate may be bonded by a wafer bonding process. Typically, the mating surfaces of the substrate and the piezoelectric plate are highly polished. One or more layers of intermediate materials, such as an oxide or metal, may be formed or deposited on the mating surface of one or both of the piezoelectric plate and the substrate. One or both mating surfaces may be activated using, for example, a plasma process. The mating surfaces may then be pressed together with considerable force to establish molecular bonds between the piezoelectric plate and the substrate or intermediate material layers.

[0087] A conductor pattern, including IDTs of each XBAR, is formed at 1130 by depositing and patterning one or more conductor layer on the front side of the piezoelectric plate. The conductor layer may be, for example, aluminum, an aluminum alloy, copper, a copper alloy, or some other conductive metal. Optionally, one or more layers of other materials may be disposed below (i.e. between the conductor layer and the piezoelectric plate) and/or on top of the conductor layer. For example, a thin film of titanium, chrome, or other metal may be used to improve the adhesion between the conductor layer and the piezoelectric plate. A conduction enhancement layer of gold, aluminum, copper or other higher conductivity metal may be formed over portions of the conductor pattern (for example the IDT bus bars and interconnections between the IDTs).

[0088] The conductor pattern may be formed at 1130 by depositing the conductor layer and, optionally, one or more other metal layers in sequence over the surface of the piezoelectric plate. The excess metal may then be removed by etching through patterned photoresist. The conductor layer can be etched, for example, by plasma etching, reactive ion etching, wet chemical etching, and other etching techniques.

[0089] Alternatively, the conductor pattern may be formed at 1130 using a lift-off process. Photoresist may be deposited over the piezoelectric plate. and patterned to define the conductor pattern. The conductor layer and, optionally, one or more other layers may be deposited in sequence over the surface of the piezoelectric plate. The photoresist may then be removed, which removes the excess material, leaving the conductor pattern.

[0090] At 1140, a front-side dielectric layer may be formed by depositing one or more layers of dielectric material on the front side of the piezoelectric plate. The one or more dielectric layers may be deposited using a conventional deposition technique such as sputtering, evaporation, or chemical vapor deposition. The one or more dielectric layers may be deposited over the entire surface of the piezoelectric plate, including on top of the conductor pattern. Alternatively, one or more lithography processes (using photomasks) may be used to limit the deposition of the dielectric layers to selected areas of the piezoelectric plate, such as only between the interleaved fingers of the IDTs. Masks may also be used to allow deposition of different thicknesses of dielectric materials on different portions of the piezoelectric plate.

[0091] In a second variation of the process 1100, one or more cavities are formed in the back-side of the substrate at 1110B. A separate cavity may be formed for each resonator in a filter device. The one or more cavities may be formed using an anisotropic or orientation-dependent dry or wet etch to open holes through the back-side of the substrate to the piezoelectric plate. In this case, the resulting resonator devices will have a cross-section as shown in FIG. 1.

[0092] In the second variation of the process 1100, a cap, such as the caps 480, 780, 980, 1080, may be attached to the substrate at 1150 to cover and seal the cavities formed at 1110B. The cap may a plate of silicon, glass, or some other material or a plate or film of a polymer material. The cap may be attached to the substrate using any of the previously discussed bonding techniques.

[0093] In a third variation of the process 1100, one or more cavities in the form of recesses in the substrate may be formed at 1110C by etching the substrate using an etchant introduced through openings in the piezoelectric plate. A separate cavity may be formed for each resonator in a filter device. The one or more cavities formed at 1110C will not penetrate through the substrate, and the resulting resonator devices will have a cross-section as shown in FIG. 3.

[0094] In all variations of the process 1100, the XBAR filter chip is completed at 1160. Actions that may occur at 1160 include depositing an encapsulation/passivation layer such as SiO.sub.2 or Si.sub.3O.sub.4 over all or a portion of the device; forming bonding pads or solder bumps or other means for making connection between the device and external circuitry; and, if necessary, tuning the resonant frequencies of the resonators within the device by adding or removing metal or dielectric material from the front side of the device. At the conclusion of 1160, the XBAR filter chip is ready to be packaged. The process 1100 then ends at 1195.

[0095] FIG. 12A, FIG. 12B, and FIG. 12C are, in combination, a flow chart of process 1200 for fabricating a package XBAR filter using a silicon interposer with TSVs (through silicon vias). While FIG. 12A, FIG. 12B, and FIG. 12C illustrate the process 1200 with an XBAR filter chip with front-side etched cavities, the process 1200 may also use an XBAR filter chip with back-side etched cavities.

[0096] The process 1200 starts at 1205 and ends at 1295 with a completed packaged XBAR filter. FIG. 12A, FIG. 12B, and FIG. 12C show major process actions, each of which may involve multiple steps. Various conventional process steps (e.g. surface preparation, cleaning, inspection, baking, annealing, monitoring, testing, etc.) may be performed before, between, after, and during the steps shown in FIG. 12A, FIG. 12B, and FIG. 12C. For each major process action, a corresponding schematic cross-sectional view is provided to illustrate the configuration of the work-in-progress at the conclusion of the action. Where appropriate, reference designators previously used in FIG. 6 are used to identify elements of the work-in-progress.

[0097] Referring to FIG. 12A, at 1210, a XBAR filter chip 605 is fabricated using, for example, the process 1100 of FIG. 11. The XBAR filter chip 605 includes a piezoelectric plate 610 attached to a substrate 620. The substrate 620 may be high resistivity silicon or some other material. Portions of the piezoelectric plate 610 form diaphragms spanning respective cavities 640 in the substrate 620. A first conductor pattern is formed on the surface of the piezoelectric plate 610. The first conductor pattern includes IDTs with interleaved IDT fingers, such as fingers 630, disposed on the diaphragms.

[0098] When the XBAR filter chip 605 has back-side etched cavities (as shown by the dot-dash lines), a cover 680 is sealed to the back side of the substrate 620. While the cover 680 is not shown in subsequent cross-sectional views in FIG. 12A, FIG. 12B, and FIG. 12C, it must be understood that all of the actions in the process 1200 are compatible with a XBAR filter chip having a cover over back-side etched cavities.

[0099] A second conductor pattern is formed on the surface of the piezoelectric plate 610. The second conductor pattern, which may overlay portions of the first conductor pattern, may be gold, aluminum, copper or some other metal. The second conductor pattern includes a continuous metal ring 662 around the perimeter of the XBAR filter chip 605. The second conductor pattern also includes pads, such as pad 672, in locations where portions of the first conductor pattern must be connected to circuitry external to the packaged XBAR filter.

[0100] At 1220, a partially-completed interposer is prepared. The partially-completed interposer includes a base 652, which may be high resistivity silicon or some other material. A dielectric layer 654, such as silicon dioxide, is formed on the surface of the base that will face the XBAR filter chip. The base 652 may have recesses 655 so that the surfaces of the base 652 that will face the diaphragms (i.e. the bottoms of the recesses 655) are sufficiently far from the diaphragms. The dielectric layer 654 may or may not cover the recesses 655. A third conductor pattern is formed on top of the dielectric layer 654. The third conductor pattern may be the same material as the second conductor pattern. The third conductor pattern includes a continuous metal ring 664 around the perimeter of the base 652. The third conductor pattern also includes pads, such as pad 674, in locations where portions of the first conductor pattern must be connected to circuitry external to the packaged XBAR filter. The arrangement of ring 664 and pads 674 of third conductor pattern is typically a mirror image of the arrangement of the ring 662 and pads 672 of the second conductor pattern.

[0101] At 1230, the XBAR filter chip 605 is bonded to the partially-completed interposer. Specifically, the ring 662 of the second conductor pattern is bonded to the ring 664 of the third conductor pattern, forming a hermetic seal around the perimeter of the XBAR filter chip and partially-completed interposer. Simultaneously, pads, such as pad 672, on the XBAR filter chip are bonded to corresponding pads, such as pad 674, on the partially-completed interposer. A preferred method of bonding the XBAR filter chip to the partially competed interposer is thermocompression bonding, which uses a combination of heat and pressure to make bonds between metallic layers. Other methods, including ultrasonic bonding, and solder or eutectic bonding may be used.

[0102] Referring now to FIG. 12B, at 1240, one or both of the substrate 620 and the XBAR filter chip, and the base 652 of the partially-completed interposer may be thinned to reduce the overall height of the package XBAR filter. The substrate 620 and/or the base 652 may be thinned, for example, by mechanical or chemo-mechanical polishing.

[0103] After the optional thinning of one or both of the substrate 620 and the base 652, through silicon via are formed in a sequence of actions from 1250 to 1280.

[0104] At 1250, deep reactive ion etching (DRIE) is used to etch holes 1252 from the back side (the lower side as shown in FIG. 12B) of the base 652 through the base 652 to the dielectric layer 654. The dielectric layer 654 is not affected by the DRIE process, so the depth of the etch holes will be precisely controlled and uniform. The locations of the etched holes 1252 correspond to the locations of the pads, such as pad 674, of the third conductor pattern.

[0105] At 1260, a dielectric layer 1262 is deposited over the back side of the base 652 and the interiors of the holes 1252. The dielectric layer may be silicon dioxide, silicon nitride, aluminum oxide, or some other dielectric material. The dielectric layer may be deposited by a conventional process such as evaporation, sputtering, chemical vapor deposition, or some other process.

[0106] Referring now to FIG. 12C, at 1270, the oxide layer at the ends of the holes 1252 is etched through a patterned photoresist mask to expose at least a portion of each contact pad (such as pad 674) of the third conductor pattern.

[0107] At 1280, a fourth conductor pattern 1256 is formed to create electric connections from the pads, such as pad 674 of the third conductor pattern, to corresponding pads, such as pad 676 on the exterior surface (the lower surface as shown in FIG. 12C) of the base 652. The fourth conductor pattern may include a primary conductive layer of gold, aluminum, copper or some other highly conductive material. A thin layer of some other metal, such as titanium or nickel may be disposed between the primary conductive layer and the base 652 to improve adhesion. The structures including the holes 1252 and the fourth conductor pattern is commonly referred to as "through silicon vias". Once the through silicon vias are complete, the process 1200 ends at 1295.

[0108] The entire process 1200 may be, and commonly will be, performed on whole wafers. A whole wafer containing multiple XBARs filter chips will be bonded to another wafer containing a corresponding number of partially-completed interposers at 1230. The subsequent actions form TSVs for all of the interposers simultaneously. Individual packaged XBAR filters may then be excised by dicing the bonded wafers after action 1230.

[0109] FIG. 13 is a flow chart of another process 1300 for fabricating a package XBAR filter using a LTCC interposer. While FIG. 13 illustrates the process 1300 with an XBAR filter chip with front-side etched cavities, the process 1300 may also use an XBAR filter chip with back-side etched cavities.

[0110] The process 1300 starts at 1305 and ends at 1395 with a completed packaged XBAR filter. FIG. 13 shows major process actions, each of which may involve multiple steps. Various conventional process steps (e.g. surface preparation, cleaning, inspection, baking, annealing, monitoring, testing, etc.) may be performed before, between, after, and during the steps shown in FIG. 13. For each major process action, a corresponding schematic cross-sectional view is provided to illustrate the configuration of the work-in-progress at the conclusion of the action. Where appropriate, reference designators previously used in FIG. 8 are used to identify elements of the work-in-progress.

[0111] At 1310, a XBAR filter chip 805 is fabricated using, for example, the process 1100 of FIG. 11. The XBAR filter chip 805 will typically be a portion of a wafer containing multiple XBAR filter chips. The XBAR filter chip 805 includes a piezoelectric plate 810 attached to a substrate 820. The substrate 820 may be high resistivity silicon or some other material. Portions of the piezoelectric plate 810 form diaphragms spanning respective cavities 840 in the substrate 820. A first conductor pattern is formed on the surface of the piezoelectric plate 810. The first conductor pattern includes IDTs with interleaved IDT fingers, such as fingers 830, disposed on the diaphragms.

[0112] When the XBAR filter chip 805 has back-side etched cavities (as shown by the dot-dash lines), a cover 880 is sealed to the back side of the substrate 820. While the cover 880 is not shown in subsequent cross-sectional views in FIG. 13, it must be understood that all of the actions in the process 1300 are compatible with a XBAR filter chip having a cover over back-side etched cavities.

[0113] A second conductor pattern is formed on the surface of the piezoelectric plate 810. The second conductor pattern, which may overlay portions of the first conductor pattern, may be gold, aluminum, copper or some other metal. The second conductor pattern may include pads (not identified) in locations where portions of the first conductor pattern must be connected to circuitry external to the packaged XBAR filter. Solder balls or bumps 872 may be formed on the pads to allow the XBAR filter chip 805 to be reflow soldered to an interposer. Alternatively, gold bumps may be formed on the pads to allow the XBAR filter chip 805 to be thermocompression bonded or ultrasonic bonded to an interposer.

[0114] At 1320, a LTCC interposer 850 is fabricated by cofiring thin ceramic layers, some or all of which bear printed conductors. The LTCC interposer 850 will typically be a portion of a larger panel including multiple interposers, An LTCC interposer has at least an upper (as shown in FIG. 13) conductor pattern 874 that includes pads for connections to the XBAR filter chip and a lower conductor pattern 878 that includes pads for connection to circuitry external to the package XBAR filter. In the example of FIG. 13, the interposer 850 includes one intermediate conductor layer. An LTCC interposer for an XBAR filter may have more than three conductor layers. The availability of multiple conductor layers allows incorporation of passive components, such as inductors, into the interposer.

[0115] The LTCC interposer 850 may have recesses 855 to ensure sufficient spacing between the diaphragms and the surfaces of the interposer facing the diaphragms. Such recess may be formed, for example, by punching openings in one or more of the ceramic layers prior to cofiring the layers of the interposer.

[0116] At 1330, the XBAR filter chip 850 is flip-chip bonded to the interposer 850. First the XBAR filter chips within a wafer are tested, and good chips are excised from the wafer. The good chips are then bonded to the LTCC interposer 850 by soldering, thermocompression bonding, ultrasonic bonding, or some other bonding method. The bonding physically attaches the XBAR filter chip 805 to the interposer 850 and makes electrical connections between the XBAR filter chip 805 and the interposer 850. The bonding typically does not make a seal to protect the diaphragms of the XBAR filter chip 805.

[0117] At 1340, a polymer cover 860 is formed over the XBAR filter chip 805 to seal the space between the XBAR filter chip 805 and the interposer 850. The cover 850 may be formed by injection molding or casting, for example. Individual covers may be formed over each XBAR filter chip, or a unitary cover 850 may be formed over the entire LTCC panel. In either case, packages XBAR filters may be excised from the panel by, for example, sawing. The process 1300 then ends at 1395.

[0118] FIG. 14 is a flow chart of another process 1400 for fabricating a package XBAR filter using a wafer-level built up interposer. The process 1400 starts at 1405 and ends at 1495 with a completed packaged XBAR filter. FIG. 14 shows major process actions, each of which may involve multiple steps. Various conventional process steps (e.g. surface preparation, cleaning, inspection, baking, annealing, monitoring, testing, etc.) may be performed before, between, after, and during the steps shown in FIG. 14. For each major process action, a corresponding schematic cross-sectional view is provided to illustrate the configuration of the work-in-progress at the conclusion of the action. Where appropriate, reference designators previously used in FIG. 10 are used to identify elements of the work-in-progress.

[0119] At 1410, a XBAR filter chip 1005 is fabricated using, for example, the process 1100 of FIG. 11. The XBAR filter chip 1005 will typically be a portion of a wafer containing multiple XBAR filter chips. The XBAR filter chip 1005 includes a piezoelectric plate 1010 attached to a substrate 1020. The substrate 1020 may be high resistivity silicon or some other material. Portions of the piezoelectric plate 1010 form diaphragms spanning respective cavities 1040 in the substrate 1020. A first conductor pattern is formed on the surface of the piezoelectric plate 1010. The first conductor pattern includes IDTs with interleaved IDT fingers, such as fingers 1030, disposed on the diaphragms.

[0120] The subsequent actions in the process require liquid materials, such as solvents, photoresist, or photopolymerizable monomers, to be applied to the front side of the piezoelectric plate 1010 after the cavities 1040 have been etched. The process 1400 is not suitable for XBAR filter chips with front-side etched cavities because the liquid materials may pass into the cavities through the etch holes in the diaphragms. Thus, the XBAR filter chip 1005 has back-side etched cavities with a cover 1080 sealed to the back side of the substrate 1020.

[0121] At 1420, walls 1052 are formed on the piezoelectric plate 1010. The walls 1052 may be formed with openings over the XBAR diaphragms and openings where electrical connections to the XBAR filter chip will be made in a subsequent process action. The walls 1052 may be formed, for example, by coating the piezoelectric plate 1010 with a photopolymerizable material and then exposing the photopolymerizable material through a suitable mask. Depending on the required thickness of the walls, multiple layers of material may be coated and patterned in succession.

[0122] A 1430, a cover layer 1054 is applied over the walls 1052. The cover layer 1054 may be applied, for example, as a continuous film bonded to the walls 1052 by an adhesive. The cover layer 1054 spans the openings in the walls 1052 over the XBAR diaphragms, forming an enclosed cavity 1055 over each diaphragm. The cover layer is pattered to form openings where electrical connections to the XBAR filter chip will be made in a subsequent process action.

[0123] At 1440, a conductor pattern 1070 is formed. The conductor pattern 1070 includes pads 1072 on the external surface of the cover layer 1054 for connection to circuitry external to the packaged XBAR filter. The conductor pattern 1070 connects the pads 1072 to connection points 1074 on the XBAR filer chip 1005. The conductor pattern 1070 may be aluminum, copper, gold, or a combination of materials deposited and patterned using conventional techniques. Once the conductor pattern is formed, the process 1400 ends at 1495.

[0124] The entire process 1400 may be, and commonly will be, performed on whole wafers. Individual packaged XBAR filters may then be excised by sawing through the bonded wafers after the conductor pattern is formed at 1440.

[0125] Closing Comments

[0126] Throughout this description, the embodiments and examples shown should be considered as exemplars, rather than limitations on the apparatus and procedures disclosed or claimed. Although many of the examples presented herein involve specific combinations of method acts or system elements, it should be understood that those acts and those elements may be combined in other ways to accomplish the same objectives. With regard to flowcharts, additional and fewer steps may be taken, and the steps as shown may be combined or further refined to achieve the methods described herein. Acts, elements and features discussed only in connection with one embodiment are not intended to be excluded from a similar role in other embodiments.

[0127] As used herein, "plurality" means two or more. As used herein, a "set" of items may include one or more of such items. As used herein, whether in the written description or the claims, the terms "comprising", "including", "carrying", "having", "containing", "involving", and the like are to be understood to be open-ended, i.e., to mean including but not limited to. Only the transitional phrases "consisting of" and "consisting essentially of", respectively, are closed or semi-closed transitional phrases with respect to claims. Use of ordinal terms such as "first", "second", "third", etc., in the claims to modify a claim element does not by itself connote any priority, precedence, or order of one claim element over another or the temporal order in which acts of a method are performed, but are used merely as labels to distinguish one claim element having a certain name from another element having a same name (but for use of the ordinal term) to distinguish the claim elements. As used herein, "and/or" means that the listed items are alternatives, but the alternatives also include any combination of the listed items.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

D00009

D00010

D00011

D00012

D00013

D00014

D00015

D00016

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.