Semiconductor Device, Semiconductor Chip And Method Of Manufacturing Semiconductor Device

PEI; Yi ; et al.

U.S. patent application number 16/760786 was filed with the patent office on 2020-10-15 for semiconductor device, semiconductor chip and method of manufacturing semiconductor device. The applicant listed for this patent is DYNAX SEMICONDUCTOR, INC.. Invention is credited to Gouchun KANG, Yi PEI, Linlin SUN.

| Application Number | 20200328133 16/760786 |

| Document ID | / |

| Family ID | 1000004938449 |

| Filed Date | 2020-10-15 |

View All Diagrams

| United States Patent Application | 20200328133 |

| Kind Code | A1 |

| PEI; Yi ; et al. | October 15, 2020 |

SEMICONDUCTOR DEVICE, SEMICONDUCTOR CHIP AND METHOD OF MANUFACTURING SEMICONDUCTOR DEVICE

Abstract

Embodiments of the disclosure provide a semiconductor device, a semiconductor chip and a method of manufacturing a semiconductor device, wherein the semiconductor device, includes a substrate, a semiconductor layer formed on the substrate, a plurality of gates, drains, and a plurality of sources formed on a side of the semiconductor layer away from the substrate, the gates located between the sources and the drains, and the gates, sources, and drains located in an active region of the semiconductor device, wherein a gate pitch is formed between any two adjacent gates, the formed respective gate pitches include at least two unequal gate pitches, the maximum gate pitch of the respective gate pitches is within a first preset range determined according to a pitch of two gates at the two outermost ends in the semiconductor device in the gate length direction and a total number of gates of the semiconductor device.

| Inventors: | PEI; Yi; (Kunshan, CN) ; KANG; Gouchun; (Kunshan, CN) ; SUN; Linlin; (Kunshan, CN) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 1000004938449 | ||||||||||

| Appl. No.: | 16/760786 | ||||||||||

| Filed: | April 25, 2019 | ||||||||||

| PCT Filed: | April 25, 2019 | ||||||||||

| PCT NO: | PCT/CN2019/084222 | ||||||||||

| 371 Date: | April 30, 2020 |

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 29/66462 20130101; H01L 29/778 20130101; H01L 23/367 20130101; H01L 29/42356 20130101 |

| International Class: | H01L 23/367 20060101 H01L023/367; H01L 29/423 20060101 H01L029/423; H01L 29/66 20060101 H01L029/66; H01L 29/778 20060101 H01L029/778 |

Foreign Application Data

| Date | Code | Application Number |

|---|---|---|

| Apr 26, 2018 | CN | 201810383833.9 |

Claims

1. A semiconductor device, device comprising: a substrate; a semiconductor layer formed on the substrate; and a plurality of gates, a plurality of drains, and a plurality of sources formed on a side of the semiconductor layer away from the substrate, the gates being located between the sources and the drains, and the gates, sources, and drains being located in an active region of the semiconductor device; wherein a gate pitch is formed between any two adjacent gates, wherein the formed respective gate pitches include at least two unequal gate pitches, and wherein the maximum gate pitch of the respective gate pitches is within a first preset range determined according to a pitch of two gates at the two outermost ends in the semiconductor device in the gate length direction and a total number of gates of the semiconductor device.

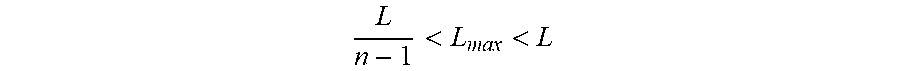

2. The semiconductor device according to claim 1, wherein the first preset range is (L/(n-1), L), and wherein the maximum gate pitch L.sub.max satisfies the following condition, L n - 1 < L max < L ##EQU00008## wherein L is the pitch of two gates at the two outermost ends in the semiconductor device in the gate length direction, and wherein n is the total number of gates of the semiconductor device.

3. The semiconductor device according to claim 1, wherein the minimum gate pitch of the respective gate pitches is within a second preset range determined according to a pitch of two gates at the two outermost ends in the semiconductor device in the gate length direction and a total number of gates of the semiconductor device, wherein the second preset range is (L/(n-1).sup.2, L/(n-1)), and wherein the minimum gate pitch L.sub.min satisfies the following condition, L ( n - 1 ) 2 < L min < L n - 1 ##EQU00009## wherein L is the pitch of two gates at the two outermost ends in the semiconductor device in the gate length direction, and wherein n is the total number of gates of the semiconductor device.

4. The semiconductor device according to claim 3, wherein the maximum gate pitch is located between adjacent gates on both sides of the source, and wherein the minimum gate pitch is located between adjacent gates on both sides of the drain.

5. The semiconductor device according to claim 3, wherein the maximum gate pitch is located at a center position of the active region, while other gate pitches are sequentially arranged in a direction from the center position of the active region to a position away from the center position, and wherein all the other gate pitches are the minimum gate pitches.

6. The semiconductor device according to claim 1, wherein, in a direction from a center position of the active region to a position away from the center position, the respective pitches between adjacent gates on both sides of the source decrease sequentially according to a first fixed value or a first change amount, and wherein the respective pitches between adjacent gates on both sides of the drain decrease sequentially according to a second fixed value or a second change amount.

7. The semiconductor device according to claim 1, wherein a plurality of the gates are interconnected together through a gate pad located in a passive region of the semiconductor device, wherein a plurality of the drains are interconnected together through a drain pad located in the passive region, and wherein a plurality of the sources are respectively connected to a ground electrode located on a side of the substrate away from the semiconductor layer respectively through a plurality of through holes penetrating the substrate and the semiconductor layer.

8. The semiconductor device according to claim 1, wherein the respective gate pitches include at least two gate pitches which are the maximum gate pitch.

9. The semiconductor device according to claim 8, wherein the maximum gate pitch is located at a center position of the active region, and in a direction from the center position of the active region to a position away from the center position, and wherein two pitches of the maximum gate pitch and the minimum gate pitch are arranged alternately.

10. A semiconductor chip, wherein the semiconductor chip comprises a plurality of semiconductor devices according to claim 1, and wherein the plurality of semiconductor devices are connected in parallel.

11. The semiconductor chip according to claim 10, wherein a gate pitch between devices is formed between edge gates of any two adjacent semiconductor devices, and in a direction from the center position of the active region of the semiconductor chip to a position away from the center position, and wherein the gate pitches between devices decrease sequentially according to a third fixed value or a third change amount.

12. The semiconductor chip according to claim 11, wherein the third fixed value or third change amount is less than or equal to twice of the maximum gate pitch inside the semiconductor devices in the semiconductor chip.

13. The semiconductor chip according to claim 10, wherein a plurality of the semiconductor devices includes a center device located at the center of the active region and an edge device away from the center of the active region, and wherein a center gate pitch of the edge device is different from an edge gate pitch of the center device; wherein the center gate pitch of the edge device is a gate pitch formed by two adjacent gates located at the center of the edge device, and wherein the edge gate pitch of the center device is a gate pitch formed by any two adjacent gates away from the center of the center device.

14. The semiconductor chip according to claim 13, wherein the center gate pitch of the center device is different from the center gate pitch of the edge device.

15. A semiconductor chip comprising a plurality of semiconductor devices, the plurality of semiconductor devices being connected in parallel, each semiconductor device comprising a plurality of gates, a plurality of drains, and a plurality of sources, the gates being located between the sources and the drains; wherein, in the semiconductor chip, a gate pitch is formed between any two adjacent gates, wherein the formed respective gate pitches include at least two unequal gate pitches, and wherein the maximum gate pitch of the respective gate pitches is within a first preset range determined according to a pitch of two gates at the two outermost ends in the semiconductor chip in the gate length direction and a total number of gates of the semiconductor chip.

16. The semiconductor chip according to claim 15, wherein in a plurality of the semiconductor devices, all gate pitches in at least one semiconductor device are equal.

17. The semiconductor chip according to claim 15, wherein the edge gate pitches between a plurality of adjacent semiconductor devices are equal or decrease from the center of the active region to both ends.

18. The semiconductor chip according to claim 15, wherein a pitch between gates on both sides of the source inside at least one semiconductor device of the plurality of semiconductor devices is d1, and wherein a pitch between gates on both sides of a drain inside the at least one semiconductor device is d2, where d2.ltoreq.d1.ltoreq.2d2.

19. A method of manufacturing a semiconductor device, the method comprising: providing a substrate; forming a semiconductor layer on a side of the substrate; and forming a plurality of gates, a plurality of drains, and a plurality of sources on a side of the semiconductor layer away from the substrate, each gate located between one of the sources and one of the drains, and the gates, sources, and drains located in an active region of the semiconductor device; wherein a gate pitch is formed between any two adjacent gates, wherein the formed respective gate pitches include at least two unequal gate pitches, and wherein the maximum gate pitch of the respective gate pitches is within a first preset range determined according to a pitch of two gates at the two outermost ends in the semiconductor device in the gate length direction and a total number of gates of the semiconductor device.

20. The method of manufacturing a semiconductor device according to claim 19, wherein the first preset range is (L/(n-1), L), and wherein the maximum gate pitch L.sub.max satisfies the following condition, L n - 1 < L max < L ##EQU00010## wherein the minimum gate pitch of the respective gate pitches is within a second preset range determined according to a pitch of two gates at the two outermost ends in the semiconductor device in the gate length direction and a total number of gates of the semiconductor device, wherein the second preset range is (L/(n-1).sup.2, L/(n-1)), and wherein the minimum gate pitch L.sub.min satisfies the following condition, L ( n - 1 ) 2 < L min < L n - 1 ##EQU00011## wherein L is the pitch of two gates at the two outermost ends in the semiconductor device in the gate length direction, and wherein n is the total number of gates of the semiconductor device.

Description

CROSS REFERENCE TO RELATED APPLICATIONS

[0001] This patent application is a National Stage Entry of PCT/CN2019/084222 filed on Apr. 25, 2019, which claims the benefit and priority of Chinese Patent Application No. 201810383833.9 filed on Apr. 26, 2018, the disclosures of which are incorporated by reference herein in their entirety as part of the present application.

BACKGROUND

[0002] The present disclosure relates to the field of microelectronic technology, and particularly to a semiconductor device, a semiconductor chip, and a method of manufacturing a semiconductor device.

[0003] Gallium Nitride High Electron Mobility Transistor (HEMT) has excellent characteristics such as high band gap width, high mobility, and is suitable for making devices of high temperature, high frequency, high voltage, and high power. It can be widely used in the field of radio frequency microwave and the field of power electronics, and is one of the current research hotspots in the field of semiconductor devices. However, during the use of a semiconductor device, uneven temperature distribution in the device results in that the device generates large amounts of heat and has low reliability, which further affects the output power of the device.

BRIEF DESCRIPTION

[0004] In view of the above, the present disclosure provides a semiconductor device, a semiconductor chip, and a method of manufacturing a semiconductor device, which can effectively solve the above problem.

[0005] One embodiment of the present disclosure provides a semiconductor device, including a substrate, a semiconductor layer formed on the substrate, and a plurality of gates, a plurality of drains, and a plurality of sources formed on a side of the semiconductor layer away from the substrate, the gates being located between the sources and the drains, and the gates, sources, and drains being located in an active region of the semiconductor device, wherein a gate pitch is formed between any two adjacent gates, the formed respective gate pitches include at least two unequal gate pitches, the maximum gate pitch of the respective gate pitches is within a first preset range determined according to a pitch of two gates at the two outermost ends in the semiconductor device in the gate length direction and a total number of gates of the semiconductor device.

[0006] Further, the first preset range is (L/(n-1), L), where L is the pitch of two gates at the two outermost ends in the semiconductor device in the gate length direction, and n is the total number of gates of the semiconductor device.

[0007] Further, the minimum gate pitch of the respective gate pitches is within a second preset range determined according to a pitch of two gates at the two outermost ends in the semiconductor device in the gate length direction and a total number of gates of the semiconductor device, the second preset range is (L/(n-1).sup.2, L/(n-1)), where L is the pitch of two gates at the two outermost ends in the semiconductor device in the gate length direction, and n is the total number of gates of the semiconductor device.

[0008] Further, the maximum gate pitch is located between adjacent gates on both sides of the source, and the minimum gate pitch is located between adjacent gates on both sides of the drain.

[0009] Further, the maximum gate pitch is located at a center position of the active region, while other gate pitches are sequentially arranged in a direction from the center position of the active region to a position away from the center position, and all the other gate pitches are the minimum gate pitches.

[0010] Further, in a direction from a center position of the active region to a position away from the center position, the respective pitches between adjacent gates on both sides of the source decrease sequentially according to a first fixed value or a first change amount, and the respective pitches between adjacent gates on both sides of the drain decrease sequentially according to a second fixed value or a second change amount.

[0011] Further, a plurality of the gates are interconnected together through a gate pad located in a passive region of the semiconductor device, a plurality of the drains are interconnected together through a drain pad located in the passive region, and a plurality of the sources are respectively connected to a ground electrode located on a side of the substrate away from the semiconductor layer respectively through a plurality of through holes penetrating the substrate and the semiconductor layer.

[0012] Further, the respective gate pitches include at least two gate pitches which are the maximum gate pitch.

[0013] Further, the maximum gate pitch is located at a center position of the active region, and in a direction from the center position of the active region to a position away from the center position, two pitches of the maximum gate pitch and the minimum gate pitch are arranged alternately.

[0014] A second embodiment of the present disclosure further provides a semiconductor chip, wherein the semiconductor chip includes a plurality of semiconductor devices above, and the plurality of semiconductor devices are connected in parallel.

[0015] Further, a gate pitch between devices is formed between edge gates of any two adjacent semiconductor devices, and in a direction from the center position of the active region of the semiconductor chip to a position away from the center position, gate pitches between the respective devices decrease sequentially according to a third fixed value or a third change amount.

[0016] Further, the third fixed value or third change amount is less than or equal to twice of the maximum gate pitch inside the semiconductor devices in the semiconductor chip.

[0017] Further, a plurality of the semiconductor devices includes a center device located at the center of the active region and an edge device away from the center of the active region, and a center gate pitch of the edge device is different from an edge gate pitch of the center device, wherein the center gate pitch of the edge device is a gate pitch formed by two adjacent gates located at the center of the edge device, and the edge gate pitch of the center device is a gate pitch formed by any two adjacent gates away from the center of the center device.

[0018] Further, the center gate pitch of the center device is different from the center gate pitch of the edge device.

[0019] Further, in a direction from the center device to a position away from the center device, the center gate pitches of respective devices decrease sequentially according to a change amount or a fixed value.

[0020] A third embodiment of the present disclosure further provides a semiconductor chip, including a plurality of semiconductor devices, the plurality of semiconductor devices being connected in parallel, each semiconductor device including a plurality of gates, a plurality of drains, and a plurality of sources, the gates being located between the sources and the drains, wherein, in the semiconductor chip, a gate pitch is formed between any two adjacent gates, the formed respective gate pitches include at least two unequal gate pitches, the maximum gate pitch of the respective gate pitches is within a first preset range determined according to a pitch of two gates at the two outermost ends in the semiconductor chip in the gate length direction and a total number of gates of the semiconductor chip.

[0021] Further, in a plurality of the semiconductor devices, all gate pitches in at least one semiconductor device are equal.

[0022] Further, the edge gate pitches between a plurality of adjacent semiconductor devices are equal or decrease from the center of the active region to both ends.

[0023] A fourth embodiment of the present disclosure further provides a method of manufacturing a semiconductor device, including providing a substrate, forming a semiconductor layer on a side of the substrate, and forming a plurality of gates, a plurality of drains, and a plurality of sources on a side of the semiconductor layer away from the substrate, each gate being located between one of the sources and one of the drains, and the gates, sources, and drains being located in an active region of the semiconductor device, wherein a gate pitch is formed between any two adjacent gates, the formed respective gate pitches include at least two unequal gate pitches, the maximum gate pitch of the respective gate pitches is within a first preset range determined according to a pitch of two gates at the two outermost ends in the semiconductor device in the gate length direction and a total number of gates of the semiconductor device.

[0024] Compared with the prior art, the present disclosure provides a semiconductor device, a semiconductor chip, and a method of manufacturing a semiconductor device, wherein without increasing the volume of the semiconductor device, the gate pitch between adjacent gates in the semiconductor device is adjusted so that the temperature distribution during the use of the semiconductor device is more uniform, so as to reduce the heat loss of the device and increase the output power thereof. At the same time, the embodiments of the present disclosure have a simple structure, are easy for manufacturing, and are suitable for large-scale promotion.

[0025] In order to make the above-mentioned features and advantages of the present disclosure more comprehensible, example embodiments are described below in detail with reference to the accompanying drawings as follows.

BRIEF DESCRIPTION OF THE DRAWINGS

[0026] In order to describe the technical solutions of the embodiments of the present disclosure more clearly, drawings of the embodiments will be briefly described below. It should be understood that the following drawings only show some embodiments of the present disclosure and therefore should not be considered as limiting the scope. For those skilled in the art, without exercise of inventive skills, other related drawings can also be obtained based on these drawings.

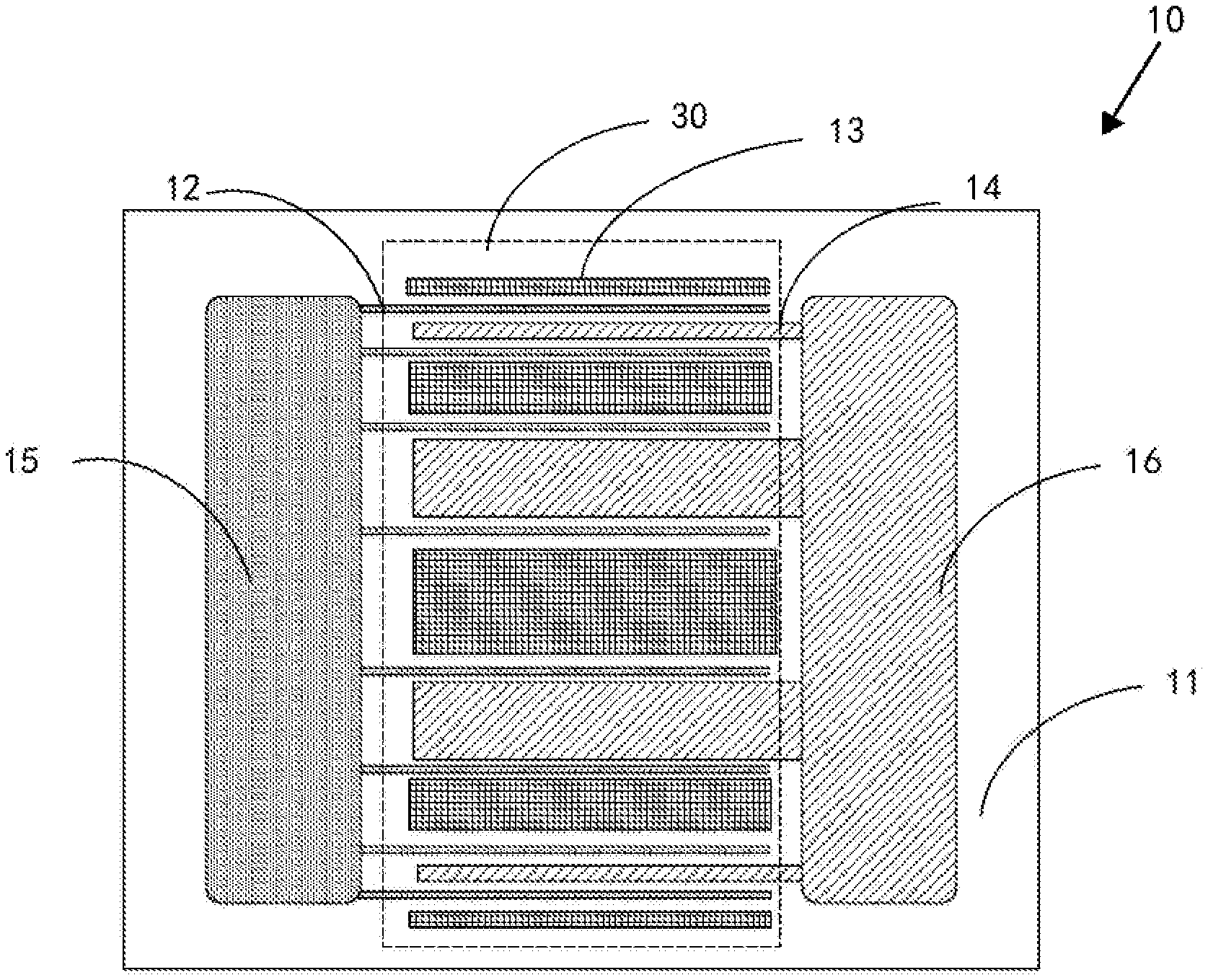

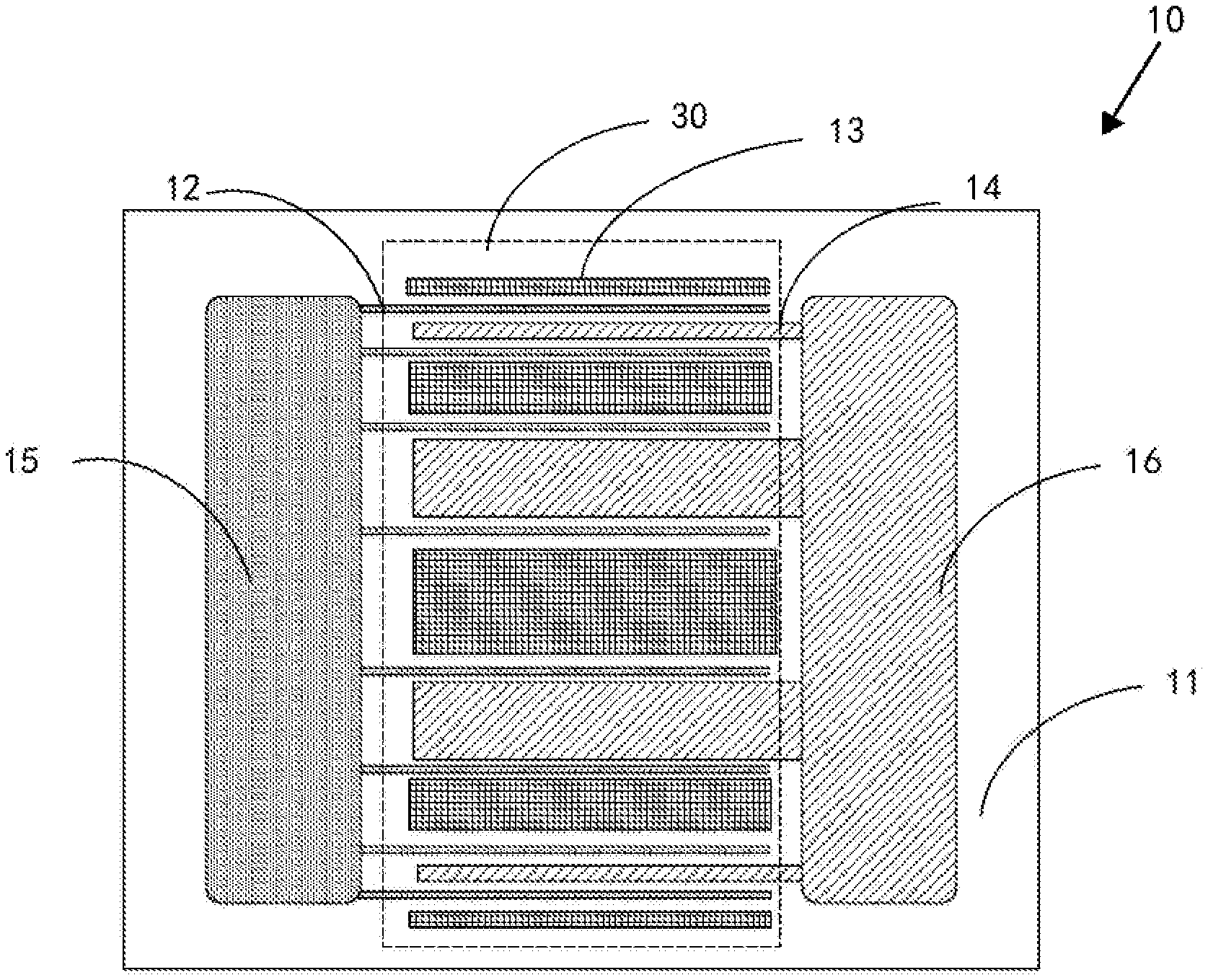

[0027] FIG. 1 is a top view of a semiconductor device provided by Embodiment one of the present disclosure.

[0028] FIG. 2 is a schematic diagram of changes of the gate pitches in the semiconductor device in Embodiment one of the present disclosure.

[0029] FIG. 3 is another schematic diagram of changes of the gate pitches in the semiconductor device in Embodiment one of the present disclosure.

[0030] FIG. 4 is a top view of a semiconductor device provided by Embodiment two of the present disclosure.

[0031] FIG. 5 is a top view of a semiconductor chip provided by Embodiment three of the present disclosure.

[0032] FIG. 6 is a top view of a semiconductor chip provided by Embodiment four of the present disclosure.

[0033] FIG. 7 is a top view of a semiconductor chip provided by Embodiment five of the present disclosure.

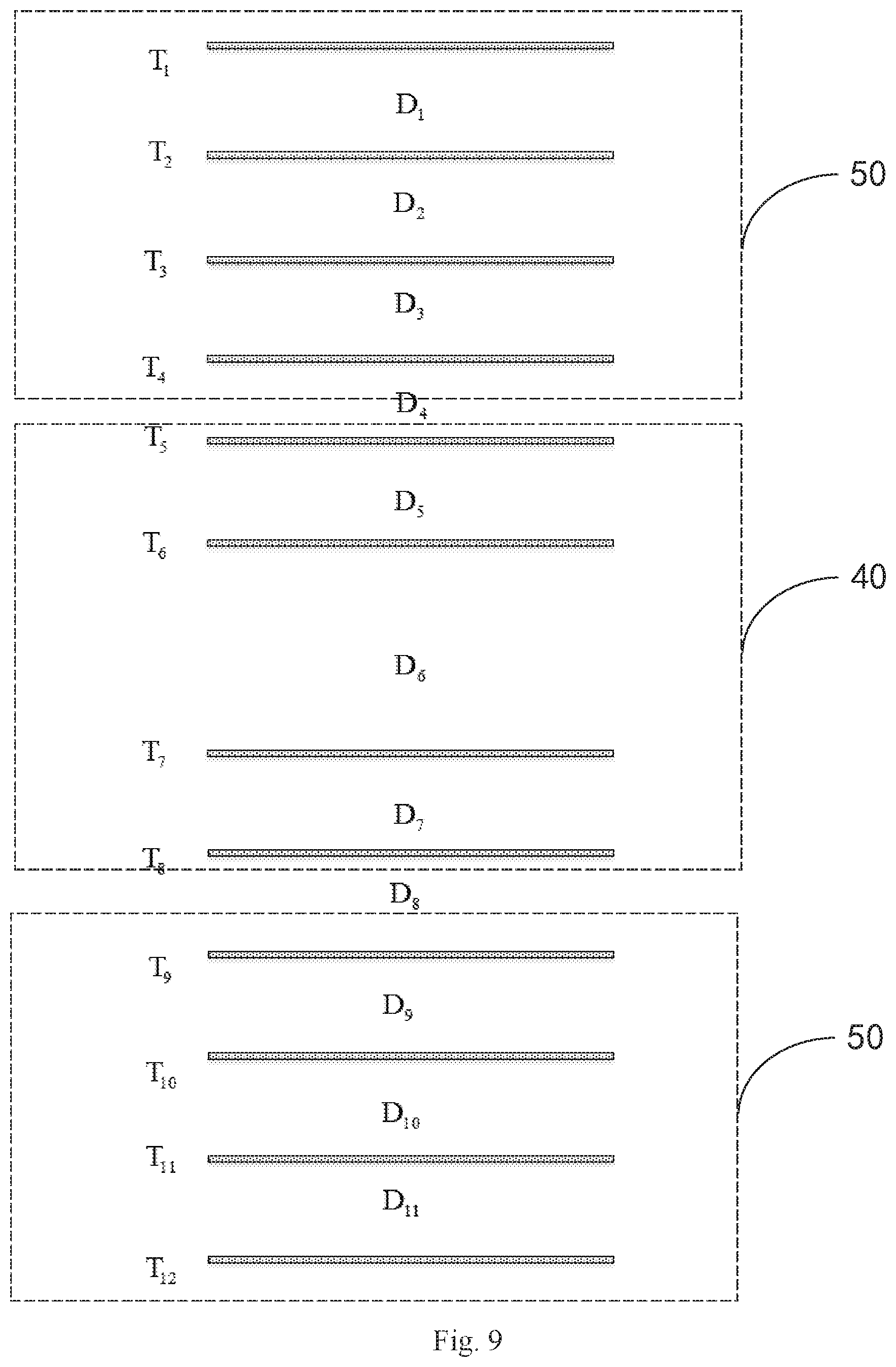

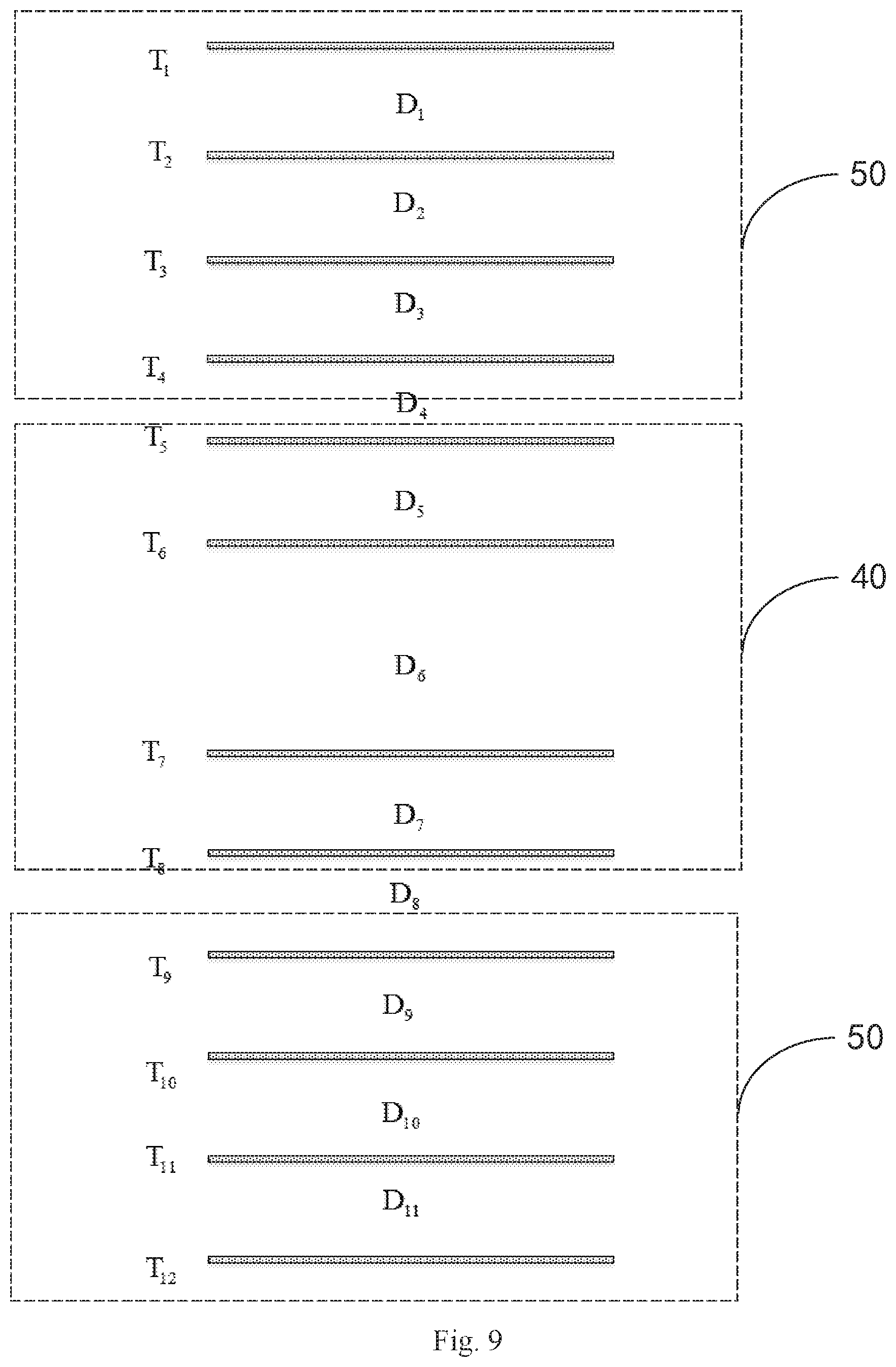

[0034] FIG. 8 is a schematic diagram of changes of the gate pitches in the semiconductor chip in Embodiment five of the present disclosure.

[0035] FIG. 9 is another schematic diagram of changes of the gate pitches in the semiconductor chip in Embodiment five of the present disclosure.

[0036] FIG. 10 is a schematic diagram of a simulation result after performing temperature simulation on a semiconductor chip in the prior art.

[0037] FIG. 11 is another schematic diagram of a simulation result after performing temperature simulation on a semiconductor chip provided by an embodiment of the present disclosure.

DETAILED DESCRIPTION

[0038] In order to clarify the technical solution and advantages of the embodiments of the present disclosure, the technical solutions of the embodiments of the present disclosure will be clearly and completely described in conjunction with the drawings of the embodiments of the present disclosure below. Obviously, the embodiments to be described refer to a part of the embodiments of the present disclosure, other than all of the embodiments. Generally, components in the embodiments of the present disclosure described and shown herein in the accompanying drawings may be arranged and designed in various different configurations.

[0039] Therefore, the following detailed descriptions of the embodiments of the present disclosure provided in the accompanying drawings are not intended to limit the claimed scope of the present disclosure, and only indicate optional embodiments of the present disclosure. All other embodiments obtained by those skilled in the art based on the embodiments of the present disclosure without any creative work fall within the protection scope of the present disclosure.

[0040] It should be noted that similar reference signs and letters represent similar items in the following drawings and thus, once a certain item is defined in a drawing, it is not required to be further defined and explained in the following drawings. In the description of the present disclosure, terms "first", "second", "third", "fourth" and the like are only adopted for distinctive description and should not be understood to indicate or imply relative importance.

[0041] In the description of the present disclosure, unless specified or limited otherwise, the terms "mounted", "coupled", "connected" should be explained broadly, and may be, for example, fixed connections, detachable connections, or integral connections; may also be mechanical or electrical connections; may also be direct connections or indirect connections via intervening structures; may also be inner communications of two elements. Those skilled in the art can understand the real meanings of the terms in the present disclosure based on the particular condition.

[0042] In the prior art, in common semiconductor devices, the heat dissipation problem during the use of the semiconductor device is mainly solved in the following three ways.

[0043] (1) Using substrate materials with higher thermal conductivity for the manufacture of semiconductor devices; for instance, polishing off the silicon carbide substrate, and forming a diamond film or a diamond-like carbon film on the back of the epitaxial layer by Chemical Vapor Deposition (CVD), sputtering, or bonding etc. However, the disadvantage of such a method is increase in the process complexity and cost.

[0044] (2) Optimizing the packaging process; for instance, using a tube shell structure etc. with better heat dissipation effect. However, the disadvantage of such a method is that the temperature inside the semiconductor device cannot be effectively, uniformly and timely dissipated through the tube shell, resulting in the temperature at the center of the device still being the highest and the temperature inside the device still being unevenly distributed.

[0045] (3) Adjusting the gate pitch; for instance, while increasing the pitch between adjacent gates or reducing the length of the gates, increasing the gates to achieve the same net active region. However, such a method would cause the heat load generated in the center of the chip to spread in a wider range. Especially in a semiconductor chip composed of a plurality of semiconductor devices, this will result in a larger semiconductor chip area and reduce the number of chips per wafer.

[0046] In summary, the existing three heat dissipation solutions have certain limitations when solving the heat dissipation problem of semiconductor devices. In this regard, the inventor found through research that the heat of the existing semiconductor device is mainly generated in the active region of the device, especially the gate position, then, at the center of the active region of the semiconductor device, by increasing the lengths of the source ohms and drain ohms in the gate length direction, the distances between adjacent gate fingers are increased to reduce the distance between adjacent temperature peak points to achieve the purpose of improving the temperature distribution gradient, to improve the problem of heat dissipation at the center position of the semiconductor device. Specifically, it will be described in details in conjunction with different embodiments below.

Embodiment One

[0047] FIG. 1 is a top view of a semiconductor device provided by Embodiment one of the present disclosure. The semiconductor device 10 includes a substrate, a semiconductor layer 11, a plurality of gates 12, a plurality of drains 14, and a plurality of sources 13. The semiconductor layer 11 is located on one side of the substrate, and the plurality of gates 12, the plurality of drains 14, and the plurality of sources 13 are located on a side of the semiconductor layer 11 away from the substrate, the gates 12 are located between the sources 14 and the drains 13, and the plurality of gates 12, the plurality of drains 14, and the plurality of sources 13 are located in an active region 30 of the semiconductor device 10. Alternatively, the gate 12 may be, but not limited to, a stripe gate.

[0048] Further, during the use of the semiconductor device 10, since the position of the gate 12 is a region where the source leakage current and the electric field are concentrated and meanwhile is the center region where the semiconductor device 10 generates heat, the temperature at the position of the gate 12 is higher than the nearby position. In addition, the region of the gate 12 located at the center position of the active region 30 of the semiconductor device 10 is less likely to dissipate the generated heat in time to the outside of the device, so the center position of the semiconductor device 10 is the highest temperature point of the entire device. However, excessively high temperature at the center will greatly increase the heat loss of the device and reduce the output power of the device. With regards to the above problem, in the semiconductor device 10 given in Embodiment one, a gate pitch is formed between any two adjacent gates 12, the formed respective gate pitches include at least two unequal gate pitches, wherein the maximum gate pitch of the respective gate pitches is within a first preset range determined according to a pitch of two gates 12 at the two outermost ends in the semiconductor device 10 in the gate length direction and a total number of gates 12 of the semiconductor device 10. In Embodiment one, through the foregoing design of the semiconductor device 10, the temperature distribution in the semiconductor device 10 can be made more uniform, and the problem of failure of the semiconductor device 10 caused by excessively high temperature of the center of the device can be avoided. Meanwhile, the embodiment of the present disclosure may also effectively reduce the heat loss of the semiconductor device 10 and improve the reliability and output power thereof by adjusting the respective gate pitches in the semiconductor device 10.

[0049] Alternatively, in an embodiment, the first preset range is (L/(n-1), L), that is, the maximum gate pitch L.sub.max of the respective gate pitches satisfies the following condition:

L n - 1 < L max < L , ##EQU00001##

where L is the pitch of two gates 12 at the two outermost ends in the semiconductor device 10 in the gate length direction, and n is the total number of gates 12 of the semiconductor device 10, n being an integer greater than 2.

[0050] Specifically, as shown in FIG. 2, assuming that the semiconductor device 10 includes n gates 12, which are T.sub.1, T.sub.2, T.sub.3, T.sub.4, T.sub.5, . . . T.sub.n-2, T.sub.n-1, T.sub.n, respectively, the gate pitches formed between respective adjacent gates 12 are D.sub.1, D.sub.2, D.sub.3, D.sub.4, D.sub.5, . . . D.sub.n-2, D.sub.n-1, D.sub.n; the pitch of two gates T.sub.1 and T.sub.n at the two outermost ends in the semiconductor device 10 in the gate length direction is L, assuming that the maximum gate pitch of the respective gate pitches is D.sub.4, the maximum gate pitch D.sub.4 satisfies

L n - 1 < D 4 < L . ##EQU00002##

Preferably, considering the actual area utilization rate of the active region 30 of the device, the maximum gate pitch satisfies the following condition:

L n - 1 < L max < ( n - 1 ) L n . ##EQU00003##

[0051] Further, referring to FIG. 2 again, the minimum gate pitch of the respective gate pitches is within a second preset range determined according to a pitch of two gates 12 at the two outermost ends in the semiconductor device 10 in the gate length direction and a total number of gates 12 of the semiconductor device 10, the second preset range is (L/(n-1).sup.2, L/(n-1)), that is, the minimum gate pitch L.sub.min satisfies the following condition:

L ( n - 1 ) 2 < L min < L n - 1 , ##EQU00004##

where L is the pitch of two gates 12 at the two outermost ends in the semiconductor device 10 in the gate length direction, and n is the total number of gates 12 of the semiconductor device 10. Preferably, in order to reduce the difference between the highest temperature and the lowest temperature, and to balance the heat distribution of the entire device, the minimum gate pitch L.sub.min is greater than or equal to L/2(n-1). Specifically, assuming that the minimum gate pitch of the respective gate pitches as shown in FIG. 2 is D.sub.1, then the minimum gate pitch D.sub.1 satisfies:

L ( n - 1 ) 2 < D 1 < L n - 1 . ##EQU00005##

[0052] In another embodiment, in order to further meet the combination of the internal structure requirements of the device and the planar layout, the maximum gate pitch L.sub.max is located between adjacent gates 12 on both sides of the source 13, and the minimum gate pitch L.sub.min is located between adjacent gates 12 on both sides of the drain 14. Based on the setting of the gate pitch in the semiconductor device 10 above, on the premise of ensuring the reduction of the heat loss of the semiconductor device 10 and improving the reliability and output power thereof, there are various design forms of the respective gate pitches.

[0053] For instance, as shown in FIG. 2 again, the gate pitch D.sub.4 of the respective gate pitches is the maximum, that is, the maximum gate pitch L.sub.max is between adjacent gates 12 on both sides of the source 13, the source 13 is located within D.sub.4, the gate pitch D.sub.1 is the minimum, and the drain 14 is located within D.sub.1, that is, the minimum gate pitch L.sub.min is located between adjacent gates 12 on both sides of the drain 14, thus, other gate pitches may be set to be less than or equal to D.sub.4, or greater than or equal to D.sub.1, for instance, the respective gate pitches may include at least two gate pitches as the maximum gate pitch, or the respective gate pitches may include at least two gate pitches as the minimum gate pitch, etc.; the maximum gate pitch may be located at a center position of the active region 30, and in a direction from the center position of the active region 30 to a position away from the center position, two pitches of the maximum gate pitch and the minimum gate pitch are arranged alternately.

[0054] For another instance, the plurality of gate pitches formed by the plurality of gates 12 may sequentially decrease in a direction from a center position of the active region 30 to a position away from the center position according to a change amount or a fixed value; for example, the differences between any two adjacent gate pitches may either be the same or substantially the same, or decrease sequentially according to an arbitrary value, which is not limited herein in Embodiment one. In addition, it can be understood that in Embodiment one, if there are an even number of gate pitches in the active region 30 of the semiconductor device 10, the two gate pitches located at the center position of the active region 30 are equal and other gate pitches away from the center position relatively decrease. Specifically, as shown in FIG. 3, assuming that the total number n of the gates 12 included in the semiconductor device 10 is 8, the two gates 12 at the center position of the active region 30 are T.sub.4 and T.sub.5, and the gate pitch D.sub.4 between T.sub.4 and T.sub.5 is greater than the gate pitches formed by other adjacent gates 12 away from the center position. Accordingly, from the position where D.sub.4 is located to the edge positions on both sides of the active region 30, the gate pitches may decrease sequentially according to a change amount or a fixed value; for instance, the difference between D.sub.3 and D.sub.4 is equal to the difference between D.sub.2 and D.sub.1, the difference between D.sub.2 and D.sub.1 is equal to the difference between D.sub.2 and D.sub.3, the difference between D.sub.4 and D.sub.3 is equal to the difference between D.sub.5 and D.sub.6, and so on.

[0055] For another instance, in the actual design of respective gate pitches, in order to effectively balance the heat distribution, in a direction from the center position of the active region 30 to a position away from the center position of a plurality of gate pitches formed by the plurality of gates 12, other gate pitches may be arranged at equal pitches in order in a direction from the center position of the active region 30 to a position away from the center position, where the equal pitch may be the minimum gate pitch, or the pitch value of the equal pitch arrangement may also be any pitch value greater than the minimum gate pitch and smaller than the maximum gate pitch.

[0056] Further, the substrate may be formed of one of sapphire, silicon carbide (SiC), silicon (Si), lithium niobate, silicon-on-insulator, gallium nitride (GaN), aluminum nitride (AlN), or any other material suitable for growing group III nitrides, which is not specifically limited in the present disclosure. The material of the semiconductor layer 11 may be, but not limited to, a group III nitride semiconductor material such as AlGaN, AlN, or InAlN.

[0057] In addition, a gate pad 15 and a drain pad 16 are provided in the passive region of the semiconductor device 10, and the gate pad 15 and the drain pad 16 are located on both sides of the active region 30, respectively. A plurality of the gates 12 are interconnected by the gate pad 15 located in the passive region of the semiconductor device 10, and a plurality of the drains 14 are interconnected by the drain pad 16 located in the passive region, wherein the gate pad 15 and the drain pad 16 may be, but not limited to, metal pads, which is not limited in this embodiment.

[0058] Alternatively, in the semiconductor chip 20, the gate pad 15, and the drain pad 16 located in the passive region may be jointly belong to the same semiconductor device 10, or may be provided by different semiconductor devices 10 together to constitute the semiconductor device 10 given in Embodiment one, that is, different semiconductor devices 10 may share a gate pad 15 or a drain pad 16, which is not specifically limited in Embodiment one.

[0059] Further, the semiconductor device 10 further includes a ground electrode located on a side of the substrate away from the semiconductor layer 11, and the plurality of sources 13 may be connected to the ground electrode located on a side of the substrate away from the semiconductor layer 11 through a plurality of through holes penetrating the substrate and the semiconductor layer 11, respectively.

Embodiment Two

[0060] In order to reduce the inductance and parasitic capacitance of the device, the source 13 needs to be provided with a through hole; therefore, the gate pitches on both sides of the adjacent source 13 and drain 14 are different. As shown in FIG. 4, the gate finger pitch of both sides of the source 13 is d1, and the gate finger pitch of both sides of the drain 14 is d2, generally, the gate pitches d1 and d2 of both sides of the adjacent source 13 and drain 14 satisfy d2.ltoreq.d1.ltoreq.3d2. In order to reduce device losses and effectively balance the heat distribution, the maximum gate pitch is located at the center position of the active region 30, in a direction from the center position of the active region 30 to a position away from the center position, the respective pitches between adjacent gates 12 on both sides of the source 13 decrease sequentially according to a first fixed value or a first change amount, and the respective pitches between adjacent gates 12 on both sides of the drain 14 decrease sequentially according to a second fixed value or a second change amount. The first fixed value or the first change amount is not equal to the second fixed value or the second change amount.

Embodiment Three

[0061] Based on the design and description of the semiconductor device 10 given in Embodiment one, as shown in FIG. 5, Embodiment three of the present disclosure further provides a semiconductor chip 20 including a plurality of semiconductor devices 10, and the plurality of semiconductor devices 10 are connected in parallel. A gate pitch between devices is formed between edge gates 12 of any two adjacent semiconductor devices 10 of the semiconductor chip 20, and the gate pitches between devices decrease sequentially according to a third fixed value or a third change amount. The setting of the gate pitch between the semiconductor devices 10 in the semiconductor chip 20 can effectively alleviate the heat generation between the device edges and balance the heat distribution of the entire chip. It should be understood that the semiconductor device 10 given in this embodiment has the same structural features as the semiconductor device 10 described in Embodiment one, so this embodiment will not repeat them.

[0062] Alternatively, in order to improve the heat distribution while obtaining a better chip layout, in an embodiment, the third fixed value or the third change amount is less than or equal to twice of the maximum gate pitch inside the semiconductor device 10 in the semiconductor chip 20. Alternatively, when the plurality of semiconductor devices 10 include a center device 40 located at the center of the active region 30 and an edge device 50 away from the center of the active region 30, the center gate pitch of the edge device 50 is defined as the gate pitch formed by two adjacent gates 12 at the center of the edge device 50, and the edge gate pitch of the center device 40 is defined as the gate pitch formed by any two adjacent gates 12 away from the center of the center device 40. Then, the center gate pitch of the edge device 50 is different from the edge gate pitch of the center device 40, for instance, the center gate pitch of the edge device 50 may be greater or smaller than the edge gate pitch of the center device 40, or the center gate pitch of the center device 40 is different from the center gate pitch of the edge device 50, for instance, the center gate pitch located at the center device 40 is greater than the center gate pitch of the edge device 50, or the center gate pitch of each edge device 50 decreases sequentially according to a change amount or a fixed value, and so on.

Embodiment Four

[0063] As shown in FIG. 6, Embodiment 4 of the present disclosure further provides a semiconductor chip 20 including a plurality of semiconductor devices 10, and the plurality of semiconductor devices 10 are connected in parallel. A gate pitch L between devices is formed between edge gates 12 of any two adjacent semiconductor devices 10 of the semiconductor chip 20. The distribution rule of the gate pitches inside the plurality of semiconductor devices 10 is the same; alternatively, the pitches of the gates 12 on both sides of the source 13 inside the semiconductor device 10 are equal and d1, the pitches of the gates 12 on both sides of the drain 14 inside the semiconductor device 10 are equal and d2, and they satisfy d2.ltoreq.d1.ltoreq.2d2 and are arranged alternately inside each semiconductor device 10. The distance L between the edge gates 12 of two adjacent semiconductor devices 10 at the center of the active region 30 of the semiconductor chip 20 is the largest, in a direction from the center position of the active region 30 of the semiconductor chip 20 to a position away from the center position, the gate pitches between devices gradually decrease, and .DELTA.L.ltoreq.2d1. In practical applications, the center loss of the active region 30 is adjusted according to the size of the chip, alternatively, at least two identical gate pitches between devices may be set near the center position of the active region 30 of the semiconductor chip 20.

Embodiment Five

[0064] FIG. 7 is a top view of a semiconductor chip provided by Embodiment five of the present disclosure. The semiconductor chip 20 includes a plurality of semiconductor devices 10 which are connected in parallel. Each semiconductor device 10 includes a plurality of gates 12, a plurality of drains 14, and a plurality of sources 13, the gates 12 being located between the sources 13 and the drains 14. Therein, in the semiconductor chip 20, a gate pitch is formed between any two adjacent gates 12, the formed respective gate pitches include at least two unequal gate pitches, the maximum gate pitch of the respective gate pitches is within a first preset range determined according to a pitch of two gates 12 at the two outermost ends in the semiconductor chip 20 in the gate length direction and a total number of gates 12 of the semiconductor chip 20.

[0065] Specifically, as shown in FIG. 8, assuming that the pitch of two gates 12 at the two outermost ends in the semiconductor device 20 in the gate length direction is L and the total number of gates 12 of the semiconductor device 20 is n, the first preset range satisfies (L/(n-1), L), that is, the maximum gate pitch L.sub.max in the semiconductor device 20 satisfies

L n - 1 < L max < L . ##EQU00006##

Alternatively, in actual implementation, the minimum gate pitch L.sub.min of the gate pitches satisfies

L ( n - 1 ) 2 < L min < L n - 1 . ##EQU00007##

By setting the gate pitch in the semiconductor chip 20, the heat dissipation performance of the semiconductor chip 20 may be effectively improved while maintaining the overall size and output power of the chip.

[0066] Compared with the above-mentioned Embodiment three, Embodiment five is different in that in the plurality of semiconductor devices 10 in the semiconductor chip 20 given in this embodiment, all the gate pitches in at least one semiconductor device 10 are equal. For instance, as shown in FIG. 9, assuming that the semiconductor chip 20 includes three semiconductor devices 10, which are one center device 40 and two edge devices 50 on both sides of the central device 40, respectively, all the gate pitches in the respective edge devices 50 may be equal, such as D.sub.1=D.sub.2=D.sub.3, D.sub.9=D.sub.10=D.sub.11, and so on. It should be noted that, in addition to this, in this embodiment, the structure of each semiconductor device 10 in the above-mentioned semiconductor chip 20 may also refer to the specific description of each gate pitch of the semiconductor device 10 in the above-mentioned Embodiment one; for instance, in the plurality of gate pitches formed by the plurality of gates 12, in a direction from the center position of the active region 30 of the semiconductor chip 20 to a position away from the center position, the respective gate pitches decrease sequentially according to a fixed value or a change amount, etc. This embodiment will not repeat them here specifically.

[0067] Compared with Embodiment three, this embodiment also provides that the edge gate pitches between a plurality of adjacent semiconductor devices 10 in the semiconductor chip 20 are equal or decrease from the center of the active region 30 to both ends. As an example form, the gate pitches in the plurality of semiconductor devices 10 in the semiconductor chip 20 are distributed at equal intervals, and the edge gate pitches between adjacent semiconductor devices 10 are not equal to the gate pitches in the semiconductor device 10. The gate pitch in the plurality of semiconductor devices 10 is the minimum gate pitch L.sub.min, and the edge gate pitch between adjacent semiconductor devices 10 is the maximum pitch L.sub.max, and the edge gate pitches between a plurality of adjacent semiconductor devices 10 are equal or the edge gate pitches between adjacent semiconductor devices 10 decrease from the center of the active region 30 to both sides.

[0068] Further, based on the design and description of the semiconductor device 10 and the semiconductor chip 20 described above, the present disclosure takes the semiconductor chip 20 as shown in FIG. 5 as an example to perform a thermal simulation setting experiment on the semiconductor chip 20. As shown in FIGS. 10 and 11, the experimental results show that while fixing the positions of the two outermost gates 12 in the semiconductor chip 20, the gate pitches between the respective gates 12 are adjusted, which can cause the maximum temperature T. and the minimum temperature T.sub.min in the semiconductor chip 20 to change accordingly. Therein, when the gate pitches between adjacent gates 12 are equal (where the semiconductor chip 20 with the same gate pitches are equal is of the structure of the semiconductor chip 20 in the prior art), as shown in FIG. 10, in such a device structure with the same gate pitches, the difference between the maximum temperature T.sub.max and the minimum temperature T.sub.min of the device is great, and the temperature distribution of the device is not uniform, and at the time .DELTA.T value is relatively great. However, as shown in FIG. 11, in the embodiment of the present disclosure, by adjusting the gate pitches, the lowest .DELTA.T value can be changed and obtained, and problems such as degradation of the radio frequency performance of the semiconductor device 10 due to the structure of the equally-spaced gate pitches in the prior art may be effectively avoided.

Embodiment Six

[0069] Embodiment six of the present disclosure also provides a method of manufacturing a semiconductor device 10. The method of manufacturing the semiconductor device 10 will be described below in conjunction with specific steps.

[0070] At step S100, a substrate is provided.

[0071] Therein, the material of the substrate is as described above, and will not be repeated here. The method of forming the substrate may include Chemical Vapor Deposition, (CVD), Vapour Phase Epitaxy (VPE), Metal-organic Chemical Vapor Deposition (MOCVD), Low Pressure Chemical Vapor Deposition (LPCVD), Plasma Enhanced Chemical Vapor Deposition (PECVD), Pulsed Laser Deposition (PLD), atomic layer epitaxy, Molecular Beam Epitaxy (MBE), sputtering, evaporation, etc., which will not be limited in this embodiment specifically.

[0072] At step S200, a semiconductor layer 11 is formed on a side of the substrate.

[0073] The method of forming the semiconductor layer 11 on the substrate may include, but is not limited to, the method of forming the substrate, in other words, the method of forming the semiconductor layer 11 may be the same as or different from the method of forming the substrate.

[0074] At step S300, a plurality of gates 12, a plurality of drains 14, and a plurality of sources 13 are formed on a side of the semiconductor layer 11 away from the substrate, each gate 12 being located between one of the sources 13 and one of the drains 14, and the gates 12, sources 13, and drains 14 being located in an active region 30 of the semiconductor device 10. Therein, a gate pitch is formed between any two adjacent gates 12, the maximum gate pitch of the respective gate pitches is within a first preset range determined according to a pitch of two gates 12 at the two outermost ends in the semiconductor device 10 in the gate length direction and a total number of gates 12 of the semiconductor device 10.

[0075] In addition, the first preset range is (L/(n-1), L), the minimum gate pitch of the respective gate pitches is within a second preset range determined according to a pitch of two gates 12 at the two outermost ends in the semiconductor device 10 in the gate length direction and a total number of gates 12 of the semiconductor device 10, the second preset range is (L/(n-1).sup.2, L/(n-1)), where L is the pitch of two gates 12 at the two outermost ends in the semiconductor device 10 in the gate length direction, and n is the total number of gates 12 of the semiconductor device 10.

[0076] In summary, the present disclosure provides a semiconductor device 10, a semiconductor chip 20, and a method of manufacturing a semiconductor device 10, wherein, by adjusting the gate pitches between adjacent gates 12 in the semiconductor device 10 without increasing the volume of the semiconductor device 10, the temperature distribution during the use of the semiconductor device 10 is more uniform, which reduces the device heat loss and increase the output power thereof. Meanwhile, the structure in the embodiments of the present disclosure is simple, easy to manufacture, and suitable for large-scale promotion.

[0077] Obviously, those skilled in the art should understand that the functions of the embodiments of the present disclosure described above may be implemented by a general-purpose computing device, they may be concentrated on a single computing device, or distributed on a network composed of a plurality of computing devices, alternatively, they may be implemented with existing program codes or algorithms executable by a computing device, thus they may be stored in a storage device and executed by a computing device, or they may be made into individual integrated circuit modules, or a plurality of modules or steps in them may be made into a single integrated circuit module for implementation. In this way, the functional implementation of the present disclosure is not limited to any specific combination of hardware and software.

[0078] The above are only example embodiments of the present disclosure and are not intended to limit the present disclosure. For those skilled in the art, the present disclosure may have various modifications and changes. Any modification, equivalent replacement, improvement, etc. made within the spirit and principle of the present disclosure should be included in the protection scope of the present disclosure.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

D00009

D00010

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.