Packaging Substrate

McDonald; John ; et al.

U.S. patent application number 16/370590 was filed with the patent office on 2020-10-01 for packaging substrate. The applicant listed for this patent is Silego Technology Inc.. Invention is credited to David Chow, John McDonald, Tom Truong.

| Application Number | 20200312795 16/370590 |

| Document ID | / |

| Family ID | 1000004169318 |

| Filed Date | 2020-10-01 |

View All Diagrams

| United States Patent Application | 20200312795 |

| Kind Code | A1 |

| McDonald; John ; et al. | October 1, 2020 |

Packaging Substrate

Abstract

A packaging substrate and a method for mounting an integrated circuit and/or a circuit component is presented. The packaging substrate has an upper surface for mounting the integrated circuit and/or circuit component, a non-conductive material, an inductor structure at least partially embedded in the non-conductive material. The inductor structure has i) a first conductive material at least partially on a first layer, ii) a second conductive material at least partially on a second layer, and iii) a plurality of conductive pillars, wherein the first conductive material, the second conductive material and the conductive pillars are arranged to form a first coil having an inductance. The first coil is arranged as one of a) a solenoid having an axis that is approximately parallel to the upper surface of the packaging substrate, and b) a toroid.

| Inventors: | McDonald; John; (Sunnyvale, CA) ; Truong; Tom; (Sunnyvale, CA) ; Chow; David; (Sunnyvale, CA) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 1000004169318 | ||||||||||

| Appl. No.: | 16/370590 | ||||||||||

| Filed: | March 29, 2019 |

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 23/645 20130101; H01L 28/10 20130101; H01L 23/49894 20130101; H01L 23/49838 20130101 |

| International Class: | H01L 23/64 20060101 H01L023/64; H01L 23/498 20060101 H01L023/498; H01L 49/02 20060101 H01L049/02 |

Claims

1. A packaging substrate for mounting an integrated circuit and/or a circuit component comprising: an upper surface for mounting the integrated circuit and/or circuit component; a non-conductive material; an inductor structure at least partially embedded in the non-conductive material and comprising: i) a first conductive material at least partially on a first layer; ii) a second conductive material at least partially on a second layer; and iii) a plurality of conductive pillars; wherein: the first conductive material, the second conductive material and the conductive pillars are arranged to form a first coil having an inductance; and the first coil is arranged as one of: a) a solenoid having an axis that is approximately parallel to the upper surface of the packaging substrate; and b) a toroid.

2. The packaging substrate of claim 1, wherein: the first conductive material is discontinuous, such that the first conductive material comprises a plurality of first conductive portions on the first layer; and the second conductive material is discontinuous, such that the second conductive material comprises a plurality of second conductive portions on the second layer; wherein: each of the first conductive portions is coupled to at least one of the second conductive portions by at least one conductive pillar.

3. The packaging substrate of claim 2, wherein at least one of the first conductive portions is coupled to one of the second conductive portions by a first conductive pillar and is coupled to another of the second conductive portions by a second conductive pillar.

4. The packaging substrate of claim 3, wherein: each of the first conductive portions is coupled to two conductive pillars; and for each first conductive portion, the two conductive pillars are coupled to different second conductive portions.

5. The packaging substrate of claim 3, wherein: the first coil is arranged as a toroid having an inner circumference and an outer circumference around a central axis; and the inner circumference is closer to the central axis than the outer circumference on a line extending outward from the central axis.

6. The packaging substrate of claim 5, wherein the conductive pillars at or near the inner circumference are smaller than the conductive pillars at or near the outer circumference.

7. The packaging substrate of claim 5, wherein: for each of the first conductive portions, there are less conductive pillars at or near the inner circumference used to couple to one second conductive portion than at or near the outer circumference used to couple to another second conductive portion.

8. The packaging substrate of claim 1, wherein the non-conductive material is a plastic.

9. The packaging substrate of claim 1, wherein at least one of the first conductive material, the second conductive material and the conductive pillars comprises at least one of copper and aluminium.

10. The packaging substrate of claim 1, wherein the first coil at least partially encloses a magnetic material.

11. The packaging substrate of claim 1, wherein the packaging substrate is one of a molded interconnect substrate and a laminate substrate.

12. The packaging substrate of claim 1, comprising a lower surface opposite to the upper surface.

13. The packaging substrate of claim 12, wherein the lower surface is for mounting to a printed circuit board (PCB).

14. The packaging substrate of claim 1 comprising a second coil having an inductance and arranged with the first coil to form a transformer or a coupled inductor.

15. The packaging substrate of claim 14, wherein the second coil comprises: i) the first conductive material; ii) the second conductive material; and iii) another plurality of conductive pillars.

16. The packaging substrate of claim 14, wherein the first and second coils are arranged as a toroid transformer wound in a double helix configuration.

17. The packaging substrate of claim 1, wherein at least one of the first and second conductive materials are formed using routing traces.

18. The packaging substrate of claim 1, wherein the conductive pillars comprises at least one via.

19. A method of providing a packaging substrate for mounting an integrated circuit and/or a circuit component comprising: an upper surface for mounting the integrated circuit and/or circuit component; a non-conductive material; an inductor structure at least partially embedded in the non-conductive material and comprising: i) a first conductive material at least partially on a first layer; ii) a second conductive material at least partially on a second layer; and iii) a plurality of conductive pillars; wherein: the first conductive material, the second conductive material and the conductive pillars are arranged to form a first coil having an inductance; and the first coil is arranged as one of: a) a solenoid having an axis that is approximately parallel to the upper surface of the packaging substrate; and b) a toroid.

Description

[0001] The present disclosure relates to a packaging substrate for mounting an integrated circuit and/or a circuit component. In particular the present disclosure relates to a packaging substrate comprising an inductor structure.

BACKGROUND

[0002] The field of electronic packaging relates to the design and fabrication of enclosures for electronic devices and systems. In modern consumer devices there is pressure for components to be smaller so that more functionality can be implemented in each device.

[0003] An inductor may be implemented in a circuit in a number of different ways, which may be dependent on the specific application and the physical constraints imposed by the manufacturing processes available. For example, spiral inductors may be fabricated on a silicon chip. Such structures are substantially planar which takes advantage of the planar metal layers in the chip fabrication process and therefore they are easy to build and have consistency in their performance. However, due to their structural limitations, spiral inductors may have a lower inductance than off-chip inductors and can be highly susceptible to nearby magnetic fields.

[0004] Electromagnetic (EM) susceptibility is reciprocal, and therefore since EM fields of a spiral inductor are not well contained, the spiral inductor affects and is affected by external EM fields. In essence, a spiral inductor may function as an antenna. In switching power supply applications, such electromagnetic interference (EMI) can be problematic, as the switching currents in the inductor can generate undesirable EM radiation that interferes with other electronic devices. Another effect of undesired coupling is that power is lost through the coupling.

[0005] Inductors may also be formed using a chip's bondwires. These inductors are cheap, however they have limited current capability and may have variable tolerances.

[0006] Known off-chip inductors, which may be mounted on a printed circuit board (PCB) include integrated iron core inductors which may be provided in a toroidal or solenoidal configuration. These inductors offer a high inductance per unit area, however can be costly to manufacture. An advantage of certain geometries such as toroids when compared to spiral inductors, is that magnetic fields associated with the circuit operation are more contained, and thus better for EMI and efficiency.

SUMMARY

[0007] It is desirable to provide an improved packaging substrate that comprises an inductor that overcomes or mitigates one or more of the above-mentioned problems.

[0008] According to a first aspect of the disclosure there is provided a packaging substrate for mounting an integrated circuit and/or a circuit component comprising an upper surface for mounting the integrated circuit and/or circuit component, a non-conductive material, an inductor structure at least partially embedded in the non-conductive material and comprising i) a first conductive material at least partially on a first layer, ii) a second conductive material at least partially on a second layer, and iii) a plurality of conductive pillars, wherein the first conductive material, the second conductive material and the conductive pillars are arranged to form a first coil having an inductance, and the first coil is arranged as one of a) a solenoid having an axis that is approximately parallel to the upper surface of the packaging substrate, and b) a toroid.

[0009] Optionally, the first conductive material is discontinuous, such that the first conductive material comprises a plurality of first conductive portions on the first layer, and the second conductive material is discontinuous, such that the second conductive material comprises a plurality of second conductive portions on the second layer, wherein each of the first conductive portions is coupled to at least one of the second conductive portions by at least one conductive pillar.

[0010] Optionally, at least one of the first conductive portions is coupled to one of the second conductive portions by a first conductive pillar and is coupled to another of the second conductive portions by a second conductive pillar.

[0011] Optionally, each of the first conductive portions is coupled to two conductive pillars, and for each first conductive portion, the two conductive pillars are coupled to different second conductive portions.

[0012] Optionally, the first coil is arranged as a toroid having an inner circumference and an outer circumference around a central axis, and the inner circumference is closer to the central axis than the outer circumference on a line extending outward from the central axis.

[0013] Optionally, the conductive pillars at or near the inner circumference are smaller than the conductive pillars at or near the outer circumference.

[0014] Optionally, for each of the first conductive portions, there are less conductive pillars at or near the inner circumference used to couple to one second conductive portion than at or near the outer circumference used to couple to another second conductive portion.

[0015] Optionally, the non-conductive material is a plastic.

[0016] Optionally, at least one of the first conductive material, the second conductive material and the conductive pillars comprises at least one of copper and aluminium.

[0017] Optionally, the first coil at least partially encloses a magnetic material.

[0018] Optionally, the packaging substrate is one of a molded interconnect substrate and a laminate substrate.

[0019] Optionally, the packaging substrate comprises a lower surface opposite to the upper surface.

[0020] Optionally, the lower surface is for mounting to a printed circuit board (PCB).

[0021] Optionally, the packaging substrate comprises a second coil having an inductance and arranged with the first coil to form a transformer or a coupled inductor.

[0022] Optionally, wherein the second coil comprises i) the first conductive material, ii) the second conductive material, and iii) another plurality of conductive pillars.

[0023] Optionally, the first and second coils are arranged as a toroid transformer wound in a double helix configuration.

[0024] Optionally, at least one of the first and second conductive materials are formed using routing traces.

[0025] Optionally, the conductive pillars comprises at least one via.

[0026] According to a second aspect of the disclosure there is provided a method of providing a packaging substrate for mounting an integrated circuit and/or a circuit component comprising an upper surface for mounting the integrated circuit and/or circuit component, a non-conductive material, an inductor structure at least partially embedded in the non-conductive material and comprising i) a first conductive material at least partially on a first layer, ii) a second conductive material at least partially on a second layer, and iii) a plurality of conductive pillars, wherein the first conductive material, the second conductive material and the conductive pillars are arranged to form a first coil having an inductance, and the first coil is arranged as one of a) a solenoid having an axis that is approximately parallel to the upper surface of the packaging substrate, and b) a toroid.

[0027] It will be appreciated that the method of the second aspect may include providing and/or using features set out in the first aspect and can incorporate other features as described herein.

BRIEF DESCRIPTION OF THE DRAWINGS

[0028] The disclosure is described in further detail below by way of example and with reference to the accompanying drawings, in which:

[0029] FIG. 1 is a schematic of a layer stack of a packaging substrate for mounting an integrated circuit and/or a circuit component in accordance with a first embodiment of the present disclosure;

[0030] FIG. 2 is a schematic of a layer stack of a packaging substrate for mounting an integrated circuit and/or a circuit component in accordance with a second embodiment of the present disclosure;

[0031] FIG. 3A is a schematic of a top down view of an inductor structure for providing an inductance in accordance with a third embodiment of the present disclosure;

[0032] FIG. 3B is a cross section of the inductor structure shown in FIG. 3A, and

[0033] FIG. 3C is a schematic of a top down view of an inductor structure for providing an inductance in accordance with a fourth embodiment of the present disclosure; and

[0034] FIG. 4A is a schematic of a top down view of an inductor structure for providing an inductance in accordance with a fifth embodiment of the present disclosure,

[0035] FIG. 4B is a schematic of a top down view of an inductor structure for providing an inductance in accordance with a sixth embodiment of the present disclosure,

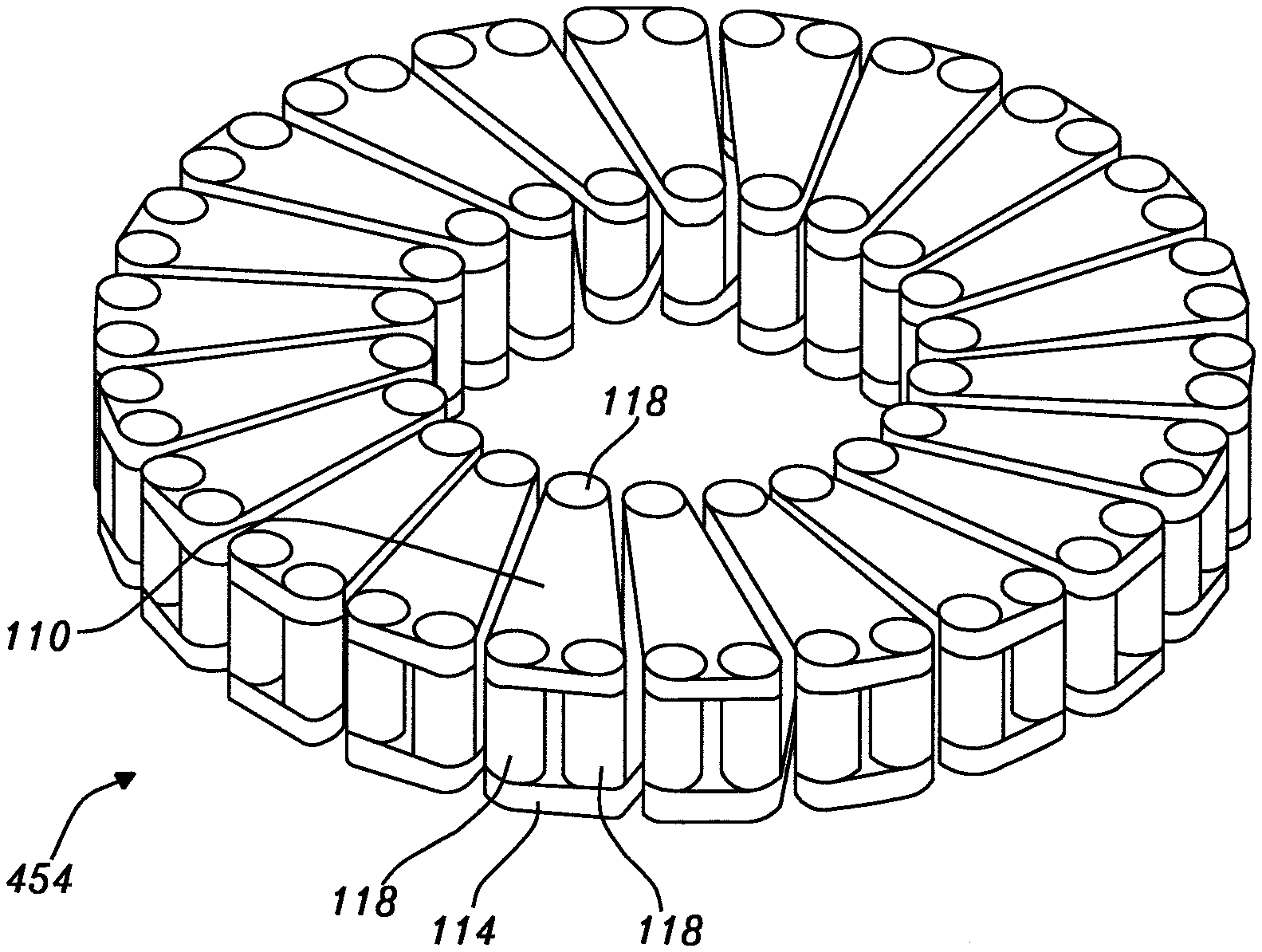

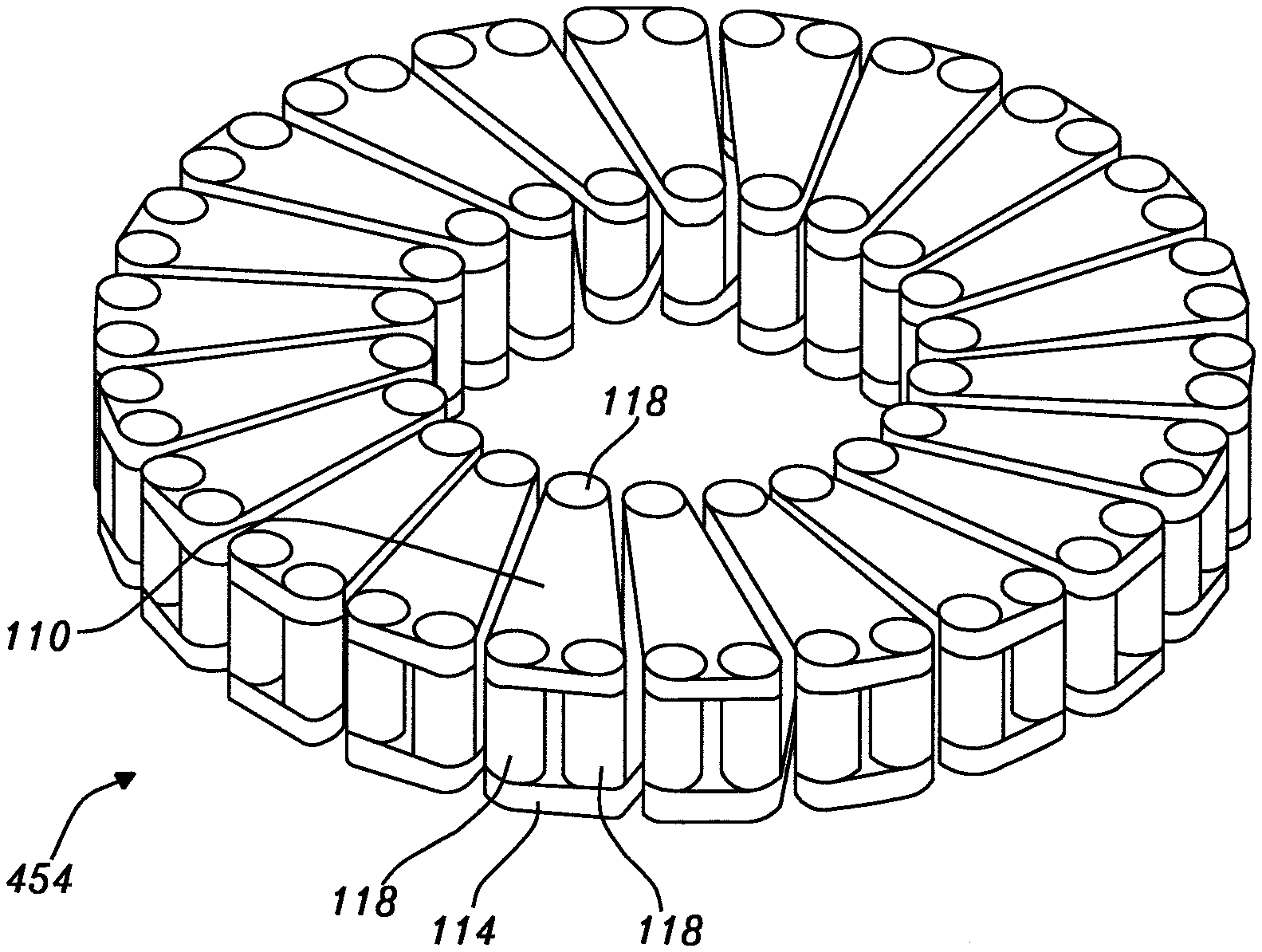

[0036] FIG. 4C is a schematic of a top down view of an inductor structure for providing an inductance in accordance with a seventh embodiment of the present disclosure,

[0037] FIG. 4D is a schematic of a top down view of an inductor structure for providing an inductance in accordance with an eighth embodiment of the present disclosure,

[0038] FIG. 4E is a schematic of a top down view of an inductor structure for providing an inductance in accordance with a ninth embodiment of the present disclosure,

[0039] FIG. 4F is a schematic of a top down view of an inductor structure for providing an inductance in accordance with a ninth embodiment of the present disclosure, and

[0040] FIG. 4G is a perspective view of the inductor structure of FIG. 4C.

[0041] FIG. 5 is a schematic of a top down view of an inductor structure for providing an inductance in accordance with a tenth embodiment of the present disclosure.

DESCRIPTION

[0042] FIG. 1 is a schematic of a layer stack of a packaging substrate 100 for mounting an integrated circuit and/or a circuit component in accordance with a first embodiment of the present disclosure. The packaging substrate 100 may be molded interconnect substrate (MIS) or a laminate substrate.

[0043] The packaging substrate 100 comprises an upper surface 102 for mounting the integrated circuit and/or circuit component and may comprise a lower surface 104 that is opposite to the upper surface 102. The packaging substrate 100 comprises a non-conductive material 106 and an inductor structure 108. The inductor structure 108 is at least partially embedded in the non-conductive material 106 and in the present embodiment, the inductor structure 108 is wholly embedded in the non-conductive material 106. The non-conductive material 106 may, for example, be a plastic.

[0044] The inductor structure 108 comprises a first conductive material 110 that is at least partially on a first layer 112, and a second conductive material 114 that is at least partially on a second layer 116. The inductor structure 108 further comprises a plurality of conductive pillars 118. Inductor structures of the type described herein, may be referred to as 3D inductors.

[0045] The first conductive material 110, the second conductive material 114 and the conductive pillars 118 may comprise copper and/or aluminium. Typically conductive pillars 118 comprising copper are referred to as copper pillars. Alternatively, the first conductive material 110, the second conductive material 114 and the conductive pillars 118 may comprise materials other than copper and/or aluminium, such as alloys with good conductivities.

[0046] The first conductive material 110, the second conductive material 114 and the conductive pillars 118 are arranged to form a coil (110+114+118) with an inductance. The non-conductive material 106 is electrically insulating when compared to the conductive materials 110, 114 and the conductive pillars 118. In effect the coil (110+114+118) forms a conducting part of an inductor. It will be appreciated that the part of the non-conductive material 106 that is enclosed by the coil (110+114+118) may affect the inductance of the coil (110+114+118). In the present embodiment the non-conductive material is a plastic material and may be referred to as an "air coil".

[0047] The coil (110+114+118) may be arranged as a solenoid which has an axis that is approximately parallel to the upper surface 102 of the packaging substrate 100. The axis of the solenoid is the axis around which the solenoid is wound. Alternatively, the coil (110+114+118) may be arranged as a toroid. In a further embodiment the coil (110+114+118) may partially or fully enclose a magnetic material 120. When the magnetic material 120 is omitted, the coil (110+114+118) may be referred to as an air core inductor. The magnetic material 120 can be used to increase the inductance of the inductor structure 108. The magnetic material 120 may comprise a polymer film and/or ferrite powders. Although individual grains of the ferrite powders may be conductive, the ferrite powder is not conductive in bulk.

[0048] It will be appreciated that additional conductive pillars 118 may be positioned behind the conductive pillars 118 that are visible in the schematic. Additionally, it should be noted that the schematic shown in FIG. 1 is a layer stack, rather than a cross section, and as such the visibility of features is not necessarily representative of their depth. For example, when viewing FIG. 1, one of the conductive pillars 118 may be positioned further away (into the page) than the other conductive pillar 118.

[0049] In a specific embodiment, when the coil (110+114+118) is arranged as the solenoid, the coil (110+114+118) may comprise a single loop where the first conductive material 110 is coupled to two conductive pillars 118, one of which is coupled to the second conductive material 114, and the other of which is disconnected from the second conductive material 114.

[0050] A coil loop may alternatively be referred to as a winding. The solenoids and toroids described herein may comprise multiple windings.

[0051] FIG. 2 is a schematic of a layer stack of a packaging substrate 200 for mounting an integrated circuit 202 (which may be referred to as a chip) and/or a circuit component in accordance with a second embodiment of the present disclosure. The packaging substrate 200 of FIG. 2 shares common features with the packaging substrate 100 of FIG. 1 and therefore common features between figures share common reference numerals and variables.

[0052] Circuit components, such as a capacitor 204, may be mounted on the packaging substrate 200 using one or more solder bumps 206. The integrated circuit 202 is also mounted on the packaging substrate 200 using solder bumps 206.

[0053] The packaging substrate 200 can be used to mount multiple integrated circuits and other components together.

[0054] In the present embodiment, the packaging substrate 200 comprises routing traces 208, and vias 210. The inductor structure 108 is electrically connected to the integrated circuit 202 and the capacitor 204 by routing traces 208, vias 210 and solder bumps 206.

[0055] In the present embodiment, the lower surface 104 of the packaging substrate is suitable for mounting the packaging substrate 200 to a printed circuit board (PCB) 212. The packaging substrate 200 comprises a PCB solder pad 214 to provide an electrical connection between the packaging substrate 200 and the PCB 212.

[0056] The inductor structure 108 may be formed using processes and materials that are included in standard fabrication processes for packaging substrates. The packaging substrate 200 may, for example, be produced using standard methods for MIS or laminate substrates. For small ICs, laminate substrates are typically more expensive than MIS, however laminate substrates are likely to be economically better for large ICs with large substrates that require more than one inductor, when compared to MIS.

[0057] Building the inductor structure 108 into the packaging substrate 200 leverages a low cost processing step to create the inductor, and, the final product takes up minimal board area, as the chip 202 can be stacked on top of the inductor. In addition to a specific packaging substrate, MIS may refer generally to the fabrication process provided for molded interconnect substrates and the conventions of this process. MIS is an in-package interconnect technology which allows layered interconnect patterns with features on the order of 25 .mu.m.

[0058] MIS enables fabrication of structures having finer geometries that those on traditional lead frames. For example, MIS can enable spacings between adjacent features as narrow as 25 .mu.m whereas in standard plastic packaging technologies and in traditional lead frames features cannot be spaced closer than approximately 100 .mu.m to 150 .mu.m.

[0059] A traditional lead frame (which may be referred to as a regular lead frame herein) is a single layer sheet of metal that is etched or stamped with a pattern, used as a support for a chip and forms metal leads which connect the chip to the outside of the package. The chip is first connected to this traditional lead frame before plastic is molded around the chip and lead frame assembly. In a traditional lead frame process, the metal sheet has to be a contiguous structure capable of holding together an array of ICs before the molding process. After molding, the individual IC's can be cut from the support lead frame.

[0060] A traditional lead frame is continuous until after chip mounting and overmolding. After molding and the assembly is cut from the outside frame, after which the metal may be discontinuous, supported by molding. The limitation is that the metal is constrained to be contiguous with the perimeter of the package.

[0061] In a typical MIS fabrication process, plastic is molded around a metal pattern before the chip is mounted on the surface of the MIS. The plastic gives structural integrity before adding the chip. Thus, the metal does not have to provide mechanical support and can be made with much finer geometries. This combined metal and plastic structure is known as a Molded Interconnect Substrate (MIS). After the chip is added, another plastic overmold may be added to encapsulate the chip and MIS together to create the final packaged substrate with mounted chip.

[0062] In MIS, the vias (pillars) are formed by lithographic patterning (cost-effective to get small geometries and arbitrary shapes) and molding is applied after the metal vias are formed. During MIS molding the metal is held in place by the layer below it. Thus an MIS substrate provides support for creating another MIS substrate layer above it and so on.

[0063] To form the inductor structures described herein, multiple MIS layers may be stacked on top of each other prior to adding the chip and before a final plastic overmold layer is applied.

[0064] As the MIS comprises plastic, it is non-conductive and additionally can provide mechanical support to multiple components simultaneously without shorting them out.

[0065] In MIS, the term "lead frame" may be used to describe the whole MIS or a metal layer within the MIS. To avoid confusion, the term lead frame, with regards to the MIS, used herein will refer to a metal layer.

[0066] The fine geometries provided by MIS is beneficial for the production of inductor structures that occupy small areas when compared to inductors formed on regular lead frames. Additionally MIS allows more loops of an inductor structure to be packed into the same area when compared with regular lead frames.

[0067] The first and second conductive materials 110, 114 are formed using routing traces and the conductive pillars 118 comprise one or more via. Multiple vias may be used to form each conductive pillar 118 to increase the height of the inductor structure 108, thereby increasing its inductance.

[0068] In a further embodiment only one of the first and second conductive materials 110, 114 may be formed using routing traces.

[0069] In packaging substrates, vias may be implemented using copper pillars. Copper pillars allow very low cost, low resistance interconnects between the chip 202, lead frames within the packaging substrate 200, and the PCB 212. In the present embodiment the first and second conductive materials 110, 114 are provided by lead frames. Additionally, a copper pillar can be used to implement a thick metal interconnect which can increase the height of the inductor structure 108, which increases the area enclosed by the coil (110+114+118). The MIS and copper pillar combination is extremely durable and highly reliable.

[0070] In the present embodiment of the MIS process, the copper interconnect patterns of the first and second conductive layers 110, 114 do not need to provide any structural support, and therefore do not have to be contiguous, which allows patterns not possible in a traditional lead frame to be realised.

[0071] The second conductive material 114 may be provided by an MIS lead frame comprising copper and having a height of 150 .mu.m. The conductive pillars 118, implemented using copper pillars may have a height of 65 .mu.m. The first conductive material 110 may be provided by thick copper on silicon and/or 3 .mu.m of copper and 5 .mu.m of aluminium. Alternatively, both the first conductive material 110 and the second conductive material 114 may be provided by MIS lead frames.

[0072] In a flip chip assembly, conductive pillars can be grown on the chip. A solder connection can be provided on the conductive pillars to enable coupling of the chip to the MIS.

[0073] The amount of metal in the coil (110+114+118) has an impact on the resistance of the coil (110+114+118), where more metal means a smaller resistance. A small resistance is desirable as it enables a high current to flow through the coil (110+114+118) and also leads to less issues with parasitics. For a practical implementation, the resistance of this inductor structures 108 described herein will be less than 0.5 mohm per loop and therefore should exhibit good current handling capability.

[0074] FIG. 3A is a schematic of a top down view of an inductor structure 300 for providing an inductance in accordance with a third embodiment of the present disclosure. The inductor structure 300 is a specific implementation of the inductor structure 108 and as such may be implemented as part of a packaging substrate, such as the packaging substrates 100, 200 as described previously.

[0075] The inductor structure 300 shares features with the inductor structure 108 and therefore common features between figures share common reference numerals and variables. It will be appreciated that although the conductive pillars 118 are shown in FIG. 3A, in a physical implementation of the inductor structure 300 it is likely that they would not be visible from this view as they are positioned underneath the first conductive material 110.

[0076] In the inductor structure 300 the first conductive material 110, the second conductive material 114 and the conductive pillars 118 are arranged to form the coil (110+114+118) that is arranged as a solenoid. When implemented as part of the packaging substrate 100, 200, the solenoid has an axis 301 that is approximately parallel to the upper surface 102 of the packaging substrate 100, 200.

[0077] The coil (110+114+118) may enclose the magnetic material 120. In a further embodiment, the coil may only partially enclose the magnetic material 120.

[0078] FIG. 3B is a cross section of the inductor structure 300 through a line 302 as shown in FIG. 3A.

[0079] The first conductive material 110 is discontinuous and comprises a plurality of first conductive portions 304, 306, 308 on the first layer 112 and the second conductive material 114 is discontinuous and comprises a plurality of second conductive portions 310, 312 on the second layer 116. Each of the first conductive portions 304, 306, 308 is coupled to at least one of the second conductive portions 310, 312 by at least one of the conductive pillars 118.

[0080] In the present embodiment there are three first conductive portions 304, 306, 308 and two second conductive portions 310, 312. It will be appreciated that in further embodiments there may be more or less conductive portions in accordance with the understanding of the skilled person.

[0081] FIG. 3C is a schematic of a top down view of an inductor structure 314 for providing an inductance in accordance with a fourth embodiment of the present disclosure. The inductor structure 314 is a specific implementation of the inductor structure 108 and as such may be implemented as part of a packaging substrate, such as the packaging substrates 100, 200 as described previously.

[0082] The inductor structure 314 shares features with the inductor structure 108 and the inductor structure 300, and therefore common features between figures share common reference numerals and variables. Compared to the inductor structure 300, the inductor structure 314 comprises the first conductive material 110 comprising nine conductive portions, and the second conductive material 114 comprising ten conductive portions.

[0083] In the inductor structure 300 of FIG. 3A, the first conductive portion 306 is coupled to the second conductive portion 312 by the conductive pillar 118a and is coupled to the second conductive portion 310 by the conductive pillar 110b.

[0084] It will be appreciated that more than one of the first conductive portions may be arranged in this manner. For example, as shown by the inductor structure 314 in FIG. 3C. For the inductor structure 314 of FIG. 3C each of the first conductive portions (associated with the first conductive material 110) is coupled to two conductive pillars 118 and for each first conductive portions, the two conductive pillars 118 are coupled to different second conductive portions (associated with the second conductive material 114).

[0085] FIG. 4A is a schematic of a top down view of an inductor structure 400 for providing an inductance in accordance with a fifth embodiment of the present disclosure. The inductor structure 400 is a specific implementation of the inductor structure 108 and as such may be implemented as part of a packaging substrate, such as the packaging substrates 100, 200 as described previously.

[0086] The inductor structure 400 shares features with the inductor structure 108 and therefore common features between figures share common reference numerals and variables. It will be appreciated that although the conductive pillars 110 are shown in FIG. 4A, in a physical implementation of the inductor structure 400 it is likely that they would not be visible from this view as they are positioned underneath the first conductive material 110.

[0087] In the inductor structure 400 the first conductive material 110, the second conductive material 114 and the conductive pillars 118 are arranged to form the coil (110+114+118) that is arranged as a toroid.

[0088] The toroid formed by the coil (110+114+118) has an inner circumference 401 and an outer circumference 403 around a central axis 405. The inner circumference 401 is closer to the central axis 405 than the outer circumference 403 on a line 407 extending outward from the central axis 405. The conductive pillars 118 at or near the inner circumference 401 are smaller than the conductive pillars 118 at or near the outer circumference 403.

[0089] The coil (110+114+118) may enclose a magnetic material 120 (not shown). In a further embodiment, the coil may only partially enclose the magnetic material 120.

[0090] The first conductive material 110 is discontinuous and comprises a plurality of first conductive portions 402, 404, 406, 408, 410, 412, 414, 416, 418, 420, 422, 424 on the first layer 112 and the second conductive material 114 is discontinuous and comprises a plurality of second conductive portions 426, 428, 430, 432, 434, 436, 438, 440, 442, 444, 446, 448 on the second layer 116. Each of the first conductive portions 402-24 is coupled to at least one of the second conductive portions 426-448 by at least one of the conductive pillars 118.

[0091] Labels denoting the first and second conductive materials 110, 114 have been omitted from FIG. 4A to aid in the clarity of the drawing.

[0092] In the present embodiment there are twelve first conductive portions 402-424 and twelve second conductive portions 426-448. It will be appreciated that in further embodiments there may be more or less conductive portions in accordance with the understanding of the skilled person.

[0093] FIG. 4B is a schematic of a top down view of an inductor structure 450 for providing an inductance in accordance with a sixth embodiment of the present disclosure. The inductor structure 450 is a specific implementation of the inductor structure 108 and as such may be implemented as part of a packaging substrate, such as the packaging substrate 100, 200 as described previously.

[0094] The inductor structure 450 shares features with the inductor structure 108 and the inductor structure 400, and therefore common features between figures share common reference numerals and variables. Compared to the inductor structure 400, the inductor structure 450 comprises more first and second conductive portions and comprises first and second conductive portions of a different shape than those of the inductor structure 400.

[0095] Additionally, in the inductor structure 450, the conductive pillars 118 at or near the inner circumference 401 are smaller than the conductive pillars 118 at or near the outer circumference 403.

[0096] To ensure clarity of the drawing, an exploded view 452 of a section of the inductor structure 450 is shown and labelled. It will be clear to the skilled person how the labelled features of the exploded view 452 applies to the remainder of the inductor structure 450.

[0097] FIG. 4C is a schematic of a top down view of an inductor structure 454 for providing an inductance in accordance with a seventh embodiment of the present disclosure. The inductor structure 454 is a specific implementation of the inductor structure 108 and as such may be implemented as part of a packaging substrate, such as the packaging substrates 100, 200 as described previously.

[0098] The inductor structure 454 shares features with the inductor structure 108 and the inductor structure 400, and therefore common features between figures share common reference numerals and variables.

[0099] In the inductor structure 454 the first conductive material 110, the second conductive material 114 and the conductive pillars 118 are arranged to form the coil (110+114+118) that is arranged as a toroid.

[0100] In the inductor structure 454, for each of the first conductive portions (associated with the first conductive material 110), there are less conductive pillars 118 at or near the inner circumference 401 used to couple to one second conductive portion (associated with the second conductive material 114) than at or near the outer circumference 403 used to couple to another second conductive portion 118. Specifically, there is one conductive pillar 118 at the inner circumference 401 and two conductive pillars 118 at the outer circumference 403 for each first conductive portion in the present embodiment. In the present embodiment all conductive pillars 118 are the same size.

[0101] To aid in the clarity of the drawing, only a single first conductive portion and its associated conductive pillars have been labelled. The second conductive material 114 is not labelled.

[0102] FIG. 4D is a schematic of a top down view of an inductor structure 456 for providing an inductance in accordance with an eighth embodiment of the present disclosure. The inductor structure 456 is a specific implementation of the inductor structure 108 and as such may be implemented as part of a packaging substrate, such as the packaging substrates 100, 200 as described previously.

[0103] The inductor structure 456 shares features with the inductor structure 108 and the inductor structure 400, and therefore common features between figures share common reference numerals and variables.

[0104] In the inductor structure 456 the first conductive material 110, the second conductive material 114 and the conductive pillars 118 are arranged to form the coil (110+114+118) that is arranged as a toroid.

[0105] To aid in the clarity of the drawing, only a single first conductive portion and its associated conductive pillars have been labelled. The second conductive material 114 is not labelled.

[0106] FIG. 4E is a schematic of a top down view of an inductor structure 458 for providing an inductance in accordance with a ninth embodiment of the present disclosure. The inductor structure 458 is a specific implementation of the inductor structure 108 and as such may be implemented as part of a packaging substrate, such as the packaging substrates 100, 200 as described previously.

[0107] The inductor structure 458 shares features with the inductor structure 108 and the inductor structure 400, and therefore common features between figures share common reference numerals and variables.

[0108] In the inductor structure 458 the first conductive material 110, the second conductive material 114 and the conductive pillars 118 are arranged to form the coil (110+114+118) that is arranged as a toroid.

[0109] The inductor structure 108 may be coupled to other components by a support structure 459.

[0110] To aid in the clarity of the drawing, only a single first conductive portion and its associated conductive pillars have been labelled. Additionally, only one of the support structures 459 has been labelled. The second conductive material 114 is not labelled.

[0111] FIG. 4F is a schematic of a top down view of an inductor structure 460 for providing an inductance in accordance with a ninth embodiment of the present disclosure. The inductor structure 460 is a specific implementation of the inductor structure 108 and as such may be implemented as part of a packaging substrate, such as the packaging substrates 100, 200 as described previously.

[0112] The inductor structure 460 shares features with the inductor structure 108 and the inductor structure 400, and therefore common features between figures share common reference numerals and variables.

[0113] In the inductor structure 460 the first conductive material 110, the second conductive material 114 and the conductive pillars 118 are arranged to form the coil (110+114+118) that is arranged as a toroid.

[0114] The inductor structure 108 may be coupled to other components by a support structure 459.

[0115] To aid in the clarity of the drawing, only a single first conductive portion and its associated conductive pillars have been labelled. Additionally, only one of the support structures 459 has been labelled. The second conductive material 114 is not labelled.

[0116] FIG. 4G is a perspective view of the inductor structure 454. To aid in the clarity of the drawing, the first conductive material 110 is only labelled for a single first conductive portion, the second conductive material 114 is only labelled for a single second conductive portion. Additionally, only three conductive pillars are labelled 118.

[0117] For each of the inductor structures 400, 450, 454, 456, 458, 460, each of the first conductive portions is coupled to two conductive pillars and for each first conductive portion, the two conductive pillars are coupled to different second conductive portions. For example, for the inductor structure 400, the first conductive portion 402 is coupled to the second conductive portions 426 and 428 by a conductive pillar 409 and a conductive pillar 411, respectively.

[0118] The inductor structures 400, 450, 454, 456, 458, 460 are arranged as toroids and therefore provides good containment of a magnetic field, low electromagnetic interference (EMI) due to the B field being approximately equal to zero outside the toroid, and low eddy current losses in surrounding conductors. Additionally, toroids provide a higher inductance per unit area when compared to solenoids, however solenoids may be more desirable for certain packaging substrate sizes. Toroids are particularly useful for power applications.

[0119] A practical physical implementation of one of the toroid-type inductor structures 400, 450, 454, 456, 458, 460 within a packaging substrate may be implemented in an area that is less than 1 mm.sup.2 and exhibit high current capacity with a good Q factor.

[0120] The packaging substrates comprising inductor structures disclosed herein provide a cost effective inductor with high current carrying capability suitable for use in Power and RF applications using high volume semiconductor processes.

[0121] FIG. 5 is a schematic of a top down view of an inductor structure 500 for providing an inductance in accordance with a tenth embodiment of the present disclosure. The inductor structure 500 is a specific implementation of the inductor structure 108 and as such may be implemented as part of a packaging substrate, such as the packaging substrates 100, 200 as described previously. The inductor structure 500 may comprise two or more coils 502, 504, each having an inductance and arranged to form a transformer or a coupled inductor. In consideration of a packaging substrate comprising two coils 502, 504, at least one of the two coils is formed by one of the inductor structures as described previously. Both coils 502, 504 may comprise the first conductive material 110, the second conductive material 114, and may both each comprise a plurality of conductive pillars (not shown). The two coils 502, 504 may be arranged as a toroid transformer, which may be in a double helix configuration. FIG. 5 show a portion of a toroid transformer wound in a double helix configuration with the curvature omitted to aid in the clarity of the drawing. Implementation of a toroid transformer within a packaging substrate yields all the normal benefits of toroid transformers including signal integrity, efficiency, etc.

[0122] Various improvements and modifications may be made to the above without departing from the scope of the disclosure.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

D00009

D00010

D00011

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.