Vertical Superlattice Transistors

CHANG; JOSEPHINE BEA ; et al.

U.S. patent application number 16/360828 was filed with the patent office on 2020-09-24 for vertical superlattice transistors. This patent application is currently assigned to NORTHROP GRUMMAN SYSTEMS CORPORATION. The applicant listed for this patent is JOSEPHINE BEA CHANG, ROBERT S. HOWELL, MATTHEW R. KING. Invention is credited to JOSEPHINE BEA CHANG, ROBERT S. HOWELL, MATTHEW R. KING.

| Application Number | 20200303536 16/360828 |

| Document ID | / |

| Family ID | 1000004016079 |

| Filed Date | 2020-09-24 |

View All Diagrams

| United States Patent Application | 20200303536 |

| Kind Code | A1 |

| CHANG; JOSEPHINE BEA ; et al. | September 24, 2020 |

VERTICAL SUPERLATTICE TRANSISTORS

Abstract

A vertical transistor is provided that includes a base structure and a superlattice structure overlying the base structure. The superlattice structure comprises a multichannel ridge having sidewalls. The multichannel ridge comprises a plurality of heterostructures that each form a channel of the multichannel ridge. The vertical transistor also includes a source region that overlies the base structure and is in contact with a first end of the superlattice structure, a floating drain that overlies the base structure and is in contact with a second end of the superlattice structure, and a drain. When the vertical transistor is in an `ON` state, current flows from the source region through the channels of the multichannel ridge to the floating drain, which funnels the current to the drain through at least a portion of the base structure.

| Inventors: | CHANG; JOSEPHINE BEA; (Ellicott City, MD) ; HOWELL; ROBERT S.; (Silver Spring, MD) ; KING; MATTHEW R.; (Wake Forest, NC) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Assignee: | NORTHROP GRUMMAN SYSTEMS

CORPORATION FALLS CHURCH VA |

||||||||||

| Family ID: | 1000004016079 | ||||||||||

| Appl. No.: | 16/360828 | ||||||||||

| Filed: | March 21, 2019 |

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 29/0847 20130101; H01L 29/66462 20130101; H01L 29/155 20130101; H01L 29/7786 20130101; H01L 21/02507 20130101; H01L 29/7788 20130101 |

| International Class: | H01L 29/778 20060101 H01L029/778; H01L 29/15 20060101 H01L029/15; H01L 29/08 20060101 H01L029/08; H01L 29/66 20060101 H01L029/66; H01L 21/02 20060101 H01L021/02 |

Claims

1. A vertical transistor comprising: a base structure; a superlattice structure overlying the base structure and comprising a multichannel ridge having a top and sidewalls, the multichannel ridge comprising a plurality of heterostructures that each form a channel of the multichannel ridge; a source region that overlies the base structure and is in contact with a first end of the superlattice structure; a floating drain that overlies the base structure and is in contact with a second end of the superlattice structure; and a drain, wherein the vertical transistor is configured such that when the vertical transistor is in an `ON` state, current is capable of flowing from the source region through the channels of the multichannel ridge to the floating drain, which is capable of funneling the current to the drain through at least a portion of the base structure.

2. The vertical transistor of claim 1, wherein each heterostructure is formed from an AlGaN layer and a GaN layer, wherein the AlGaN layer is a layer that is doped.

3. The vertical transistor of claim 1, further comprising a gate contact that wraps around and substantially surrounds the top and at least one side of the multichannel ridge.

4. The vertical transistor of claim 1, further comprising a plurality of multichannel ridges spaced apart from one another by non-channel openings and each comprising a plurality of heterostructures that each form a portion of a parallel channel of each respective multichannel ridge of the plurality of multichannel ridges.

5. The vertical transistor of claim 4, further comprising a gate contact that wraps around and substantially surrounds the top and both sides of each of the plurality of multichannel ridges along their depth.

6. The vertical transistor of claim 1, wherein the vertical transistor has a general circular shape.

7. The vertical transistor of claim 1, wherein the drain is disposed on a bottom surface of the base structure and extends into a portion of the base structure in general alignment with the floating drain.

8. The vertical transistor of claim 1, wherein the drain is disposed on a top surface of the base structure wherein current is capable of flowing from the floating drain to the base structure along a portion of the base structure and back up to the drain.

9. The vertical transistor of claim 1, further comprising a high voltage protection region that is configured to act as a depletion region that is capable of growing to pinch off the vertical transistor in response to high voltages on the source region when the vertical transistor is in an `OFF` state.

10. A transistor comprising: a base structure; a generally circular source region that overlies the base structure; a floating drain that overlies the base structure and resides within the generally circular source region; a superlattice structure overlying the base structure positioned in between the generally circular source region and the floating drain, and comprising a plurality of multichannel ridges spaced apart from one another by non-channel openings and each having a top and sidewalls, each of the plurality of multichannel ridges being formed from a plurality of heterostructures that each form a channel of the plurality of multichannel ridges, the plurality of multichannel ridges and non-channel openings each having a generally radial direction from the floating drain region to the generally circular source region; and a drain, wherein the vertical transistor is configured such that when the vertical transistor is in an `ON` state, current is capable of flowing from the generally circular source region through the channels of the multichannel ridges to the floating drain, which is capable of funneling the current to the drain through at least a portion of the base structure.

11. The transistor of claim 10, wherein the floating drain extends through a portion of the base structure.

12. The transistor of claim 10, further comprising a gate contact disposed between the source region and the floating drain, wherein the gate contact wraps around and substantially surrounds the top and both sides of each of the multichannel ridges along their depth, and wherein a voltage applied above a threshold to the gate contacts is capable of turning the vertical transistor to an `OFF` state.

13. The transistor of claim 10, wherein the drain is disposed on a bottom surface of the base structure and extends into a portion of the base structure in general alignment with the floating drain.

14. The transistor of claim 10, wherein the drain is disposed on a top surface of the base structure wherein current is capable of flowing from the floating drain to the base structure along a portion of the base structure and back up to the drain.

15. The transistor of claim 10, further comprising a high voltage protection region in contact with the source region, the high voltage protection region being configured to act as a depletion region that is capable of growing to pinch off the vertical transistor in response to a high voltage on the source region when the vertical transistor is in an `OFF` state.

16. A method of forming a vertical transistor, the method comprising: forming a superlattice structure having a plurality of heterostructures over a base structure; etching openings in the superlattice structure to form a plurality of multichannel ridges spaced apart from one another by non-channel openings, each of the plurality of multichannel ridges being formed from a plurality of heterostructures and each having a top and sidewalls; etching a source region opening and a floating drain opening in the superlattice structure; filling the source region opening and the floating drain opening with a doped material to form a floating drain and a source region; and forming a drain in the base structure.

17. The method of claim 16, further comprising forming a gate contact that wraps around and substantially surrounds the top and at least one side of each of the multichannel ridges along at least a portion of their depth.

18. The method of claim 16, wherein the drain is formed on a bottom surface of the base structure and extends into a portion of the base structure in general alignment with the floating drain, or the drain is formed on a top surface of the base structure.

19. The method of claim 16, further comprising forming a high voltage protection region in contact with the source region, the high voltage protection region being configured to act as a depletion region that is capable of growing to pinch off the vertical transistor in response to a high voltage on the source region when the vertical transistor is in an `OFF` state.

20. The method of claim 16, wherein the vertical transistor has a general circular shape.

Description

TECHNICAL FIELD

[0001] The present disclosure relates generally to transistors, and more particularly to vertical superlattice transistors.

BACKGROUND

[0002] Certain heterostructure materials, such as aluminum gallium nitride (AlGaN and GaN, create an electron well (i.e., a sheet of electrons) at the interface between the two dissimilar materials resulting from the piezoelectric effect and spontaneous polarization effect between those two dissimilar materials. The piezoelectric effect and spontaneous polarization cause a sheet of electrons at the interface between the two dissimilar materials called a two-dimensional electron gas ("2DEG") channel. Equally applicable is a lattice structure having a plurality of two-dimensional hole gas (2DHG) channels. Both of these types of structures are known as "2D.times.G channel(s)" devices. FETs that operate by generating and controlling the charge carriers in the 2D.times.G channel are generally called high electron mobility transistors ("HEMTs").

[0003] By stacking a plurality of these two-material heterostructures, and with the addition of appropriate doping in the layers to maintain the presence of the 2D.times.G channels when stacking a plurality of heterostructure layers, the charge sheets are able to act in parallel, allowing for greater current flow through the superlattice device. When this type of FET is "on", the superlattice device has a lower on-resistance, relative to a single heterostructure-layer device, because the multiple 2D.times.G channels allow a proportionally higher current to flow between the source and drain, resulting in an overall reduction in on-resistance. This type of structure has been well suited for providing an ultra-low channel resistance high-frequency switch.

[0004] A Super-Lattice Castellated gate Field Effect Transistor, or SLCFET, is a transistor built out of a superlattice of 2D.times.G channels (e.g. multiple pairs of barrier and channel epitaxial layers such as AlGaN/GaN grown and stacked on top each other to produce 2DEG or 2DHG channels).

[0005] Power transistors that operate at higher voltages and with better heat dissipation are desirable. In general, GaN devices on SiC are of particular interest for power transistors due to the combination of wide bandgap in GaN and high thermal conductivity in SiC. Therefore, SLCFET devices built out of AlGaN/GaN on SiC can operate at a higher voltage without electrical fields breaking down the device and causing failure of the device, making them suitable for use as power transistors.

SUMMARY

[0006] In one example, a vertical transistor is provided that comprises a base structure and a superlattice structure overlying the base structure. The superlattice structure comprises a multichannel ridge having sidewalls. The multichannel ridge comprises a plurality of heterostructures that each form a channel of the multichannel ridge. The vertical transistor also includes a source region that overlies the base structure and is in contact with a first end of the superlattice structure, a floating drain that overlies the base structure and is in contact with a second end of the superlattice structure, and a drain. When the vertical transistor is in an `ON` state, current flows from the source region through the channels of the multichannel ridge to the floating drain, which funnels the current to the drain through at least a portion of the base structure.

[0007] In another example, a transistor comprises a base structure, a generally circular source region that overlies the base structure, and a floating drain that overlies the base structure and resides within the generally circular source region. The transistor further comprises a superlattice structure overlying the base structure positioned in between the generally circular source region and the floating drain, and comprising a plurality of multichannel ridges spaced apart from one another by non-channel openings and each having sidewalls. Each of the plurality of multichannel ridges are formed from a plurality of heterostructures that each form a channel of the plurality of multichannel ridges. The plurality of multichannel ridges and non-channel openings each having a generally radial direction from the floating drain region to the generally circular source region. The transistor comprises a drain, wherein when the vertical transistor is in an `ON` state, current flows from the generally circular source region through the channels of the multichannel ridges to the floating drain, which funnels the current to the drain through at least a portion of the base structure.

[0008] In yet a further example, a method of forming a vertical transistor is disclosed. The method comprises forming a superlattice structure having a plurality of heterostructures over a base structure, and etching openings in the superlattice structure to form a plurality of multichannel ridges spaced apart from one another by non-channel openings. Each of the plurality of multichannel ridges are formed from a plurality of heterostructures with each having sidewalls. The method further comprises etching a source region opening and a floating drain opening in the superlattice structure, filling the source region opening and the floating drain opening with a doped material to form a floating drain and a source region, and forming a drain in the base structure.

BRIEF DESCRIPTION OF THE DRAWINGS

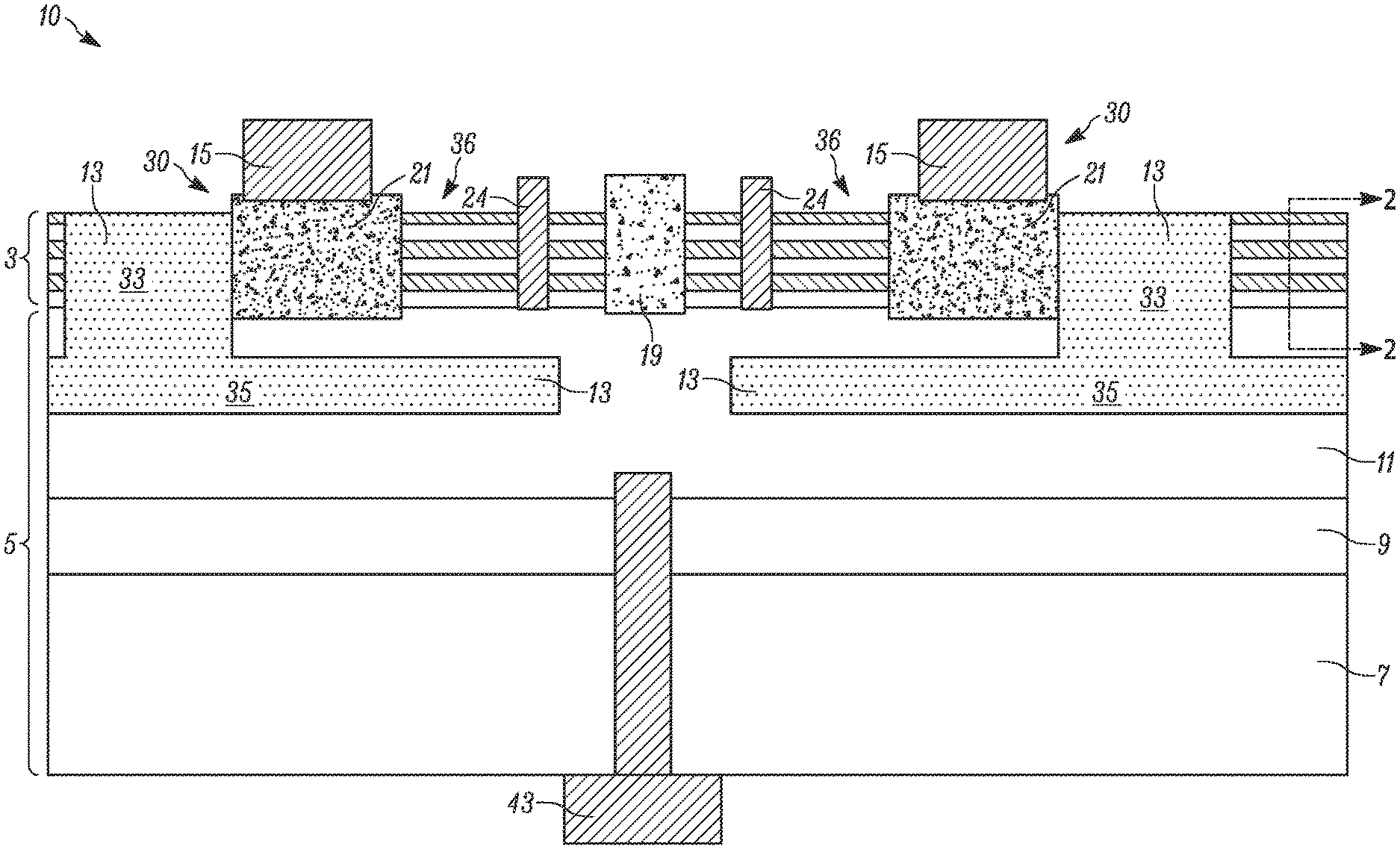

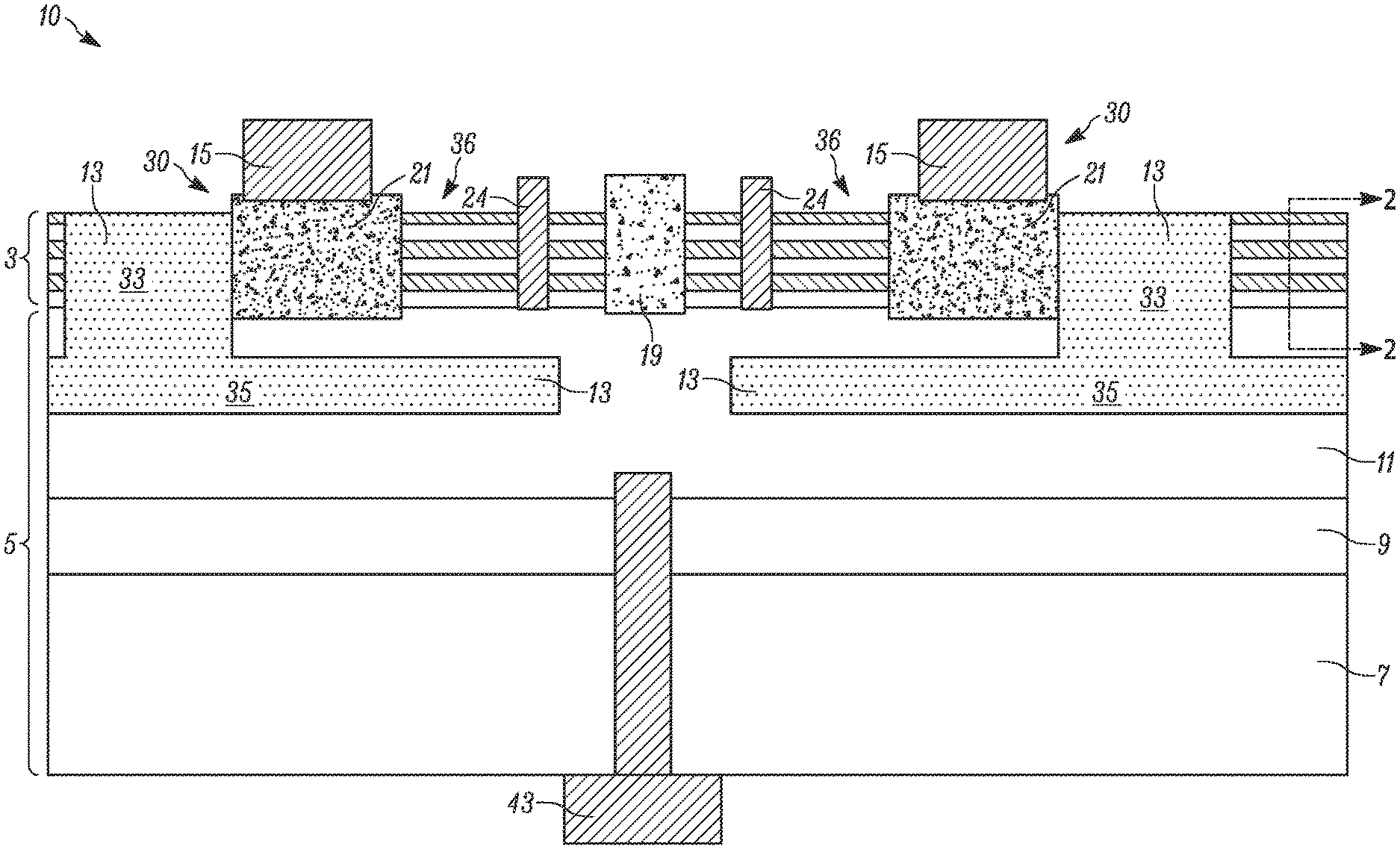

[0009] FIG. 1 illustrates an example cross-sectional view of an example vertical super-lattice castellated gate field-effect-transistor (vSLCFET) having a high breakdown voltage and providing for high power operation device.

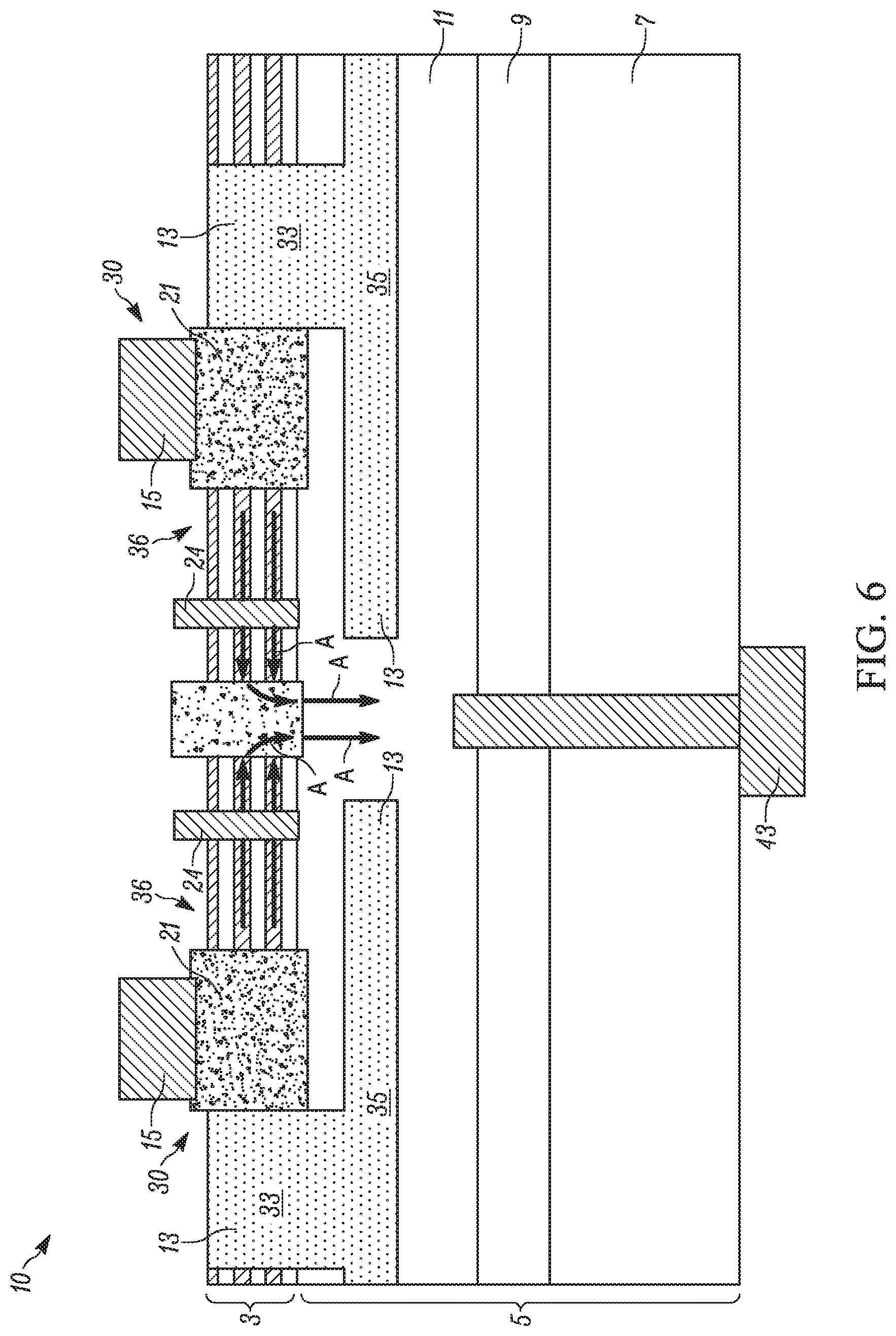

[0010] FIG. 2 illustrates a partial cross-sectional view of an example of a portion of a superlattice of the vSLCFET device of FIG. 1 along the lines 2-2.

[0011] FIG. 3 illustrates a top plan view of the example vSLCFET device of FIG.1.

[0012] FIG. 4 illustrates a partial cross-sectional view of an example of a portion of a castellated gate of the vSLCFET device of FIG. 1 along the lines 4-4 of FIG. 3.

[0013] FIG. 5 illustrates an example plan view of the example vSLCFET of FIGS. 1-4 in operation with current flowing from source region through a castellated gate to a floating drain and ultimately a drain contact.

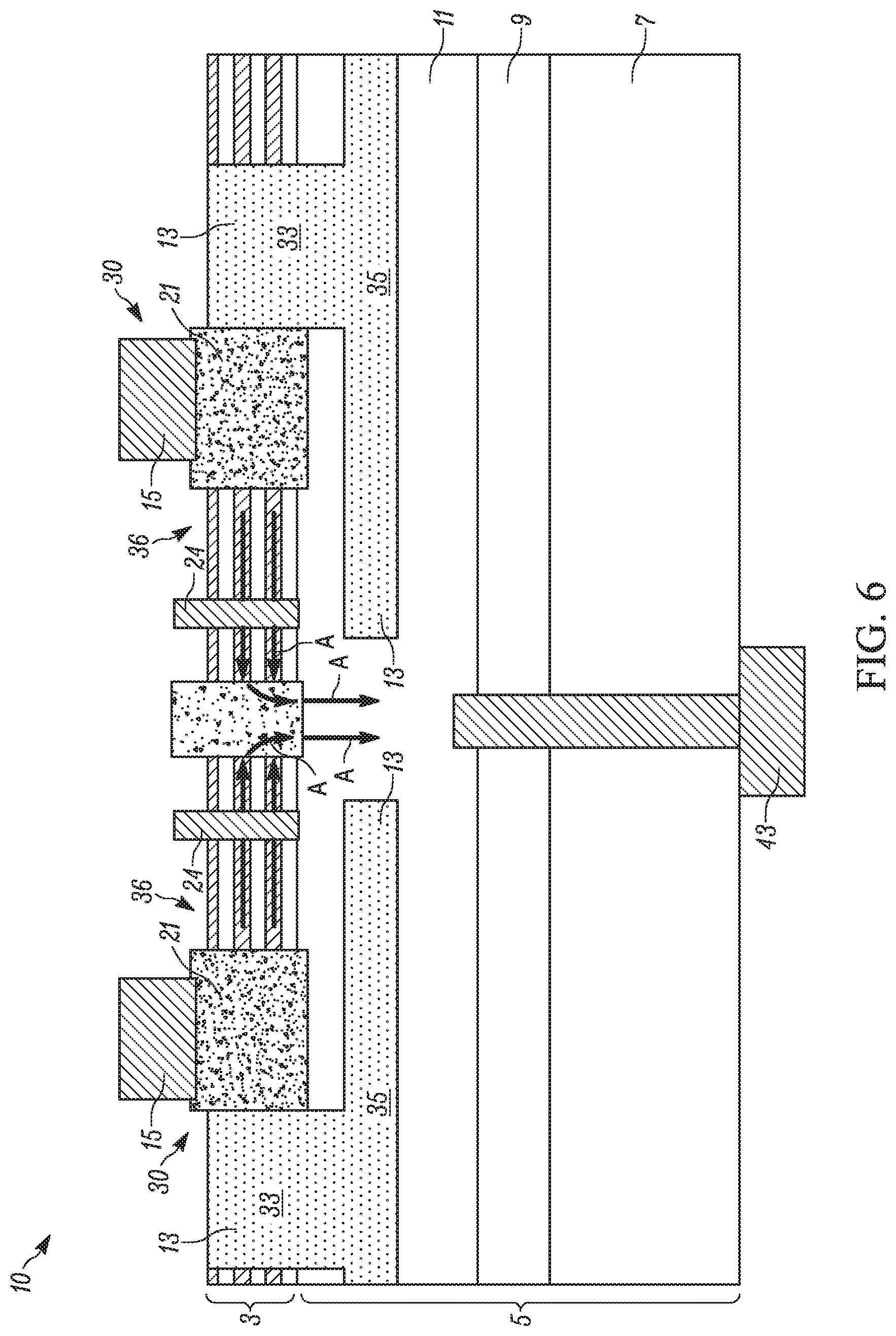

[0014] FIG. 6 illustrates an example cross-sectional side view of the example vSLCFET of FIGS. 1-4 in operation with current flowing horizontally from source region through a castellated gate to a floating drain and then flowing vertically downward toward a drain contact.

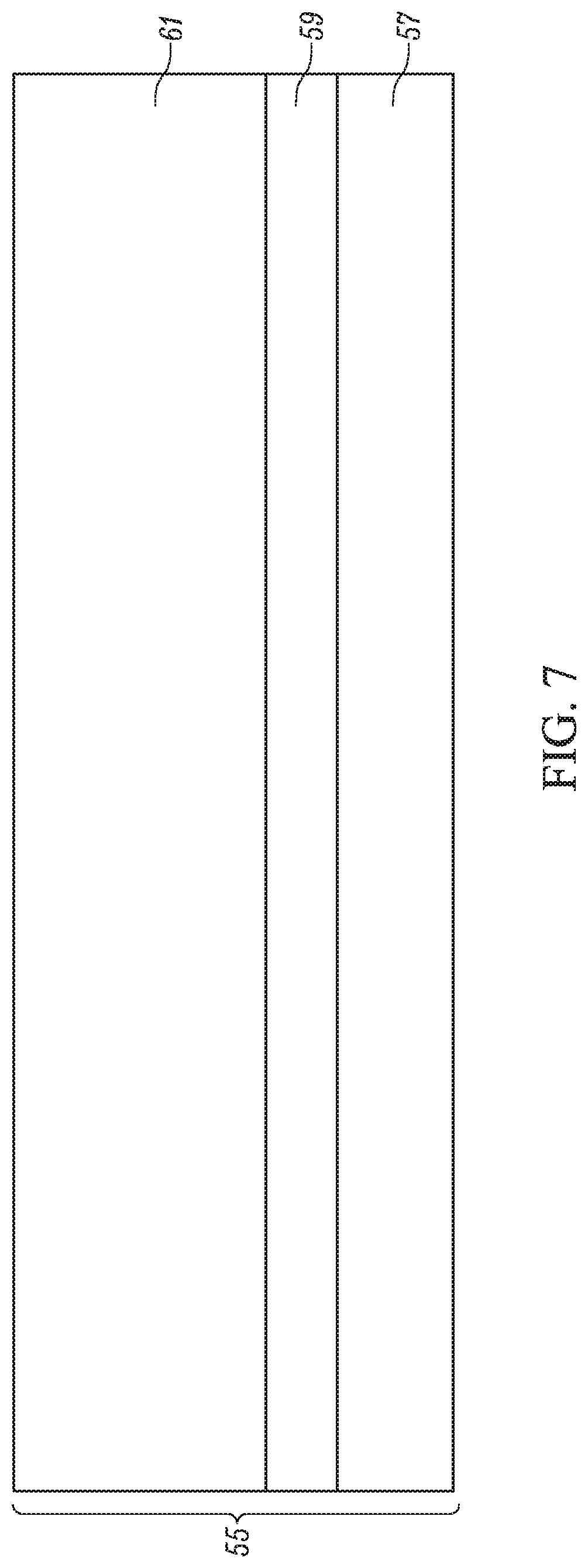

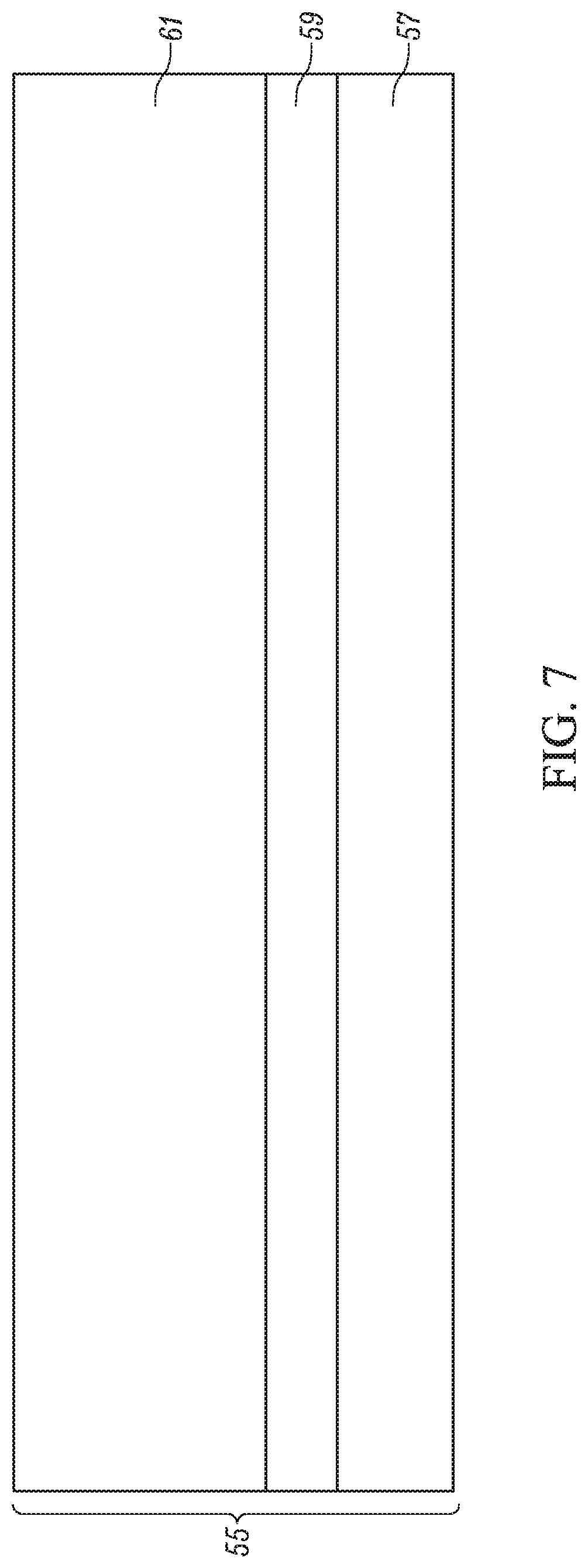

[0015] FIG. 7 illustrates an example cross-sectional view of a base of a vSLCFET early in the manufacturing process.

[0016] FIG. 8 illustrates an example cross-sectional view of the vSLCFET of FIG. 7 after formation of a mask defining the buried blocking layer.

[0017] FIG. 9 illustrates an example cross-sectional view of the vSLCFET device of FIG. 8 after formation of the buried blocking layer.

[0018] FIG. 10 illustrates a cross-sectional view of the structure of FIG. 9 after undergoing a series of deposition processes to form a superlattice.

[0019] FIG. 11 illustrates a cross-sectional view of the example vSLCFET device of FIG. 10 after formation of a mask overlying the superlattice to form high voltage protection contact openings.

[0020] FIG. 12 illustrates a cross-sectional view of the structure of FIG. 11 after formation of the high voltage protection contact openings and after the stripping of the mask.

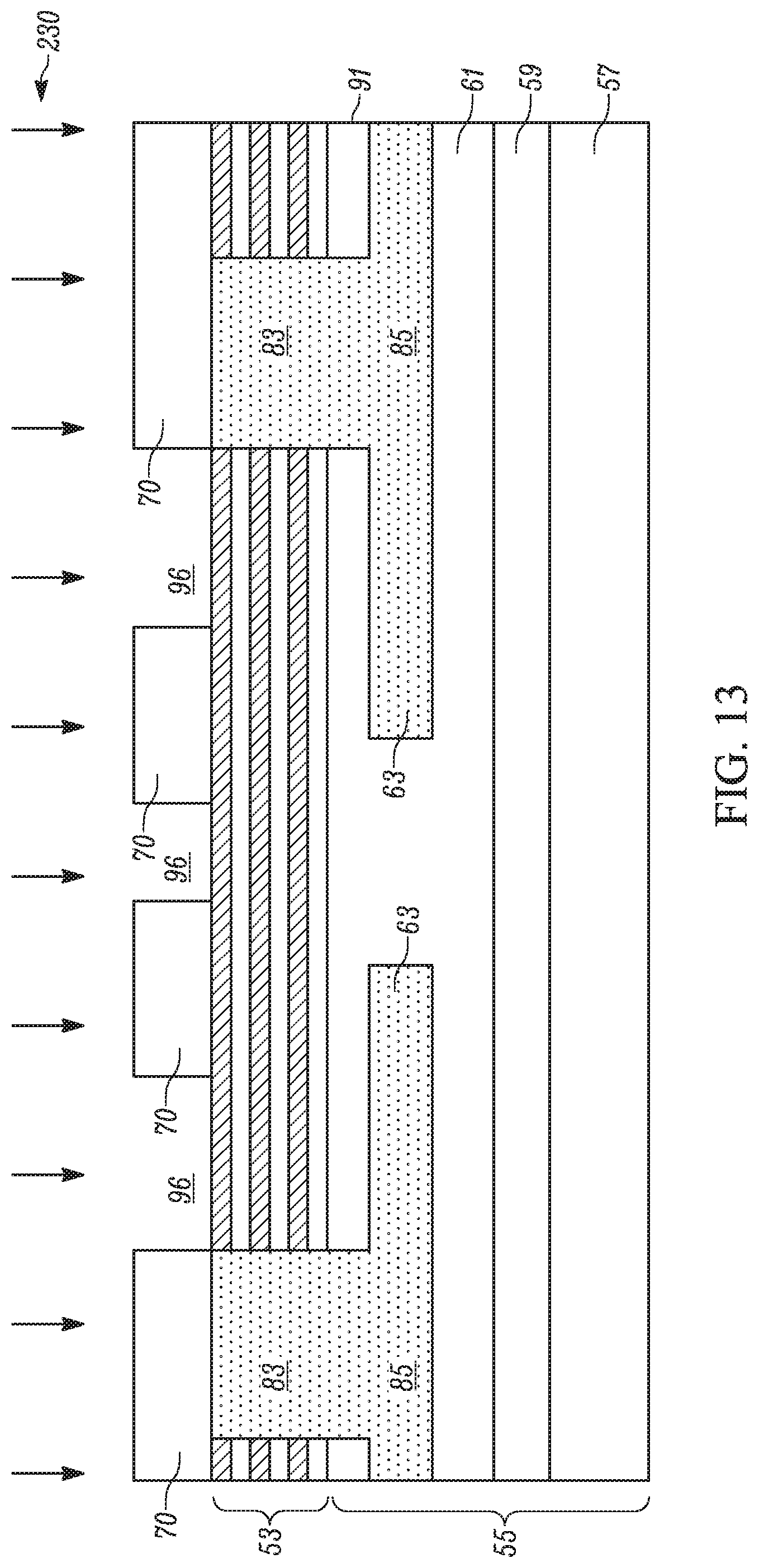

[0021] FIG. 13 illustrates a cross-sectional view of the structure of FIG. 12 with a mask in place to define the source and floating drain.

[0022] FIG. 14 illustrates a cross-sectional view of the structure of FIG. 13 after undergoing the etching process to form source and floating drain openings.

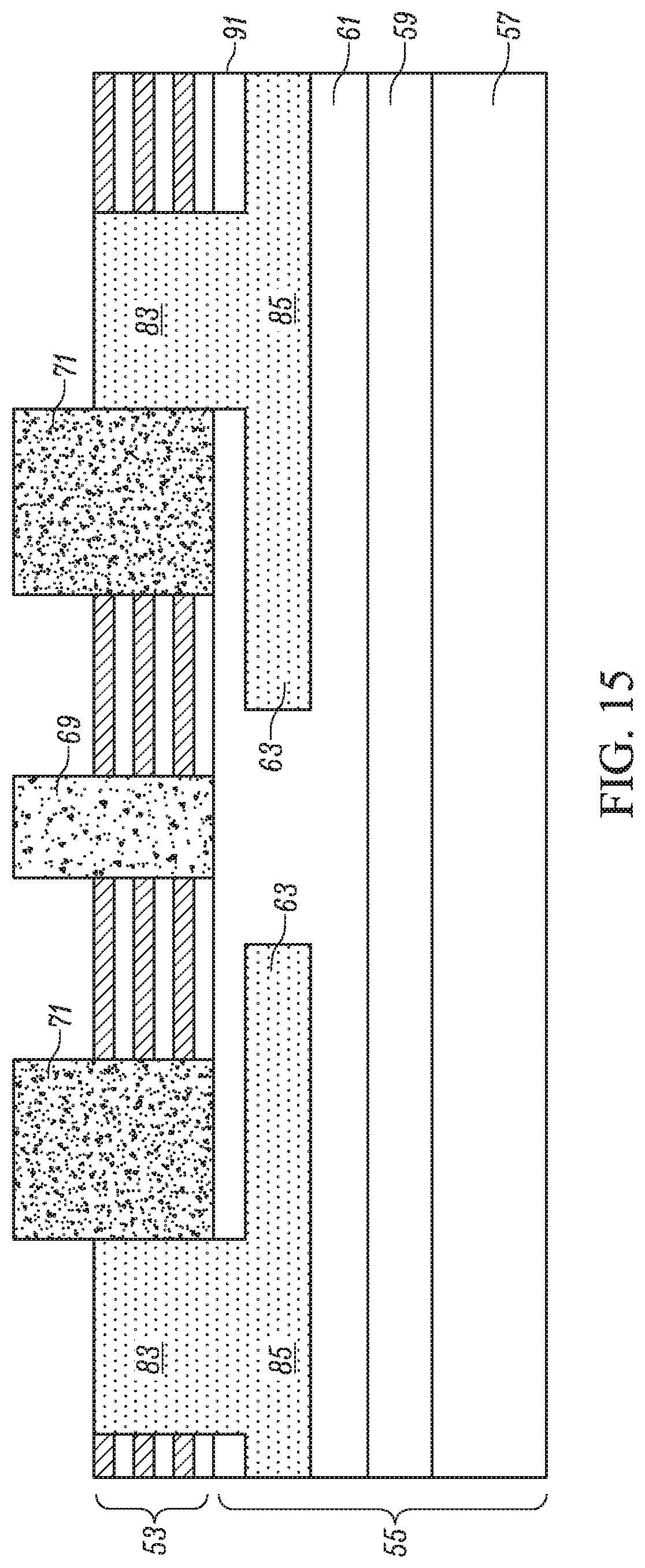

[0023] FIG. 15 illustrates a cross-sectional view of the structure of FIG. 14 after undergoing a source contact and floating drain deposition process.

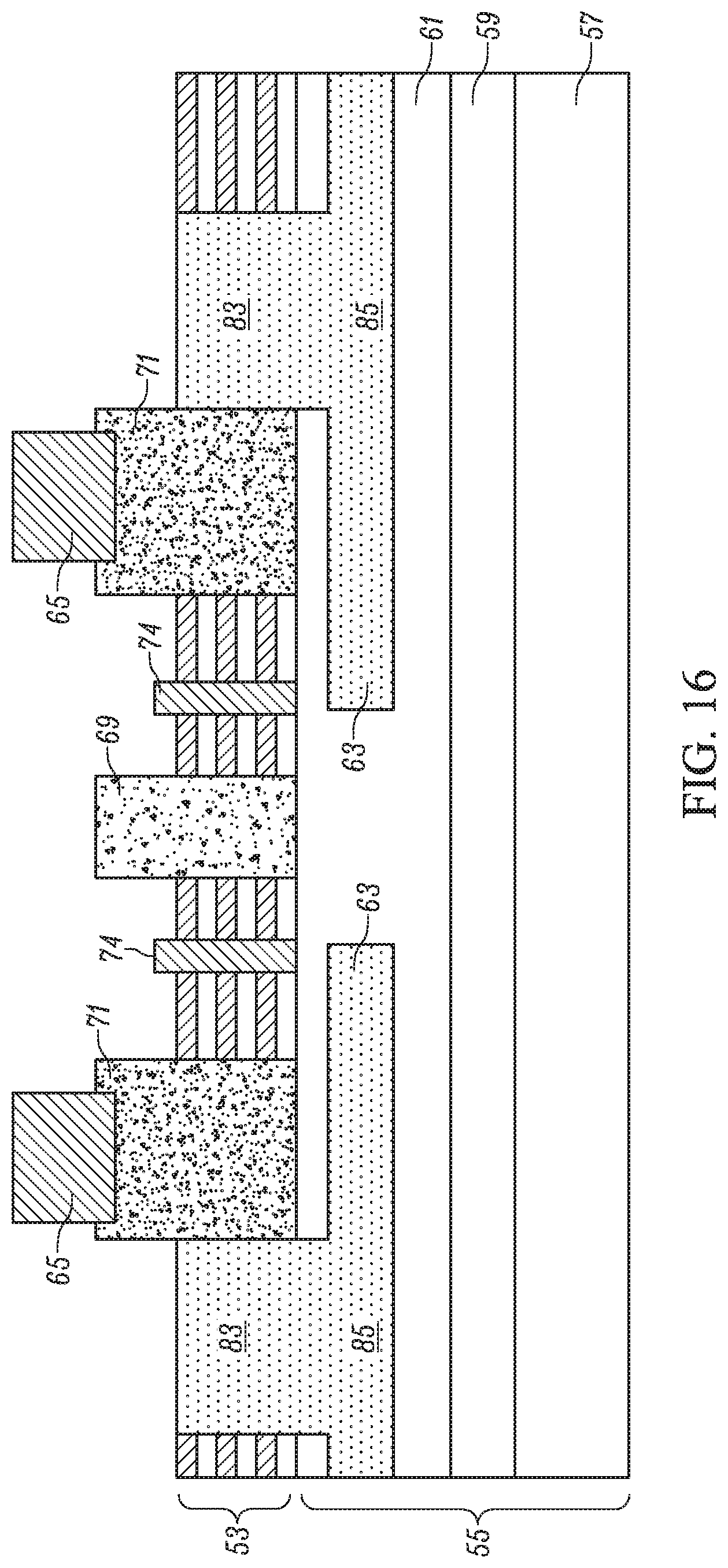

[0024] FIG. 16 illustrates a cross-sectional view of the structure of FIG. 15 after metallization of a source contact and a castellated gate contact.

[0025] FIG. 17 illustrates a cross-sectional view of the structure of FIG. 16 after formation of a backside drain contact.

[0026] FIG. 18 illustrates a cross-sectional view of another example SLCFET with its drain contact horizontally disposed from the source contacts so that all connections are located on a top side of the vSLCFET.

[0027] FIG. 19 illustrates an example cross-sectional view of another example vSLCFET in which the buried blocking layer formed in the SiC substrate material rather than the epitaxial GaN. The floating drain is extended downward to reach the underlying SiC substrate as well.

DETAILED DESCRIPTION

[0028] One or more examples of vertical superlattice castellated field-effect-transistors (vSLCFETs) are disclosed having a high breakdown voltage and providing for high power operation. Gallium Nitride (GaN) devices on Silicon Carbide (SiC) are useful when fabricating superlattice castellated field-effect-transistor (SLCFET) devices for use in power transistors because their combination provides for a wide bandgap in GaN and a high thermal conductivity in SiC. Vertical device structures are suitable for high voltage RF switches because the geometries and material locations provide for a large voltage between source contacts and drain contacts. Thus, some of the various examples discussed below disclose how a SLCFET can be adapted to work in a vertical configuration, enabling a GaN-on-SiC power transistor with high current density and low-loss advantages inherent to the SLCFET structure.

[0029] The vSLCFET utilizes an epitaxial approach of stacked superlattice channels on top of a substrate to yield an improved high-voltage transistor with low resistance. However, stacked 2DEG channels funnel conduction in a horizontal manner that is incompatible with vertical structures, such as vertical double-implemented metallic-oxide field-effect-transistors (FETs) (DMOSFETs) and current aperture vertical electron transistors (CAVETs). In order to funnel current from the upper levels of the stacked superlattice downwards into the substrate, at least some examples disclosed use a floating drain or floating drain plunger inserted within a generally circular source region having a generally circular source electrode, as discussed in detail below.

[0030] A castellated gate contact controls current flow from the source electrodes to the floating drain. The castellated gate contact is disposed between the source region and the floating drain plunger. The castellated gate contact substantially surrounds on top and on its sides over at least a portion of its depth a plurality of superlattice heterostructure ridges (multichannel ridges) that form a set of channels. The floating drain has a relatively low resistance and can direct the current through the substrate toward the bottom of the device. A drain or drain plug can be disposed on a bottom side of the device to capture the current. The vSLCFET device is in a normal "ON" state when no voltage is applied to the gate contact, and can be turned to an "OFF" state by applying a threshold voltage to the castellated gate contact.

[0031] In another example, a monolithic microwave integrated circuit (MMIC) or MMIC-compatible version of the example illustrated in example FIG. 1 is disclosed, where contacts including a drain contact are all accessed through a topside of the device. This would be compatible with operating voltages in the 100V range, potentially useful for power conditioning applications integrated on-chip with MMICs for efficient power distribution.

[0032] FIG. 1 illustrates a cross-sectional view of an example of a vSLCFET device 10 (device) having a castellated gate structure and a floating drain. FIG. 2 illustrates a partial cross-sectional view of an example of a portion of a multichannel ridge of the vSLCFET device 10 of FIG. 1 along the lines 2-2. FIG. 3 illustrates a top plan view of the vSLCFET device 10, and FIG. 4 illustrates a partial cross-sectional view of an example of a portion of a castellated gate surrounding a portion of a superlattice heterostructure of alternating multichannel ridges and non-channel openings of the vSLCFET device 10 of FIG. 1 along the lines 4-4 of FIG. 3. Although the present example is illustrated as a generally circular device as shown in the top plan view of FIG. 3, the vSLCFET device 10 can have a variety of different configurations, such as a multiple finger device, a generally rectangular device or a variety of other configurations.

[0033] The vSLCFET device 10 includes a castellated gate contact 24 disposed between a source region 30 and a floating drain 19 (n+region). The castellated gate contact 24 substantially surrounds three sides of a plurality of multichannel ridges 36. The plurality of multichannel ridges 36 are each formed from plurality of heterostructures that includes stacks of an AlGaN layer overlying a GaN layer. The plurality of multichannel ridges 36 are separated from one another by non-channel openings 22 (FIG. 4). The plurality of multichannel ridges 36 extend between the source region 30 to the floating drain 19. The castellated gate contact 24 extends through the non-channel openings such that the castellated gate contact 24 electrically couples each of the plurality of multichannel ridges 36 to one another. The vSLCFET device is in a normal "ON" state when no voltage is applied to the castellated gate contact, and can be turned to an "OFF" state by applying a threshold voltage to the castellated gate contact.

[0034] The source region 30 includes a source interface region 21 (n+doped region) that interfaces with the plurality of multichannel ridges 36, and a source ohmic contact 15. A high voltage protection region 13 is disposed adjacent and in contact with the source interface region 21. The high voltage protection region 13 includes a surface contact portion 33 (p+doped region) coupled to a buried portion 35 (p+doped region).

[0035] As illustrated in FIG. 2 and FIG. 4, each multichannel ridge 36 includes a plurality of heterostructures 4 that overly a base 5 (base structure). Three layers may be used to construct the base 5 including a substrate layer 7, a lattice material layer 9, and a buffer layer 11. A drain contact 43 extends from a bottom surface of the base 5, the lattice material layer 9, and a portion of the drift region toward the floating drain 19. A protection layer 25 that is a dielectric layer (FIG. 4), for example, of silicon nitride (SiN) can overly the vSLCFET device 10, and be disposed between the plurality of multichannel ridges 36 and the castellated gate contact 24.

[0036] The substrate layer 7 can be formed of Silicon Carbide (SiC), the lattice matching material layer 9 can be formed of Aluminum Galium Nitride layer (AlGaN, and the buffer layer 11 can be formed of an undoped GaN drift region. In one example implementation, an AlGaN layer 18 overlying a GaN layer 16 form one layer of the heterostructure 4. Each heterostructure 4 forms a portion of a channel of the multichannel gate formed from the plurality of multichannel ridges 36 of the vSLCFET device 10.

[0037] The multichannel ridges 36 can comprise a plurality of heterostructures that may number between 2 and K, where K is defined as the maximum number of heterostructures that can be grown, deposited or otherwise formed on each other without cracking or other mechanical failure in the layers or 2DEG channels. One of ordinary skill in the art appreciates that several values including the value of K, relative positions of AlGaN and GaN may be reversed, other suitable materials may be used, and other parameters, options, and the like that are desirable may be used to implement the multichannel ridges 36. By stacking a plurality of these two-material heterostructures, and with the addition of appropriate doping in the layers to maintain the presence of the 2D.times.G channels when stacking a plurality of heterostructure layers, the electron sheets are able to act in parallel, allowing for greater current flow through each heterostructure 4.

[0038] Carriers, which form a 2DEG in a standard channel of AlGaN/GaN, can be spontaneously generated and maintained due to piezoelectric and spontaneous polarization. In this case, the AlGaN barrier is strained by virtue of its epitaxial relationship with the GaN channel and since these materials are piezoelectric, free carriers are generated in the channel. Carriers may also be generated through the insertion of doping layers within the epitaxial stack. The strain state of barrier and channel layers used, in some examples, may control the carrier concentration in the AlGaN/GaN heterostructures. One of ordinary skill in the art understands that precise control of composition, thickness, and the ordering of the AlGaN and GaN layers provides for the precise control of the production of the vSLCFET device 10. An epitaxial scheme and device fabrication method may exploit this phenomenon, which is unique to the GaN-based material system, and allows for fabrication of high-voltage high-power low-loss RF switches.

[0039] Having described the components of a vSLCFET and their orientation, the benefits, use, and operation of a high voltage power vSLCFET is now described in more detail. As previously mentioned, a vertical superlattice castellated field-effect-transistor (vSLCFET) device has a high breakdown voltage and may operate at high power. The vSLCFET is a hybrid device that is adapted from a standard (horizontal) SLCFET device to work in a vertical orientation. The vertical orientation enables a GaN-on-SiC power transistor with the high layout current density while retaining the low-loss advantages inherent to a standard SLCFET device. Additionally, using the vSLCFET in place of traditional 2DEG provides the benefit of confining the current in the channel preventing leakage from the channel into the bulk and increasing the physical offset of source contacts from the drain contact without much penalty in series resistance. Designing a high voltage power transistor with a vertical orientation provides for a floating drain plunger to allow current to funnel from the upper levels of the stacked superlattice heterostructures downwards into the substrate. Furthermore, the floating drain 19 provides flexibility in the placement of the region across in which high voltage is spread out and dropped as current enters the floating drain 19.

[0040] As one example, the floating drain 19 may be sunk completely through the buffer layer 11 and lattice matching material layer 9 into the substrate layer 7. In such a situation, the device can combine the high mobility of a 2DEG or stacked 2DEG GaN channel with the voltage blocking capabilities of bulk SiC. In practice, the surface contact portion 33 of the high voltage protection region 13 may be grounded together and provide p-n junctions with the source interface region 21. During the off state, a large bias applied to the source region 30 cause a depletion field to grow together between the p+region to pinch off the device 10. The depletion region prevents the electric field from growing at the gate contact 24, thus, protecting the gates from the high electric fields.

[0041] When the device goes into the "on" state in response to an applied voltage drop across the source contact 15 and the gate contact 24, for example, the vSLCFET device 10 goes into a forward bias mode. In this mode, current flows (as shown by arrows AA in FIG. 5) from the source region 30 through the plurality of multichannel ridges 36 to the floating drain 19 (floating drain plunger). The floating drain 19 provides a pathway for the current to flow from the upper levels of the multichannel ridges 36 downwards towards the substrate as indicated by arrows A in FIG. 6. The current will then flow downwards from the floating drain 19 and through the buffer layer 11 to the drain contact 43. The downward flow of the current protects the gate from high voltage fields so that voltage breakdown is prevented.

[0042] In various example manufacturing methods and techniques of producing various vSLCFETs and other high voltage FETs the various example methods disclosed herein can provide for optimization of one or more device parameters such as, for example, the breakdown voltage, a pinch-off voltage, linearity and other device parameters. For example, the vSLCFET device 10 can be a side-pinching gate control contact multi-channel device, such as a superlattice castellated gate heterojunction field (e.g., switches) for a variety of applications such as time delay units, low loss phase shifters and attenuators, switch matrices, T/R switches, circulator replacements or as amplifiers, and the like. Though such multi-channel devices offer low on-state resistance, power consumption and related voltages can be very high and sometimes high enough to cause these devices to fail when operating at high voltages and high power.

[0043] During fabrication, carriers, which form a 2DEG in a standard channel of AlGaN/GaN, are spontaneously generated and maintained due to piezoelectric and spontaneous polarization, or introduced through dopants. In this case, the AlGaN barrier is strained by virtue of its epitaxial relationship with the GaN channel and since these materials are piezoelectric, free carriers are generated in the channel. The strain state of barrier and channel layers used, in some examples, may control the carrier concentration in the AlGaN/GaN heterostructures. One of ordinary skill in the art understands that precise control of composition, thickness, and the ordering of the AlGaN and GaN layers provides for the precise control of the production of the vSLCFET device 10. An epitaxial scheme and device fabrication method may exploit this phenomenon, which is unique to the GaN-based material system, and allows for fabrication of high-voltage high-power low-loss RF switches.

[0044] FIGS. 7-17 illustrate stages of an example method of fabrication in connection with formation of the example vSLCFET device illustrated in FIGS. 1-6. FIG. 7 illustrates a cross-sectional view of a vSLCFET device in its early stages of fabrication starting with a base structure 55. As discussed earlier, three layers may be used to construct the base structure 55 including a substrate layer 57, a lattice matching material layer 59, and a buffer layer 61. The substrate layer 57 can be formed of Silicon Carbide (SiC), the lattice matching material layer 59 can be formed of Aluminum Galium Nitride layer (AlGaN, and the buffer layer 61 can be formed of an undoped Galium Nitride (GaN) drift region.

[0045] FIG. 8 illustrates the stage where a protective etch mask 62 has been formed overlying the buffer layer 61. The etch mask 62 can be formed by depositing, patterning and developing a photoresist material layer over the buffer layer 61. FIG. 8 also illustrated the structure undergoing a dopant process 200 to form p-doped buried region 85 as shown in FIG. 9. Alternatively, an opening can be formed in the buffer layer 61 and doped material deposited in the opening to form p-doped buried region 85. FIG. 9 illustrates the resultant structure after the protective mask 62 has been removed.

[0046] Once the protective mask 62 has been removed, an intermediate dielectric layer 91 can be formed on the buffer layer 61, and the upper surface of the intermediate dielectric layer 91 or buffer layer 61 prepared for subsequent processing. A superlattice heterostructure 53 is then fabricated across the entire upper surface of the intermediate dielectric layer 91 resulting in the structure of FIG. 10. In one example implementation, each heterostructure is formed from an AlGaN layer overlying a GaN layer. Example methods of fabrication involve sequential growth of multichannel profiles in a monolithic epitaxial scheme known by those of ordinary skill in the art. By sequentially growing the epitaxial multichannel layers that will later become devices and appropriate doping, all devices fabricated from this structure will benefit from the inherently high-quality material properties, atomically flat interfaces and compositional control associated with epitaxial growth.

[0047] The epitaxial growth of different materials upon each other may optionally be enhanced with appropriate deposition technique(s) until the layered lattice structures illustrated in FIG. 10 has been produced. Any suitable technique for depositing each layer can be employed such as metal organic chemical vapor deposition (MOVCD), molecular beam epitaxy (MBE), Low Pressure Chemical Vapor Deposition (LPCVD), Plasma Enhanced Chemical Vapor Deposition (PECVD), High Density Chemical Plasma Vapor Deposition (HDPCVD), Atomic Layer Deposition (ALD), physical vapor deposition or high-density plasma chemical vapor deposition (HDPCVD) techniques, or other suitable deposition techniques.

[0048] FIG. 11 illustrates a formation of another protective mask 64 on the upper surface of the device being fabricated with portions of the mask 64 selectively removed to form openings 92. The protective mask 64 can be formed of a photoresist material or formed as a hard mask. FIG. 11 also illustrates the structure undergoing a p+dopant implantation process 220 to implant p+doped material into the heterostructure to form p+doped surface contact portion 83 (FIG. 12) that are in electrical contact with the p-doped buried region 85. The resulting structure is illustrated in FIG. 12 after the mask 64 has been removed. The p-doped buried region 85 and the p-doped surface contact portion 83 form high voltage protection region 63 that grow to pinch off the transistor in response to a high voltage across the drain and sources of the device in an "OFF" state.

[0049] FIG. 13 illustrates formation of an etch mask 70 with patterned openings 96 over the structure of FIG. 12. This etch mask 70 specifies (unblocks) areas where openings 98 (FIG. 14) are to be formed. The etch mask 70 can also be used to form a plurality of multichannel ridges from the superlattice heterostructure 53. That is, the multichannel ridges can be formed at this time/stage, or just prior or just after this stage. Techniques for forming alternating multichannel ridges and non-channel openings are disclosed in commonly owned U.S. Pat. No. 9,419,120, entitled, "Multichannel Devices with Improved Performances and Methods of Making the Same", and commonly owned U.S. Pat. No. 9,773,897, entitled, "Multichannel Devices with Gate Structures to Increase Breakdown Voltage", both of which are herein incorporated by reference.

[0050] Additionally, FIG. 13 illustrates the structure undergoing an etch process 230 to form the opening 98 and an opening 99 for depositing or regrowing n+doped material in the openings to form a source interface region 71 and a floating drain 69, respectively. The resultant structure is illustrated in FIG. 14 after the etch process 230 has been completed. Next, the structure undergoes a deposition or regrowth process to fill the openings with the n+doped material to form source interface region 71 and floating drain 69 (FIG. 15). The regrowth occurs at this stage until the n+regrowth has reached a height to the top of the etch mask. FIG. 15 illustrates the resultant structure after the n+regrowth has been completed and the etch mask 70 has having been removed.

[0051] Example FIG. 16 illustrates the structure of FIG. 15 after a source contact 65 has been formed onto the upper surface of the source n+regrowth region 71, so that source input connections can now be formed, and a castellated gate contact 74 through the multichannel ridges and non-channel openings. These metal components may be ohmic types of metal for creating input contacts for the source inputs. Next, the structure is flipped so that the base bottom is pointing upward. This orientation allows drain material to be deposited by etching the bottom of the base structure 55 to form an opening and performing a series of deposition processes to form a drain plug 93 as illustrated in FIG. 17. After the creation of the drain plug 93, a vSLCFET device 50 (FIG. 17) has the necessary major components and may be considered a generally completed SLCFET high-voltage power-transistor device.

[0052] FIG. 18 illustrates another example of a vSLCFET device 110 that has its source interface region 121 and source contact 115, floating drain 119, and castellated gate contact 124 all on the upper, surface of the vSLCFET device 110. Similar to the vSLCFET device 10 of FIG. 1, the vSLCFET device 110 of FIG. 18 includes a base 105 and a superlattice 103. In this example illustration, the base 205 includes an n+SiC region 107, an n-SiC drift region 109 overlying the n+SiC region 107, and an undoped GaN drift region 111 overlying the n-SiC drift region 109. Of course, other appropriate materials may be used for these or other components of the example vSLCFET device 110 of FIG. 18.

[0053] The example vSLCFET device 110 of FIG. 18 may include other components with similar compositions, geometries, and functionality to the vSLCFET device 10 of FIG. 1. The vSLCFET device 110 of FIG. 18 includes a high voltage protection region 113 to protect against high voltage off states. The primary difference between the example vSLCFET device 10 of FIG. 1 and example vSLCFET device 110 of FIG. 18 is that the drain 123 and its drain contact 127 is located off to the side of a source contact 115 away from the floating drain 119.

[0054] The operation of the example vSLCFET device 110 of FIG. 18 is initially similar to that the example vSLCFET device 10 of FIG. 1. As shown by arrows B in FIG. 18, current flows from the source contact 115 through the superlattice 103, through gate 124, when the gates are turned off, and then into the floating drain 119 (floating drain plunger). The floating drain 119 provides a pathway for the current to flow from the upper levels of the superlattice 103 downwards towards the base105. The current will then flow downwards from the floating drain 119 and through the doped drift region 109 (arrows B) and up to the drain 123 where it exits the vSLCFET device 110 through the drain contact 127.

[0055] FIG. 19 illustrates another example of a vSLCFET device 210 that has source interface region 221 and source contact 215, floating drain 219, and castellated gate 224 on the same, upper, surface of the vSLCFET device 210. The vSLCFET device 210 of FIG. 19 includes a base 205 and a superlattice 203. In this example illustration, the base 205 includes an n+SiC region 207, an n-SiC drift region 209 overlying the n+SiC region 207, and an undoped GaN drift region 211 overlying the n-SiC drift region 209. Of course, other appropriate materials may be used for these or other components of the example vSLCFET device 210 of FIG. 19.

[0056] The example vSLCFET device 210 of FIG. 19 may include other components with similar compositions, geometries, and functionality to the vSLCFET device 10 of FIG. 1. The vSLCFET device 210 of FIG. 19 includes a high voltage protection region 213 with a buried dopant region that reside in the n-SiC drift region 209. The primary difference between the example vSLCFET device 210 of FIG. 19 and example vSLCFET device 10 of FIG. 1 is that it contains a floating drain 219 that extends from a top surface of the vSLCFET device 210 through the undoped GaN drift region 211 to the n-SiC drift region 209.

[0057] The operation of the example vSLCFET device 210 of FIG. 19 is initially similar to that the example vSLCFET device 10 of FIG. 1. Current will flow (electrons or holes depending on a specific configuration) in response to an applied voltage drop across the source contact 215 and the castellated gate 224. Similar to the example vSLCFET device 10 of FIG. 1, current flows from the source contact 215 and source interface region 221 through the superlattice 203, through the castellated gate 224, when the castellated gate is turned off, and then into the floating drain 219 (floating drain plunger). The floating drain 219 provides a pathway for the current to flow from the upper levels of the superlattice 203 downwards towards the n-SiC drift region 209 and n+SiC region 207 to a drain (not shown) on the bottom of the vSLCFET device 210.

[0058] The examples of the invention described above are a merely a few representative examples of the invention. It is, of course, not possible to describe every conceivable combination of components or methodologies for purposes of describing the invention, but one of ordinary skill in the art will recognize that many further combinations and permutations of the invention are possible. Accordingly, the invention embraces all such alterations, modifications, and variations that fall within the scope of this application, including the appended claims.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

D00009

D00010

D00011

D00012

D00013

D00014

D00015

D00016

D00017

D00018

D00019

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.