Fault Current Mitigation Method And System For Solid State Circuit Breaker

Zhou; Xin ; et al.

U.S. patent application number 16/867640 was filed with the patent office on 2020-08-20 for fault current mitigation method and system for solid state circuit breaker. The applicant listed for this patent is Eaton Intelligent Power Limited. Invention is credited to Brian E. Carlson, Ruppert Russoniello, Xin Zhou.

| Application Number | 20200266624 16/867640 |

| Document ID | 20200266624 / US20200266624 |

| Family ID | 1000004828755 |

| Filed Date | 2020-08-20 |

| Patent Application | download [pdf] |

| United States Patent Application | 20200266624 |

| Kind Code | A1 |

| Zhou; Xin ; et al. | August 20, 2020 |

FAULT CURRENT MITIGATION METHOD AND SYSTEM FOR SOLID STATE CIRCUIT BREAKER

Abstract

A solid state circuit breaker apparatus includes a solid state switch, a current sensor, and a control circuit. The control circuit is programmed to operate the solid state switch by, in response to receipt of a signal from the current sensor indicating that an overcurrent condition exists: (i) using pulse width modulation to generate a set of control pulses; and (ii) using the control pulses to trigger the solid state switch to open and close in a pattern that corresponds to the control pulses, and thus limit an amount of let-through current that the solid state switch may pass to a load. The amount of let-through current that the solid state switch may pass to the load may be, for example, a threshold level above which the overcurrent condition will exist.

| Inventors: | Zhou; Xin; (Wexford, PA) ; Russoniello; Ruppert; (Sewickley, PA) ; Carlson; Brian E.; (Gibsonia, PA) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 1000004828755 | ||||||||||

| Appl. No.: | 16/867640 | ||||||||||

| Filed: | May 6, 2020 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| PCT/EP2019/025448 | Dec 10, 2019 | |||

| 16867640 | ||||

| 62777307 | Dec 10, 2018 | |||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | G01R 19/16528 20130101; H02H 9/025 20130101; H02H 3/025 20130101; H02H 3/006 20130101; H02H 9/002 20130101; G05F 1/573 20130101; G05F 1/462 20130101 |

| International Class: | H02H 9/02 20060101 H02H009/02; G05F 1/573 20060101 G05F001/573; H02H 3/02 20060101 H02H003/02; H02H 9/00 20060101 H02H009/00; H02H 3/00 20060101 H02H003/00; G01R 19/165 20060101 G01R019/165; G05F 1/46 20060101 G05F001/46 |

Claims

1. A solid state circuit breaker apparatus comprising: a solid state switch; a current sensor; and a control circuit, wherein the control circuit is programmed to operate the solid state switch by, in response to receipt of a signal from the current sensor indicating that an overcurrent condition exists: using pulse width modulation to generate a set of control pulses, and using the control pulses to trigger the solid state switch to open and close in a pattern that corresponds to the control pulses, and thus limit an amount of let-through current that the solid state switch may pass to a load.

2. The solid state circuit breaker apparatus of claim 1, wherein the control circuit is programmed to determine a frequency for the control pulses based on a maximum interruption current level of the solid state circuit breaker apparatus and circuit power factor.

3. The solid state circuit breaker apparatus of claim 1, wherein the control circuit is programmed to determine a trip time of the solid state switch based on a frequency for the control pulses.

4. The solid state circuit breaker apparatus of claim 1, wherein: a frequency for the control pulses is programmed into the control circuit; and the control circuit is programmed to determine a trip time for the solid state switch based on a level of the let-through current that the current sensor is detecting.

5. The circuit breaker apparatus of claim 1, wherein the control circuit comprises: a microprocessor that is configured to generate the set of control pulses; a gate drive circuit that is configured to receive the control pulses from the microprocessor and use the control pulses to trigger the solid state switch to open and close according to the pattern; and a hardware trigger circuit that is electrically connected to the current sensor and the gate drive circuit, and that is configured to: receive the signal from the current sensor indicating that the overcurrent condition exists, and send a trigger signal to the gate drive circuit to open the solid state switch.

6. The circuit breaker apparatus of claim 1, wherein the amount of let-through current that the solid state switch may pass to the load is a threshold level above which the overcurrent condition will exist.

7. The circuit breaker apparatus of claim 1, wherein the apparatus does not monitor current profile through the circuit breaker apparatus when the control pulses are triggering the solid state switch to open and close.

8. A transformer apparatus with a solid state circuit breaker apparatus comprising: a transformer; a conductive path leading from the transformer to a load output; a solid state switch in the conductive path; a current sensor positioned in the conductive path between the transformer and the solid state switch; and a control circuit, wherein the control circuit is programmed to operate the solid state switch by, in response to receipt of a signal from the current sensor indicating that an overcurrent condition exists: using pulse width modulation to generate a set of control pulses, and using the control pulses to trigger the solid state switch to open and close in a pattern that corresponds to the control pulses, and thus limit an amount of let-through current that the solid state switch may pass to a load.

9. The transformer apparatus of claim 8, wherein the control circuit is programmed to determine a frequency for the control pulses based on a maximum interruption current level of the solid state switch and circuit power factor.

10. The transformer apparatus of claim 8, wherein the control circuit is programmed to determine a trip time of the solid state switch based on a frequency for the control pulses.

11. The transformer apparatus of claim 8, wherein: a frequency for the control pulses is programmed into the control circuit; and the control circuit is programmed to determine a trip time for the solid state switch based on a level of the let-through current that the current sensor is detecting.

12. The transformer apparatus of claim 8, wherein the control circuit comprises: a microprocessor that is configured to generate the set of control pulses; a gate drive circuit that is configured to receive the control pulses from the microprocessor and use the control pulses to trigger the solid state switch to open and close according to the pattern; and a hardware trigger circuit that is electrically connected to the current sensor and the gate drive circuit, and that is configured to: receive the signal from the current sensor indicating that the overcurrent condition exists, and send a trigger signal to the gate drive circuit to open the solid state switch.

13. The transformer apparatus of claim 8, wherein the amount of let-through current that the solid state switch may pass to the load is a threshold level above which the overcurrent condition will exist.

14. The transformer apparatus of claim 8, wherein the apparatus does not monitor current profile through the solid state switch when the control pulses are triggering the solid state switch to open and close.

15. A method for controlling a solid state circuit breaker system to limit current to a load output in overcurrent conditions, the method comprising: operating a circuit having a conductive path between a power source and a load output and also having a solid state switch in the conductive path; by a current sensor, monitoring a level of current through the conductive path and sending a signal to the control circuit indicating that an overcurrent condition exists; by a control circuit, upon receiving the signal from the current sensor, using pulse width modulation to generate a set of control pulses; and by the gate drive circuit, using the set of control pulses to trigger the solid state switch to open and close in a pattern that corresponds to the control pulses, wherein the opening and closing of the solid state switch limits a level of let-through current that the solid state switch passes to the load output.

16. The method of claim 15, further comprising: by the control circuit, using the set of control pulses to trigger the solid state switch to open and close at a specified frequency, wherein the specified frequency controls the level of let-through current that the solid state switch passes to the load output.

17. The method of claim 15, further comprising determining the specified frequency for the control pulses based on a maximum interruption current level of the solid state circuit breaker apparatus and circuit power factor.

18. The method of claim 15, further comprising determining a trip time of the solid state switch based on the specified frequency for the control pulses.

19. The method of claim 15, further comprising determining a trip time for the solid state switch based on the level of the current that the current sensor is detecting.

20. The method of claim 15, wherein: the control circuit comprises: a microprocessor, a gate drive circuit that is electrically connected to the microprocessor and to the solid state switch, and a hardware trigger circuit that is electrically connected to the current sensor and to the gate drive circuit; and wherein: generating the set of control pulses is performed by the microprocessor; using the set of control pulses to trigger the solid state switch to open and close in the pattern is performed by the gate drive circuit, and the method further comprises, by the hardware trigger circuit, sending a trigger signal to the gate drive circuit to open the solid state switch in response to receiving the signal from the current sensor indicating that the overcurrent condition exists.

21. The method of claim 15, wherein the amount of let-through current that the solid state switch passes to the load output is a threshold level above which the overcurrent condition will exist.

22. The method of claim 15, further comprising dynamically determining the amount of let-through current that the solid state switch may pass to the load output as perspective fault current of the solid state switch.

23. The method of claim 15, wherein current profile through the circuit when the control pulses are triggering the solid state switch to open and close.

Description

RELATED APPLICATIONS AND CLAIM OF PRIORITY

[0001] This patent document claims priority to, and is a continuation-in-part under 35 U.S.C. .sctn. 111(a) of, International Patent Application Number PCT/EP2019/025448, which was filed Dec. 10, 2019. International Patent Application Number PCT/EP2019/025448 claims priority to U.S. provisional patent application No. 62/777,307, filed Dec. 10, 2018, titled "Fault Current Mitigation Method and System for Solid State Circuit Breaker".

BACKGROUND

[0002] This disclosure is related to methods and systems for controlling solid state circuit breakers.

[0003] Circuit breakers are designed to provide protection for power distribution systems. Circuit breakers safeguard connected electrical devices and conductors against current overloads and short circuits, thereby protecting people and equipment in the field.

[0004] When a fault occurs in a low voltage power distribution system, fault current will flow from a source (such as a transformer) through the system to the source of the fault. A low voltage solid state circuit breaker, which in alternating current (AC) systems is typically rated at approximately 600 volts AC (VAC), 480 VAC or 240 VAC, can interrupt a fault very quickly--typically in tens or hundreds of microseconds. This fast reaction time significantly reduces the fault current that flows through the system and thus protects the system. However, it can present a challenge in that the solid state circuit breaker must be able to just as quickly distinguish a fault from a temporary overload (or even high rated current).

[0005] This disclosure describes systems that address at least some of the technical issues discussed above, and/or other issues.

SUMMARY

[0006] In various embodiments, a solid state circuit breaker apparatus includes a solid state switch, a current sensor, and a control circuit. The control circuit is programmed to operate the solid state switch by, in response to receipt of a signal from the current sensor indicating that an overcurrent condition exists: (i) using pulse width modulation to generate a set of control pulses; and (ii) using the control pulses to trigger the solid state switch to open and close in a pattern that corresponds to the control pulses, and thus limit an amount of let-through current that the solid state switch may pass to a load. The amount of let-through current that the solid state switch may pass to the load may be, for example, a threshold level above which the overcurrent condition will exist.

[0007] In some embodiments, the control circuit may be programmed to determine a frequency for the control pulses based on a maximum interruption current level of the solid state switch and circuit power factor. Additionally or in other embodiments, the control circuit may be programmed to determine a frequency for the control pulses based on a trip time of the solid state switch. Additionally or in other embodiments, a frequency for the control pulses may be programmed into the control circuit, and the control circuit may be programmed to determine a trip time for the solid state switch based on a level of the let-through current that the current sensor is detecting.

[0008] In various embodiments, the control circuit may include a microprocessor that is configured to generate the set of control pulses, a gate drive circuit that is configured to receive the control pulses from the microprocessor and use the control pulses to trigger the solid state switch to open and close according to the pattern, and a hardware trigger circuit that is electrically connected to the current sensor and the gate drive circuit. The hardware trigger circuit may be configured to receive the signal from the current sensor indicating that the overcurrent condition exists, and also to send a trigger signal to the gate drive circuit to open the solid state switch.

[0009] The circuit breaker apparatus may be incorporated into various elements of equipment, such as a transformer having a conductive path leading from the transformer to a load output, in which the circuit breaker's solid state switch is positioned in the conductive path.

[0010] In various embodiments, a method for controlling a solid state circuit breaker system to limit current to a load output in overcurrent conditions includes: (i) operating a circuit having a conductive path between a power source and a load output and also having a solid state switch in the conductive path; (ii) by a current sensor, monitoring a level of current through the conductive path and sending a signal to the control circuit indicating that an overcurrent condition exists; (iii) by a control circuit, upon receiving the signal from the current sensor, using pulse width modulation to generate a set of control pulses; and (iv) by the control circuit, using the set of control pulses to trigger the solid state switch to open and close in a pattern that corresponds to the control pulses, wherein the opening and closing of the solid state switch limits a level of let-through current that the solid state switch passes to the load output.

[0011] Optionally, the method may include, by the control circuit, using the set of control pulses to trigger the solid state switch to open and close at a specified frequency, wherein the specified frequency controls the level of let-through current that the solid state switch passes to the load output. Alternatively or in addition, the method may include determining the specified frequency for the control pulses based on a maximum interruption current level of the solid state switch and circuit power factor. Alternatively or in addition, the method may include determining a trip time of the solid state switch based on the specified frequency for the control pulses. Alternatively or in addition, the method may include determining a trip time for the solid state switch based on the level of the current that the current sensor is detecting.

BRIEF DESCRIPTION OF THE DRAWINGS

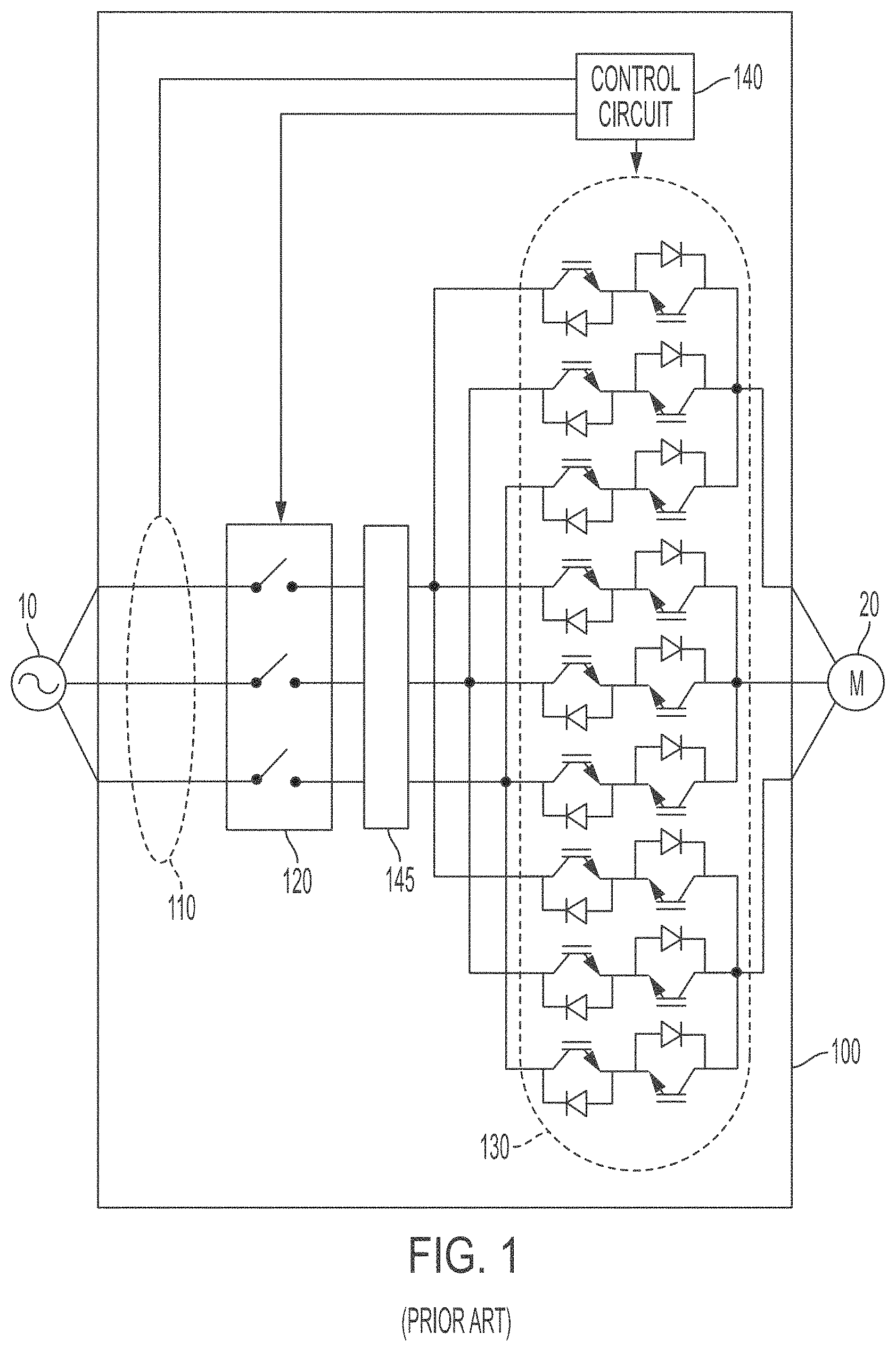

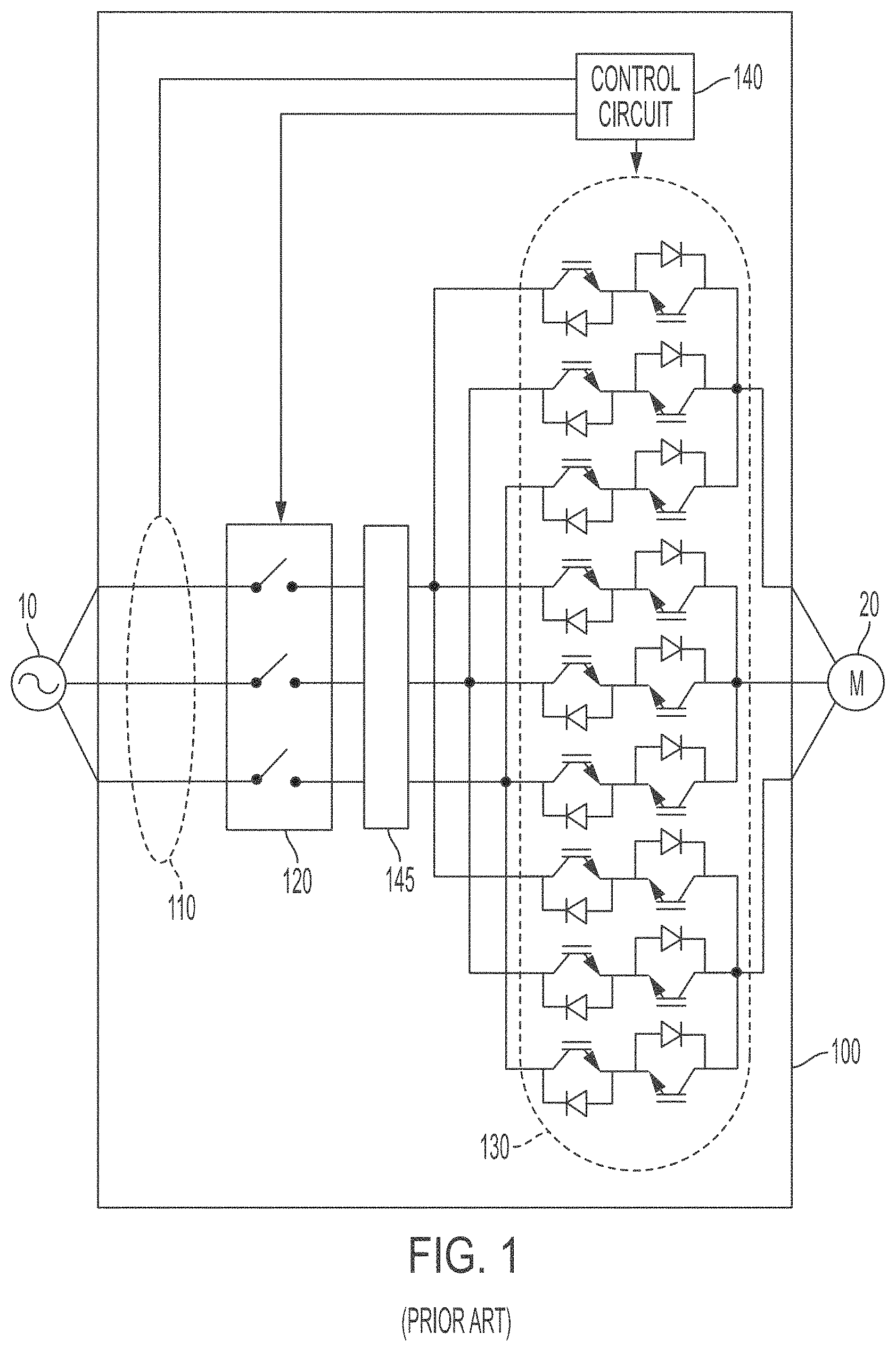

[0012] FIG. 1 is a block diagram of components of an example of a system that includes a solid state circuit breaker, such as may exist in the prior art.

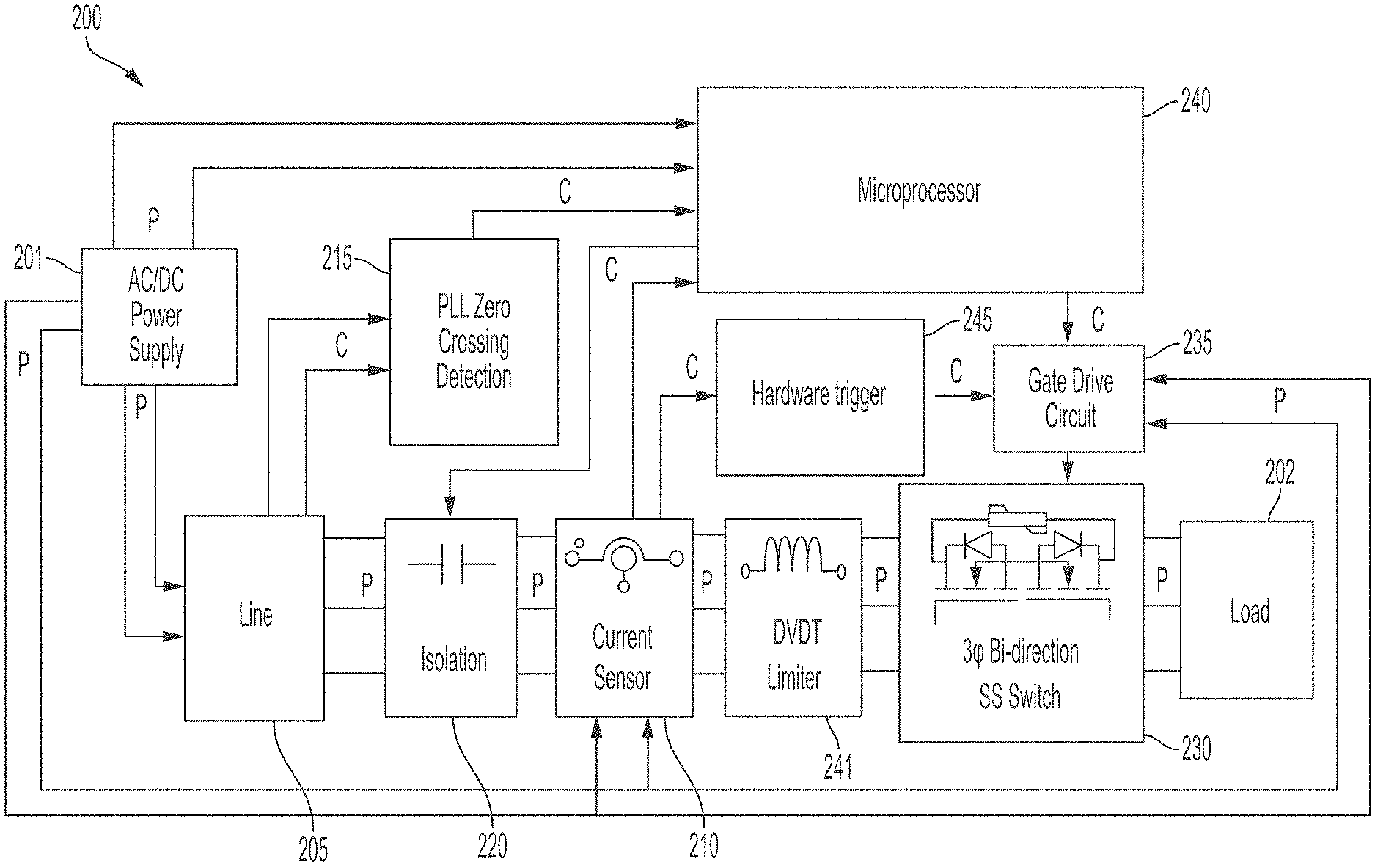

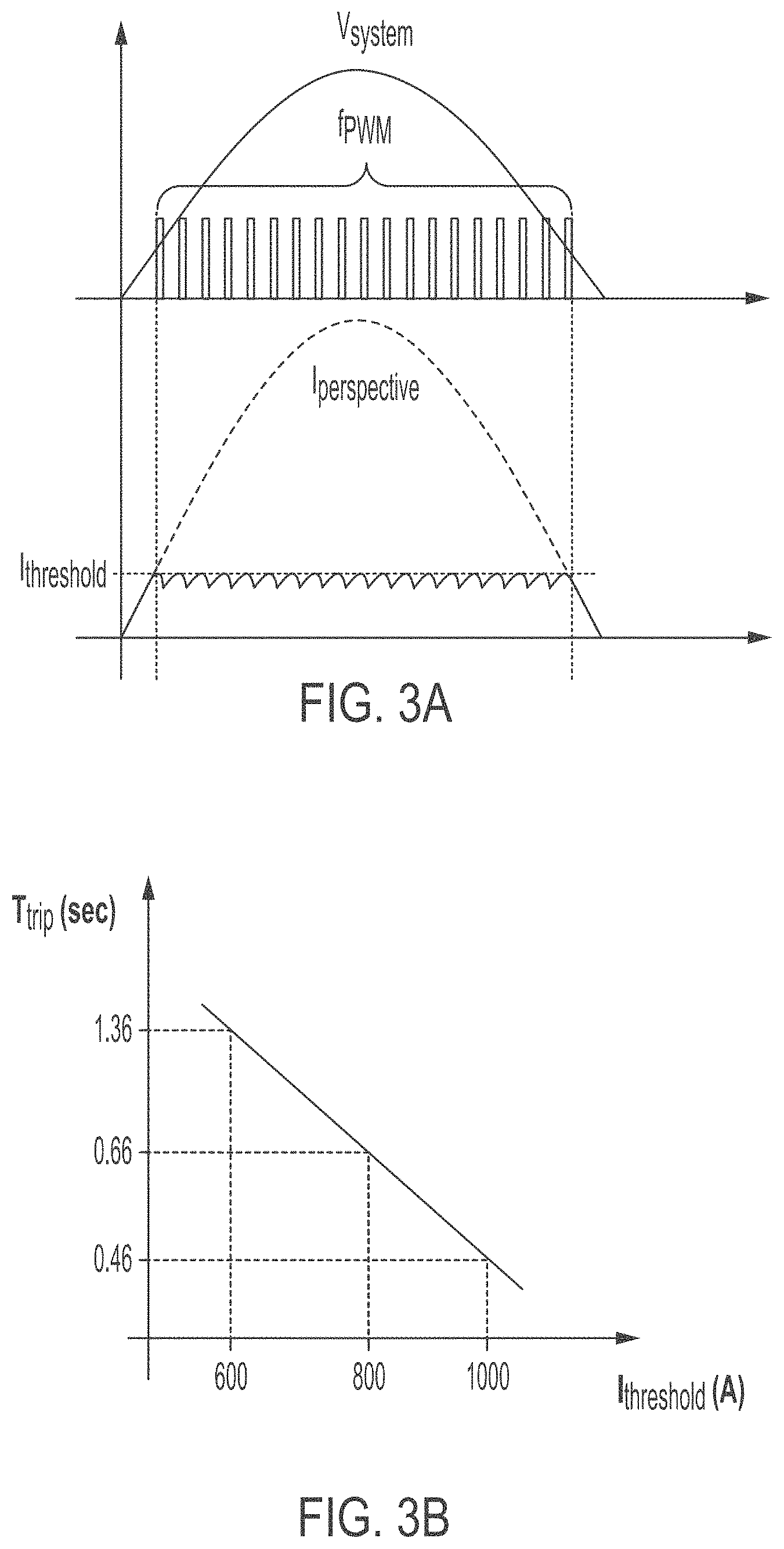

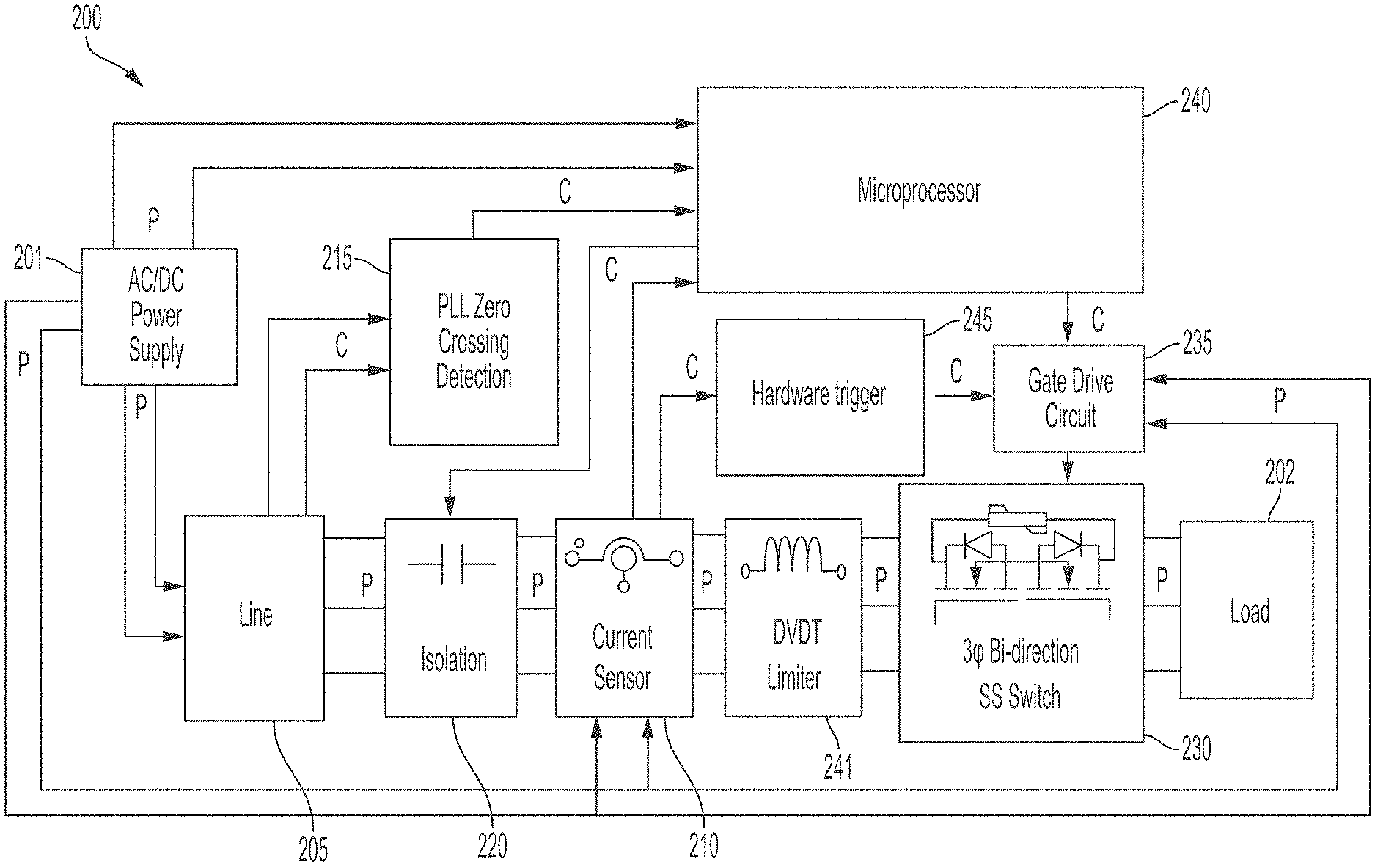

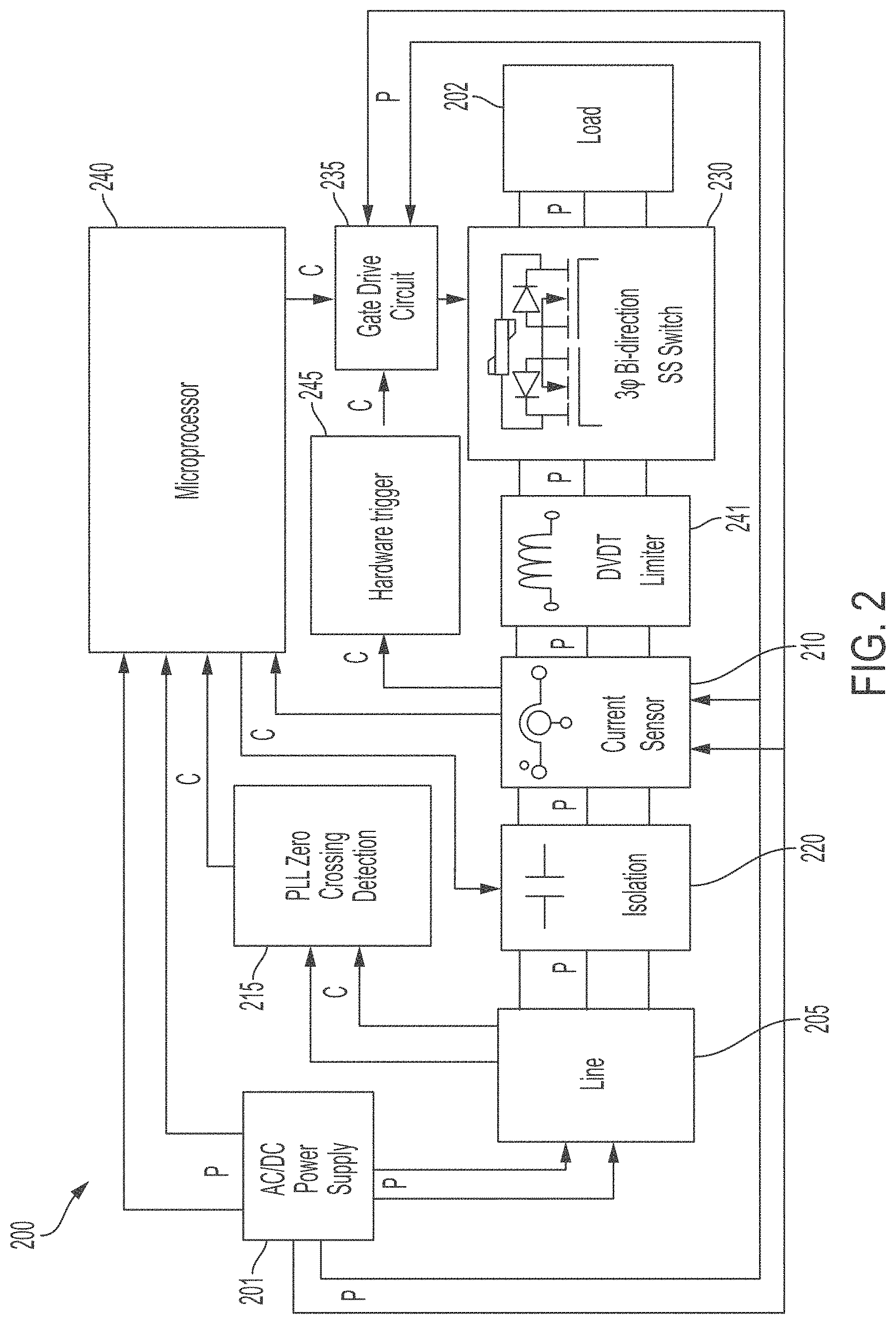

[0013] FIG. 2 is a block diagram of components of an example of a system that includes a solid state circuit breaker, with additional components according to the present embodiments.

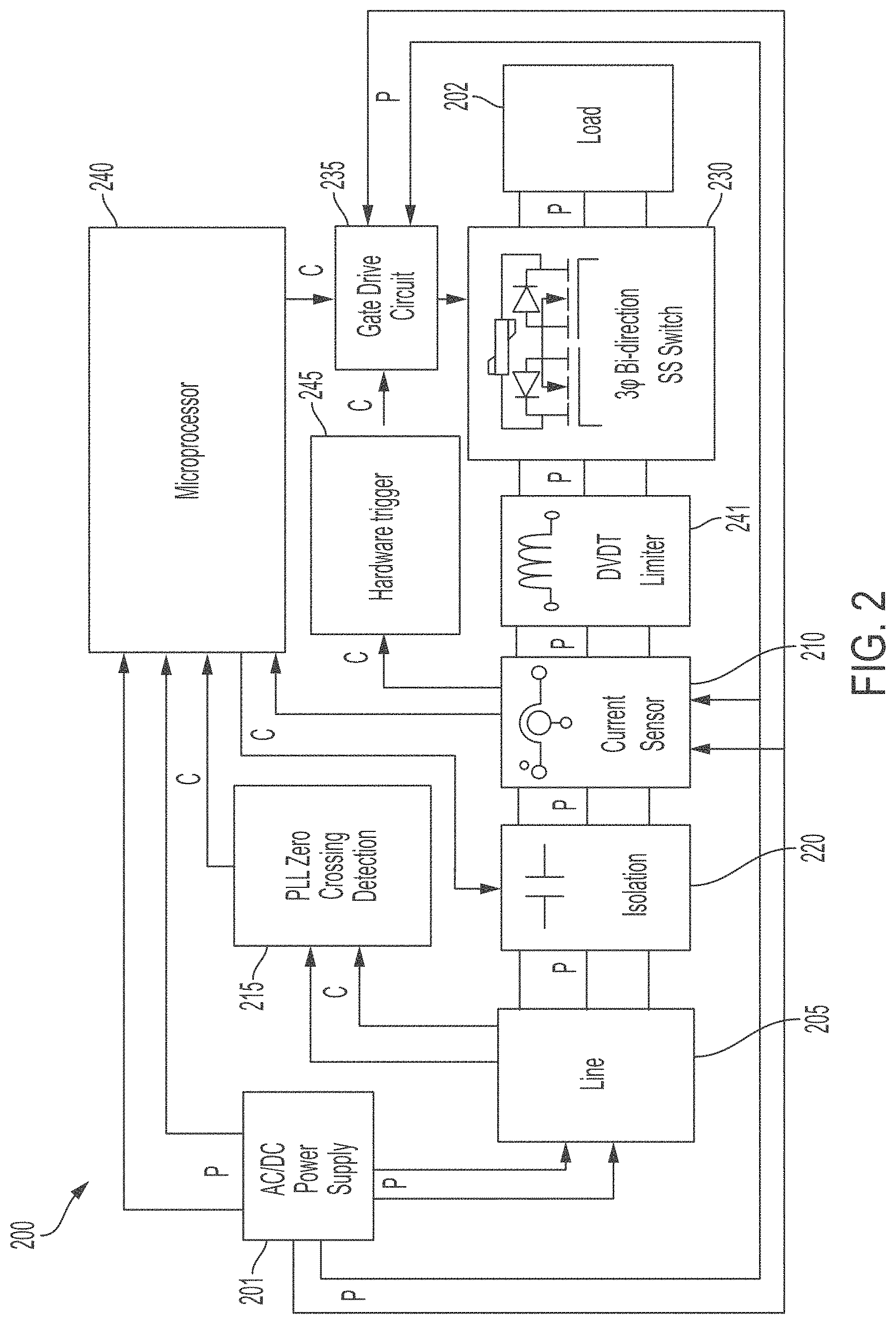

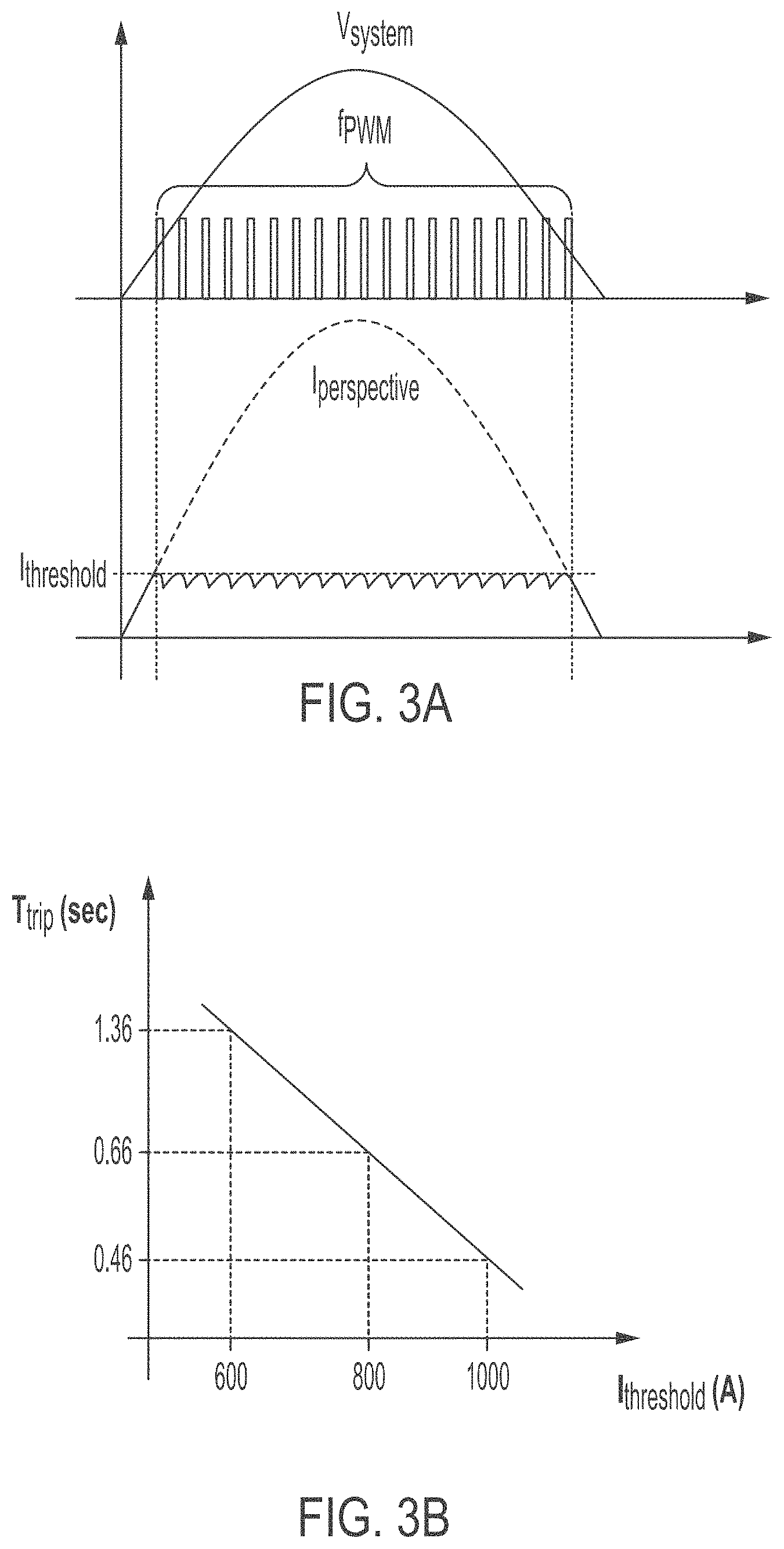

[0014] FIGS. 3A and 3B illustrate a first method of controlling a solid state circuit breaker.

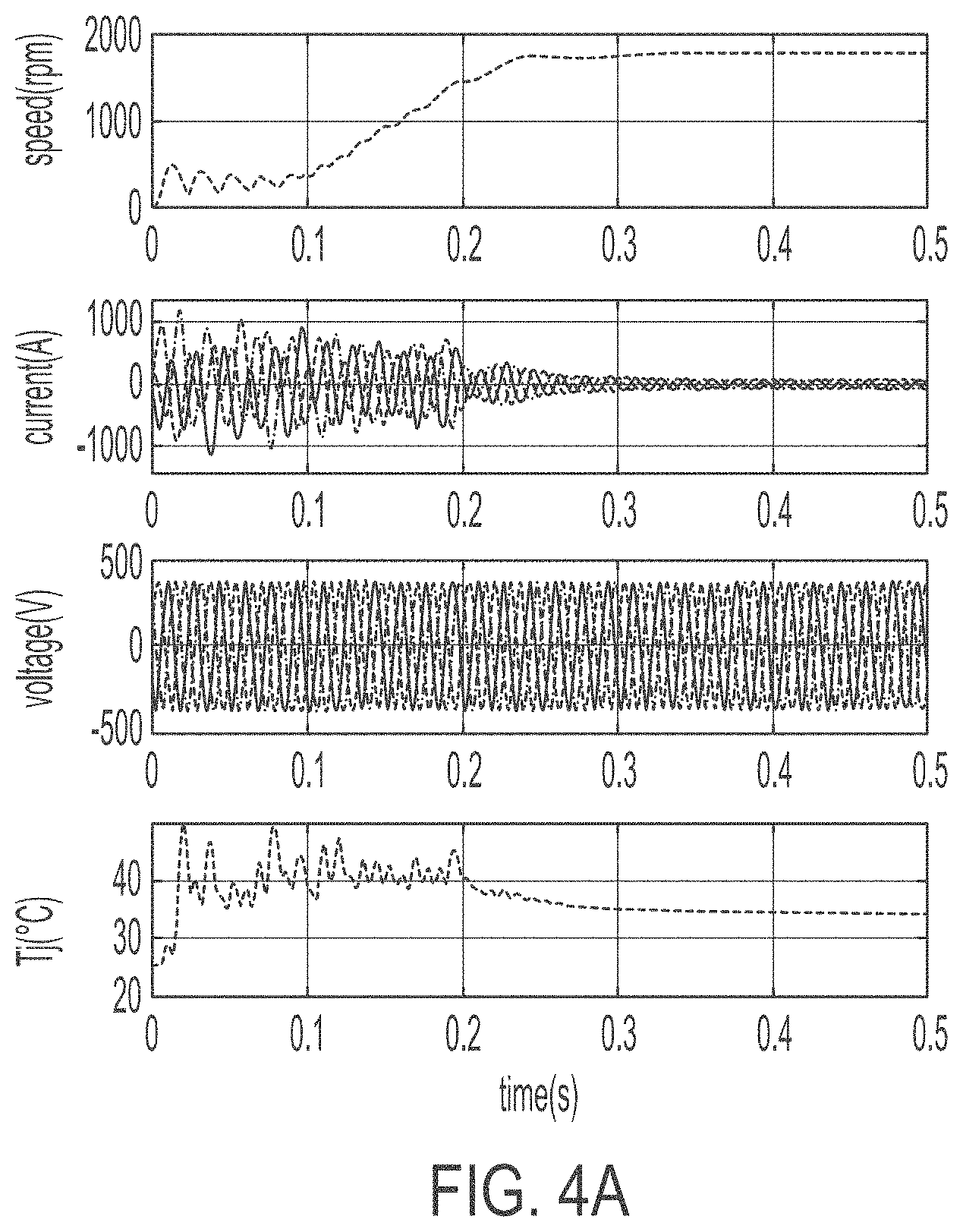

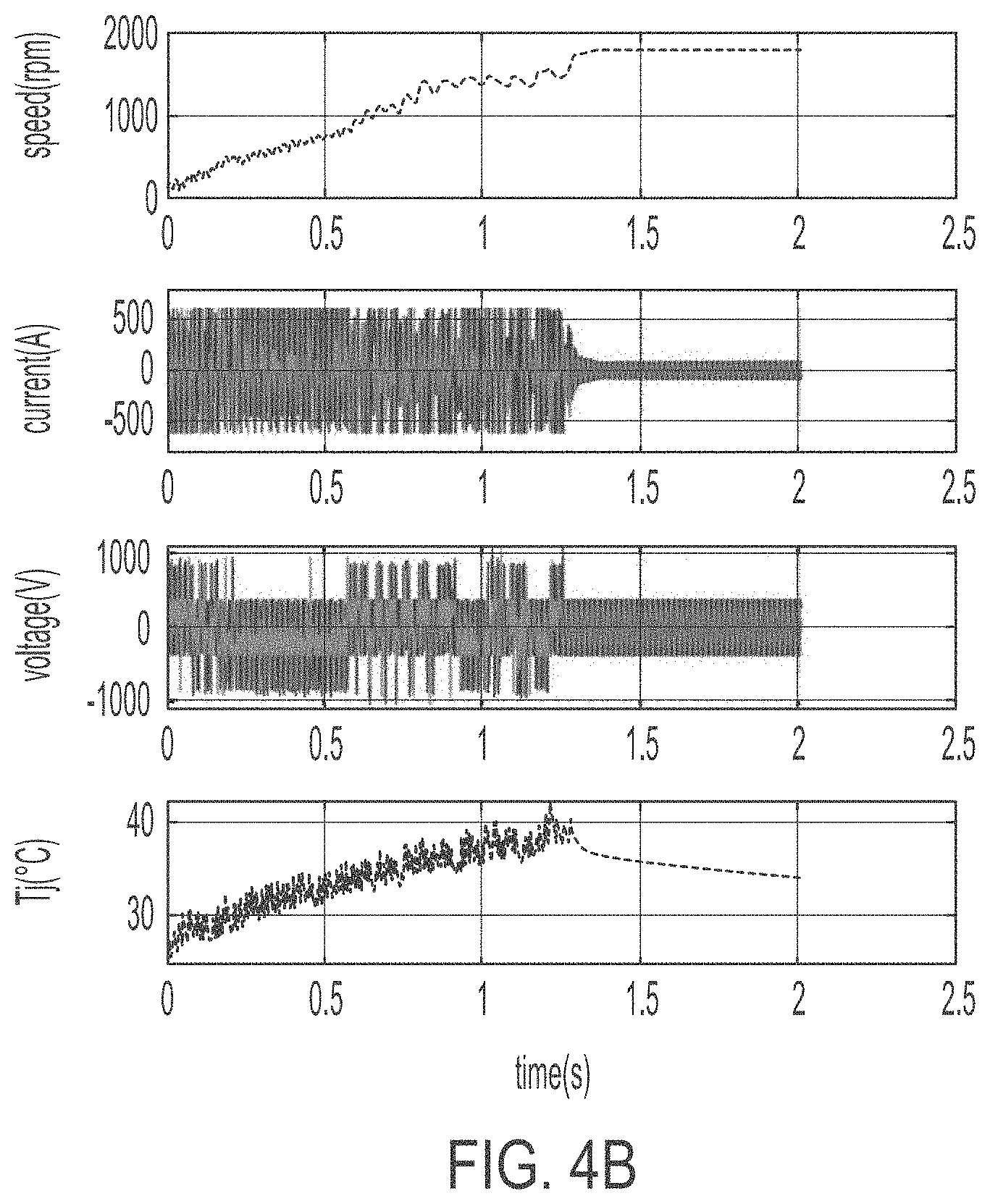

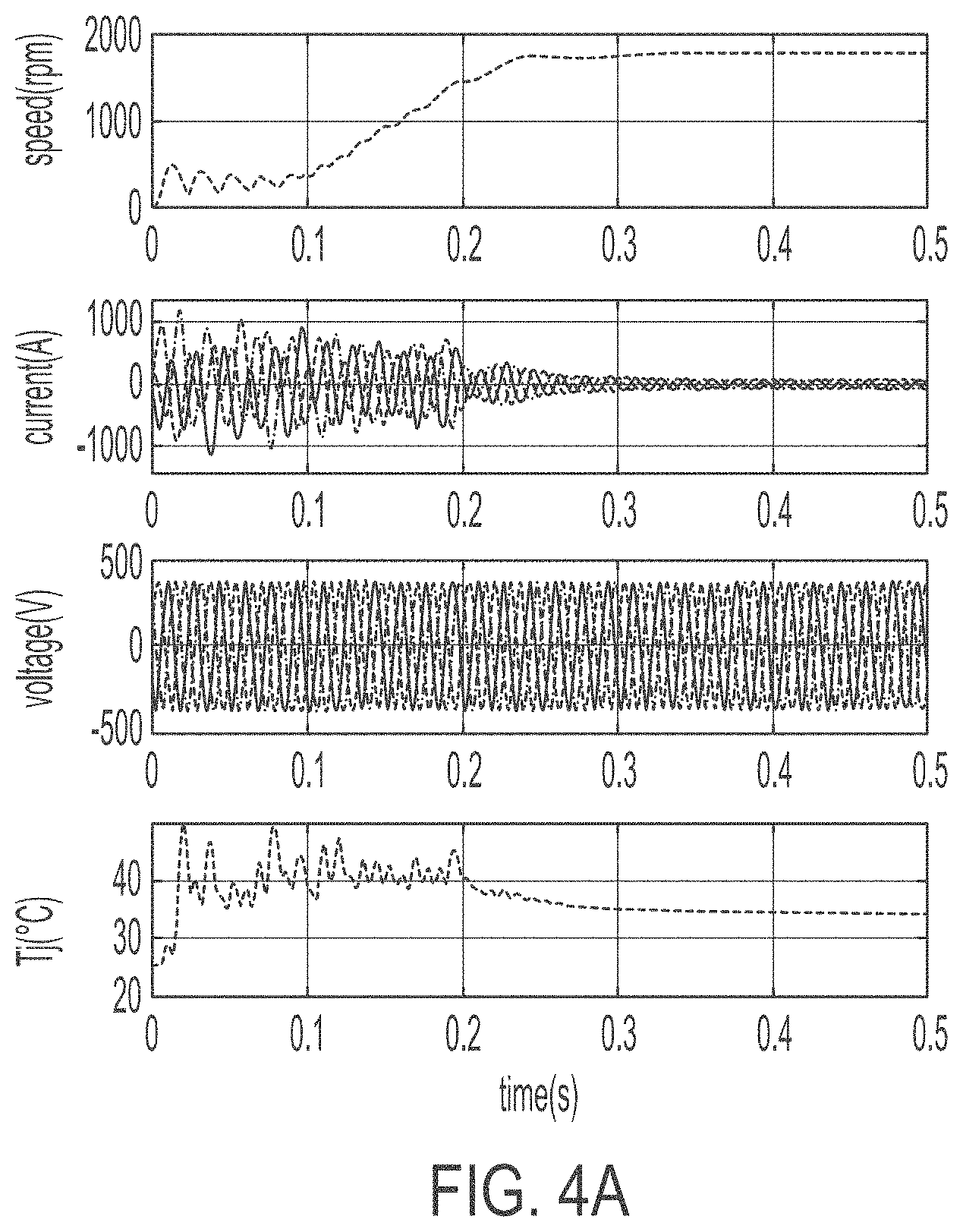

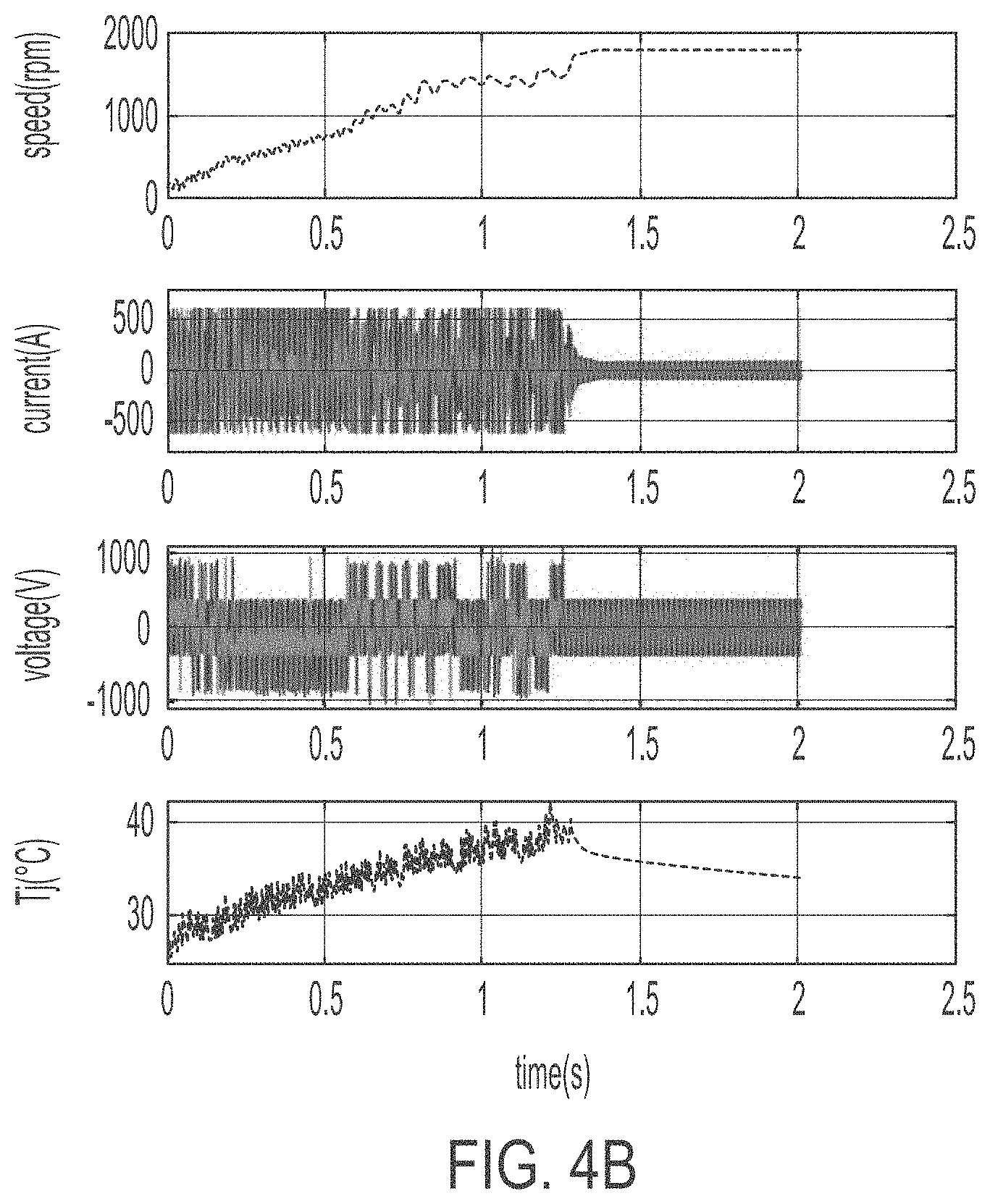

[0015] FIGS. 4A and 4B illustrate an example application of the method illustrated in FIGS. 3A and 3B to an induction motor with a direct on line starter.

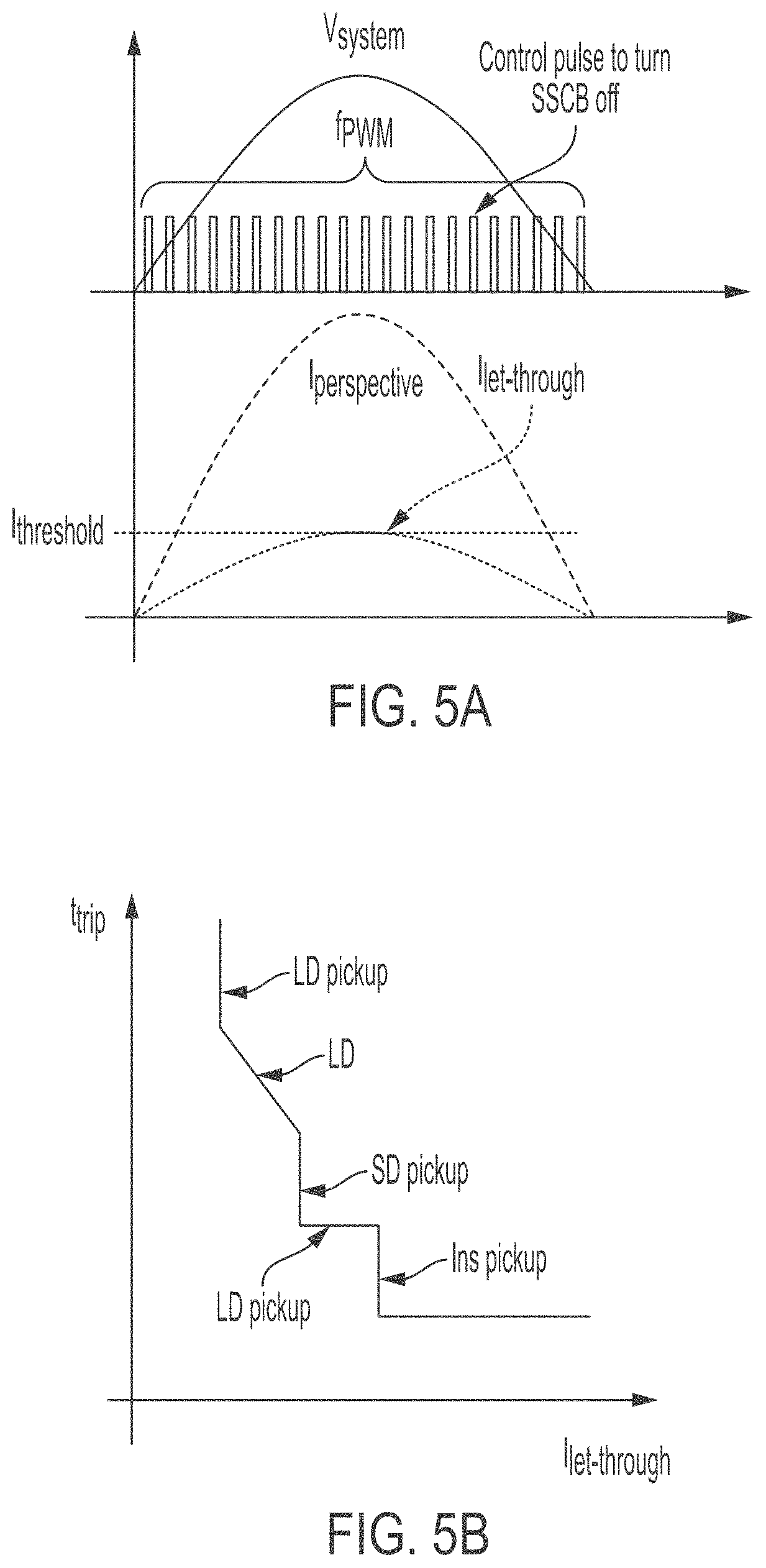

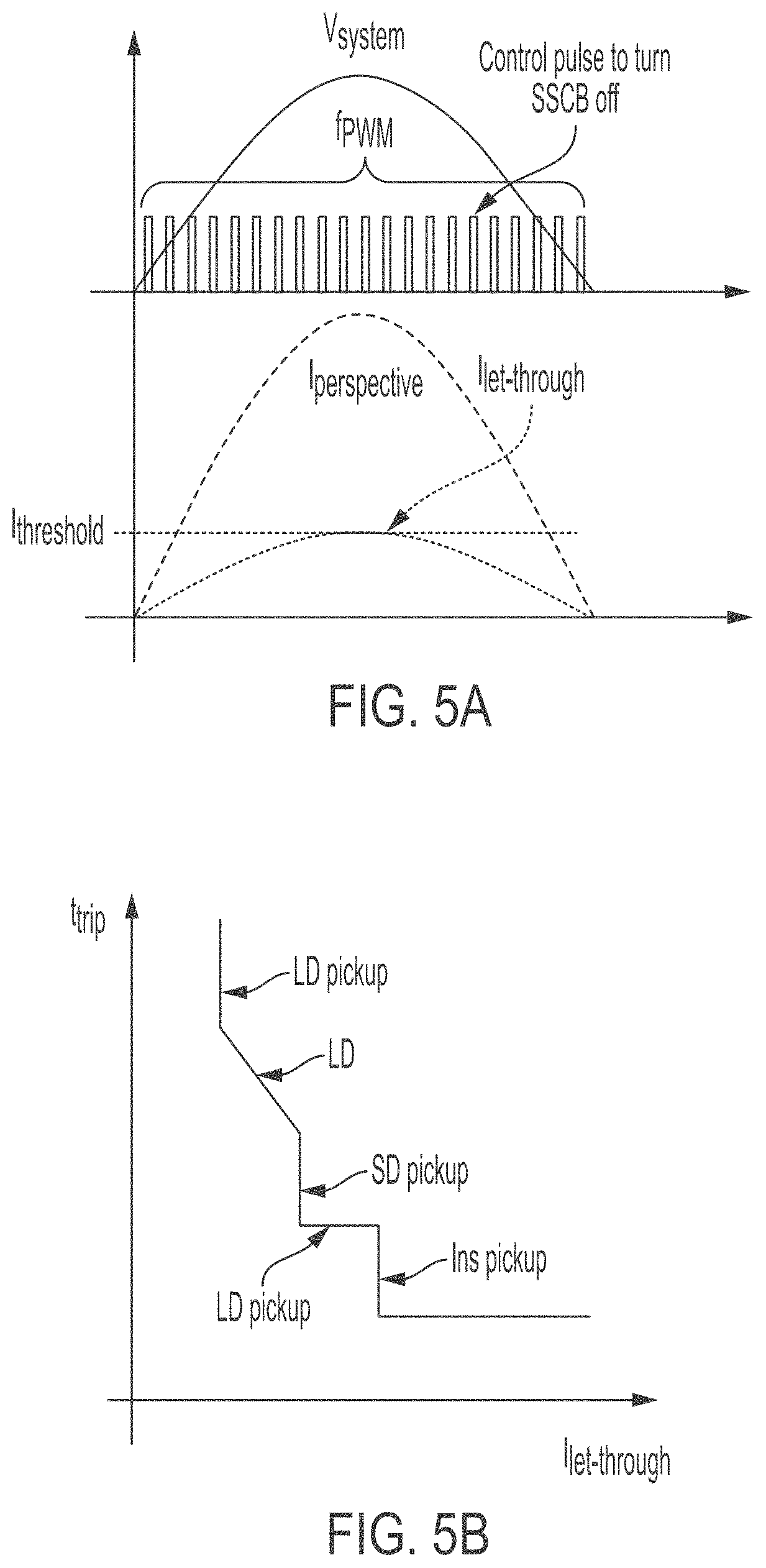

[0016] FIGS. 5A and 5B illustrate a second method of controlling a solid state circuit breaker.

DETAILED DESCRIPTION

[0017] As used in this document, the singular forms "a," "an," and "the" include plural references unless the context clearly dictates otherwise. Unless defined otherwise, all technical and scientific terms used herein have the same meanings as commonly understood by one of ordinary skill in the art. As used in this document, the term "comprising" means "including, but not limited to."

[0018] In this document, the terms "memory" and "memory device" each refer to a non-transitory device on which computer-readable data, programming instructions or both are stored. Except where specifically stated otherwise, the terms "memory" and "memory device" are intended to include single-device embodiments, embodiments in which multiple memory devices together or collectively store a set of data or instructions, as well as one or more individual sectors within such devices.

[0019] In this document, the terms "processor" and "processing device" refer to a hardware component of an electronic device (such as a controller) that is configured to execute programming instructions. Except where specifically stated otherwise, the singular term "processor" or "processing device" is intended to include both single processing device embodiments and embodiments in which multiple processing devices together or collectively perform a process.

[0020] FIG. 1 is a block diagram of a system that includes a solid state switch 130. In the system, power is delivered from a power source 10 such as a three-phase transformer to a load 20. The solid state switch 130 is positioned between the power and the load to disconnect the conductive path to the load when the system detects an overcurrent or fault event. The solid state switch 130 may be a conventional solid state relay or it may be a custom design, and it may or may not be bidirectional. As shown the solid state switch 130 may be made of an array of insulated gate bipolar transistors (IGBTs), although in some embodiments other switching components may be used, such as metal-oxide-semiconductor field-effect transistors (MOSFETs) or bipolar junction transistors (BJTs). The system 100 also includes a current sensor 110 and input filter 145 that are positioned between the power supply 10 and the solid state switch 130, along with a control circuit 140. The system also may include an isolation switch 120 that may be opened manually, or in response to a command from the control circuit 140, to ensure that the system is completely de-energized for maintenance.

[0021] The control circuit 140 may include a processor, with programming stored as memory and programming instructions (or as firmware or in the form of a programmable logic device such as a field-programmable gate array). The programming is configured to cause the control circuit 140 to issue signals to cause other components of the system to take action in response to certain actions. For example, the control circuit 140 may receive signals from the current sensor 110 that reflect the detected current level, and the control circuit 140 may cause the solid state switch 130 to open in response to detection of an overcurrent condition. Systems such as those of FIG. 1 may exist in the prior art.

[0022] FIG. 2 provides additional details of an example circuit breaker system 200 with a solid state switch 230 in accordance with the present embodiments. The solid state switch 230 is positioned along a conductive path between the power line input 205 and the load 202. In this example the solid state switch 230 is a three-phase bi-directional solid state switch. The power line input 205 may be connected to a power source. An AC/DC converter power supply 201 harvests power from the power line and powers the electronic components of the circuit, including a microprocessor 240 and a gate drive circuit 235, which will be described below.

[0023] A current sensor 210 detects the level of current traveling along the conductive path and provides output signals to the control circuit 240. The control circuit 240 includes a processor and programming instructions to take action in response to receiving an overcurrent signals from the current sensor 210. Such actions may include commanding the solid state switch 230 to open. The control circuit 240 may send such a command signal to a gate drive circuit 235, which amplifies the command signal into a high-current drive input that is sufficient to drive the gates of the transistors in the solid state circuit breakers.

[0024] The system also may include an isolation switch 220 that may be opened to de-energize the circuit and provide galvanic isolation for maintenance. An inductor 241 may be positioned in the conductive path near the solid state switch 230 to serve as a rate of current change (dI/dt) limiter and provide additional protection against sudden faults. A phase-locked loop (PLL) 215 may be connected to the conductive path to help the system measure the power frequency via zero crossing detection. The PLL 215 may provide the zero crossing information to the control circuit 240 which may use that information to measure the frequency of the line voltage and phase angle.

[0025] The system may include a hardware trigger circuit 245, which is an analog circuit that receives as its input a current signal from current sensor 210, and which uses comparators to compare the current signal to a predefined threshold. If the current signal level is higher than the predefined threshold, the hardware trigger circuit 245 will send a trigger signal to gate drive circuit 235 to open the solid state breaker (switch 230). This reduces or minimizes the time delay that is caused by the microprocessor circuit.

[0026] As noted in the Background section of this document, one issue with solid state circuit breakers is that they may not be able to distinguish an overload current or a high rated current or a brief spike in current from a fault condition in just a few microseconds or tens of microseconds. In traditional approaches, the solid state circuit breaker needs to trip nearly instantaneously in response to detecting current that exceeds a threshold so that the power electronic switch will not be damaged by the high current. This may result in the circuit breaker tripping in situations where it may not need to do so. In such situations, it may be desirable to keep the circuit operating for a period of time before fully triggering the solid state circuit breaker to open and remain open.

[0027] FIGS. 3A and 3B illustrate a first method by which a circuit breaker system such as that described above may mitigate fault current and other overcurrent conditions and allow the circuit to continue operating for a period of time in a reduced current condition before (or in lieu of) triggering the solid state switch. As illustrated in FIG. 3A, when the system detects an overcurrent condition (I.sub.perspective>I.sub.threshold) by receiving a signal of the condition from the current sensor, the processor uses pulse width modulation (PWM) to generate a control pulse at a frequency f.sub.PWM that will limit let-through current by the solid state switch. Rather than just triggering the circuit breaker to open and remain open, the control pulses will trigger the solid state switch breaker to open and close at a frequency that will effectively control the current that the circuit breaker lets through so that the current does not exceed a threshold level I.sub.threshold. As illustrated in FIG. 3B, the control circuit may be programmed to dynamically determine a trip time for the solid state circuit breaker as an inverse function of the threshold current level I.sub.threshold. (The numeric values shown in FIG. 3B follow an example that will be discussed in the context of FIGS. 4A and 4B.) Alternatively, the trip time t.sub.trip of the circuit breaker may be determined as a function of the frequency of the PWM pulses f.sub.PWM (i.e., the lower the frequency of the PWM pulses, the higher the trip time). In these ways, rather than passing the full potential current I.sub.perspective through to the load, the solid state circuit breaker would limit its let-through current to a maximum threshold level I.sub.threshold.

[0028] FIGS. 4A and 4B illustrate an example application of the method of FIGS. 3A and 3B in which an induction motor is started using a direct on line (DOL) starter. In this example, the motor is rated 75 kVA and operates at 1800 rotations per minute (rpm). As illustrated in FIG. 4A, in typical operation when the motor starts it will draw a peak current of approximately 1200 amps (A), and then settle to its normal operation with a nominal 67 A.sub.rms after about 0.24 seconds. When the method of FIGS. 3A and 3B is applied, FIG. 4B illustrates that the method limits inrush current to approximately 600 A. In normal operation the current will drop to its nominal 67 A.sub.rms after about 1.3 seconds when the motor reaches approximately 1800 rpm. However, with this method if there is a short circuit event the current will remain at a maximum of 600 A after the 1.3 second startup period. In addition, referring back to FIG. 3B, the trip time T.sub.trip is an inverse function of the current threshold I.sub.threshold. If the current threshold I.sub.threshold is 600 A as discussed in the example above, the trip time T.sub.trip is 1.36 seconds. However, if the current threshold I.sub.threshold is higher, the trip time T.sub.trip will be faster. For example, in the example shown in FIG. 3B if I.sub.threshold is 800 A then T.sub.trip will be 0.66 seconds; if I.sub.threshold is 100 A then T.sub.trip will be 0.46 seconds.

[0029] FIGS. 5 A and 5B illustrate an alternate method by which a system such as that described above shown may mitigate fault current and other overcurrent conditions. As with the embodiment of FIG. 3A, in this embodiment FIG. 5 A illustrates that the processor uses PWM to generate a control pulse at a predefined frequency that will limit let-through current by the solid state circuit breaker. In this case the PWM need not be triggered by an overcurrent condition, but instead may be initiated as soon as or shortly after the breaker closes. Or, the system may trigger PWN upon detecting current of a threshold level (such as a percentage of rated capacity) that is not necessarily an overcurrent condition. The PWM pulses will trigger the solid state switch to open and close at a defined frequency that will effectively control the current that the circuit breaker lets through so that the current does not exceed a threshold level I.sub.threshold that the solid state switch can withstand. For example, the threshold level I.sub.threshold may be a current level that is within the safe operating area of power electronic components of the switch such as insulated-gate bipolar transistors (IGBTs) or metal-oxide semiconductor field-effect transistors (MOSFETs). During operation, rather than maintaining the let-through current I.sub.let_through at a constant maximum level, the let-through current I.sub.let-through will vary as the perspective fault current I.sub.perspective varies, with a peak at the maximum threshold level I.sub.threshold corresponding to the maximum breaker interruption current level. The trip time t.sub.trip of the circuit breaker is a function of the let-through current curve I.sub.let-through, with: (i) a first period of long delay (LD pickup, associated with a low level of fault), followed by a short delay as the fault level increases, followed by an instantaneous trip when the let-through current reaches the maximum threshold I.sub.threshold.

[0030] In either of the embodiments listed above, the system may continue to operate the circuit breaker in this way up to a maximum period of time, or for a maximum number of current cycles. If the fault continues past the maximum time or cycles, the controller may trigger the circuit breaker to open and remain open until the fault is cleared.

[0031] In addition, in either of the embodiments listed above, the system may or may not continue to monitor the current profile (i.e., the variation in current over time), but instead may only monitor instantaneous current, or it may not monitor current at all when PWM is triggered.

[0032] The controller may further wait for a predefined period of time after the fault is cleared to reclose. The solid state circuit breaker may perform the same operation to the maximum period of time, or for the maximum number of current cycles, and after doing so it will reclose. If the fault persists past the maximum time or cycles, the controller may trigger the circuit breaker to open. The solid state circuit breaker may repeat this operation with different predefined or dynamically determined periods of times for one or more additional operations before it finally interrupts the fault and remains open, or it may reclose the circuit if the fault is gone.

[0033] The methods of operating a solid state circuit breaker described above, and circuits programmed to implement such methods, may be added to various power equipment items, such as transformers, reclosers, and other products. In addition, the methods and systems described above are not limited to low voltage applications, but could also be used in medium voltage applications that employ solid state or hybrid breakers, reclosers and the like.

[0034] Various alternatives, modifications, variations or improvements, and combinations may be made by those skilled in the art, each of which is also intended to be encompassed by, the disclosed embodiments.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.