Methods For Generating Wire Loop Profiles For Wire Loops, And Methods For Checking For Adequate Clearance Between Adjacent Wire

Kind Code

U.S. patent application number 16/856009 was filed with the patent office on 2020-08-06 for methods for generating wire loop profiles for wire loops, and methods for checking for adequate clearance between adjacent wire . The applicant listed for this patent is Kulicke and Soffa Industries, Inc.. Invention is credited to Basil Milton, Wei Qin.

| Application Number | 20200251444 16/856009 |

| Document ID | / |

| Family ID | 1000004778063 |

| Filed Date | 2020-08-06 |

| United States Patent Application | 20200251444 |

| Kind Code | A1 |

| Milton; Basil ; et al. | August 6, 2020 |

METHODS FOR GENERATING WIRE LOOP PROFILES FOR WIRE LOOPS, AND METHODS FOR CHECKING FOR ADEQUATE CLEARANCE BETWEEN ADJACENT WIRE LOOPS

Abstract

A method of generating a wire loop profile in connection with a semiconductor package is provided. The method includes the steps of: (a) providing package data related to the semiconductor package; and (b) creating a loop profile of a wire loop of the semiconductor package, the loop profile including a tolerance band along at least a portion of a length of the wire loop.

| Inventors: | Milton; Basil; (Furlong, PA) ; Qin; Wei; (Ambler, PA) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 1000004778063 | ||||||||||

| Appl. No.: | 16/856009 | ||||||||||

| Filed: | April 22, 2020 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 16401511 | May 2, 2019 | 10672735 | ||

| 16856009 | ||||

| 15623978 | Jun 15, 2017 | 10325878 | ||

| 16401511 | ||||

| 62357006 | Jun 30, 2016 | |||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 2224/45014 20130101; H01L 24/05 20130101; H01L 23/528 20130101; H01L 2224/48095 20130101; H01L 2224/05554 20130101; H01L 2924/00014 20130101; H01L 21/48 20130101; H01L 2224/48463 20130101; H01L 2224/49111 20130101; H01L 2224/85129 20130101; H01L 24/49 20130101; H01L 21/4889 20130101; H01L 2224/859 20130101; H01L 2224/85125 20130101; H01L 2224/49052 20130101; H01L 24/48 20130101; H01L 2224/4917 20130101; H01L 2224/49171 20130101; H01L 2224/48091 20130101; H01L 2224/85127 20130101; H01L 24/85 20130101; H01L 2224/4847 20130101; H01L 2224/85123 20130101; H01L 2224/49175 20130101 |

| International Class: | H01L 23/00 20060101 H01L023/00; H01L 21/48 20060101 H01L021/48; H01L 23/528 20060101 H01L023/528 |

Claims

1. A method of generating a wire loop profile in connection with a semiconductor package, the method comprising the steps of: (a) providing package data related to the semiconductor package; and (b) creating a loop profile of a wire loop of the semiconductor package, the loop profile including a tolerance band along at least a portion of a length of the wire loop.

2. The method of claim 1 wherein step (b) includes creating a three dimensional loop profile of the wire loop including the tolerance band.

3. The method of claim 1 wherein step (b) includes creating the loop profile for a plurality of wire loops in the semiconductor package.

4. The method of claim 3 further comprising the step of (c) checking if the loop profiles of the plurality of wire loops created in step (b) meet predetermined criteria.

5. The method of claim 4 wherein the predetermined criteria includes an acceptable level of clearance between ones of the loop profiles.

6. The method of claim 4 wherein at least one of the loop profiles is adjusted if the loop profiles do not meet the predetermined criteria.

7. The method of claim 1 wherein step (b) is performed using a computer on a wire bonding machine.

8. The method of claim 1 wherein step (b) is performed using a computer separate from a wire bonding machine.

9. The method of claim 1 wherein the wire loop connects at least two contact points on the semiconductor package.

10. The method of claim 1 wherein the wire loop is connected to a single contact point on the semiconductor package.

11. The method of claim 1 wherein the tolerance band is an indication of an acceptable position of the wire loop at a plurality of positions along a length of the wire loop.

12. The method of claim 1 wherein the loop profile is used to derive looping parameters on a wire bonding machine.

13. The method of claim 12 wherein the looping parameters derived include at least one of (i) a tool trajectory for forming the wire loop, (ii) bonding energy parameters to be applied by a transducer of the wire bonding machine, (iii) bonding force parameters to be applied by the wire bonding machine, (iv) timing parameters related to at least one of the bonding energy and bonding force, (v) bonding tool speed during at least a portion of a wire bonding cycle to form the wire loop, and (vi) a wire clamp position during at least a portion of a wire bonding cycle to form the wire loop.

14. The method of claim 1 wherein step (b) includes generating the loop profile including the tolerance band for each of a plurality of wire loops configured for bonding on the semiconductor package, the tolerance band of each of the being a function of the shape of the corresponding loop profile.

15. The method of claim 1 wherein the tolerance band has a circular shape at various points along the length of the wire loop.

16. The method of claim 14 wherein the circular shape of the tolerance band has a uniform diameter.

17. The method of claim 14 wherein the circular shape of the tolerance band has a diameter that varies at different locations along the length of the wire loop.

18. The method of claim 1 wherein the tolerance band has a non-circular shape at various points along the length of the wire loop.

19. The method of claim 1 wherein the package data provided in step (a) includes at least one of (a1) CAD data related to the semiconductor package and (a2) package data derived using an online teaching reference system of the wire bonding machine.

20. The method of claim 1 wherein the package data provided in step (a) includes at least one of semiconductor die height, die pad locations of a semiconductor die, lead locations of a leadframe, relative distances between first bonding locations and second bonding locations, a wire diameter, and a wire type.

21. The method of claim 1 wherein the wire loop is formed using a ball bonding process on a ball bonding machine.

22. The method of claim 1 wherein the wire loop is formed using a wedge bonding process on a wedge bonding machine.

23. The method of claim 1 wherein the wire loop is formed using a ribbon bonding process on a ribbon bonding machine.

Description

CROSS REFERENCE TO RELATED APPLICATION

[0001] This application is a continuation of U.S. patent application Ser. No. 16/401,511 filed on May 2, 2019, which is a continuation of U.S. patent application Ser. No. 15/623,978 filed on Jun. 15, 2017, now U.S. Pat. No. 10,325,878 granted on Jun. 18, 2018, which claims the benefit of U.S. Provisional Application No. 62/357,006, filed Jun. 30, 2016, the content of each of which is incorporated herein by reference.

FIELD

[0002] The invention relates to the formation of wire loops, and more particularly, to improved methods of generating wire loop profiles for wire loops in a semiconductor package.

BACKGROUND

[0003] In the processing and packaging of semiconductor devices, wire bonding continues to be a primary method of providing electrical interconnection between two locations within a package (e.g., between a die pad of a semiconductor die and a lead of a leadframe). More specifically, using a wire bonder (also known as a wire bonding machine) wire loops are formed between respective locations to be electrically interconnected. For example, wire loops may be formed using a ball bonding machine, a wedge bonding machine, a ribbon bonding machine, etc. Exemplary wire loops formed on a ball bonding machine include (i) a ball bond bonded to a first bonding location (e.g., a die pad of a semiconductor die), (ii) a stitch bond bonded to a second bonding location (e.g., a lead of a leadframe), and (iii) a length of wire between the ball bond and the stitch bond. Exemplary patent documents related to the wire bonding industry include: U.S. Pat. Nos. 8,302,840; 9,496,240; and U.S. Patent Application Publication No. 2001/0072406--wherein each of these patent documents is incorporated by reference in its entirety.

[0004] In packages having a high number of wire loops (e.g., high pin-count wire bond applications) wire loops may be overlapping in space (e.g., crisscrossing one another in three dimensional space). The process of on-bonder looping optimization is laborious, and often involves a time period of weeks or months. Further, after the looping optimization is complete, there is no guarantee that all of the wire loops intended to be included in a given package are truly possible. The uncertainty around the feasibility of wire looping forces package designers to consider alternate packaging techniques (other than wire bonding).

[0005] Thus, it would be desirable to provide improved methods of generating loop profiles for wire loops in a semiconductor package.

SUMMARY

[0006] According to an exemplary embodiment of the invention, a method of generating a wire loop profile in connection with a semiconductor package is provided. The method includes the steps of: (a) providing package data related to the semiconductor package; and (b) creating a loop profile of a wire loop of the semiconductor package, the loop profile including a tolerance band along at least a portion of a length of the wire loop.

[0007] The methods of the invention may also be embodied as an apparatus (e.g., as part of the intelligence of a wire bonding machine), or as computer program instructions on a computer readable carrier (e.g., a computer readable carrier used in connection with a wire bonding machine).

BRIEF DESCRIPTION OF THE DRAWINGS

[0008] The invention is best understood from the following detailed description when read in connection with the accompanying drawings. It is emphasized that, according to common practice, the various features of the drawings are not to scale. On the contrary, the dimensions of the various features are arbitrarily expanded or reduced for clarity. Included in the drawings are the following figures:

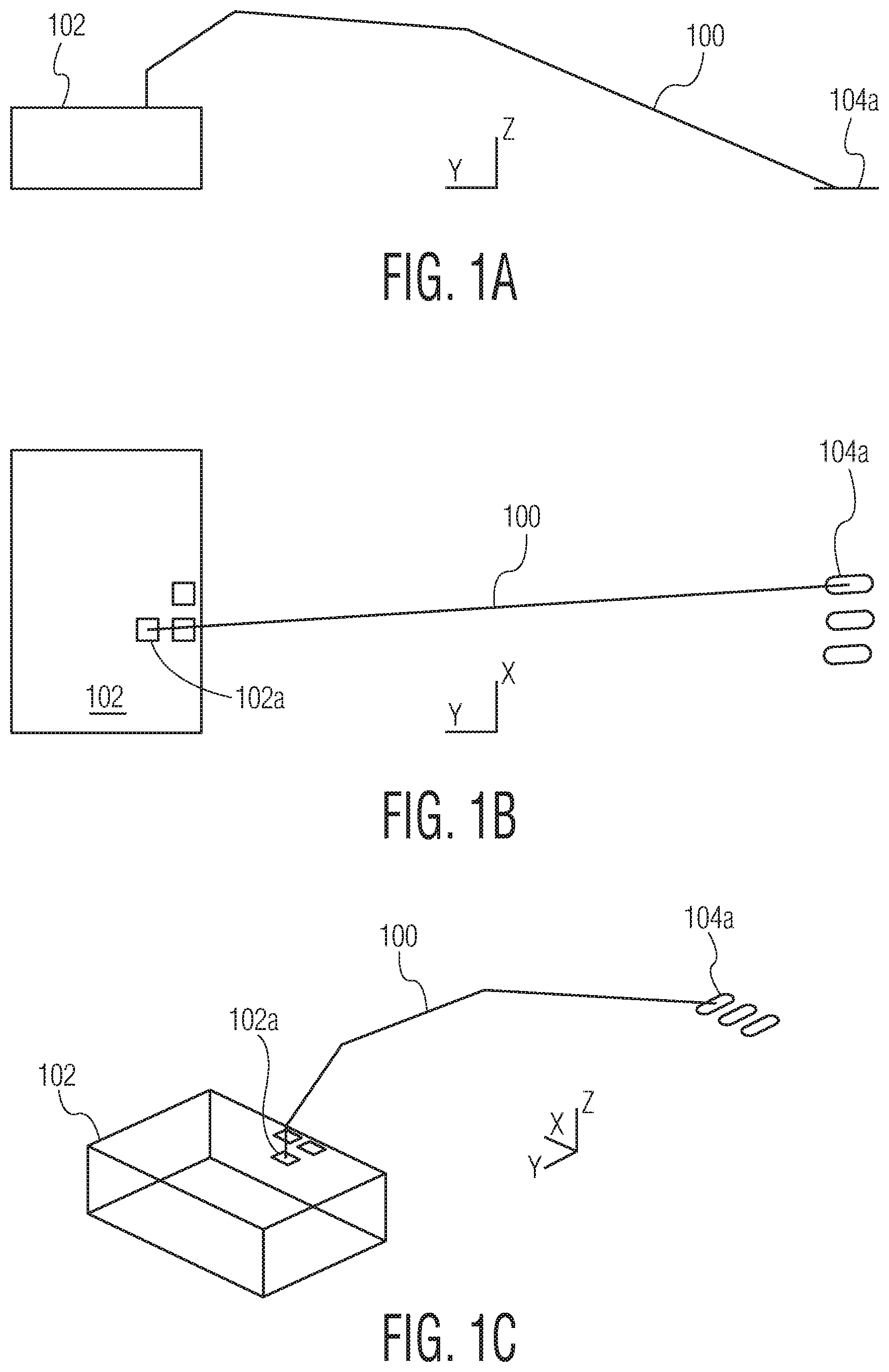

[0009] FIG. 1A is a side view of a wire loop useful for explaining certain exemplary embodiments of the invention;

[0010] FIG. 1B is a top view of the wire loop of FIG. 1A;

[0011] FIG. 1C is a perspective view of the wire loop of FIG. 1A;

[0012] FIG. 2A is a side view of a wire loop including a tolerance band in accordance with an exemplary embodiment of the invention;

[0013] FIG. 2B is a top view of the wire loop of FIG. 2A;

[0014] FIG. 2C is a perspective view of the wire loop of FIG. 2A;

[0015] FIG. 3A is a side view of the wire loop of FIG. 2A with a different tolerance band in accordance with an exemplary embodiment of the invention;

[0016] FIG. 3B is a top view of the wire loop of FIG. 3A;

[0017] FIG. 3C is a perspective view of the wire loop of FIG. 3A;

[0018] FIG. 4A is a side view of two wire loops useful for explaining certain exemplary embodiments of the invention;

[0019] FIG. 4B is a top view of the wire loops of FIG. 4A;

[0020] FIG. 4C is a perspective view of the wire loops of FIG. 4A;

[0021] FIG. 5A is a side view of the two wire loops of FIG. 4A including tolerance bands in accordance with an exemplary embodiment of the invention;

[0022] FIG. 5B is a top view of FIG. 5A;

[0023] FIG. 5C is a perspective view of FIG. 5A;

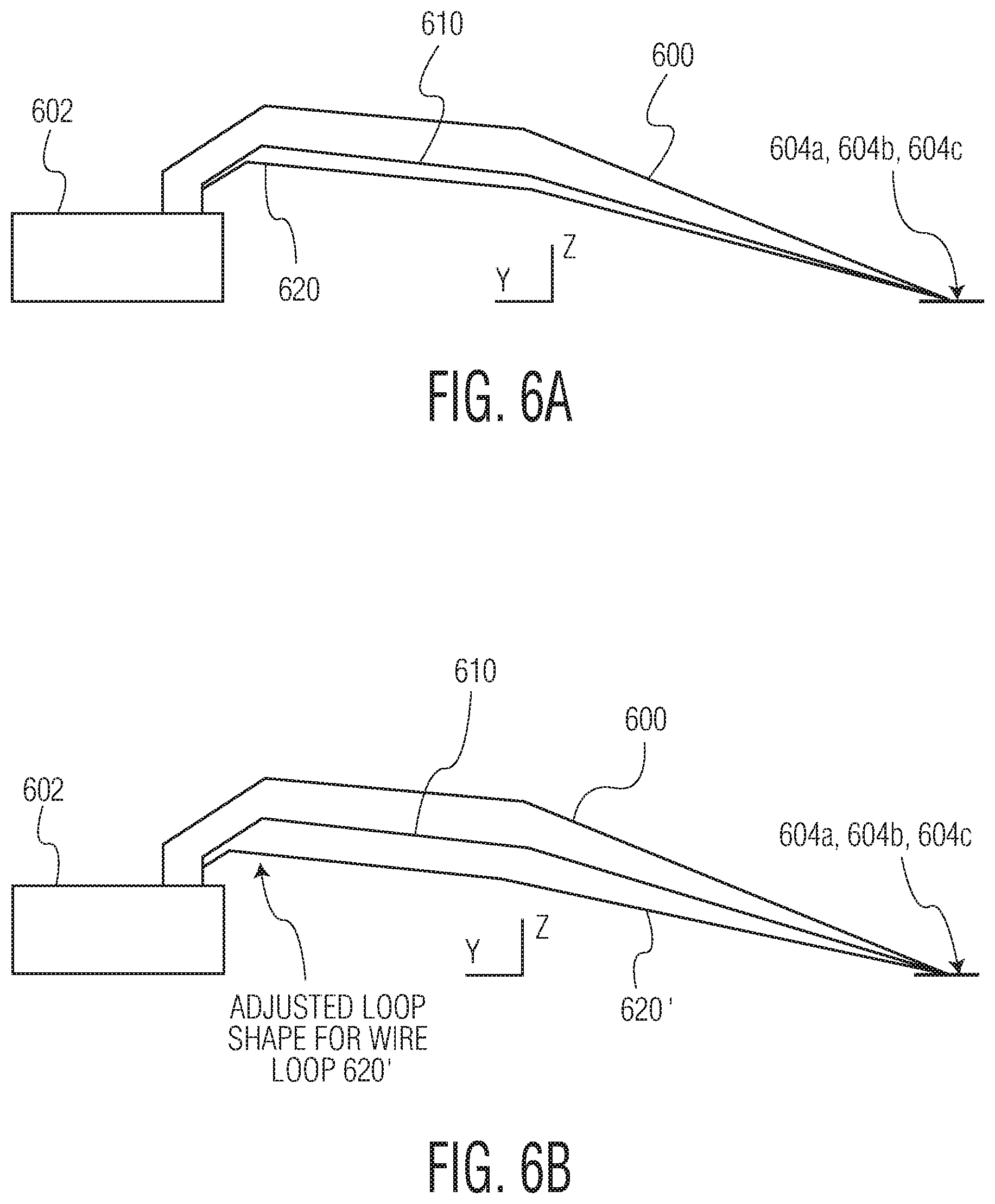

[0024] FIG. 6A is a side view of three wire loops, where there is interference between two of the wire loops, useful for explaining certain exemplary embodiments of the invention;

[0025] FIG. 6B is a side view of the three wire loops of FIG. 6A, with a loop profile of one of the wire loops having been adjusted, in accordance with an exemplary embodiment of the invention;

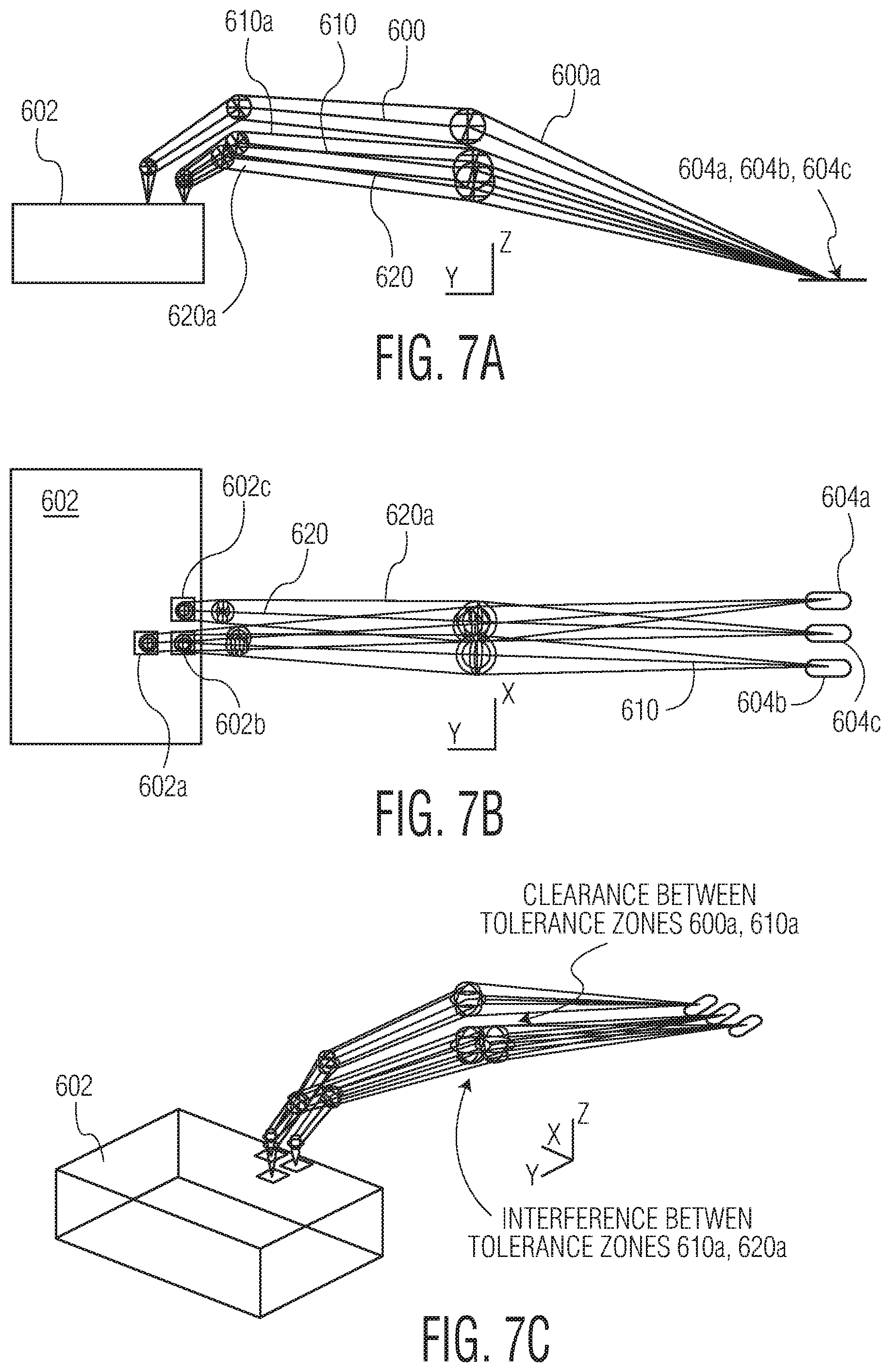

[0026] FIG. 7A is a side view of the three wire loops of FIG. 6A including tolerance bands in accordance with an exemplary embodiment of the invention;

[0027] FIG. 7B is a top view of FIG. 7A;

[0028] FIG. 7C is a perspective view of FIG. 7A;

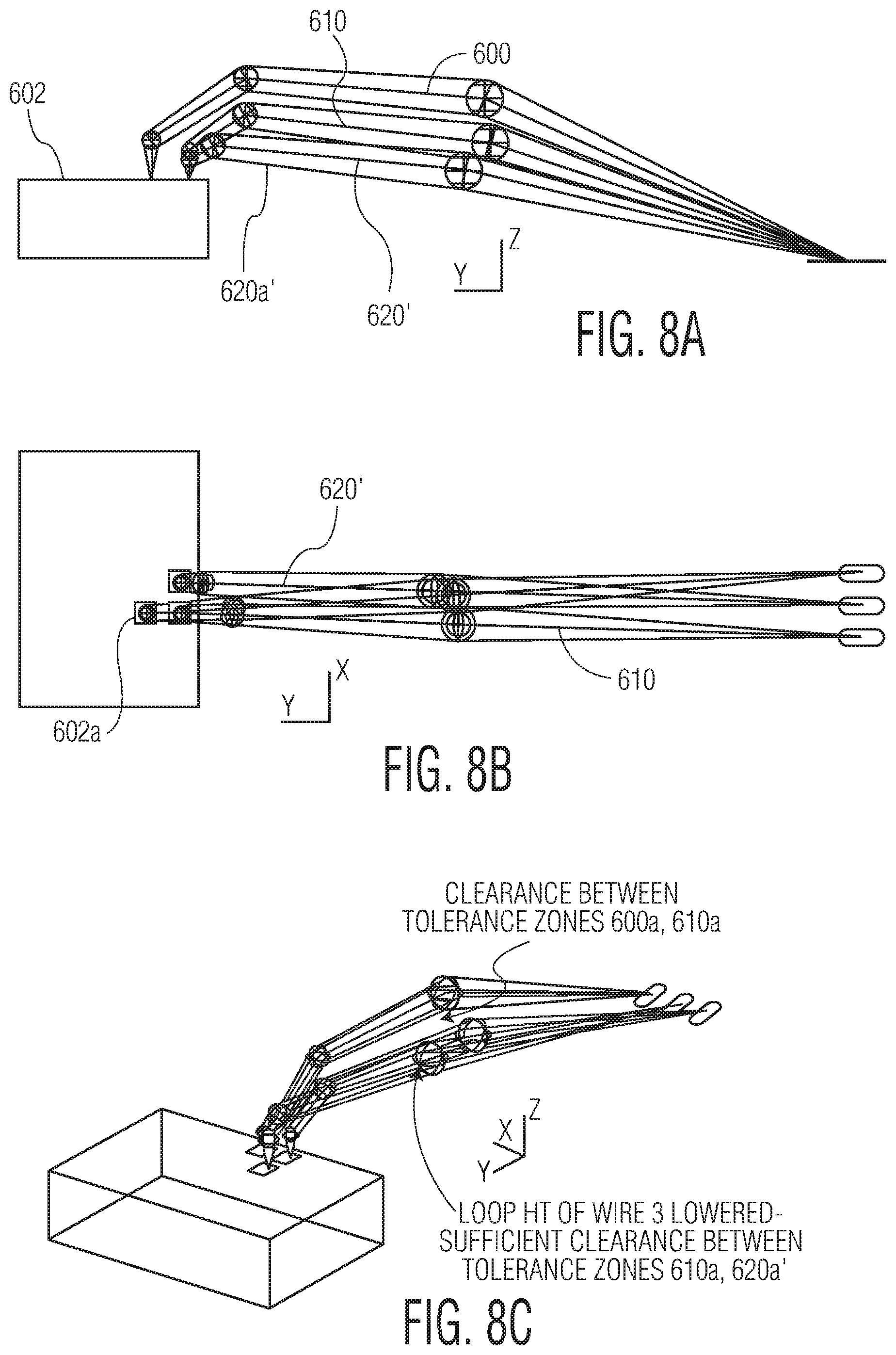

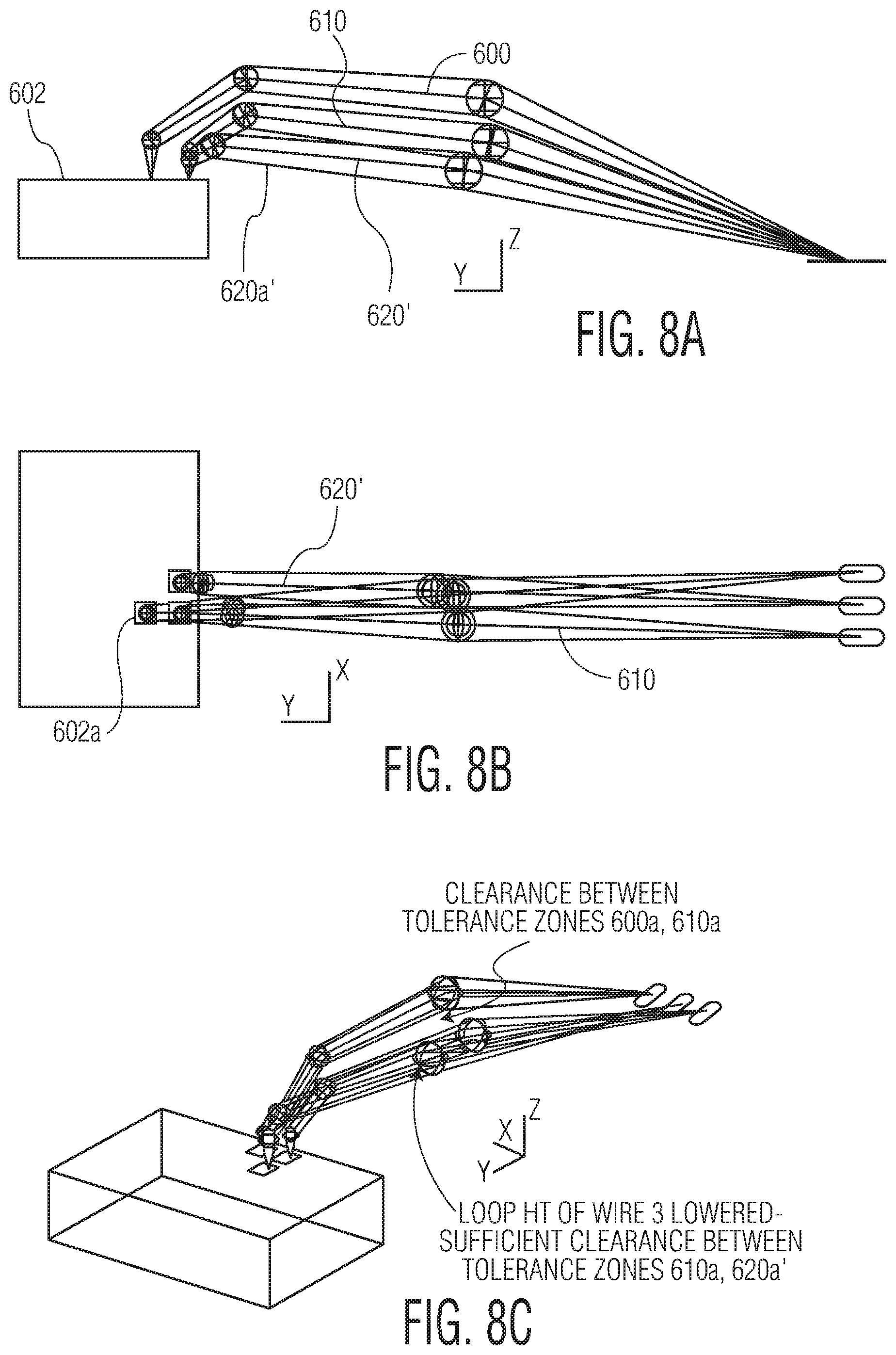

[0029] FIG. 8A is a side view of the three wire loops of FIG. 7A, with a loop profile of one of the wire loops having been adjusted, in accordance with an exemplary embodiment of the invention;

[0030] FIG. 8B is a top view of FIG. 8A;

[0031] FIG. 8C is a perspective view of FIG. 8A; and

[0032] FIG. 9 is a flow diagram illustrating a method of generating a wire loop profile in connection with a semiconductor package, in accordance with an exemplary embodiment of the invention.

DETAILED DESCRIPTION

[0033] As used herein, the terms "loop profile" or "wire loop profile" refer to specifications of a wire loop shape between a first bonding location (e.g., the location of a ball bond of a wire loop) and a second bonding location (e.g., the location of a stitch bond of the wire loop). The loop profiles are often specified by the user of the wire bonding machine, and include the desired specifications of a given wire loop. For example, the loop profile specifications typically include (i) the number of bends and/or kinks to be included in the wire loop, and (ii) the locations of the bends/kinks in space (e.g., the xyz coordinates with respect to at least one of the first bond location and the second bond location). Since the maximum loop height often occurs at a bend/kink of a wire loop, the loop profile may also include a maximum loop height of the resultant wire loop. Often the terms "loop shape" or "wire loop shape" are used synonymously with "loop profile" or "wire loop profile". In accordance with certain aspects of the invention, the loop profile shall also include a tolerance band provided around (or about) at least a portion of a wire loop.

[0034] As used herein, the terms "tolerance band" or "clearance zone" refers to an area (e.g., a 3D zone) around (or about) a given wire loop profile. According to exemplary aspects of the invention, adjacent tolerance bands desirably do not overlap with one another, or if they do, they may overlap within a predetermined specification. Of course, it is an option within the scope of the invention that adjacent tolerance bands may overlap. Further, the tolerance band also applies to other obstructions such as a portion of a die (e.g., a die edge), an adjacent component (e.g., a surface mounted component), etc. That is, according to exemplary aspects of the invention, tolerance bands desirably do not overlap with the location of such obstructions.

[0035] In accordance with certain exemplary embodiments of the invention, methods of optimizing wire loop profiles (e.g., wire loop shapes) are provided, including three-dimensional wire loop optimization. The methods may include generating a loop profile for each wire loop in the semiconductor package in 3D. Wire loops often lean and sway when bonded on a wire bonder. Aspects of the invention consider potential defects (e.g., wire lean, wire sway, etc.) of wire loops based on their physical characteristics and establishes a tolerance band (e.g., also referred to as a tolerance zone, a clearance zone, a collision zone, etc.) around each wire. Such tolerance bands may be formed to include, frustums, ellipsoids. Furthermore, methods to perform a clearance/interference check between such tolerance bands allows for a robust loop shape design, and a significant time reduction in looping optimization time.

[0036] In order to perform such clearance/interference checks, algorithms (e.g., algorithms run on a computer on the wire bonder, or algorithms run on a computer off the wire bonder, etc.) may utilize wire loop shapes, kink positions, wire spans, wire lengths, wire bond locations, etc. After confirming acceptable wire loop profiles (including acceptable tolerance bands), additional processes (including other algorithms) may be used to determine (e.g., automatically determine using one or more algorithms operating on a computer of the wire bonding machine, or another computer, etc.) the order in which to form wire loops included in a semiconductor package.

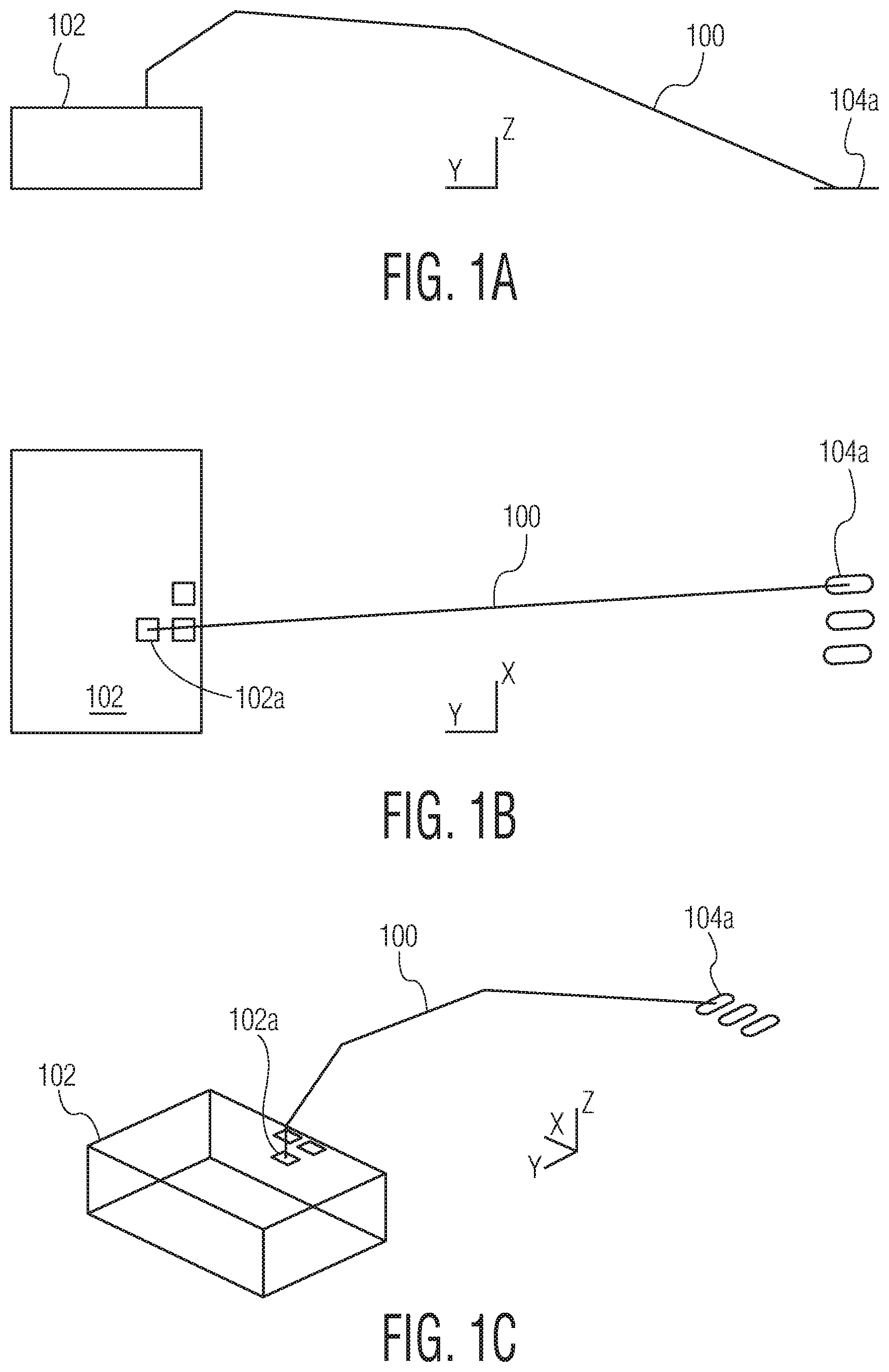

[0037] Referring now to the drawings, FIG. 1A illustrates a wire loop 100 extending between a semiconductor die 102 and a lead 104a of a leadframe. As can be seen in FIG. 1A, wire loop 100 has a loop profile (e.g., a loop shape), for example, including various kinks, bends, and wire spans. FIG. 1B illustrates wire loop 100 connected to die pad 102a (of semiconductor die 102) on a first end of wire loop 100, and connected to lead 104a on a second end of wire loop 100. FIG. 1C illustrates a perspective view of wire loop 100.

[0038] In accordance with certain exemplary embodiments of the invention, tolerance bands are included in wire loop profiles. FIGS. 2A-2C illustrate an example of such a loop profile. More specifically, the loop profile of wire loop 100 shown in FIG. 2A includes tolerance band 100a. Tolerance band 100a includes a plurality of sections including section 100a1, section 100a2, section 100a3, and section 100a4. Between the various sections of tolerance band 100a are shapes such as spheres, ellipsoids, etc. In the example shown in FIGS. 2A-2C, the tolerance band has a circular shape that has a uniform diameter along its length. However, it should be understood that tolerance bands included in loop profiles in accordance with the invention may vary significantly. For example, such tolerance bands may have a non-circular shape (e.g., an eliptical or other shape), and such tolerance bands may have a diameter (or other measurable quantity) that varies along the length of the wire loop.

[0039] FIGS. 3A-3C illustrates a different tolerance band 200a in connection with wire loop 100 as compared with tolerance band 100a shown in FIGS. 2A-2C. As shown in FIGS. 3A-3C tolerance band 200a includes section 200a1, section 200a2, section 200a3, and section 200a4. As further shown in FIGS. 3A-3C, each of sections 200a1, 200a2, 200a3, and 200a4 have shapes that vary along their respective length. For example, referring specifically to section 200a1, the size of the tolerance band increases as the wire extends above away from the first bond location on semiconductor die 102.

[0040] In accordance with the invention, loop profiles including tolerance bands are particularly useful in applications having a plurality of wire loops in a semiconductor package (e.g., where one or more of the wire loops may overlap or criss-cross others of the wire loops). FIGS. 4A-4C illustrate two wire loops 400 and 410 extending between a semiconductor die 402 and leads 404a, 404b of a leadframe. More specifically, wire loop 400 extends between die pad 402a and lead 404a. Likewise, wire loop 410 extends between die pad 402b and lead 404b.

[0041] FIGS. 5A-5C illustrate loop profiles of wire loops 400 and 410 including tolerance bands. More specifically, wire loop 400 includes tolerance band 400a (where tolerance band 400a includes sections as described above in connection with other tolerance bands), and wire loop 410 includes tolerance band 410a (where tolerance band 410a includes sections as described above). As shown in FIG. 5C, adequate clearance exists between tolerance band 400a and 410a.

[0042] In order to determine if there is adequate clearance between adjacent tolerance bands of wire loops, an algorithm (or the like) may be used to check if the adjacent tolerance bands meet predetermined criteria such as an acceptable level of clearance between the adjacent tolerance bands. Such an algorithm may rely on pre-existing data (e.g., in data structures, databases, look-up tables, etc.) in the determination of an acceptable amount of clearance in the given application. If the check indicates that the predetermined criteria is not met (e.g., there is not an acceptable level of clearance between at least a portion of the loop profiles including tolerance bands), one or more of the loop profiles may be adjusted. After the adjustment, another check may be performed to determine if the predetermined criteria is met.

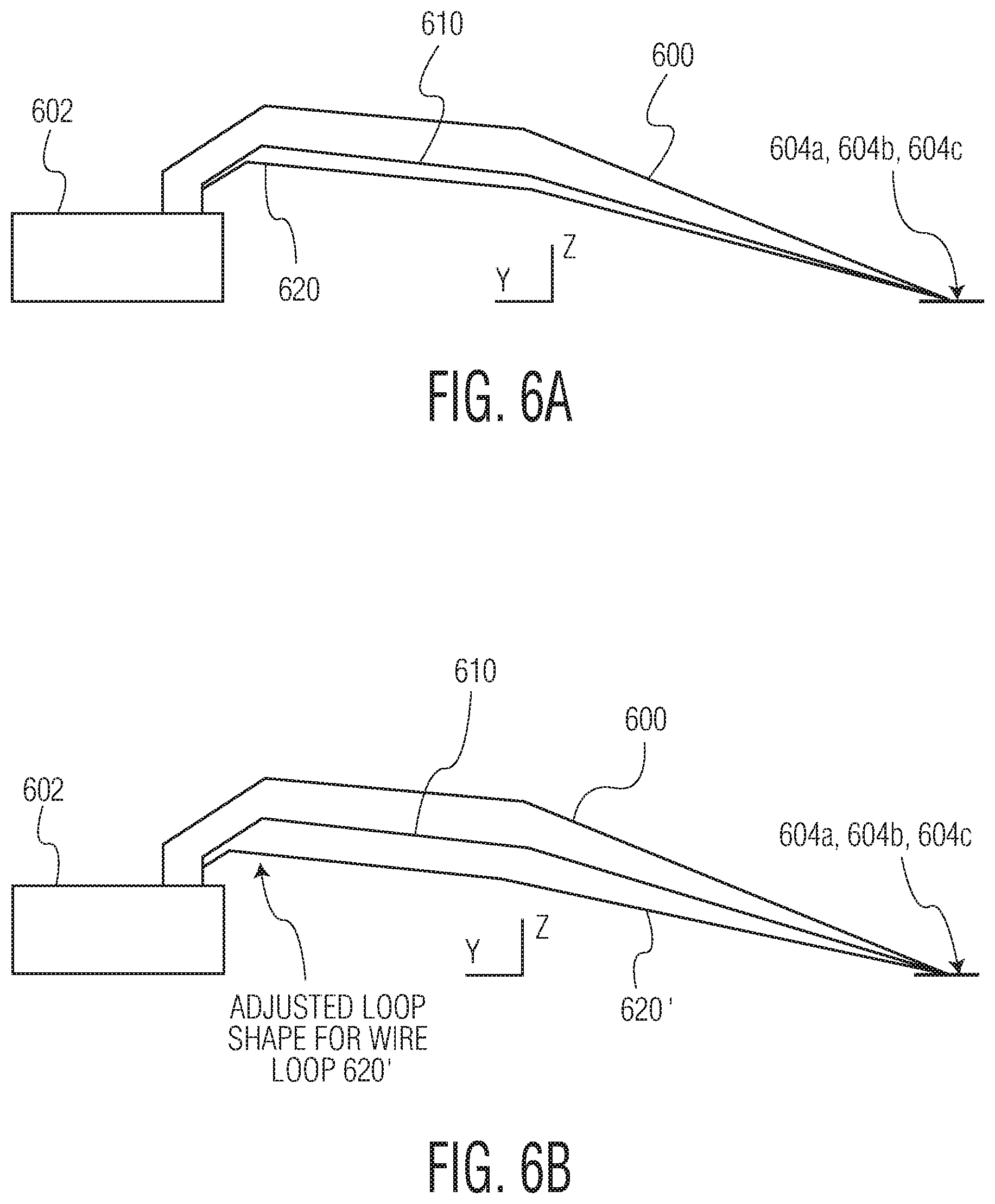

[0043] FIG. 6A illustrates three wire loops 600, 610, and 620, extending between a semiconductor die 602 and a leads 604a, 604b, 604c of a lead frame. More specifically, wire loop 600 extends between a die pad of semiconductor die 602 (not shown) and lead 604a. Likewise wire loop 610 extends between a die pad of semiconductor die 602 (not shown) and lead 604b. Likewise, wire loop 620 extends between a die pad of semiconductor 602 (not shown) and lead 604c. To illustrate an aspect of the invention, let us assume that the "check" determines that the predetermined criteria is not met for adjacent wire loops 610 and 620. More specifically, let us assume that there is not adaquate clearance between the tolerance zones of wire loop 610 and wire loop 620. In the example shown in FIG. 6B the loop profile (e.g., the loop shape) of wire loop 620 (now referred to as wire loop 620') has been changed to provide adequate clearance. Specifically, a kink position of wire loop 620 is changed to derive wire loop 620'. This process is detailed in connection with FIGS. 7A-7C and FIGS. 8A-8C.

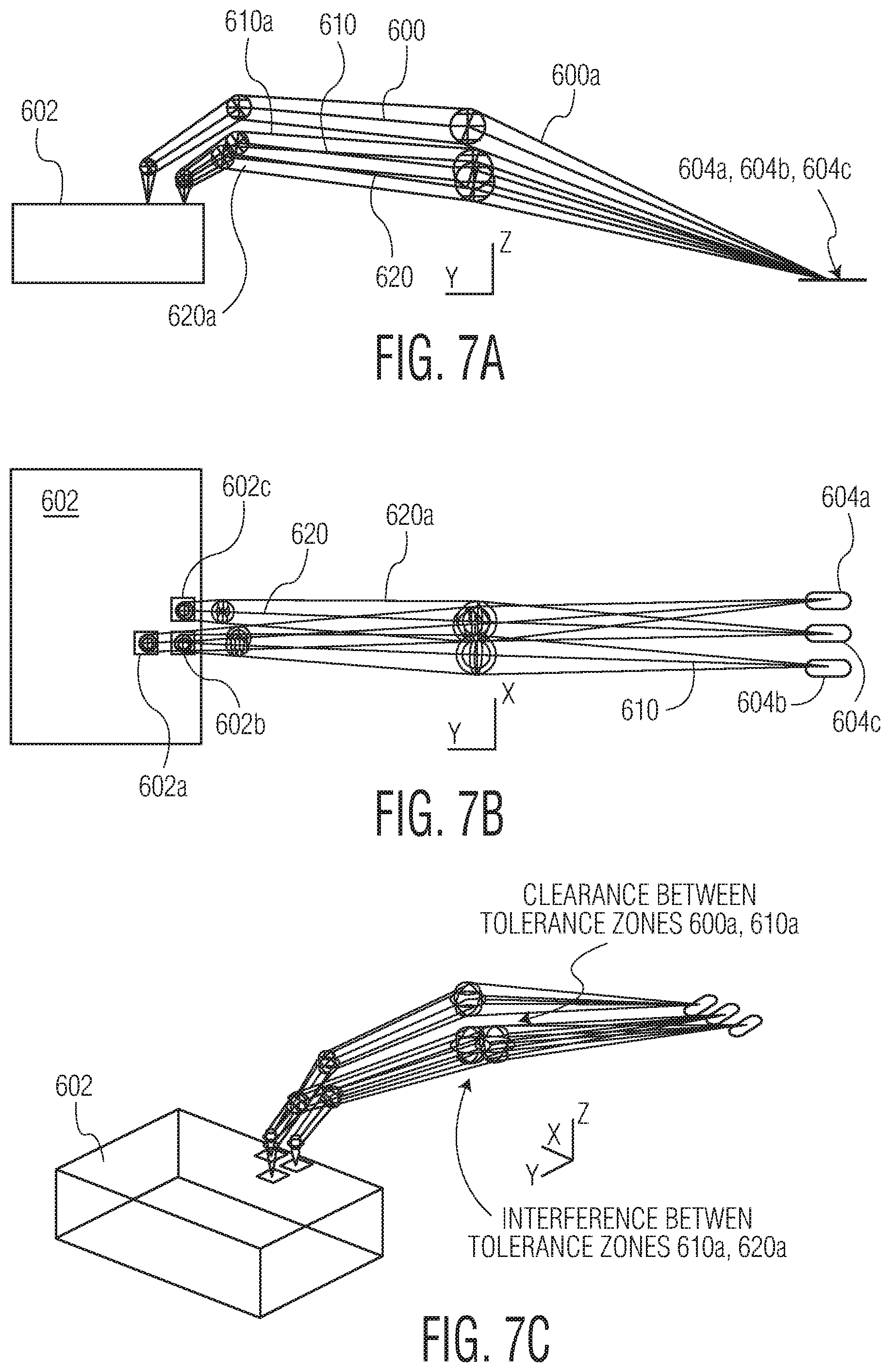

[0044] Referring specifically to FIGS. 7A-7C, each of wire loops 600, 610, and 620 include respective tolerance bands 600a, 610a, and 620a. As shown in FIG. 7C there is not adequate clearance between tolerance bands 610a and 620a. Referring specifically to FIGS. 8A-8C, where the loop profile of wire loop 620 has been changed (as described above in connection with FIG. 6B, where the wire loop is now labelled as 620') adequate clearance is now provided between tolerance band 610a and 620a'.

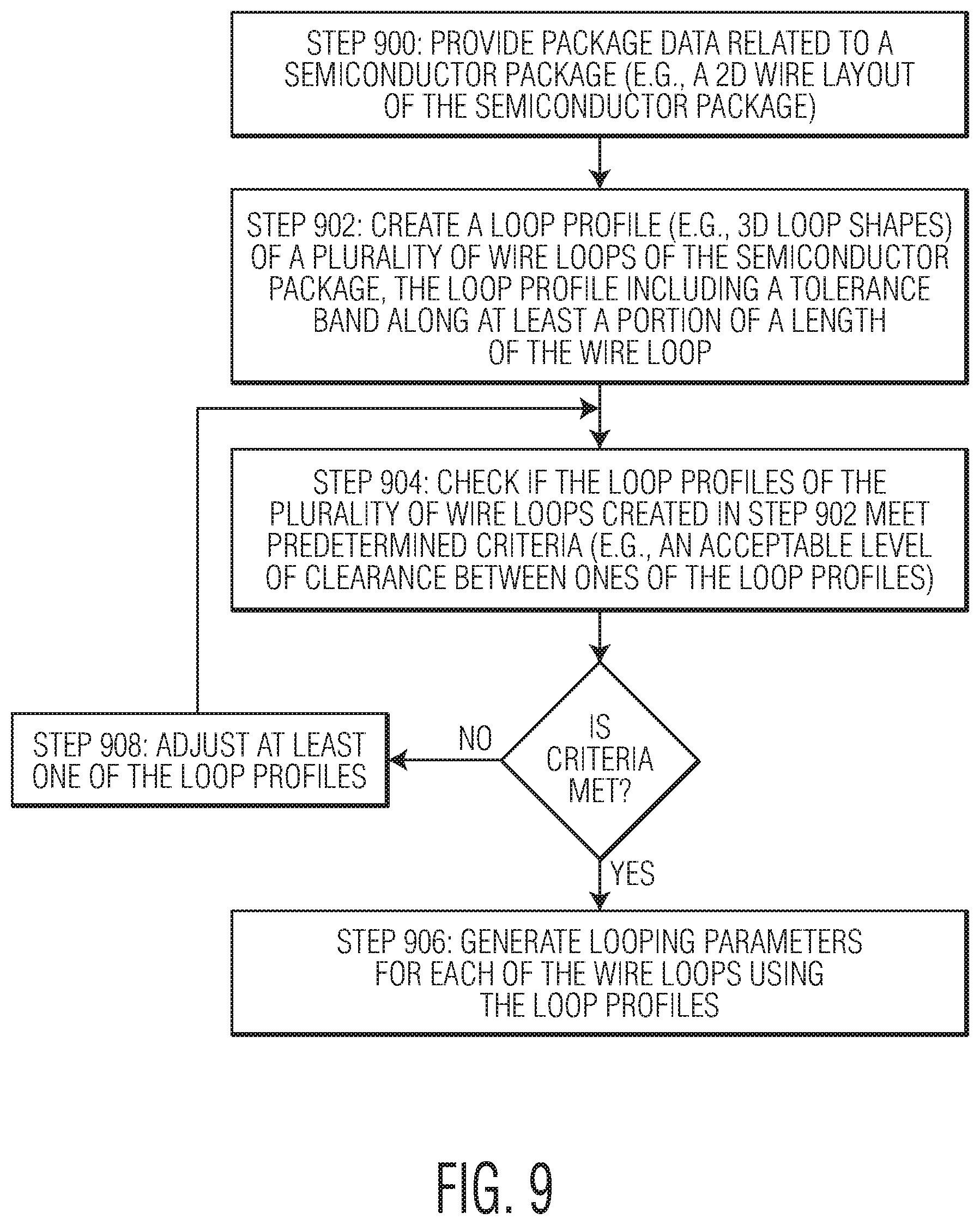

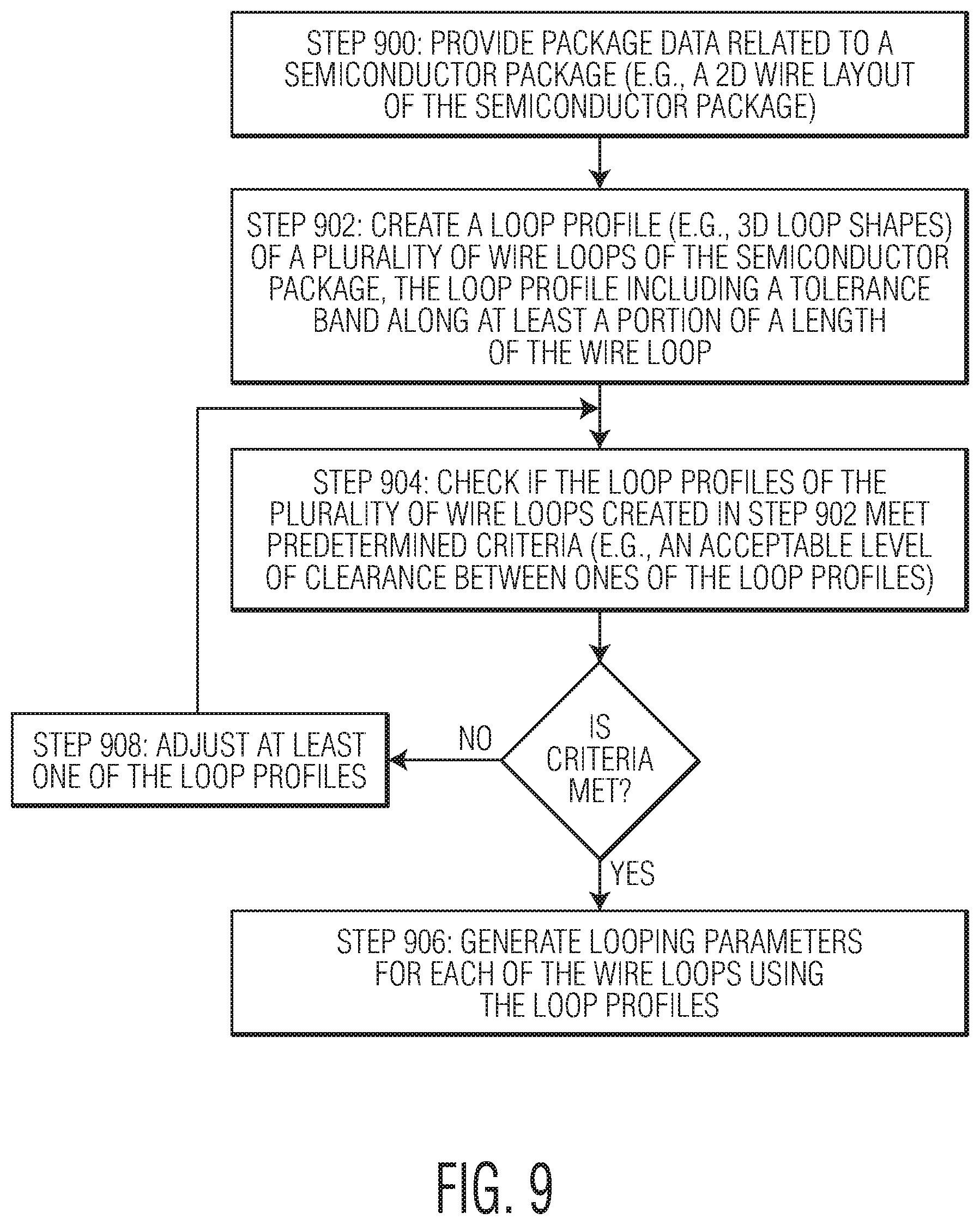

[0045] FIG. 9 is a flow diagram in accordance with certain exemplary embodiments of the invention. As is understood by those skilled in the art, certain steps included in the flow diagram may be omitted; certain additional steps may be added; and the order of the steps may be altered from the order illustrated.

[0046] FIG. 9 illustrates a method of generating a wire loop profile in connection with a semiconductor package. At Step 900, package data (e.g., a two-dimensional wire layout of the semiconductor package) is provided related to the semiconductor package. Such package data may be provided to the wire bonding machine using computer data about the package (e.g., CAD data related to the semiconductor package). In another example, the package data may be provided using an online (e.g., on bonder) teaching reference system of the wire bonding machine. Specific pieces of package data will of course vary from application to application; however, examples of the type of data that may be provided to the wire bonding machine (or offline from the wire bonding machine, for example, to an offline computer system) as package data includes semiconductor die height, die pad locations of a semiconductor die, lead locations of a leadframe, relative distances between first bonding locations and second bonding locations, wire diameter, and wire type.

[0047] At Step 902, a loop profile of each wire loop of the semiconductor package is created. The loop profile (e.g., a wire loop shape) includes a tolerance band along at least a portion of a length of the wire loop. At Step 904, a check is performed to determine if the loop profiles of the plurality of wire loops created at Step 902 meet predetermined criteria (e.g., where such predetermined criteria may include an acceptable level of clearance between ones of the loop profiles).

[0048] If the predetermined criteria is met (as determined during the check at Step 904), looping parameters are generated for each of the wire loops using the loop profiles at Step 906. If the predetermined criteria is not met (as determined during the check at Step 904), at least one of the loop profiles is adjusted at Step 908 (e.g., see adjustment to loop profile illustrated and described in connection with FIG. 6B and FIGS. 7A-7C). After Step 908, the check is repeated at Step 904 with the adjusted loop profile(s). The process may be repeated until the predetermined criteria is met at Step 906. Alternatively, after a predetermined number of cycles (or time, or other criteria) the process may be abandoned, and the semiconductor device may be considered inappropriate for wire bonding. In yet another alternative, a user may be able to override (e.g., manually or automatically) the predetermined criteria not being met.

[0049] In accordance with certain exemplary embodiments of the invention, looping parameters (and therefore, a looping trajectory) are defined using an algorithm(s) running on a computer (e.g., a computer on or off the wire bonding machine). Exemplary looping parameters include: (a) a tool trajectory for forming the wire loop including the end point locations for each segment of the motion and the trajectory between the end points; (b) bonding energy parameters to be applied by a transducer of the wire bonding machine, (c) bonding force parameters to be applied by the wire bonding machine, (d) timing parameters related to at least one of the bonding energy and bonding force, (e) bonding tool speed during at least a portion of a wire bonding cycle to form the desired wire loop, and (f) a wire clamp position during at least a portion of a wire bonding cycle to form the desired wire loop.

[0050] In connection with the derivation of the looping parameters, the algorithm may utilize loop model data stored in the wire bonding machine (or stored in another location) to more closely approximate the looping parameters related to the desired wire loop. For example, through experimentation and testing, desirable looping parameters for various types of wire loops, using various wire types may be derived and stored in memory of the wire bonding machine (e.g., through look-up tables or the like) or accessible to the wire bonding machine (through computer networking or the like).

[0051] In accordance with the invention, a significant reduction in loop optimization time may be provided. Further, a robust loop shape design may be provided while considering neighboring wire loop shapes. Further still, uncertainty around the feasibility of looping in advanced high pin count applications for package designers may be avoided.

[0052] Although the invention is illustrated and described herein with reference to specific embodiments, the invention is not intended to be limited to the details shown. Rather, various modifications may be made in the details within the scope and range of equivalents of the claims and without departing from the invention.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

D00009

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.