Semiconductor Devices And Methods Of Fabricating The Same

DO; JUNG-HO ; et al.

U.S. patent application number 16/725155 was filed with the patent office on 2020-05-14 for semiconductor devices and methods of fabricating the same. The applicant listed for this patent is SAMSUNG ELECTRONICS CO., LTD.. Invention is credited to SANGHOON BAEK, JUNG-HO DO, JONGHOON JUNG, SEUNGYOUNG LEE, JINYOUNG LIM, TAEJOONG SONG, GIYOUNG YANG.

| Application Number | 20200152640 16/725155 |

| Document ID | / |

| Family ID | 58721935 |

| Filed Date | 2020-05-14 |

View All Diagrams

| United States Patent Application | 20200152640 |

| Kind Code | A1 |

| DO; JUNG-HO ; et al. | May 14, 2020 |

SEMICONDUCTOR DEVICES AND METHODS OF FABRICATING THE SAME

Abstract

A semiconductor device including: a conductor disposed on a substrate; a first contact disposed on the conductor; a second contact having a first portion disposed on the first contact and a second portion protruded away from the first portion in a direction parallel to the substrate, wherein the first and second contacts are disposed in an insulating layer; a via disposed on the insulating layer and the second portion of the second contact; and a metal line disposed on the via.

| Inventors: | DO; JUNG-HO; (YONGIN-SI, KR) ; LEE; SEUNGYOUNG; (SEOUL, KR) ; JUNG; JONGHOON; (SEONGNAM-SI, KR) ; LIM; JINYOUNG; (SEOUL, KR) ; YANG; GIYOUNG; (SEOUL, KR) ; BAEK; SANGHOON; (SEOUL, KR) ; SONG; TAEJOONG; (SEONGNAM-SI, KR) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 58721935 | ||||||||||

| Appl. No.: | 16/725155 | ||||||||||

| Filed: | December 23, 2019 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 15355159 | Nov 18, 2016 | 10541243 | ||

| 16725155 | ||||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 27/1104 20130101; H01L 28/00 20130101; H01L 23/485 20130101; H01L 21/76895 20130101; H01L 23/5226 20130101 |

| International Class: | H01L 27/11 20060101 H01L027/11; H01L 23/522 20060101 H01L023/522; H01L 49/02 20060101 H01L049/02; H01L 21/768 20060101 H01L021/768 |

Foreign Application Data

| Date | Code | Application Number |

|---|---|---|

| Nov 19, 2015 | KR | 10-2015-0162668 |

| Nov 19, 2015 | KR | 10-2015-0162675 |

| Apr 20, 2016 | KR | 10-2016-0048379 |

| Jul 8, 2016 | KR | 10-2016-0086996 |

Claims

1. A semiconductor device, comprising: a first conductor disposed on a substrate; a first contact disposed on the first conductor; a second contact disposed on the substrate and spaced apart from the first conductor and the first contact; and a third contact directly disposed on the first and second contacts and connecting the first and second contacts to each other.

2. The semiconductor device of claim 1, wherein the first to third contacts are disposed in an insulating layer.

3. The semiconductor device of claim 1, wherein the first and second contacts are disposed in an insulating layer and the third contact is disposed on the insulating layer.

4. The semiconductor device of claim 1, further comprising: a via disposed on the third contact; and a metal line disposed on the via.

5. The semiconductor device of claim 4, wherein an upper surface of the third contact is coplanar with an upper surface of each of the first and second contacts.

6. The semiconductor device of claim 4, wherein a bottom surface of the third contact is coplanar with an upper surface of each of the first and second contacts.

7. The semiconductor device of claim 1, further comprising: a second conductor disposed on the substrate, wherein the second contact is disposed between the first and second conductors.

8. The semiconductor device of claim 1, wherein the first conductor is a gate electrode and the first to third contacts are conductive structures.

9. A semiconductor device, comprising: a first trench silicide disposed on a substrate; a first contact disposed on an upper surface of the first trench silicide, wherein the upper surface of the first trench silicide is wider than a lower surface of the first contact; a second trench silicide disposed on the substrate; a second contact disposed on the second trench silicide; and a third contact directly disposed on the first and second contacts and connecting the first and second contacts to each other.

10. The semiconductor device of claim 9, wherein the first to third contacts are disposed in an insulating layer.

11. A semiconductor device, comprising: a first contact disposed on a substrate and extending lengthwise in a first direction; a second contact disposed on the substrate and extending lengthwise in the first direction; a conductor disposed between the first and second contacts and extending lengthwise in the first direction; and a third contact disposed on the first and second contacts and extending lengthwise in a second direction crossing the first direction, wherein a first portion of the third contact protrudes beyond an edge of the first contact such that the first contact is disposed between the first portion and the conductor in the second direction.

12. The semiconductor device of claim 11, wherein a second portion of the third contact protrudes beyond an edge of the second contact such that the second contact is disposed between the second portion and the conductor in the second direction.

13. The semiconductor device of claim 11, wherein the width of the bottom surface of the third contact in the second direction is greater than the width from a leftmost edge of the first contact to a rightmost edge of the second contact in the second direction.

14. The semiconductor device of claim 11, wherein the first and second contacts are disposed in an insulating layer and the third contact is disposed on the insulating layer.

Description

CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application is a divisional of U.S. patent application Ser. No. 15/355,159, filed on Nov. 18, 2016, which claims priority under 35 U.S.C. .sctn. 119 to Korean Patent Application Nos. 10-2015-0162668, 10-2015-0162675, 10-2016-0048379 and 10-2016-0086996, filed on Nov. 19, 2015, Nov. 19, 2015, Apr. 20, 2016 and Jul. 8, 2016, respectively, in the Korean Intellectual Property Office, the disclosures of which are incorporated by reference herein in their entireties.

TECHNICAL FIELD

[0002] The present inventive concept relates to semiconductor devices and methods of fabricating the same, and more particularly, to semiconductor devices including field effect transistors and methods of fabricating the same.

DISCUSSION OF RELATED ART

[0003] Due to their small-sizes, multifunctional, and/or low-cost characteristics, semiconductor devices are ubiquitous in the electronic industry. Semiconductor devices may be a memory device for storing data, a logic device for processing data, or a hybrid device including both of memory and logic elements. To meet increased demand for electronic devices with fast speed and/or low power consumption, semiconductor devices with high reliability, high performance, and/or multiple functions are desired. To satisfy these technical requirements, the complexity and/or integration density of semiconductor devices are being increased.

SUMMARY

[0004] According to an exemplary embodiment of the present inventive concept, there is provided a semiconductor device including: a conductor disposed on a substrate; a first contact disposed on the conductor; a second contact having a first portion disposed on the first contact and a second portion protruded away from the first portion in a direction parallel to the substrate, wherein the first and second contacts are disposed in an insulating layer; a via disposed on the insulating layer and the second portion of the second contact; and a metal line disposed on the via.

[0005] According to an exemplary embodiment of the present inventive concept, there is provided a semiconductor device including: a dummy conductor disposed on a substrate; a first contact disposed on the dummy conductor; a trench silicide disposed on the substrate and spaced apart from the dummy conductor; a second contact disposed on the trench silicide; and a third contact directly disposed on the first and second contacts and connecting the first and second contacts to each other.

[0006] According to an exemplary embodiment of the present inventive concept, there is provided a semiconductor device including: a first conductor disposed on a substrate; a first contact disposed on the first conductor; a second contact disposed on the substrate and spaced apart from the first conductor and the first contact; and a third contact directly disposed on the first and second contacts and connecting the first and second contacts to each other.

[0007] According to an exemplary embodiment of the present inventive concept, there is provided a semiconductor device including: a first trench silicide disposed on a substrate; a first contact disposed on an upper surface of the first trench silicide, wherein the upper surface of the first trench silicide is wider than a lower surface of the first contact; a second trench silicide disposed on the substrate; a second contact disposed on the second trench silicide; and a third contact directly disposed on the first and second contacts and connecting the first and second contacts to each other.

[0008] According to an exemplary embodiment of the present inventive concept, there is provided a semiconductor device including: a first contact disposed on a substrate and extending lengthwise in a first direction; a second contact disposed on the substrate and extending lengthwise in the first direction; a conductor disposed between the first and second contacts and extending lengthwise in the first direction; and a third contact disposed on the first and second contacts and extending lengthwise in a second direction crossing the first direction, wherein a first portion of the third contact protrudes beyond an edge of the first contact such that the first contact is disposed between the first portion and the conductor in the second direction.

[0009] According to an exemplary embodiment of the present inventive concept, there is provided a semiconductor device including: a first conductor disposed on a substrate; a first contact disposed on the first conductor; a second conductor disposed on the substrate and spaced apart from the first conductor; a second contact disposed on the second conductor; and a third contact directly disposed on the first and second contacts and connecting the first and second contacts to each other.

BRIEF DESCRIPTION OF THE DRAWINGS

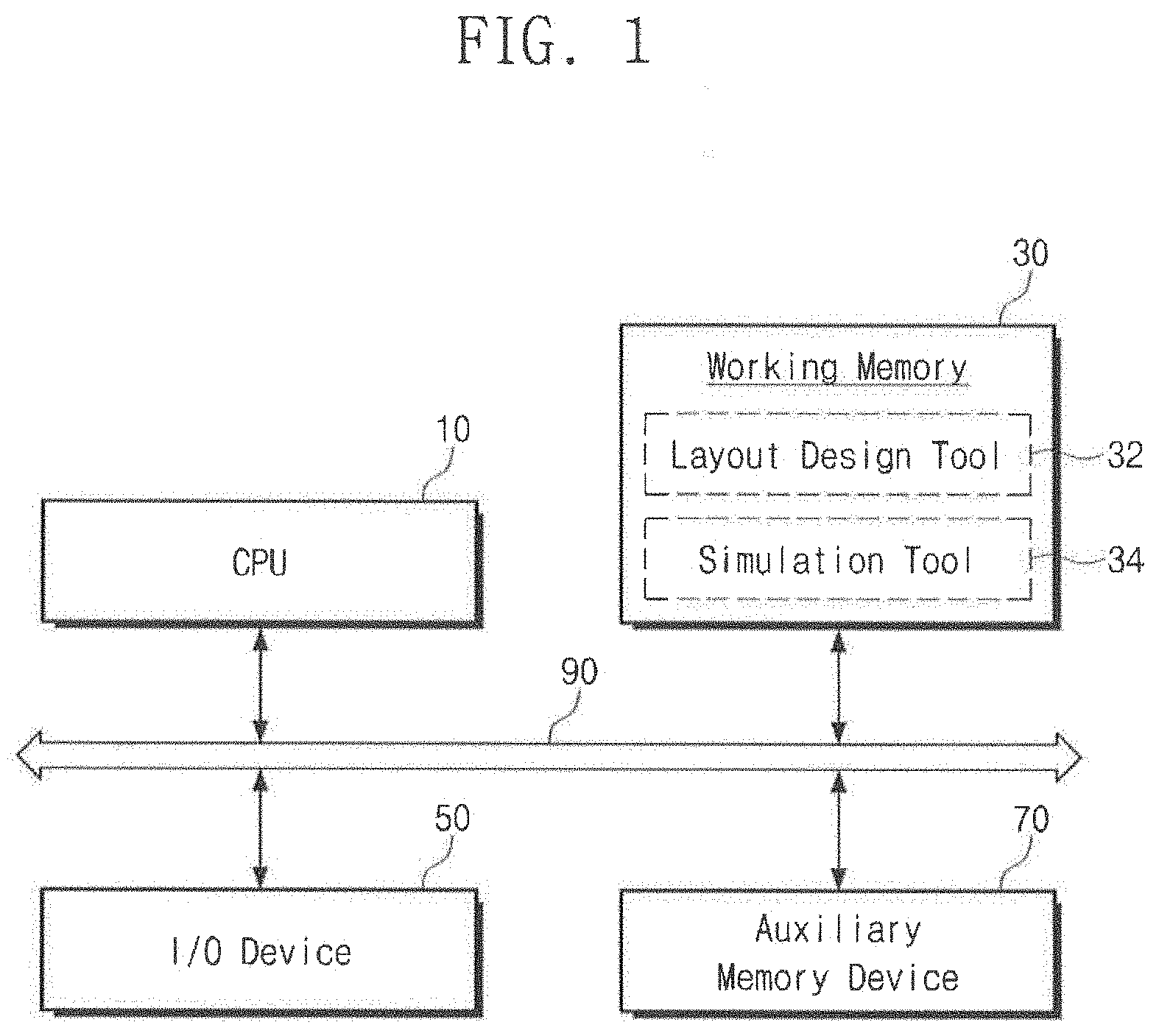

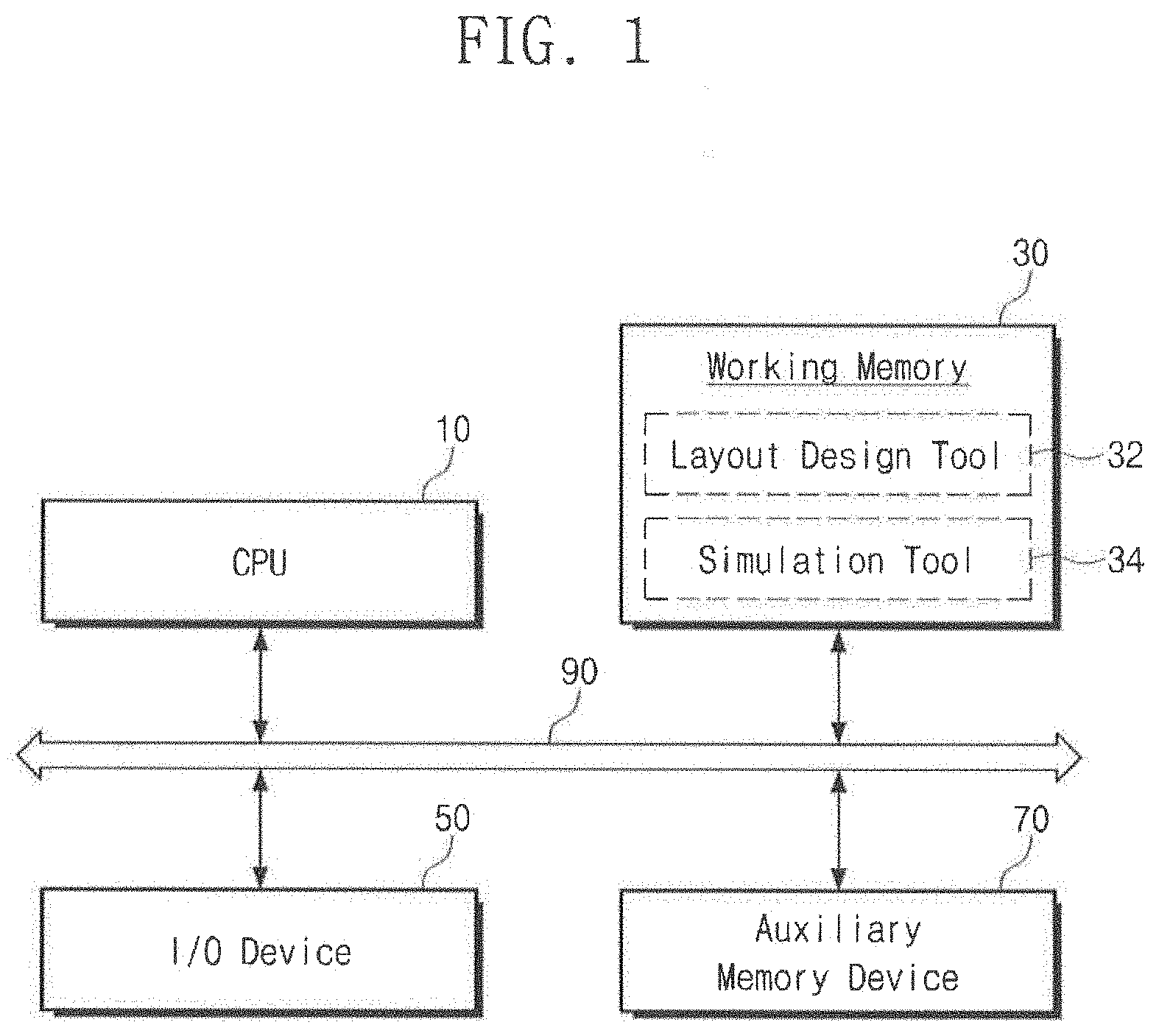

[0010] FIG. 1 is a block diagram illustrating a computer system for performing a semiconductor design process, according to exemplary embodiments of the present inventive concept.

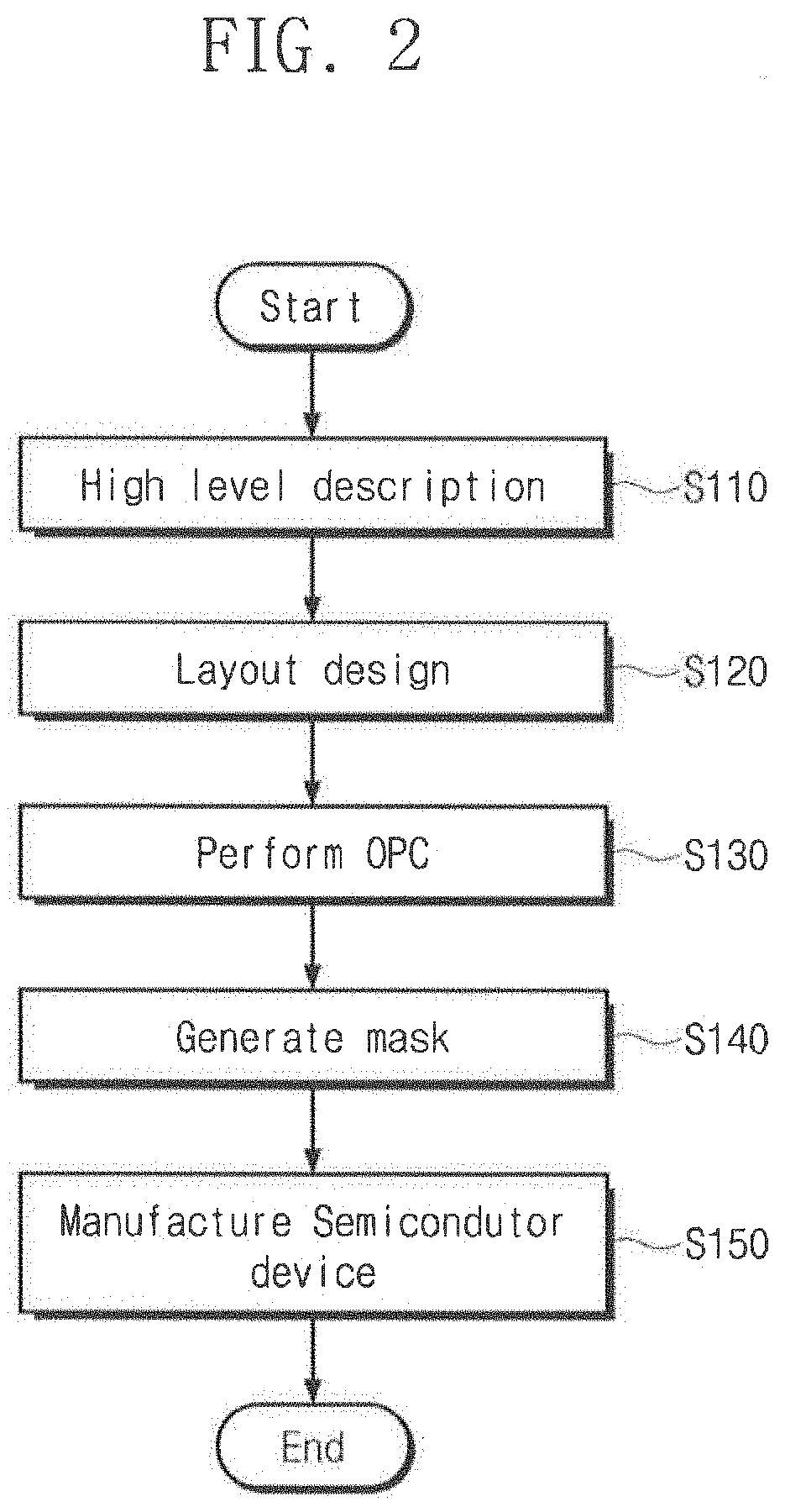

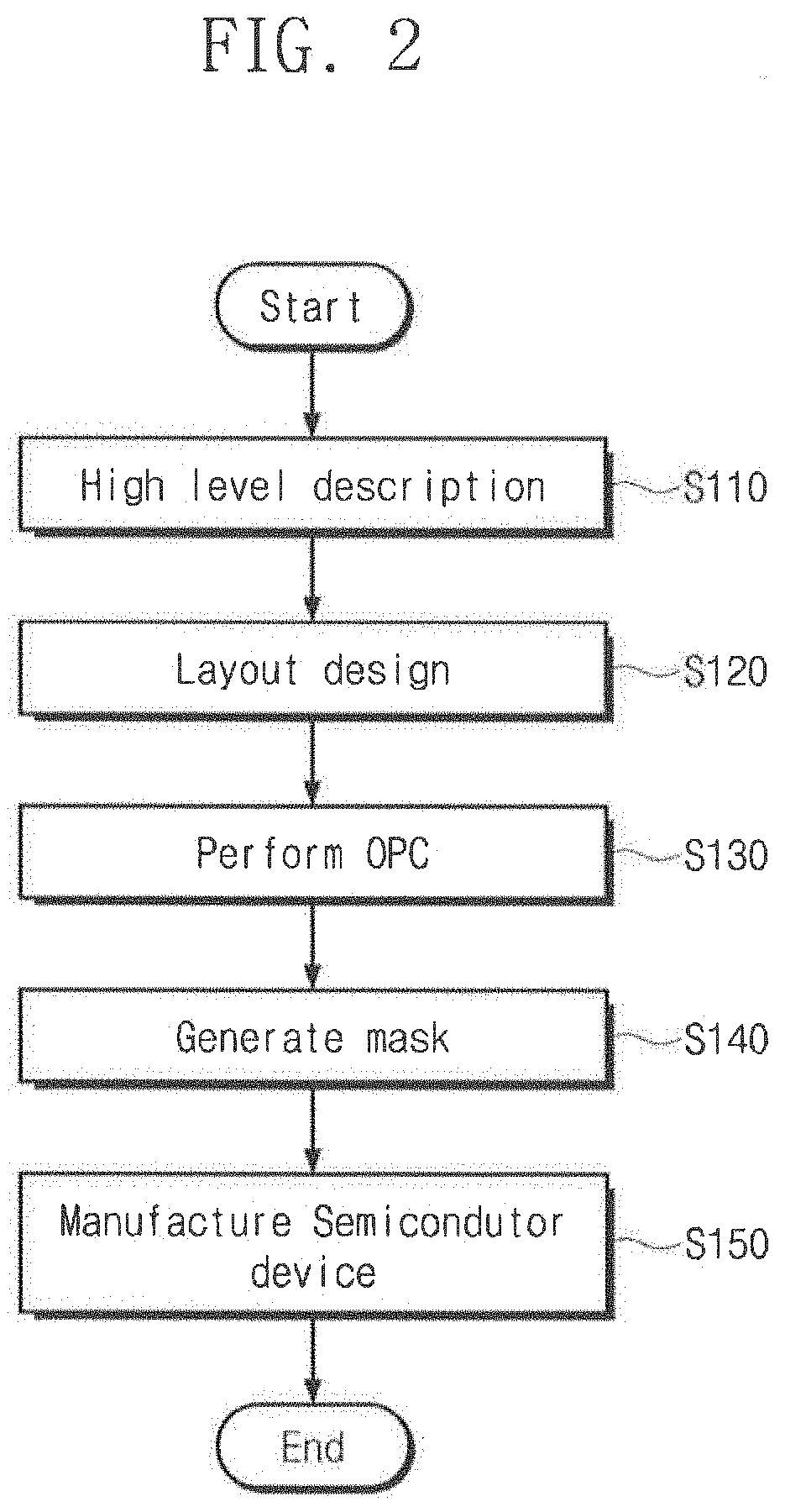

[0011] FIG. 2 is a flow chart illustrating a method of designing and fabricating a semiconductor device, according to exemplary embodiments of the present inventive concept.

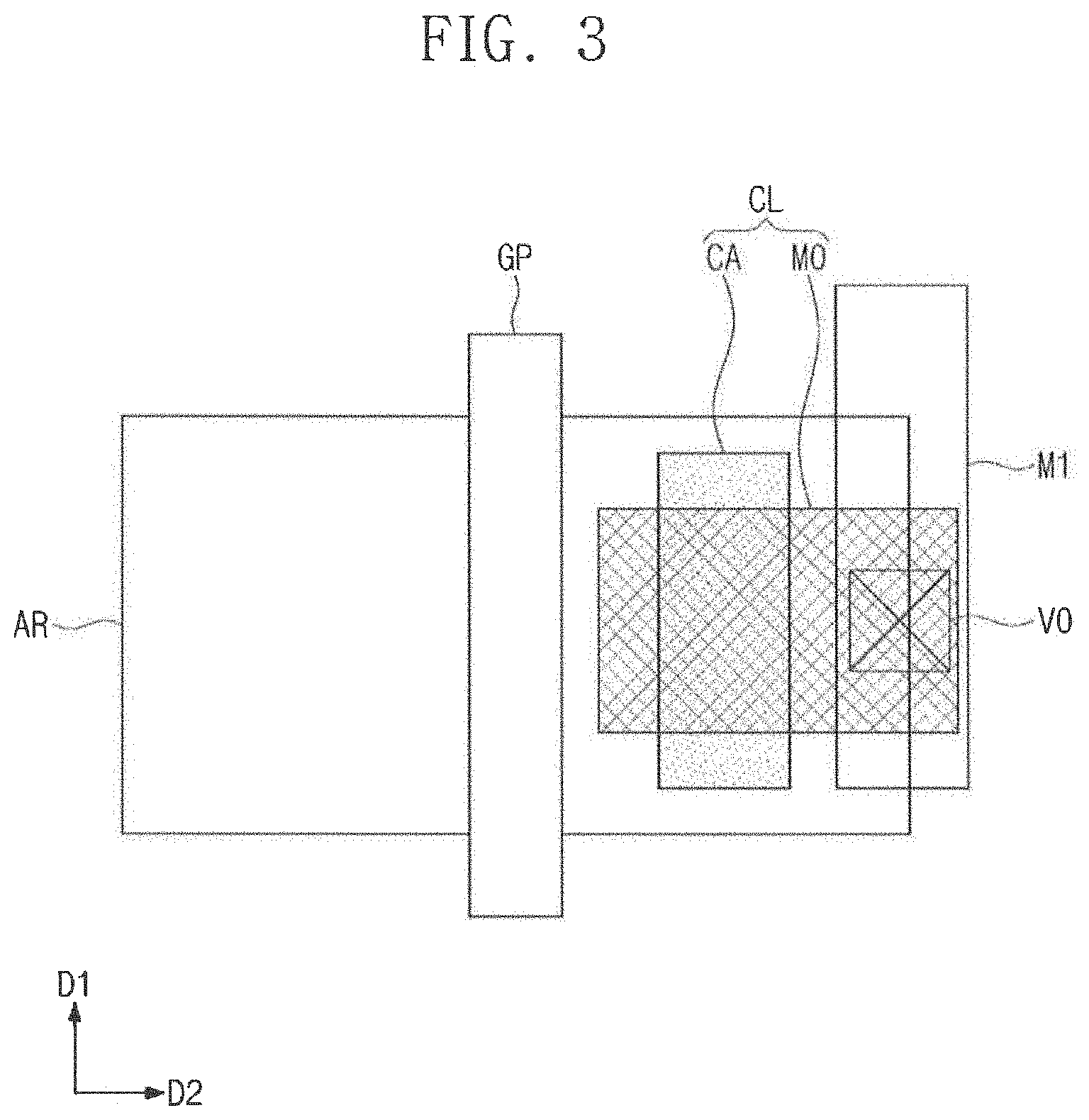

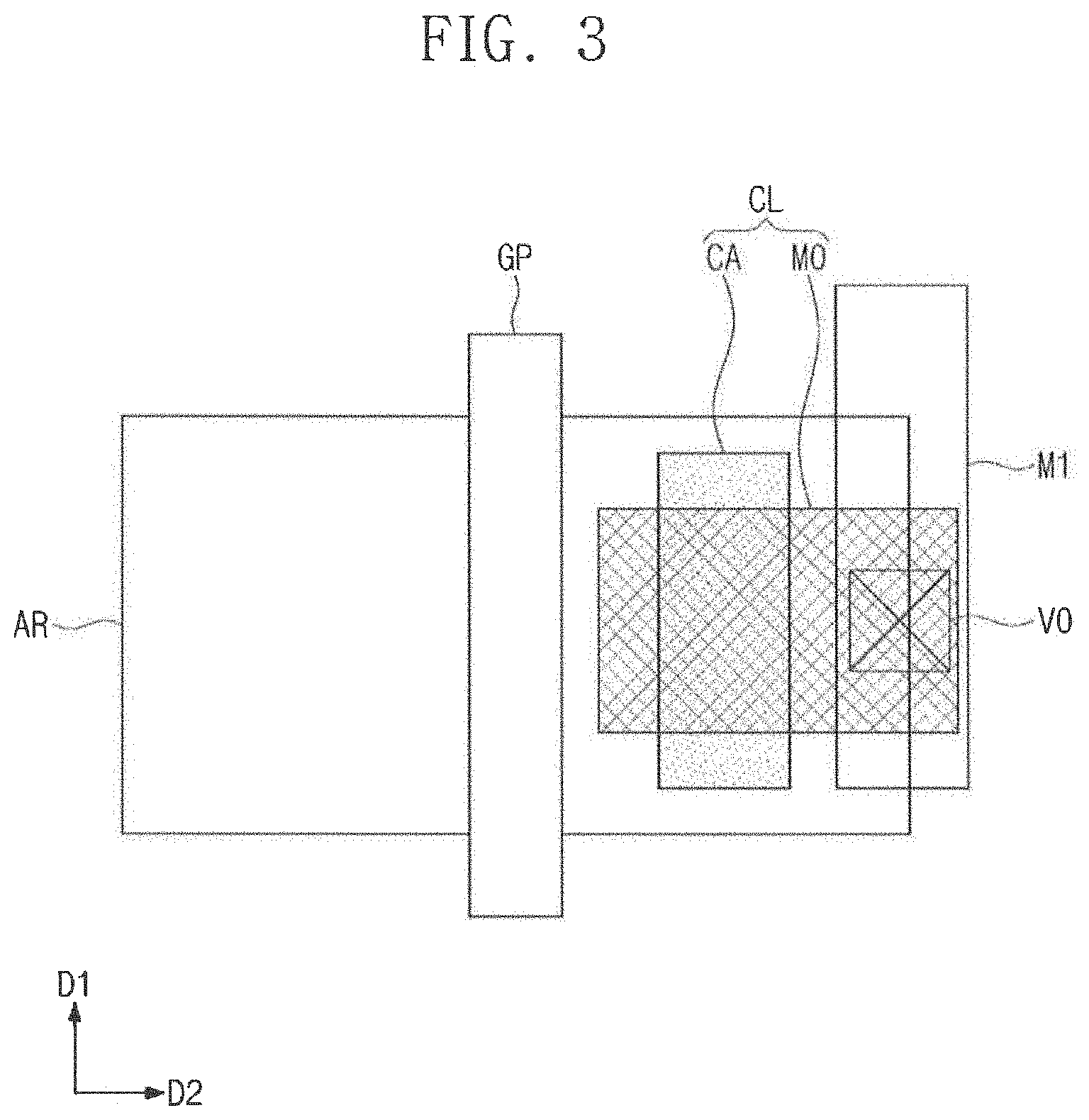

[0012] FIG. 3 is a layout diagram illustrating a portion of a standard cell layout according to exemplary embodiments of the present inventive concept.

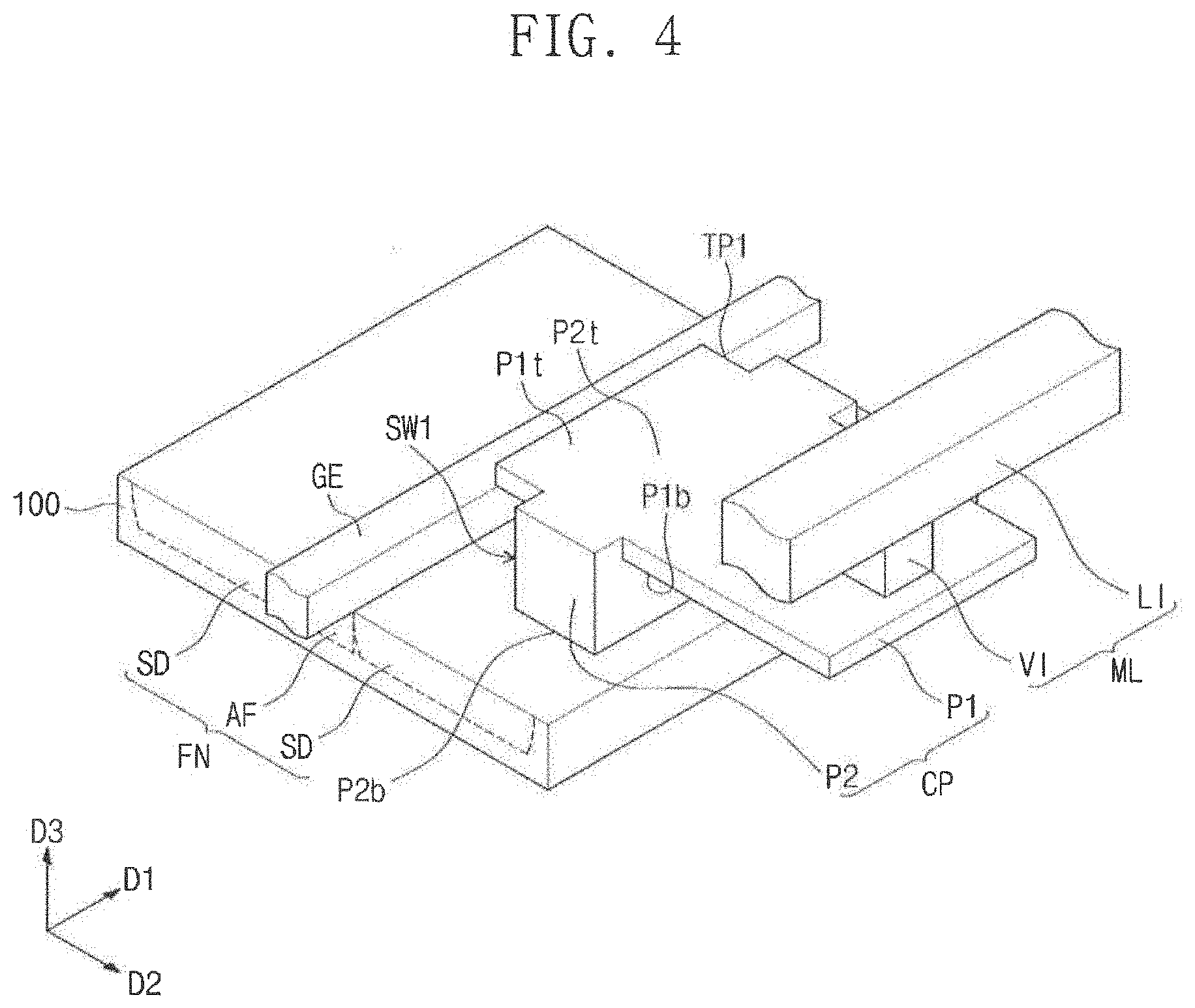

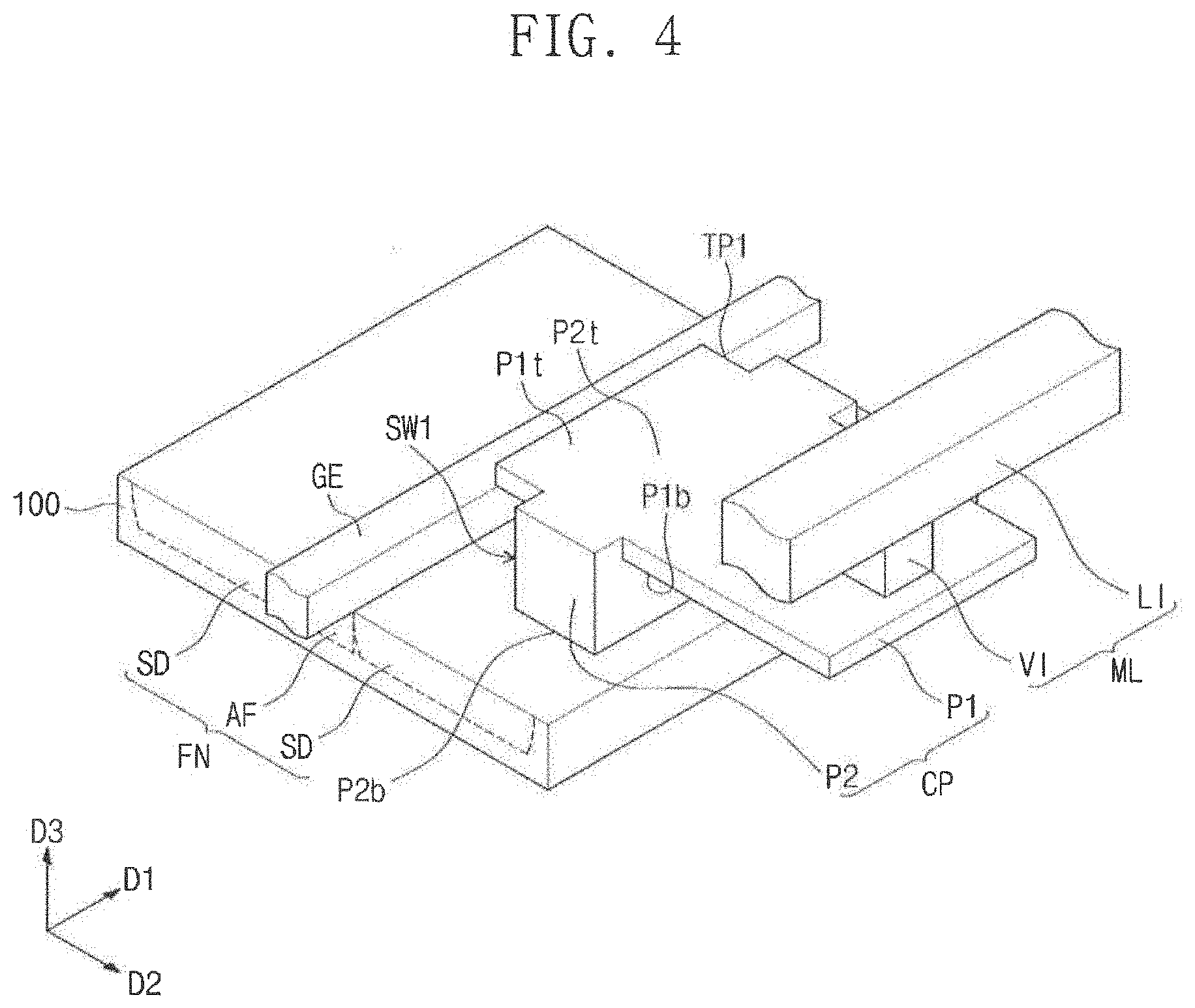

[0013] FIG. 4 is a perspective view illustrating a semiconductor device that is formed based on the layout of FIG. 3 according to exemplary embodiments of the preset inventive concept.

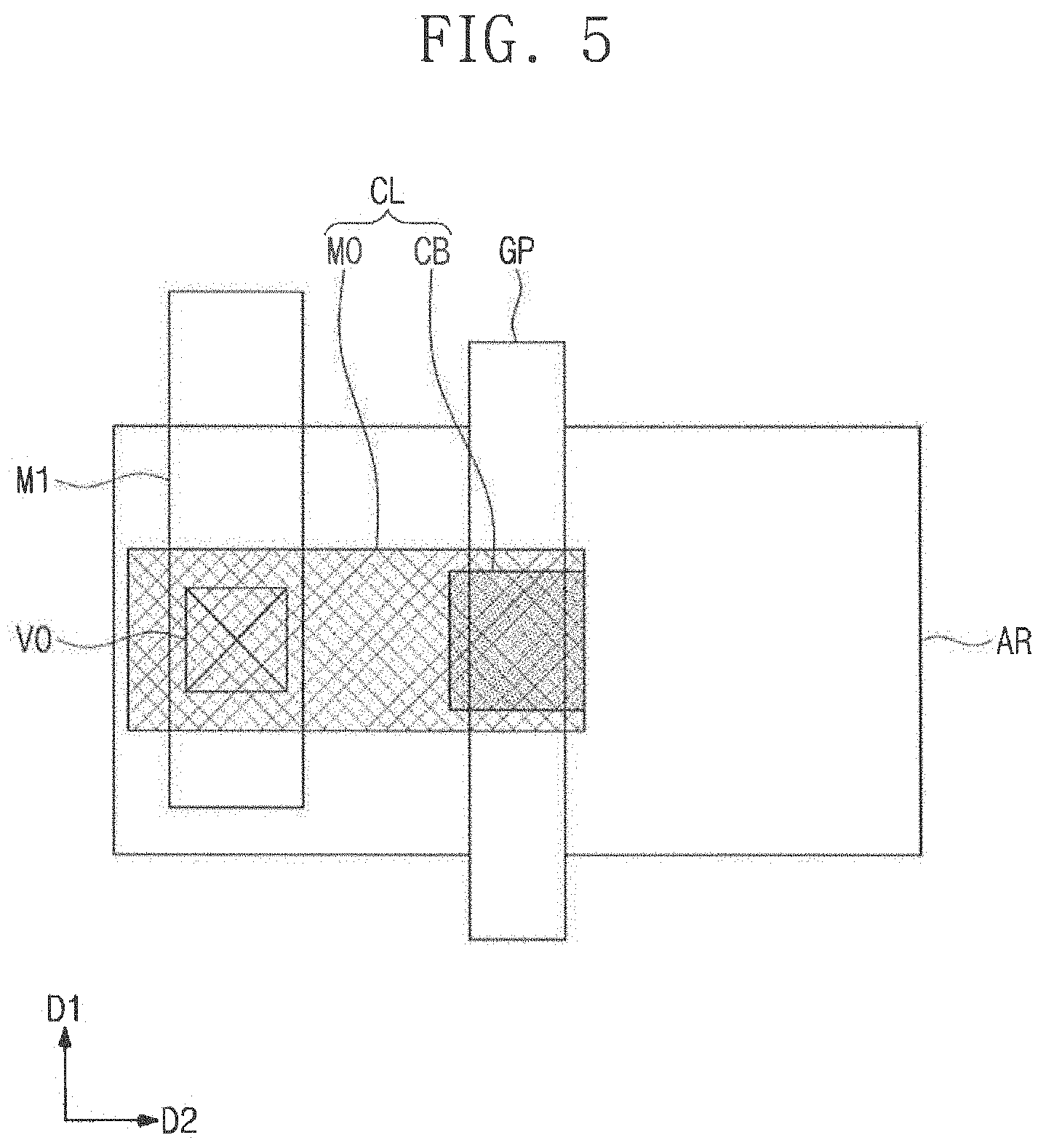

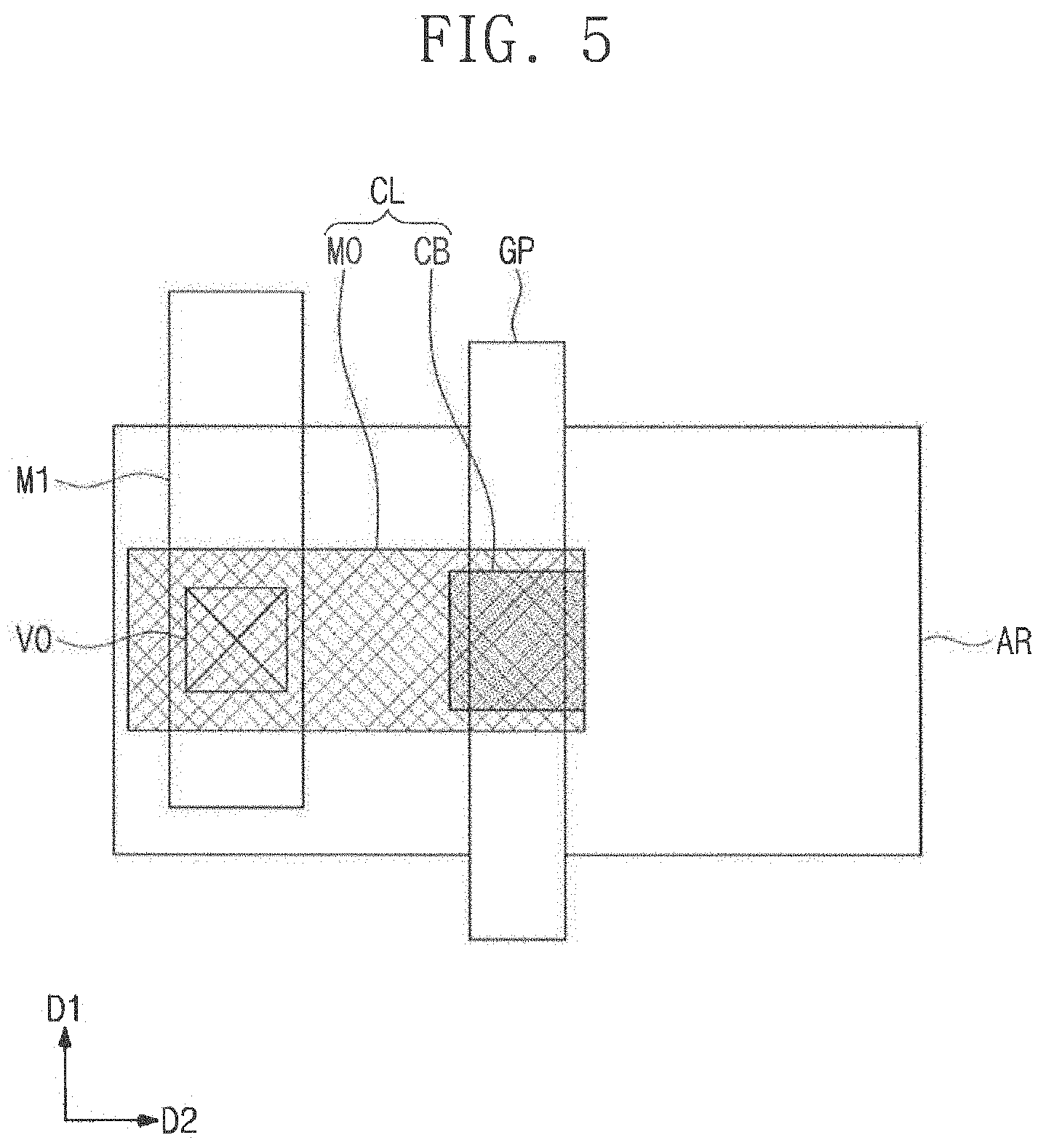

[0014] FIG. 5 is a layout diagram illustrating a portion of a standard cell layout according to exemplary embodiments of the present inventive concept.

[0015] FIG. 6 is a perspective view illustrating a semiconductor device that is formed based on the layout of FIG. 5 according to exemplary embodiments of the preset inventive concept.

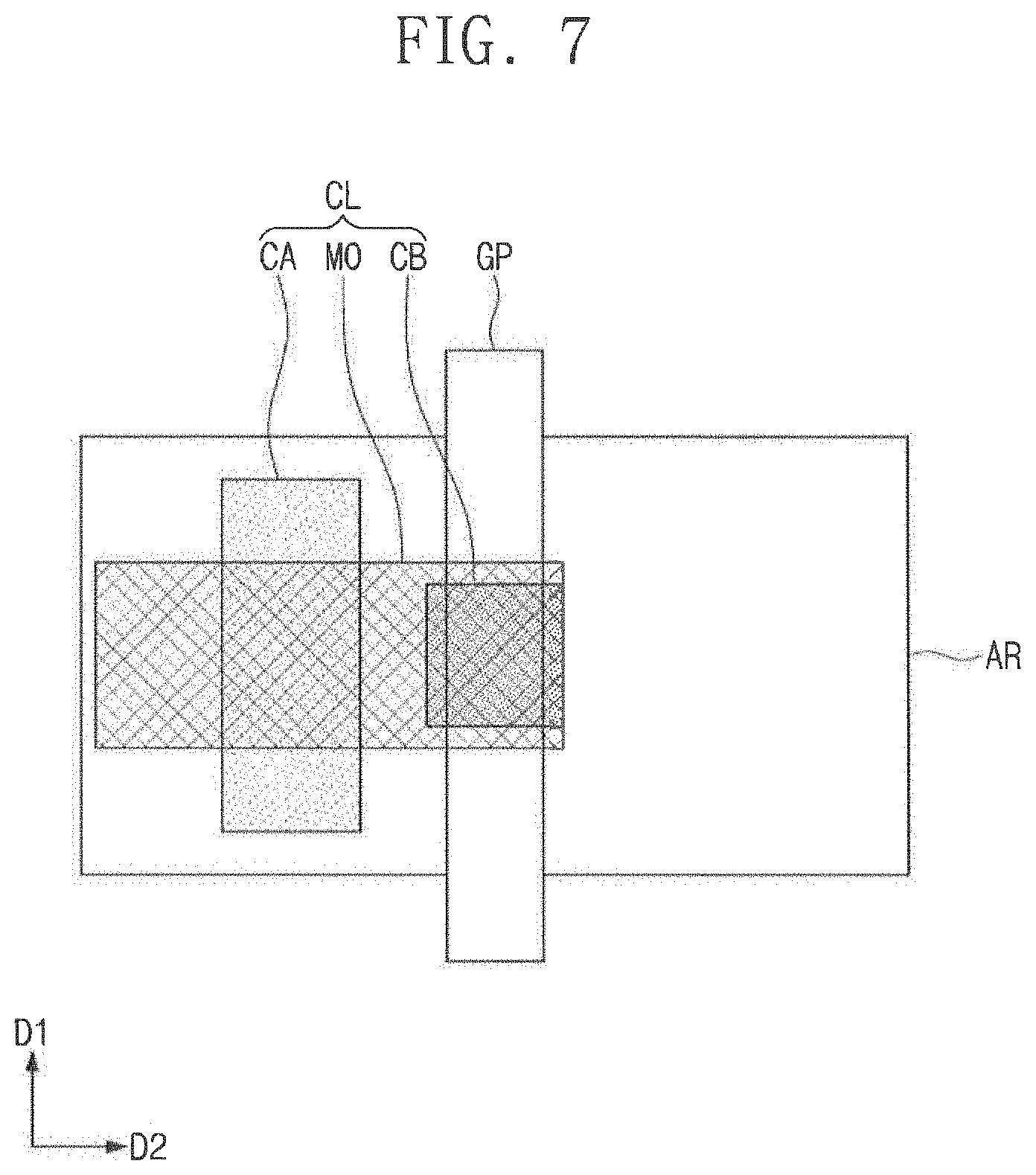

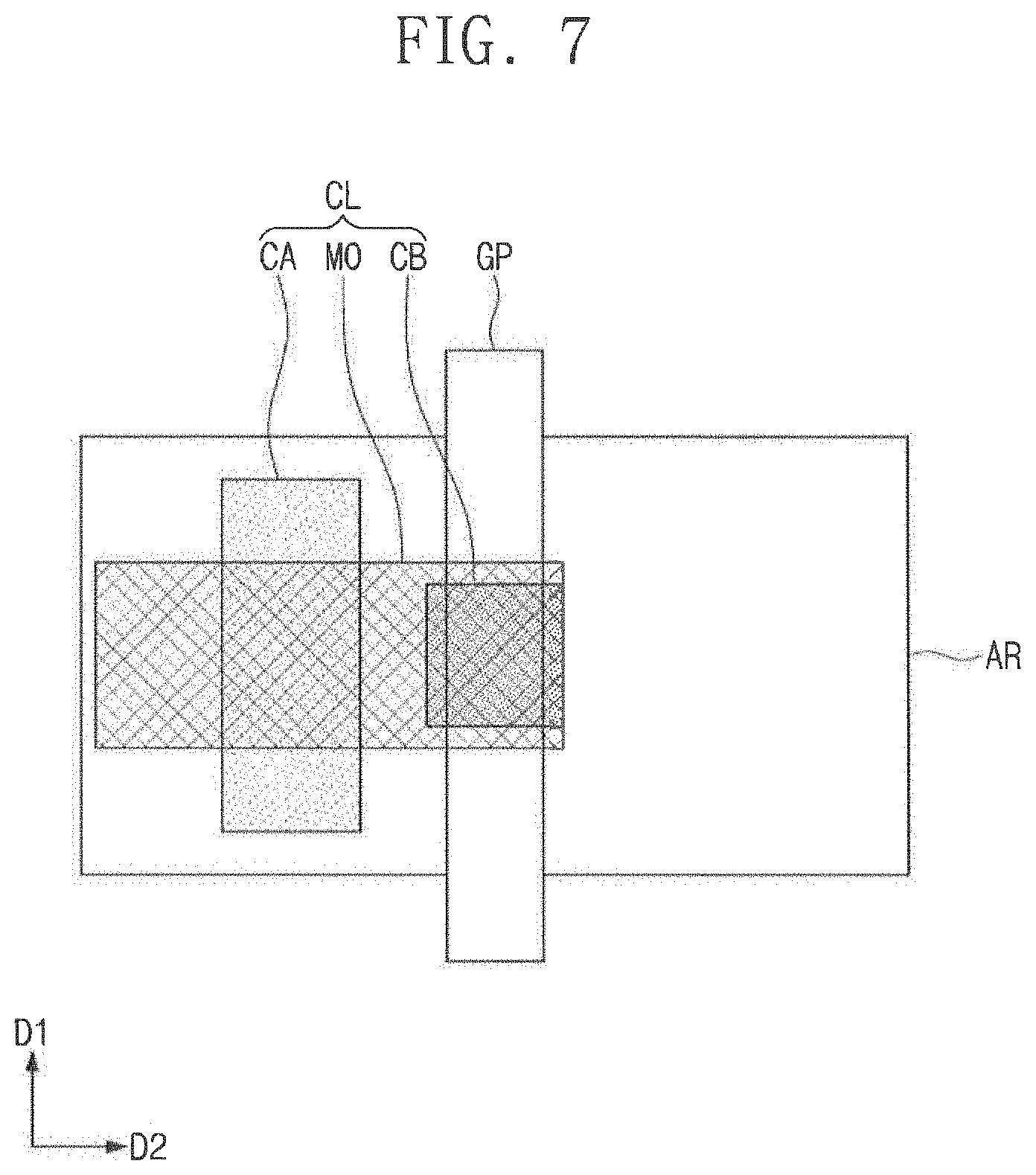

[0016] FIG. 7 is a layout diagram illustrating a portion of a standard cell layout according to exemplary embodiments of the present inventive concept.

[0017] FIG. 8 is a perspective view illustrating a semiconductor device that is formed based on the layout of FIG. 7 according to exemplary embodiments of the preset inventive concept.

[0018] FIG. 9 is a layout diagram illustrating a portion of a standard cell layout according to exemplary embodiments of the present inventive concept.

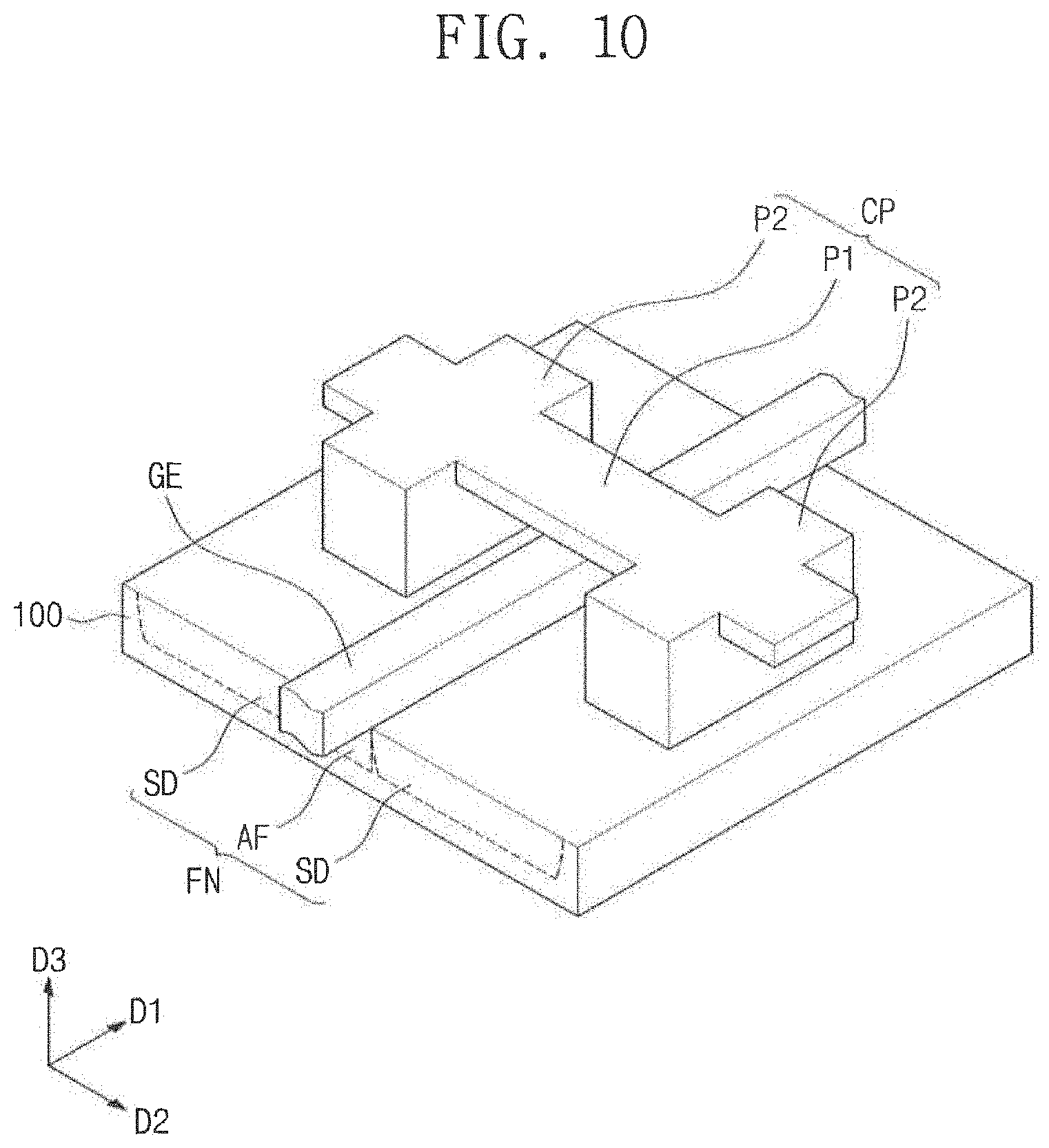

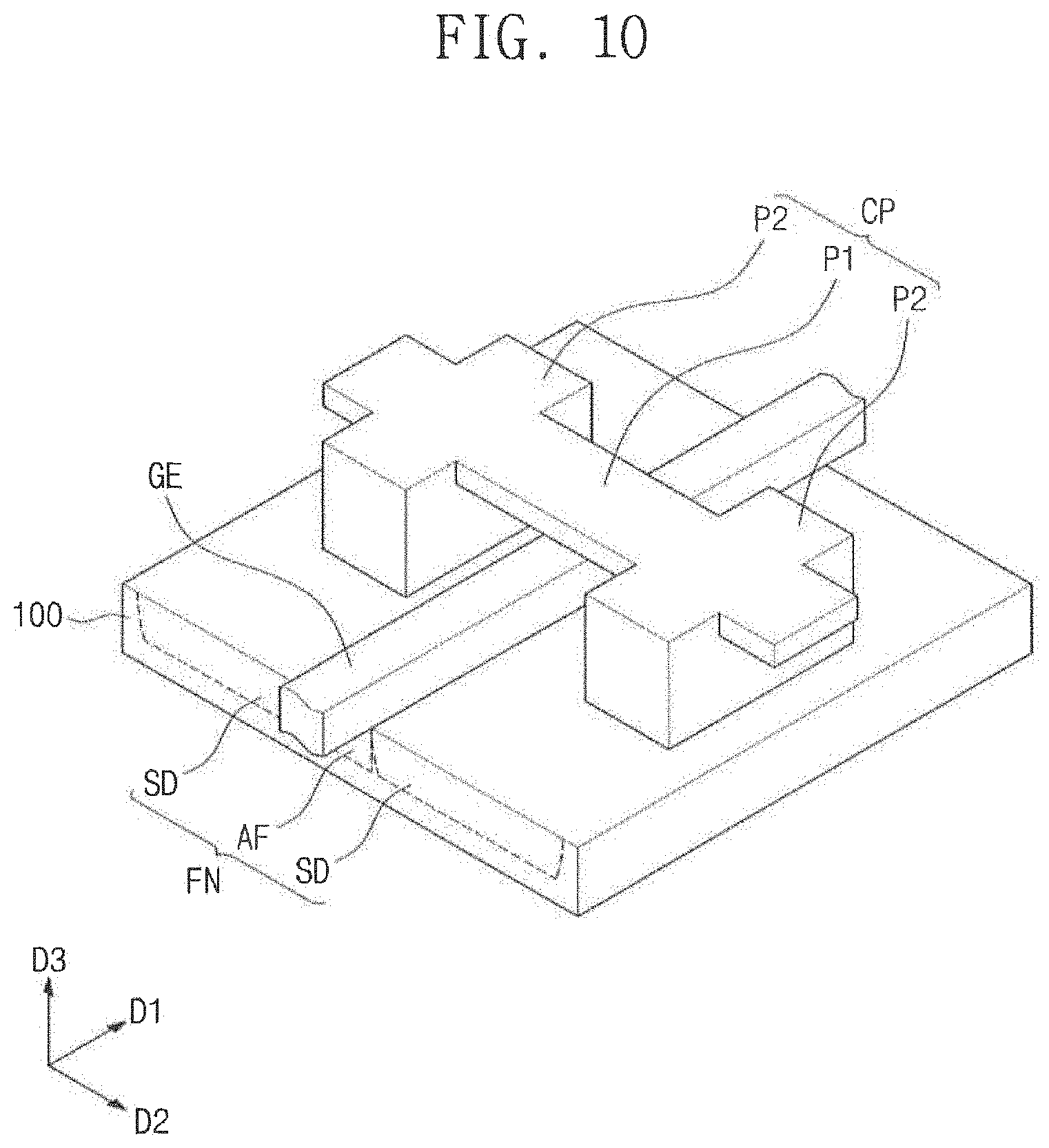

[0019] FIG. 10 is a perspective view illustrating a semiconductor device that is formed based on the layout of FIG. 9 according to exemplary embodiments of the preset inventive concept.

[0020] FIG. 11 is a layout diagram illustrating a portion of a standard cell layout according to exemplary embodiments of the present inventive concept.

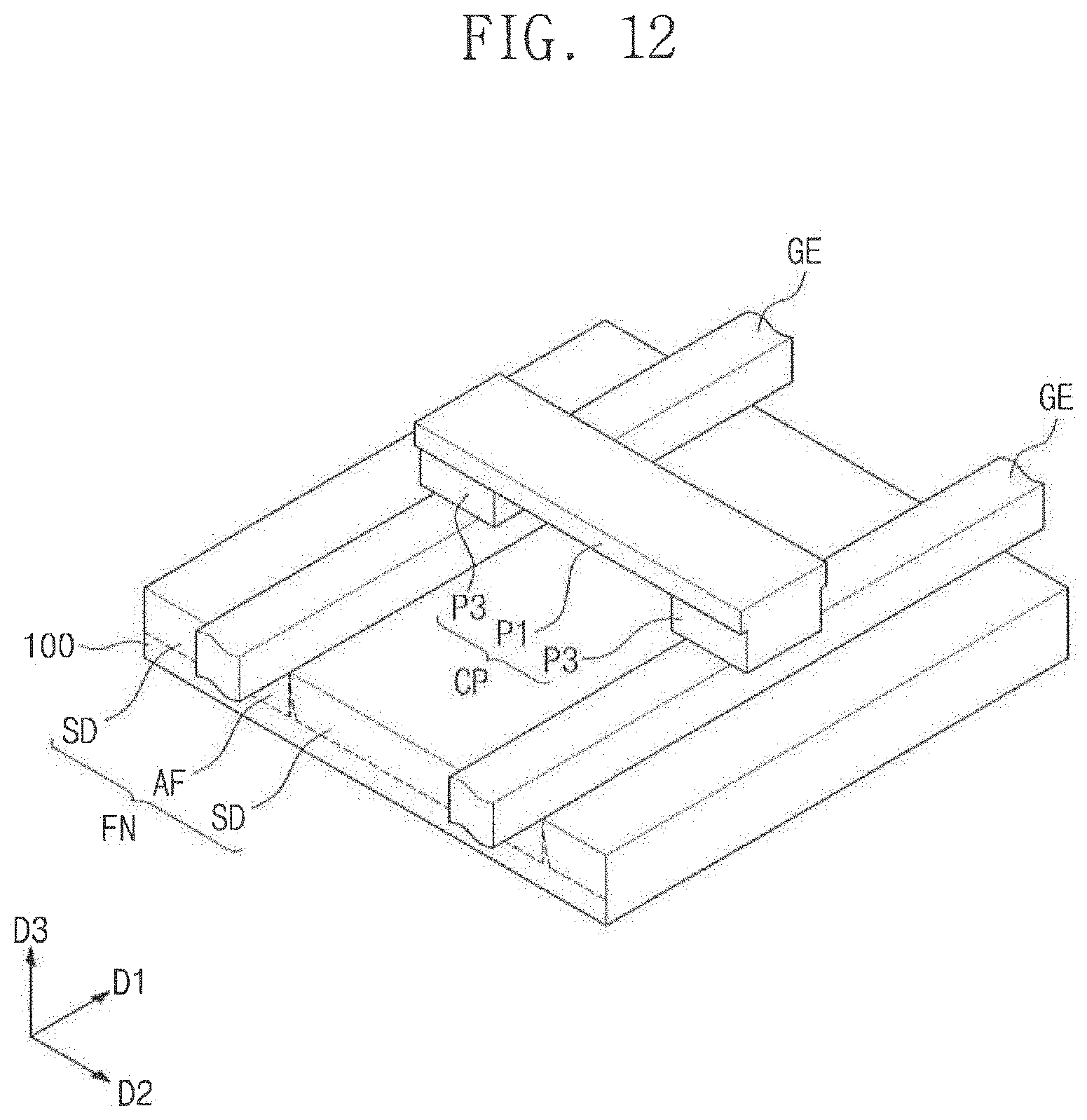

[0021] FIG. 12 is a perspective view illustrating a semiconductor device according to exemplary embodiments of the present inventive concept.

[0022] FIG. 13 is a layout diagram including standard cell layouts according to exemplary embodiments of the present inventive concept.

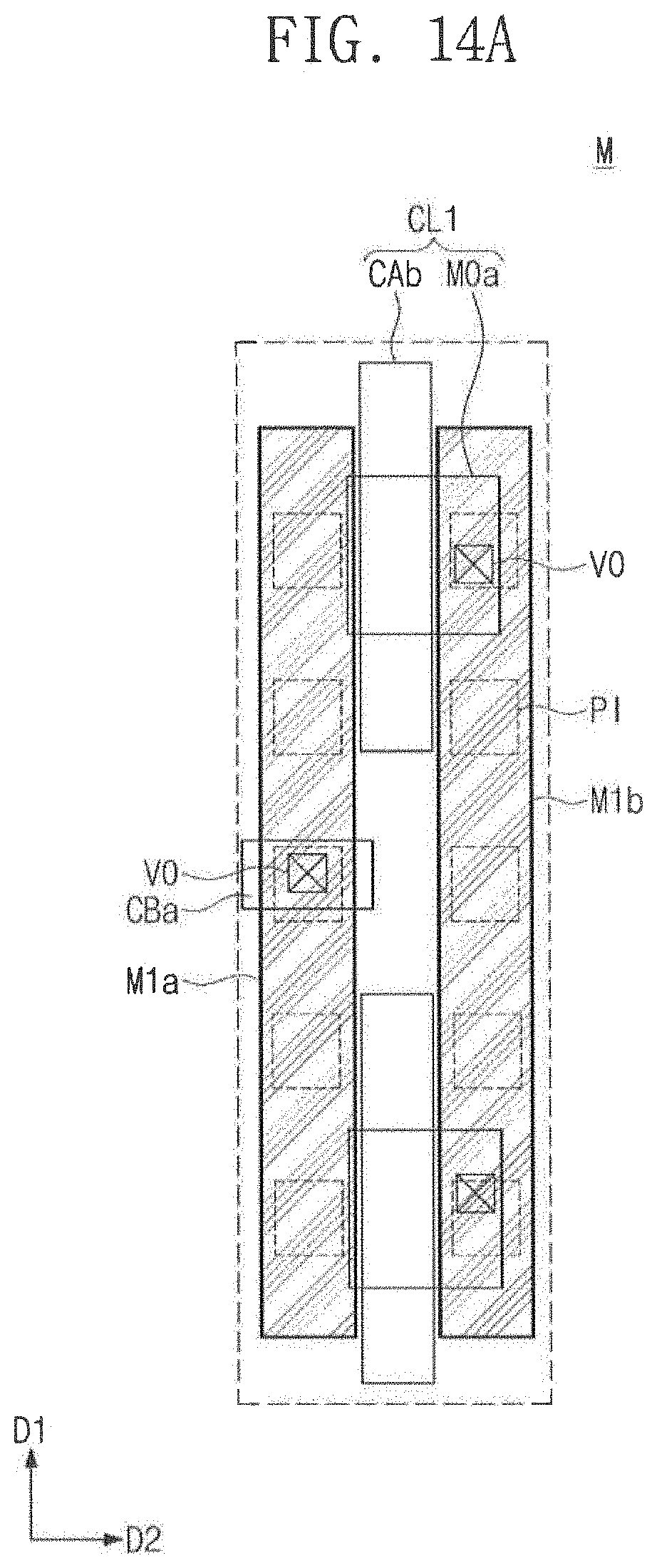

[0023] FIG. 14A is a layout diagram illustrating a region `M` of FIG. 13 according to exemplary embodiments of the present inventive concept.

[0024] FIG. 14B is a layout diagram illustrating the region `M` of FIG. 13 according to a comparative example.

[0025] FIG. 15A is a layout diagram illustrating a region `N` of FIG. 13 according to exemplary embodiments of the inventive concept.

[0026] FIG. 15B is a layout diagram illustrating the region `N` of FIG. 13 according to a comparative example.

[0027] FIG. 16 is a plan view illustrating a semiconductor device according to exemplary embodiments of the inventive concept.

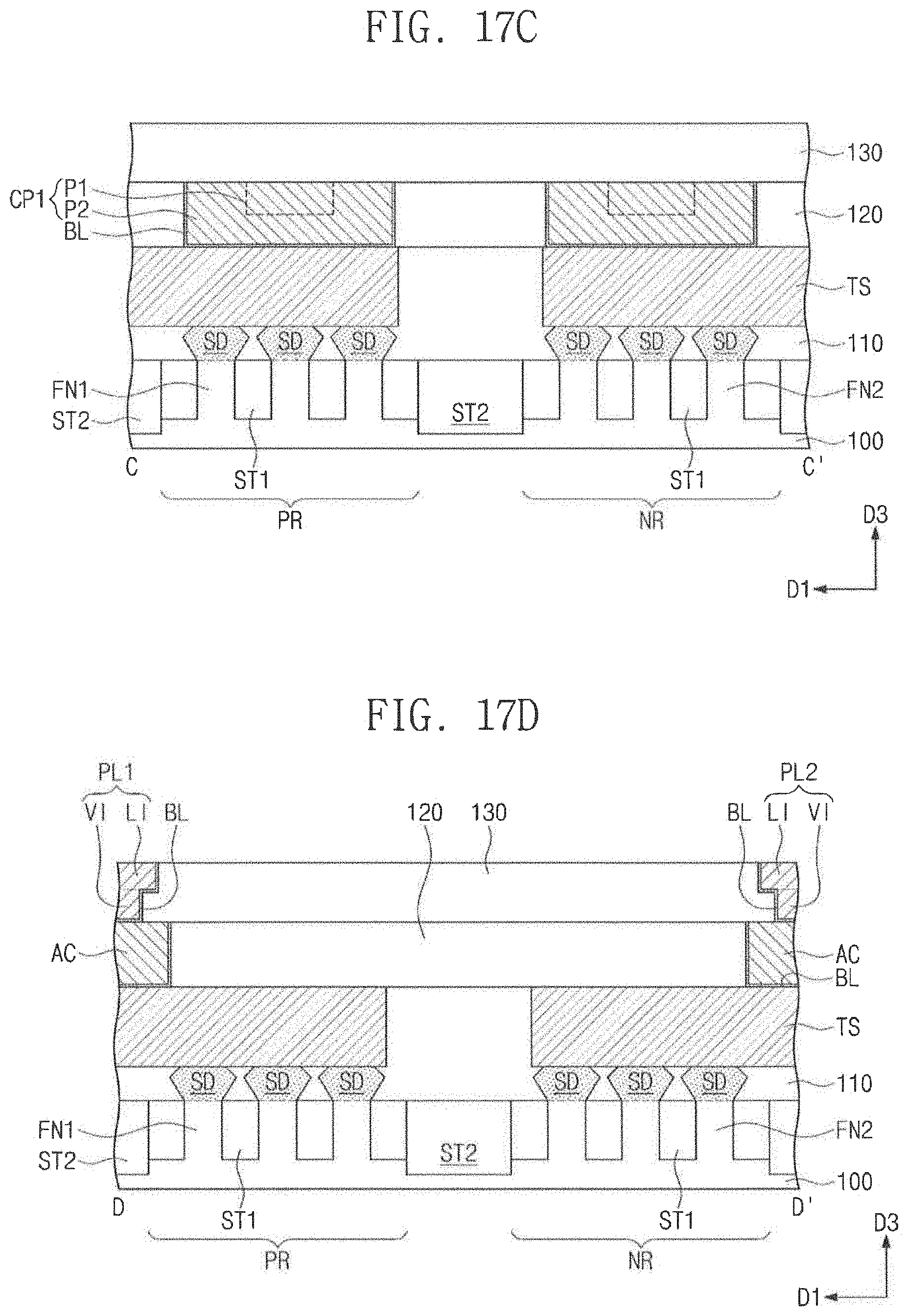

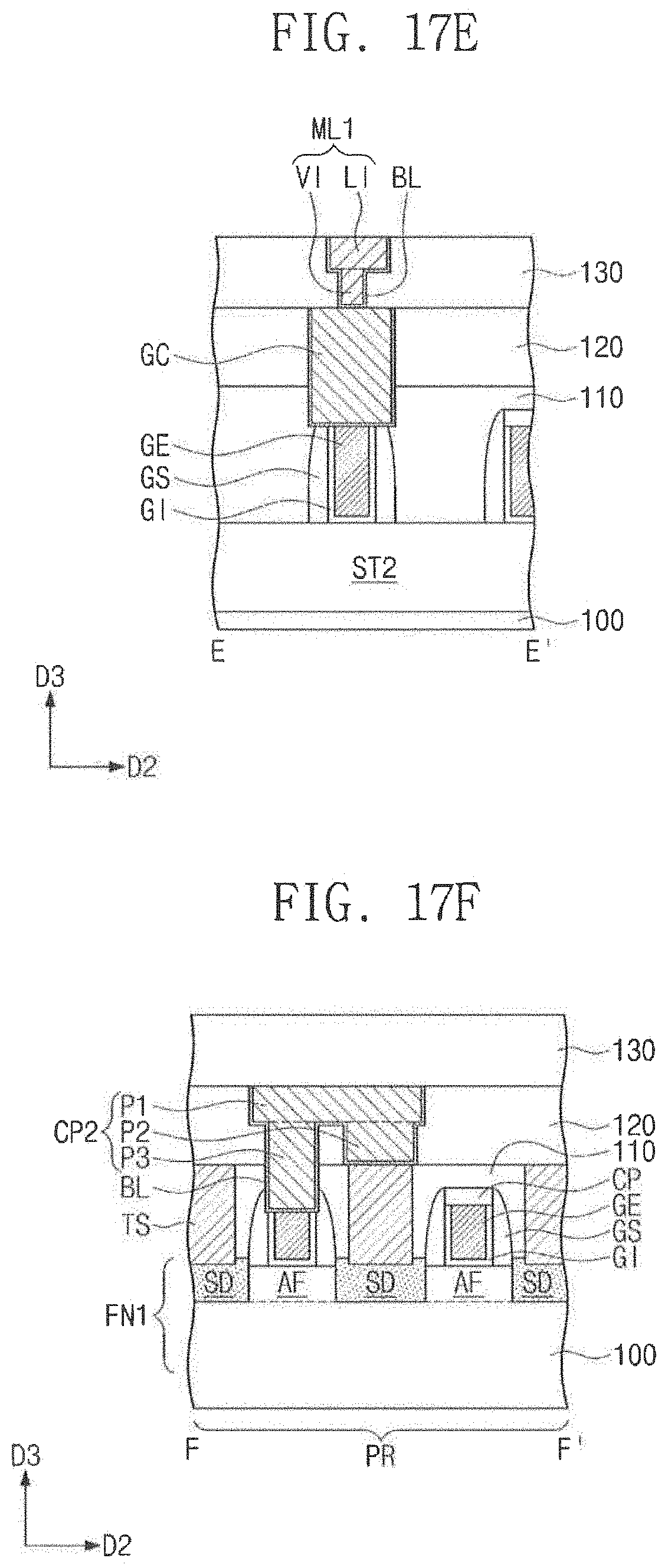

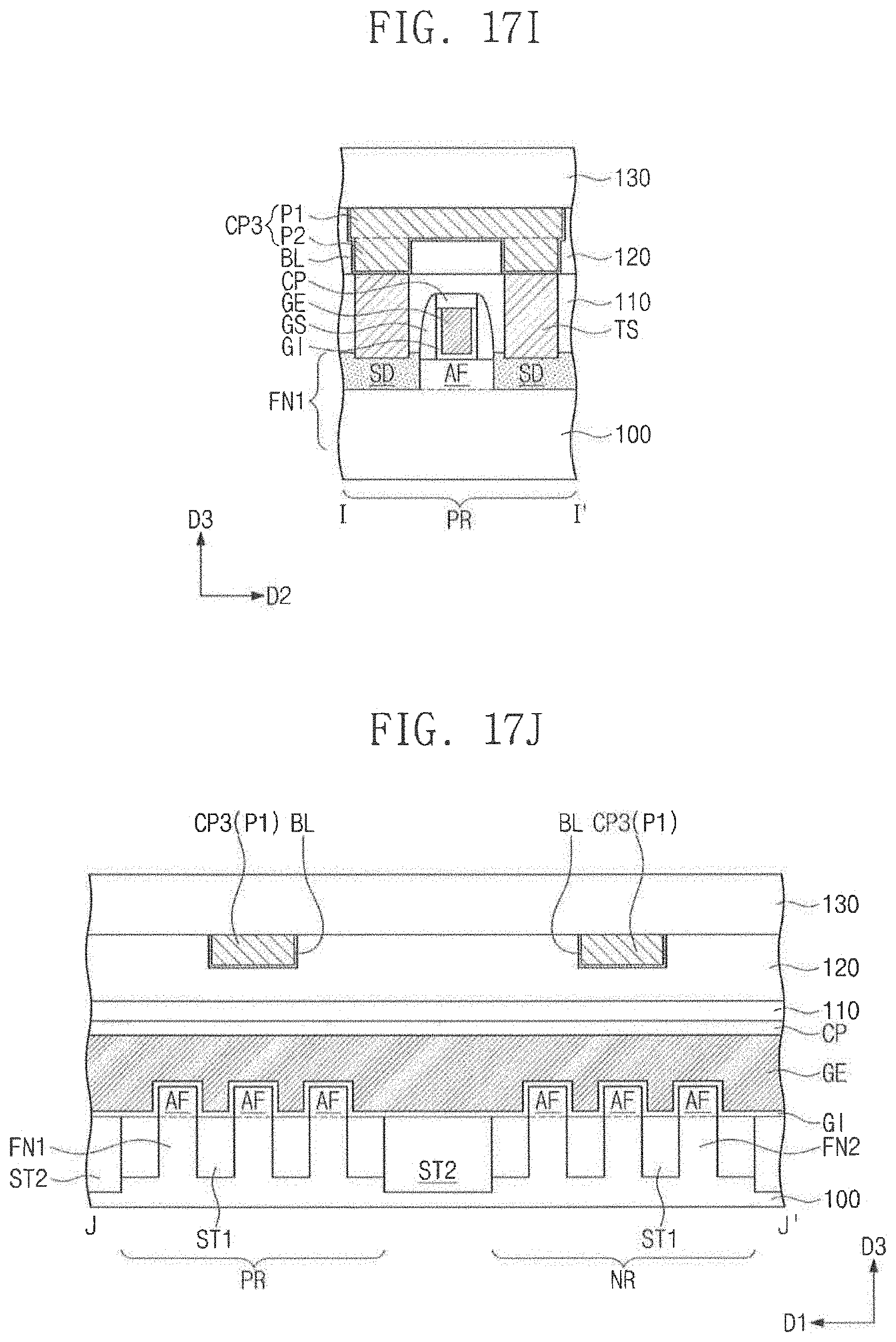

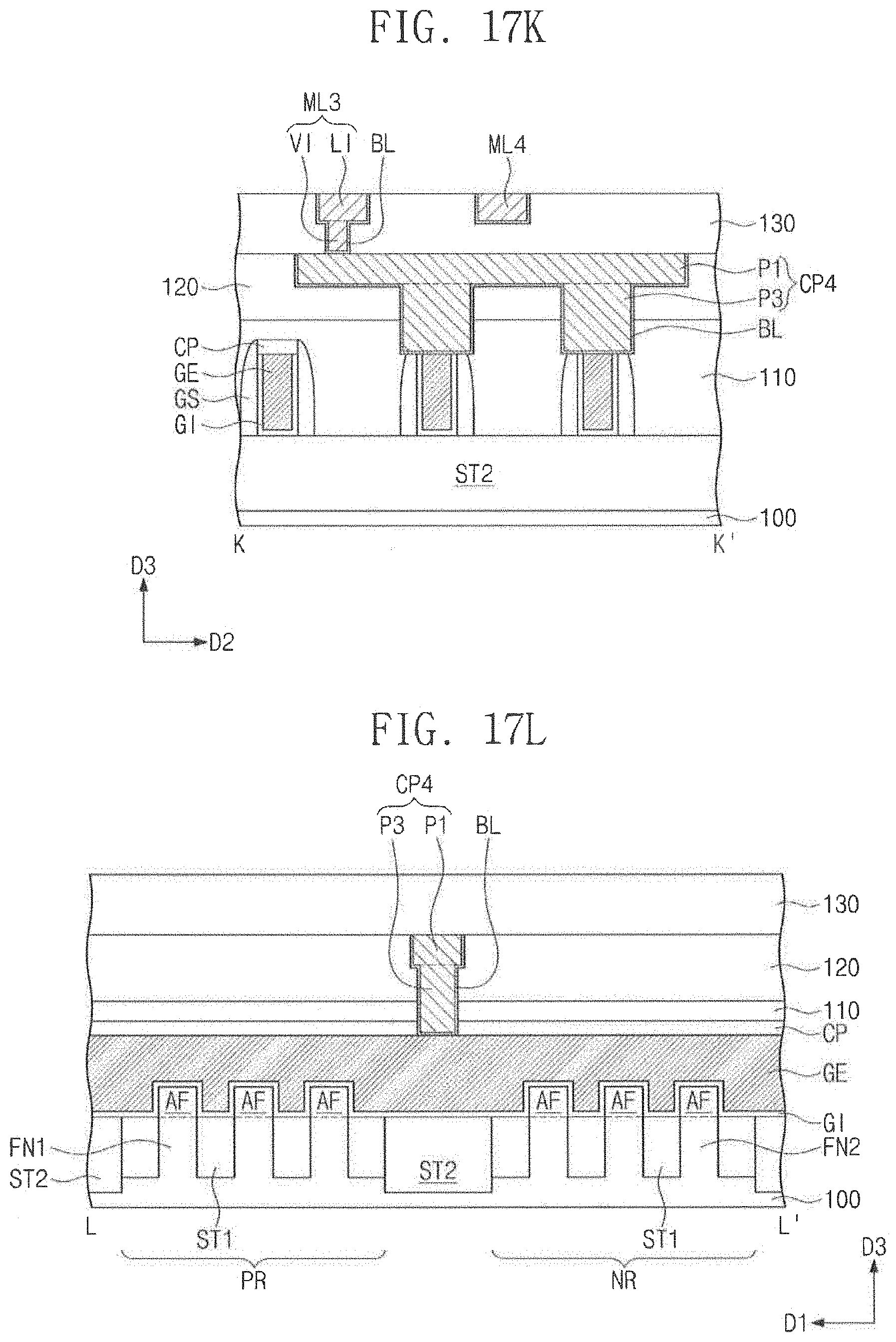

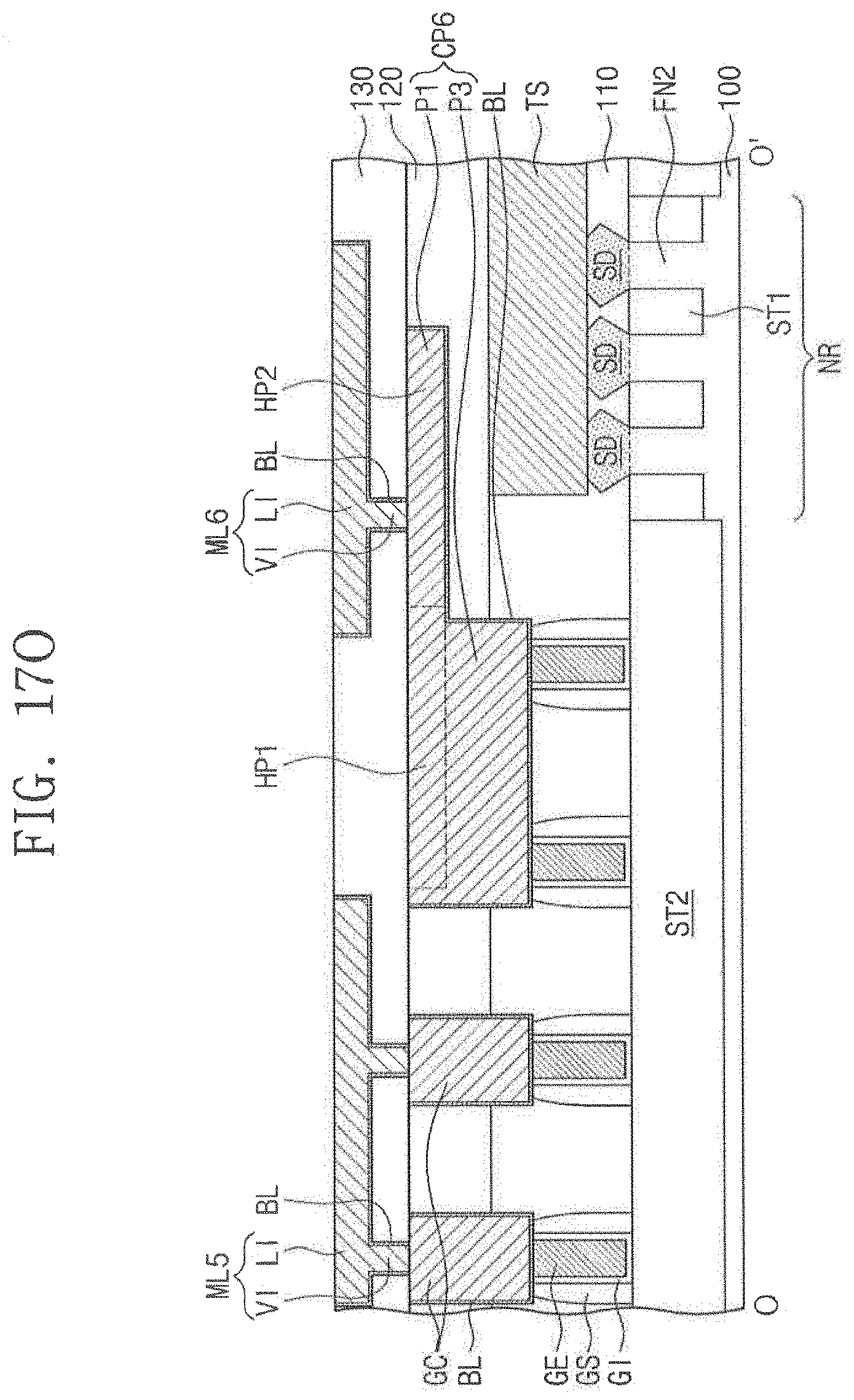

[0028] FIGS. 17A, 17B, 17C, 17D, 17E, 17F, 17G, 17H, 17I, 17J, 17K, 17L, 17M, 17N, 17O, 17P, 17Q and 17R are sectional views taken along lines A-A', B-B', C-C', D-D', E-E', F-F', G-G', H-H', I-I', J-J', K-K', L-L', M-M', N-N', O-O', P-P', Q-Q', and R-R', respectively, of FIG. 16 according to exemplary embodiments of the preset inventive concept.

[0029] FIGS. 18A and 18B are sectional views taken along the line A-A' of FIG. 16 to illustrate a semiconductor device according to exemplary embodiments of the present inventive concept.

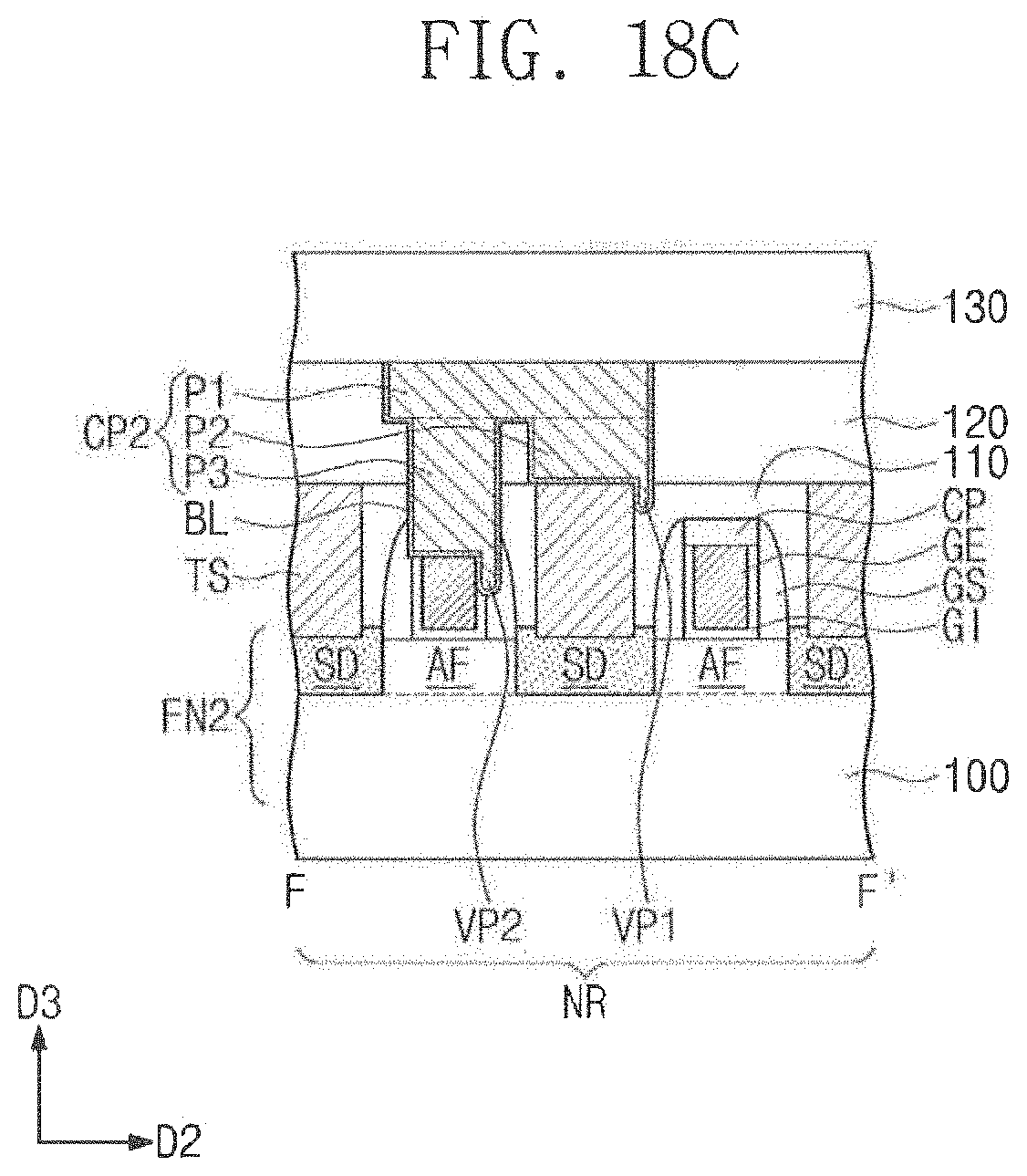

[0030] FIG. 18C is a sectional view taken along the line F-F' of FIG. 16 to illustrate a semiconductor device according to exemplary embodiments of the present inventive concept.

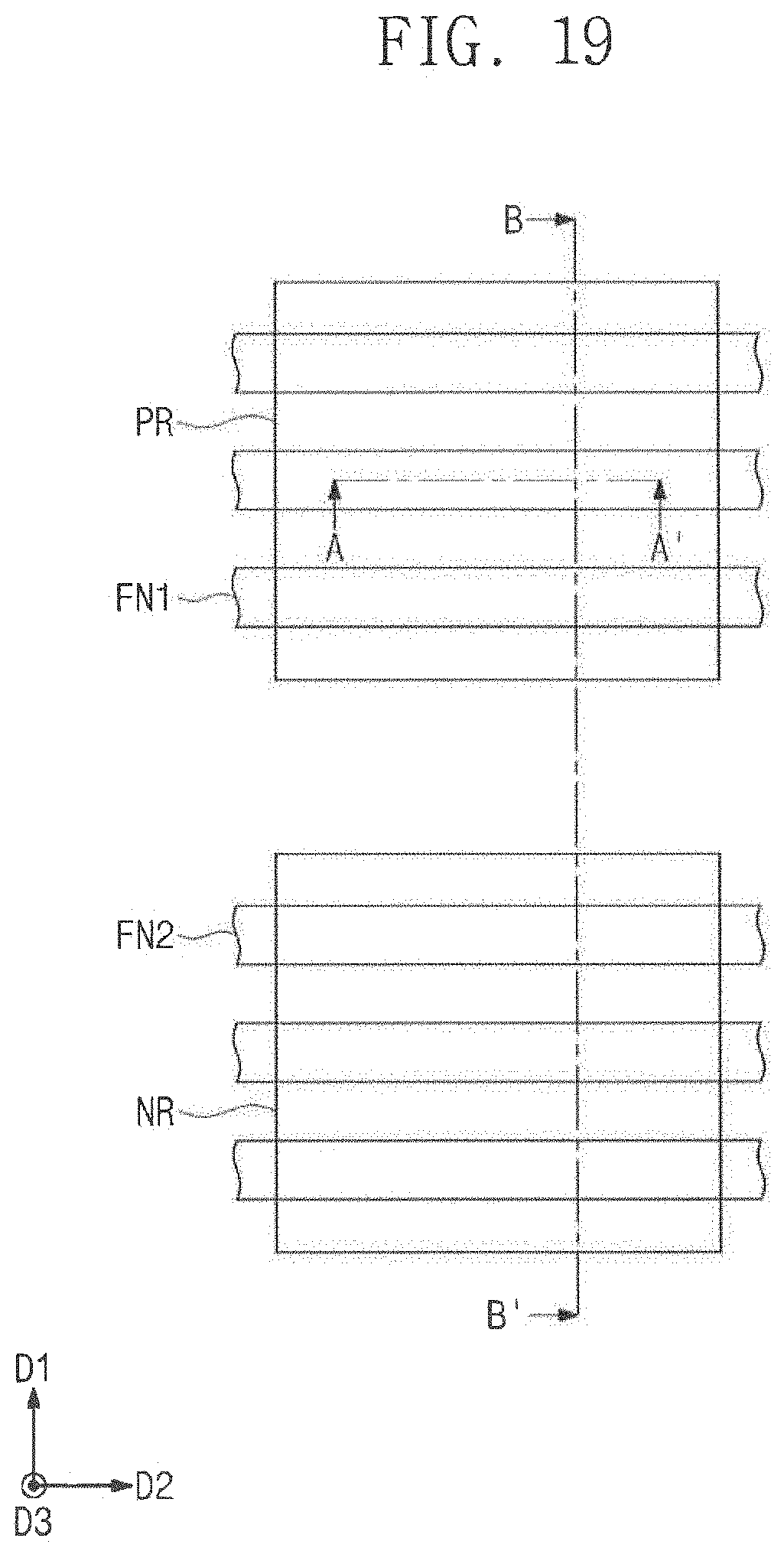

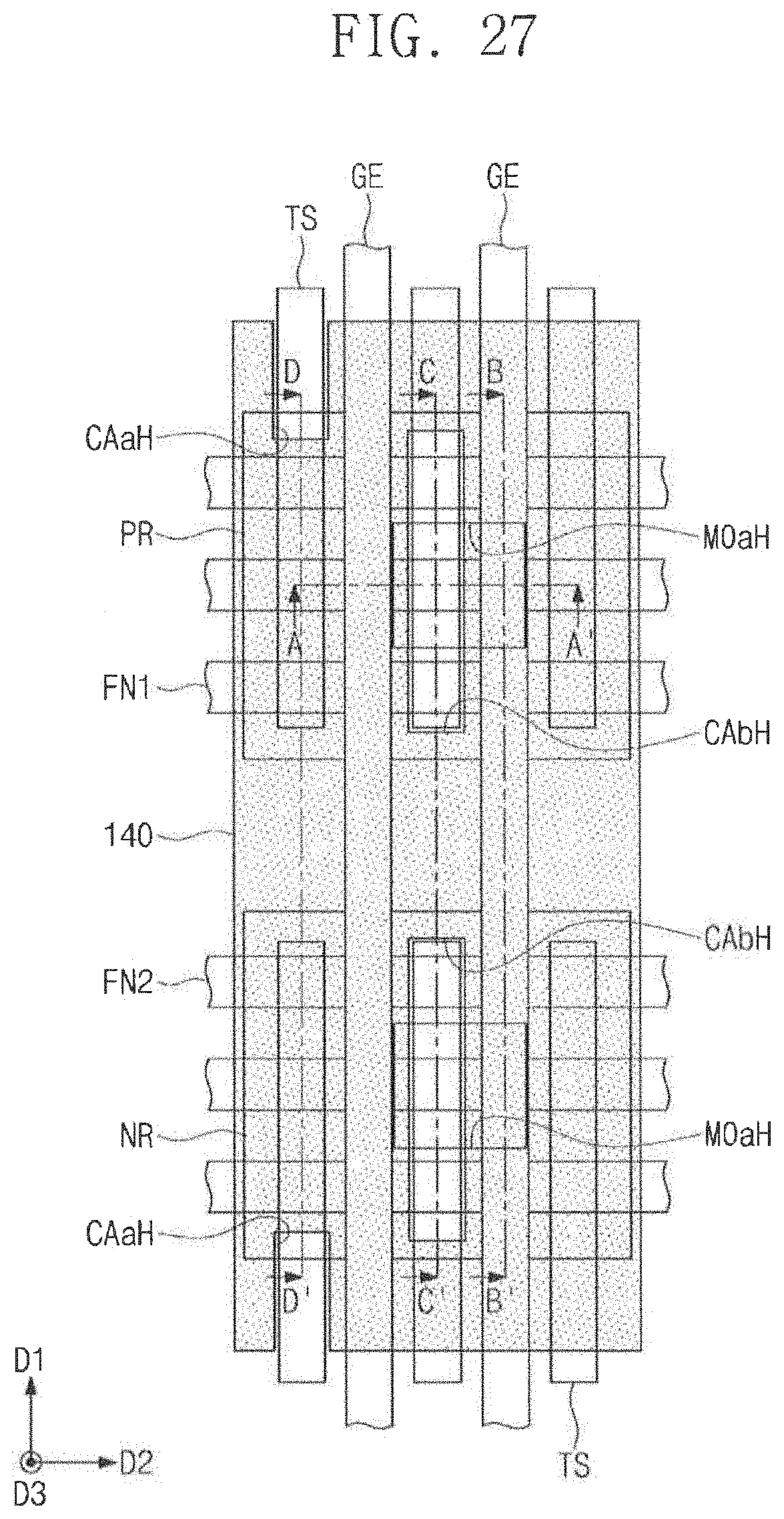

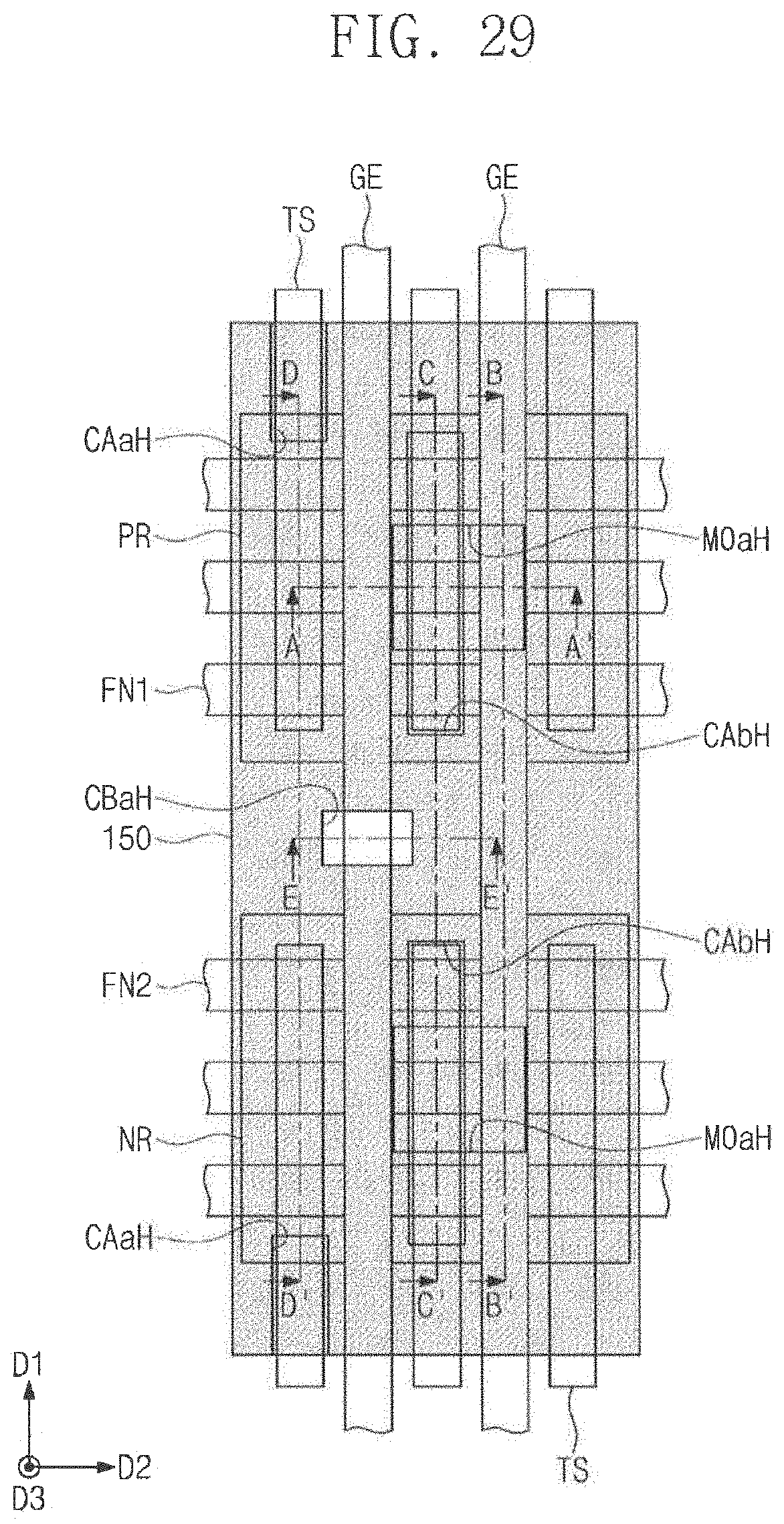

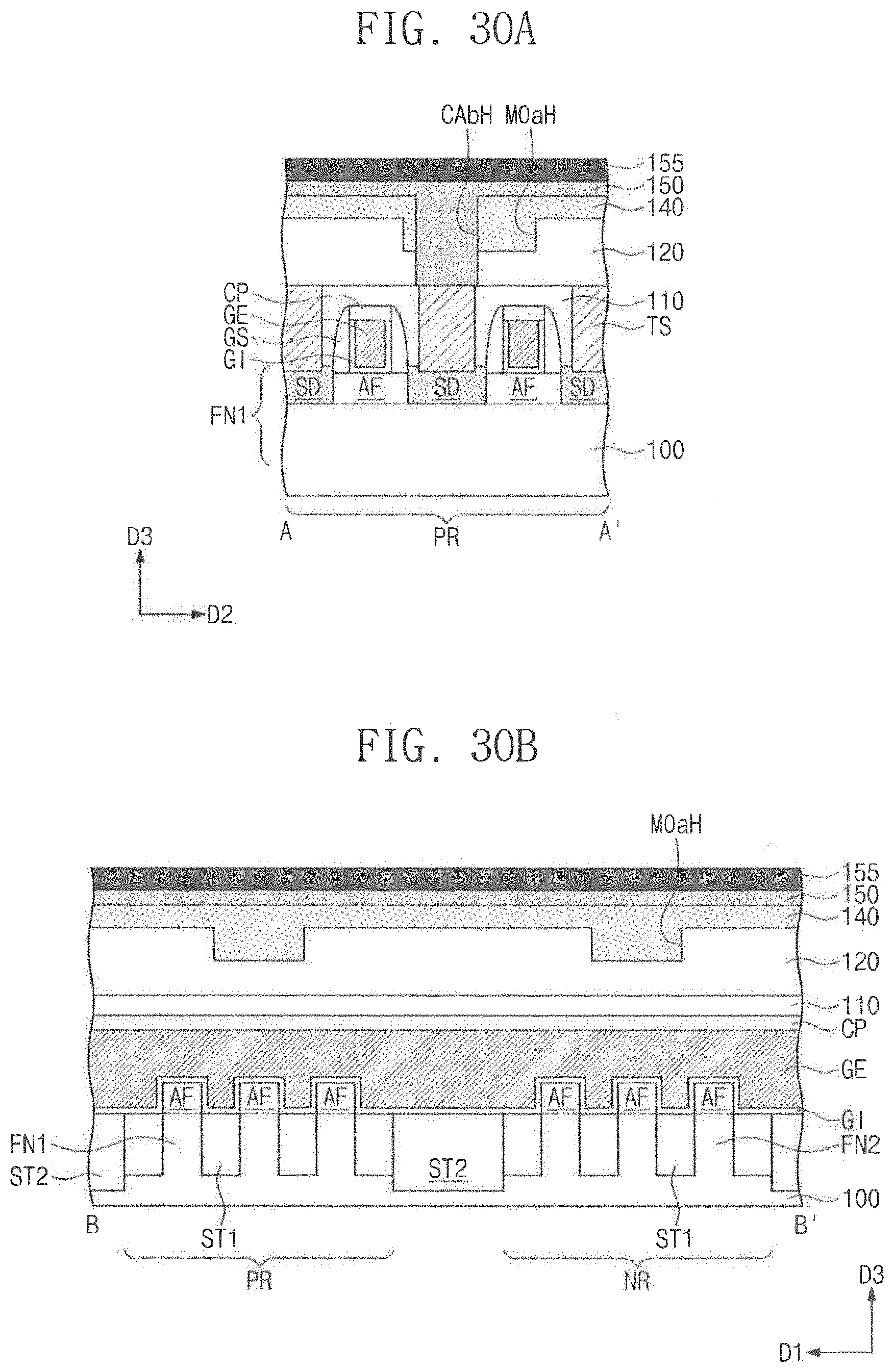

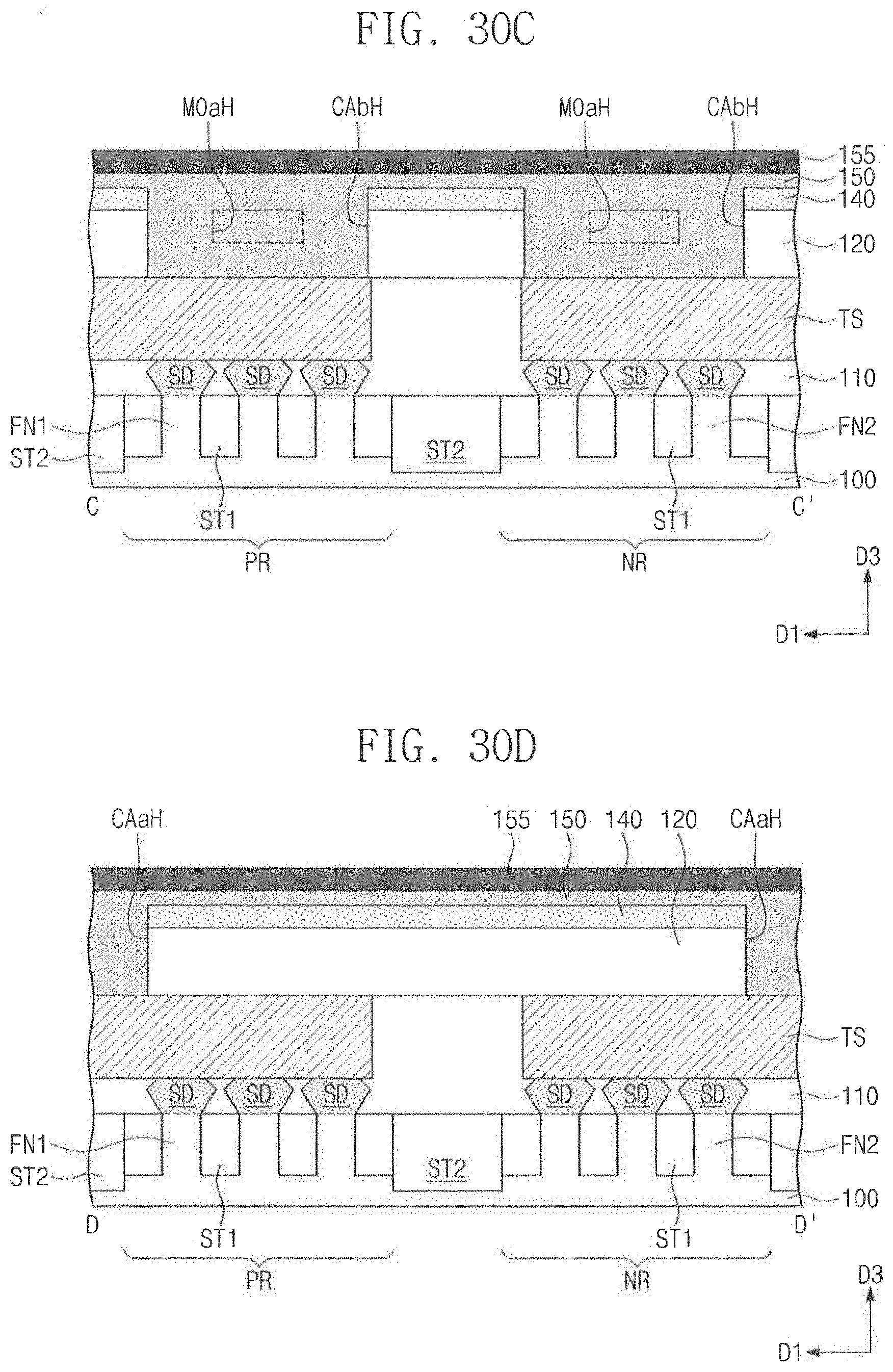

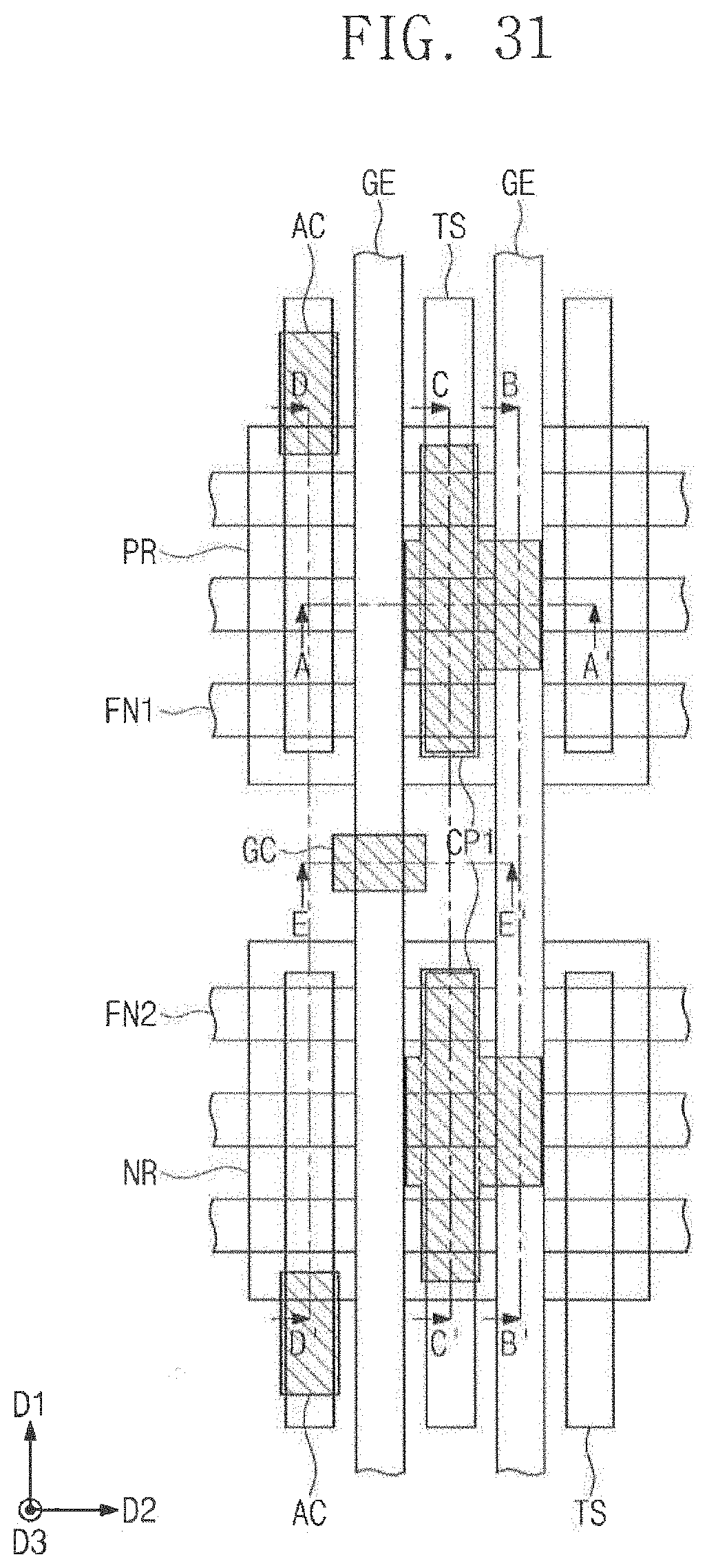

[0031] FIGS. 19, 21, 23, 25, 27, 29, and 31 are plan views illustrating a method of fabricating a semiconductor device, according to exemplary embodiments of the present inventive concept.

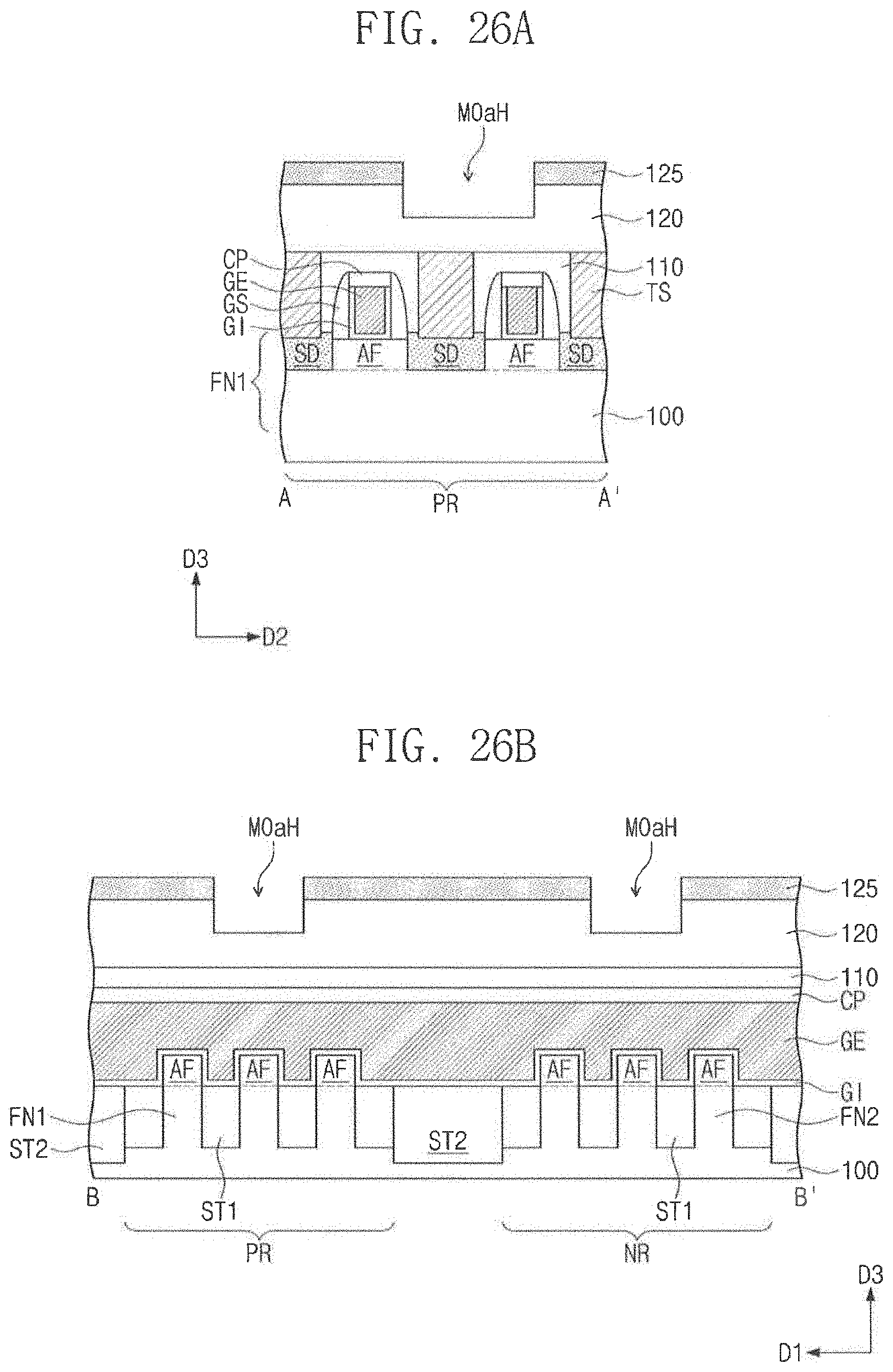

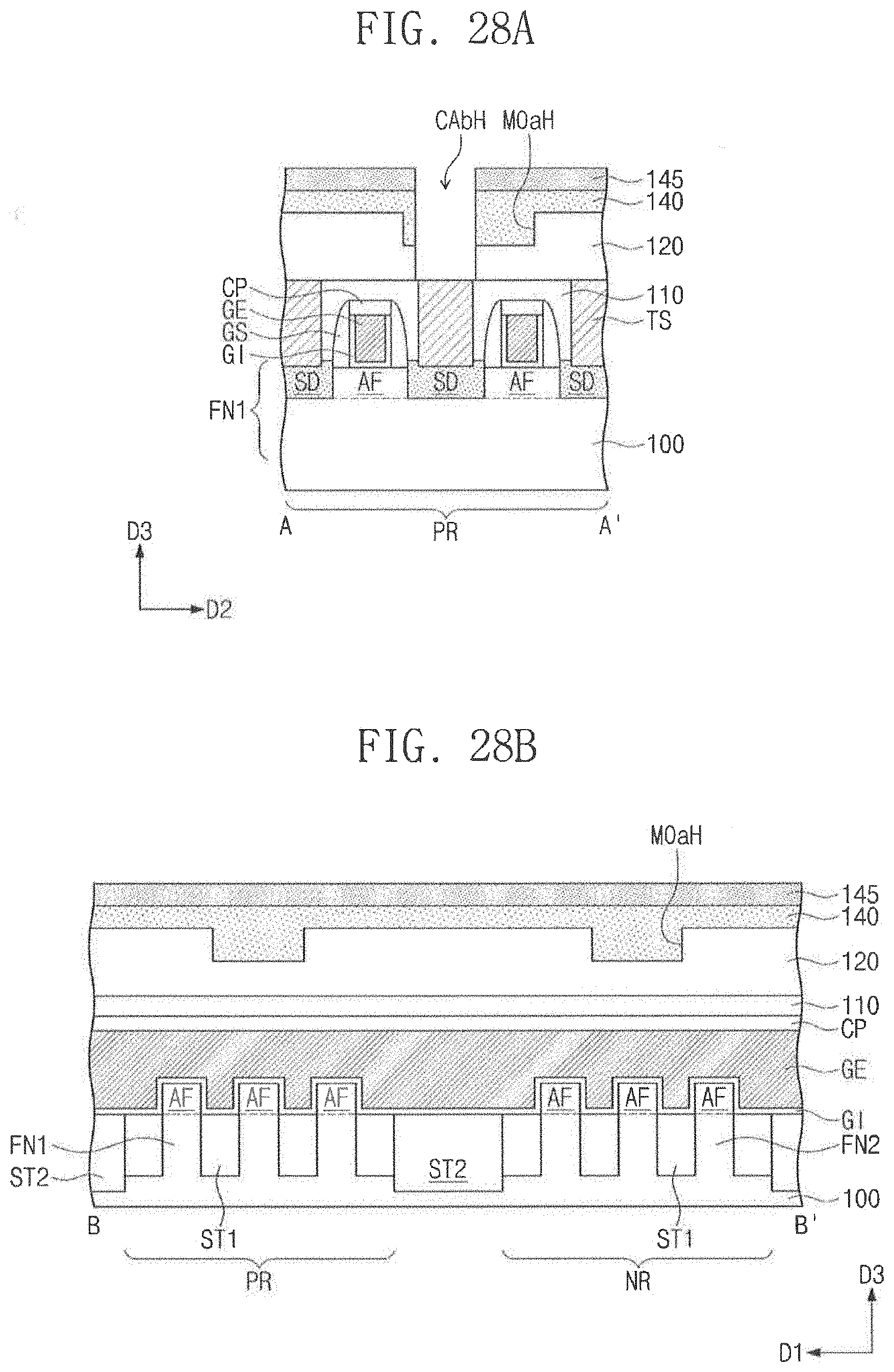

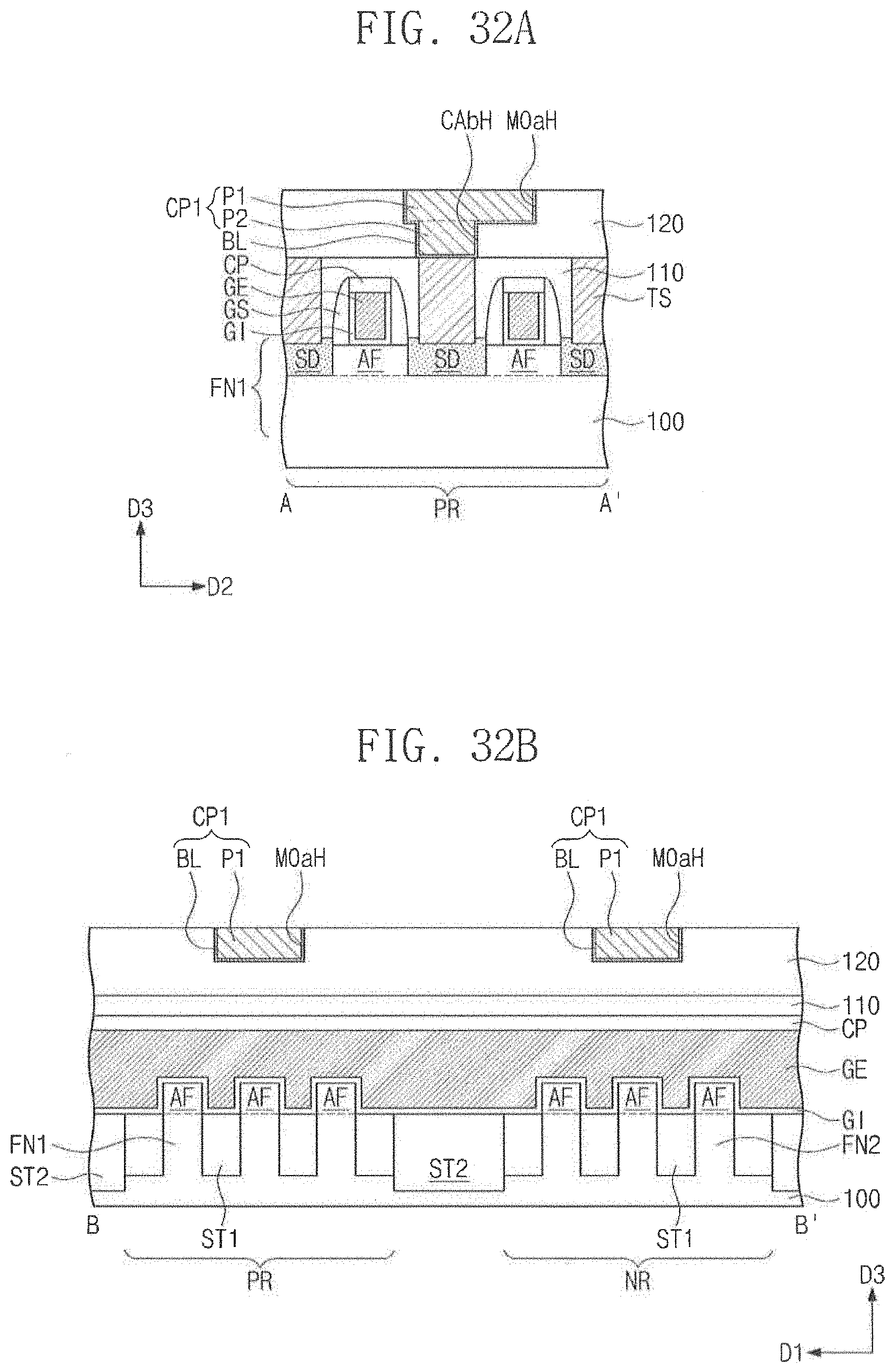

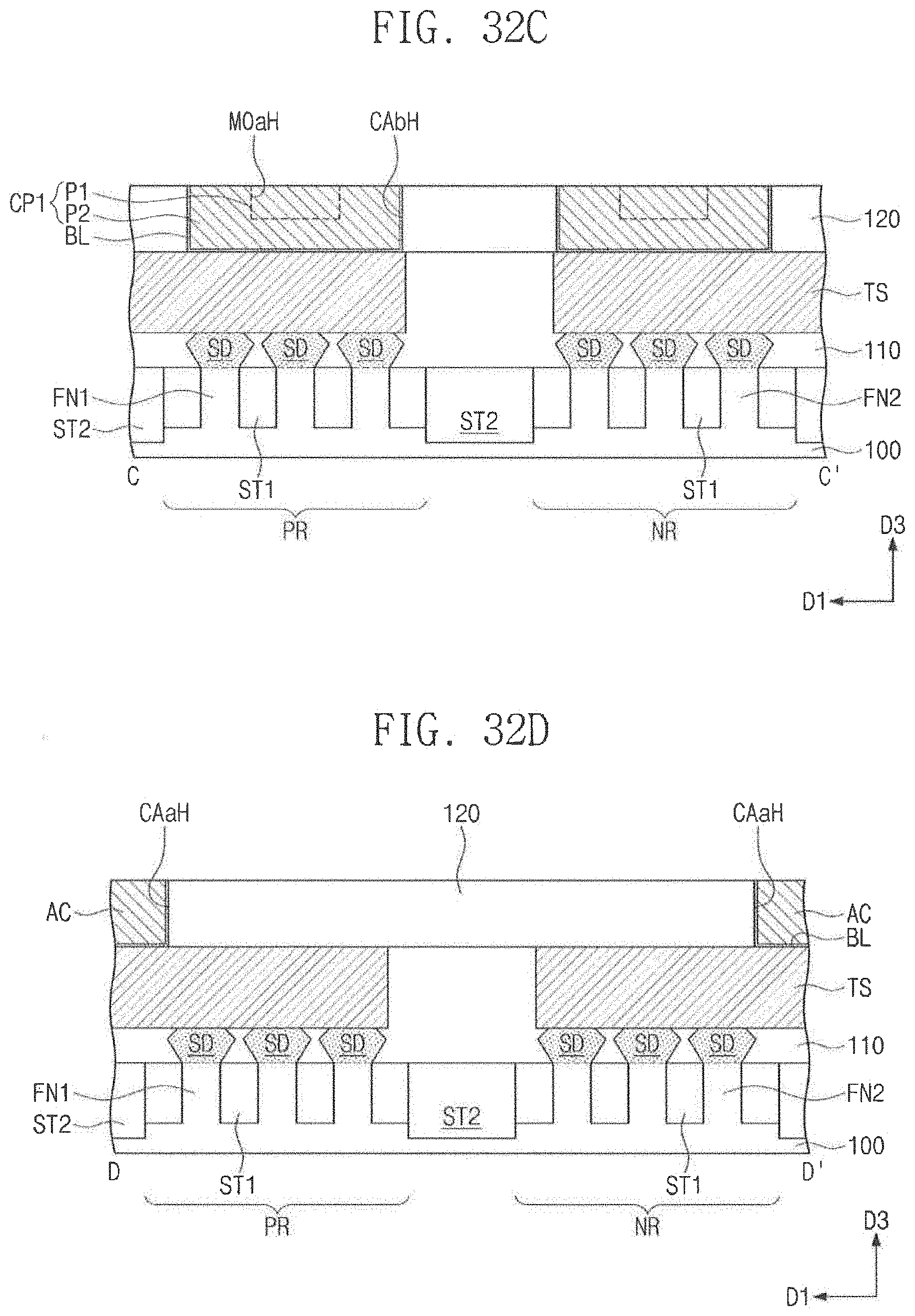

[0032] FIGS. 20A, 22A, 24A, 26A, 28A, 30A, and 32A are sectional views taken along lines A-A' of FIGS. 19, 21, 23, 25, 27, 29, and 31, respectively, according to exemplary embodiments of the preset inventive concept.

[0033] FIGS. 20B, 22B, 24B, 26B, 28B, 30B, and 32B are sectional views taken along lines B-B' of FIGS. 19, 21, 23, 25, 27, 29, and 31, respectively, according to exemplary embodiments of the preset inventive concept.

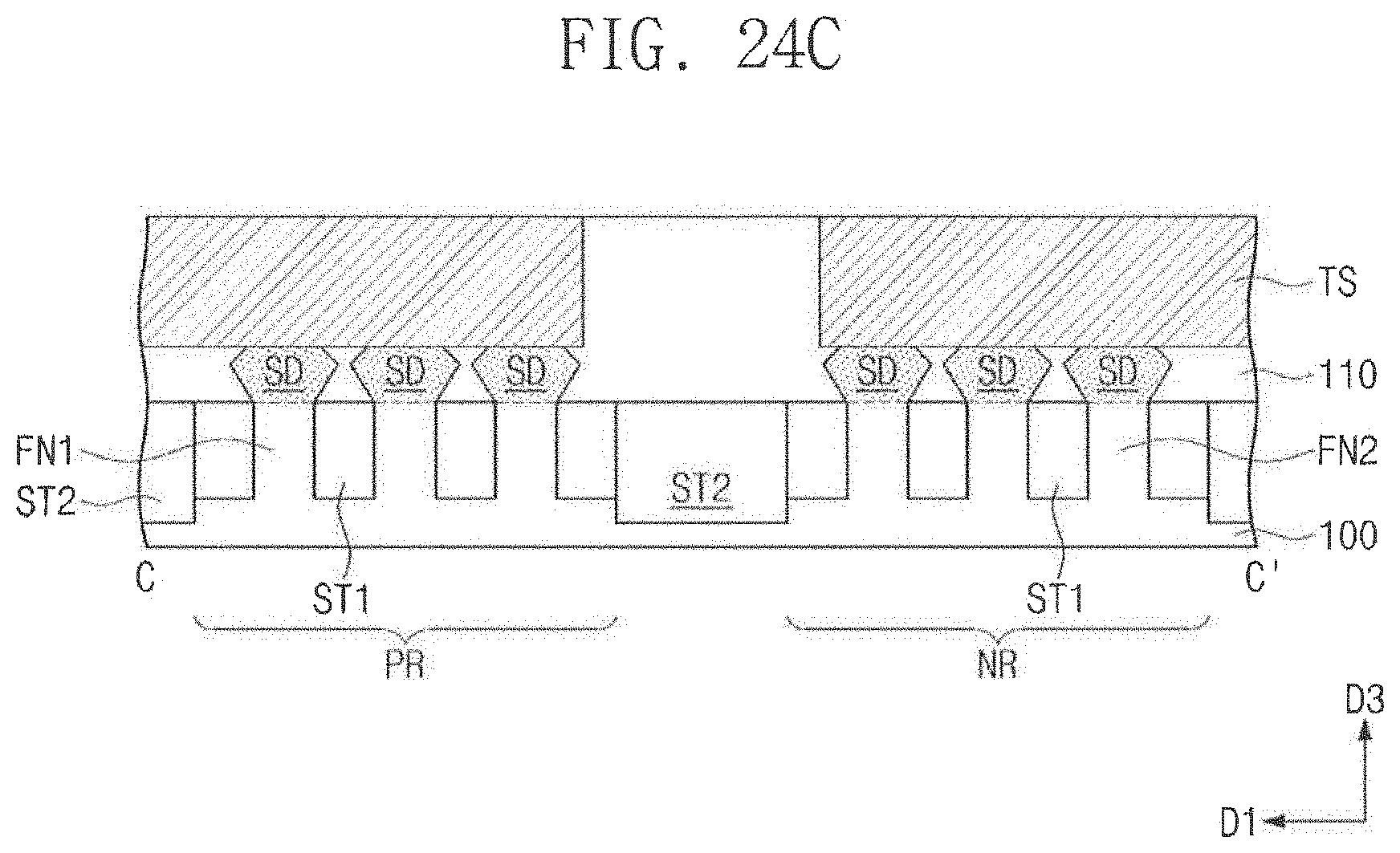

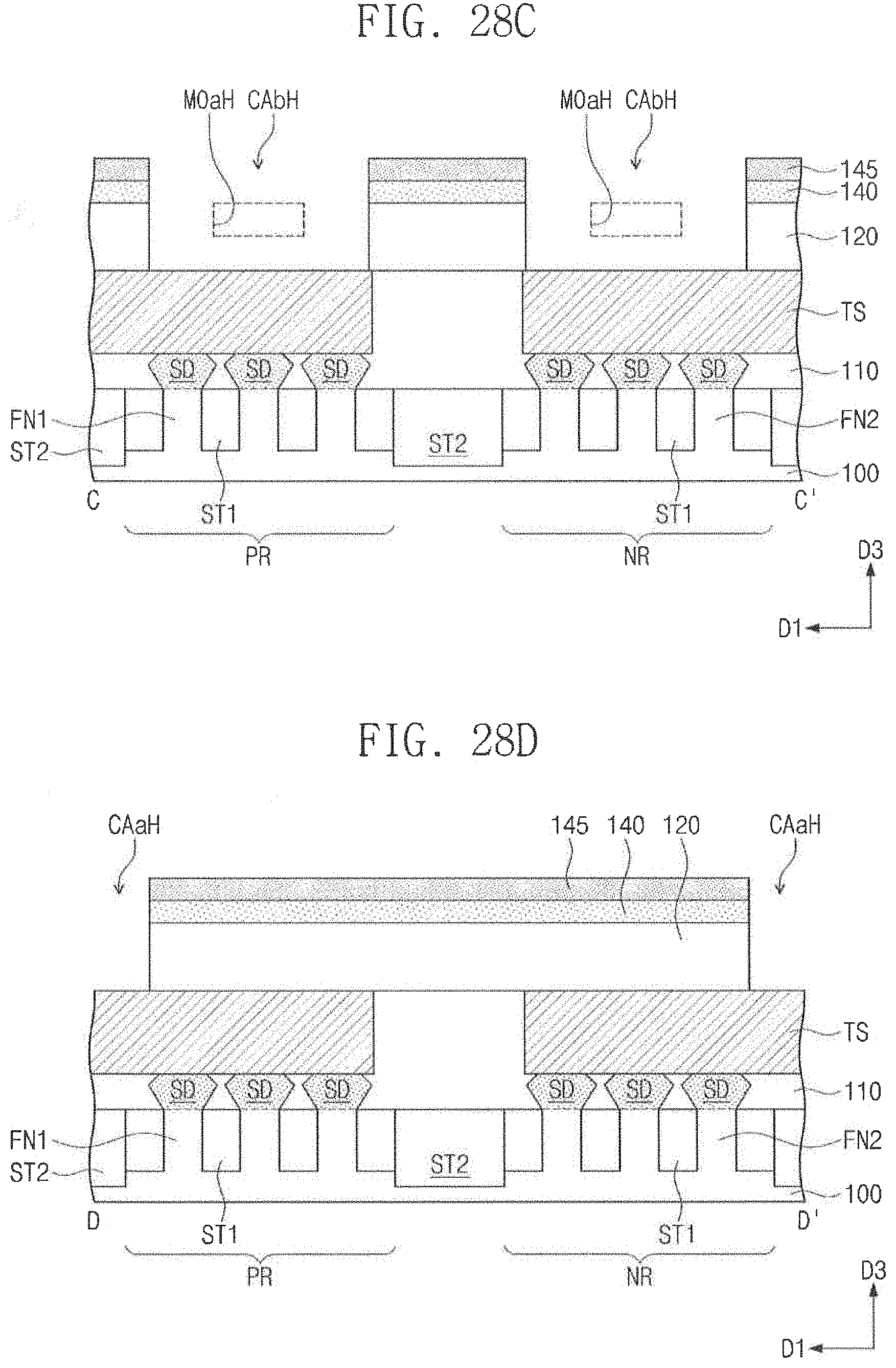

[0034] FIGS. 22C, 24C, 26C, 28C, 30C, and 32C are sectional views taken along lines C-C' of FIGS. 21, 23, 25, 27, 29, and 31, respectively, according to exemplary embodiments of the preset inventive concept.

[0035] FIGS. 28D, 30D, and 32D are sectional views taken along lines D-D' of FIGS. 27, 29, and 31, respectively, according to exemplary embodiments of the preset inventive concept.

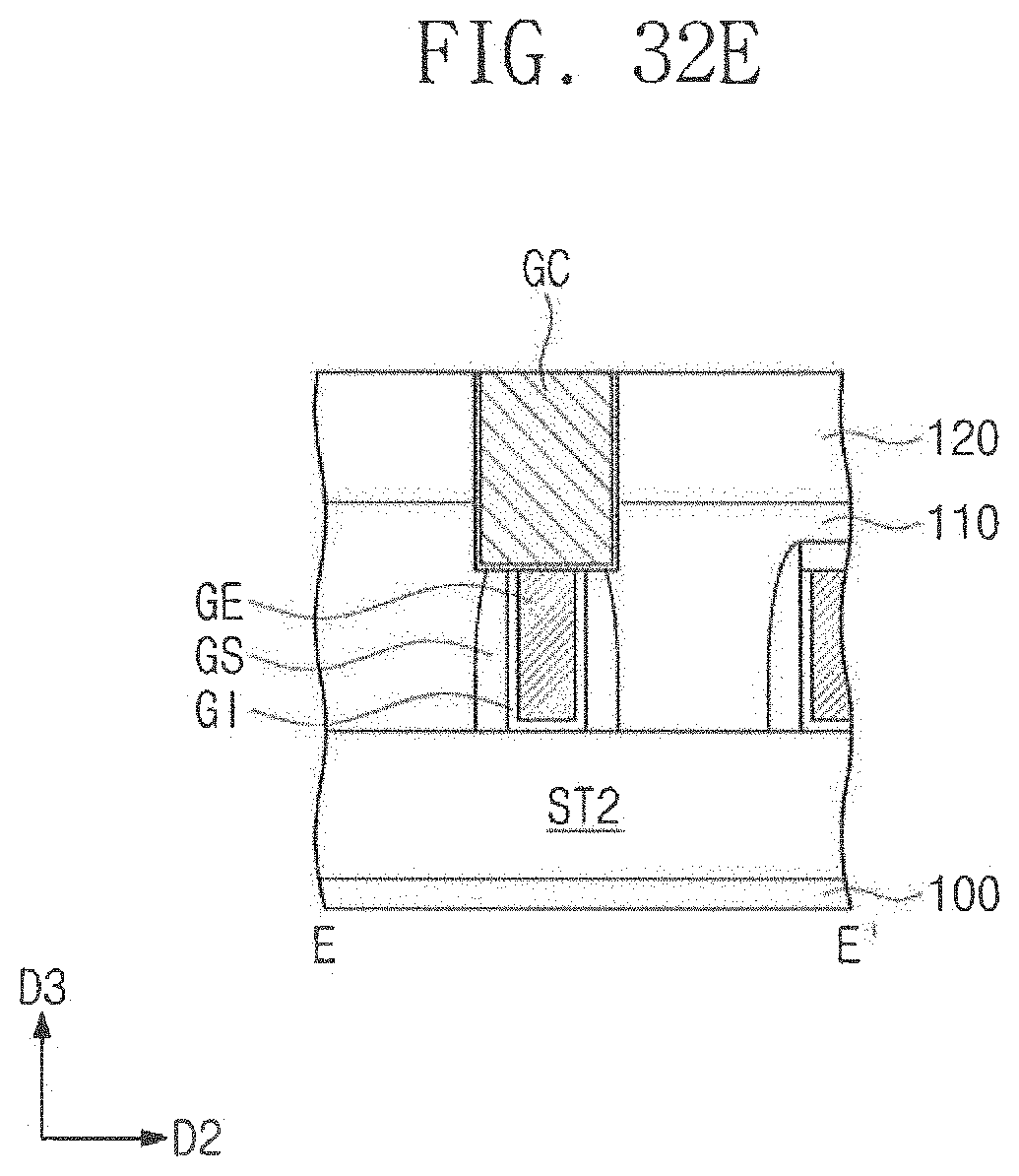

[0036] FIGS. 30E and 32E are sectional views taken along lines E-E' of FIGS. 29 and 31, respectively, according to exemplary embodiments of the preset inventive concept.

[0037] FIG. 33 is a plan view illustrating a semiconductor device that is fabricated based on standard cell layouts according to an exemplary embodiment of the present inventive concept.

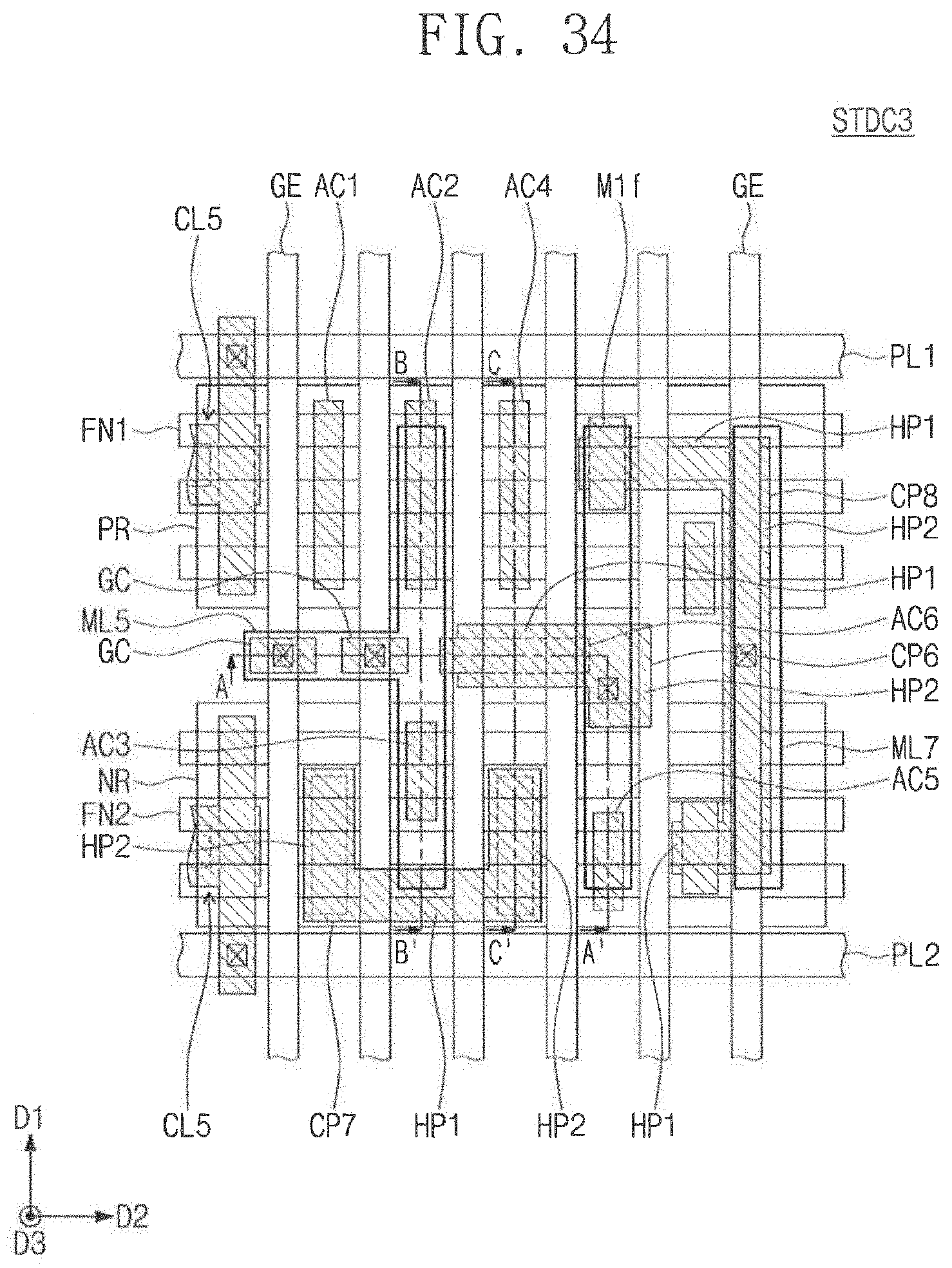

[0038] FIG. 34 is a plan view illustrating a semiconductor device according to exemplary embodiments of the present inventive concept.

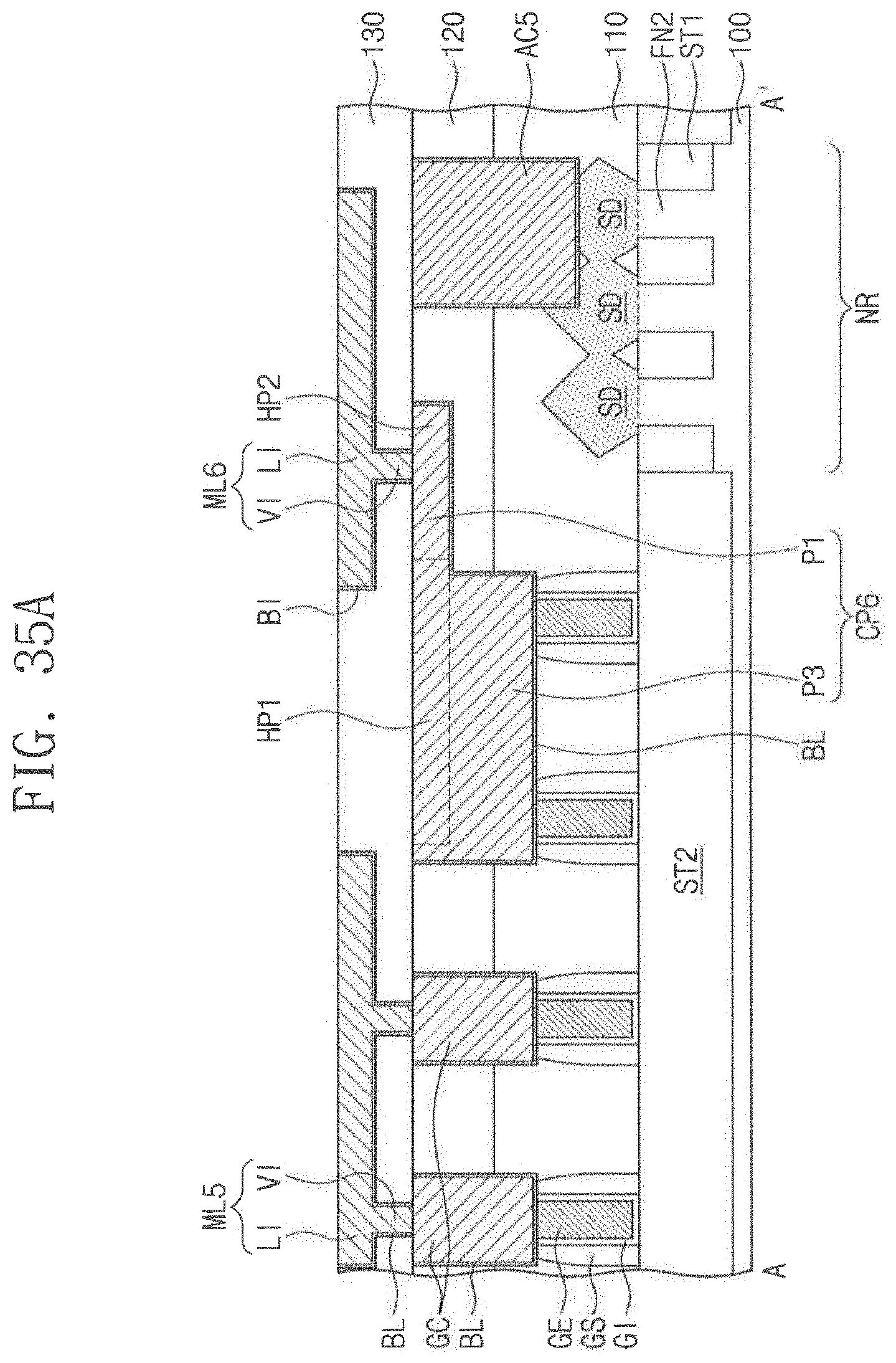

[0039] FIGS. 35A through 35C are sectional views taken along lines A-A', B-B', and C-C' of FIG. 34, respectively, according to exemplary embodiments of the preset inventive concept.

DETAILED DESCRIPTION OF THE EMBODIMENTS

[0040] FIG. 1 is a block diagram illustrating a computer system for performing a semiconductor design process, according to exemplary embodiments of the present inventive concept. Referring to FIG. 1, a computer system may include a central processing unit (CPU) 10, a working memory 30, an input-output device 50, and an auxiliary memory device 70. In exemplary embodiments of the present inventive concept, the computer system may be a customized system for performing a layout design process according to exemplary embodiments of the present inventive concept. Furthermore, the computer system may include a computing system configured to execute various design and check simulation programs.

[0041] The CPU 10 may be configured to run a variety of software, such as application programs, operating systems, and device drivers. For example, the CPU 10 may be configured to run an operating system loaded on the working memory 30. Furthermore, the CPU 10 may be configured to run various application programs on the operating system. For example, the CPU 10 may be configured to run a layout design tool 32 loaded on the working memory 30.

[0042] The operating system or application programs may be loaded on the working memory 30. For example, when the computer system starts a booting operation, an operating system (OS) image stored in the auxiliary memory device 70 may be loaded on the working memory 30 according to a booting sequence. In the computer system, input/output operations may be managed by the operating system. Certain application programs, which may be selected by a user or be provided for basic services, may be loaded on the working memory 30. According to exemplary embodiments of the present inventive concept, the layout design tool 32 prepared for a layout design process may be loaded on the working memory 30, from the auxiliary memory device 70.

[0043] The layout design tool 32 may provide a function for changing biasing data for specific layout patterns. For example, the layout design tool 32 may be configured to allow the specific layout patterns to have shapes and positions different from those defined by a design rule. The layout design tool 32 may be configured to perform a design rule check (DRC) under the changed condition of the biasing data. The working memory 30 may be a volatile memory device (e.g., a static random access memory (SRAM) or dynamic random access memory (DRAM) device) or a nonvolatile memory device (e.g., a phase change random access memory (PRAM), magnetoresistive random access memory (MRAM), resistive random access memory (ReRAM), ferroelectric (FRAM), or NOR FLASH memory device).

[0044] In addition, a simulation tool 34 may be loaded on the working memory 30 to perform an optical proximity correction (OPC) operation on the designed layout data.

[0045] The input-output device 50 may be configured to control user input and output operations of user interface devices. For example, the input-output device 50 may include a keyboard or a monitor, allowing a designer to input relevant information. By using the input-output device 50, the designer may receive information on several regions or data paths, to which adjusted operating characteristics can be applied, of a semiconductor device. The input-output device 50 may be configured to display a progress status or a process result of the simulation tool 34.

[0046] The auxiliary memory device 70 may be a storage medium for the computer system. The auxiliary memory device 70 may be configured to store application programs, an OS image, and various data. The auxiliary memory device 70 may be provided in the form of memory cards (e.g., a multimedia card (MMC), an embedded multimedia card (eMMC), secure digital (SD), MicroSD, and so forth) or a hard disk drive (HDD). The auxiliary memory device 70 may include a NAND FLASH memory device with a large memory capacity. The auxiliary memory device 70 may include nonvolatile memory devices (e.g., PRAM, MRAM, ReRAM, or FRAM) or NOR FLASH memory devices.

[0047] A system interconnector 90 may serve as a system bus for realizing a network in the computer system. The CPU 10, the working memory 30, the input-output device 50, and the auxiliary memory device 70 may be electrically connected to each other through the system interconnector 90, and thus, data may be exchanged therebetween. However, the system interconnector 90 may not be limited to the afore-described configuration. For example, the system interconnector 90 may include an additional element for increasing efficiency in data communication.

[0048] FIG. 2 is a flow chart illustrating a method of designing and fabricating a semiconductor device, according to exemplary embodiments of the present inventive concept.

[0049] Referring to FIG. 2, a high-level design process for a semiconductor integrated circuit may be performed using the computer system described with reference to FIG. 1 (in S110). For example, in the high-level design process, an integrated circuit to be designed may be described in terms of a high-level computer language (e.g., C language). Circuits designed by the high-level design process may be more concretely described by a register transfer level (RTL) coding or a simulation. Furthermore, codes generated by the RTL coding may be converted into a netlist, and the results may be combined with each other to wholly describe a semiconductor device. The combined schematic circuit may be verified by a simulation tool. In exemplary embodiments of the present inventive concept, an adjusting step may be further performed, in consideration of a result of the verification step.

[0050] A layout design process may be performed to realize a logically complete form of the semiconductor integrated circuit on a silicon wafer (in S120). For example, the layout design process may be performed, based on the schematic circuit prepared in the high-level design process or the corresponding netlist. The layout design process may include a routing step of placing and connecting various standard cells that are provided from a cell library, based on a predetermined design rule. A diffusion prevention pattern may be introduced at a boundary of at least one of the standard cells and may be configured to have technical features suitable for electric characteristics of the corresponding standard cell. Such a redesigned standard cell may be provided in the cell library.

[0051] The cell library may contain information on operation, speed, and power consumption of a plurality of cells. In exemplary embodiments of the present inventive concept, a cell library for representing a layout of a circuit in a gate level may be defined in or by the layout design tool. Here, the layout may be prepared to define or describe shapes, positions, or dimensions of patterns constituting transistors and metal interconnection lines, which will be actually formed on a silicon wafer. For example, to actually form an inverter circuit on a silicon wafer, it may be necessary to prepare or draw a layout for patterns (e.g., p-channel metal oxide semiconductor (PMOS), n-channel metal oxide semiconductor (NMOS), N-WELL, gate electrodes, and metal interconnection lines thereon). For this reason, at least one of the inverters defined in the cell library may be selected.

[0052] A routing step of connecting the selected cells to each other may also be performed. For example, the routing step may be performed on the selected and disposed standard cells to connect them to upper interconnection lines. These steps may be automatically or manually performed in the layout design tool. In exemplary embodiments of the present inventive concept, a step of placing the standard cells and establishing routing structures thereto may be automatically performed by a Place & Routing tool.

[0053] After the routing step, a verification step may be performed on the layout to check whether there is a portion violating the design rule. In exemplary embodiments of the present inventive concept, the verification step may include evaluating verification items, such as a design rule check (DRC), an electrical rule check (ERC), and a layout vs. schematic (LVS). The evaluating of the DRC item may be performed to evaluate whether the layout meets the design rule. The evaluating of the ERC item may be performed to evaluate whether there is an issue of electrical disconnection in the layout. The evaluating of the LVS item may be performed to evaluate whether the layout is prepared to coincide with the gate-level netlist.

[0054] An optical proximity correction (OPC) step may be performed (in S130). The OPC step may be performed to correct optical proximity effects, which may occur when a photolithography process is performed on a silicon wafer using a photomask manufactured based on the layout. The optical proximity effect may be an unintended optical effect (such as refraction or diffraction) which may occur in the exposing process using the photomask manufactured based on the layout. In the OPC step, the layout may be modified to have a reduced difference in shape between designed patterns and actually-formed patterns, which may be caused by the optical proximity effects. As a result of the optical proximity correction step, the designed shapes and positions of the layout patterns may be slightly changed.

[0055] A photomask may be manufactured, based on the layout modified by the OPC step (in S140). For example, the photomask may be manufactured by patterning a chromium layer provided on a glass substrate, using the layout pattern data.

[0056] The photomask manufactured may be used to manufacture a semiconductor device (in S150). In the actual fabricating process, the exposing and etching steps may be repeatedly performed, and thus, patterns defined in the layout design process may be sequentially formed on a semiconductor substrate.

[0057] FIG. 3 is a layout diagram illustrating a portion of a standard cell layout according to exemplary embodiments of the present inventive concept.

[0058] Referring to FIG. 3, a standard cell layout may include a layout for an active region AR (hereinafter, also referred to as an active region AR), a layout for a gate electrode GE (hereinafter, also referred to as a gate pattern GP), a layout for a conductive structure CP (hereinafter, also referred to as a conductive pattern CL), a layout for a via (hereinafter, also referred to as via pattern V0), and a layout for an interconnection line ML (hereinafter, also referred to as a conductive line M1).

[0059] The active region AR may be a PMOSFET region or an NMOSFET region. The gate pattern GP may cross the active region AR and extend in a first direction D1. A portion of the active region AR, which is not overlapped with the gate pattern GP, may serve as a source/drain region SD.

[0060] The conductive pattern CL may include a connection pattern M0 and an active contact pattern CA. The active contact pattern CA may be disposed on the active region AR. The active contact pattern CA may be spaced apart from the gate pattern GP in a second direction D2 crossing the first direction D1. The connection pattern M0 and the active contact pattern CA may be partially overlapped with each other. The connection pattern M0 may extend in the second direction D2.

[0061] The via pattern V0 and the conductive line M1 may be disposed on the connection pattern M0. The via pattern V0 may be overlapped with the connection pattern M0 but may be spaced apart from the active contact pattern CA in the second direction D2. The conductive line M1 may be overlapped with the via pattern V0 and may extend in the first direction D1.

[0062] FIG. 4 is a perspective view illustrating a semiconductor device according to exemplary embodiments of the present inventive concept. For example, FIG. 4 is a perspective view illustrating a semiconductor device that is formed based on the layout of FIG. 3.

[0063] Referring to FIG. 4, a substrate 100 with an active pattern FN may be provided. The active pattern FN may be formed in accordance with the active region AR described with reference to FIG. 3. The active pattern FN may include a pair of source/drain regions SD and a channel region AF between the source/drain regions SD.

[0064] A gate electrode GE may be disposed on the channel region AF to cross the active pattern FN. The gate electrode GE may extend in a first direction D1 parallel to a top surface of the substrate 100. The gate electrode GE may be a pattern that is formed in accordance with the gate pattern GP described with reference to FIG. 3. A gate insulating pattern may be interposed between the channel region AF and the gate electrode GE. The gate electrode GE may include doped semiconductor materials, conductive metal nitrides (e.g., titanium nitride or tantalum nitride), or metals (e.g., aluminum or tungsten).

[0065] A conductive structure CP may be provided on at least one of the source/drain regions SD. The conductive structure CP may include a first portion P1 and a second portion P2. The conductive structure CP may be a pattern that is formed in accordance with the conductive pattern CL previously described with reference to FIG. 3. For example, the first portion P1 may be a pattern that is formed in accordance with the connection pattern M0 described with reference to FIG. 3, and the second portion P2 may be a pattern that is formed in accordance with the active contact pattern CA previously described with reference to FIG. 3.

[0066] The second portion P2 may be electrically connected to the source/drain region SD. For example, the second portion P2 may serve as a contact plug that is in direct contact with the source/drain region SD. The second portion P2 may be spaced apart from the gate electrode GE in a second direction D2 crossing the first direction D1. The second portion P2 may extend in the first direction D1.

[0067] The first portion P1 may extend from the second portion P2 in the second direction D2. Furthermore, the first portion P1 may include a first end portion TP1 protruding from at least one sidewall (e.g., a first sidewall SW1) of the second portion P2. The first sidewall SW1 may be a sidewall that extends in the first direction D1 and faces the gate electrode GE. In other words, the first portion P1 may have a shape passing through a top portion of the second portion P2.

[0068] A top surface P1t of the first portion P1 may be substantially coplanar with a top surface P2t of the second portion P2. A bottom surface P1b of the first portion P1 may be positioned at a level higher than that of a bottom surface P2b of the second portion P2. In other words, the bottom surface P1b of the first portion is higher than the bottom surface P2b of the second portion P2 with respect to an upper surface of the substrate 100. In addition, the bottom surface P1b of the first portion P1 may be positioned at a level higher than that of the top surface of the gate electrode GE.

[0069] The first portion P1 and the second portion P2 may be connected to each other to constitute the conductive structure CP, which is provided in the form of a single body. The conductive structure CP may include conductive metal nitrides (e.g., titanium nitride or tantalum nitride) or metals (e.g., aluminum or tungsten).

[0070] An interconnection line ML may be provided on the conductive structure CP. The interconnection line ML may include a line portion LI extending in the first direction D1 and a contact portion VI vertically connecting the line portion LI to the conductive structure CP. The line portion LI may be a pattern that is formed in accordance with the conductive line M1 previously described with reference to FIG. 3, and the contact portion VI may be a pattern that is formed in accordance with the via pattern V0 previously described with reference to FIG. 3. The interconnection line ML may include conductive metal nitrides (e.g., titanium nitride or tantalum nitride) or metals (e.g., aluminum or tungsten).

[0071] When viewed in a plan view, the line portion LI may be spaced apart from the second portion P2 in the second direction D2. However, the line portion LI may be electrically connected to the second portion P2 through the contact portion VI and the first portion P1. In other words, the line portion LI may be electrically connected to the source/drain region SD. As a result, when the line portion LI is horizontally spaced apart from the second portion P2, the line portion LI and the second portion P2 may be electrically connected to each other through the first portion P1. This may allow electrical signals to be input to or output from the source/drain region SD through the interconnection line ML.

[0072] Referring back to FIG. 3, the connection pattern M0 of the conductive pattern CL may be used to increase a degree of freedom in placing the conductive line M1 in a layout design process. As a result, the routing step described with reference to FIG. 2 can be easily performed on a standard cell layout.

[0073] FIG. 5 is a layout diagram illustrating a portion of a standard cell layout according to exemplary embodiments of the present inventive concept. In the following description of the present embodiment, an element previously described with reference to FIG. 3 may not be described in much further detail for the sake of brevity.

[0074] Referring to FIG. 5, a standard cell layout may include an active region AR, a gate pattern GP, a conductive pattern CL, a via pattern V0, and a conductive line M1. The conductive pattern CL may include a connection pattern M0 and a gate contact pattern CB. The gate contact pattern CB may be disposed on the gate pattern GP. The gate contact pattern CB may be overlapped with the connection pattern M0. The connection pattern M0 may have a longitudinal axis that is parallel to a second direction D2.

[0075] The via pattern V0 and the conductive line M1 may be disposed on the connection pattern M0. The via pattern V0 may be overlapped with the connection pattern M0 but may be spaced apart from the gate contact pattern CB in the second direction D2. The conductive line M1 may be overlapped with the via pattern V0 and may extend in a first direction D1.

[0076] FIG. 6 is a perspective view illustrating a semiconductor device according to exemplary embodiments of the present inventive concept. For example, FIG. 6 is a perspective view illustrating a semiconductor device that is formed based on the layout of FIG. 5. In the following description of the present embodiment, an element previously described with reference to FIG. 4 may not be described in much further detail for the sake of brevity.

[0077] Referring to FIG. 6, a conductive structure CP may be disposed on a gate electrode GE. The conductive structure CP may include a first portion P1 and a third portion P3. The third portion P3, not the second portion P2, may be provided in the conductive structure CP, unlike the conductive structure CP previously described with reference to FIG. 4. The first portion P1 may be a pattern that is formed in accordance with the connection pattern M0 previously described with reference to FIG. 5, and the third portion P3 may be a pattern that is formed in accordance with the gate contact pattern CB previously described with reference to FIG. 5.

[0078] The third portion P3 may be electrically connected to the gate electrode GE. For example, the third portion P3 may serve as a contact plug that is in direct contact with the source/drain regions SD. The third portion P3 may be vertically spaced apart from the source/drain regions SD.

[0079] The first portion P1 may be extended from the third portion P3 in a direction opposite to the second direction D2. Furthermore, the first portion P1 may include second end portions TP2 protruding from both sidewalls (e.g., second sidewalls SW2) of the third portion P3. In other words, the first portion P1 may have a line width greater than that of the third portion P3.

[0080] A top surface P1t of the first portion P1 may be substantially coplanar with a top surface P3t of the third portion P3. A bottom surface P1b of the first portion P1 may be higher than a bottom surface P3b of the third portion P3. For example, the bottom surface P1b of the first portion P1 is higher than the bottom surface P3b of the third portion P3 with respect to an upper surface of the substrate 100. Since the bottom surface P3b of the third portion P3 is positioned at substantially the same level as the top surface of the gate electrode GE, the bottom surface P1b of the first portion P1 may be higher than the top surface of the gate electrode GE.

[0081] An interconnection line ML may be provided on the conductive structure CP. When viewed in a plan view, a line portion LI of the interconnection line ML may be spaced apart from the third portion P3 in the second direction D2. However, the line portion LI may be electrically connected to the third portion P3 via a contact portion VI and the first portion P1. For example, the line portion LI may be electrically connected to the gate electrode GE. As a result, when the line portion LI is horizontally spaced apart from the third portion P3, the line portion LI and the third portion P3 may he electrically connected to each other through the first portion P1. This may allow electrical signals to be input or output to or from the gate electrode GE through the interconnection line ML.

[0082] FIG. 7 is a layout diagram illustrating a portion of a standard cell layout according to exemplary embodiments of the present inventive concept. In the following description of the present embodiment, an element previously described with reference to FIGS. 3 and 5 may not be described in much further detail for the sake of brevity.

[0083] Referring to FIG. 7, a standard cell layout may include an active region AR, a gate pattern GP, a conductive pattern CL, a via pattern V0, and a conductive line M1. The conductive pattern CL may include a connection pattern M0, an active contact pattern CA and a gate contact pattern CB.

[0084] The active contact pattern CA may be disposed on the active region AR, and the gate contact pattern CB may be disposed on the gate pattern GP. The active contact pattern CA and the connection pattern M0 may be partially overlapped with each other, and the gate contact pattern CB may be overlapped with the connection pattern M0.

[0085] To reduce complexity in the drawings and to provide better understanding of exemplary embodiments of the inventive concept, the via pattern V0 and the conductive line M1 are not shown in FIG. 7; however, they may be freely disposed on the connection pattern M0, as previously described with reference to FIGS. 3 and 5, for example.

[0086] FIG. 8 is a perspective view illustrating a semiconductor device according to exemplar embodiments of the present inventive concept. For example, FIG. 8 is a perspective view illustrating a semiconductor device that is formed based on the layout of FIG. 7. In the following description of the present embodiment, an element previously described with reference to FIGS. 4 and 6 may not be described in much further detail for the sake of brevity.

[0087] Referring to FIG. 8, a conductive structure CP may be disposed on a substrate 100. The conductive structure CP may include a first portion P1, a second portion P2, and a third portion P3. The second portion P2 may be disposed on and electrically connected to the source/drain region SD, and the third portion P3 may be disposed on and electrically connected to the gate electrode GE. The first portion P1 may extend in a second direction D2 and may connect the second portion P2 and the third portion P3 to each other.

[0088] A top surface P1t of the first portion P1, a top surface P2t of the second portion P2, and a top surface P3t of the third portion P3 may be substantially coplanar with each other. A bottom surface P1b of the first portion P1, a bottom surface P2b of the second portion P2, and a bottom surface P3b of the third portion P3 may be positioned at different heights with respect to an upper surface of the substrate 100. For example, the bottom surface P1b of the first portion P1 may be higher than the bottom surface P3b of the third portion P3, and the bottom surface P3b of the third portion P3 may be higher than the bottom surface P2b of the second portion P2.

[0089] An interconnection line ML, as previously described with reference to FIGS. 3 and 5, may be provided on the conductive structure CP.

[0090] FIG. 9 is a layout diagram illustrating a portion of a standard cell layout according to exemplary embodiments of the present inventive concept. In the following description of the present embodiment, an element previously described with reference to FIG. 3 may not be described in much further detail for the sake of brevity.

[0091] Referring to FIG. 9, a standard cell layout may include an active region AR, a gate pattern GP, a conductive pattern CL, a via pattern V0, and a conductive line M1. The conductive pattern CL may include a connection pattern M0 and a pair of active contact patterns CA.

[0092] The active contact patterns CA may be respectively disposed on opposite portions of the active region AR that are positioned at both sides of the gate pattern GP. Each of the active contact patterns CA may be overlapped with the connection pattern M0. The connection pattern M0 may cross the gate pattern GP and extend in a second direction D2.

[0093] To reduce complexity in the drawings and to provide better understanding of exemplary embodiments of the present inventive concept, the via pattern V0 and the conductive line M1 are not shown in FIG. 9; however, they may be freely disposed on the connection pattern M0, as previously described with reference to FIG. 3, for example.

[0094] FIG. 10 is a perspective view illustrating a semiconductor device according to exemplary embodiments of the present inventive concept. For example, FIG. 10 is a perspective view illustrating a semiconductor device that is formed based on the layout of FIG. 9. In the following description of the present embodiment, an element previously described with reference to FIG. 4 may not be described in much further detail for the sake of brevity.

[0095] Referring to FIG. 10, a conductive structure CP may be disposed on a substrate 100. The conductive structure CP may include a first portion P1 and a pair of second portions P2. The second portions P2 may be disposed on and electrically connected to the source/drain regions SD, respectively, which are disposed at both sides of the gate electrode GE. Here, the first portion P1 may be formed to cross the gate electrode GE and extend in a second direction D2 and may be used to connect the second portions P2 to each other. In other words, the first portion P1 may connect the second portions P2, which are spaced apart from each other with the gate electrode GE interposed therebetween, to each other.

[0096] An interconnection line ML may be provided on the conductive structure CP, as previously described with reference to FIG. 3.

[0097] FIG. 11 is a layout diagram illustrating a portion of a standard cell layout according to exemplary embodiments of the present inventive concept. In the following description of the present embodiment, an element previously described with reference to FIG. 5 may not be described in much further detail for the sake of brevity.

[0098] Referring to FIG. 11, a standard cell layout may include an active region AR, gate patterns GP, a conductive pattern CL, a via pattern V0, and a conductive line M1. The conductive pattern CL may include a connection pattern M0 and a pair of gate contact patterns CB.

[0099] The gate contact patterns CB may be disposed on the gate patterns GP, respectively. The gate contact patterns CB may be overlapped with the connection pattern M0. The connection pattern M0 may cross the gate patterns GP and extend in a second direction D2.

[0100] To reduce complexity in the drawings and to provide better understanding of exemplary embodiments of the present inventive concept, the via pattern V0 and the conductive line M1 are not shown in FIG. 11; however, they may be freely disposed on the connection pattern M0, as previously described with reference to FIG. 5, for example.

[0101] FIG. 12 is a perspective view illustrating a semiconductor device according to exemplary embodiments of the present inventive concept. For example, FIG. 12 is a perspective view illustrating a semiconductor device that is formed based on the layout of FIG. 11. In the following description of the present embodiment, an element previously described with reference to FIG. 6 may not be described in much further detail for the sake of brevity.

[0102] Referring to FIG. 12, a conductive structure CP may be disposed on gate electrodes GE that are formed on a substrate 100. The conductive structure CP may include a first portion P1 and a pair of third portions P3. The third portions P3 may be electrically connected to the gate electrodes GE, respectively. Here, the first portion P1 may extend in a second direction D2 to cross the gate electrodes GE, and the third portions P3 may be connected to each other by the first portion P1.

[0103] An interconnection line ML may be provided on the conductive structure CP, as previously described with reference to FIG. 3.

[0104] FIG. 13 is a layout diagram including standard cell layouts according to exemplary embodiments of the present inventive concept. In the following description of the present embodiment, an element previously described with reference to FIGS. 3, 5, 7, 9, and 11 may not be described in much further detail for the sake of brevity.

[0105] Referring to FIG. 13, a layout design tool may be used to dispose standard cell layouts side by side. As an example, the standard cell layouts may include first to third standard cell layouts STD1, STD2, and STD3. The first to third standard cell layouts STD1, STD2, and STD3 may be arranged in a second direction D2. Each of the first to third standard cell layouts STD1, STD2, and STD3 may include a logic layout for logic transistors, an interconnection line layout for interconnection lines provided on the logic transistors, and a contact layout for contacts connecting the logic transistors and the interconnection lines to each other.

[0106] The logic layout may include active layouts for active regions. The active layouts may include a PMOSFET region PR and an NMOSFET region NR. The PMOSFET region PR and the NMOSFET region NR may be spaced apart from each other in a first direction D1 crossing the second direction D2.

[0107] The logic layout may include layouts (e.g., gate patterns GP) for gate electrodes, which extend in the first direction D1 and cross the PMOSFET region PR and the NMOSFET region NR. The gate patterns GP may be spaced apart from each other in the second direction D2. The PMOSFET region PR, the NMOSFET region NR, and the gate patterns GP may constitute logic transistors provided on a semiconductor substrate 100.

[0108] The contact layout may include layouts (e.g., lower conductive patterns LP) for a lower conductive structure overlapped with or connected to each of the PMOSFET region PR and the NMOSFET region NR, layouts (e.g., connection patterns M0a-M0h) for connection patterns M0, layouts (e.g., active contact patterns CAa-CAl) for an active contact AC overlapped with or connected to the lower conductive patterns LP, and layouts (e.g., gate contact patterns CBa-CBh) for gate contacts GC overlapped with or connected to the gate patterns GP. Each of the connection patterns M0a-M0h may be overlapped with or connected to at least one of the active contact patterns CAa-CAl and the gate contact patterns CBa-CBh. In addition, layouts (e.g., conductive patterns CL1-CL8) for a conductive structure CP may be defined in the contact layout. The conductive patterns CL1-CL8 may include first to eighth conductive patterns CL1-CL8.

[0109] The interconnection line layout may include layouts (e.g., via patterns V0) for via patterns, layouts (e.g., conductive lines M1a-M1g) for interconnection lines, and layouts (e.g., power lines PM1 and PM2) for power interconnection lines. Each of the first and second power lines PM1 and PM2 may be a line-shaped structure extending in the second direction D2. The first and second power lines PM1 and PM2 may be connected to some of the active contact patterns CAa-CAl through the via patterns V0. The conductive lines M1a-M1g may be connected to some of the connection patterns M0a-M0h, some of the active contact patterns CAa-CAl, and some of the gate contact patterns CBa-CBh through the via patterns V0.

[0110] The first standard cell layout STD1 will now be described. For example, first active contact patterns CAa may be provided to be overlapped with the first and second power lines PM1 and PM2, respectively. The first and second power lines PM1 and PM2 may be respectively connected to the first active contact patterns CAa through the via patterns V0. A first gate contact pattern CBa may be provided to be overlapped with at least one of the gate patterns GP. The first conductive line M1a may be connected to the first gate contact pattern CBa through the via pattern V0.

[0111] A pair of first conductive patterns CL1 may be disposed to be adjacent to the first conductive line M1a. The pair of first conductive patterns CL1 may be disposed on the PMOSFET region PR and the NMOSFET region NR, respectively. Each of the first conductive patterns CL1 may include a second active contact pattern CAb and a first connection pattern M0a. The second active contact pattern CAb and the first connection pattern M0a may be partially overlapped with each other. A second conductive line M1b may be connected to the pair of first conductive patterns CL1, respectively, through the via patterns V0.

[0112] A pair of second conductive patterns CL2 may be disposed on a boundary between the first standard cell layout STD1 and the second standard cell layout STD2. The pair of second conductive patterns CL2 may be disposed on the PMOSFET region PR and the NMOSFET region NR, respectively. Each of the second conductive patterns CL2 may include a second gate contact pattern CBb, a second connection pattern M0b, and a third active contact pattern CAc. The second gate contact pattern CBb may be overlapped with the second connection pattern M0b. The third active contact pattern CAc and the second connection pattern M0b may be partially overlapped with each other. However, the second gate contact pattern CBb and the third active contact pattern CAc may be spaced apart from each other in the second direction D2. The first and second power lines PM1 and PM2 may be connected to the pair of second conductive patterns CL2, respectively, through the via patterns V0.

[0113] The second standard cell layout STD2 will now be described. A pair of third conductive patterns CL3 may be disposed on the substrate 100. The pair of third conductive patterns CL3 may be disposed on the PMOSFET region PR and the NMOSFET region NR, respectively. Each of the third conductive patterns CL3 may include a fourth active contact pattern CAd, a fifth active contact pattern CAe, and a third connection pattern M0c. The fourth and fifth active contact patterns CAd and CAe may be spaced apart from each other in the second direction D2 with the gate pattern GP interposed therebetween. The third connection pattern M0c may cross the gate pattern GP and extend in the second direction D2. The fourth active contact pattern CAd and the third connection pattern M0c may be partially overlapped with each other, and the fifth active contact pattern CAe and the third connection pattern M0c may be partially overlapped with each other.

[0114] A fourth conductive pattern CL4 may be disposed to be adjacent to the pair of third conductive patterns CL3. The fourth conductive pattern CL4 may be disposed between the PMOSFET region PR and the NMOSFET region NR. The fourth conductive pattern CL4 may include a third gate contact pattern CBc, a fourth gate contact pattern CBd, and a fourth connection pattern M0d. The third and fourth gate contact patterns CBc and CBd may each be overlapped with adjacent gate patterns GP. The fourth connection pattern M0d may cross the gate patterns GP and extend in the second direction D2. The third and fourth gate contact patterns CBc and CBd may be overlapped with the fourth connection pattern M0d. A third conductive line M1c may be connected to the fourth conductive pattern CL4 through the via pattern V0.

[0115] A pair of sixth active contact patterns CAf may be disposed between the gate patterns GP connected to the third and fourth gate contact patterns CBc and CBd, respectively. The pair of sixth active contact patterns CAf may be disposed on the PMOSFET region PR and the NMOSFET region NR, respectively. A fourth conductive line M1d may be connected to the pair of sixth active contact patterns CAf through the via patterns V0.

[0116] If the fourth connection pattern M0d is omitted, the third and fourth conductive lines M1c and M1d may not be formed in the shapes and positions shown in FIG. 13. For example, the first and second conductive lines M1a and M1b may have shapes and positions similar to those shown in FIG. 14B.

[0117] A pair of fifth conductive patterns CL5 may be disposed on a boundary between the second standard cell layout STD2 and the third standard cell layout STD3. The pair of fifth conductive patterns CL5 may be disposed on the PMOSFET region PR and the NMOSFET region NR, respectively. Each of the fifth conductive patterns CL5 may include a seventh active contact pattern CAg, a fifth connection pattern M0e, a fifth gate contact pattern CBe, and an eighth active contact pattern CAh. The fifth gate contact pattern CBe may be overlapped with the fifth connection pattern M0e. The seventh active contact pattern CAg and the fifth connection pattern M0e may be partially overlapped with each other, and the eighth active contact pattern CAh and the fifth connection pattern M0e may be partially overlapped with each other. The seventh and eighth active contact patterns CAg and CAh and the fifth gate contact pattern CBe may be spaced apart from each other in the second direction D2. The eighth active contact pattern CAh may extend in the first direction D1 and may be partially overlapped with the power lines PM1 and PM2. The first and second power lines PM1 and PM2 may be connected to the pair of fifth conductive patterns CL5, respectively, through the via patterns V0.

[0118] The third standard cell layout STD3 will now be described. For example, a sixth gate contact pattern CBf and a seventh gate contact pattern CBg may be provided on the substrate 100. The sixth and seventh gate contact patterns CBf and CBg may be disposed between the PMOSFET region PR and the NMOSFET region NR. The sixth and seventh gate contact patterns CBf and CBg may be respectively overlapped with the gate patterns GP that are adjacent to each other. Furthermore, the sixth and seventh gate contact patterns CBf and CBg may be overlapped with a fifth conductive line M1e. The fifth conductive line M1e may include a first portion, which is overlapped with the sixth and seventh gate contact patterns CBf and CBg and extends in the second direction D2, and a second portion extending in the first direction D1. The fifth conductive line M1e may be connected to the sixth and seventh gate contact patterns CBf and CBg through the via patterns V0.

[0119] A sixth conductive pattern CL6 may be disposed to be adjacent to the fifth conductive line M1e. The sixth conductive pattern CL6 may be disposed between the PMOSFET region PR and the NMOSFET region NR. The sixth conductive pattern CL6 may include an eighth gate contact pattern CBh and a sixth connection pattern M0f. The eighth gate contact pattern CBh may extend in the second direction D2 and may be overlapped with a pair of the gate patterns GP that are adjacent to each other. The sixth connection pattern M0f may include a first portion, which extends in the second direction D2 and is overlapped with the eighth gate contact pattern CBh, and a second portion extending in the first direction D1. The second portion of the sixth connection pattern M0f may be overlapped with the sixth conductive line M1f. The sixth conductive line M1f may be connected to the sixth conductive pattern CL6 through the via pattern V0.

[0120] A seventh conductive pattern CL7 may be provided on the NMOSFET region NR. The seventh conductive pattern CL7 may include a ninth active contact pattern CAi, a tenth active contact pattern CAj, and a seventh connection pattern M0g. The ninth and tenth active contact patterns CAi and CAj may be spaced apart from each other in the second direction D2 with the gate patterns GP interposed therebetween. The seventh connection pattern M0g may include a first portion, which extends in the first direction D1 and is overlapped with the ninth active contact pattern CAi, a second portion, which extends in the first direction D1 and is overlapped with the tenth active contact pattern CAj, and a third portion, which extends in the second direction D2 and crosses the gate patterns GP.

[0121] An eighth conductive pattern CL8 may be disposed to be adjacent to the sixth conductive pattern CL6. The eighth conductive pattern CL8 may extend from the PMOSFET region PR to the NMOSFET region NR. The eighth conductive pattern CL8 may include an eleventh active contact pattern CAk, a twelfth active contact pattern CAl, and an eighth connection pattern M0h. The eleventh and twelfth active contact patterns CAk and CAl may be disposed on the PMOSFET region PR and the NMOSFET region NR, respectively. The eleventh active contact pattern CAk may be overlapped with the sixth conductive line M1f. The eighth connection pattern M0h may include a first portion, which extends in the second direction D2 and is overlapped with the eleventh active contact pattern CAk, a second portion, which extends in the second direction D2 and is overlapped with the twelfth active contact pattern CAl, and a third portion, which extends in the first direction D1 and connects the first and second portions to each other. The first portion of the eighth connection pattern M0h may cross at least one of the gate patterns GP. Furthermore, the eighth connection pattern M0h and a seventh conductive line M1g may be partially overlapped with each other. The seventh conductive line M1g may be connected to the eighth connection pattern M0h through the via pattern V0.

[0122] In the pair of first conductive patterns CL1 described above, a pair of the second active contact patterns CAb may be connected to each other through the first connection patterns M0a and the second conductive line M1b. In the eighth conductive pattern CL8, the eleventh and twelfth active contact patterns CAk and CAl may be electrically connected to each other through only the eighth connection pattern M0h.

[0123] So far, examples of the first to eighth conductive patterns CL1-CL8, which are disposed on the first to third standard cell layouts STD1, STD2, and STD3, have been described. However, the inventive concept may not be limited thereto. For example, the active contact patterns, the gate contact patterns, and the connection patterns may be changed in terms of their shapes and positions and may be connected to each other in various manners.

[0124] FIG. 14A is a layout diagram illustrating a region `M` of FIG. 13 according to exemplary embodiments of the present inventive concept. FIG. 14B is a layout diagram illustrating the region `M` of FIG. 13 according to a comparative example.

[0125] Referring to FIG. 14A, the first gate contact pattern CBa, the pair of first conductive patterns CL1, and the first and second conductive lines M1a and M1b that have been previously described with reference to FIG. 13 may be disposed on the substrate 100. The first conductive line M1a may be connected to the first gate contact pattern CBa through a via pattern V0. Each of the first conductive patterns CL1 may include a second active contact pattern CAb and a first connection pattern M0a. The first connection pattern M0a and the second conductive line M1b may be partially overlapped with each other. Accordingly, the second conductive line M1b may be connected to the pair of the first connection patterns M0a through the via patterns V0.

[0126] Each of the first and second conductive lines M1a and M1b may include pin regions PI for establishing routing paths to upper interconnection lines. As an example, each of the first and second conductive lines M1a and M1b may include five pin regions PI, which are arranged parallel to its longitudinal axis or in the first direction D1. In other words, the first and second conductive lines M1a and M1b may include ten pin regions PI.

[0127] Referring to FIG. 14B, a first gate contact pattern CBa, a pair of second active contact patterns CAb, and first and second conductive lines M1a and M1b may be disposed on a substrate. However, unlike that of FIG. 14A, the first connection patterns M0a are not included. The second conductive line M1b may include a first portion extending in a first direction D1 and second portions, which extend in a second direction D2 and are overlapped with the pair of second active contact patterns CAb, respectively. The second conductive line M1b may be connected to the pair of second active contact patterns CAb through via patterns V0.

[0128] Each of the first and second conductive lines M1a and M1b may include pin regions PI for establishing routing paths to upper interconnection lines. Due to the second portions of the second conductive line M1b, a length of the first conductive line M1a in the first direction D1 may be shorter than that of the first conductive line M1a of FIG. 14A. Thus, the first conductive line M1a may include, for example, three pin regions PI, and the second conductive line M1b may include five pin regions PI. As a result, the first and second conductive lines M1a and M1b may include eight pin regions PI. In other words, the number of the pin regions PI on the first and second conductive lines M1a and M1b may be less than that in the embodiment described with reference to FIG. 14A.

[0129] FIG. 15A is a layout diagram illustrating a region `N` of FIG. 13 according to exemplary embodiments of the present inventive concept. FIG. 15B is a layout diagram illustrating the region `N` of FIG. 13 according to a comparative example.

[0130] Referring to FIG. 15A, the sixth conductive pattern CL6, the eighth conductive pattern CL8, and the sixth and seventh conductive lines M1f and M1g previously described with reference to FIG. 13 may be disposed on the substrate 100. The sixth conductive pattern CL6 may include an eighth gate contact pattern CBh and a sixth connection pattern M0f. The eighth conductive pattern CL8 may include an eleventh active contact pattern CAk, a twelfth active contact pattern CAl, and an eighth connection pattern M0h. The sixth connection pattern M0f and the sixth conductive line M1f may be partially overlapped with each other, and the eighth connection pattern M0h and the seventh conductive line M1g may be partially overlapped with each other. Accordingly, the sixth conductive line M1f may be connected to the sixth connection pattern M0f through the via pattern V0, and the seventh conductive line M1g may be connected to the eighth connection pattern M0h through the via pattern V0.

[0131] Each of the sixth and seventh conductive lines M1f and M1g may include pin regions PI for establishing routing paths to upper interconnection lines. As an example, each of the sixth and seventh conductive lines M1f and M1g may include five pin regions PI, which are arranged parallel to its longitudinal axis or in the first direction D1. In other words, the sixth and seventh conductive lines M1f and M1g may include ten pin regions PI.

[0132] Referring to FIG. 15B, a sixth conductive pattern CL6, an eleventh active contact pattern CAk, a twelfth active contact pattern CAl, and sixth and seventh conductive lines M1f and M1g may be disposed on a substrate. However, unlike that of FIG. 15A, the eighth connection pattern M0h is not included. The seventh conductive line M1g may include a first portion extending in a first direction D1 and second portions, which extend in a second direction D2 and are overlapped with the eleventh and twelfth active contact patterns CAk and CAl, respectively. The seventh conductive line M1g may be connected to each of the eleventh and twelfth active contact patterns CAk and CAl through via patterns V0.

[0133] Each of the sixth and seventh conductive lines M1f and M1g may include pin regions PI for establishing routing paths to upper interconnection lines. Due to the second portions of the seventh conductive line M1g, a length of the sixth conductive line M1f in the first direction D1 may be shorter than that of the sixth conductive line M1f of FIG. 15A. Thus, the sixth conductive line M1f may include, for example, three pin regions PI, and the seventh conductive line M1g may include five pin regions PI. As a result, the sixth and seventh conductive lines M1f and M1g may include eight pin regions PI. In other words, the number of the pin regions PI on the sixth and seventh conductive lines M1f and M1g may be less than that in the embodiment described with reference to FIG. 15A.

[0134] As described with reference to FIGS. 14 and 15, a standard cell layout according to exemplary embodiments of the present inventive concept may include an additional connection pattern, as well as an active contact pattern and a gate contact pattern. Thus, it is possible to increase a degree of freedom in placing a layout for interconnection lines or conductive lines and to increase an area of pin regions for establishing routing paths to upper interconnection lines. In other words, the connection pattern makes it possible to more easily construct a routing structure.

[0135] FIG. 16 is a plan view illustrating a semiconductor device according to exemplary embodiments of the present inventive concept. FIGS. 17A through 17R are sectional views taken along lines A-A', B-B', C-C', D-D', E-E', F-F', G-G', H-H', I-I', J-J', K-K', L-L', M-M', N-N', O-O', P-P', Q-Q', and R-R', respectively, of FIG. 16. For example, FIG. 16 and FIGS. 17A through 17R illustrate an example of a semiconductor device that is formed based on the standard cell layouts of FIG. 13. In the following description of the present embodiment, an element previously described with reference to FIGS. 4, 6, 8, 10, and 12 may not be described in much further detail for the sake of brevity.

[0136] In a semiconductor device to be described with reference to FIGS. 16 and 17A to 17R, each element of the semiconductor device may be integrated on a semiconductor substrate 100 through the photolithography process S150 of FIG. 2, and thus, they may not be identical to corresponding patterns constituting the standard cell layout of FIG. 13. The semiconductor device may be, for example, a system-on-chip.

[0137] Referring to FIGS. 16 and 17A to 17R, second device isolation patterns ST2 may be provided on a substrate 100 to define a PMOSFET region PR and an NMOSFET region NR. The second device isolation patterns ST2 may be provided in an upper portion of the substrate 100. In exemplary embodiments of the present inventive concept, the substrate 100 may be a silicon substrate, a germanium substrate, or a silicon-on-insulator (SOI) substrate.

[0138] The PMOSFET and NMOSFET regions PR and NR may be spaced apart from each other, in a first direction D1 parallel to a top surface of the substrate 100, by the second device isolation patterns ST2 interposed therebetween. Although each of the PMOSFET and NMOSFET regions PR and NR is illustrated to be a single region, each of the PMOSFET and NMOSFET regions PR and NR may include a plurality of regions spaced apart from each other by the second device isolation patterns ST2.

[0139] A plurality of first active patterns FN1 may be provided on the PMOSFET region PR to extend in a second direction D2 crossing the first direction D1, and a plurality of second active patterns FN2 may be provided on the NMOSFET region NR to extend in the second direction D2. The first and second active patterns FN1 and FN2 may be parts of the substrate 100 and may have a protruding shape. In other words, they may protrude from the substrate 100. The first and second active patterns FN1 and FN2 may be arranged in the first direction D1. First device isolation patterns ST1 extending in the second direction D2 may be disposed at both sides of each of the first and second active patterns FN1 and FN2.

[0140] Between the first device isolation patterns ST1, upper portions of the first and second active patterns FN1 and FN2 may vertically protrude with respect to the first device isolation patterns ST1. In other words, each of the upper portions of the first and second active patterns FN1 and FN2 may have a fin-shaped structure, between the first device isolation patterns ST1.

[0141] The second device isolation patterns ST2 may be substantially connected to the first device isolation patterns ST1 to form a single insulating pattern. The second device isolation patterns ST2 may be thicker than the first device isolation patterns ST1. In this case, the first device isolation patterns ST1 and the second device isolation patterns ST2 may be formed by different processes. As an example, the first and second device isolation patterns ST1 and ST2 may be formed of or include a silicon oxide layer.

[0142] Gate electrodes GE may be provided on the first and second active patterns FN1 and FN2 to extend in the first direction D1 and to cross the first and second active patterns FN1 and FN2. The gate electrodes GE may be spaced apart from each other in the second direction D2. Each of the gate electrodes GE may extend in the first direction D1 and cross the PMOSFET region PR, the second device isolation patterns ST2, and the NMOSFET region NR.

[0143] In exemplary embodiments of the present inventive concept, dummy gate electrodes DM may be respectively provided on a boundary between a first standard cell STDC1 and a second standard cell STDC2 and on a boundary between the second standard cell STDC2 and a third standard cell STDC3. Each of the dummy gate electrodes DM may be divided into two electrodes, by the second device isolation pattern ST2, but the present inventive concept may not be limited thereto. The dummy gate electrodes DM may have substantially the same structure as the gate electrodes GE and may be formed of substantially the same material as the gate electrodes GE. In a circuit, the dummy gate electrodes DM may serve as a conductive line, of a transistor.

[0144] A gate insulating pattern GI may be provided below each of the gate electrodes GE, and gate spacers GS may be provided at both sides of each of the gate electrodes GE. Furthermore, a capping pattern CP may be provided to cover a top surface of each of the gate electrodes GE. However, in exemplary embodiments of the present inventive concept, the capping pattern CP may be partially removed from a portion of the top surface of the gate electrode GE, to which a gate contact GC to be described below is connected. The gate insulating pattern GI may be vertically extended to cover both sidewalls of the gate electrode GE. For example, the gate insulating pattern GI may be interposed between the gate electrode GE and the gate spacer GS. First to third interlayer insulating layers 110-130 may be provided to cover the first and second active patterns FN1 and FN2 and the gate electrodes GE.

[0145] The gate electrodes GE may be formed of or include doped semiconductor materials, conductive metal nitrides, or metals. The gate insulating pattern GI may be formed of or include a silicon oxide layer, a silicon oxynitride layer, or high-k dielectric materials, whose dielectric constants are lower than that of silicon oxide. Each of the capping pattern CP and the gate spacers GS may include a silicon oxide layer, a silicon nitride layer, or a silicon oxynitride layer. Each of the first to third interlayer insulating layers 110-130 may include a silicon oxide layer or a silicon oxynitride layer.

[0146] Source/drain regions SD may be provided on or in the upper portions of the first and second active patterns FN1 and FN2. The source/drain regions SD on the PMOSFET region PR may be p-type impurity regions, and the source/drain regions SD on the NMOSFET region NR may be n-type impurity regions. Channel regions AF may be provided in the upper portion of each of the first and second active patterns FN1 and FN2 that are overlapped with the gate electrodes GE, respectively. Each of the channel regions AF may be interposed between the source/drain regions SD.

[0147] The source/drain regions SD may be epitaxial patterns formed by a selective epitaxial growth process. Accordingly, the source/drain regions SD may have top surfaces positioned at a higher level than those of the channel regions AF. The source/drain regions SD may include a semiconductor element different from those of the substrate 100. As an example, the source/drain regions SD may be formed of or include a semiconductor material having a lattice constant different from (for example, greater or smaller than) the substrate 100. Accordingly, the source/drain regions SD may exert a compressive stress or a tensile stress on the channel regions AF.

[0148] Lower conductive structures TS may be provided on the PMOSFET and NMOSFET regions PR and NR between the gate electrodes GE. The lower conductive structures TS may be a pattern that is formed in accordance with the lower conductive patterns LP of FIG. 13. The lower conductive structures TS may be provided in the first interlayer insulating layer 110 and may be directly connected to the source/drain regions SD. The lower conductive structures TS may extend in the first direction D1. Each of the lower conductive structures TS may be partially overlapped with a first or second power interconnection line PL1 or PL2, when viewed in a plan view. The lower conductive structures TS may have top surfaces that are substantially coplanar with that of the first interlayer insulating layer 110. In the present embodiment, each of the lower conductive structures TS are illustrated to be in contact with a plurality of the source/drain regions SD, but the present inventive concept may not be limited thereto. As an example, at least one of the lower conductive structures TS may be in contact with one or two of the source/drain regions SD. The lower conductive structures TS may be formed of or include doped semiconductor materials, conductive metal nitrides, metals, or metal silicides.

[0149] Conductive structures GC, AC, and CP1-CP8 may be provided in the second interlayer insulating layer 120. The conductive structures GC, AC, and CP1-CP8 may include gate contacts GC, active contacts AC, and first to eighth conductive structures CP1-CP8. The conductive structures GC, AC, and CP1-CP8 may be patterns that are formed in accordance with the connection patterns M0a-M0h, the active contact patterns CAa-CAl, and the gate contact patterns CBa-CBh of FIG. 13. The conductive structures GC, AC, and CP1-CP8 may include conductive metal nitrides or metals.

[0150] The conductive structures GC, AC, and CP1-CP8 may have top surfaces that are substantially coplanar with that of the second interlayer insulating layer 120. In addition, the active contacts AC may have bottom surfaces that are substantially coplanar with that of the second interlayer insulating layer 120. The bottom surfaces of the gate contacts GC may be lower than that of the second interlayer insulating layer 120. In other words, the bottom surfaces of the gate contacts GC may be lower than those of the active contacts AC. The first to eighth conductive structures CP1-CP8 will be described in more detail below.

[0151] Barrier patterns BL may be respectively interposed between the second interlayered insulating layer 120 and the conductive structures GC, AC, and CP1-CP8. The barrier pattern BL may directly cover side and bottom surfaces of the conductive structures GC, AC, and CP1-CP8, except for top surfaces thereof. The barrier patterns BL may include a metal nitride for preventing metallic elements in the conductive structures GC, AC, and CP1-CP8 from being diffused. For example, the barrier patterns BL may be formed of or include TiN.

[0152] First and second power interconnection lines PL1 and PL2 and first to sixth interconnection lines ML1-ML6 may be provided in the third interlayer insulating layer 130. The first and second power interconnection lines PL1 and PL2 may be patterns that are formed in accordance with the power lines PM1 and PM2 of FIG. 13, and the first to sixth interconnection lines ML1-ML6 may be patterns that are formed in accordance with the conductive lines M1a-M1f of FIG. 13.

[0153] Each of the first and second power interconnection lines PL1 and PL2 and each of the first to sixth interconnection lines ML1-ML6 may include a line portion LI extending parallel to the top surface of the substrate 100 and a contact portion VI, which is vertically connected to the conductive structures GC, AC, and CP1-CP8. The contact portion VI may be a pattern that is formed in accordance with the via pattern V0 of FIG. 13.

[0154] Barrier patterns BL may be respectively interposed between the third interlayer insulating layer 130 and the first and second power interconnection lines PL1 and PL2 and between the third interlayer insulating layer 130 and the first to sixth interconnection lines ML1-ML6. The barrier patterns BL may include a metal nitride for preventing metallic elements from being diffused. For example, the barrier patterns BL may be formed of or include TiN.