Thin Film Capacitor And Circuit Board Incorporating The Same

YOSHIKAWA; Kazuhiro ; et al.

U.S. patent application number 16/665503 was filed with the patent office on 2020-04-30 for thin film capacitor and circuit board incorporating the same. The applicant listed for this patent is TDK Corporation. Invention is credited to Yuuki ABURAKAWA, Tatsuo NAMIKAWA, Hitoshi SAITA, Kenichi YOSHIDA, Kazuhiro YOSHIKAWA.

| Application Number | 20200137883 16/665503 |

| Document ID | / |

| Family ID | 70326043 |

| Filed Date | 2020-04-30 |

View All Diagrams

| United States Patent Application | 20200137883 |

| Kind Code | A1 |

| YOSHIKAWA; Kazuhiro ; et al. | April 30, 2020 |

THIN FILM CAPACITOR AND CIRCUIT BOARD INCORPORATING THE SAME

Abstract

Disclosed herein is a thin film capacitor that includes a capacitive insulating film, a first metal film formed on one surface of the capacitive insulating film, and a second metal film formed on other surface of the capacitive insulating film and made of a metal material different from that of the first metal film. The thin film capacitor has an opening penetrating the capacitive insulating film, first metal film, and second metal film. The second metal film is thicker than the first metal film. A first size of a part of the opening that penetrates the first metal film is larger than a second size of a part of the opening that penetrates the second metal film.

| Inventors: | YOSHIKAWA; Kazuhiro; (Tokyo, JP) ; ABURAKAWA; Yuuki; (Tokyo, JP) ; NAMIKAWA; Tatsuo; (Tokyo, JP) ; YOSHIDA; Kenichi; (Tokyo, JP) ; SAITA; Hitoshi; (Tokyo, JP) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 70326043 | ||||||||||

| Appl. No.: | 16/665503 | ||||||||||

| Filed: | October 28, 2019 |

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H05K 1/162 20130101; H05K 2201/09845 20130101; H05K 2201/0352 20130101; H05K 1/0271 20130101; H05K 2201/0179 20130101; H05K 2201/09827 20130101; H05K 3/007 20130101; H05K 2201/09154 20130101; H05K 1/0231 20130101; H05K 1/113 20130101 |

| International Class: | H05K 1/02 20060101 H05K001/02; H05K 1/16 20060101 H05K001/16; H05K 1/11 20060101 H05K001/11 |

Foreign Application Data

| Date | Code | Application Number |

|---|---|---|

| Oct 29, 2018 | JP | 2018-202468 |

| Oct 11, 2019 | JP | 2019-187615 |

Claims

1. A thin film capacitor comprising: a capacitive insulating film; a first metal film formed on one surface of the capacitive insulating film; and a second metal film formed on other surface of the capacitive insulating film and made of a metal material different from that of the first metal film, wherein the thin film capacitor has an opening penetrating the capacitive insulating film, first metal film, and second metal film, wherein the second metal film is thicker than the first metal film, and wherein a first size of a part of the opening that penetrates the first metal film is larger than a second size of apart of the opening that penetrates the second metal film.

2. The thin film capacitor as claimed in claim 1, wherein the thin film capacitor has a plurality of the openings, and wherein a ratio of the capacitive area where the capacitive insulating film is sandwiched between the first and second metal films in a plan view to a sum of the capacitive area and a non-capacitive area where the capacitive insulating film is not present or the capacitive insulating film is not sandwiched between the first and second metal films in a plan view is set to 80% or less.

3. The thin film capacitor as claimed in claim 1, wherein a third size of a part of the opening that penetrates the capacitive insulating film is smaller than the first size.

4. The thin film capacitor as claimed in claim 3, wherein the third size is smaller than a fourth size of a part of the opening that penetrates the second metal film at the boundary of the capacitive insulating film.

5. The thin film capacitor as claimed in claim 1, wherein the opening is filled with an insulating material.

6. A circuit board in which a thin film capacitor is embedded, wherein the thin film capacitor comprises: a capacitive insulating film; a first metal film formed on one surface of the capacitive insulating film; and a second metal film formed on other surface of the capacitive insulating film and made of a metal material different from that of the first metal film, wherein the thin film capacitor has an opening penetrating the capacitive insulating film, first metal film, and second metal film, wherein the second metal film is thicker than the first metal film, wherein a first size of a part of the opening that penetrates the first metal film is larger than a second size of a part of the opening that penetrates the second metal film, and wherein the circuit board includes a via conductor that passes through the opening without contacting the first and second metal films.

Description

BACKGROUND OF THE INVENTION

Field of the Invention

[0001] The present invention relates to a thin film capacitor and a circuit board incorporating the thin film capacitor and, more particularly, to a thin film capacitor capable of being embedded in a circuit board and used and a circuit board incorporating the thin film capacitor.

Description of Related Art

[0002] In general, a decoupling capacitor is mounted on a circuit board on which an IC is mounted for stabilizing the potential of a power supply to be fed to the IC. A laminated ceramic chip capacitor is generally used as the decoupling capacitor, and a required decoupling capacitance is ensured by mounting many laminated ceramic chip capacitors on the surface of a circuit board.

[0003] However, in recent years, it is often the case that a space on a circuit board for mounting many laminated ceramic chip capacitors is insufficient. Thus, there has been proposed a method of using a thin film capacitor in place of the laminated ceramic chip capacitor and embedding the thin film capacitor in the circuit board (see JP 2005-191559 A).

[0004] In order to enable the thin film capacitor to be embedded in the circuit board, it is necessary to reduce the overall thickness of the thin film capacitor as much as possible. However, when the thin film capacitor is reduced in thickness, it may be easily warped. To prevent the warpage of the thin film capacitor, the thicknesses and materials of metal films formed on the front and back sides of a capacitive insulating film are made the same as each other; however, it is not realistic to make the thicknesses and materials thereof the same as each other.

SUMMARY

[0005] It is therefore an object of the present invention to provide a thin film capacitor whose warpage can be suppressed without making the thicknesses or materials of metal films formed on the front and back sides of a capacitive insulating film the same as each other and a circuit board incorporating the thin film capacitor.

[0006] A thin film capacitor according to the present invention includes a capacitive insulating film, a first metal film formed on one surface of the capacitive insulating film, and a second metal film formed on the other surface of the capacitive insulating film and made of a metal material different from that of the first metal film and has an opening penetrating the capacitive insulating film, first metal film, and second metal film. The second metal film is thicker than the first metal film. Assuming that the size of a part of the opening that penetrates the first metal film is a first size and that the size of a part of the opening that penetrates the second metal film is a second size, the first size is larger than the second size.

[0007] Further, a circuit board according to the present invention is a circuit board in which the above thin film capacitor is embedded and includes a via conductor that passes through the opening without contacting the first and second metal films.

[0008] According to the present invention, since the opening that penetrates the capacitive insulating film, first metal film and second metal film is formed, stress due to a difference in thickness or metal material between the first and second metal films is released through the opening. In addition, the second metal film is made thicker than the first metal film, and the first size is made larger than the second size, so that rigidity is ensured by the thicker second metal film, thereby significantly suppressing warpage. Thus, warpage of the thin film capacitor that may occur when it is embedded in the circuit board can be minimized.

[0009] In the thin film capacitor according to the present invention, the opening may comprise a plurality of openings, and assuming that an area where the capacitive insulating film is sandwiched between the first and second metal films in a plan view is a capacitive area and that an area where the capacitive insulating film is not present and an area where the capacitive insulating film is not sandwiched between the first and second metal films in a plan view is a non-capacitive area, the ratio of the capacitive area to the sum of the capacitive area and non-capacitive area may be set to 80% or less. This allows further suppression of warpage that may occur in the thin film capacitor.

[0010] In the present invention, assuming that the size of a part of the opening that penetrates the capacitive insulating film is a third size, the third size may be smaller than the first size. In addition, assuming that the size of a part of the opening that penetrates the second metal film at the boundary of the capacitive insulating film is a fourth size, the third size may be smaller than the fourth size. This increases the creepage distance between the first and second metal films inside the opening, thereby making it possible to improve withstand voltage.

[0011] In the present invention, the opening may be filled with an insulating material. This can improve product reliability.

[0012] As described above, according to the present invention, there can be provided a thin film capacitor whose warpage can be suppressed without making the thicknesses or materials of metal films formed on the front and back sides of a capacitive insulating film the same as each other and a circuit board incorporating the thin film capacitor.

BRIEF DESCRIPTION OF THE DRAWINGS

[0013] The above and other objects, features and advantages of this invention will become more apparent by reference to the following detailed description of the invention taken in conjunction with the accompanying drawings, wherein:

[0014] FIG. 1 is a schematic cross-sectional view for explaining the configuration of a thin film capacitor according to a first embodiment of the present invention;

[0015] FIGS. 2A and 2B are partial plan views of the thin film capacitor shown in FIG. 1, where FIG. 2 A illustrates a first example and FIG. 2B illustrates a second example;

[0016] FIG. 3 is a schematic cross-sectional view for explaining the configuration of a circuit board in which the thin film capacitor according to the first embodiment of the present invention is embedded;

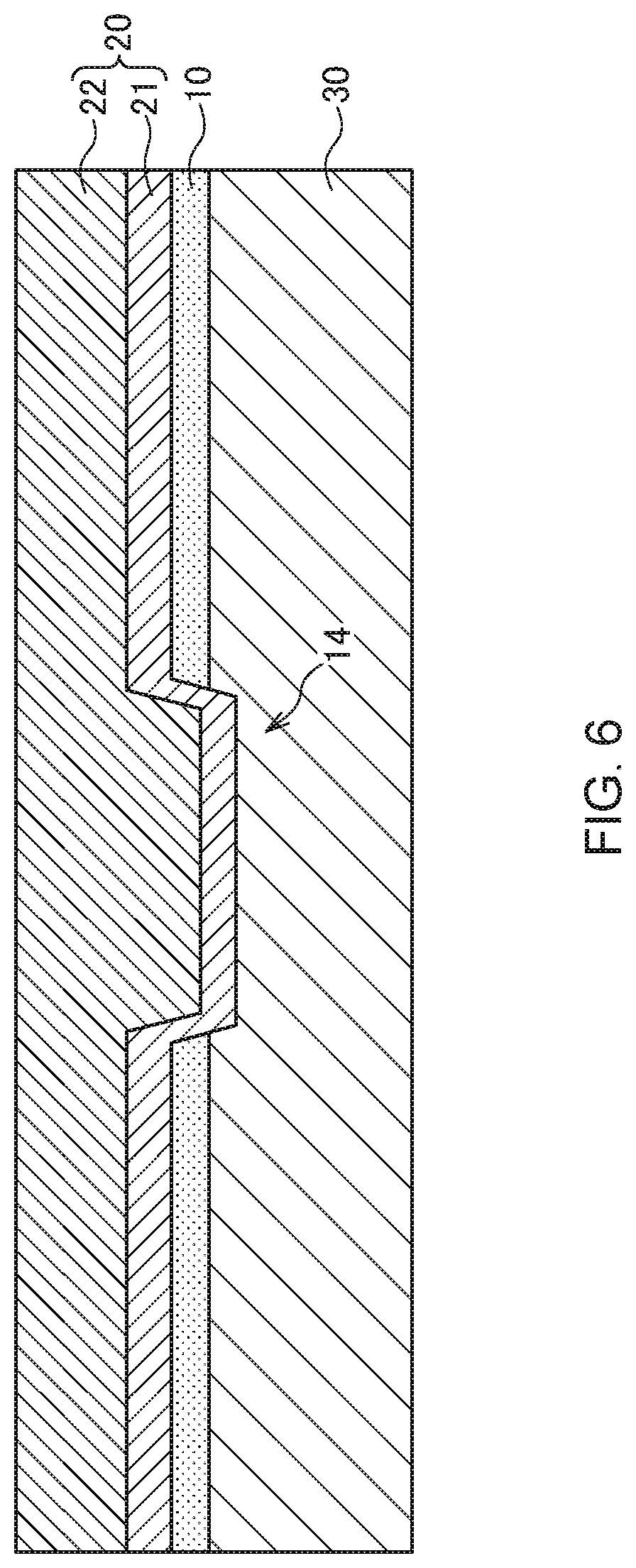

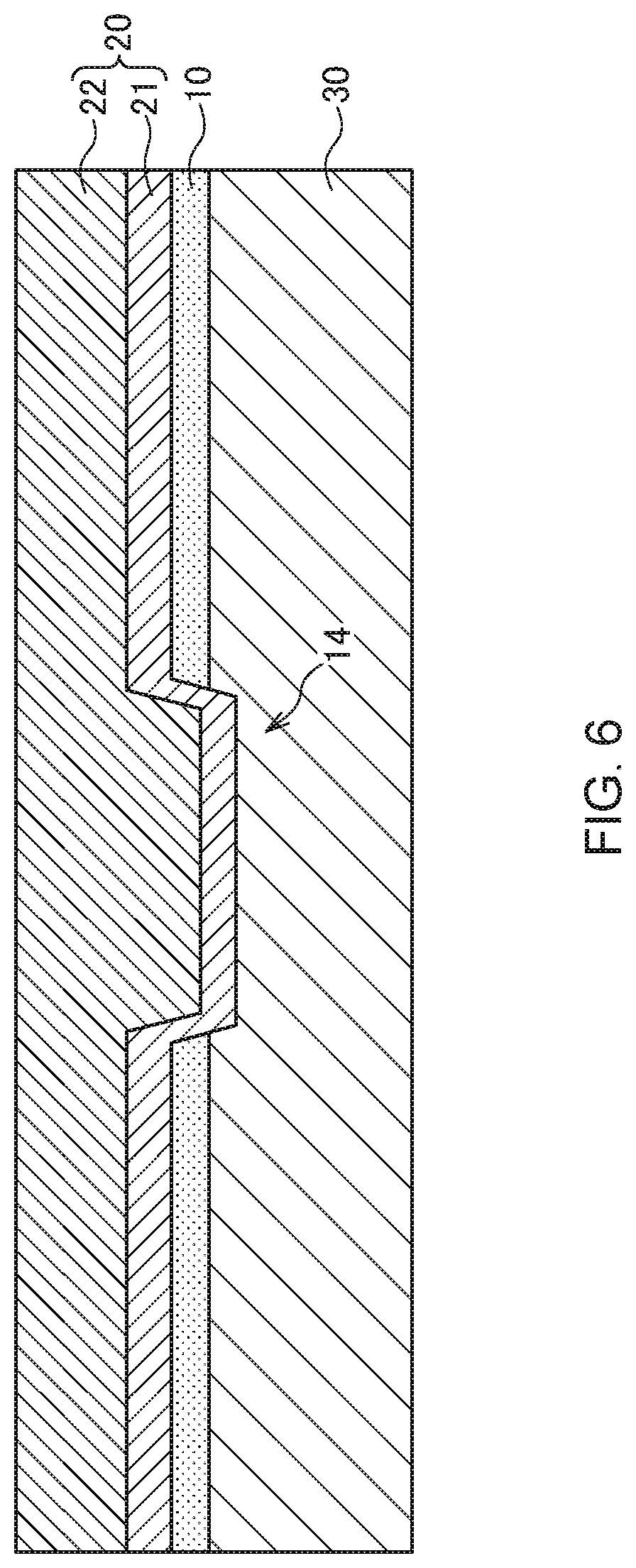

[0017] FIGS. 4 to 8 are process views illustrating a manufacturing method for the thin film capacitor according to the first embodiment of the present invention is embedded;

[0018] FIG. 9 is a schematic cross-sectional view for indicating an edge of the individual thin film capacitor at which a dummy opening is formed;

[0019] FIG. 10 is a schematic cross-sectional view for explaining the configuration of a thin film capacitor according to a second embodiment of the present invention;

[0020] FIGS. 11 to 13 are process views illustrating a manufacturing method for the thin film capacitor according to the second embodiment of the present invention;

[0021] FIG. 14 is a schematic cross-sectional view for explaining the configuration of a thin film capacitor according to a third embodiment of the present invention;

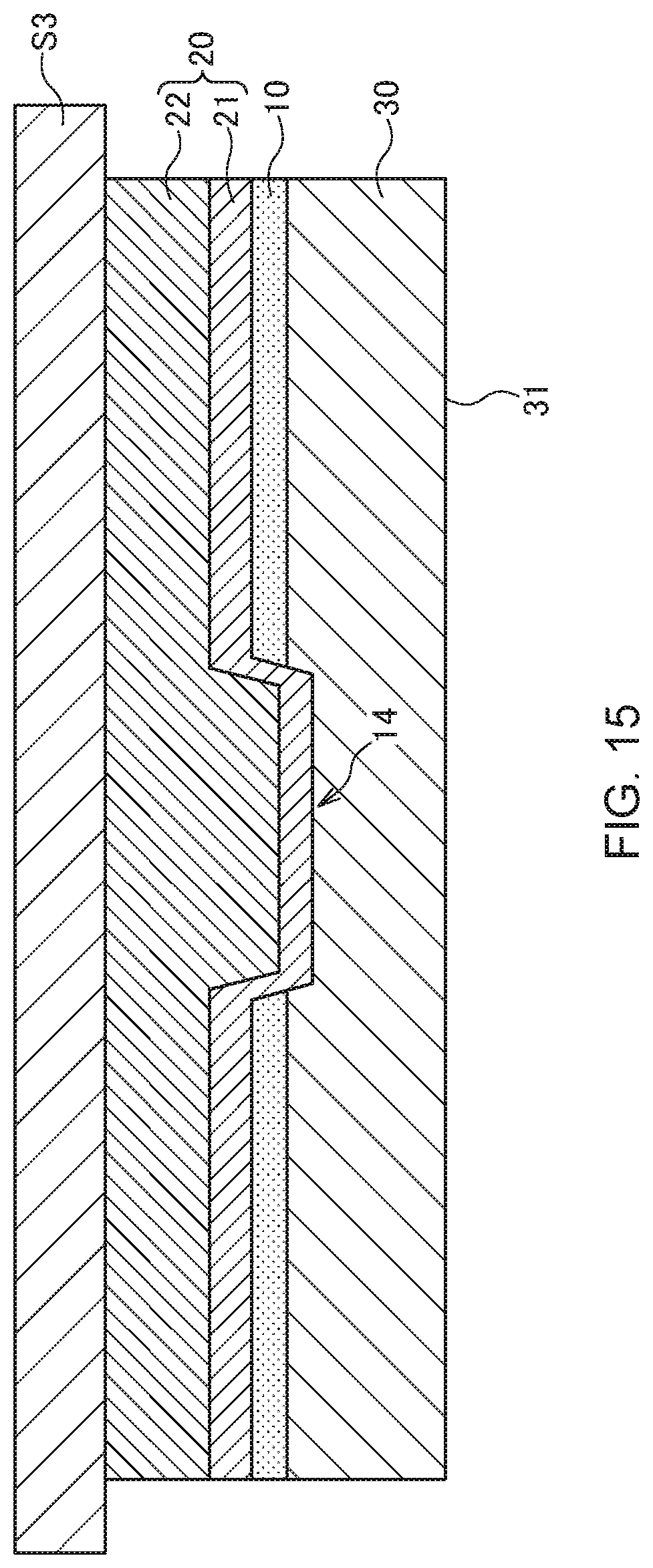

[0022] FIGS. 15 to 18 are process views illustrating a manufacturing method for the thin film capacitor according to the third embodiment of the present invention; and

[0023] FIG. 19 is a schematic cross-sectional view for explaining the configuration of a thin film capacitor according to a fourth embodiment of the present invention.

DETAILED DESCRIPTION OF THE EMBODIMENTS

[0024] Preferred embodiments of the present invention will now be explained in detail with reference to the drawings.

First Embodiment

[0025] FIG. 1 is a schematic cross-sectional view for explaining the configuration of a thin film capacitor 1 according to the first embodiment of the present invention. FIGS. 2A and 2B are partial plan views of the thin film capacitor 1 and illustrate a first example and a second example, respectively. The cross section illustrated in FIG. 1 corresponds to that taken along line A-A in FIG. 2.

[0026] As illustrated in FIGS. 1 and 2A and 2B, the thin film capacitor 1 according to the present embodiment includes a capacitive insulating film 10, a first metal film 20 formed on one surface 11 of the capacitive insulating film 10, and a second metal film 30 formed on the other surface 12 of the capacitive insulating film 10. The capacitive insulating film 10 is made of a ceramic material having a perovskite structure, such as barium titanate. The metal film 20 has a structure in which a seed layer 21 and a plated film 22 are laminated. The seed layer 21 is made of, e.g., a laminated film of nickel (Ni) and copper (Cu), and the plated film 22 is made of copper (Cu). The metal film 30 serves as a base material of the thin film capacitor 1 according to the present embodiment and is made of, e.g., nickel (Ni).

[0027] In the present embodiment, assuming that the thicknesses of the metal film 20, metal film 30 and capacitive insulating film 10 are set to T1, T2 and T3, respectively, the following relationship is satisfied:

T2>T1>T3.

T1 is in the range of 5 .mu.m to 20 .mu.m and set to, e.g., about 10 .mu.m, and T2 is in the range of 8 .mu.m to 50 .mu.m and set to, e.g., about 15 .mu.m. T3 is set to about 3 .mu.m.

[0028] As described above, the overall thickness of the thin film capacitor 1 according to the present embodiment is very small. In addition, the metal films 20 and 30 formed on the front and back sides of the capacitive insulating film 10 differ from each other in terms of thickness and material. Thus, the capacitive insulating film 10 is very easily warped if no measure is taken. However, in the present embodiment, such warpage stress is partially released through an opening 40 formed so as to penetrate the capacitive insulating film 10 and the metal films 20 and 30. As illustrated in FIGS. 2A and 2B, a plurality of openings 40 are formed. The planar shape of the opening 40 is an L-shape in the example of FIG. 2A, and is a circular shape in the example of FIG. 2B. Thus, the planar shape of the opening 40 is not particularly limited.

[0029] The higher the formation density of the openings 40 is, the more stress is released to reduce warpage, but a capacitance value to be obtained is reduced. The following configuration is preferable in order to sufficiently reduce the warpage of the thin film capacitor 1. That is, assuming that an area that functions as a capacitor, i.e., an area where the capacitive insulating film 10 is sandwiched between the metal films 20 and 30 in a plan view is a capacitive area C1 and that an area that does not function as a capacitor, i.e., an area where the capacitive insulating film 10 is not present and an area where the capacitive insulating film 10 is not sandwiched between the metal films 20 and 30 in a plan view is a non-capacitive area C2, the ratio (C1/(C1+C2)) of the capacitive area C1 to the sum of the capacitive area C1 and non-capacitive area C2 is preferably set to 80% or less. However, in this case, a capacitance value is reduced by 20% or more as compared to the instance where the openings 40 are not formed.

[0030] Further, in the present embodiment, assuming that the sizes of a part of each opening 40 that penetrates the metal film 20, a part of each opening 40 that penetrates the metal film 30 and a part of each opening 40 that penetrates the capacitive insulating film 10 are .PHI.1, .PHI.2 and .PHI.3, respectively, the following relationship is satisfied:

.PHI.1>.PHI.3>.PHI.2.

In addition, assuming that the size of a part of each opening 40 that penetrates the metal film 30 at the boundary of the capacitive insulating film 10 is .PHI.2a, the following relationship is satisfied:

.PHI.1>.PHI.2a>.PHI.3.

When the opening 40 has an elongated shape in a plan view as illustrated in FIG. 2A, the sizes .PHI.1 to .PHI.3 are defined by the width thereof in the short-side direction, and when the opening 40 has a circular shape in a plan view as illustrated in FIG. 2B, the sizes .PHI.1 to .PHI.3 are defined by the diameter thereof. Further, when the size of the capacitive insulating film 10, metal film 20, or metal film 30 is not constant in the depth direction, each of the sizes .PHI.1, .PHI.2 and .PHI.3 is defined by the narrowest part thereof. The size .PHI.1 is about 150 .mu.m to about 250 .mu.m, and the sizes .PHI.2 and .PHI.3 are each about 100 .mu.m to about 200 .mu.m.

[0031] As described above, in the thin film capacitor 1 according to the present embodiment, the size .PHI.2 of the opening 40 in the metal film 30 having a larger thickness is smaller than the size .PHI.1 of the opening 40 in the metal film 20 having a smaller thickness, so that rigidity is ensured by the thicker metal film 30 to thereby suppress the warpage of the thin film capacitor 1. In addition, in the present embodiment, the size .PHI.3 of the opening 40 in the capacitive insulating film 10 is smaller than the sizes .PHI.1 and .PHI.2, causing the capacitive insulating film 10 to protrude to the inside of the opening 40 as illustrated in FIG. 1. As a result, the creepage distance between the metal films 20 and 30 inside the opening is increased, thereby preventing deterioration in withstand voltage due to the presence of the opening 40.

[0032] FIG. 3 is a schematic cross-sectional view for explaining the configuration of a circuit board 100 in which the thin film capacitor 1 according to the present embodiment is embedded.

[0033] The circuit board 100 illustrated in FIG. 3 has six wiring layers L1 to L6, a resin layer 110 that insulates the wiring layers L1 to L6 from one another, and a via conductor 120 that connects different wiring layers. A part of a conductor pattern formed in the wiring layer L1 and a part of a conductor pattern formed in the wiring layer L6 each constitute a land pattern. An IC chip 200 and a laminated ceramic chip capacitor 300 are mounted on the land pattern constituted by the wiring layer L6.

[0034] In the thus configured circuit board 100, the thin film capacitor 1 according to the present embodiment is embedded between the wiring layers L5 and L6. As illustrated in FIG. 3, the IC chip 200 is provided with a bump electrode BV for supplying a power supply potential, a bump electrode BG for supplying a ground potential, and a bump electrode BS for transmitting/receiving a signal. The bump electrode BV for supplying a power supply potential is connected to the metal film 30 of the thin film capacitor 1, and the bump electrode BG for supplying a ground potential is connected to the metal film 20 of the thin film capacitor 1. Thus, a decoupling capacitance constituted of the thin film capacitor 1 is connected between the bump electrode BV and the bump electrode BG, allowing the power supply potential and ground potential to be supplied to the IC chip 200 to be stabilized. The metal films 20 and 30 of the thin film capacitor 1 are also connected to terminal electrodes 301 and 302 of the laminated ceramic chip capacitor 300, respectively.

[0035] The bump electrode BS for transmitting/receiving a signal is connected to the wiring layer L5 in a lower layer through a via conductor 130 passing through the opening 40. As described above, the thin film capacitor 1 according to the present embodiment has the plurality of openings 40, so that it is possible to connect the bump electrode BS to a conductor pattern in a lower layer at the shortest distance without signal wire routing by thus providing the via conductor 130 passing through the opening 40 without contacting the metal films 20 and 30.

[0036] However, not all the via conductors that pass through the opening 40 need to be signal wiring, but some via conductors may be power supply wiring or ground wiring.

[0037] As described above, the thin film capacitor 1 according to the present embodiment has the plurality of openings 40, allowing the via conductor that passes through each of the openings 40 to be provided in the circuit board 100.

[0038] The following describes a manufacturing method for the thin film capacitor 1 according to the present embodiment.

[0039] FIGS. 4 to 8 are process views illustrating a manufacturing method for the thin film capacitor 1 according to the present embodiment.

[0040] First, as illustrated in FIG. 4, the metal film 30 made of, e.g., nickel (Ni) and having a thickness of T2 is prepared, and the capacitive insulating film 10 having a thickness of T3 is formed on the surface of the metal film 30, followed by baking. Although high temperature is applied also to the metal film 30 during baking, the metal film 30 can be made to withstand baking temperature by using refractory metal such as nickel (Ni) as the material thereof.

[0041] Then, as illustrated in FIG. 5, the capacitive insulating film 10 is patterned to form an opening 14 in the capacitive insulating film 10. The opening 14 is a part to be the opening 40 by way of the subsequent processes and has a size of .PHI.3.

[0042] Then, as illustrated in FIG. 6, the metal film 20 composed of the seed layer 21 and plated film 22 is formed on the surface 11 of the capacitive insulating film 10. The seed layer 21 is, e.g., a laminated film of nickel (Ni) and copper (Cu) and formed through a thin-film process such as a sputtering method. On the other hand, the plated film 22 is, e.g., an electroplated copper (Cu) film. The metal film 20 is formed not only on the surface 11 of the capacitive insulating film 10, but also in the opening 14, so that the metal films 20 and 30 contact each other in the opening 14.

[0043] Then, as illustrated in FIG. 7, a support panel S1 is bonded to the metal film 30 side, and then an opening 40a is formed in the metal film 20 by pattering. The opening 40a is formed in a location overlapping the opening 14 and has a size of .PHI.1. When the metal film 20 is patterned, the size .PHI.1 tends to decrease in the depth direction, so that it is preferable to perform patterning so as to make the size .PHI.1 at the bottom portion larger than the size 03 of the opening 14. The opening 40a overlaps the opening 14, so that the metal film 30 is overetched at this portion.

[0044] Then, as illustrated in FIG. 8, the support panel S1 is peeled off, and another support panel S2 is bonded to the metal film 20 side. After that, the metal film 30 is patterned from the back side to form an opening 40b. The opening 40b is formed in a location overlapping the opening 40a, whereby the opening 40 constituted of the openings 40a and 40b is formed. When the metal film 30 is patterned, the size .PHI.2 tends to decrease in the depth direction, so that it is preferable to perform patterning so as to make the size .PHI.2 at the bottom portion smaller than the size .PHI.1.

[0045] After the support panel S2 is peeled off, dicing is performed in predetermined locations, whereby the thin film capacitor 1 illustrated in FIG. 1 is completed. In the dicing location, a dummy opening 40 may be formed in advance, thereby facilitating dicing work. In this case, the edge of the individual thin film capacitor 1 at which the dummy opening 40 is formed has the same cross section as the opening 40 as illustrated in FIG. 9.

[0046] As described above, in the present embodiment, the metal film 30 is patterned so as to make the size .PHI.2 smaller than the size .PHI.1, allowing the rigidity of the metal film 30 to be ensured. In addition, the metal film 30 is overetched when the metal film 20 is patterned, allowing the capacitive insulating film 10 to protrude to the inside of the opening 40. As a result, the creepage distance between the metal films 20 and 30 inside the opening 40 is increased, thereby preventing deterioration in withstand voltage.

Second Embodiment

[0047] FIG. 10 is a schematic cross-sectional view for explaining the configuration of a thin film capacitor 2 according to the second embodiment of the present invention. The planar shape of the thin film capacitor 2 according to the present embodiment is as illustrated in FIGS. 2A and 2B.

[0048] As illustrated in FIG. 10, the thin film capacitor 2 according to the second embodiment differs from the thin film capacitor 1 according to the first embodiment in that the inside of the opening 40 is filled with insulating resin 50. Other basic configurations are the same as those of the thin film capacitor 1 according to the first embodiment, so the same reference numerals are given to the same elements, and overlapping description will be omitted.

[0049] The following describes a manufacturing method for the thin film capacitor 2 according to the present embodiment.

[0050] FIGS. 11 to 13 are process views illustrating a manufacturing method for the thin film capacitor 2 according to the present embodiment.

[0051] First, the processes illustrated in FIGS. 4 to 7 are performed. After that, as illustrated FIG. 11, the entire upper surface of the metal film 20 is covered with the insulating resin 50 so as to fill the opening 40a therewith, and then the unnecessary insulating resin 50 is removed so as to expose the upper surface of the metal film 20. As a result, the opening 40a is filled with the insulating resin 50.

[0052] Then, as illustrated in FIG. 12, the support panel S1 is peeled off, and another support panel S2 is bonded to the metal film 20 side. After that, the metal film 30 is patterned from the back side to form the opening 40b. The opening 40b is formed in a location overlapping the opening 40a, whereby the opening 40 constituted of the openings 40a and 40b is formed.

[0053] Then, as illustrated in FIG. 13, the entire lower surface of the metal film 30 is covered with the insulating resin 50 so as to fill the opening 40b therewith. As a result, the opening 40 is filled with the insulating resin 50. Then, after the support panel S2 is peeled off, the insulating resin 50 is bonded to a dicing tape 70 through a die attach film 60, and dicing is performed in predetermined locations, whereby the thin film capacitor 2 illustrated in FIG. 10 is completed.

[0054] As described above, in the thin film capacitor 2 according to the second embodiment, the inside of the opening is filled with the insulating resin 50, allowing improvement in product reliability in a shipping state before embedding in the circuit board.

Third Embodiment

[0055] FIG. 14 is a schematic cross-sectional view for explaining the configuration of a thin film capacitor 3 according to the third embodiment of the present invention. The planar shape of the thin film capacitor 3 according to the present embodiment is as illustrated in FIGS. 2A and 2B.

[0056] As illustrated in FIG. 14, the basic configuration of the thin film capacitor 3 according to the third embodiment is the same as that of the thin film capacitor 1 according to the first embodiment. That is, the thickness T2 of the metal film 30 formed on the surface 12 of the capacitive insulating film 10 is larger than the thickness T1 of the metal film 20 formed on the surface 11 of the capacitive insulating film 10, and the size .PHI.1 of the opening 40 in the metal film 20 is larger than the size .PHI.2 of the opening 40 in the metal film 30. However, in the thin film capacitor 3 according to the present embodiment, the opening 40 formed in the metal film 30 is tapered in a form reversal of the opening 40 of the thin film capacitor 1 according to the first embodiment.

[0057] Even with such a configuration, it is possible to suppress warpage as in the thin film capacitor 1 according to the present embodiment. Further, the capacitive insulating film 10 protrudes to the inside of the opening 40, so that it is possible to prevent deterioration in withstand voltage.

[0058] The following describes a manufacturing method for the thin film capacitor 3 according to the present embodiment.

[0059] FIGS. 15 to 18 are process views illustrating a manufacturing method for the thin film capacitor 3 according to the present embodiment.

[0060] First, the processes illustrated in FIGS. 4 to 6 are performed. Next, as illustrated FIG. 15, a support panel S3 is bonded to the metal film 20 side. In this state, etching or polishing is performed from a back surface 31 of the metal film 30 to reduce the thickness of the metal film 30. Then, as illustrated in FIG. 16, the support panel S3 is peeled off, and the insulating resin 50 is formed on the back surface 31 of the metal film 30.

[0061] Then, as illustrated in FIG. 17, another support panel S4 is bonded to the insulating resin 50 side, and then patterning is performed to form the opening 40a in the metal film 20. The opening 40a is formed at a position overlapping the opening 14 and has a size of .PHI.1. Also in the present embodiment, the metal film 30 is overetched at a part thereof overlapping the opening 14.

[0062] Then, as illustrated in FIG. 18, the metal film 30 exposed to the opening 40a is removed by patterning to form the opening 40. At this time, it is possible to reduce damage applied to the plated film 22 by performing patterning under a condition that the etching selectivity of a metal material (e.g., Ni) constituting the metal film 30 relative to a metal material (e.g., Cu) constituting the plated film 22 is as high as possible. Then, after the support panel S4 is peeled off, the insulating resin 50 is bonded to the dicing tape 70 and dicing is performed in predetermined locations, whereby the thin film capacitor 3 illustrated in FIG. 14 is completed.

[0063] As exemplified in the present embodiment, the metal films 20 and 30 may be patterned from the same direction in the present invention.

Fourth Embodiment

[0064] FIG. 19 is a schematic cross-sectional view for explaining the configuration of a thin film capacitor 4 according to the fourth embodiment of the present invention. The planar shape of the thin film capacitor 4 according to the present embodiment is as illustrated in FIGS. 2A and 2B.

[0065] As illustrated in FIG. 19, the thin film capacitor 4 according to the fourth embodiment differs from the thin film capacitor 3 according to the third embodiment in that an interface 80 between the lower edge of the capacitive insulating film 10 and the upper edge of the metal film 30 which are exposed inside the opening 40 does not have a step. That is, the size of the capacitive insulating film 10 at the interface 80 and the size of the metal film 30 at the interface 80 are equal to each other. Other configurations are the same as those of the thin film capacitor 3 according to the third embodiment.

[0066] As exemplified in the present embodiment, the capacitive insulating film 10 need not protrude from both the metal films 20 and 30 inside the opening 40.

[0067] It is apparent that the present invention is not limited to the above embodiments, but may be modified and changed without departing from the scope and spirit of the invention.

EXAMPLES

[0068] A 15.times.15 mm thin film capacitor having the same configuration as the thin film capacitor 1 illustrated in FIG. 1 and having 2000 circular openings 40 was produced, and the warpage amount was measured. As the capacitive insulating film 10, barium titanate having the thickness T3 of 3 .mu.m was used. As the plated film 22 constituting the metal film 20, copper (Cu) was used. As the metal film 30, nickel (Ni) was used. The thicknesses T1 and T2 of the respective metal films 20 and 30, and the sizes (diameters) .PHI.1 and .PHI.2 of parts of the opening 40 penetrating the metal films 20 and 30, respectively, were set in different combinations for each sample.

[0069] The results are illustrated in Table 1. The capacitance (%) shown in Table 1 is represented by a percentage when the capacitance in Sample 1 having no opening 40 is set as 100.

TABLE-US-00001 TABLE 1 Warpage o1 o2 T1 Amount Capacitance SAMPLE (.mu.m) (.mu.m) (.mu.m) T2 (.mu.m) (.mu.m) (%) 1 0 0 10 20 55 100 2 100 150 10 20 108 84 3 150 150 10 20 48 84 4 200 150 10 20 16 72 5 250 150 10 20 12 56 6 200 100 10 20 14 72 7 200 150 10 20 18 72 8 200 200 10 20 43 72 9 200 150 5 20 8 72 10 200 150 10 20 12 72 11 200 150 15 20 19 72 12 200 150 20 20 35 72 13 200 150 10 5 45 72 14 200 150 5 5 32 72 15 200 150 5 8 18 72 16 200 150 5 10 11 72 17 200 150 5 15 9 72 18 200 150 5 25 8 72 19 200 150 5 35 5 72 20 200 150 5 50 6 72 21 200 150 20 15 38 72 22 200 150 20 20 41 72 23 200 150 20 25 17 72 24 200 150 20 35 15 72 25 200 150 20 50 8 72

[0070] As shown in Table 1, the warpage amount in Sample 1 having no opening 40 is 55 .mu.m. On the other hand, in Samples 4 to 7, 9 to 11, 15 to 20, and 23 to 25, in which both T1<T2 and .PHI.1>.PHI.2 are satisfied, the warpage amount is less than 20 .mu.m and, thus, it is confirmed that the warpage is significantly suppressed. In Samples 2, 3, 8, 12 to 14, 21, and 22 in which the above conditions are not satisfied, the warpage amount is 30 .mu.m or more. That is, the warpage cannot be sufficiently suppressed although many openings 40 are formed.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

D00009

D00010

D00011

D00012

D00013

D00014

D00015

D00016

D00017

D00018

D00019

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.