Spur Cancellation With Adaptive Frequency Tracking

Monk; Timothy A. ; et al.

U.S. patent application number 16/143717 was filed with the patent office on 2020-04-02 for spur cancellation with adaptive frequency tracking. The applicant listed for this patent is Silicon Laboratories Inc.. Invention is credited to Timothy A. Monk, Rajesh Thirugnanam.

| Application Number | 20200106451 16/143717 |

| Document ID | / |

| Family ID | 69947842 |

| Filed Date | 2020-04-02 |

| United States Patent Application | 20200106451 |

| Kind Code | A1 |

| Monk; Timothy A. ; et al. | April 2, 2020 |

SPUR CANCELLATION WITH ADAPTIVE FREQUENCY TRACKING

Abstract

A spur cancellation circuit receives a target spur frequency indicative of a frequency of a spur to be canceled and supplies a spur cancellation signal based on the frequency. A frequency tracking circuit tracks a change in the frequency of the spur to be canceled based on a change in phase of the spur cancellation signal and generates an updated target spur frequency based on the change in the frequency of the spur.

| Inventors: | Monk; Timothy A.; (Hudson, NH) ; Thirugnanam; Rajesh; (Nashua, NH) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 69947842 | ||||||||||

| Appl. No.: | 16/143717 | ||||||||||

| Filed: | September 27, 2018 |

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H03L 7/091 20130101; G04F 10/005 20130101; H03L 7/093 20130101 |

| International Class: | H03L 7/091 20060101 H03L007/091; H03L 7/093 20060101 H03L007/093 |

Claims

1. A method for tracking spur frequency comprising: generating a spur cancellation signal with a first phase using a target spur frequency; determining the first phase of the spur cancellation signal with the first phase from a first sample of parameters used in generating the spur cancellation signal with the first phase; generating the spur cancellation signal with a second phase; determining the second phase from a second sample of parameters used in determining the spur cancellation signal with the second phase; determining a phase difference between the first phase and the second phase; updating a target spur frequency to an updated target spur frequency based on the phase difference; and generating an updated spur cancellation signal using the updated target spur frequency.

2. The method as recited in claim 1 further comprising: scaling the phase difference and generating a scaled phase difference.

3. The method as recited in claim 2, further comprising: adding the scaled phase difference to the target spur frequency to generate the updated target spur frequency.

4. The method as recited in claim 1, wherein the first sample of parameters used in determining the spur cancellation signal with the first phase includes a first sine weight and a first cosine weight and wherein the second sample of parameters used in determining the spur cancellation signal with the second phase includes a second sine weight and a second cosine weight.

5. The method as recited in claim 1, further comprising: generating a first sine weight applied to a sine signal and a first cosine weight applied to a cosine signal as part of generating the spur cancellation signal with the first phase at a first time; generating a second sine weight and a second cosine weight as part of generating the spur cancellation signal with the second phase at a second time; and using the first sine weight and the first cosine weight to determine the first phase and using the second sine weight and the second cosine weight to determine the second phase, the first sine weight and the first cosine weight being the first sample of parameters and the second sine weight and the second cosine weight being the second sample of parameters.

6. The method as recited in claim 1 wherein the spur cancellation signal is a sinusoid.

7. The method as recited in claim 1 wherein the spur cancellation signal is other than a sinusoid.

8. The method as recited in claim 1 further comprising cancelling a spur in a phase-locked loop using the updated target spur frequency.

9. An apparatus comprising: a spur cancellation circuit coupled to receive a target spur frequency indicative of a frequency of a spur to be canceled and supply a spur cancellation signal based on the target spur frequency; and a frequency tracker to track a change in the frequency of the spur to be canceled, the frequency tracker including, a phase determination block configured to divide a first sine weight used to generate a first sine component of the spur cancellation signal by a first cosine weight used to generate a first cosine component of the spur cancellation signal and generate a first divide value and wherein the first sine component and the first cosine component are summed to generate the spur cancellation signal with a first phase in the spur cancellation circuit, and wherein the first phase is determined in the phase determination block according to an arctangent of the first divide value; wherein the phase determination block is further configured to divide a second sine weight used to generate a second sine component of the spur cancellation signal by a second cosine weight used to generate a second cosine component of the spur cancellation signal and generate a second divide value and wherein the second sine component and the second cosine component are summed to generate the spur cancellation signal with a second phase in the spur cancellation circuit, and wherein the second phase is determined in the phase determination block according to an arctangent of the second divide value; a difference block to determine a phase difference between the first phase of a first spur cancellation signal and a second phase of a second spur cancellation signal; and wherein the frequency tracker is configured to adjust the target spur frequency to an updated target spur frequency based on the phase difference.

10. The apparatus as recited in claim 9 wherein the frequency further comprises: a scale circuit to adjust the phase difference by a scale factor and generate a scaled phase difference; and a summing circuit to add the scaled phase difference to the target spur frequency to generate the updated target spur frequency.

11. The apparatus as recited in claim 10, wherein the frequency tracker further comprises: a delay circuit coupled to the summing circuit to delay the updated target spur frequency.

12. (canceled)

13. The apparatus as recited in claim 9, wherein the spur cancellation circuit further comprises: a summing circuit to sum the first sine component and the first cosine component to generate the spur cancellation signal with the first phase.

14. The apparatus as recited in claim 9 wherein the spur cancellation signal is a sinusoid.

15. (canceled)

16. The apparatus as recited in claim 9 further comprising: a phase-locked loop generating a loop filter input signal in which the spur has been attenuated by the spur cancellation signal.

17. A method comprising: using a sum of a sine component and a cosine component to generate a spur cancellation signal; using a first weight applied to a sine signal to generate the sine component and a second weight applied to a cosine signal to generate the cosine component; applying the spur cancellation signal to cancel a spur at a first frequency; determining a first phase of the spur cancellation signal using the first and second weights; using an updated first weight to generate an updated sine component of the spur cancellation signal and using an updated second weight to generate an updated cosine component of the spur cancellation signal; determining a second phase of the spur cancellation signal using the updated first weight and the updated second weight; generating a phase difference based on a difference between the first phase and the second phase; tracking a frequency change of the spur based on the phase difference; and updating the first frequency of the spur cancellation signal to a second frequency based on the tracking.

18. (canceled)

19. The method as recited in claim 17 wherein the spur cancellation signal is a sinusoid.

20. (canceled)

Description

BACKGROUND

Field of the Invention

[0001] This invention relates to spur cancellation and more particularly to tracking spur frequency changes.

Description of the Related Art

[0002] Signals generated by phase-locked loops and other timing circuits can include undesirable spurious tones. Canceling these spurious tones can improve the output of the timing circuits. Accordingly, improved techniques for canceling spurious tones are desirable.

SUMMARY OF EMBODIMENTS OF THE INVENTION

[0003] In one embodiment, a method for tracking spur frequency includes extracting phase information from parameters used in determining a spur cancellation signal and updating a target spur frequency to an updated target spur frequency based on the phase information.

[0004] In another embodiment, an apparatus includes a spur cancellation circuit coupled to receive a target spur frequency indicative of a frequency of a spur to be canceled and supply a spur cancellation signal based on the frequency. A frequency tracking circuit tracks a change in the frequency of the spur to be canceled based on a change in phase of the spur cancellation signal and updates the frequency control word based on the change in the frequency of the spur.

[0005] In another embodiment a method includes applying a spur cancellation signal to cancel a spur at a first frequency. The method further includes tracking a frequency change in the spur based on a change in phase of the spur cancellation signal, the change in phase of the cancellation signal responsive to the frequency change of the spur. The first frequency of the spur cancellation signal is updated to a second frequency based on the tracking.

BRIEF DESCRIPTION OF THE DRAWINGS

[0006] The present invention may be better understood, and its numerous objects, features, and advantages made apparent to those skilled in the art by referencing the accompanying drawings.

[0007] FIG. 1 illustrates a high level block diagram of a spur cancellation circuit with a spur frequency tracking circuit.

[0008] FIG. 2 illustrates additional details of the spur cancellation circuit.

[0009] FIG. 3 illustrates a high level block diagram of an embodiment of an adaptive spur frequency tracking circuit.

[0010] FIG. 4 illustrates a high level flow diagram showing operation of an embodiment of an adaptive spur frequency tracking circuit.

[0011] The use of the same reference symbols in different drawings indicates similar or identical items.

DETAILED DESCRIPTION

[0012] Embodiments described herein relate to a spur, or tone, cancellation system or circuit such as one incorporated in a high-performance fractional-N highly-digital phase-locked loop (PLL). One such PLL is described in U.S. Pat. No. 9,762,250, entitled "Cancellation of Spurious Tones Within A Phase-Locked Loop With A Time-To-Digital Converter", filed Jul. 31, 2014, naming Michael H. Perrott as inventor, which application is incorporated herein by reference.

[0013] FIG. 1 illustrates a high level block diagram of an embodiment of a PLL 100 with a spur cancellation circuit 101. The PLL 100 receives a reference clock signal from crystal oscillator (XO) or other clock source 103. A digitally controlled oscillator (DCO) 105 supplies an output signal 107, which is fed back through feedback divider 109 to the phase detector 111. The phase detector supplies a time to digital converter circuit 115, which supplies a signal r that has a spurious tone (spur) canceled by the spur cancellation circuit 101 before being supplied to the loop filter 117.

[0014] The spur cancellation circuit receives a programmable frequency control word (FCW) 119 that identifies the target spur of interest (target spur frequency) to be canceled. As described further herein, the FCW is modified by the use of adaptive frequency tracking circuit 120 to track movement in spur frequency over time. In the spur cancellation circuit 101, sine and cosine terms 131 and 133 at the programmable target frequency are correlated against a sense node, d.sub.sense, 121 inside the PLL. The resulting error signals drive a pair of accumulators, which set the weights on the sine and cosine signals, producing a spur cancellation signal, d.sub.inject 135. Negative feedback drives the amplitude and phase of the cancellation signal to be such that no spur appears (or the spur is significantly reduced) in the PLL output signal 107.

[0015] FIG. 2 illustrates an embodiment of the spur cancellation circuit 101 in more detail. In the embodiment of FIG. 2, the two correlators are respectively implemented with high-resolution multipliers 201 and 203 and accumulate-and-dump circuits 205 and 206. The accumulate and dump circuits 205 and 206 average a number of samples by accumulating samples over the chosen measurement time frame (N samples) and then "dumping" the resulting value. A phase adjust block 207 follows the accumulate and dump circuits to compensate for PLL dynamics. The final weights on the sine and cosine terms are a.sub.q and a.sub.i, which are the scale factors for the sine and cosine components of the cancellation signal. The weights multiply the sine and cosine terms (sin {circumflex over (.theta.)}.sub.F and cos {circumflex over (.theta.)}.sub.F) and summer 209 sums together the multiplication results and supplies the spur cancellation signal d.sub.inject ({circumflex over (r)} in FIG. 2) to cancel the spurious tone at the frequency specified by FCW. Note that the spur cancellation circuit can be implemented digitally.

[0016] In many applications the spur frequency tracks the spur cancellation circuit's main clock signal. However, in other applications such as jitter-attenuating clock applications with multiple asynchronous inputs or in the presence of an external interferer, the spur frequency does not track the spur cancellation circuit's main clock signal. In such situations, absent adaptive tracking of the spur frequency, the spur cancellation circuit does not accurately target the spur frequency resulting in a reduced quality of the spur cancellation. Further, multiple spurs may also diminish the quality of the spur cancellation. Embodiments described herein alleviate these issues by tracking the spur location directly and adapting the target frequency of the spur being canceled as the spur frequency changes.

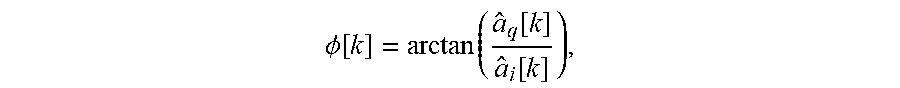

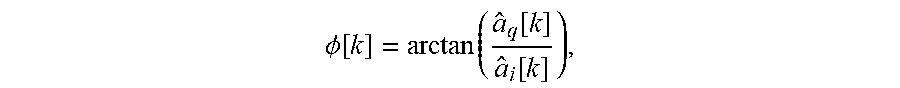

[0017] Using the weights a.sub.q and a.sub.i for the sine and cosine components of the cancellation signal described above with relation to FIG. 2, the phase of the cancellation signal is equal to

.phi. [ k ] = arctan ( a ^ q [ k ] a ^ i [ k ] ) , ##EQU00001##

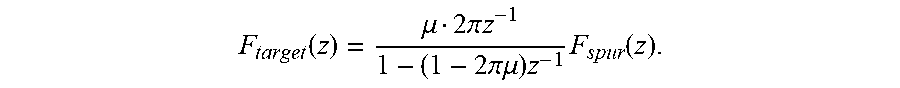

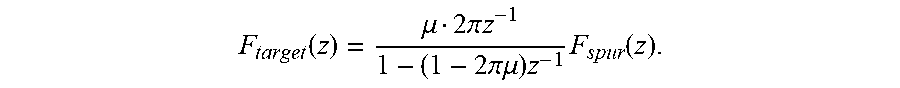

where k is the sample index at the spur cancellation circuit clock rate. The difference in the phase from one sample to the next provides information about the difference between the actual spur frequency, f.sub.spur, and the spur cancellation circuit target frequency, f.sub.target. The relationship is expressed in the equation .DELTA..PHI.[k]=.PHI.[k]-.PHI.[k-1]=2.pi.(f.sub.spur[k]-f.sub.target[k]) If the actual spur frequency is higher than the targeted frequency, then the phase given by the weights will advance according to the difference. If the actual spur frequency is lower than the targeted frequency, then the phase given by the weights will retreat according to the difference. That assumes that the frequency difference is small enough that the spur cancellation circuit adaptive frequency tracking can track the difference, but this is a necessary condition for good cancellation, so it is valid to assume. Embodiments update the target frequency according to the equation f.sub.target[k+1]=f.sub.target[k]+.mu.. (.PHI.[k]-.PHI.[k-1]), where .mu. is a weighting factor that sets the rate at which the target frequency tracks the spur frequency. The same relationship can be expressed in the frequency domain as

F target ( z ) = .mu. 2 .pi. z - 1 1 - ( 1 - 2 .pi..mu. ) z - 1 F spur ( z ) . ##EQU00002##

The frequency domain equation shows that the DC gain is 1, with some lag given by the low-pass characteristic of the filter. The tracking rate set by .mu. is determined by the rate at which the spur frequency can change over time, the clock rate, and the rate at which it is desired to respond to variation of the spur frequency. The tracking rate is typically low, because it is tracking changes in spur frequency due to aging and environmental changes, which are gradual and slow compared to the high-speed operation of modern digital circuits. For example, the frequency change may be a maximum of 10,000 parts per million or 1% in embodiments due to temperature change. In other embodiments, that frequency change may be less.

[0018] FIG. 3 illustrates an embodiment of a hardware implementation of the adaptive frequency tracking circuit 120 shown in FIG. 1. A divider circuit 301 divides weight a.sub.q by a.sub.i and supplies the result to the arctan function 303, which supplies the phase .PHI.[k] to the difference block 305. The difference block generates the phase difference .DELTA..PHI.[k]=.PHI.[k]-.PHI.[k-1] and supplies the phase difference to the scaling block 307, which scales the phase difference by a weighting factor .mu.. Summer 309 adds the scaled phase difference (.mu.(.PHI.[k]-.PHI.[k-1]) to f.sub.target[k] to generate f.sub.target[k+1], which is supplied to the delay block 311. The frequency f.sub.target[k] is supplied as the frequency control word FCW to spur cancellation circuit. The initial spur frequency target may be loaded into the delay block 311 at power up or other reset condition. Note that if the phase difference is zero, the target spur frequency remains the same.

[0019] The embodiment illustrated in FIG. 3 assumes that the computation of the arctangent can be done within one clock cycle of the spur cancellation circuit. However, because the tracking rate for this loop is low, the loop can operate at a down-sampled rate in order to allow for efficient implementation. Thus, the arctangent function can take multiple clock cycles to complete, or use an iterative calculation method. The spur adaptation circuit may use custom logic to implement the various functions described in FIG. 3. In other embodiments, a microcontroller may be used to implement some or all of the functionality illustrated in FIG. 3.

[0020] FIG. 4 illustrates a high level flow diagram of operation of an embodiment of adaptive frequency tracking for spur cancellation. In 401 first phase information is extracted from parameters specifying the cancellation signal. In 403 the next phase sample is taken. In the embodiment of FIGS. 1-3 the phase information is extracted from the weights assigned to the sine and cosine signals. More generally, the spur cancellation requirement is that a spur cancellation circuit cancels a periodic signal, which could be sinusoidal, as shown in the embodiments shown in FIGS. 1-3, but could also be, for example, a square wave or a triangle wave. The spur cancellation circuit cancels the periodic signal by injecting an opposite signal to cancel the spur. Thus, in other embodiments the same adaptive frequency tracking approach shown in FIG. 3 is applied to other spur or tone cancellation systems. The requisite phase information can be extracted from the parameters specifying the cancellation signal whether the signal is a sinusoid, square wave, triangular wave, or other periodic signal, and the phase information can then be used to update the target frequency. Once the first phase information is generated 401, the adaptive frequency tracking takes another phase sample in 403. In 405, the difference between two phase samples is determined and the difference is scaled in 407. The scaled phase difference is then added to the target frequency in 409 to generate an updated target frequency. If the phase has not changed, the updated target frequency is unchanged. The direction of the phase change determines whether the target frequency increases or decreases. The adaptive frequency tracking then returns to 403 to obtain the next phase sample and continues to track frequency changes of the spur signal.

[0021] Thus, various aspects have been described relating to tracking of the spur frequency. The description of the invention set forth herein is illustrative, and is not intended to limit the scope of the invention as set forth in the following claims. Other variations and modifications of the embodiments disclosed herein, may be made based on the description set forth herein, without departing from the scope of the invention as set forth in the following claims.

* * * * *

D00000

D00001

D00002

D00003

D00004

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.