Semiconductor Device

YAMAZAKI; Shunpei

U.S. patent application number 16/691730 was filed with the patent office on 2020-03-19 for semiconductor device. This patent application is currently assigned to SEMICONDUCTOR ENERGY LABORATORY CO., LTD.. The applicant listed for this patent is SEMICONDUCTOR ENERGY LABORATORY CO., LTD.. Invention is credited to Shunpei YAMAZAKI.

| Application Number | 20200091154 16/691730 |

| Document ID | / |

| Family ID | 43921822 |

| Filed Date | 2020-03-19 |

View All Diagrams

| United States Patent Application | 20200091154 |

| Kind Code | A1 |

| YAMAZAKI; Shunpei | March 19, 2020 |

SEMICONDUCTOR DEVICE

Abstract

Disclosed is a semiconductor device capable of functioning as a memory device. The memory device comprises a plurality of memory cells, and each of the memory cells contains a first transistor and a second transistor. The first transistor is provided over a substrate containing a semiconductor material and has a channel formation region in the substrate. The second transistor has an oxide semiconductor layer. The gate electrode of the first transistor and one of the source and drain electrodes of the second transistor are electrically connected to each other. The extremely low off current of the second transistor allows the data stored in the memory cell to be retained for a significantly long time even in the absence of supply of electric power.

| Inventors: | YAMAZAKI; Shunpei; (Tokyo, JP) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Assignee: | SEMICONDUCTOR ENERGY LABORATORY

CO., LTD. ATSUGI-SHI JP |

||||||||||

| Family ID: | 43921822 | ||||||||||

| Appl. No.: | 16/691730 | ||||||||||

| Filed: | November 22, 2019 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 12913464 | Oct 27, 2010 | 10490553 | ||

| 16691730 | ||||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 21/46 20130101; H01L 29/7869 20130101; H01L 28/60 20130101; H01L 29/78693 20130101; H01L 21/8258 20130101; H01L 27/11551 20130101; H01L 27/11524 20130101; H01L 27/1156 20130101; G11C 11/405 20130101; H01L 27/1225 20130101; H01L 21/02664 20130101; H01L 27/0207 20130101; H01L 29/06 20130101; H01L 27/11521 20130101; H01L 27/11519 20130101; H01L 27/105 20130101; G11C 16/0433 20130101; H01L 29/7833 20130101 |

| International Class: | H01L 27/105 20060101 H01L027/105; H01L 27/11521 20060101 H01L027/11521; H01L 27/12 20060101 H01L027/12; H01L 27/11551 20060101 H01L027/11551; H01L 27/11524 20060101 H01L027/11524; G11C 11/405 20060101 G11C011/405; H01L 27/11519 20060101 H01L027/11519; G11C 16/04 20060101 G11C016/04; H01L 21/8258 20060101 H01L021/8258; H01L 27/1156 20060101 H01L027/1156; H01L 29/06 20060101 H01L029/06; H01L 29/786 20060101 H01L029/786; H01L 21/02 20060101 H01L021/02; H01L 21/46 20060101 H01L021/46 |

Foreign Application Data

| Date | Code | Application Number |

|---|---|---|

| Oct 29, 2009 | JP | 2009-249330 |

| Jan 22, 2010 | JP | 2010-012619 |

Claims

1. (canceled)

2. A semiconductor device comprising: a first transistor comprising a first gate electrode; and a second transistor comprising a second source electrode and a second drain electrode, wherein the second transistor includes an oxide semiconductor layer, the oxide semiconductor layer including a channel formation region, the channel formation region of the second transistor being intrinsic or substantially intrinsic, wherein the first gate electrode and one of the second source electrode and the second drain electrode are electrically connected to each other, and wherein an off current of the second transistor is 1.times.10.sup.-20 A or less.

3. The semiconductor device according to claim 2, further comprising an insulating layer over the first transistor, wherein the second transistor is provided over the insulating layer.

4. The semiconductor device according to claim 2, further comprising an insulating layer over the first transistor, wherein the second transistor is provided over the insulating layer, and wherein the second transistor overlaps with the first transistor.

5. The semiconductor device according to claim 2, further comprising a capacitor, wherein an electrode of the capacitor is connected to a node between the first gate electrode of the first transistor and the one of the second source electrode and the second drain electrode.

6. The semiconductor device according to claim 2, wherein the oxide semiconductor layer contains hydrogen at a concentration 5.times.10.sup.19 atoms/cm.sup.3 or less.

7. The semiconductor device according to claim 2, wherein a channel formation region of the first transistor comprises a compound semiconductor.

8. The semiconductor device according to claim 2, wherein a channel formation region of the first transistor comprises crystalline silicon.

9. The semiconductor device according to claim 2, wherein a node between the first gate electrode and the one of the second source electrode and the second drain electrode is configured to be electrically floating to store electric charges when the second transistor is in an off state.

10. A semiconductor device comprising: a first transistor comprising a first gate electrode; an insulating layer over the first transistor; and a second transistor comprising: an oxide semiconductor layer over the insulating layer; a gate insulating layer adjacent to the oxide semiconductor layer; and a second gate electrode adjacent to the oxide semiconductor layer with the gate insulating layer therebetween; wherein the first gate electrode and one of a source and a drain of the second transistor are electrically connected to each other, wherein the oxide semiconductor layer includes a channel formation region, and wherein the oxide semiconductor layer contains hydrogen at a concentration 5.times.10.sup.19 atoms/cm.sup.3 or less.

11. The semiconductor device according to claim 10, wherein an off current of the second transistor is 1.times.10.sup.-20 A or less.

12. The semiconductor device according to claim 10, further comprising a capacitor, wherein an electrode of the capacitor is connected to a node between the first gate electrode of the first transistor and the one of the source and the drain of the second transistor.

13. The semiconductor device according to claim 10, wherein a channel formation region of the first transistor comprises a compound semiconductor.

14. The semiconductor device according to claim 10, wherein a channel formation region of the first transistor comprises crystalline silicon.

15. A semiconductor device comprising: a first transistor comprising a first gate electrode; and a second transistor comprising a second gate electrode, a second source electrode and a second drain electrode, a first signal line electrically connected to one of the second source electrode and the second drain electrode; a second signal line electrically connected to the second gate electrode, wherein the second transistor includes an oxide semiconductor layer, the oxide semiconductor layer including a channel formation region, wherein the first gate electrode and the other one of the second source electrode and the second drain electrode are electrically connected to each other, and wherein an off current of the second transistor is 1.times.10.sup.-20 A or less.

16. The semiconductor device according to claim 15, further comprising a capacitor, wherein an electrode of the capacitor is connected to a node between the first gate electrode of the first transistor and the other one of the second source electrode and the second drain electrode.

17. The semiconductor device according to claim 15, wherein the oxide semiconductor layer contains hydrogen at a concentration 5.times.10.sup.19 atoms/cm.sup.3 or less.

18. The semiconductor device according to claim 15, wherein a channel formation region of the first transistor comprises a compound semiconductor.

19. The semiconductor device according to claim 15, wherein a channel formation region of the first transistor comprises crystalline silicon.

20. The semiconductor device according to claim 15, wherein a node between the first gate electrode and the other one of the second source electrode and the second drain electrode is configured to be electrically floating to store electric charges when the second transistor is in an off state.

21. The semiconductor device according to claim 15, wherein the second transistor is formed over the first transistor.

Description

CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application is a continuation of U.S. application Ser. No. 12/913,464, filed Oct. 27, 2010, now allowed, which claims the benefit of foreign priority applications filed in Japan as Serial No. 2009-249330 on Oct. 29, 2009, and Serial No. 2010-012619 on Jan. 22, 2010, all of which are incorporated by reference.

TECHNICAL FIELD

[0002] The invention disclosed herein relates to a semiconductor device using a semiconductor element and a method for manufacturing the semiconductor device.

BACKGROUND ART

[0003] Memory devices using semiconductor elements are broadly classified into two categories: a volatile device that loses stored data when power supply stops, and a non-volatile device that retains stored data even when power is not supplied.

[0004] A typical example of a volatile memory device is a DRAM (dynamic random access memory). A DRAM stores data in such a manner that a transistor included in a memory element is selected and charge is stored in a capacitor.

[0005] When data is read from a DRAM, charge in a capacitor is lost on the above-described principle; thus, another writing operation is necessary whenever data is read out. Moreover, a transistor included in a memory element has a leakage current and charge flows into or out of a capacitor even when the transistor is not selected, so that the data holding time is short. For that reason, another writing operation (refresh operation) is necessary at predetermined intervals, and it is difficult to sufficiently reduce power consumption. Furthermore, since stored data is lost when power supply stops, an additional memory device using a magnetic material or an optical material is needed in order to hold the data for a long time.

[0006] Another example of a volatile memory device is an SRAM (static random access memory). An SRAM retains stored data by using a circuit such as a flip-flop and thus does not need refresh operation. This means that an SRAM has an advantage over a DRAM. However, cost per storage capacity is increased because a circuit such as a flip-flop is used. Moreover, as in a DRAM, stored data in an SRAM is lost when power supply stops.

[0007] A typical example of a non-volatile memory device is a flash memory. A flash memory includes a floating gate between a gate electrode and a channel formation region in a transistor and stores data by holding charge in the floating gate. Therefore, a flash memory has advantages in that the data holding time is extremely long (almost permanent) and refresh operation which is necessary in a volatile memory device is not needed (e.g., see Patent Document 1).

[0008] However, a gate insulating layer included in a memory element deteriorates by tunneling current which flows in writing, so that the memory element stops its function after a numerous number of writing operations. In order to avoid this problem, a method in which the number of writing operations for memory elements is equalized is employed, for example. However, complicated supplemental circuits are additionally needed to realize this method. Moreover, employing such a method does not solve the fundamental problem of lifetime. In other words, a flash memory is not suitable for applications in which data is frequently rewritten.

[0009] In addition, high voltage is necessary for injecting charge to the floating gate or removing the charge. Further, it takes a relatively long time to injector remove charge, and it is not easy to perform writing and erasing at higher speed.

REFERENCE

[0010] Patent Document 1: Japanese Published Patent Application No. S57-105889

DISCLOSURE OF INVENTION

[0011] In view of the foregoing problems, an object of one embodiment of the invention disclosed herein is to provide a semiconductor device with a novel structure where stored data can be held even when power is not supplied and where there is no limitation on the number of times of writing.

[0012] One embodiment of the present invention is a semiconductor device having a layered structure of a transistor formed using an oxide semiconductor and a transistor formed using a material other than the oxide semiconductor. The following structures can be employed, for example.

[0013] An embodiment of the present invention is a semiconductor device including a first line (source line); a second line (bit line); a third line (first signal line); a fourth line (second signal line); a first transistor having a first gate electrode, a first source electrode, and a first drain electrode; and a second transistor having a second gate electrode, a second source electrode, and a second drain electrode. The first transistor is provided over a substrate including a semiconductor material. The second transistor includes an oxide semiconductor layer. The first gate electrode and one of the second source electrode and the second drain electrode are electrically connected to each other. The first line (source line) and the first source electrode are electrically connected to each other. The second line (bit line) and the first drain electrode are electrically connected to each other. The third line (first signal line) and the other of the second source electrode and the second drain electrode are electrically connected to each other. The fourth line (second signal line) and the second gate electrode are electrically connected to each other.

[0014] In the above structure, the first transistor includes a channel formation region provided over the substrate including the semiconductor material; impurity regions provided so as to sandwich the channel formation region; a first gate insulating layer over the channel formation region; the first gate electrode over the first gate insulating layer; and the first source electrode and the first drain electrode electrically connected to the impurity regions.

[0015] In the above structure, the second transistor includes the second gate electrode over the substrate including the semiconductor material; a second gate insulating layer over the second gate electrode; an oxide semiconductor layer over the second gate insulating layer; and the second source electrode and the second drain electrode electrically connected to the oxide semiconductor layer.

[0016] In the above structure, the substrate including the semiconductor material is preferably a single crystal semiconductor substrate or an SOI substrate. In particular, the semiconductor material is preferably silicon.

[0017] In the above structure, the oxide semiconductor layer preferably includes an In--Ga--Zn--O-based oxide semiconductor material. In particular, the oxide semiconductor layer preferably includes a crystal of In.sub.2Ga.sub.2ZnO.sub.7. Further, the hydrogen concentration of the oxide semiconductor layer is preferably 5.times.10.sup.19 atoms/cm.sup.3 or less. The off current of the second transistor is preferably 1.times.10.sup.-13 A or less, more preferably 1.times.10.sup.-20 A or less.

[0018] In the above structure, the second transistor can be provided in a region overlapping with the first transistor.

[0019] Note that in this specification, the term such as "over" or "below" does not necessarily mean that a component is placed "directly on" or "directly under" another component. For example, the expression "a first gate electrode over a gate insulating layer" does not exclude the case where a component is placed between the gate insulating layer and the gate electrode. Moreover, the terms such as "over" and "below" are only used for convenience of description and can include the case where the positional relation of components is reversed, unless otherwise specified.

[0020] In addition, in this specification, the term such as "electrode" or "line" does not limit a function of a component. For example, an "electrode" is sometimes used as part of a "line", and vice versa. Furthermore, the term "electrode" or "line" can include the case where a plurality of "electrodes" or "lines" are formed in an integrated manner.

[0021] Functions of a "source" and a "drain" are sometimes replaced with each other when a transistor of opposite polarity is used or when the direction of current flowing is changed in circuit operation, for example. Therefore, the terms "source" and "drain" can be replaced with each other in this specification and the like.

[0022] Note that in this specification, the term "electrically connected" includes the case where components are connected through an object having any electric function. There is no particular limitation on an object having any electric function as long as electric signals can be transmitted and received between components that are connected through the object.

[0023] Examples of an object having any electric function are a switching element such as a transistor, a resistor, an inductor, a capacitor, and an element with a variety of functions as well as an electrode and a line.

[0024] In general, the term SOI substrate.quadrature. means a substrate where a silicon semiconductor layer is provided on an insulating surface. In this specification, the term .quadrature.SOI substrate also includes a substrate where a semiconductor layer formed using a material other than silicon is provided over an insulating surface in its category. That is, a semiconductor layer included in the SOI substrate.quadrature. is not limited to a silicon semiconductor layer. A substrate in the "SOI substrate" is not limited to a semiconductor substrate such as a silicon wafer and can be a non-semiconductor substrate such as a glass substrate, a quartz substrate, a sapphire substrate, or a metal substrate. In other words, the .quadrature.SOI substrate.quadrature. also includes a conductive substrate having an insulating surface or an insulating substrate provided with a layer formed of a semiconductor material in its category. In addition, in this specification, the term "semiconductor substrate" means not only a substrate formed using only a semiconductor material but also all substrates including a semiconductor material. That is, in this specification, the "SOI substrate" is also included in the category of the "semiconductor substrate".

[0025] One embodiment of the present invention provides a semiconductor device in which a transistor including a material other than an oxide semiconductor is placed in a lower portion and a transistor including an oxide semiconductor is placed in an upper portion.

[0026] Since the off current of a transistor including an oxide semiconductor is extremely low, stored data can be retained for an extremely long time by using the transistor. In other words, power consumption can be considerably reduced because refresh operation becomes unnecessary or the frequency of refresh operation can be extremely low. Moreover, stored data can be retained for a long time even when power is not supplied.

[0027] Further, high voltage is not needed to write data, and deterioration of the element is negligible. Furthermore, data is written by switching between the on state and the off state of the transistor, whereby high-speed operation can be easily realized. In addition, since data can be rewritten by controlling a potential input to the transistor, there is no need of operation for erasing data, which is another merit.

[0028] Since a transistor including a material other than an oxide semiconductor can operate at higher speed than a transistor including an oxide semiconductor, stored data can be read out at high speed by using the transistor.

[0029] A semiconductor device with a novel feature can be realized by including both the transistor including a material other than an oxide semiconductor and the transistor including an oxide semiconductor.

BRIEF DESCRIPTION OF DRAWINGS

[0030] In the accompanying drawings:

[0031] FIG. 1 is a circuit diagram of a semiconductor device;

[0032] FIGS. 2A and 2B are a cross-sectional view and a plan view for illustrating a semiconductor device;

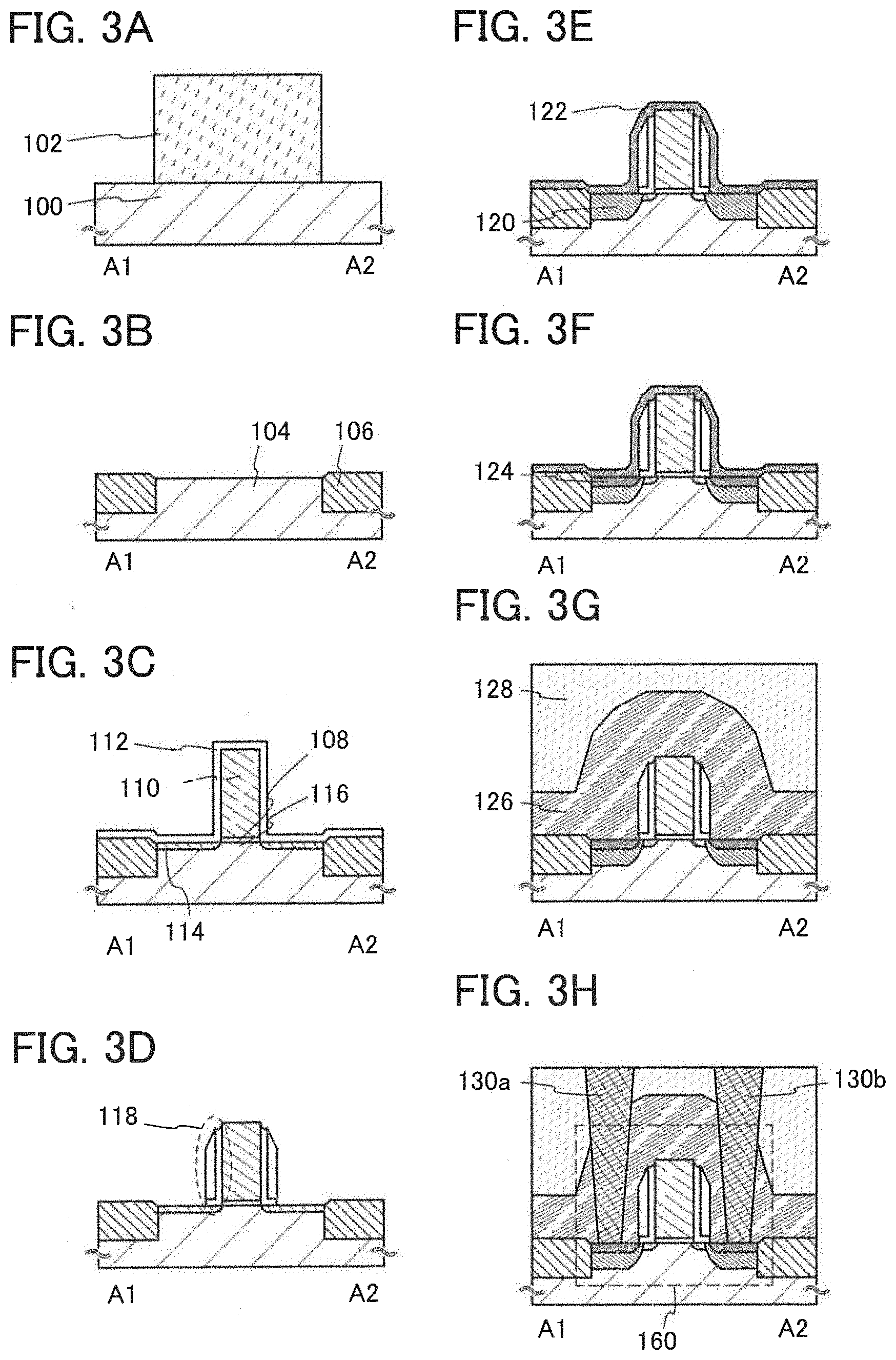

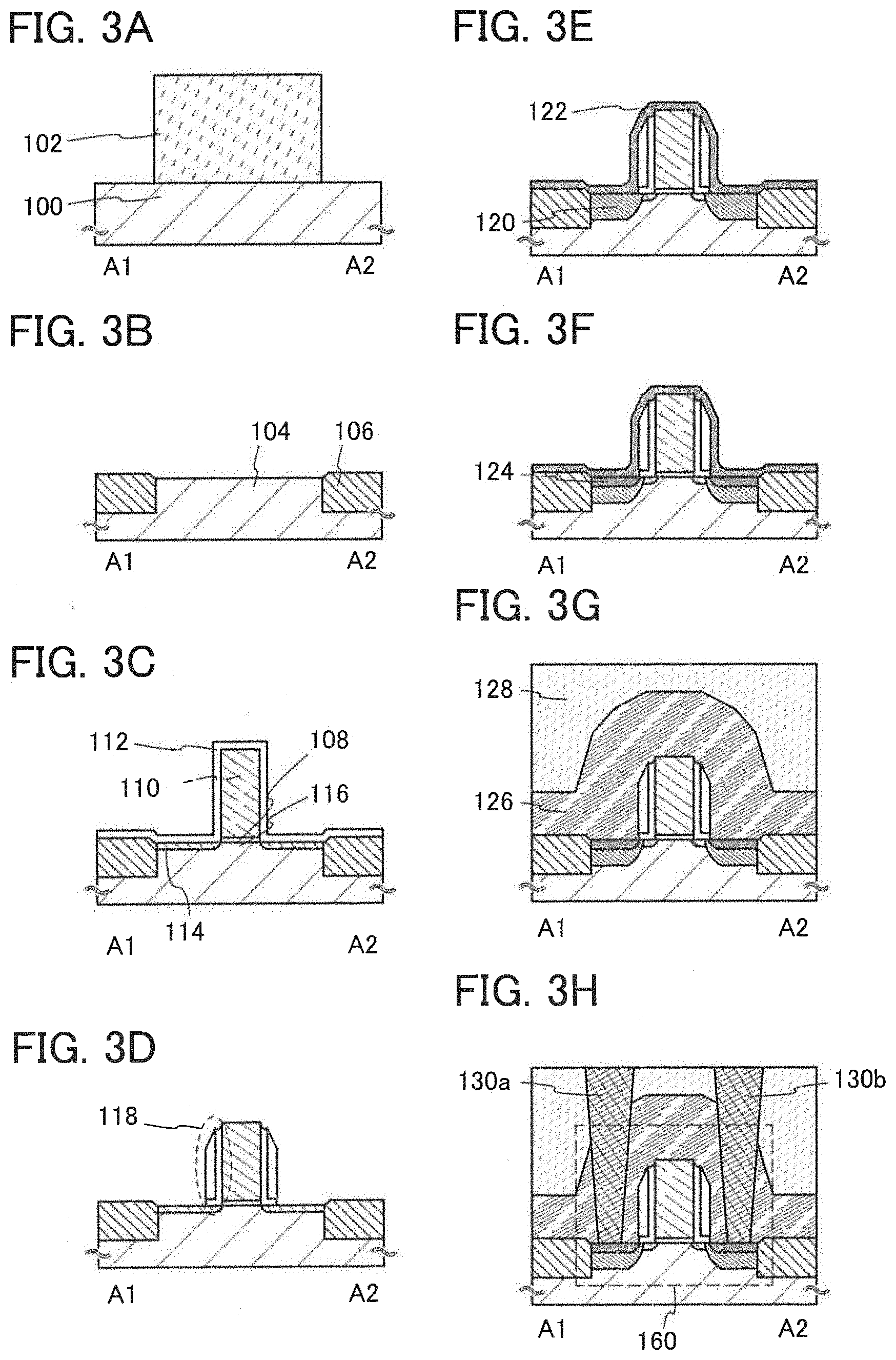

[0033] FIGS. 3A to 3H are cross-sectional views illustrating steps for manufacturing a semiconductor device;

[0034] FIGS. 4A to 4G are cross-sectional views illustrating steps for manufacturing a semiconductor device;

[0035] FIGS. 5A to 5D are cross-sectional views illustrating steps for manufacturing a semiconductor device;

[0036] FIG. 6 is a cross-sectional view of a semiconductor device;

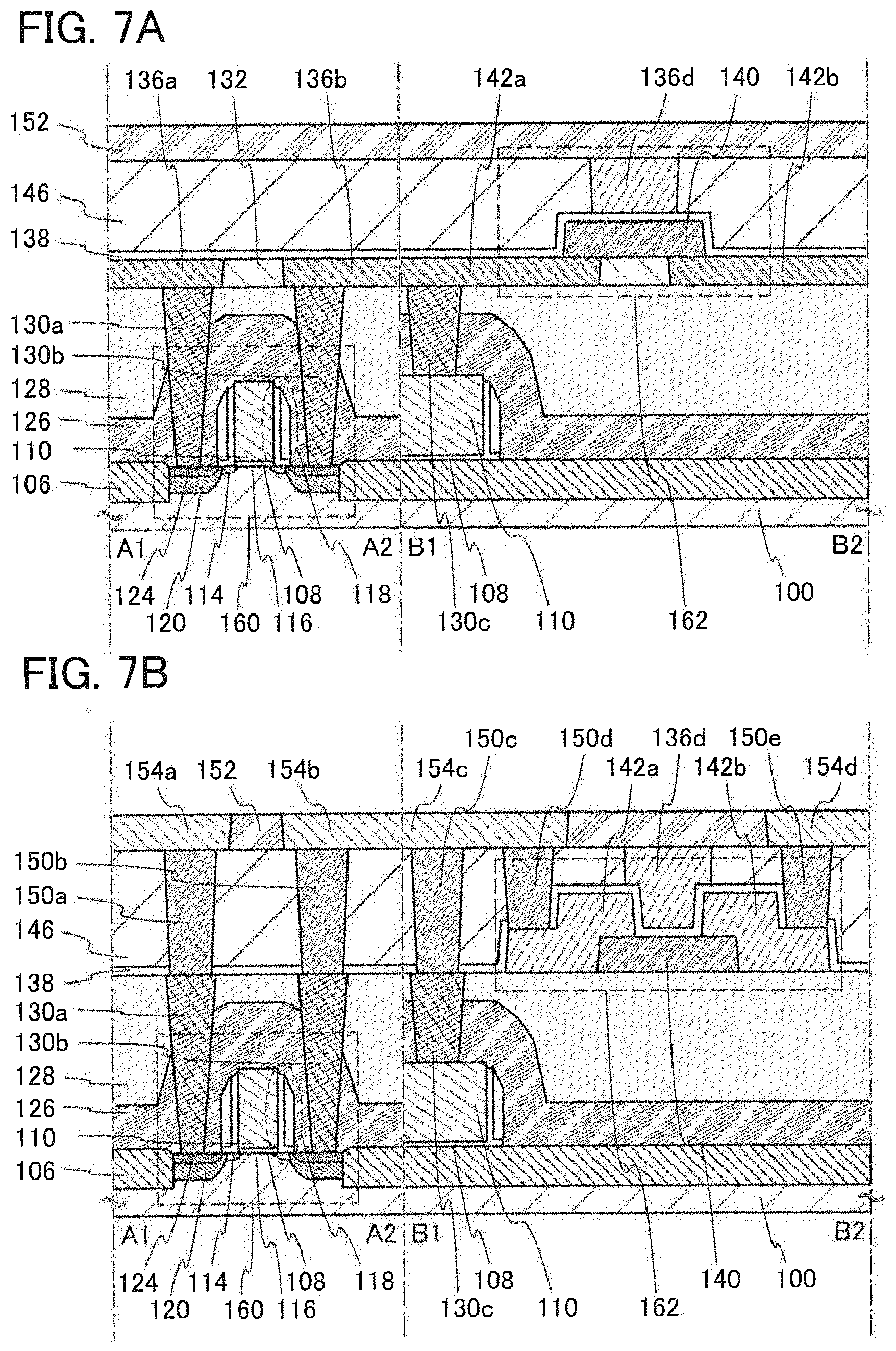

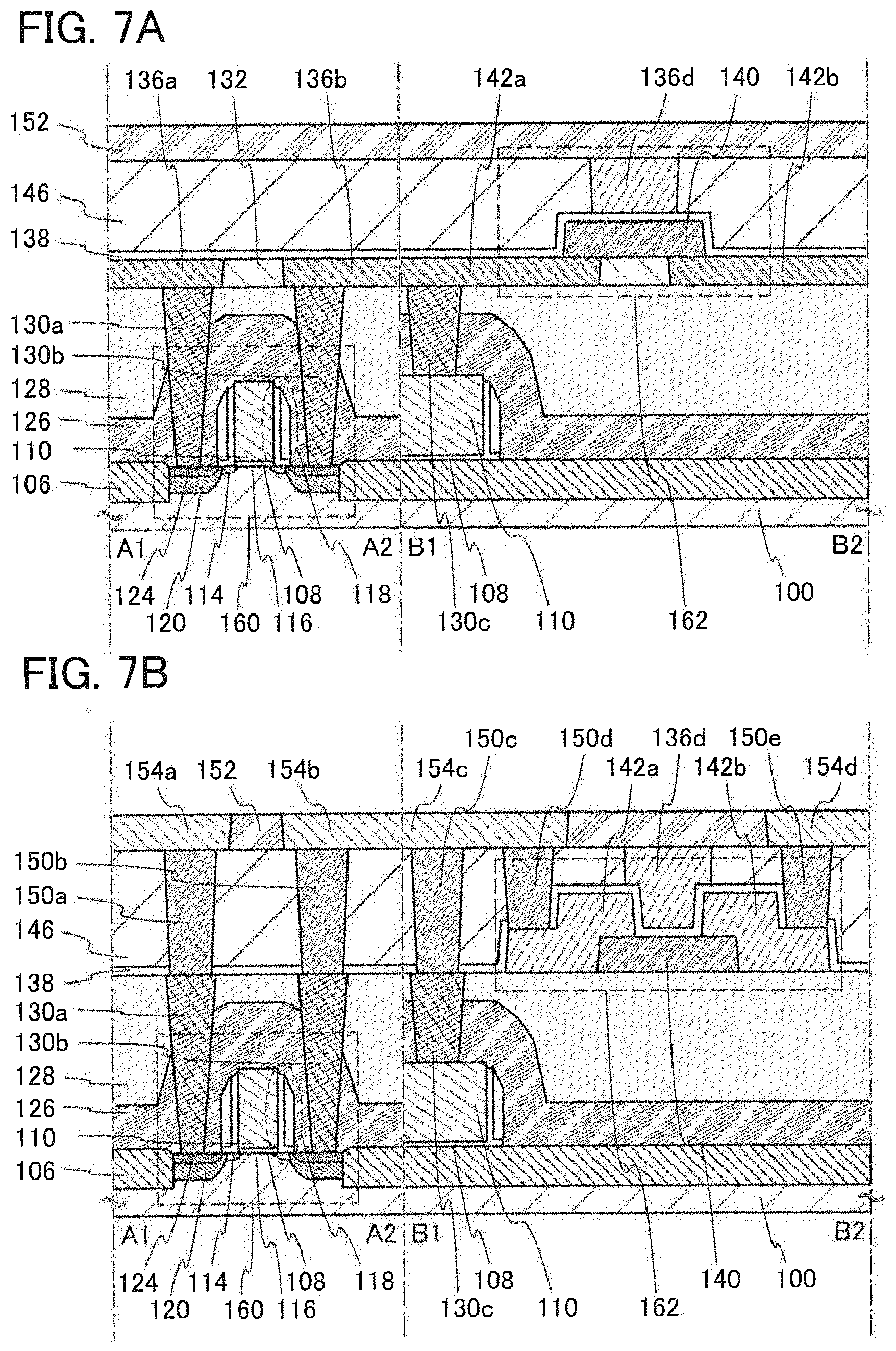

[0037] FIGS. 7A and 7B are cross-sectional views each illustrating a semiconductor device;

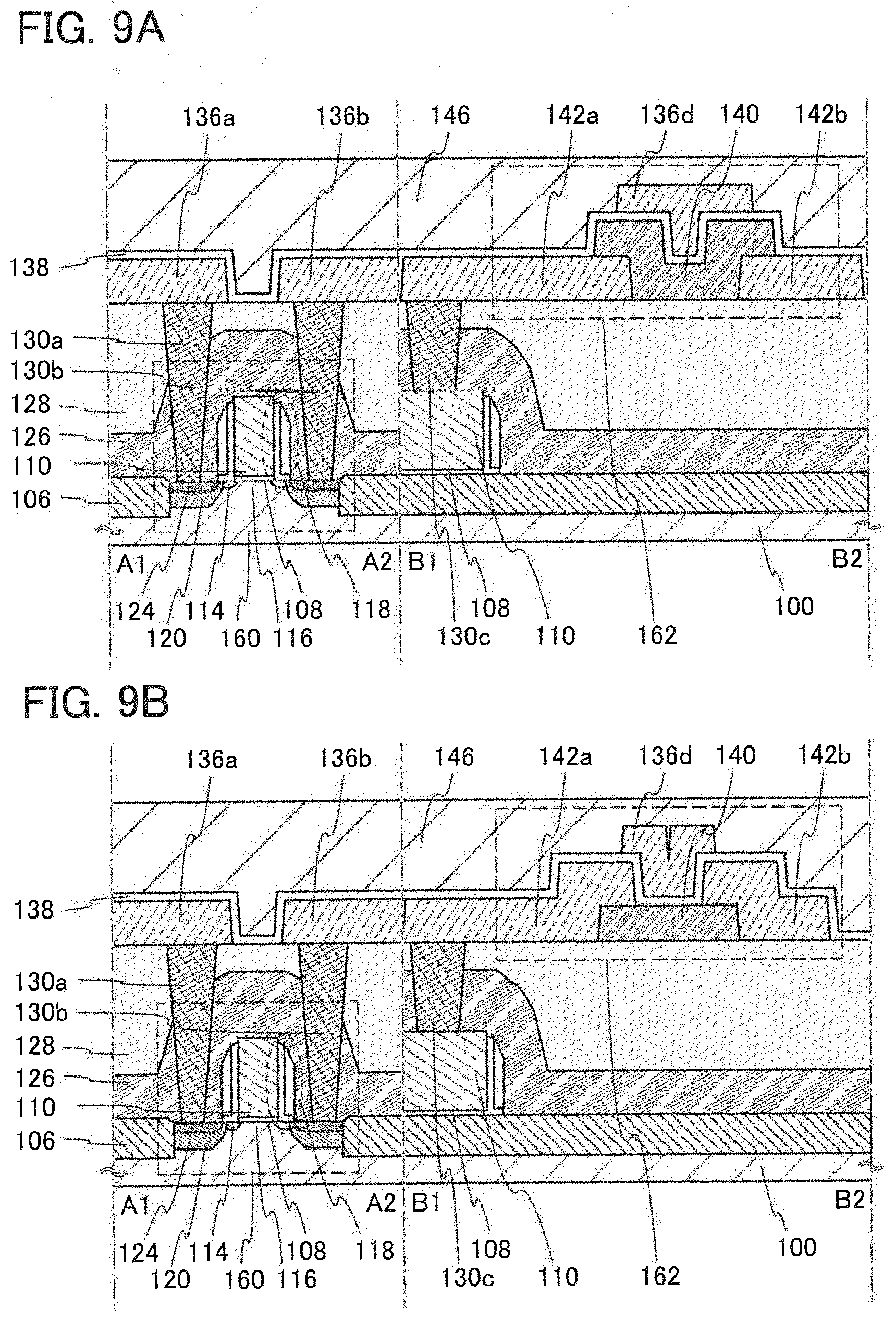

[0038] FIGS. 8A and 8B are cross-sectional views each illustrating a semiconductor device;

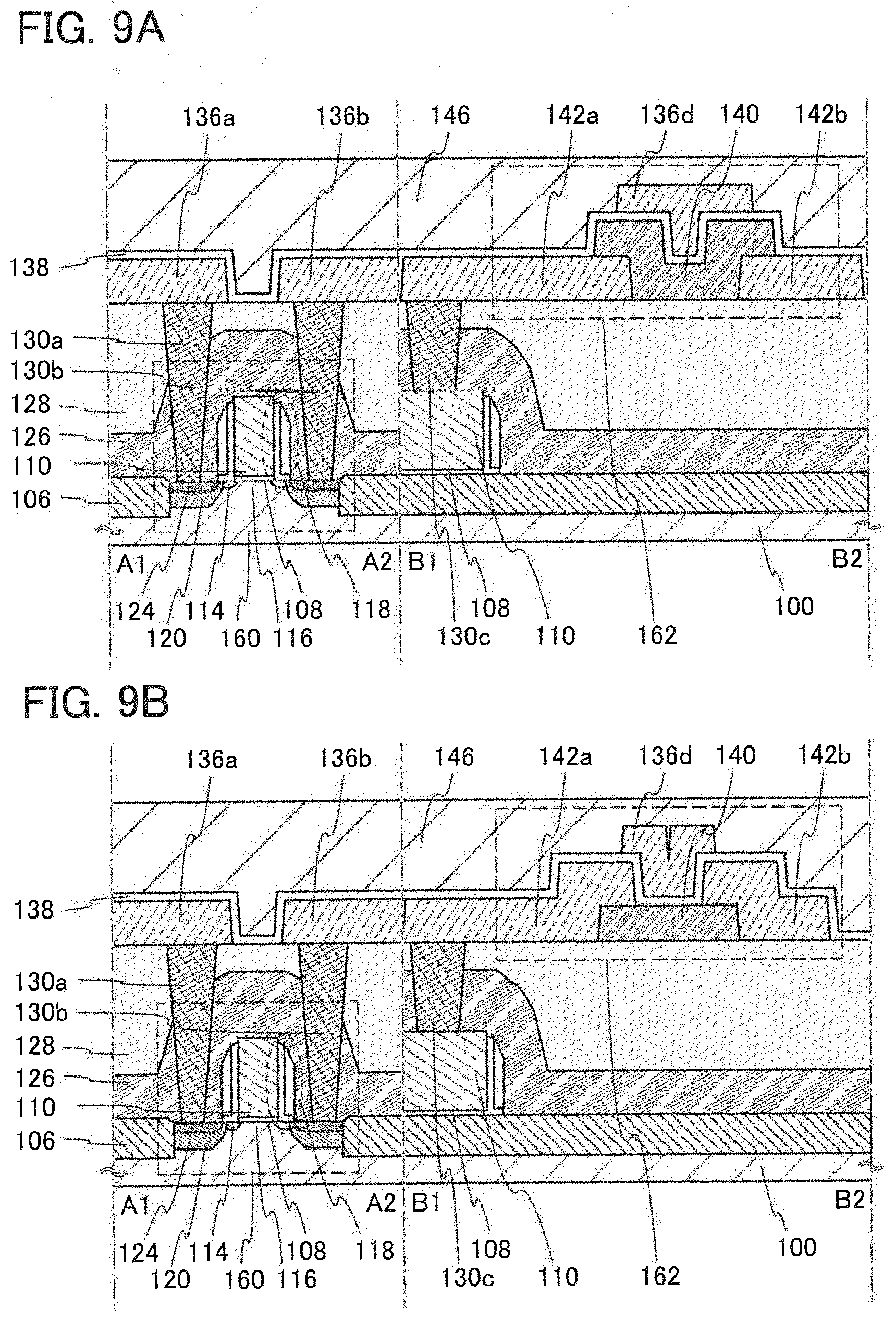

[0039] FIGS. 9A and 9B are cross-sectional views each illustrating a semiconductor device;

[0040] FIGS. 10A to 10F each illustrate an electronic device;

[0041] FIG. 11 is a cross-sectional view of an inverted staggered transistor including an oxide semiconductor;

[0042] FIGS. 12A and 12B are energy band diagrams (schematic diagrams) of a cross section A-A' in FIG. 11;

[0043] FIG. 13A illustrates a state in which a positive potential (+V.sub.G) is applied to a gate (GE1), and FIG. 13B illustrates a state in which a negative potential (-V.sub.G) is applied to the gate (GE1); and

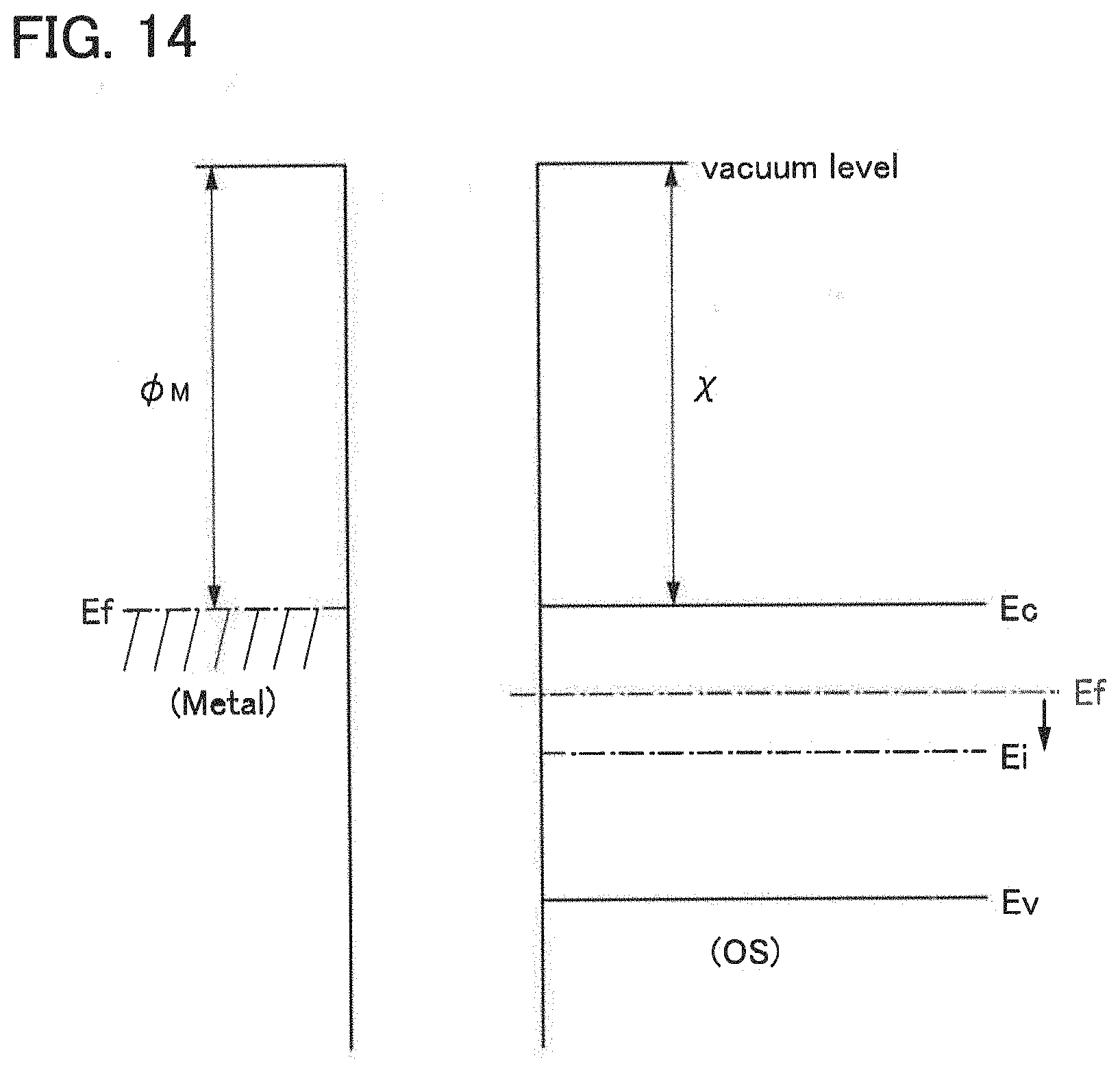

[0044] FIG. 14 illustrates a relation of vacuum level, work function (.phi..sub.M) of a metal, and electron affinity (.chi.) of an oxide semiconductor;

[0045] FIGS. 15A and 15B are circuit diagrams of semiconductor devices;

[0046] FIG. 16 is a circuit diagram of a semiconductor device;

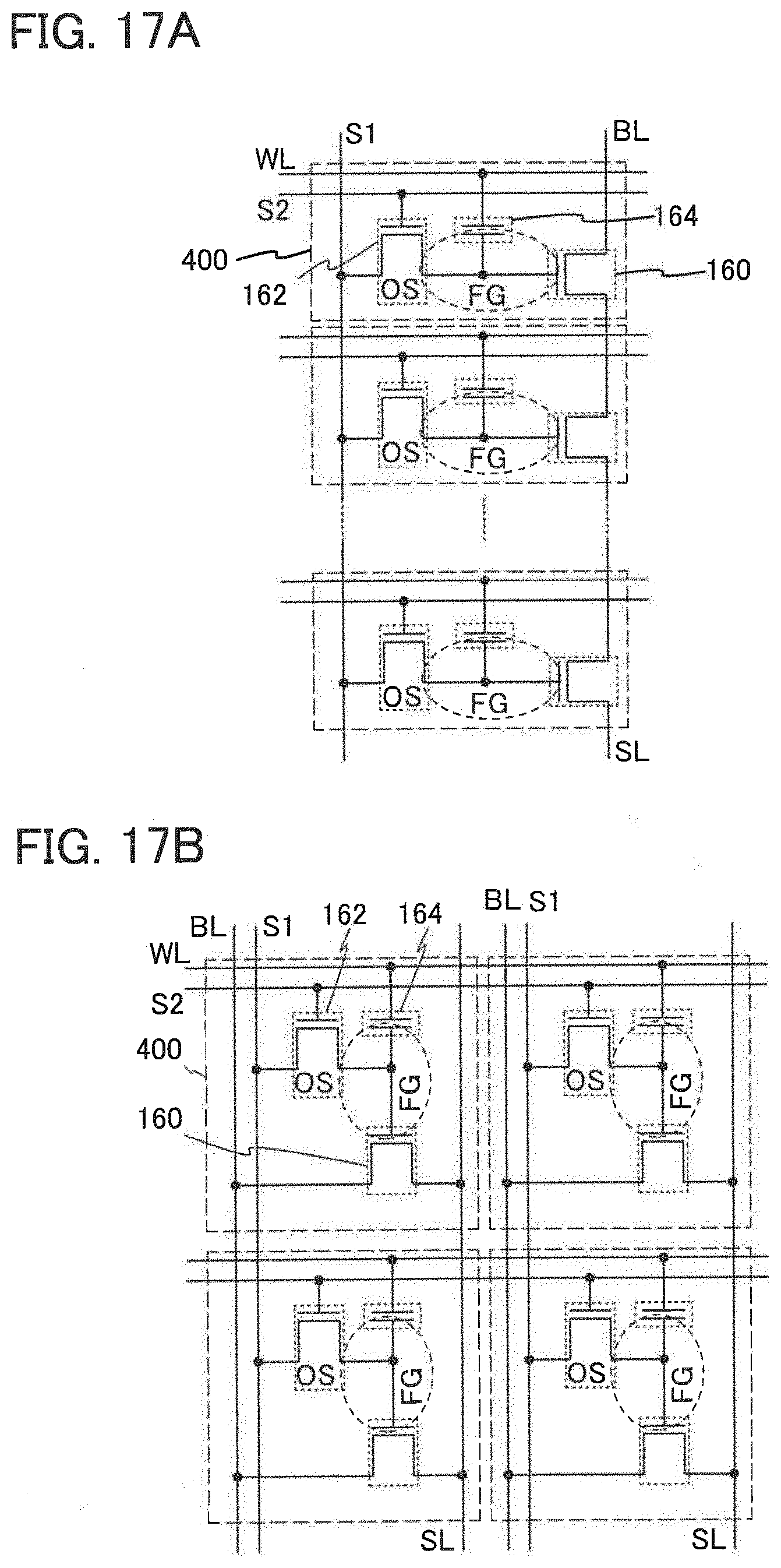

[0047] FIGS. 17A and 17B are circuit diagrams of semiconductor devices;

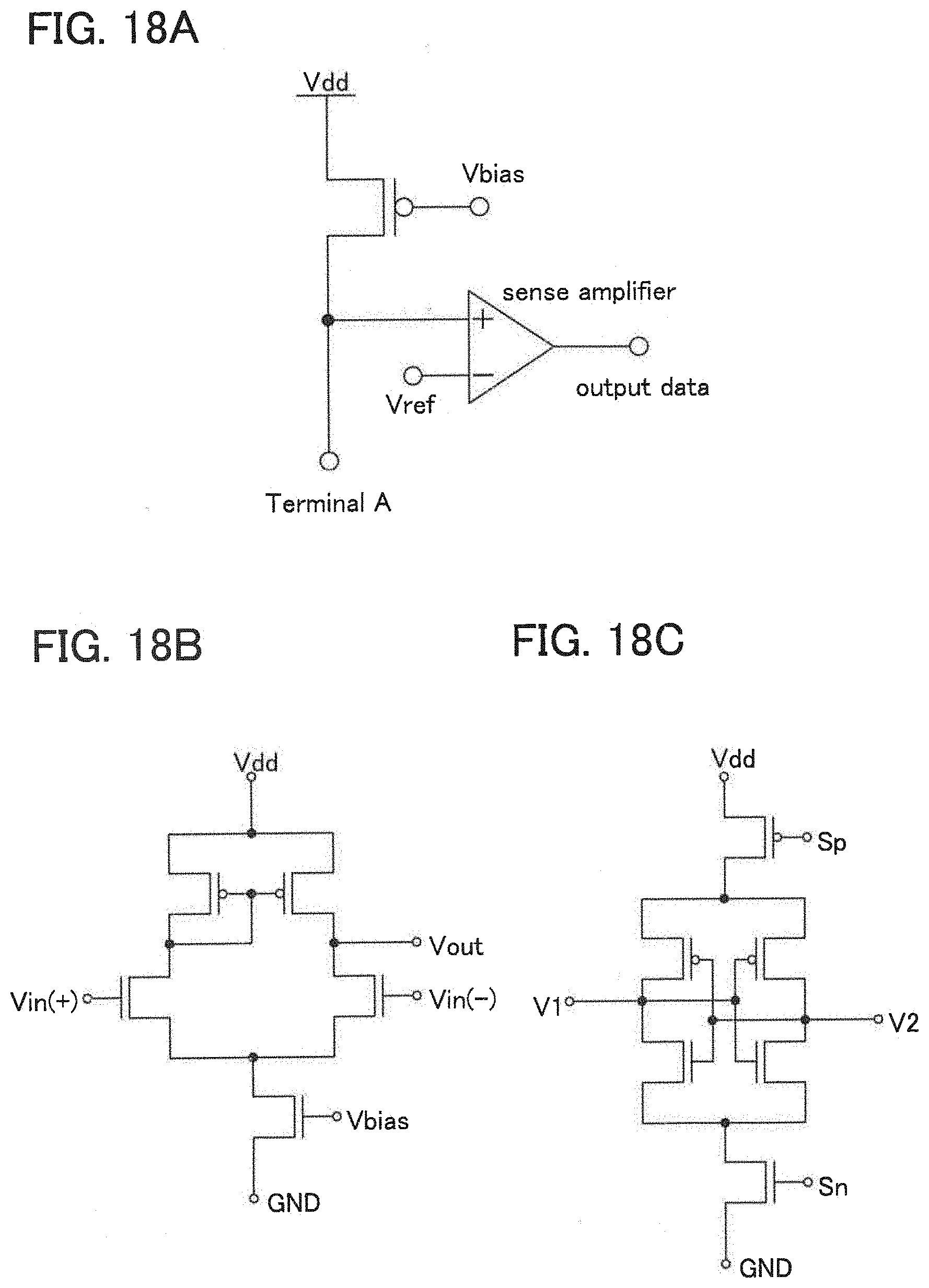

[0048] FIGS. 18A to 18C are circuit diagrams of a semiconductor device;

[0049] FIG. 19 is a circuit diagram of a semiconductor device;

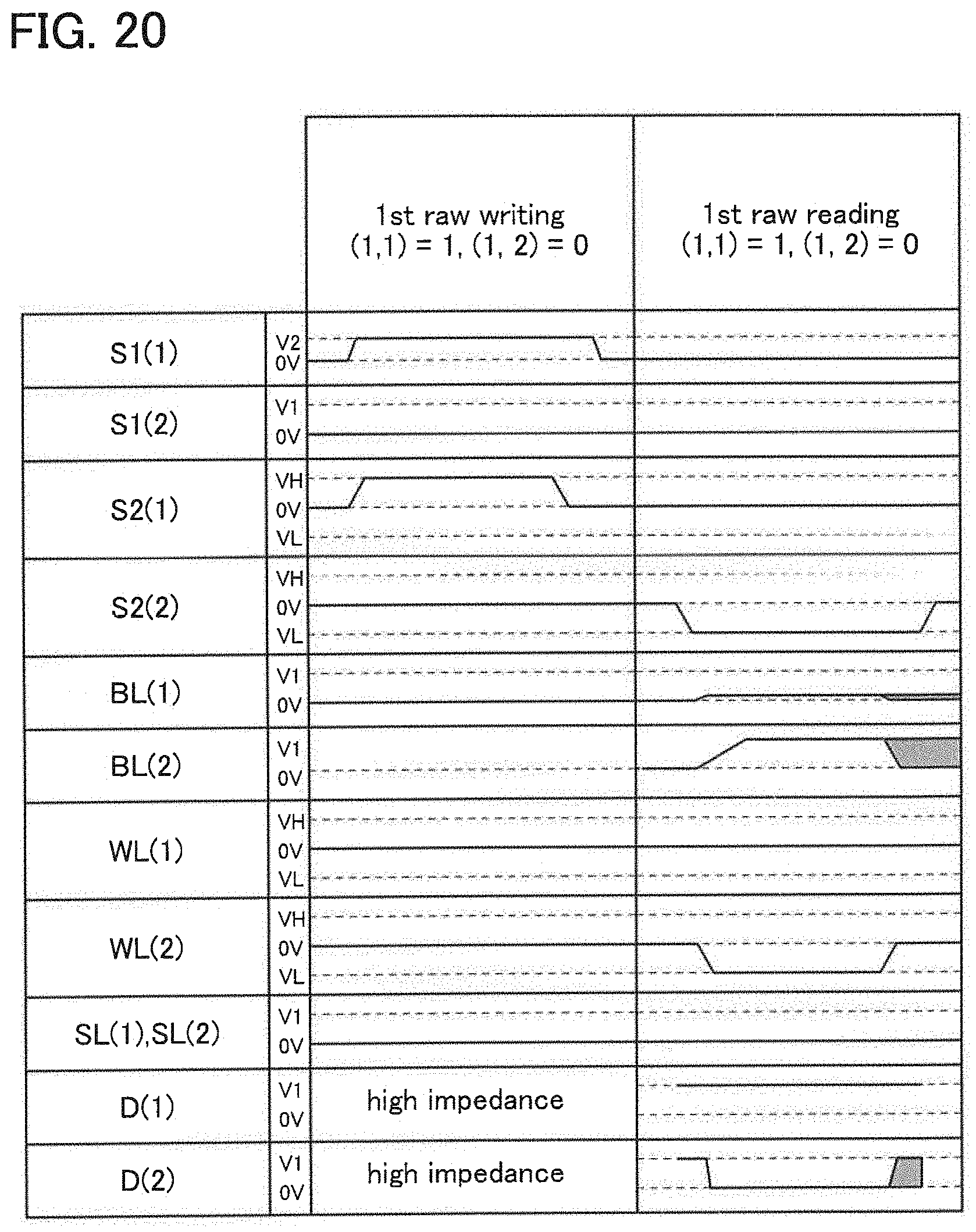

[0050] FIG. 20 is a timing chart for illustrating the relation of potentials;

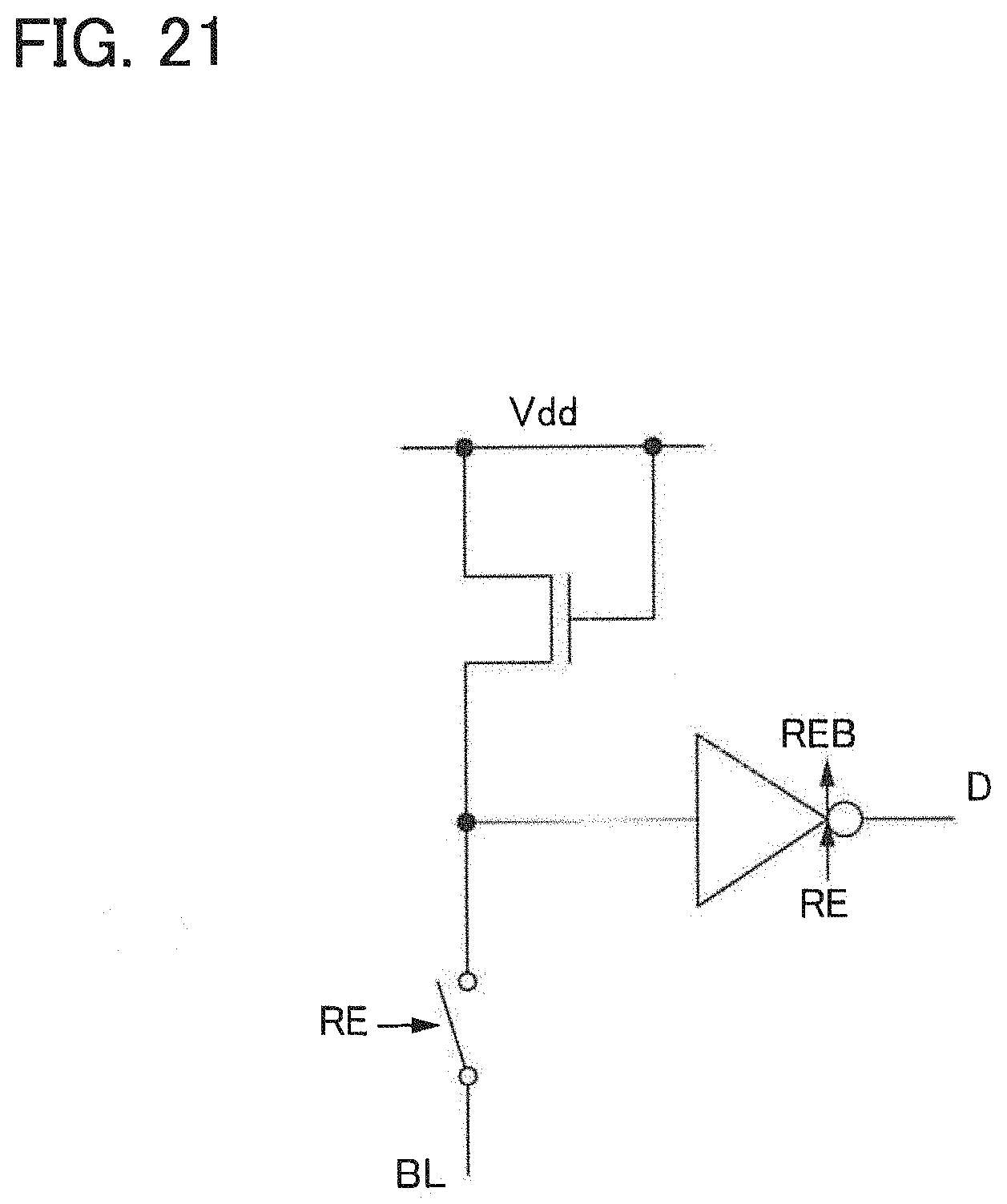

[0051] FIG. 21 is a circuit diagram of a semiconductor device;

[0052] FIGS. 22A and 22B are a cross-sectional view and a plan view for illustrating a semiconductor device;

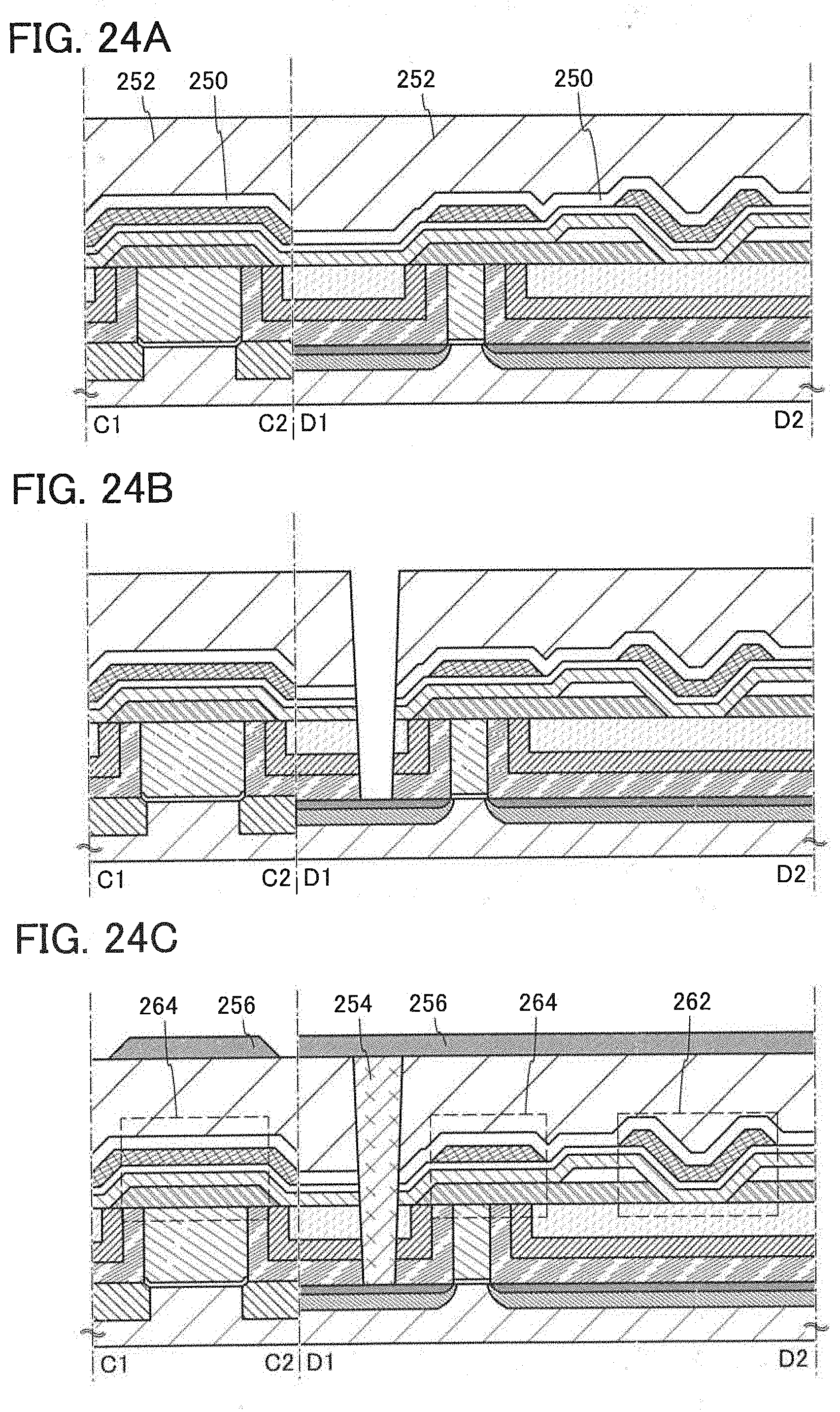

[0053] FIGS. 23A to 23D are cross-sectional views illustrating the semiconductor device;

[0054] FIGS. 24A to 24C are cross-sectional views illustrating the semiconductor device;

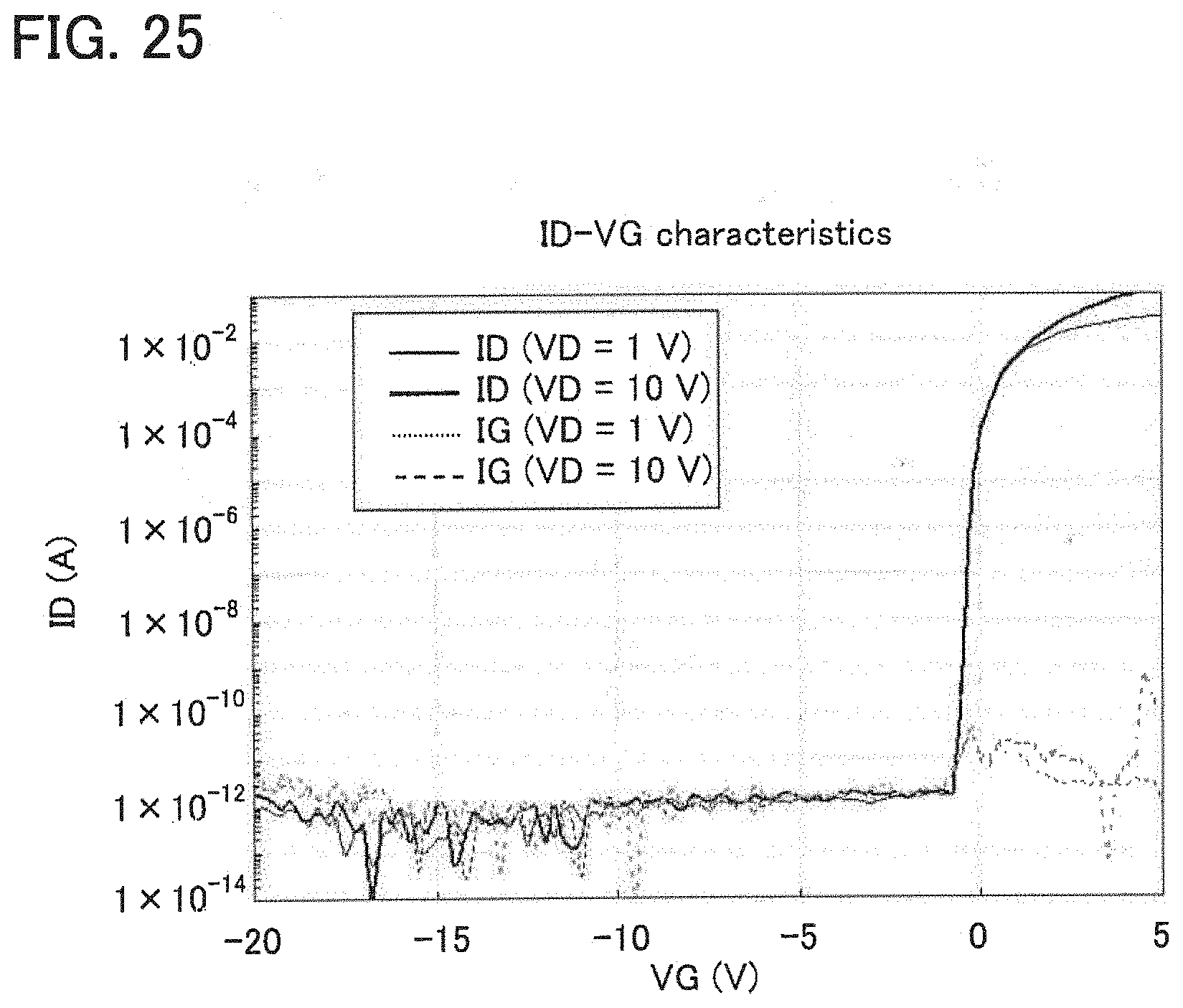

[0055] FIG. 25 is a graph showing characteristics of a transistor including an oxide semiconductor;

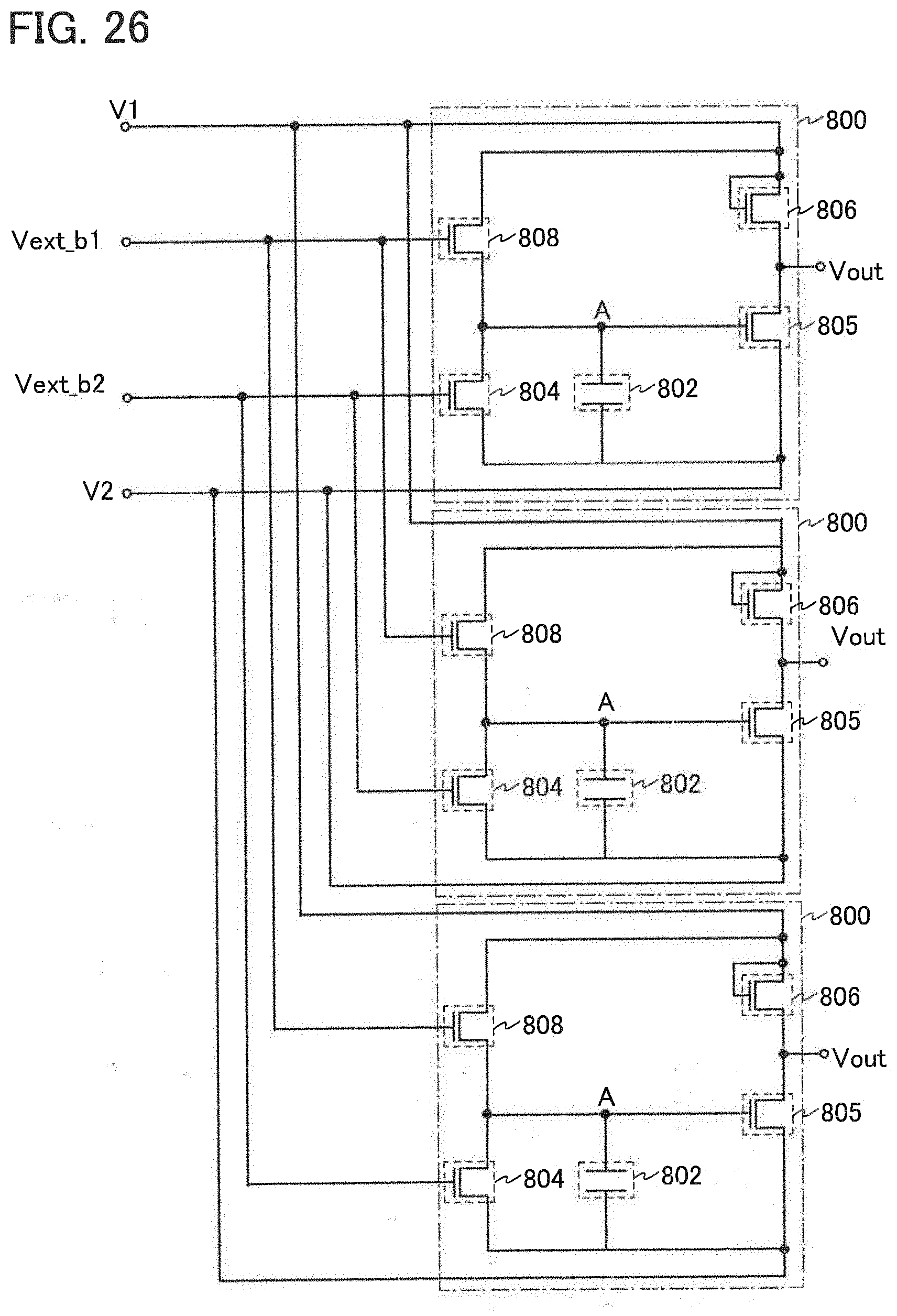

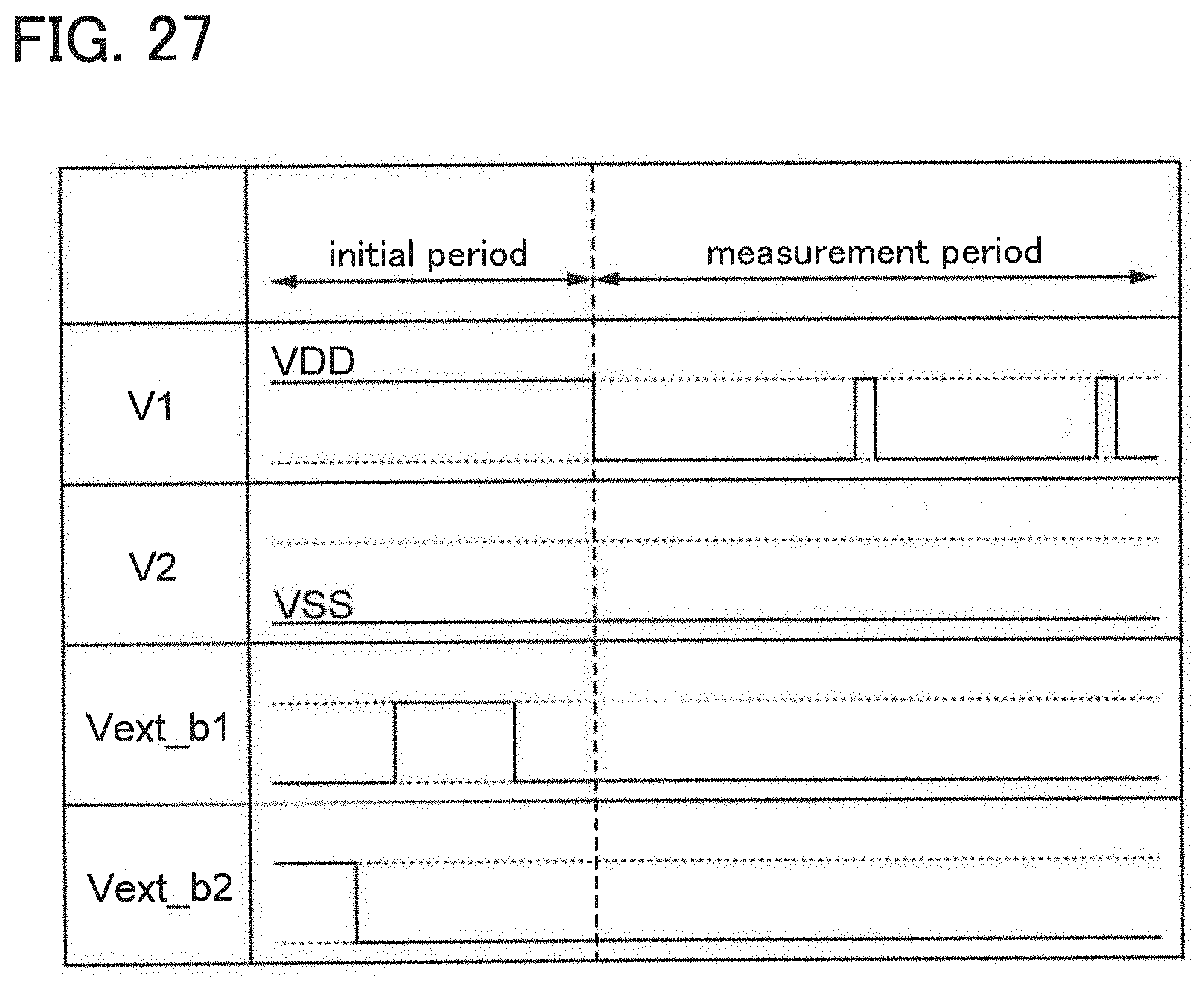

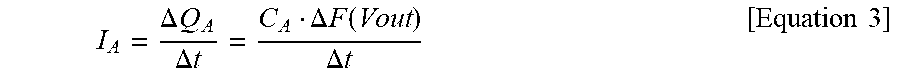

[0056] FIG. 26 is a circuit diagram for evaluating characteristics of a transistor including an oxide semiconductor;

[0057] FIG. 27 is a timing chart for evaluating characteristics of a transistor including an oxide semiconductor;

[0058] FIG. 28 is a graph showing characteristics of a transistor including an oxide semiconductor;

[0059] FIG. 29 is a graph showing characteristics of a transistor including an oxide semiconductor; and

[0060] FIG. 30 is a graph showing characteristics of a transistor including an oxide semiconductor.

[0061] FIG. 31 is a graph showing evaluation results of a memory window width.

BEST MODE FOR CARRYING OUT THE INVENTION

[0062] Examples of embodiments of the present invention will be described below with reference to the accompanying drawings. Note that the present invention is not limited to the following description, and it is easily understood by those skilled in the art that modes and details disclosed herein can be modified in various ways without departing from the spirit and the scope of the present invention. Therefore, the present invention is not to be construed as being limited to the content of the embodiments included herein.

[0063] Note that the position, the size, the range, or the like of each structure illustrated in drawings is not accurately represented in some cases for easy understanding. Therefore, embodiments of the present invention are not necessarily limited to such a position, size, range, or the like disclosed in the drawings.

[0064] In this specification, ordinal numbers such as "first", "second", and "third" are used in order to avoid confusion among components, and the terms do not mean limitation of the number of components.

Embodiment 1

[0065] In this embodiment, a structure and a manufacturing method of a semiconductor device according to one embodiment of the invention disclosed herein will be described with reference to FIG. 1, FIGS. 2A and 2B, FIGS. 3A to 3H, FIGS. 4A to 4G, FIGS. 5A to 5D, FIG. 6, FIGS. 7A and 7B, FIGS. 8A and 8B, and FIGS. 9A and 9B.

<Circuit Configuration of Semiconductor Device>

[0066] FIG. 1 illustrates an example of a circuit configuration of a semiconductor device. The semiconductor device includes a transistor 160 formed using a material other than an oxide semiconductor (e.g., silicon), and a transistor 162 formed using an oxide semiconductor. Note that the semiconductor device illustrated in FIG. 1 is called a memory cell in some cases in the following description.

[0067] Here, a gate electrode of the transistor 160 is electrically connected to one of a source electrode and a drain electrode of the transistor 162. A first line (also referred to as a source line SL) is electrically connected to a source electrode of the transistor 160. A second line (also referred to as a bit line BL) is electrically connected to a drain electrode of the transistor 160. A third line (also referred to as a first signal line) is electrically connected to the other of the source electrode and the drain electrode of the transistor 162. A fourth line (also referred to as a second signal line) is electrically connected to a gate electrode of the transistor 162.

[0068] Since the transistor 160 including a material other than an oxide semiconductor can operate at higher speed than a transistor including an oxide semiconductor, stored data can be read out at high speed by using the transistor 160. Moreover, the transistor 162 including an oxide semiconductor has extremely low off current. For those reasons, a potential of the gate electrode of the transistor 160 can be held for an extremely long time by turning off the transistor 162. In addition, in the transistor 162 including an oxide semiconductor, a short channel effect does not occur, which is another merit.

[0069] Writing, holding, and reading of data can be performed in the following manner, using the advantage that the potential of the gate electrode can be held.

[0070] Firstly, writing and holding of data will be described. First, a potential of the fourth line is set to a potential at which the transistor 162 is turned on, and the transistor 162 is turned on. Thus, a potential of the third line is supplied to the gate electrode of the transistor 160 (writing). After that, the potential of the fourth line is set to a potential at which the transistor 162 is turned off, and the transistor 162 is turned off, whereby the potential of the gate electrode of the transistor 160 is held (holding).

[0071] Since the off current of the transistor 162 is extremely low, the potential of the gate electrode of the transistor 160 is held for a long time. For example, when the potential of the gate electrode of the transistor 160 is a potential at which the transistor 160 is turned on, the on state of the transistor 160 is kept for a long time. Moreover, when the potential of the gate electrode of the transistor 160 is a potential at which the transistor 160 is turned off, the off state of the transistor 160 is kept for a long time.

[0072] Secondly, reading of data will be described. When a predetermined potential (a low potential) is supplied to the first line in a state where the on state or the off state of the transistor 160 is kept as described above, a potential of the second line varies depending on the on state or the off state of the transistor 160. For example, when the transistor 160 is on, the potential of the second line becomes lower under the influence of the potential of the first line. In contrast, when the transistor 160 is off, the potential of the second line is not changed.

[0073] In such a manner, the potential of the second line and a predetermined potential are compared with each other in a state where data is held, whereby the data can be read out.

[0074] Thirdly, rewriting of data will be described. Rewriting of data is performed in a manner similar to that of the writing and holding of data. That is, the potential of the fourth line is set to a potential at which the transistor 162 is turned on, and the transistor 162 is turned on. Thus, a potential of the third line (a potential for new data) is supplied to the gate electrode of the transistor 160. After that, the potential of the fourth line is set to a potential at which the transistor 162 is turned off, and the transistor 162 is turned off, whereby the new data is stored.

[0075] In the semiconductor device according to the invention disclosed herein, data can be directly rewritten by another writing of data as described above. For that reason, erasing operation which is necessary for a flash memory or the like is not needed, so that a reduction in operation speed caused by the erasing operation can be prevented. In other words, high-speed operation of the semiconductor device can be realized.

[0076] Since an off current of the transistor 162 for writing, which includes an oxide semiconductor, is extremely small, the potential of the gate electrode of the transistor 160 is held for a long time. Therefore, for example, refresh operation needed for a conventional DRAM can be unnecessary, or the frequency of refresh operation can be significantly low (e.g., about once a month or a year). Thus, the semiconductor device according to the disclosed invention substantially has a feature of a nonvolatile memory device.

[0077] Further, in the semiconductor device of the disclosed invention, data is not lost when data is read unlike in a conventional DRAM; thus, rewriting of data is not necessary in every reading operation. As described above, the frequency of data writing can be significantly reduced as compared to a DRAM, which enables a sufficient reduction in power consumption.

[0078] Further, as for the semiconductor device according to the disclosed invention, data can be directly rewritten by overwriting of new data to the semiconductor device. Therefore, erasing operation which is necessary for a flash memory or the like is not needed, and reduction in operation speed, which is attributed to erasing operation, can be suppressed. In other words, high-speed operation of the semiconductor device can be realized. Moreover, a high voltage necessary for a conventional floating gate transistor to write and erase data is unnecessary; thus, power consumption of the semiconductor device can be further reduced.

[0079] The semiconductor device according to the disclosed invention may include at least a writing transistor and a reading transistor; therefore, the area of each memory cell can be sufficiently small as compared to an SRAM or the like which requires six transistors in each memory cell. In other words, such semiconductor devices can be arranged at high density.

[0080] In a conventional floating gate transistor, charge travels in a gate insulating film (tunnel insulating film) during writing operation, so that deterioration of the gate insulating film (tunnel insulating film) cannot be avoided. In contrast, in the memory cell according to an embodiment of the present invention, data is written by switching operation of a writing transistor; therefore, the deterioration of a gate insulating film, which has been traditionally recognized as a problem, can be neglected. This means that there is no limit on the number of times of writing in principle and writing durability is very high. For example, the current-voltage characteristics are not degraded even after data is written 1.times.10.sup.9 or more times (one billion or more times).

[0081] Note that the field effect mobility of the transistor 162 for writing, which includes an oxide semiconductor, is 3 cm.sup.2/Vs to 250 cm.sup.2/Vs inclusive, preferably 5 cm.sup.2/Vs to 200 cm.sup.2/Vs inclusive, more preferably 10 cm.sup.2/Vs to 150 cm.sup.2/Vs inclusive, in an on state. Further, the subthreshold swing (S value) of the transistor including an oxide semiconductor is set to 0.1 V/dec. or less. With the use of such a transistor, time needed for data writing can be short enough.

[0082] The channel length L of the transistor 162 for writing, which includes an oxide semiconductor, is preferably 10 nm to 400 nm inclusive. With such a channel size, various effects such as high-speed operation, low power consumption, and high integration of the transistor can be obtained.

[0083] Note that a transistor including crystalline silicon is preferably used for the transistor 160 for reading. In particular, in terms of increasing speed of reading operation, an n-channel transistor including single crystal silicon is preferably used. Such a single crystal silicon transistor can be formed using, for example, bulk silicon (a so-called silicon wafer).

[0084] Note that an n-channel transistor is used in the above description; it is needless to say that a p-channel transistor can be used instead of the n-channel transistor.

<Planar Structure and Cross-Sectional Structure of Semiconductor Device>

[0085] FIGS. 2A and 2B illustrate an example of a structure of the semiconductor device. FIG. 2A illustrates a cross section of the semiconductor device, and FIG. 2B illustrates a plan view of the semiconductor device. Here, FIG. 2A corresponds to a cross section along line A1-A2 and line B1-B2 in FIG. 2B. The semiconductor device illustrated in FIGS. 2A and 2B includes the transistor 160 including a material other than an oxide semiconductor in a lower portion, and the transistor 162 including an oxide semiconductor in an upper portion. Note that the transistors 160 and 162 are n-channel transistors here; alternatively, a p-channel transistor may be used. In particular, it is easy to use a p-channel transistor as the transistor 160.

[0086] The transistor 160 includes a channel formation region 116 provided in a substrate 100 including a semiconductor material, impurity regions 114 and high-concentration impurity regions 120 (these regions can be collectively referred to simply as impurity regions) provided so as to sandwich the channel formation region 116, a gate insulating layer 108 provided over the channel formation region 116, a gate electrode 110 provided over the gate insulating layer 108, and a source electrode or drain electrode (hereinafter referred to as a source/drain electrode) 130a and a source/drain electrode 130b electrically connected to the impurity regions 114.

[0087] A sidewall insulating layer 118 is provided on a side surface of the gate electrode 110. The high-concentration impurity region 120 is placed in a region of the substrate 100 that does not overlap with the sidewall insulating layer 118 as shown in the cross-sectional view. A metal compound region 124 is placed over the high-concentration impurity region 120. An element isolation insulating layer 106 is provided over the substrate 100 so as to surround the transistor 160. An interlayer insulating layer 126 and an interlayer insulating layer 128 are provided so as to cover the transistor 160. Each of the source/drain electrode 130a and the source/drain electrode 130b is electrically connected to the metal compound region 124 through an opening formed in the interlayer insulating layers 126 and 128. That is, each of the source/drain electrodes 130a and 130b is electrically connected to the high-concentration impurity region 120 and the impurity region 114 through the metal compound region 124. An electrode 130c that is formed in a manner similar to that of the source/drain electrodes 130a and 130b is electrically connected to the gate electrode 110.

[0088] The transistor 162 includes a gate electrode 136d provided over the interlayer insulating layer 128, a gate insulating layer 138 provided over the gate electrode 136d, an oxide semiconductor layer 140 provided over the gate insulating layer 138, and a source/drain electrode 142a and a source/drain electrode 142b that are provided over the oxide semiconductor layer 140 and electrically connected to the oxide semiconductor layer 140.

[0089] Here, the gate electrode 136d is provided so as to be embedded in an insulating layer 132 formed over the interlayer insulating layer 128. Like the gate electrode 136d, an electrode 136a, an electrode 136b, and an electrode 136c are formed in contact with the source/drain electrode 130a, the source/drain electrode 130b, and the electrode 130c, respectively.

[0090] A protective insulating layer 144 is provided over the transistor 162 so as to be in contact with part of the oxide semiconductor layer 140. An interlayer insulating layer 146 is provided over the protective insulating layer 144. Openings that reach the source/drain electrode 142a and the source/drain electrode 142b are formed in the protective insulating layer 144 and the interlayer insulating layer 146. An electrode 150d and an electrode 150e are formed in contact with the source/drain electrode 142a and the source/drain electrode 142b, respectively, through the respective openings. Like the electrodes 150d and 150e, an electrode 150a, an electrode 150b, and an electrode 150c are formed in contact with the electrode 136a, the electrode 136b, and the electrode 136c, respectively, through openings provided in the gate insulating layer 138, the protective insulating layer 144, and the interlayer insulating layer 146.

[0091] Here, the oxide semiconductor layer 140 is preferably a highly purified oxide semiconductor layer from which impurities such as hydrogen are sufficiently removed. Specifically, the concentration of hydrogen in the oxide semiconductor layer 140 is 5.times.10.sup.19 atoms/cm.sup.3 or less, preferably 5.times.10.sup.18 atoms/cm.sup.3 or less, more preferably 5.times.10.sup.17 atoms/cm.sup.3 or less. Such an extremely low hydrogen concentration leads to a sufficiently low carrier concentration (e.g., less than 1.times.10.sup.12/cm.sup.3, or less than 1.45.times.10.sup.10/cm.sup.3) as compared to a general silicon wafer (a silicon wafer to which an impurity such as a slight amount of phosphorus or boron is added) having a carrier concentration of approximately 1.times.10.sup.14/cm.sup.3. The transistor 162 with significantly excellent off current characteristics can be obtained with the use of such an oxide semiconductor that is highly purified by a sufficient reduction in hydrogen concentration and becomes intrinsic (i-type) or substantially intrinsic (i-type). For example, the off current (per unit channel width (1 .mu.m), here) of the transistor 162 at room temperature (25.degree. C.) is 10 zA/.mu.m (1 zA (zeptoampere) is 1.times.10.sup.-21 A) or less, preferably 1 zA/.mu.m or less. The off current of the transistor 162 at 85.degree. C. is 100 zA/.mu.m (1.times.10.sup.-19 A/.mu.m) or less, preferably 10 zA/.mu.m (1.times.10.sup.-20 A/.mu.m) or less. The oxide semiconductor layer 140 which is made to be intrinsic or substantially intrinsic by a sufficient reduction in hydrogen concentration is used so that the off current of the transistor 162 is reduced, whereby a semiconductor device with a novel structure can be realized. Note that the concentration of hydrogen in the oxide semiconductor layer 140 is measured by secondary ion mass spectrometry (SIMS).

[0092] An insulating layer 152 is provided over the interlayer insulating layer 146. An electrode 154a, an electrode 154b, an electrode 154c, and an electrode 154d are provided so as to be embedded in the insulating layer 152. The electrode 154a is in contact with the electrode 150a. The electrode 154b is in contact with the electrode 150b. The electrode 154c is in contact with the electrode 150c and the electrode 150d. The electrode 154d is in contact with the electrode 150e.

[0093] That is, in the semiconductor device illustrated in FIGS. 2A and 2B, the gate electrode 110 of the transistor 160 and the source/drain electrode 142a of the transistor 162 are electrically connected through the electrodes 130c, 136c, 150c, 154c, and 150d.

<Method for Manufacturing Semiconductor Device>

[0094] Next, an example of a method for manufacturing the semiconductor device will be described. First, a method for manufacturing the transistor 160 in the lower portion will be described below with reference to FIGS. 3A to 3H, and then a method for manufacturing the transistor 162 in the upper portion will be described with reference to FIGS. 4A to 4G and FIGS. 5A to 5D.

<Method for Manufacturing Lower Transistor>

[0095] First, the substrate 100 including a semiconductor material is prepared (see FIG. 3A). As the substrate 100 including a semiconductor material, a single crystal semiconductor substrate or a polycrystalline semiconductor substrate made of silicon, silicon carbide, or the like; a compound semiconductor substrate made of silicon germanium or the like; an SOI substrate; or the like can be used. Here, an example of using a single crystal silicon substrate as the substrate 100 including a semiconductor material is described.

[0096] A protective layer 102 serving as a mask for forming an element isolation insulating layer is formed over the substrate 100 (see FIG. 3A). As the protective layer 102, an insulating layer formed using silicon oxide, silicon nitride, silicon nitride oxide, or the like can be used, for example. Note that before or after this step, an impurity element imparting n-type conductivity or an impurity element imparting p-type conductivity may be added to the substrate 100 in order to control the threshold voltage of the transistor. When the semiconductor material included in the substrate 100 is silicon, phosphorus, arsenic, or the like can be used as the impurity imparting n-type conductivity. Boron, aluminum, gallium, or the like can be used as the impurity imparting p-type conductivity.

[0097] Next, part of the substrate 100 in a region that is not covered with the protective layer 102 (i.e., in an exposed region) is removed by etching, using the protective layer 102 as a mask. Thus, an isolated semiconductor region 104 is formed (see FIG. 3B). As the etching, dry etching is preferably performed, but wet etching may be performed. An etching gas and an etchant can be selected as appropriate depending on a material of a layer to be etched.

[0098] Then, an insulating layer is formed so as to cover the semiconductor region 104, and the insulating layer in a region overlapping with the semiconductor region 104 is selectively removed, so that element isolation insulating layers 106 are formed (see FIG. 3B). The insulating layer is formed using silicon oxide, silicon nitride, silicon nitride oxide, or the like. As a method for removing the insulating layer, any of etching treatment and polishing treatment such as CMP can be employed. Note that the protective layer 102 is removed after the formation of the semiconductor region 104 or after the formation of the element isolation insulating layers 106.

[0099] Next, an insulating layer is formed over the semiconductor region 104, and a layer including a conductive material is formed over the insulating layer.

[0100] Because the insulating layer serves as a gate insulating layer later, the insulating layer preferably has a single-layer structure or a layered structure using a film containing silicon oxide, silicon nitride oxide, silicon nitride, hafnium oxide, aluminum oxide, tantalum oxide, or the like formed by a CVD method, a sputtering method, or the like. Alternatively, the insulating layer may be formed in such a manner that a surface of the semiconductor region 104 is oxidized or nitrided by high-density plasma treatment or thermal oxidation treatment. The high-density plasma treatment can be performed using, for example, a mixed gas of a rare gas such as He, Ar, Kr, or Xe and a gas such as oxygen, nitrogen oxide, ammonia, nitrogen, or hydrogen. There is no particular limitation on the thickness of the insulating layer; the insulating layer can have a thickness of 1 nm to 100 nm inclusive, for example.

[0101] The layer including a conductive material can be formed using a metal material such as aluminum, copper, titanium, tantalum, or tungsten. The layer including a conductive material may be formed using a semiconductor material such as polycrystalline silicon containing a conductive material. There is no particular limitation on the method for forming the layer containing a conductive material, and a variety of film formation methods such as an evaporation method, a CVD method, a sputtering method, or a spin coating method can be employed. Note that this embodiment shows an example of the case where the layer containing a conductive material is formed using a metal material.

[0102] After that, the insulating layer and the layer including a conductive material are selectively etched, so that the gate insulating layer 108 and the gate electrode 110 are formed (see FIG. 3C).

[0103] Next, an insulating layer 112 that covers the gate electrode 110 is formed (see FIG. 3C). Then, the impurity regions 114 with a shallow junction depth with the substrate 100 are formed by adding phosphorus (P), arsenic (As), or the like to the semiconductor region 104 (see FIG. 3C). Note that phosphorus or arsenic is added here in order to form an n-channel transistor; an impurity element such as boron (B) or aluminum (Al) may be added in the case of forming a p-channel transistor. With the formation of the impurity regions 114, the channel formation region 116 is formed in the semiconductor region 104 below the gate insulating layer 108 (see FIG. 3C). Here, the concentration of the impurity added can be set as appropriate; the concentration is preferably increased when the size of a semiconductor element is extremely decreased. The step in which the impurity regions 114 are formed after the formation of the insulating layer 112 is employed here; alternatively, the insulating layer 112 may be formed after the formation of the impurity regions 114.

[0104] Next, the sidewall insulating layers 118 are formed (see FIG. 3D). An insulating layer is formed so as to cover the insulating layer 112 and then subjected to highly anisotropic etching, whereby the sidewall insulating layers 118 can be formed in a self-aligned manner. At this time, it is preferable to partly etch the insulating layer 112 so that a top surface of the gate electrode 110 and top surfaces of the impurity regions 114 are exposed.

[0105] Then, an insulating layer is formed so as to cover the gate electrode 110, the impurity regions 114, the sidewall insulating layers 118, and the like. Next, phosphorus (P), arsenic (As), or the like is added to regions where the insulating layer is in contact with the impurity regions 114, so that the high-concentration impurity regions 120 are formed (see FIG. 3E). After that, the insulating layer is removed, and a metal layer 122 is formed so as to cover the gate electrode 110, the sidewall insulating layers 118, the high-concentration impurity regions 120, and the like (see FIG. 3E). A variety of film formation methods such as a vacuum evaporation method, a sputtering method, or a spin coating method can be employed for forming the metal layer 122. The metal layer 122 is preferably formed using a metal material that reacts with a semiconductor material included in the semiconductor region 104 to be a low-resistance metal compound. Examples of such a metal material are titanium, tantalum, tungsten, nickel, cobalt, and platinum.

[0106] Next, heat treatment is performed so that the metal layer 122 reacts with the semiconductor material. Thus, the metal compound regions 124 that are in contact with the high-concentration impurity regions 120 are formed (see FIG. 3F). Note that when the gate electrode 110 is formed using polycrystalline silicon or the like, a metal compound region is also formed in a region of the gate electrode 110 in contact with the metal layer 122.

[0107] As the heat treatment, irradiation with a flash lamp can be employed, for example. Although it is needless to say that another heat treatment method may be used, a method by which heat treatment for an extremely short time can be achieved is preferably used in order to improve the controllability of chemical reaction in formation of the metal compound. Note that the metal compound regions are formed by reaction of the metal material and the semiconductor material and have sufficiently high conductivity. The formation of the metal compound regions can properly reduce the electric resistance and improve element characteristics. Note that the metal layer 122 is removed after the metal compound regions 124 are formed.

[0108] Then, the interlayer insulating layer 126 and the interlayer insulating layer 128 are formed so as to cover the components formed in the above steps (see FIG. 3G). The interlayer insulating layers 126 and 128 can be formed using a material including an inorganic insulating material such as silicon oxide, silicon nitride oxide, silicon nitride, hafnium oxide, aluminum oxide, or tantalum oxide. Moreover, the interlayer insulating layers 126 and 128 can be formed using an organic insulating material such as a polyimide or an acrylic resin. Note that a two-layer structure of the interlayer insulating layer 126 and the interlayer insulating layer 128 is employed here; however, the structure of an interlayer insulating layer is not limited to this structure. After the formation of the interlayer insulating layer 128, a surface of the interlayer insulating layer 128 is preferably planarized with CMP, etching, or the like.

[0109] Then, openings that reach the metal compound regions 124 are formed in the interlayer insulating layers 126 and 128, and the source/drain electrode 130a and the source/drain electrode 130b are formed in the openings (see FIG. 3H). The source/drain electrodes 130a and 130b can be formed in such a manner, for example, that a conductive layer is formed in a region including the openings by a PVD method, a CVD method, or the like and then part of the conductive layer is removed by etching, CMP, or the like.

[0110] Note that in the case where the source/drain electrodes 130a and 130b are formed by removing part of the conductive layer, the process is preferably performed so that the surfaces are planarized. For example, when a thin titanium film or a thin titanium nitride film is formed in a region including the openings and then a tungsten film is formed so as to be embedded in the openings, excess tungsten, titanium, titanium nitride, or the like can be removed and the planarity of the surface can be improved by subsequent CMP. The surface including the source/drain electrodes 130a and 130b is planarized in such a manner, so that an electrode, a wiring, an insulating layer, a semiconductor layer, and the like can be favorably formed in later steps.

[0111] Note that only the source/drain electrodes 130a and 130b in contact with the metal compound regions 124 are shown here; however, an electrode that is in contact with the gate electrode 110 (e.g., the electrode 130c in FIG. 2A) and the like can also be formed in this step. There is no particular limitation on a material used for the source/drain electrodes 130a and 130b, and a variety of conductive materials can be used. For example, a conductive material such as molybdenum, titanium, chromium, tantalum, tungsten, aluminum, copper, neodymium, or scandium can be used.

[0112] Through the above steps, the transistor 160 using the substrate 100 including a semiconductor material is formed. Note that an electrode, a wiring, an insulating layer, or the like may be further formed after the above step. When the wirings have a multi-layer structure including a layered structure of an interlayer insulating layer and a conductive layer, a highly integrated semiconductor device can be provided.

<Method for Manufacturing Upper Transistor>

[0113] Next, steps for manufacturing the transistor 162 over the interlayer insulating layer 128 will be described with reference to FIGS. 4A to 4G and FIGS. 5A to 5D. Note that FIGS. 4A to 4G and FIGS. 5A to 5D illustrate steps for manufacturing electrodes, the transistor 162, and the like over the interlayer insulating layer 128; therefore, the transistor 160 and the like placed below the transistor 162 are omitted.

[0114] First, the insulating layer 132 is formed over the interlayer insulating layer 128, the source/drain electrodes 130a and 130b, and the electrode 130c (see FIG. 4A). The insulating layer 132 can be formed by a PVD method, a CVD method, or the like. The insulating layer 132 can be formed using a material including an inorganic insulating material such as silicon oxide, silicon nitride oxide, silicon nitride, hafnium oxide, aluminum oxide, or tantalum oxide.

[0115] Next, openings that reach the source/drain electrodes 130a and 130b and the electrode 130c are formed in the insulating layer 132. At this time, an opening is also formed in a region where the gate electrode 136d is to be formed later. Then, a conductive layer 134 is formed so as to be embedded in the openings (see FIG. 4B). The openings can be formed by a method such as etching using a mask. The mask can be formed by a method such as light exposure using a photomask. Either wet etching or dry etching may be used as the etching; dry etching is preferably used in terms of microfabrication. The conductive layer 134 can be formed by a film formation method such as a PVD method or a CVD method. The conductive layer 134 can be formed using a conductive material such as molybdenum, titanium, chromium, tantalum, tungsten, aluminum, copper, neodymium, or scandium or an alloy or a compound (e.g., a nitride) of any of these materials, for example.

[0116] Specifically, it is possible to employ a method, for example, in which a thin titanium film is formed in a region including the openings by a PVD method and a thin titanium nitride film is formed by a CVD method, and then, a tungsten film is formed so as to be embedded in the openings. Here, the titanium film formed by a PVD method has a function of reducing an oxide film formed on the surface of lower electrodes (here, the source/drain electrodes 130a and 130b, the electrode 130c, and the like) to decrease the contact resistance with the lower electrodes. The titanium nitride film formed after the formation of the titanium film has a barrier function of preventing diffusion of the conductive material. A copper film may be formed by a plating method after the formation of the barrier film of titanium, titanium nitride, or the like.

[0117] After the conductive layer 134 is formed, part of the conductive layer 134 is removed by etching, CMP, or the like, so that the insulating layer 132 is exposed and the electrodes 136a, 136b, and 136c and the gate electrode 136d are formed (see FIG. 4C). Note that when the electrodes 136a, 136b, and 136c and the gate electrode 136d are formed by removing part of the conductive layer 134, the process is preferably performed so that the surfaces are planarized. The surfaces of the insulating layer 132, the electrodes 136a, 136b, and 136c, and the gate electrode 136d are planarized in such a manner, whereby an electrode, a wiring, an insulating layer, a semiconductor layer, and the like can be favorably formed in later steps.

[0118] Next, the gate insulating layer 138 is formed so as to cover the insulating layer 132, the electrodes 136a, 136b, and 136c, and the gate electrode 136d (see FIG. 4D). The gate insulating layer 138 can be formed by a CVD method, a sputtering method, or the like. The gate insulating layer 138 is preferably formed using silicon oxide, silicon nitride, silicon oxynitride, silicon nitride oxide, aluminum oxide, hafnium oxide, tantalum oxide, or the like. Note that the gate insulating layer 138 may have a single-layer structure or a layered structure. For example, the gate insulating layer 138 made of silicon oxynitride can be formed by a plasma CVD method using silane (SiH.sub.4), oxygen, and nitrogen as a source gas. There is no particular limitation on the thickness of the gate insulating layer 138; the gate insulating layer 138 can have a thickness of 10 nm to 500 nm inclusive, for example. In the case of employing a layered structure, for example, the gate insulating layer 138 is preferably a stack of a first gate insulating layer having a thickness of 50 nm to 200 nm inclusive, and a second gate insulating layer with a thickness of 5 nm to 300 nm inclusive over the first gate insulating layer.

[0119] Note that an oxide semiconductor that becomes intrinsic or substantially intrinsic by removal of impurities (a highly purified oxide semiconductor) is quite susceptible to the interface level and the interface charge; therefore, when such an oxide semiconductor is used for an oxide semiconductor layer, the interface with the gate insulating layer is important. In other words, the gate insulating layer 138 that is to be in contact with a highly purified oxide semiconductor layer needs to have high quality.

[0120] For example, the gate insulating layer 138 is preferably formed by a high-density plasma CVD method using a microwave (2.45 GHz) because the gate insulating layer 138 can be dense and have high withstand voltage and high quality. When a highly purified oxide semiconductor layer and a high-quality gate insulating layer are in contact with each other, the interface level can be reduced and interface characteristics can be favorable.

[0121] It is needless to say that, even when a highly purified oxide semiconductor layer is used, another method such as a sputtering method or a plasma CVD method can be employed as long as a high-quality insulating layer can be formed as a gate insulating layer. Moreover, it is possible to use an insulating layer whose quality and characteristics of an interface with the oxide semiconductor layer are improved with heat treatment performed after the formation of the insulating layer. In any case, an insulating layer that has favorable film quality as the gate insulating layer 138 and can reduce interface level density with an oxide semiconductor layer to form a favorable interface is formed as the gate insulating layer 138.

[0122] If an impurity is included in an oxide semiconductor, a bond between the impurity and a main component of the oxide semiconductor is cleaved by a stress such as high electric field or high temperature to result in a dangling bond, which causes a shift of the threshold voltage (Vth).

[0123] Impurities included in the oxide semiconductor, particularly hydrogen and water, are reduced to a minimum and interface characteristics between the oxide semiconductor and the gate insulating layer are made favorable as described above, whereby a transistor that is stable against stresses such as high electric field and high temperature can be obtained.

[0124] Next, an oxide semiconductor layer is formed over the gate insulating layer 138 and processed by a method such as etching using a mask, so that the island-shaped oxide semiconductor layer 140 is formed (see FIG. 4E).

[0125] As the oxide semiconductor layer, it is preferable to use an In--Ga--Zn--O-based oxide semiconductor layer, an In--Sn--Zn--O-based oxide semiconductor layer, an In--Al--Zn--O-based oxide semiconductor layer, a Sn--Ga--Zn--O-based oxide semiconductor layer, an Al--Ga--Zn--O-based oxide semiconductor layer, a Sn--Al--Zn--O-based oxide semiconductor layer, an In--Zn--O-based oxide semiconductor layer, a Sn--Zn--O-based oxide semiconductor layer, an Al--Zn--O-based oxide semiconductor layer, an In--O-based oxide semiconductor layer, a Sn--O-based oxide semiconductor layer, or a Zn--O-based oxide semiconductor layer. It is particularly preferred that these oxide semiconductor layers exist in an amorphous state. In this embodiment, as the oxide semiconductor layer, an amorphous oxide semiconductor layer is formed by a sputtering method using a target for depositing an In--Ga--Zn--O-based oxide semiconductor. Note that since crystallization of an amorphous oxide semiconductor layer can be suppressed by adding silicon to the amorphous oxide semiconductor layer, an oxide semiconductor layer may be formed, for example, using a target containing SiO.sub.2 at 2 wt % to 10 wt % inclusive.

[0126] As a target used for forming an oxide semiconductor layer by a sputtering method, an oxide semiconductor deposition target containing zinc oxide as its main component can be used, for example. Moreover, a target for depositing an oxide semiconductor containing In, Ga, and Zn (a composition ratio of In.sub.2O.sub.3:Ga.sub.2O.sub.3:ZnO=1:1:1 [molar ratio]) can be used, for example. Furthermore, a target for depositing an oxide semiconductor containing In, Ga, and Zn (a composition ratio of In.sub.2O.sub.3:Ga.sub.2O.sub.3:ZnO=1:1:2 [molar ratio] or a composition ratio of In.sub.2O.sub.3:Ga.sub.2O.sub.3:ZnO=1:1:4 [molar ratio]) may be used. The filling rate of a target for depositing an oxide semiconductor is 90% to 100% .quadrature..quadrature..quadrature..quadrature..quadrature..quadrature..- quadrature..quadrature..quadrature..quadrature., preferably greater than or equal to 95% (e.g., 99.9%). A dense oxide semiconductor layer is formed using a target for depositing an oxide semiconductor with a high filling rate.

[0127] The atmosphere in which the oxide semiconductor layer is formed is preferably a rare gas (typically argon) atmosphere, an oxygen atmosphere, or a mixed atmosphere containing a rare gas (typically argon) and oxygen. Specifically, it is preferable to use a high-purity gas, for example, from which an impurity such as hydrogen, water, a compound having a hydroxyl group, or a hydride is removed so that the concentration is several ppm (preferably several ppb).

[0128] In forming the oxide semiconductor layer, the substrate is held in a treatment chamber that is maintained at reduced pressure and the substrate temperature is set to 100.degree. C. to 600.degree. C. inclusive, preferably 200.degree. C. to 400.degree. C. inclusive. The oxide semiconductor layer is formed while the substrate is heated, so that the impurity concentration of the oxide semiconductor layer can be reduced. Moreover, damage of the oxide semiconductor layer due to sputtering is reduced. Then, a sputtering gas from which hydrogen and water are removed is introduced into the treatment chamber from which remaining moisture is being removed, and the oxide semiconductor layer is formed using a metal oxide as a target. An entrapment vacuum pump is preferably used in order to remove moisture remaining in the treatment chamber. For example, a cryopump, an ion pump, or a titanium sublimation pump can be used. An evacuation unit may be a turbo pump provided with a cold trap. In the deposition chamber that is evacuated with the cryopump, in addition to a compound containing a carbon atom, a hydrogen atom, a compound containing a hydrogen atom such as water (H.sub.2O), and the like are removed, whereby the impurity concentration of the oxide semiconductor layer formed in the deposition chamber can be reduced.

[0129] The oxide semiconductor layer can be formed under the following conditions, for example: the distance between the substrate and the target is 100 mm; the pressure is 0.6 Pa; the direct-current (DC) power supply is 0.5 kW; and the atmosphere is oxygen (the flow rate of oxygen is 100%). Note that it is preferable to use a pulse direct current (DC) power supply because powder substances (also referred to as particles or dust) generated in film deposition can be reduced and the thickness distribution can be small. The thickness of the oxide semiconductor layer is 2 nm to 200 nm inclusive, preferably 5 nm to 30 nm inclusive. Note that an appropriate thickness differs depending on an oxide semiconductor material, and the thickness is set as appropriate depending on the material to be used.

[0130] Note that before the oxide semiconductor layer is formed by a sputtering method, dust on a surface of the gate insulating layer 138 is preferably removed by reverse sputtering in which an argon gas is introduced and plasma is generated. Here, the reverse sputtering is a method by which ions collide with a surface to be processed so that the surface is modified, in contrast to normal sputtering by which ions collide with a sputtering target. An example of a method for making ions collide with a surface to be processed is a method in which high-frequency voltage is applied to the surface in an argon atmosphere so that plasma is generated near a substrate. Note that a nitrogen atmosphere, a helium atmosphere, an oxygen atmosphere, or the like may be used instead of an argon atmosphere.

[0131] As an etching method for the oxide semiconductor layer, either dry etching or wet etching may be employed. It is needless to say that dry etching and wet etching can be used in combination. The etching conditions (e.g., an etching gas or an etching solution, etching time, and temperature) are set as appropriate depending on the material so that the oxide semiconductor layer can be etched into a desired shape.

[0132] An example of an etching gas used for dry etching is a gas containing chlorine (a chlorine-based gas such as chlorine (Cl.sub.2), boron chloride (BCl.sub.3), silicon chloride (SiCl.sub.4), or carbon tetrachloride (CCl.sub.4)). Moreover, a gas containing fluorine (a fluorine-based gas such as carbon tetrafluoride (CF.sub.4), sulfur fluoride (SF.sub.6), nitrogen fluoride (NF.sub.3), or trifluoromethane (CHF.sub.3)), hydrogen bromide (HBr), oxygen (O.sub.2), any of these gases to which a rare gas such as helium (He) or argon (Ar) is added, or the like may be used.

[0133] As the dry etching method, a parallel plate RIE (reactive ion etching) method or an ICP (inductively coupled plasma) etching method can be used. In order to etch the oxide semiconductor layer into a desired shape, etching conditions (e.g., the amount of electric power applied to a coiled electrode, the amount of electric power applied to an electrode on the substrate side, and the electrode temperature on the substrate side) are set as appropriate.

[0134] As an etchant used for wet etching, a mixed solution of phosphoric acid, acetic acid, and nitric acid or the like can be used. An etchant such as ITO07N (produced by KANTO CHEMICAL CO., INC.) may also be used.

[0135] Then, first heat treatment is preferably performed on the oxide semiconductor layer. The oxide semiconductor layer can be dehydrated or dehydrogenated with the first heat treatment. The temperature of the first heat treatment is greater than or equal to 300.degree. C. and less than or equal to 750.degree. C., preferably greater than or equal to 400.degree. C. and less than the strain point of the substrate. For example, the substrate is introduced into an electric furnace in which a resistance heating element or the like is used and the oxide semiconductor layer 140 is subjected to heat treatment at 450.degree. C. for one hour in a nitrogen atmosphere. The oxide semiconductor layer 140 is not exposed to the air during the heat treatment so that entry of water and hydrogen can be prevented.

[0136] The heat treatment apparatus is not limited to the electric furnace and can be an apparatus for heating an object by thermal radiation or thermal conduction from a medium such as a heated gas. For example, a rapid thermal annealing (RTA) apparatus such as a gas rapid thermal annealing (GRTA) apparatus or a lamp rapid thermal annealing (LRTA) apparatus can be used. An LRTA apparatus is an apparatus for heating an object to be processed by radiation of light (an electromagnetic wave) emitted from a lamp such as a halogen lamp, a metal halide lamp, a xenon arc lamp, a carbon arc lamp, a high pressure sodium lamp, or a high pressure mercury lamp. A GRTA apparatus is an apparatus for performing heat treatment using a high-temperature gas. As the gas, an inert gas that does not react with an object by heat treatment, for example, nitrogen or a rare gas such as argon is used.

[0137] For example, as the first heat treatment, a GRTA process may be performed as follows. The substrate is put in an inert gas that has been heated to a high temperature of 650.degree. C. to 700.degree. C., heated for several minutes, and taken out from the inert gas. The GRTA process enables high-temperature heat treatment for a short time. Moreover, the GRTA process can be employed even when the temperature exceeds the strain point of the substrate because it is heat treatment for a short time.

[0138] Note that the first heat treatment is preferably performed in an atmosphere that contains nitrogen or a rare gas (e.g., helium, neon, or argon) as its main component and does not contain water, hydrogen, or the like. For example, the purity of nitrogen or a rare gas such as helium, neon, or argon introduced into a heat treatment apparatus is greater than or equal to 6 N (99.9999%), preferably greater than or equal to 7 N (99.99999%) (i.e., the impurity concentration is less than or equal to 1 ppm, preferably less than or equal to 0.1 ppm).

[0139] Depending on the conditions of the first heat treatment or the material of the oxide semiconductor layer, the oxide semiconductor layer is sometimes crystallized to be microcrystalline or polycrystalline. For example, the oxide semiconductor layer sometimes becomes a microcrystalline oxide semiconductor layer having a degree of crystallization of 90% or more, or 80% or more. Further, depending on the conditions of the first heat treatment or the material of the oxide semiconductor layer, the oxide semiconductor layer may be an amorphous oxide semiconductor layer containing no crystalline component.

[0140] Furthermore, the oxide semiconductor layer sometimes becomes a layer in which a microcrystal (the grain size is 1 nm to 20 nm inclusive, typically 2 nm to 4 nm inclusive) is mixed in an amorphous oxide semiconductor (e.g., a surface of the oxide semiconductor layer).

[0141] The electrical characteristics of the oxide semiconductor layer can be changed by aligning microcrystals in an amorphous region of the oxide semiconductor layer. For example, when the oxide semiconductor layer is formed using a target for depositing In--Ga--Zn--O-based oxide semiconductor, the electrical characteristics of the oxide semiconductor layer can be changed by formation of a microcrystalline portion in which crystal grains of In.sub.2Ga.sub.2ZnO.sub.7 with electrical anisotropy are aligned.

[0142] Specifically, for example, when the crystal grains are arranged so that the c-axis of In.sub.2Ga.sub.2ZnO.sub.7 is perpendicular to a surface of the oxide semiconductor layer, the conductivity in the direction parallel to the surface of the oxide semiconductor layer can be improved and insulating properties in the direction perpendicular to the surface of the oxide semiconductor layer can be improved. Furthermore, such a microcrystalline portion has a function of suppressing entry of an impurity such as water or hydrogen into the oxide semiconductor layer.

[0143] Note that the oxide semiconductor layer including the microcrystalline portion can be formed by heating the oxide semiconductor layer by a GRTA process. Further, the oxide semiconductor layer can be formed in a more preferred manner by using a sputtering target in which the amount of Zn is smaller than that of In or Ga.

[0144] The first heat treatment for the oxide semiconductor layer 140 can be performed on the oxide semiconductor layer that has not yet been processed into the island-shaped oxide semiconductor layer 140. In that case, after the first heat treatment, the substrate is taken out of the heating apparatus and a photolithography step is performed.

[0145] Note that the first heat treatment can be referred to as dehydration treatment, dehydrogenation treatment, or the like because of its effect of dehydration or dehydrogenation on the oxide semiconductor layer 140. Such dehydration treatment or dehydrogenation treatment can be performed, for example, after the oxide semiconductor layer is formed, after a source electrode and a drain electrode are stacked over the oxide semiconductor layer 140, or after a protective insulating layer is formed over the source and drain electrodes. Such dehydration treatment or dehydrogenation treatment may be performed once or plural times.

[0146] Next, the source/drain electrode 142a and the source/drain electrode 142b are formed in contact with the oxide semiconductor layer 140 (see FIG. 4F). The source/drain electrodes 142a and 142b can be formed in such a manner that a conductive layer is formed so as to cover the oxide semiconductor layer 140 and then is selectively etched.

[0147] The conductive layer can be formed by a PVD method such as a sputtering method, or a CVD method such as a plasma CVD method. As a material for the conductive layer, an element selected from aluminum, chromium, copper, tantalum, titanium, molybdenum, or tungsten; an alloy containing any of these elements as a component; or the like can be used. Moreover, one or more materials selected from manganese, magnesium, zirconium, beryllium, or thorium may be used. Aluminum combined with one or more of elements selected from titanium, tantalum, tungsten, molybdenum, chromium, neodymium, or scandium may be used. The conductive layer can have a single-layer structure or a layered structure including two or more layers. For example, the conductive layer can have a single-layer structure of an aluminum film containing silicon, a two-layer structure in which a titanium film is stacked over an aluminum film, or a three-layer structure in which a titanium film, an aluminum film, and a titanium film are stacked in this order.

[0148] Here, ultraviolet light, KrF laser light, or ArF laser light is preferably used for light exposure in forming a mask used for etching.

[0149] The channel length (L) of the transistor is determined by a distance between a lower edge portion of the source/drain electrode 142a and a lower edge portion of the source/drain electrode 142b. Note that for light exposure in the case where the channel length (L) is less than 25 nm, light exposure for forming a mask is performed with extreme ultraviolet rays whose wavelength is several nanometers to several hundreds of nanometers, which is extremely short. The resolution of light exposure with extreme ultraviolet rays is high and the depth of focus is large. For these reasons, the channel length (L) of the transistor to be formed later can be in the range of 10 nm to 1000 nm, and the circuit can operate at higher speed. Moreover, the off current is extremely low, which prevents power consumption from increasing.

[0150] The materials and etching conditions of the conductive layer and the oxide semiconductor layer 140 are adjusted as appropriate so that the oxide semiconductor layer 140 is not removed in etching of the conductive layer. Note that in some cases, the oxide semiconductor layer 140 is partly etched in the etching step and thus has a groove portion (a recessed portion) depending on the materials and the etching conditions.

[0151] An oxide conductive layer may be formed between the oxide semiconductor layer 140 and the source/drain electrode 142a and between the oxide semiconductor layer 140 and the source/drain electrode 142b. The oxide conductive layer and a metal layer for forming the source/drain electrodes 142a and 142b can be successively formed. The oxide conductive layer can function as a source region and a drain region. The placement of such an oxide conductive layer can reduce the resistance of the source region and the drain region, so that the transistor can operate at high speed.

[0152] In order to reduce the number of masks to be used and reduce the number of steps, an etching step may be performed with the use of a resist mask formed using a multi-tone mask which is a light-exposure mask through which light is transmitted to have a plurality of intensities. A resist mask formed with the use of a multi-tone mask has a plurality of thicknesses (has a stair-like shape) and further can be changed in shape by ashing; therefore, the resist mask can be used in a plurality of etching steps for processing into different patterns. That is, a resist mask corresponding to at least two kinds of different patterns can be formed by using a multi-tone mask. Thus, the number of light-exposure masks can be reduced and the number of corresponding photolithography steps can also be reduced, whereby a process can be simplified.

[0153] Note that plasma treatment is preferably performed with the use of a gas such as N.sub.2O, N.sub.2, or Ar after the above step. This plasma treatment removes water or the like attached to an exposed surface of the oxide semiconductor layer. Plasma treatment may be performed using a mixed gas of oxygen and argon.

[0154] Next, the protective insulating layer 144 is formed in contact with part of the oxide semiconductor layer 140 without exposure to the air (see FIG. 4G).

[0155] The protective insulating layer 144 can be formed by a method by which impurities such as water and hydrogen are prevented from being mixed to the protective insulating layer 144, such as a sputtering method, as appropriate. The protective insulating layer 144 has a thickness of at least 1 nm. The protective insulating layer 144 can be formed using silicon oxide, silicon nitride, silicon oxynitride, silicon nitride oxide, or the like. The protective insulating layer 144 can have a single-layer structure or a layered structure. The substrate temperature in forming the protective insulating layer 144 is preferably higher than or equal to room temperature and lower than or equal to 300.degree. C. The atmosphere for forming the protective insulating layer 144 is preferably a rare gas (typically argon) atmosphere, an oxygen atmosphere, or a mixed atmosphere containing a rare gas (typically argon) and oxygen.