Fuse Latch Of Semiconductor Device

CHUN; Duk Su

U.S. patent application number 16/215205 was filed with the patent office on 2020-03-19 for fuse latch of semiconductor device. This patent application is currently assigned to SK hynix Inc.. The applicant listed for this patent is SK hynix Inc.. Invention is credited to Duk Su CHUN.

| Application Number | 20200090774 16/215205 |

| Document ID | / |

| Family ID | 69590949 |

| Filed Date | 2020-03-19 |

| United States Patent Application | 20200090774 |

| Kind Code | A1 |

| CHUN; Duk Su | March 19, 2020 |

FUSE LATCH OF SEMICONDUCTOR DEVICE

Abstract

A fuse latch of a semiconductor device is disclosed. The fuse latch includes a plurality of PMOS transistors and a plurality of NMOS transistors to latch fuse cell data. In the fuse latch, the PMOS transistors are formed in a single P-type active region, and the NMOS transistors are arranged in a two-stage structure at one side of the P-type active region.

| Inventors: | CHUN; Duk Su; (Icheon-si Gyeonggi-do, KR) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Assignee: | SK hynix Inc. Icheon-si Gyeonggi-do KR |

||||||||||

| Family ID: | 69590949 | ||||||||||

| Appl. No.: | 16/215205 | ||||||||||

| Filed: | December 10, 2018 |

| Current U.S. Class: | 1/1 |

| Current CPC Class: | G11C 29/789 20130101; G11C 29/787 20130101; G11C 17/16 20130101; G11C 2029/4402 20130101; G11C 17/18 20130101; H01L 23/5256 20130101 |

| International Class: | G11C 17/16 20060101 G11C017/16; G11C 17/18 20060101 G11C017/18; G11C 29/00 20060101 G11C029/00; H01L 23/525 20060101 H01L023/525 |

Foreign Application Data

| Date | Code | Application Number |

|---|---|---|

| Sep 14, 2018 | KR | 10-2018-0110489 |

Claims

1. A fuse latch of a semiconductor device comprising: first and second NMOS transistors, each of which is configured to receive a first control signal through its gate terminal and to transmit fuse cell data in response to the first control signal; a first inverter comprising a first PMOS transistor and a third NMOS transistor that are coupled in series between a power-supply voltage and a ground voltage, the first inverter configured to include an output node coupled to the first NMOS transistor and to include an input node coupled to the second NMOS transistor; a second inverter comprising a second PMOS transistor and a fourth NMOS transistor that are coupled in series between the power-supply voltage and the ground voltage, the second inverter configured to include an input node coupled to the output node of the first inverter and to include an output node coupled to the input node of the first inverter; a fifth NMOS transistor comprising a gate terminal coupled to the input node of the first inverter and coupled to the output node of the second inverter and comprising a first terminal coupled to a data output terminal; and a sixth NMOS transistor configured to receive a second control signal through its gate terminal and configured to selectively couple the ground voltage to a second terminal of the fifth NMOS transistor in response to the second control signal, wherein the first and second PMOS transistors are formed in a first active region, the first to fourth NMOS transistors are formed in a second active region located at one side of the first active region in a first direction, and the fifth and sixth transistors are formed in a third active region located at one side of the second active region in the first direction.

2. The fuse latch of the semiconductor device according to claim 1, wherein: the first NMOS transistor and the second NMOS transistor are respectively arranged at both ends of the second active region; and the third and fourth NMOS transistors are arranged between the first NMOS transistor and the second NMOS transistor within the second active region.

3. The fuse latch of the semiconductor device according to claim 1, further comprising: a first power-supply line located at both sides of the first active region, the first power-supply line configured to supply the power-supply voltage; and a second power-supply line coupled to one end of the third active region through a contact, the second power-supply line configured to supply the ground voltage.

4. The fuse latch of the semiconductor device according to claim 3, further comprising: a dummy active region located at one side of the third active region in a second direction substantially perpendicular to the first direction, the dummy active region comprising a dummy NMOS transistor.

5. The fuse latch of the semiconductor device according to claim 4, wherein both ends of the dummy active region are coupled to the second power-supply line.

6. The fuse latch of the semiconductor device according to claim 1, wherein both ends of the second active region are coupled to the first NMOS transistor and the second NMOS transistor, respectively, through a contact.

7. The fuse latch of the semiconductor device according to claim 3, further comprising: a seventh NMOS transistor configured to receive a reset signal through its gate terminal, the seventh NMOS transistor coupled between the input node of the first inverter and the ground voltage.

8. The fuse latch of the semiconductor device according to claim 7, wherein the seventh NMOS transistor is formed in a fourth active region located at one side of the third active region in a second direction substantially perpendicular to the first direction.

9. The fuse latch of the semiconductor device according to claim 8, wherein one end of the fourth active region is coupled to the second power-supply line.

10. A fuse latch of a semiconductor device comprising a plurality of PMOS transistors and a plurality of NMOS transistors to latch fuse cell data, wherein the plurality of PMOS transistors are formed in a single P-type active region, and the plurality of NMOS transistors are formed in a plurality of N-type active regions, wherein the plurality of N-type active regions are arranged in a two-stage structure at one side of the P-type active region.

11. The fuse latch according to claim 10, wherein the plurality of N-type active regions comprises: a first N-type active region arranged at one side of the P-type active region in a first direction; and a second N-type active region arranged at one side of the first N-type active region in the first direction.

12. The fuse latch according to claim 11, wherein the plurality of N-type active regions further comprises: a third N-type active region located at one side of the second N-type active region in a second direction substantially perpendicular to the first direction.

Description

CROSS-REFERENCE TO RELATED APPLICATION

[0001] The present application claims priority under 35 U.S.C. .sctn. 119(a) to Korean patent application No. 10-2018-0110489, filed on Sep. 14, 2018, the disclosure of which is incorporated herein in its entirety.

BACKGROUND OF THE INVENTION

[0002] Embodiments of the present disclosure relate to a semiconductor device, and more particularly to a fuse latch for latching information of a repair fuse cell.

[0003] With rapid development of higher-performance electronic systems (e.g., personal computers (PCs) and electronic communication systems), semiconductor devices acting as memory mounted to the electronic systems have been developed to implement products having higher speeds and higher degrees of integration.

[0004] In order to implement semiconductor devices having higher degrees of integration, a function for efficiently arranging memory cells of a memory cell region within a limited region is of importance. However, another function related to efficiently arranging a peripheral circuit region (hereinafter referred to as a peripheral region) that is needed to operate memory cells is more important than the function related to efficiently arranging memory cells of a memory cell region.

[0005] Many fuse-related circuits for repairing memory cells have been widely used in semiconductor devices. Therefore, the technology of efficiently arranging such fuse-related circuits to attain a regional gain of semiconductor devices is also of importance.

BRIEF SUMMARY OF THE INVENTION

[0006] Various embodiments of the present disclosure are directed to providing a fuse latch of a semiconductor device that substantially mitigates or obviates one or more problems due to limitations and disadvantages of the related art.

[0007] An embodiment of the present disclosure relates to a fuse latch capable of improving a regional gain of a semiconductor device.

[0008] In accordance with an aspect of the present disclosure, a fuse latch of a semiconductor device includes first and second NMOS transistors, each of which is configured to receive a first control signal through its gate terminal and to transmit fuse cell data in response to the first control signal. The fuse latch also includes a first inverter including a first PMOS transistor and a third NMOS transistor that are coupled in series between a power-supply voltage and a ground voltage, the first inverter configured to include an input node and an output node such that the input node is coupled to the first NMOS transistor and the output node is coupled to the second NMOS transistor. The fuse latch further includes a second inverter including a second PMOS transistor and a fourth NMOS transistor that are coupled in series between the power-supply voltage and the ground voltage, the second inverter configured to include an input node and an output node such that the input node is coupled to the output node of the first inverter and the output node is coupled to the input node of the first inverter. The fuse latch additionally includes a fifth NMOS transistor including a gate terminal and a first terminal such that the gate terminal is coupled to the output node of the first inverter and coupled to the input node of the second inverter and the first terminal is coupled to a data output terminal. The fuse latch also includes and a sixth NMOS transistor configured to receive a second control signal through its gate terminal and configured to selectively couple the ground voltage to a second terminal of the fifth NMOS transistor in response to the second control signal. The first and second PMOS transistors are formed in a first active region, the first to fourth NMOS transistors are formed in a second active region located at one side of the first active region in a first direction, and the fifth and sixth transistors are formed in a third active region located at one side of the second active region in the first direction.

[0009] In accordance with another aspect of the present disclosure, a fuse latch of a semiconductor device is disclosed. The fuse latch includes a plurality of PMOS transistors and a plurality of NMOS transistors to latch fuse cell data. The PMOS transistors are formed in a single P-type active region, and the NMOS transistors are formed in a plurality of N-type active regions. The plurality of N-type active regions may be arranged in a two-stage structure at one side of the P-type active region.

[0010] It is to be understood that both the foregoing general description and the following detailed description of embodiments are for purposes of explanation and not intended to be exhaustive.

BRIEF DESCRIPTION OF THE DRAWINGS

[0011] The above and other features and advantages of the present disclosure will become readily apparent by reference to the following detailed description when considered in conjunction with the accompanying drawings wherein:

[0012] FIG. 1 shows a schematic diagram of a circuit structure of a fuse latch, according to an embodiment of the present disclosure.

[0013] FIG. 2 shows a conceptual diagram illustrating an actual layout structure of constituent elements contained in the fuse latch shown in FIG. 1, according to an embodiment of the present disclosure.

[0014] FIG. 3 shows a conceptual diagram illustrating a layout structure of active regions of unit fuse latches (shown in FIG. 2) arranged in an array shape, according to an embodiment of the present disclosure.

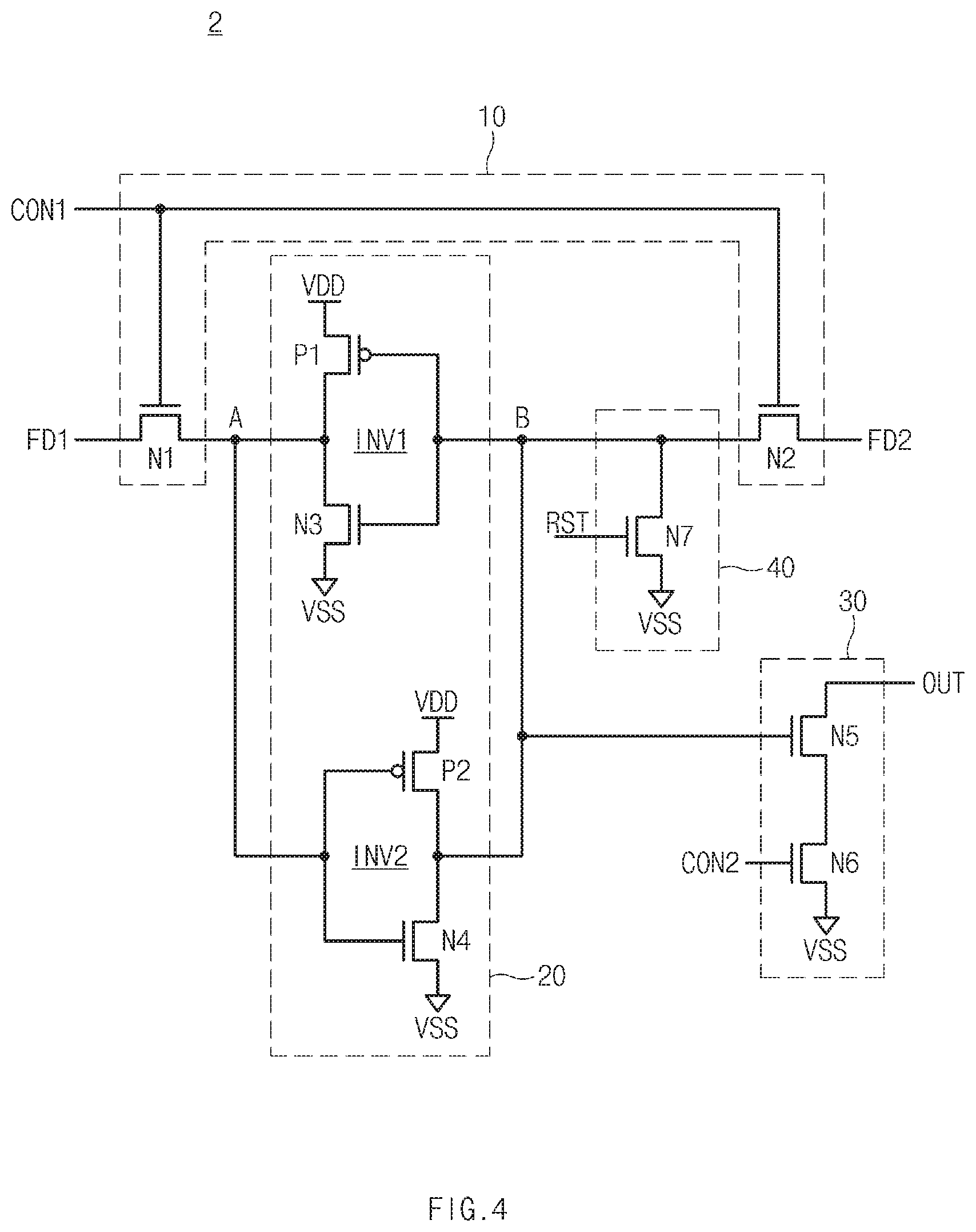

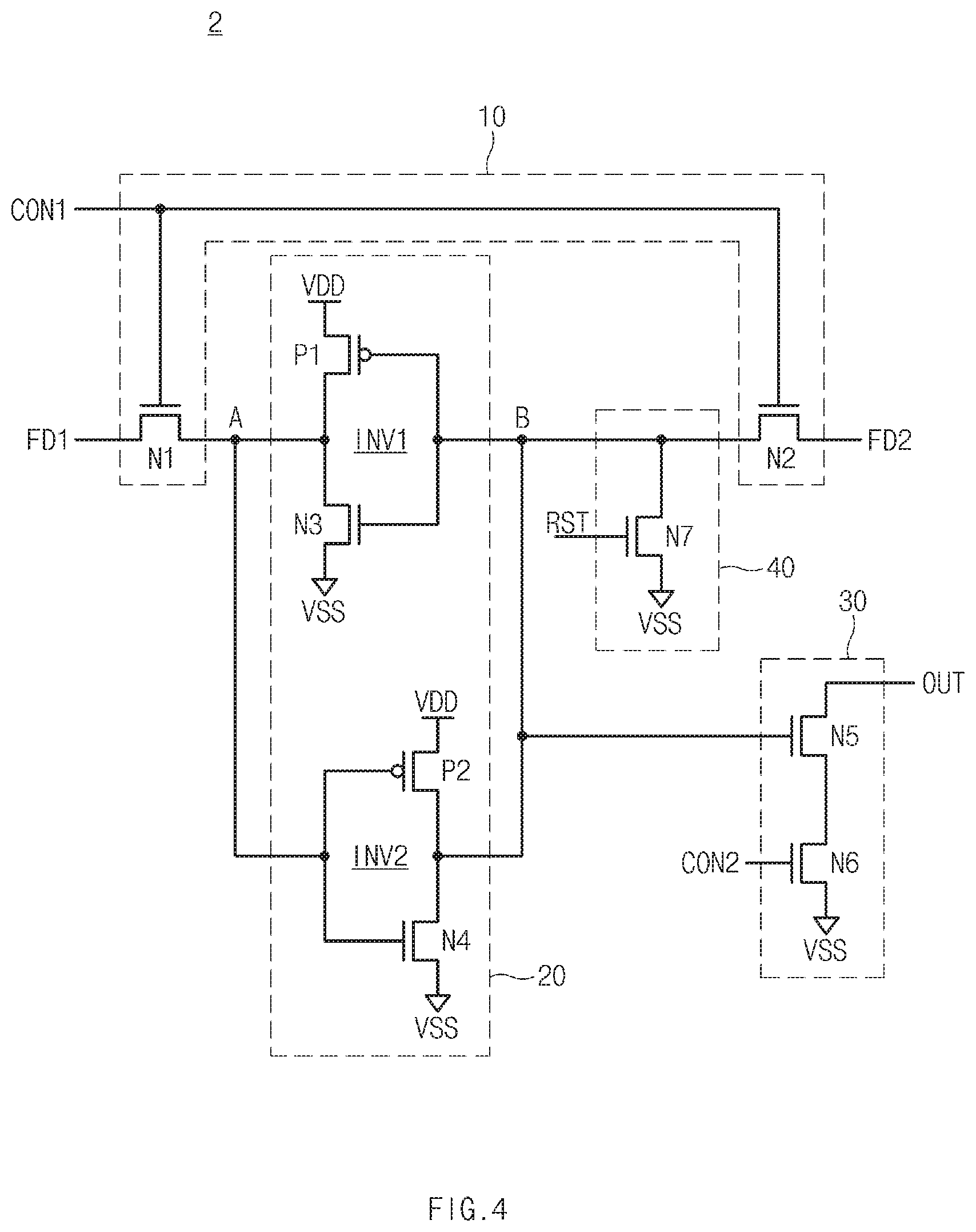

[0015] FIG. 4 shows a schematic diagram illustrating a circuit structure of a fuse latch, according to an embodiment of the present disclosure.

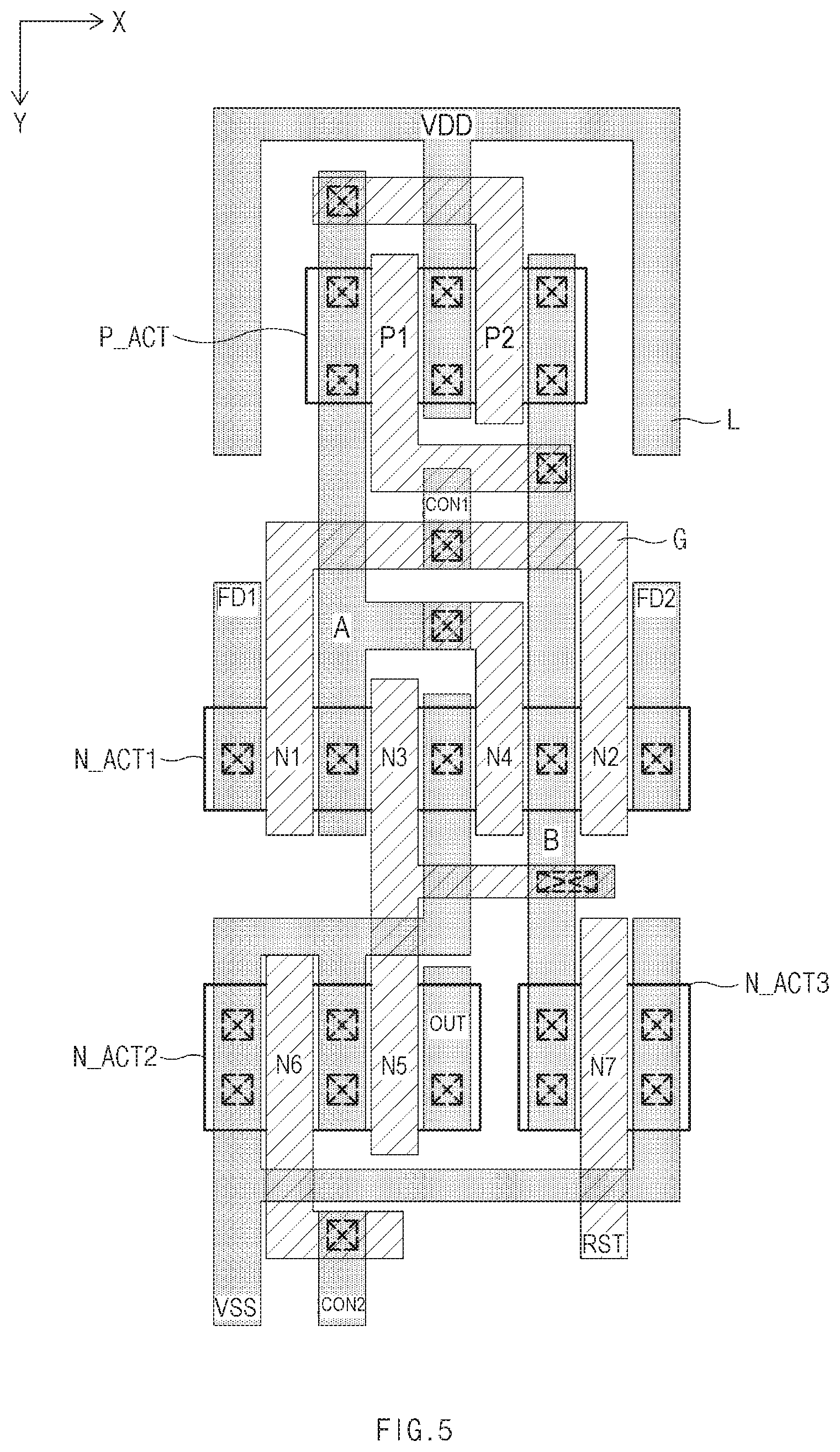

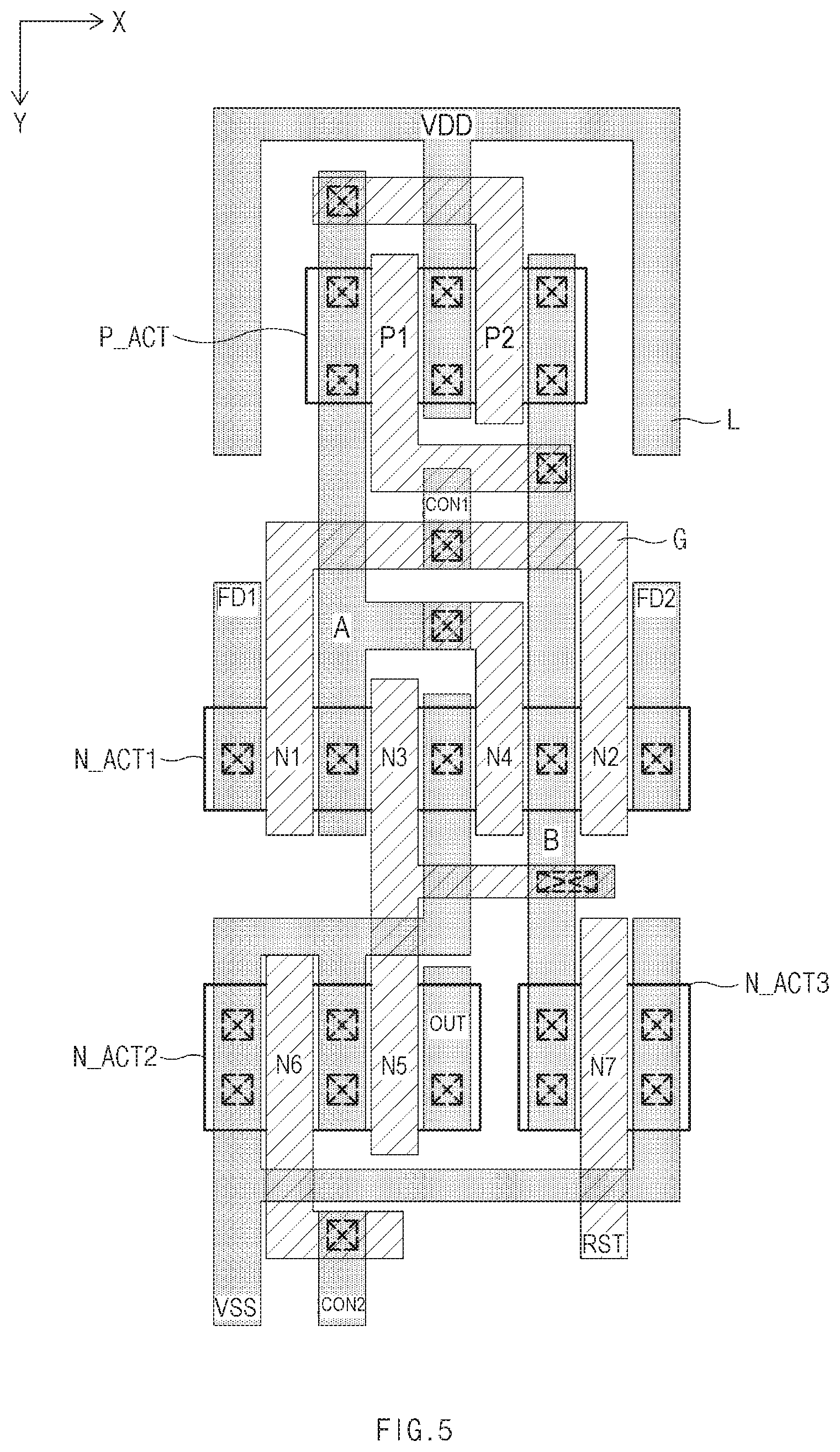

[0016] FIG. 5 shows a schematic diagram illustrating an actual layout structure of constituent elements contained in the fuse latch shown in FIG. 4, according to an embodiment of the present disclosure.

[0017] FIG. 6 shows a schematic diagram illustrating an actual layout structure of constituent elements contained in the fuse latch shown in FIG. 4, according to an embodiment of the present disclosure.

DESCRIPTION OF EMBODIMENTS

[0018] Reference is now made to presented embodiments of the present disclosure, examples of which are illustrated in the accompanying drawings. Wherever possible, the same reference numbers are used throughout the drawings to refer to the same or like parts.

[0019] In association with the presented embodiments of the present disclosure, specific structural and functional descriptions are disclosed only for illustrative purposes. The presented embodiments represent a limited number of possible embodiments. Embodiments of the present disclosure can be implemented in various ways without departing from the scope or spirit of the present disclosure.

[0020] In describing the present disclosure, the terms "first" and "second" may be used to distinguish multiple components from one another, but the components are not limited by the terms in number or order. For example, a first component may be called a second component and a second component may be called a first component without departing from the scope of the present disclosure.

[0021] The terms used in the present application are merely used to describe specific embodiments and are not intended to limit the present disclosure. A singular expression may include a plural expression unless explicitly stated otherwise.

[0022] Unless otherwise defined, all terms used herein, including technical or scientific terms, have the same meanings as understood by those skilled in the art. Terms defined in a generally used dictionary may be analyzed to have the same meaning as the context of the relevant art and should not be analyzed to have an ideal meaning or an excessively formal meaning unless clearly defined in the present application. The terminology used in the present disclosure is for the purpose of describing particular embodiments only and is not intended to limit the disclosure.

[0023] FIG. 1 shows a schematic diagram illustrating a circuit structure of a fuse latch 1, according to an embodiment of the present disclosure.

[0024] Referring to FIG. 1, the fuse latch 1 may include a fuse information transmission circuit 10, a latch circuit 20, and a data output circuit 30.

[0025] The fuse information transmission circuit 10 may transmit fuse cell data FD1 and FD2 to the latch circuit 20 in response to a control signal CON1. In this case, a value of first fuse cell data FD1 is opposite to a value of second fuse cell data FD2. For example, if a phase of the first fuse cell data FD1 is at a high level (H), a phase of the second fuse cell data FD2 is at a low level (L). The fuse information transmission circuit 10 may include pass NMOS transistors N1 and N2.

[0026] The NMOS transistor N1 may include a gate terminal configured to receive the control signal CON1 as an input signal, a first terminal coupled to a first output terminal so as to receive first fuse cell data FD1 as an input signal, and a second terminal coupled to the latch circuit 20 through a node A. The NMOS transistor N2 may include a gate terminal configured to receive the control signal CON1 as an input signal, a first terminal coupled to a second output terminal of a fuse cell (not shown) so as to receive second fuse cell data FD2 as an input signal, and a second terminal coupled to the latch circuit 20 through a node B.

[0027] The latch circuit 20 may latch fuse cell data FD1 and FD2 received through the fuse information transmission circuit 10. The latch circuit 20 may include first and second inverters INV1 and INV2. Input and output (I/O) terminals of the first inverter INV1 may be coupled to input and output (I/O) terminals of the second inverter INV2 such that I/O signals of the first inverter INV1 and I/O signals of the second inverter INV2 may be fed back to each other.

[0028] The first inverter INV1 may include a PMOS transistor P1 and an NMOS transistor N3 that are coupled in series between a power-supply voltage (VDD) terminal and a ground voltage (VSS) terminal. A gate terminal of the PMOS transistor P1 and a gate terminal of the NMOS transistor N3 may be commonly coupled to a second terminal of the NMOS transistor N2 through a node B. A first terminal of the PMOS transistor P1 may be coupled to the power-supply voltage (VDD) terminal, and a second terminal of the PMOS transistor P1 may be coupled to a second terminal of the NMOS transistor N3. A first terminal of the NMOS transistor N3 may be coupled to the ground voltage (VSS) terminal, and a second terminal of the NMOS transistor N3 may be coupled to the second terminal of the PMOS transistor P1. That is, a specific node to which the second terminal of the PMOS transistor P1 and the second terminal of the NMOS transistor N3 are commonly coupled may be an output node (i.e., Node A) of the first inverter INV1, such that this output node (Node A) may be coupled to the second terminal of the NMOS transistor N1. A specific node to which the PMOS transistor P1 and the NMOS transistor N3 are commonly coupled may be an input node (i.e., Node B), such that this input node (Node B) may be coupled to the second terminal of the NMOS transistor N2.

[0029] The second inverter INV2 may include a PMOS transistor P2 and an NMOS transistor N4 that are coupled in series between the power-supply voltage (VDD) terminal and the ground voltage (VSS) terminal. A gate terminal of the PMOS transistor P2 and a gate terminal of the NMOS transistor N4 may be commonly coupled to a second terminal of the NMOS transistor N1 through the node A. A first terminal of the PMOS transistor P2 may be coupled to the power-supply voltage (VDD) terminal, and a second terminal of the PMOS transistor P2 may be coupled to a second terminal of the NMOS transistor N4. A first terminal of the NMOS transistor N4 may be coupled to the ground voltage (VSS) terminal, and a second terminal of the NMOS transistor N4 may be coupled to the second terminal of the PMOS transistor P2. That is, a specific node to which the second terminal of the PMOS transistor P2 and the second terminal of the NMOS transistor N4 are commonly coupled may be an output node (i.e., Node B) of the second inverter INV2, such that this output node (Node B) may be coupled to the second terminal of the NMOS transistor N2. A specific node to which the PMOS transistor P2 and the NMOS transistor N4 are commonly coupled may be an input node (i.e., Node A), such that this input node (Node A) may be coupled to the second terminal of the NMOS transistor N1.

[0030] The data output circuit 30 may output data latched by the latch circuit 20 in response to a control signal CON2. The data output circuit 30 may include NMOS transistors N5 and N6 coupled in series between a data output terminal OUT and a ground voltage (VSS) terminal.

[0031] The NMOS transistor N5 may include a gate terminal coupled to the node B, a first terminal coupled to the data output terminal OUT, and a second terminal coupled to the NMOS transistor N6. The NMOS transistor N6 may include a gate terminal configured to receive the control signal CON2 as an input signal, a first terminal coupled to the ground voltage (VSS) terminal, and a second terminal coupled to the second terminal of the NMOS transistor N5.

[0032] FIG. 2 shows a conceptual diagram illustrating an actual layout structure of constituent elements contained in the fuse latch 1 shown in FIG. 1, according to an embodiment of the present disclosure.

[0033] For convenience of description and better understanding of the present disclosure, reference numerals indicating the PMOS transistors P1 and P2 and the NMOS transistors N1 to N6 of FIG. 1 are illustrated in gates of the corresponding transistors as shown in FIG. 2.

[0034] Referring to FIG. 2, the PMOS transistors P1 and P2 of the latch circuit 20 may be formed in a single P-type active region P_ACT. In other words, for an embodiment, the two PMOS transistors P1 and P2 contained in the two inverters INV1 and INV2, respectively, may share a single active region P_ACT.

[0035] For an embodiment, the NMOS transistors N1 and N2 of the fuse information transmission circuit 10 and the NMOS transistors N3 and N4 of the latch circuit 20 may be formed to share a single N-type active region N_ACT1. The NMOS transistors N5 and N6 of the data output circuit 30 may be formed to share another N-type active region N_ACT2. In this case, the N-type active region N_ACT1 may be located at one side of a P-type active region P_ACT in a first direction (e.g., a Y-axis direction), and the other N-type active region N_ACT2 may be located at one side (i.e., an opposite side of the P-type active region P_ACT) of the N-type active region N_ACT1 in the first direction.

[0036] That is, in each fuse latch (unit fuse latch) 1, the NMOS transistors N1 to N6 may be formed in two N-type active regions N_ACT1 and N_ACT2, and the PMOS transistors P1 and P2 may be formed in one P-type active region P_ACT1. In this case, because the N-type active regions N_ACT1 and N_ACT2 may be arranged in a two-stage structure at one side of the P-type active region P_ACT1, the active regions P_ACT, N_ACT1, and N_ACT2 may be arranged to have a P-N-N structure.

[0037] In the N-type active region N_ACT1, first terminals of the NMOS transistors N1 and N2 configured to respectively receive first fuse cell data FD1 and second fuse cell data FD2 may be arranged at both ends of the N-type active region N_ACT1. Through the above-indicated structure, if the fuse latches 1 are arranged in an array shape, adjacent fuse latches 1 may share a terminal (i.e., a signal transmission line) to which the first fuse cell data FD1 and the second fuse cell data FD2 are input.

[0038] In addition, power lines to supply the power-supply voltage VDD and the ground voltage VSS may be arranged at both sides of each fuse latch. Through the above-indicated structure, if the fuse latches 1 are arranged in an array shape, adjacent fuse latches may share the corresponding power lines.

[0039] A dummy active region DUMMY_ACT for facilitating a fabrication process may be formed at one side of the N-type active region N_ACT2 in a second direction (e.g., an X-axis direction) perpendicular to the first direction. A dummy NMOS transistor DN may be formed in the dummy active region DUMMY_ACT. A gate terminal, a first terminal, and a second terminal of the dummy NMOS transistor DN may be coupled to the ground voltage (VSS) terminal. The dummy active region DUMMY_ACT can be formed of not formed as necessary.

[0040] As is evident from FIG. 2, lines through which signals FD1, FD2, CON1, and CON2 are transmitted and lines (L) through which voltages VDD and VSS are transmitted may be formed of metal lines composed of M0 metal layer. In addition, the above-mentioned lines may be coupled to the gate G or the active regions P_ACT, N_ACT1, and N_ACT2 through a contact CONT.

[0041] FIG. 3 shows a conceptual diagram illustrating a layout structure of active regions of unit fuse latches (shown in FIG. 2) arranged in an array shape, according to an embodiment of the present disclosure.

[0042] Referring to FIG. 3, each unit fuse latch 1 may include a P-type active region P_ACT and N-type active regions N_ACT1 and N_ACT2 arranged in a first direction (Y-axis direction). In more detail, the P-type active region P_ACT, the N-type active region N_ACT1, and the N-type active region N_ACT2 may be sequentially arranged in the first direction (Y-axis direction), resulting in formation of a P-N-N structure arranged in the first direction. A fuse latch array may include a plurality of unit fuse latches 1 arranged in a line in a second direction (X-axis direction) perpendicular to the first direction (Y-axis direction).

[0043] As described above, active regions of each unit fuse latch 1 may be arranged to have a P-N-N structure, resulting in reduction in a width (W1) of the unit fuse latch 1. Specifically, if the unit fuse latches 1 are arranged in a line as an array shape, a width (W2) of the fuse latch array can be greatly reduced.

[0044] FIG. 4 shows a schematic diagram illustrating a circuit structure of a fuse latch 2, according to an embodiment of the present disclosure. For convenience of description, when possible, the same reference numerals are used throughout the drawings to refer to the same or like parts.

[0045] Referring to FIG. 4, the fuse latch 2 may include a fuse information transmission circuit 10, a latch circuit 20, a data output circuit 30, and an initialization circuit 40.

[0046] That is, the fuse latch 2 shown in FIG. 2 may further include the initialization circuit 40 as compared to the fuse latch 1 shown in FIG. 1.

[0047] The fuse information transmission circuit 10, the latch circuit 20, and the data output circuit 30 shown in FIG. 4 are identical in structure to those of FIG. 1, and as such, a detailed description of these components is omitted here for brevity.

[0048] The initialization circuit 40 may initialize a node B using a ground voltage (VSS) level in response to a reset signal RST. The initialization circuit 40 may include an NMOS transistor N7 coupled between the node B and the ground voltage (VSS) terminal.

[0049] The NMOS transistor N7 may include a gate terminal configured to receive the reset signal RST as an input signal, a first terminal coupled to the ground voltage (VSS) terminal, and a second terminal coupled to the node B.

[0050] As described above, the fuse latch 2 shown in FIG. 4 may include the initialization circuit 40, such that the fuse latch 2 may initialize fuse information at a desired time point using the initialization circuit 40.

[0051] FIG. 5 shows a schematic diagram illustrating an actual layout structure of constituent elements contained in the fuse latch 2 shown in FIG. 4, according to an embodiment of the present disclosure.

[0052] For convenience of description and better understanding of the present disclosure, reference numerals indicating the PMOS transistors P1 and P2 and the NMOS transistors N1 to N7 of FIG. 4 are illustrated in gates of the corresponding transistors as shown in FIG. 5.

[0053] Referring to FIG. 5, the PMOS transistors P1 and P2 of the latch circuit 20 may be formed in a single P-type active region P_ACT. In other words, for an embodiment, the two PMOS transistors P1 and P2 contained in the two inverters INV1 and INV2, respectively, may share a single active region P_ACT.

[0054] For an embodiment, the NMOS transistors N1 and N2 of the fuse information transmission circuit 10 and the NMOS transistors N3 and N4 of the latch circuit 20 may be formed to share a single N-type active region N_ACT1. The NMOS transistors N5 and N6 of the data output circuit 30 may be formed to share another N-type active region N_ACT2. In addition, the NMOS transistor N7 of the initialization circuit 40 may be formed in still another N-type active region N_ACT3.

[0055] In this case, the N-type active region N_ACT1 may be located at one side of a P-type active region P_ACT in a first direction (Y-axis direction), and each of the N-type active regions N_ACT2 and N_ACT3 may be located at one side (i.e., an opposite side of the P-type active region P_ACT) of the N-type active region N_ACT1 in the first direction. The N-type active regions N_ACT2 and N_ACT3 may be arranged parallel to each other in a second direction (X-axis direction) perpendicular to the first direction. The N-type active region N_ACT3 may act as the dummy active region DUMMY_ACT shown in FIG. 2.

[0056] In other words, in the unit fuse latch 2 of FIG. 5, three N-type active regions N_ACT1, N_ACT2, and N_ACT3 may be arranged in a two-stage structure at one side of the P-type active region P_ACT1.

[0057] In the second direction, a total length of the arrangement structure of the N-type active regions N_ACT2 and N_ACT3 may be identical to the length of the N-type active region N_ACT1.

[0058] FIG. 6 shows a schematic diagram illustrating an actual layout structure of constituent elements contained in the fuse latch 2 shown in FIG. 4, according to an embodiment of the present disclosure.

[0059] Compared with the layout structure of FIG. 5, the layout structure of FIG. 6 illustrates a case in which positions of the N-type active regions N_ACT2 and N_ACT3 are interchanged with each other such that positions of transistors and the connection relationship of metal lines (L) may be partially changed. That is, the active regions and transistors shown in FIG. 6 may be arranged with bilateral symmetry with respect to the active regions and transistors shown in FIG. 5.

[0060] As illustrated in FIGS. 5 and 6, assuming that three N-type active regions N_ACT1, N_ACT2, and N_ACT3 are arranged in a two-stage structure at one side of the P-type active region P_ACT1, the positions of the N-type active regions N_ACT2 and N_ACT3 may be interchanged with each other.

[0061] Likewise, positions of the N-type active region N_ACT2 and the dummy active region DUMMY_ACT shown in FIG. 2 may also be interchanged with each other as necessary.

[0062] As is apparent from the above description, embodiments of the present disclosure may improve a structure of a fuse latch, resulting in increased regional gain.

[0063] Those skilled in the art will appreciate that embodiments may be carried out in other specific ways to those set forth herein without departing from the spirit and essential characteristics of the disclosure. The above embodiments are therefore to be construed in all aspects as illustrative and not restrictive. The scope of the disclosure should be determined by the appended claims and their legal equivalents, not by the above description. Further, all changes coming within the meaning and equivalency range of the appended claims are intended to be embraced therein. In addition, it is obvious to those skilled in the art that claims that are not explicitly cited in each other in the appended claims may be presented in combination as an embodiment or included as a new claim by a subsequent amendment after the application is filed.

[0064] Although a number of illustrative embodiments have been described, it should be understood that numerous other modifications and embodiments can be devised by those skilled in the art that will fall within the spirit and scope of the principles of this disclosure. Particularly, numerous variations and modifications are possible in the component parts and/or arrangements which are within the scope of the disclosure, the drawings and the accompanying claims. In addition to variations and modifications in the component parts and/or arrangements, alternative uses will also be apparent to those skilled in the art.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.