Apparatus And Method For Assisting Envelope Tracking With Transient Response In Supply Voltage For Power Amplifier

MCGOWAN; Michael ; et al.

U.S. patent application number 16/353632 was filed with the patent office on 2020-02-13 for apparatus and method for assisting envelope tracking with transient response in supply voltage for power amplifier. The applicant listed for this patent is QUALCOMM Incorporated. Invention is credited to Michael MCGOWAN, Iulian MIREA.

| Application Number | 20200052654 16/353632 |

| Document ID | / |

| Family ID | 69406556 |

| Filed Date | 2020-02-13 |

| United States Patent Application | 20200052654 |

| Kind Code | A1 |

| MCGOWAN; Michael ; et al. | February 13, 2020 |

APPARATUS AND METHOD FOR ASSISTING ENVELOPE TRACKING WITH TRANSIENT RESPONSE IN SUPPLY VOLTAGE FOR POWER AMPLIFIER

Abstract

A power amplifier (PA) circuit includes a circuit for generating a supply voltage at an upper voltage rail for a power amplifier (PA). The circuit includes a DC-to-DC converter for generating a voltage from which the supply voltage is generated; a linear amplifier for sourcing or sinking current to or from the upper voltage rail via a capacitor for performing fine adjustment of the supply voltage; a first switching device coupled between an output of the linear amplifier and a lower voltage rail to selectively assist the linear amplifier sink current through the capacitor to deal with actual or anticipated transient response of the supply voltage; and a second switching device coupled between the upper voltage rail and the lower voltage rail to selectively discharge the capacitor in response to actual or anticipated transient response of the supply voltage.

| Inventors: | MCGOWAN; Michael; (Mesa, AZ) ; MIREA; Iulian; (San Diego, CA) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 69406556 | ||||||||||

| Appl. No.: | 16/353632 | ||||||||||

| Filed: | March 14, 2019 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 62717317 | Aug 10, 2018 | |||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H03F 3/245 20130101; H03F 3/213 20130101; H03F 2200/393 20130101; H03F 3/68 20130101; H03F 1/0227 20130101; H03F 2200/301 20130101; H03F 2200/102 20130101; H03F 3/195 20130101; H03F 2200/144 20130101; H03F 2200/267 20130101; H03F 2203/45116 20130101; H03F 2200/396 20130101; H03F 3/45475 20130101; H03F 2203/45526 20130101; H03F 3/45071 20130101; H03F 1/0255 20130101; H03F 2200/129 20130101 |

| International Class: | H03F 1/02 20060101 H03F001/02; H03F 3/213 20060101 H03F003/213 |

Claims

1. An apparatus, comprising: a load coupled between a first voltage rail and a second voltage rail; a capacitor; an amplifier configured to source or sink current to or from the first voltage rail via the capacitor; and a first switching device coupled between an output of the amplifier and the second voltage rail, wherein the first switching device is configured to selectively sink current from the first voltage rail via the capacitor to control a supply voltage on the first voltage rail.

2. The apparatus of claim 1, further comprising a controller configured to turn on the first switching device to sink current from the first voltage rail via the capacitor in response to an event.

3. The apparatus of claim 2, wherein the event includes a mode change between a first mode where the supply voltage is tracking an average power of an input signal and a second mode where the supply voltage is tracking an envelope of the input signal.

4. The apparatus of claim 3, wherein the load comprises a power amplifier configured to generate an output signal based on the input signal.

5. The apparatus of claim 1, wherein the amplifier is configured to sink current from the first voltage rail via the capacitor at the same time the first switching device is selected to sink current from the first voltage rail via the capacitor.

6. The apparatus of claim 1, wherein the first switching device is configured to be turned off while the amplifier is sourcing current to the first voltage rail via the capacitor.

7. The apparatus of claim 1, wherein the first switching device comprises a field effect transistor (FET).

8. The apparatus of claim 1, further comprising a second switching device coupled between the first voltage rail and the second voltage rail, wherein the second switching device is configured to selectively discharge the capacitor.

9. The apparatus of claim 8, further comprising: a measuring device configured to measure a voltage drop across the capacitor; and a controller configured to turn on the second switching device based on the voltage drop across the capacitor.

10. The apparatus of claim 8, wherein the second switching device comprises a field effect transistor (FET).

11. The apparatus of claim 8, further comprising a controller configured to turn on the second switching device based on an input signal or a change between a first mode of controlling the supply voltage based on an average power of the input signal and a second mode of controlling the supply voltage based on an envelope of the input signal.

12. The apparatus of claim 1, further comprising a DC-to-DC converter configured to generate a voltage, wherein the supply voltage is based on the voltage from the DC-to-DC converter.

13. The apparatus of claim 12, further comprising an inductor coupled between the DC-to-DC converter and the first voltage rail for the load.

14. A method, comprising: sourcing or sinking current to or from a first voltage rail for a load via a first current path including a capacitor to control a supply voltage on the first voltage rail; and selectively sinking current from the first voltage rail for the load via a second current path including the capacitor to further control the supply voltage on the first voltage rail, wherein the second current path is different than the first current path.

15. The method of claim 14, wherein the first current path comprises an amplifier, the capacitor, and the first voltage rail.

16. The method of claim 15, wherein the second current path comprises the first voltage rail, the capacitor, a switching device, and a second voltage rail.

17. The method of claim 14, wherein the load comprises a power amplifier, and wherein sourcing or sinking current to or from the first voltage rail is based on an input signal to the power amplifier.

18. The method of claim 17, wherein sourcing or sinking current to or from the first voltage rail is based on an average power of the input signal.

19. The method of claim 17, wherein sourcing or sinking current to or from the first voltage rail is based on an envelope of the input signal.

20. The method of claim 17, wherein selectively sinking current from the first voltage rail for the load via the second current path is in response to a mode change between a first mode where sourcing or sinking current to or from the first voltage rail is based on an average power of the input signal and a second mode where sourcing or sinking current to or from the first voltage rail is based on an envelope of the input signal.

21. The method of claim 14, further comprising selectively discharging the capacitor.

22. The method of claim 21, wherein selectively discharging the capacitor is via a third current path.

23. The method of claim 22, wherein the third current path comprises the capacitor, a switching device, and a second voltage rail.

24. The method of claim 14, wherein the load comprises a power amplifier, and wherein selectively discharging the capacitor is in response to an input signal to a power amplifier or a mode change between a first mode where sourcing or sinking current to or from the first voltage rail is based on an average power of the input signal and a second mode where sourcing or sinking current to or from the first voltage rail is based on an envelope of the input signal.

25. An apparatus, comprising: a load coupled between a first voltage rail and a second voltage rail; a capacitor; an amplifier configured to source or sink current to or from the first voltage rail via the capacitor; and a switching device coupled between the first voltage rail and the second voltage rail, wherein the switching device is configured to selectively discharge the capacitor.

26. The apparatus of claim 25, further comprising: a measuring device configured to measure a voltage drop across the capacitor; and a controller configured to turn on the second switching device based on the voltage drop across the capacitor.

27. The apparatus of claim 25, further comprising a controller configured to turn on the second switching device based on an input signal or a mode change between a first mode of controlling the supply voltage based on an average power of the input signal and a second mode of controlling the supply voltage based on an envelope of the input signal.

28. A method, comprising: sourcing or sinking current to or from a voltage rail for a load via a first current path including a capacitor to control a supply voltage on the voltage rail; and selectively discharging the capacitor via a second current path different than the first current path.

29. The method of claim 28, wherein selectively discharging the capacitor is based on an input signal or a mode change between a first mode of controlling the supply voltage based on an average power of the input signal and a second mode of controlling the supply voltage based on an envelope of the input signal.

Description

CROSS-REFERENCE TO RELATED APPLICATION

[0001] This application claims the benefit of the filing date of U.S. Provisional Application, Ser. No. 62/717,317, filed on Aug. 10, 2018, which is incorporated herein by reference.

FIELD

[0002] Aspects of the present disclosure relate generally to envelop tracking power amplifiers, and in particular, to an apparatus and method for assisting an envelope tracking circuit with transient response in a supply voltage for a power amplifier (PA) by employing a pair of shunt switching devices for discharging a capacitor and increasing the sinking current through the capacitor, respectively.

BACKGROUND

[0003] A power amplifier (PA) is typically employed in a transmitter to amplify an input radio frequency (RF) signal to generate an output RF signal for transmission into free space via an antenna. Many power amplifiers (PAs) are employed in small formfactor devices, such as smart phones. Because such formfactor devices use batteries as their primary power source, it is often desirable to operate power amplifiers (PAs) in a power efficient manner.

[0004] To this end, such devices employ power amplifier (PA) circuits that use average power tracking (APT) and envelope tracking (ET) for generating a supply voltage for a power amplifier (PA) such that the operation of the power amplifier (PA) is performed in a power efficient manner. Accordingly, the disclosure relates to improvements in this regard.

SUMMARY

[0005] The following presents a simplified summary of one or more embodiments in order to provide a basic understanding of such embodiments. This summary is not an extensive overview of all contemplated embodiments, and is intended to neither identify key or critical elements of all embodiments nor delineate the scope of any or all embodiments. Its sole purpose is to present some concepts of one or more embodiments in a simplified form as a prelude to the more detailed description that is presented later.

[0006] An aspect of the disclosure relates to an apparatus including a load coupled between an upper voltage rail and a lower voltage rail; a capacitor; an amplifier configured to source or sink current to or from the upper voltage rail via the capacitor; and a first switching device coupled between an output of the amplifier and the lower voltage rail, wherein the first switching device is configured to selectively sink current from the upper voltage rail via the capacitor to control a supply voltage on the upper voltage rail.

[0007] Another aspect of the disclosure relates to a method including sourcing or sinking current to or from a voltage rail for a load via a first current path including a capacitor to control a supply voltage on the voltage rail; and selectively sinking current from the voltage rail for the load via a second current path including the capacitor to further control the supply voltage on the voltage rail, wherein the second current path is different than the first current path.

[0008] Another aspect of the disclosure relates to an apparatus including means for sourcing or sinking current to or from a voltage rail for a load via a first current path including a capacitor; and means for selectively sinking current from the voltage rail for the load via a second current path including the capacitor to further control the supply voltage on the voltage rail, wherein the second current path is different than the first current path.

[0009] Another aspect of the disclosure relates to an apparatus including a load coupled between an upper voltage rail and a lower voltage rail; a capacitor; an amplifier configured to source or sink current to or from the upper voltage rail via the capacitor; and a switching device coupled between the upper voltage rail and the lower voltage rail, wherein the switching device is configured to selectively discharge the capacitor.

[0010] Another aspect of the disclosure relates to a method including sourcing or sinking current to or from a voltage rail for a load via a first current path including a capacitor to control a supply voltage on the voltage rail; and selectively discharging the capacitor via a second current path different than the first current path.

[0011] Another aspect of the disclosure relates to an apparatus including means for sourcing or sinking current to or from a voltage rail for a load via a first current path including a capacitor to control a supply voltage on the voltage rail; and means for selectively discharging the capacitor via a second current path different than the first current path.

[0012] To the accomplishment of the foregoing and related ends, the one or more embodiments include the features hereinafter fully described and particularly pointed out in the claims. The following description and the annexed drawings set forth in detail certain illustrative aspects of the one or more embodiments. These aspects are indicative, however, of but a few of the various ways in which the principles of various embodiments may be employed and the description embodiments are intended to include all such aspects and their equivalents.

BRIEF DESCRIPTION OF THE DRAWINGS

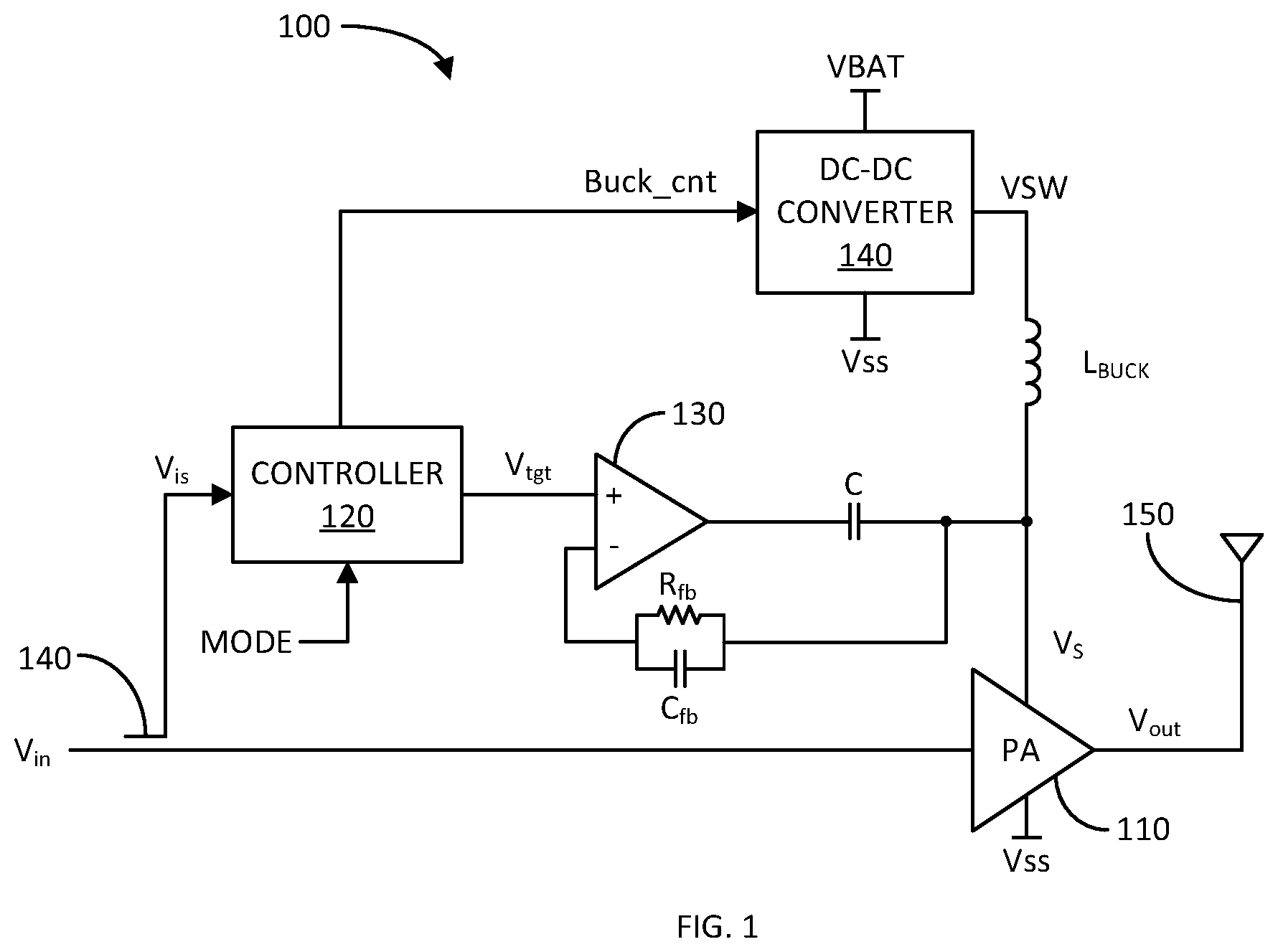

[0013] FIG. 1 illustrates a schematic diagram of an exemplary power amplifier (PA) circuit with average power tracking (APT) and envelope tracking (ET) in accordance with an aspect of the disclosure.

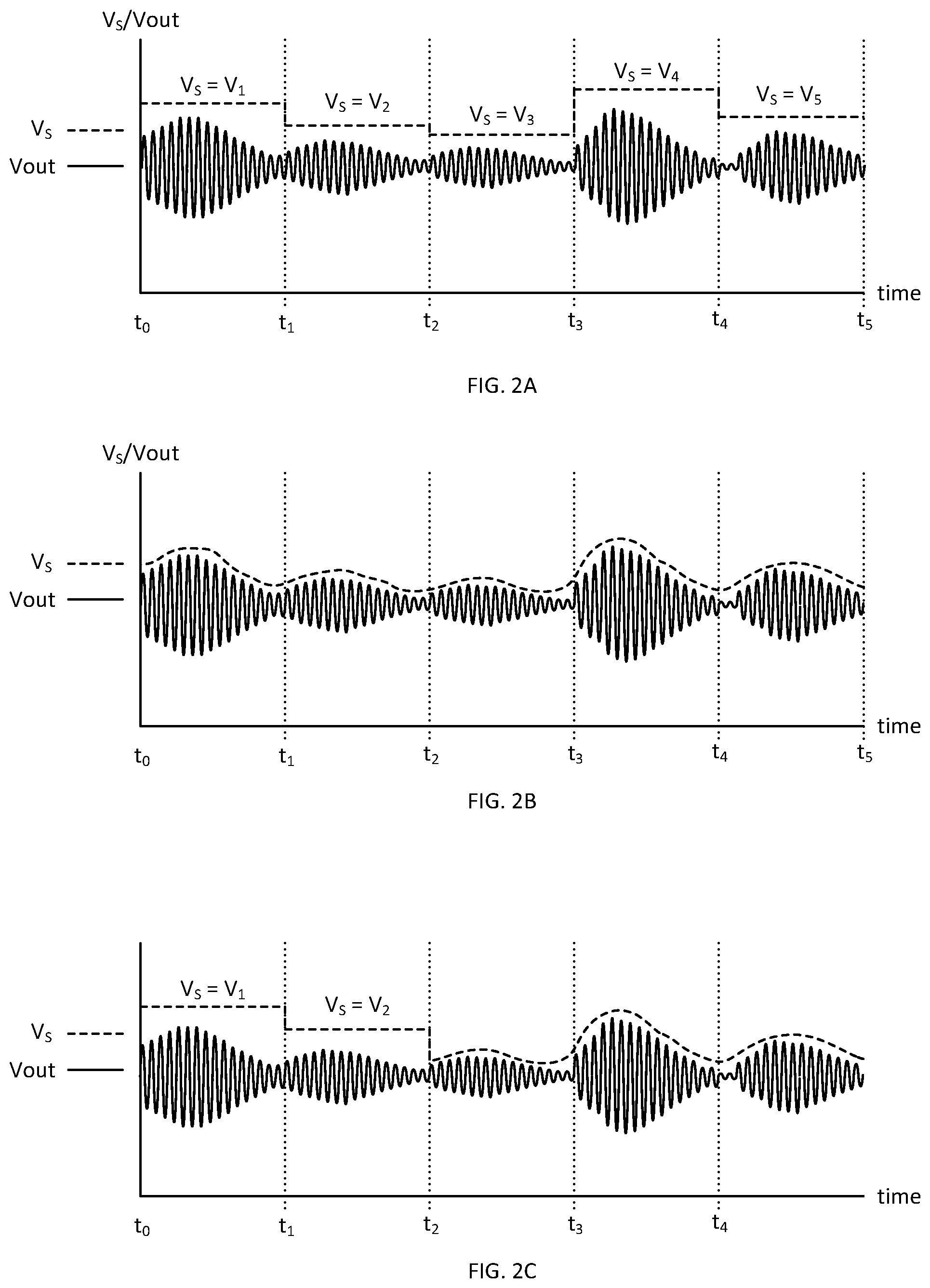

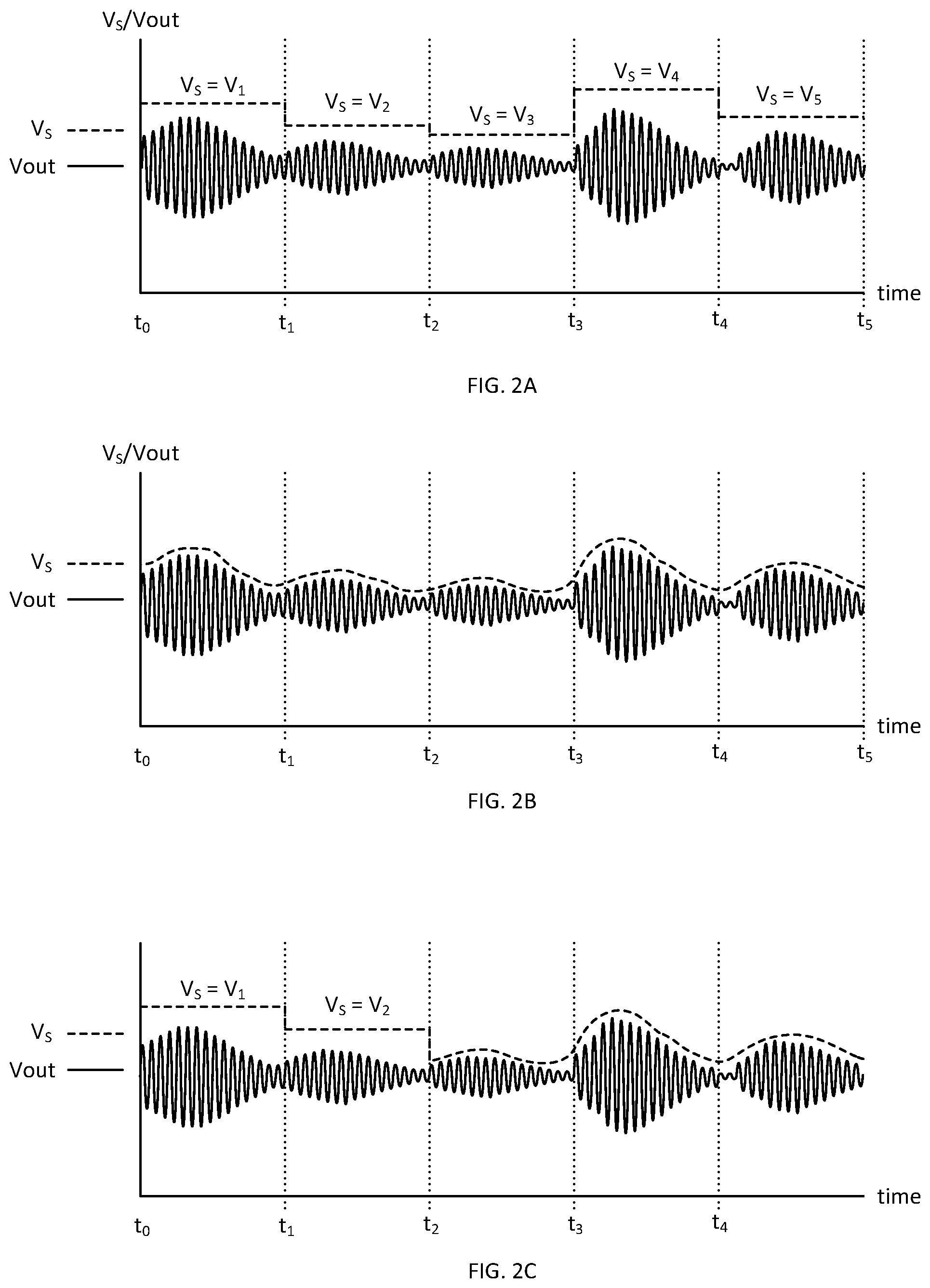

[0014] FIG. 2A illustrates a graph of an exemplary supply voltage V.sub.S and output voltage signal V.sub.out of a power amplifier (PA) over time when the PA circuit is operating in an average power tracking (APT) mode in accordance with another aspect of the disclosure.

[0015] FIG. 2B illustrates a graph of an exemplary supply voltage V.sub.S and output voltage signal V.sub.out of a power amplifier (PA) over time when the PA circuit is operating in an envelope tracking (ET) mode in accordance with another aspect of the disclosure.

[0016] FIG. 2C illustrates a graph of an exemplary supply voltage V.sub.S and output voltage signal V.sub.out of a power amplifier (PA) over time when the PA circuit changes its operating mode from average power tracking (APT) to envelope tracking (ET) in accordance with another aspect of the disclosure.

[0017] FIG. 3 illustrates a schematic diagram of another exemplary power amplifier (PA) circuit with average power tracking (APT) and envelope tracking (ET) in accordance with another aspect of the disclosure.

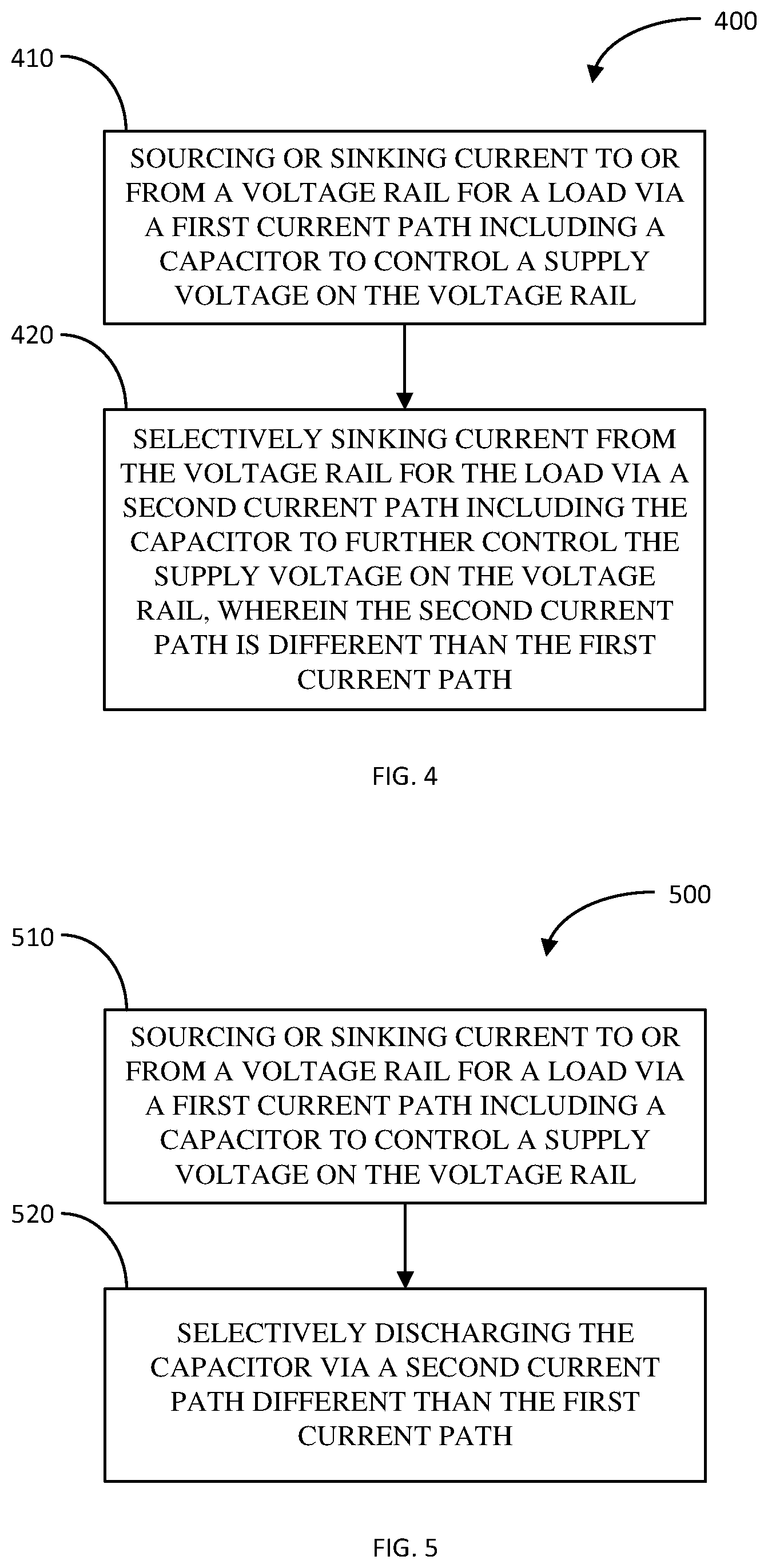

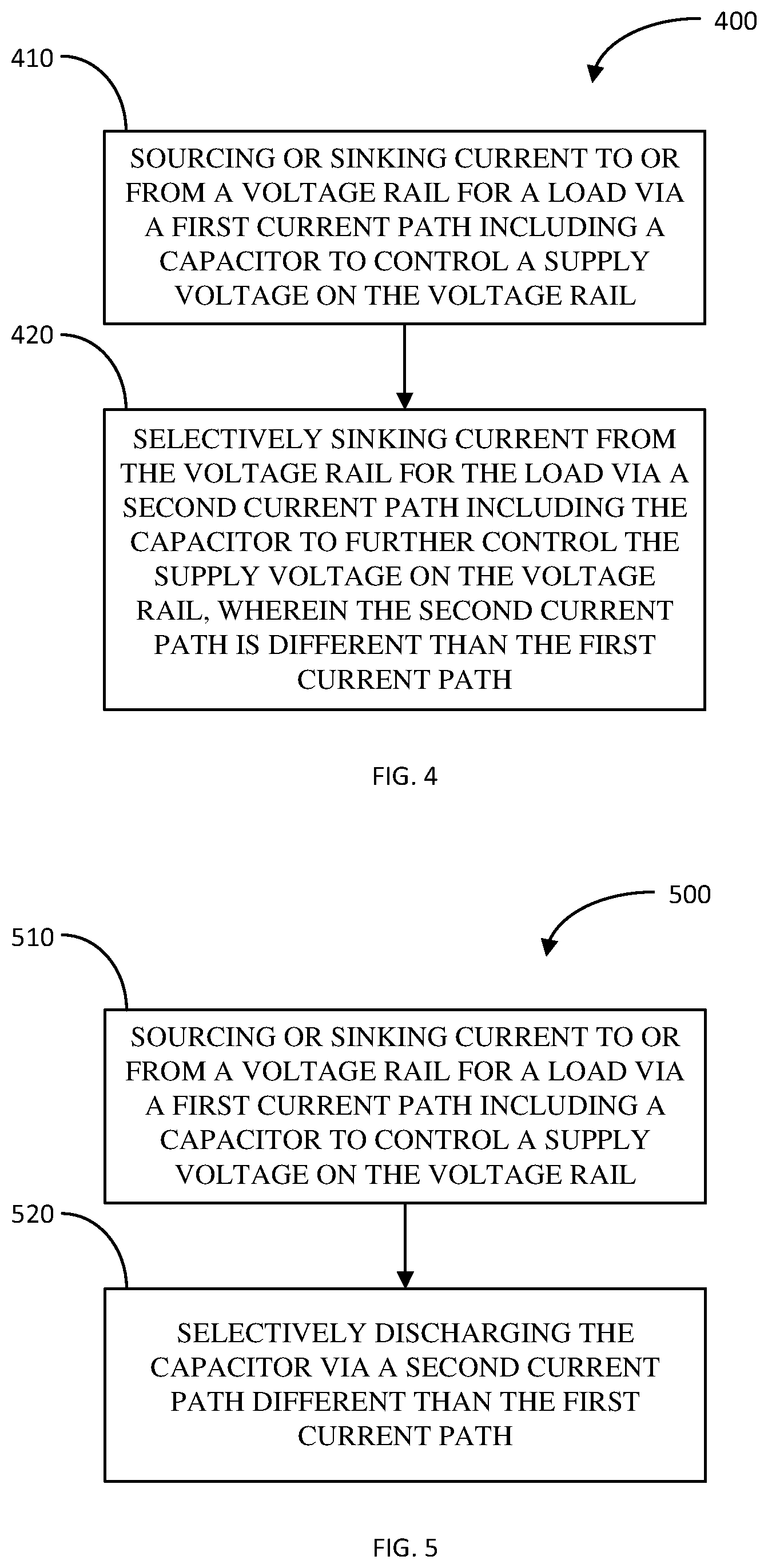

[0018] FIG. 4 illustrates a flow diagram of an exemplary method of generating a supply voltage for a power amplifier (PA) in accordance with another aspect of the disclosure.

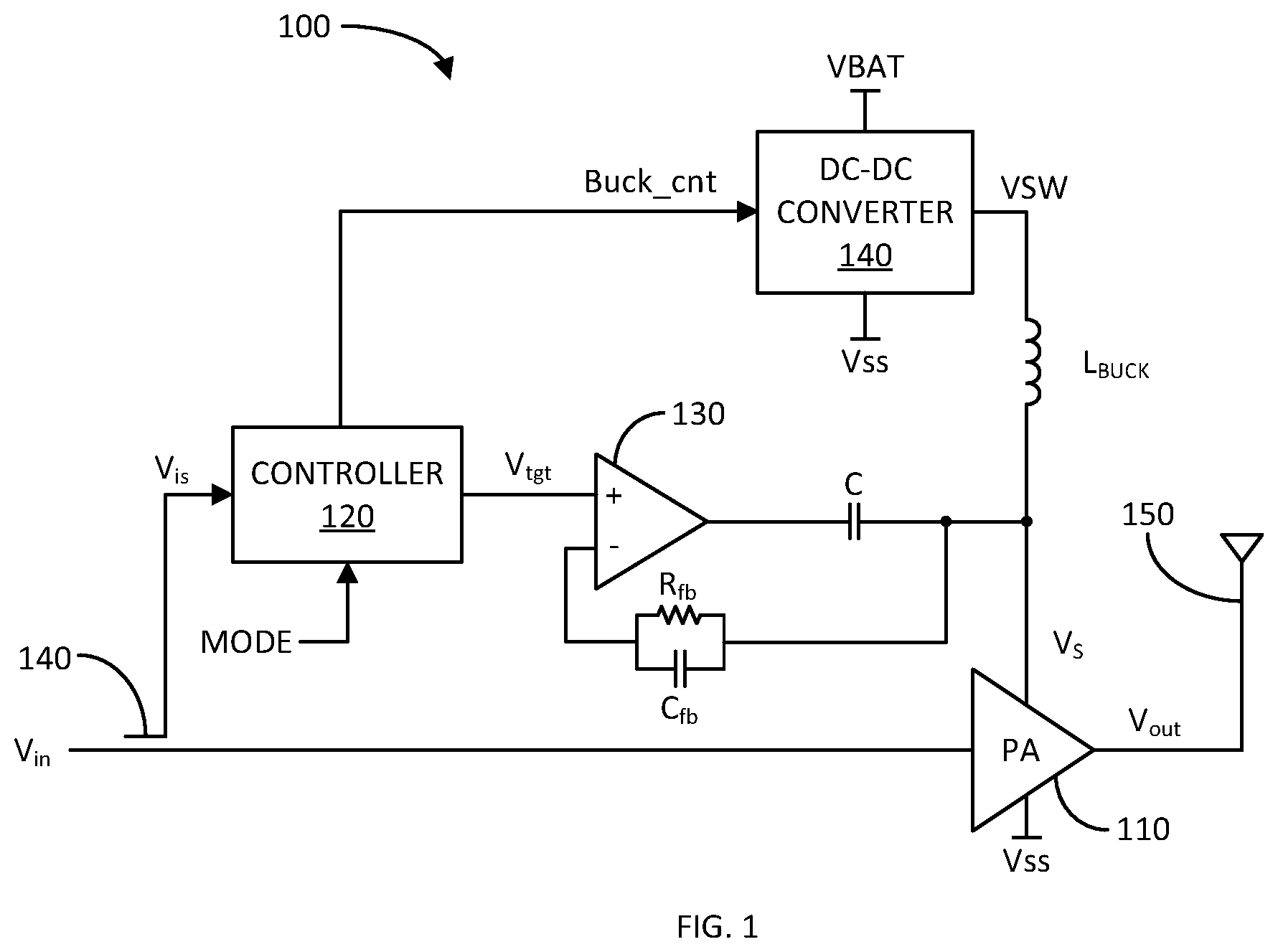

[0019] FIG. 5 illustrates a flow diagram of another exemplary method of generating a supply voltage for a power amplifier (PA) in accordance with another aspect of the disclosure.

DETAILED DESCRIPTION

[0020] The detailed description set forth below, in connection with the appended drawings, is intended as a description of various configurations and is not intended to represent the only configurations in which the concepts described herein may be practiced. The detailed description includes specific details for the purpose of providing a thorough understanding of the various concepts. However, it will be apparent to those skilled in the art that these concepts may be practiced without these specific details. In some instances, well-known structures and components are shown in block diagram form in order to avoid obscuring such concepts.

[0021] FIG. 1 illustrates a schematic diagram of an exemplary power amplifier (PA) circuit 100 with average power tracking (APT) and envelope tracking (ET) in accordance with an aspect of the disclosure. The power amplifier (PA) circuit 100 includes a power amplifier (PA) 110 configured to amplify an input voltage signal V.sub.in to generate an output voltage signal V.sub.out. The power amplifier (PA) circuit 100 further includes an antenna 150 for converting the output voltage signal V.sub.out into a wireless signal for transmission into free space.

[0022] As discussed, in many applications, it is desirable to operate the power amplifier (PA) 110 in a power efficient manner. This is typically accomplished by providing a variable supply voltage V.sub.S such that the power amplifier (PA) 110 is driven into compression (e.g., to the 1 dB compression point) for at least a portion of the output voltage signal V.sub.out. As such, the variable supply voltage V.sub.S is varied as a function of the input voltage signal V.sub.in to operate the power amplifier (PA) 110 in compression for a significant amount of time to achieve the desired power efficiency.

[0023] Two techniques that have gained wide popularity in varying a PA supply voltage for power efficient operation purpose are average power tracking (APT) and envelope tracking (ET). In accordance with the average power tracking (APT), the supply voltage for a power amplifier (PA) is varied as a function of the average voltage or power of the input voltage signal V.sub.in over different intervals. In accordance with the envelope tracking (ET), the supply voltage for a power amplifier (PA) is varied in accordance with the envelope of the input voltage signal V.sub.in. These techniques are discussed further with reference to FIGS. 2A-2B.

[0024] FIG. 2A illustrates a graph of an exemplary supply voltage V.sub.S and output voltage signal V.sub.out of the power amplifier (PA) 110 over time when the power amplifier (PA) circuit 100 is operating in average power tracking (APT) mode in accordance with another aspect of the disclosure. The vertical or y-axis of the graph represents the supply voltage V.sub.S indicated as a dashed line and the output voltage signal V.sub.out indicated as a solid line. The horizontal or x-axis of the graph represents time.

[0025] Thus, as depicted, during time interval t.sub.0 to t.sub.1, the PA circuit 100 determines the average voltage or power of the input voltage signal V.sub.in during such time interval, and generates the supply voltage V.sub.S at a voltage level V.sub.1, which is a function or based on the average voltage or power of the input voltage signal V.sub.in. Similarly, during time interval t.sub.1 to t.sub.2, the PA circuit 100 determines the average voltage or power of the input voltage signal V.sub.in during such time interval, and generates the supply voltage V.sub.S at a voltage level V.sub.2 as a function or based on the average voltage or power of the input voltage signal V.sub.in. Since the average voltage or power of the input voltage signal V.sub.in during time interval t.sub.1 to t.sub.2 is less than the average voltage or power of the input voltage signal V.sub.in during time interval t.sub.0 to t.sub.1, the voltage level V.sub.2 is less than the voltage level V.sub.1.

[0026] Similarly, the PA circuit 100 varies the supply voltage V.sub.S for the power amplifier (PA) 100 in accordance with the average voltage or power of the input voltage signal V.sub.in during time intervals t.sub.2-t.sub.3, t.sub.3-t.sub.4, and t.sub.4-t.sub.5 to generate the supply voltage V.sub.S at voltage levels V.sub.3, V.sub.4, and V.sub.S, respectively. As the average voltage or power of the input voltage signal V.sub.in during time intervals t.sub.2-t.sub.3, t.sub.3-t.sub.4, and t.sub.4-t.sub.5 decreases, increases, and decreases after time interval t.sub.1-t.sub.2, the voltage levels V.sub.3, V.sub.4, and V.sub.5 of the supply voltage V.sub.S similarly decreases, increases, and decreases with respect to voltage level V.sub.2 (e.g., V.sub.3<V.sub.2, V.sub.4>V.sub.3, and V.sub.5<V.sub.4).

[0027] To operate the power amplifier (PA) efficiently in average power tracking (APT) mode, the power amplifier (PA) circuit 100 sets of the voltage level of the supply voltage V.sub.S such that the power amplifier (PA) is somewhat in compression (e.g., at substantially the 1 dB compression point) during the highest peak of the output voltage signal V.sub.OUT during each interval. However, with average power tracking (APT), there is some power efficiency reduction when the output voltage signal V.sub.out is not at its peak; such as when the output voltage signal V.sub.out dips into a valley. Generally, the average power tracking (APT) is more efficient when the output signal V.sub.OUT has a relatively low power-to-average power ratio (PAPR) or low crest factor.

[0028] FIG. 2B illustrates a graph of an exemplary supply voltage V.sub.S and output voltage signal V.sub.out of the power amplifier (PA) 110 over time when the PA circuit 100 is operating in envelope tracking (ET) mode in accordance with another aspect of the disclosure. Similarly, the vertical or y-axis of the graph represents the supply voltage V.sub.S indicated as a dashed line and the output voltage signal V.sub.out indicated as a solid line. The horizontal or x-axis of the graph represents time.

[0029] As depicted, in envelope tracking (ET) mode, the power amplifier (PA) circuit 100 generates the supply voltage V.sub.S for the power amplifier (PA) 110 such that the supply voltage V.sub.S varies with the envelope of the input voltage signal V.sub.in or the output voltage signal V.sub.out. Thus, the power amplifier (PA) circuit 100 attempts to operate the power amplifier (PA) 110 into or close to compression during the entire time the output voltage signal V.sub.in is varying. The power amplifier (PA) circuit 100 may limit the amount at which the supply voltage V.sub.S may be decreased during envelope tracking to prevent the power amplifier (PA) 110 from malfunctioning or operating in an unintended manner.

[0030] As can be seen, envelope tracking (ET) is a more aggressive technique of operating the power amplifier (PA) 110 in a power efficient manner. Envelope tracking (ET) improves power efficiency more so when the output signal V.sub.OUT has a relatively high power-to-average power ratio (PAPR) or crest factor. The application of the average power tracking (APT) and envelope tracking (ET) techniques need not be mutually exclusive. For example, the power amplifier (PA) circuit 100 may employ average power tracking (APT) when the input or output voltage signal V.sub.in or V.sub.out has a relatively low PAPR or crest factor and/or another condition exists, and employ envelope tracking (ET) when the input or output voltage signal V.sub.in or V.sub.out has a relatively high PAPR or crest factor and/or yet another condition exists.

[0031] Referring again to FIG. 1, for effectuating average power tracking (APT) or envelope tracking (ET), the power amplifier (PA) circuit 100 further includes a controller 120, and an amplifier 130 including an output capacitor C and a feedback network with a feedback resistor R.sub.fb coupled in parallel with a feedback capacitor C.sub.fb. Additionally, the power amplifier (PA) circuit 100 includes a DC-to-DC converter circuit 140, which may be configured as a Buck converter including a Buck inductor L.sub.BUCK.

[0032] A sample V.sub.is of the input voltage signal V.sub.in is applied to an input of the controller 120 via a directional coupler 140. Additionally, a mode signal is applied to the controller 120; the mode signal indicating whether average power tracking (APT) or envelope tracking (ET) should be employed. Based on the sampled input voltage signal V.sub.is and the mode signal, the controller 120 generates a control voltage Buck_cnt for the DC-to-DC converter 140 and a target supply voltage V.sub.tgt. If the mode signal indicates average power tracking (APT) mode, the linear amplifier 330 may be disabled. In such case, the DC-to-DC converter 140 solely controls the supply voltage V.sub.S for the power amplifier (PA) 310 based on the average power of the input signal Vin.

[0033] The DC-to-DC converter 140 is coupled between an upper voltage rail which may receive a battery voltage VBAT and a lower voltage rail Vss (e.g., ground). The DC-to-DC converter 140 generates a voltage VSW based on the control signal Buck_cnt from the controller 120 and the battery voltage VBAT. As an example, the DC-to-DC converter 140 may vary the voltage VSW from 0V to the battery voltage VBAT to an auxiliary voltage VAUX (higher than the battery voltage VBAT), down to the battery voltage VBAT again, and then back to 0V. The process is repeated or altered to achieve a supply voltage V.sub.S for the power amplifier (PA) 110, via current flowing through the Buck inductor L.sub.BUCK, that substantially tracks the average voltage or power of the input voltage signal V.sub.in. Most of the power (e.g., direct current (DC) power) supplied to the power amplifier (PA) 110 comes from the DC-to-DC converter 140.

[0034] The target supply voltage V.sub.tgt from the controller 120 is applied to a positive input of the amplifier 130. The capacitor C couples the output of the amplifier 130 to the voltage rail for the power amplifier (PA) 110. The feedback network (R.sub.fb in parallel with C.sub.fb) is coupled between the voltage rail for the power amplifier (PA) 110 and the negative input of the amplifier 130. The amplifier 130 sources or sinks current (e.g., alternating current (ac)) to and from the voltage rail for the power amplifier (PA) 110 to perform fine adjustment of the supply voltage V.sub.S to achieve the desired average power tracking (APT) or envelope tracking (ET), as discussed. Typically, the linear amplifier 330 control of the supply voltage V.sub.s may be performed on envelope tracking (ET) mode as the linear amplifier 330 has a higher bandwidth than the DC-to-DC converter 340, and is able to control the supply voltage V.sub.S in response to the high frequency changes of the envelope of the input signal V.sub.in.

[0035] In order to perform the fine adjustment of the supply voltage V.sub.S for the power amplifier (PA) 110, the amplifier 130 needs to source or sink the proper amount of current through the capacitor C to regulate the supply voltage V.sub.S as required based on the selected mode. However, when the supply voltage V.sub.S is subject to a large transient response (e.g., the supply voltage V.sub.S increases at a fast rate), the amplifier 130 needs to sink a large amount of current to lower or maintain the supply voltage V.sub.S at the desired level as well as prevent damage to the power amplifier (PA) 110 from excessive supply voltage V.sub.S. Often these kinds of transient response in the supply voltage V.sub.S occur when the power amplifier (PA) circuit is changing modes, as explained in more detail below.

[0036] FIG. 2C illustrates a graph of an exemplary supply voltage V.sub.S and output voltage signal V.sub.out of the power amplifier (PA) 110 over time when the PA circuit 100 changes its operating mode from average power tracking (APT) to envelope tracking (ET) in accordance with another aspect of the disclosure. Similarly, the vertical or y-axis of the graph represents the supply voltage V.sub.S indicated as a dashed line and the output voltage signal V.sub.out indicated as a solid line. The horizontal or x-axis of the graph represents time.

[0037] As indicated, during time interval t.sub.0-t.sub.2, the power amplifier (PA) circuit 100 is operating in average power tracking (APT) mode. Then, at time t.sub.2, the power amplifier (PA) circuit 100 changes mode from average power tracking (APT) to envelope tracking (ET). Accordingly, during time interval t.sub.2-t.sub.5, the power amplifier (PA) circuit 100 is operating in envelope tracking (ET) mode.

[0038] During the transition between modes at time t.sub.2, the supply voltage V.sub.S has to change or decrease considerably (an example of a transient response) so that the supply voltage V.sub.S is at the appropriate level for envelope tracking (ET). This may require the amplifier 130 to sink substantial current to bring the supply voltage V.sub.S down in a fast manner so that envelop tracking (ET) is effectuated. Additionally, the voltage across the capacitor C may need to be reduced (i.e., the discharging of the capacitor C) in a fast manner in order to maintain the supply voltage V.sub.S at a desired voltage level based on the operation mode or the waveform of the input signal Vin, as well as to keep the supply voltage V.sub.S from spiking up to dangerous level where damage may occur to the power amplifier (PA) 110. The following implementation addresses these concerns.

[0039] FIG. 3 illustrates a schematic diagram of another exemplary power amplifier (PA) circuit 300 with average power tracking (APT) and envelope tracking (ET) in accordance with another aspect of the disclosure.

[0040] In summary, the power amplifier (PA) circuit 300 includes a first switching device coupled between the output of the linear amplifier and the lower voltage rail Vss to assist the linear amplifier in sinking current from the voltage rail of the power amplifier (PA). This helps the linear amplifier reduce the supply voltage V.sub.S when needed, for example, in response to an actual or anticipated transient response condition due to a mode change. Additionally, the power amplifier (PA) circuit 300 includes a second switching device coupled between the upper voltage rail for the power amplifier (PA) and the lower voltage rail Vss to discharge the capacitor as needed, such as in response to an actual or anticipated transient response condition due to a mode change or change in an input waveform requiring a small voltage drop across a capacitor C between a linear amplifier and the upper voltage rail for the power amplifier (PA).

[0041] In conjunction with the second switching device, the power amplifier (PA) circuit 300 includes a circuit for measuring the voltage across the capacitor. The measured voltage is provided to the controller. The controller turns on the second switching device based on the mode signal, the waveform of the input signal V.sub.in, and/or the measured voltage across the capacitor to deal with transient response that may be present in the supply voltage V.sub.S.

[0042] More specifically, the power amplifier (PA) circuit 300 includes a power amplifier (PA) 310, a controller 320, a linear amplifier 330 including an output capacitor C and a feedback network with feedback resistor R.sub.fb coupled in parallel with a feedback capacitor C.sub.fb, a DC-to-DC converter 340 including a Buck inductor L.sub.BUCK, and an antenna 360. These devices operate similar to the corresponding devices in power amplifier (PA) circuit 100 previously discussed in detail.

[0043] To deal with actual or anticipated transient response that may occur in the supply voltage V.sub.S, the power amplifier (PA) circuit 300 further includes a first switching device M1 coupled between the output of the linear amplifier 330 and the lower voltage rail Vss. Additionally, the power amplifier (PA) circuit 300 further includes a second switching device M2 coupled between the upper voltage rail for the power amplifier (PA) 310 and the lower voltage rail Vss. The first and second switching devices M1 and M2 may each be configured as an n-channel metal oxide semiconductor field effect transistor (NMOS FET).

[0044] Further, the power amplifier (PA) circuit 300 includes a measuring circuit 350 configured to measure the voltage .DELTA.V.sub.C across the capacitor C. The measured voltage .DELTA.V.sub.C is provided to the controller 320. The controller 320 generates a control signal SWA, applied to the first switching device M1, to control its on and off state. For example, during non-transient response condition, the controller 320 generates the control signal SWA as a low logic voltage (e.g., Vss) to maintain the first switching device M1 off. During transient response condition, such as when the mode of operation is switched between average power tracking (APT) and envelope tracking (ET) modes, the controller 320 generates the control signal SWA as a high logic voltage (e.g., Vdd) to turn on the first switching device M1 to help the output of the linear amplifier 330 sink current from the upper voltage rail for the power amplifier (PA) 310 so as to reduce the supply voltage V.sub.S quickly to counter the transient response.

[0045] Similarly, the controller 320 may monitor the voltage .DELTA.V.sub.C across the capacitor C via the measuring circuit 350, and generate the control signal SWP based on the voltage .DELTA.V.sub.C to counter any potentially dangerous or undesirable transient response in the supply voltage V.sub.S or set the supply voltage at the desired level to effectuate envelope tracking For example, if the controller 320 does not detect the transient response condition or the voltage .DELTA.V.sub.C across the capacitor C is at an appropriate level based on the current operating condition, the controller 320 generates the control signal SWP as a low logic voltage (e.g., Vss) to maintain the second switching device M2 off. If, on the other hand, the controller 320 determines that the transient response is occurring in the supply voltage V.sub.S or for any reason in which the voltage .DELTA.V.sub.C across the capacitor C needs to be reduced in a quick manner, the controller 320 generates the control signal as a high logic voltage (e.g., Vdd) to turn on the second switching device M2 to discharge the capacitor C and reduce the voltage .DELTA.V.sub.C across the capacitor C to a desired level.

[0046] However, the controller 320 may not turn on the second switching device M2 if the supply voltage V.sub.S is lower than the output voltage V.sub.A of the linear amplifier 330. In other words, the voltage .DELTA.V.sub.C across the capacitor C should be equal to or greater than zero (0) as a condition for the controller 320 to turn on the second switching device M2. This condition is summarized below in equation form:

.DELTA.V.sub.C=V.sub.S-V.sub.A, wherein .DELTA.V.sub.C.gtoreq.0

[0047] FIG. 4 illustrates a flow diagram of an exemplary method 400 of generating a supply voltage for a load in accordance with another aspect of the disclosure.

[0048] The method 400 includes sourcing or sinking current to or from a voltage rail for a load (e.g., a power amplifier) via a first current path including a capacitor to control a supply voltage on the voltage rail (block 410). An example of means for sourcing or sinking current to or from a voltage rail for a load via a first current path including a capacitor to control a supply voltage on the voltage rail includes the amplifier 330 described herein. The first current path includes the amplifier 330, the capacitor C, and the upper voltage rail for the power amplifier (PA) 310.

[0049] The method 400 further includes selectively sinking current from the voltage rail for the load via a second current path including the capacitor to further control the supply voltage on the voltage rail, wherein the second current path is different than the first current path (block 420). An example of means for selectively sinking current from the voltage rail for the load via a second current path including the capacitor to further control the supply voltage on the voltage rail, wherein the second current path is different than the first current path includes switching device M1 described herein. The second current path includes the switching device M1, the capacitor C, and the upper voltage rail for the power amplifier (PA) 310.

[0050] FIG. 5 illustrates a flow diagram of another exemplary method 500 of generating a supply voltage for a load in accordance with another aspect of the disclosure.

[0051] The method 500 includes sourcing or sinking current to or from a voltage rail for a load (e.g., a power amplifier) via a first current path including a capacitor to control a supply voltage on the voltage rail (block 510). An example of means for sourcing or sinking current to or from a voltage rail for a load via a first current path including a capacitor to control a supply voltage on the voltage rail includes amplifier 330 described herein. The first current path includes the amplifier 330, the capacitor C, and the upper voltage rail for the power amplifier (PA) 310.

[0052] The method 500 further includes selectively discharging the capacitor via a second current path different than the first current path (block 520). An example of means for selectively discharging the capacitor via a second current path different than the first current path includes switching device M2 described herein. The second current path includes the capacitor C, the second switching device M2, and the lower voltage rail Vss.

[0053] The previous description of the disclosure is provided to enable any person skilled in the art to make or use the disclosure. Various modifications to the disclosure will be readily apparent to those skilled in the art, and the generic principles defined herein may be applied to other variations without departing from the spirit or scope of the disclosure. Thus, the disclosure is not intended to be limited to the examples described herein but is to be accorded the widest scope consistent with the principles and novel features disclosed herein.

* * * * *

D00000

D00001

D00002

D00003

D00004

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.