Control Of Current Collapse In Thin Patterned Gan

Gallagher; William J. ; et al.

U.S. patent application number 16/219300 was filed with the patent office on 2020-01-23 for control of current collapse in thin patterned gan. The applicant listed for this patent is International Business Machines Corporation, Massachusetts Institute of Technology. Invention is credited to William J. Gallagher, Marinus Johannes Petrus Hopstaken, Ko-Tao Lee, Tomas Palacios, Daniel Piedra, Devendra K. Sadana.

| Application Number | 20200027745 16/219300 |

| Document ID | / |

| Family ID | 56553343 |

| Filed Date | 2020-01-23 |

| United States Patent Application | 20200027745 |

| Kind Code | A1 |

| Gallagher; William J. ; et al. | January 23, 2020 |

CONTROL OF CURRENT COLLAPSE IN THIN PATTERNED GAN

Abstract

A GaN device is formed on a semiconductor substrate having a plurality of recessed regions formed in a surface thereof. A seed layer, optional buffer layer, and gallium nitride layer such as a carbon-doped gallium nitride layer are successively deposited within the recessed regions. Improved current collapse response of the GaN device is attributed to maximum length and width dimensions of the multilayer stack.

| Inventors: | Gallagher; William J.; (Ardsley, NY) ; Hopstaken; Marinus Johannes Petrus; (Carmel, NY) ; Lee; Ko-Tao; (Yorktown Heights, NY) ; Palacios; Tomas; (Belmont, MA) ; Piedra; Daniel; (Cambridge, MA) ; Sadana; Devendra K.; (Pleasantville, NY) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 56553343 | ||||||||||

| Appl. No.: | 16/219300 | ||||||||||

| Filed: | December 13, 2018 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 15001957 | Jan 20, 2016 | 10217641 | ||

| 16219300 | ||||

| 62105498 | Jan 20, 2015 | |||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 21/0254 20130101; H01L 21/30612 20130101; H01L 21/0262 20130101; H01L 29/2003 20130101; H01L 21/02579 20130101; H01L 29/778 20130101; H01L 29/1075 20130101; H01L 29/207 20130101; H01L 21/02458 20130101 |

| International Class: | H01L 21/306 20060101 H01L021/306; H01L 21/02 20060101 H01L021/02 |

Goverment Interests

GOVERNMENT RIGHTS

[0001] This invention was made with government support under contract no. N00014-13-C-0167, awarded by the Office of Naval Research. The government has certain rights in the invention.

Claims

1. A method of improving current collapse in a gallium nitride high electron mobility transistor, comprising: forming a recessed region in a surface of a substrate comprising a semiconductor material, wherein the recessed region exposes a first vertical sidewall of the substrate, a second vertical sidewall of the substrate, and a horizontal surface of the semiconductor material of the substrate; forming a seed layer within the recessed region and directly on the horizontal surface of the semiconductor material of the substrate, wherein the seed layer extends continuously from the first vertical sidewall to the second vertical sidewall; and forming a layered structure over the seed layer, the layered structure comprising at least a gallium nitride layer, wherein the gallium nitride layer is formed directly on the seed layer and extends continuously from, and is in direct contact with, the first vertical sidewall and the second vertical sidewall.

2. The method of claim 1, wherein the layered structure has a thickness of at least 0.5 microns, a length of 1 to 200 microns, and a width of 1 to 200 microns.

3. The method of claim 2, wherein the layered structure has a length of 10 to 50 microns and a width of 10 to 50 microns.

4. The method of claim 2, wherein the layered structure has a thickness of at least 1 micron.

5. The method of claim 4, wherein the layered structure has a thickness of 0.5 to 2.5 microns.

6. The method of claim 1, wherein the recessed region is formed by etching the semiconductor material.

7. The method of claim 1, wherein the recessed region has a depth of 0.6 to 3.5 microns, a length of 1 to 200 microns, and a width of 1 to 200 microns.

8.-9. (canceled)

10. The method of claim 1, wherein the seed layer and the gallium nitride layer have outermost sidewalls that are vertically aligned to each other.

11. (canceled)

12. A method of improving current collapse in a gallium nitride high electron mobility transistor, comprising: forming a recessed region in a surface of a substrate comprising a semiconductor material, wherein the recessed region exposes a first vertical sidewall of the substrate, a second vertical sidewall of the substrate, and a horizontal surface of the semiconductor material of the substrate; forming a seed layer within the recessed region and directly on the horizontal surface of the semiconductor material of the substrate, wherein the seed layer extends continuously from the first vertical sidewall to the second vertical sidewalk, and forming a layered structure over the seed layer, the layered structure comprising at least a gallium nitride layer and a buffer layer, wherein the buffer layer is located directly on the seed layer and extends continuously from, and is in direct contact with, the first vertical sidewall and the second vertical sidewall, and the gallium nitride layer is located directly on the buffer layer and extends continuously from, and is in direct contact with, the first vertical sidewall and the second vertical sidewall.

13. The method of claim 12, wherein the seed layer, the buffer layer and the gallium nitride layer have outermost sidewalls that are vertically aligned to each other.

14. The method of claim 12, wherein the buffer layer is composed of AlGaN and the gallium nitride layer is composed of carbon doped GaN.

15. The method of claim 1, wherein the first and second vertical sidewalls include a dielectric material and a topmost semiconductor layer that are located above the semiconductor material of the substrate.

16. The method of claim 1, wherein the forming of the seed layer comprises a selective deposition process.

17. The method of claim 1, wherein the forming of the layered structure comprise a selective deposition process.

18. The method of claim 2, wherein the layered structure has a current collapse of less than 10%.

19.-20. (canceled)

Description

BACKGROUND

[0002] The present application relates generally to semiconductor devices and methods of manufacture, and more specifically to gallium nitride-based devices.

[0003] Gallium nitride (GaN) possesses fundamental materials properties that make it an attractive candidate for semiconductor device fabrication. These properties include a large bandgap (.about.3.4 eV), which enables high temperature operation, a direct bandgap for fabricating light emitting diodes, the ability to form heterostructures with aluminum and indium, and high saturation velocity and breakdown field strength.

[0004] Though significant advances have been made in the development of GaN-based optoelectronic devices, including devices suitable for high power, high frequency and/or high temperature applications, a limitation to improving device efficiency is the presence of various deep traps within GaN, especially traps responsible for a current collapse phenomena in GaN metal-semiconductor field effect transistors. Current collapse occurs when the GaN on-resistance increases and current decreases during the application of high voltage to the device.

[0005] In view of the foregoing, it would be advantageous to develop structures and related methods of manufacture that minimize the impact of current collapse in GaN-based devices.

SUMMARY

[0006] In accordance with embodiments of the present application, a gallium nitride device is formed on a semiconductor substrate having a plurality of recessed regions formed in a surface thereof. A seed layer, optional buffer layer, and doped gallium nitride layer are successively deposited within the recessed regions. Improved current collapse response of the GaN device is attributed to maximum length and width dimensions of the aforementioned multilayer stack. In embodiments, the layered structure of the optional buffer layer and the doped gallium nitride layer has a thickness of at least 0.5 microns, a length of 1 to 200 microns, and a width of 1 to 200 microns. The device may comprise a gallium nitride high electron mobility transistor.

[0007] A method of forming such a gallium nitride device, which in embodiments exhibits improved current collapse, includes forming a recessed region in a surface of a semiconductor substrate, forming a seed layer within the recessed region directly over the semiconductor material, and forming a layered structure over the seed layer, the layered structure including a buffer layer and a doped gallium nitride layer.

BRIEF DESCRIPTION OF SEVERAL VIEWS OF THE DRAWINGS

[0008] The following detailed description of specific embodiments of the present application can be best understood when read in conjunction with the following drawings, where like structure is indicated with like reference numerals and in which:

[0009] FIG. 1 is a simplified cross-sectional schematic of a high electron mobility transistor (HEMT) structure;

[0010] FIGS. 2A and 2B are cross-sectional schematics showing recessed GaN structures according to various embodiments;

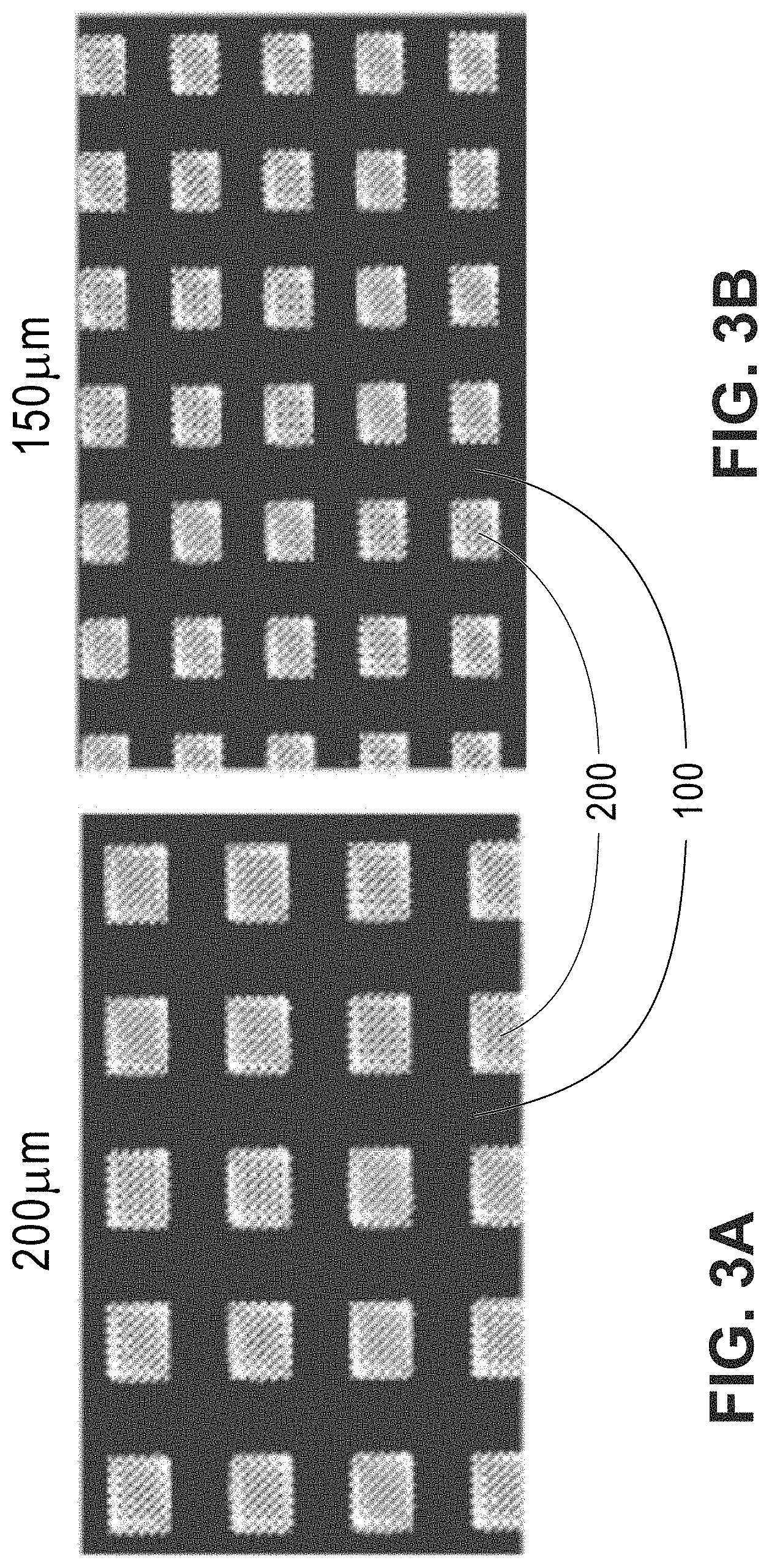

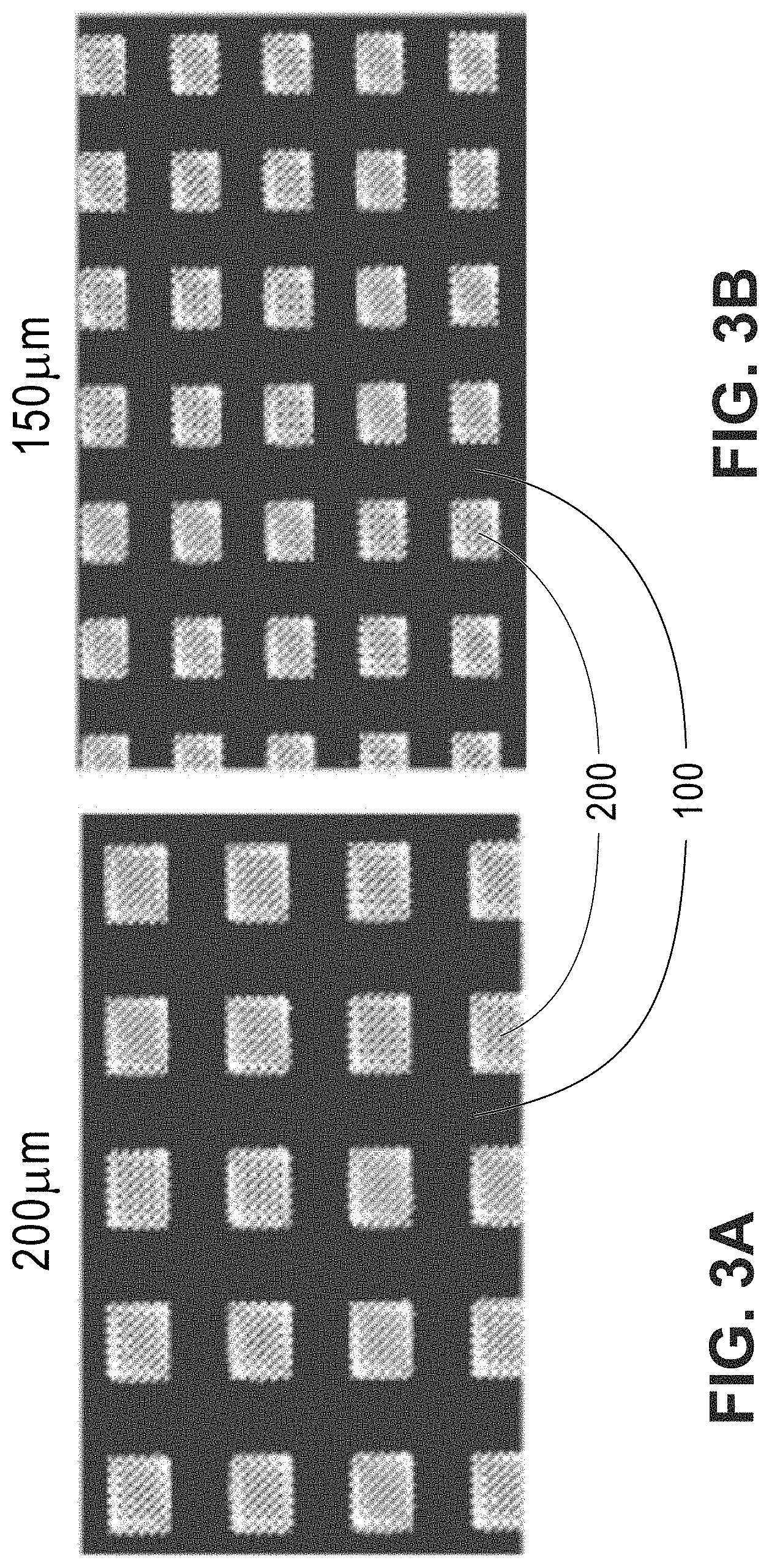

[0011] FIGS. 3A and 3B show top-down plan view optical micrographs of carbon-doped GaN structures grown on hybrid SOI substrates according to various embodiments;

[0012] FIG. 4 is a top-down plan view SEM micrograph of the GaN structure of FIG. 3;

[0013] FIG. 5 is a cross-sectional SEM micrograph showing a HEMT structure including an aluminum nitride seed layer, aluminum gallium nitride buffer layer, and a carbon-doped GaN layer formed on a hybrid SOI substrate;

[0014] FIG. 6 is a cross-sectional TEM micrograph of the HEMT structure of FIG. 5;

[0015] FIG. 7 is a plot of drain current versus source-drain voltage for patterned GaN HEMTs according to various embodiments;

[0016] FIG. 8 is a plot of drain current versus source-drain voltage for a blanket carbon-doped GaN HEMT having a GaN layer thickness of 1 micron;

[0017] FIG. 9 is a graphic showing drain current for 200 micron.times.200 micron carbon-doped GaN HEMTs having a GaN layer thickness of 1 micron;

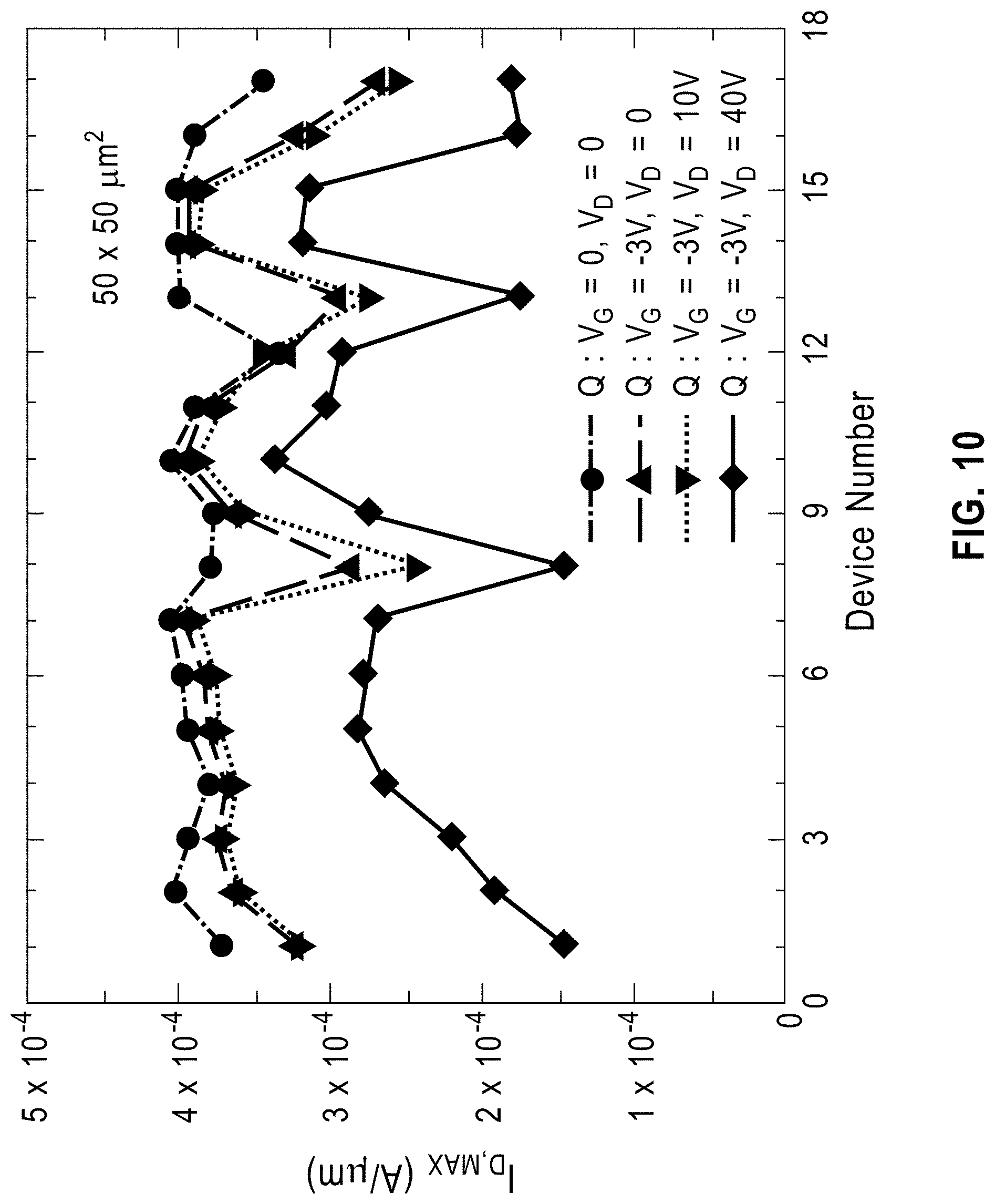

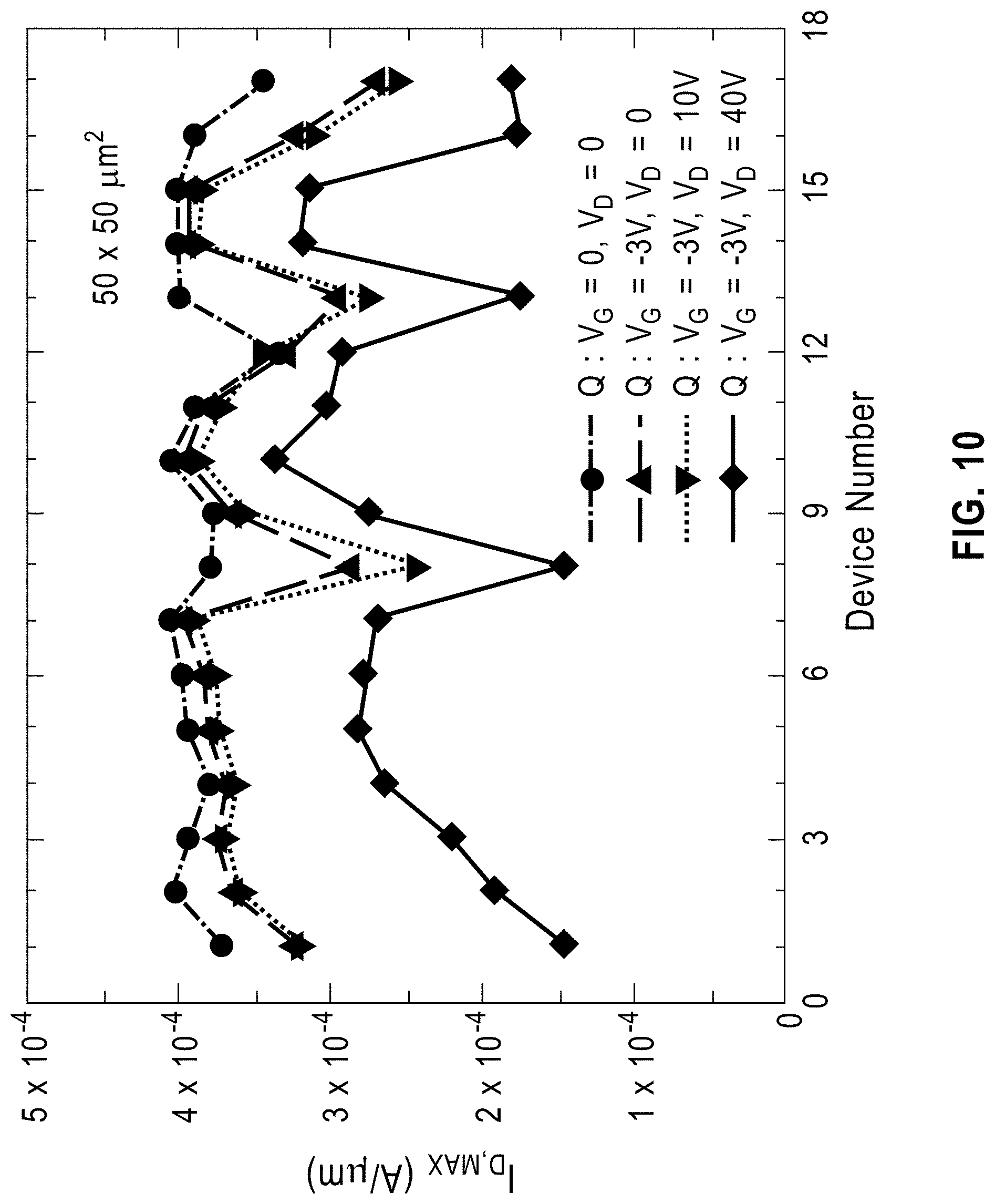

[0018] FIG. 10 is a graphic showing drain current for 50 micron.times.50 micron carbon-doped GaN HEMTs having a GaN layer thickness of 1.2 to 1.4 micron; and

[0019] FIG. 11 is a series of micro Raman plots for patterned carbon-doped GaN structures showing no measureable variation in GaN-related peak position as a function of pattern size.

DETAILED DESCRIPTION

[0020] Reference will now be made in greater detail to various embodiments of the subject matter of the present application, some embodiments of which are illustrated in the accompanying drawings. The same reference numerals will be used throughout the drawings to refer to the same or similar parts.

[0021] Heterojunction field effect transistors (FETs), also known as high electron mobility transistors (HEMTs), have as a channel a junction between two materials with different band gaps instead of a doped region as in the case of conventional metal oxide semiconductor field effect transistors (MOSFETs). Gallium nitride HEMTs have attracted attention due to their high-power performance. HEMT transistors are able to operate at higher frequencies than traditional transistors, up to millimeter wave frequencies, and can be used in high-frequency products such as cell phones, satellite television receivers, voltage converters, and RADAR equipment.

[0022] Compared to silicon devices, GaN devices exhibit lower power losses and higher energy efficiency. Widespread implementation of conventional GaN heterojunction FETs (HFETs) has been dampened, however, due to a current collapse phenomenon where current decreases and on-resistance increases during operation.

[0023] Current collapse is a phenomenon observed in GaN-based transistors where the device current measured at a non-zero drain-source voltage (V.sub.ds) and gate voltage (V.sub.g) under certain pulsed conditions is less than the current measured at the same drain and gate voltage under DC conditions, or pulsed conditions where no stress is applied, i.e., V.sub.ds=0V and V.sub.g=0V.

[0024] When reference is made herein to current collapse or a relative current collapse, the DARPA milestone metric was used (quiescent operating point of V.sub.ds=10V and V.sub.g=-3V with a pulse width of 500 ns).

[0025] Pronounced current collapse (40% or greater) has been observed in comparative carbon-doped GaN HEMTs when a blanket GaN layer thickness is less than 2 microns (e.g., less than 1.2 microns). As shown herein, current collapse can be reduced to less than 10% for patterned GaN HEMT structures having a gallium nitride thickness of 2 microns or less, e.g., 0.5, 0.6, 0.7, 0.8, 0.9, 1, 1.2, 1.5 or 2 microns, including ranges between any of the foregoing values.

[0026] In addition to current collapse under an applied bias, a large mismatch in the coefficient of thermal expansion (CTE) between gallium nitride and many substrate materials including silicon, silicon carbide, and sapphire may lead to crack formation in the deposited gallium nitride layer and/or unacceptable bow or warp of the substrate when the deposited structure is cooled, for example, during processing.

[0027] As used herein, `bow` and `warp` are complimentary measures of the flatness of a wafer or semiconductor substrate. For a wafer having a median surface defined as the locus of points in the wafer equidistant between the front and back surfaces, wafer bow is equal to the deviation of the center point of the median surface of a free, unclamped wafer from the median surface reference plane established by three points equally spaced on a circle with a diameter a specified amount less than the nominal diameter of the wafer (ASTM F534).

[0028] When measuring and calculating bow, the location median surface of the wafer must be known. By measuring deviations of the median surface, localized thickness variations at the center point of the wafer are removed from the calculation.

[0029] Because bow is measured at the center point of the wafer only, a three (3) point reference plane about the edge of the wafer is calculated. The value of bow is then calculated by measuring the location of the median surface at the center of the wafer and determining its distance from the reference plane. Bow can be positive or negative. A positive value indicates that the center point of the median surface is above the three point reference plane, while a negative value indicates that the center point of the median surface is below the three point reference plane.

[0030] Like bow, warp is a measurement of the differentiation between the median surface of a wafer and a reference plane. Warp, however, uses the entire median surface of the wafer instead of only the position at the center point. By looking at the entire wafer, warp provides a measurement of true wafer shape. Warp is defined as the differences between the maximum and minimum distances of the median surface of a free, unclamped wafer from a reference place (ASTM F1390).

[0031] The location of the median surface is calculated as it is for bow. For warp determination, there are typically two choices for construction of the reference plane. One is the same three point plane around the edge of the wafer. The other is by performing a least squares fit calculation of median surface data acquired during the measurement scan. Warp is then calculated by finding the maximum deviation from the reference plane (RPD.sub.max) and the minimum differentiation from the reference plane (RPD.sub.min). RPD.sub.max is defined as the largest distance above the reference plane and is a positive number. RPD.sub.min is the largest distance below the reference plane and is a negative number. Warp is equal to RPD.sub.max-RPD.sub.min. In embodiments, the deposited gallium nitride layer(s) induce a bow in the substrate of less than 500 microns, e.g., less than 500, 200 or 100 microns.

[0032] Cracking can be particularly problematic for gallium nitride layer thicknesses greater than 0.5 micron. Also, gallium nitride also has a different lattice constant than many substrate materials, which may lead to the formation of defects in gallium nitride layers that ultimately impair device performance.

[0033] Disclosed are structures and related methods of manufacture that facilitate the integration of gallium nitride with substrate materials such as silicon, improve the mechanical robustness of the integrated architectures, and minimize the phenomenon of current collapse in GaN-based devices, including HEMTs.

[0034] Unless the context clearly dictates otherwise, the term "gallium nitride" refers to gallium nitride (GaN) and any of its alloys, such as aluminum gallium nitride (Al.sub.xGa.sub.1-xN), indium gallium nitride (In.sub.yGa.sub.1-yN), aluminum indium gallium nitride (Al.sub.xIn.sub.yGa.sub.1-x-yN), etc. Further, gallium nitride may be doped, for example, with up to 6 percent by weight of carbon, magnesium, silicon, germanium, arsenic and/or phosphorus.

[0035] A schematic cross-section of a portion of a GaN-HEMT stack architecture is shown in FIG. 1. Hetero-epitaxial layers, which include from bottom to top, a seed layer 210 such as an AlN layer, a gallium nitride buffer layer 220 such as an AlGaN layer, and a doped gallium nitride layer 230 such as a carbon-doped GaN layer, can be grown by metal organic chemical vapor deposition (MOCVD) on a semiconductor substrate 100. Layers 210, 220 and 230 are collective referred to as GaN-HEMT stack 200.

[0036] Substrate 100 may be a semiconductor material such as silicon or a silicon-containing material, including a bulk substrate. Silicon-containing materials include, but are not limited to, single crystal Si, polycrystalline Si, single crystal silicon germanium (SiGe), polycrystalline silicon germanium, silicon doped with carbon (Si:C), amorphous Si, as well as combinations and multi-layers thereof. Example silicon substrates include silicon-on-insulator (SOI) substrates, silicon-on-sapphire (SOS) substrates, separation by implanted oxygen (SIMOX) substrates, and the like. As used herein, the term "single crystal" denotes a crystalline solid, in which the crystal lattice of the entire sample is substantially continuous and substantially unbroken to the edges of the sample with substantially no grain boundaries. In embodiments, substrate 100 can comprise (100) oriented silicon or (111) oriented silicon, for example.

[0037] Substrate 100 is not limited to silicon-containing materials, as the substrate 100 may comprise other semiconductor materials, including Ge and compound semiconductors such as GaAs, InAs and other like semiconductors.

[0038] The transistor structure depicted in FIG. 1 is formed on a semiconductor-on-insulator (SOI) substrate 100. The SOI structure includes, from top to bottom, a top semiconductor layer 130, an intermediate buried oxide (BOX) layer 120, and a bottom supporting substrate 110.

[0039] The substrate 100 may have dimensions as typically used in the art. Example substrate diameters include, but are not limited to, 50, 100, 150, 200, 300 and 450 mm. The total substrate thickness may range from 250 microns to 1500 microns, though in particular embodiments the substrate thickness is in the range of 725 to 775 microns, which corresponds to thickness dimensions commonly used in silicon CMOS processing.

[0040] The thickness of the top semiconductor layer 130 may range from 40 to 150 nm, e.g., 40, 100 or 150 nm, including ranges between any of the foregoing values. The top semiconductor layer 130 may comprise single crystal silicon (Si) such as (100)-oriented silicon. The thickness of the buried oxide layer 120 may range from 30 to 300 nm, e.g., 30, 50, 100, 150, 200, 250 or 300 nm, including ranges between any of the foregoing values. The buried oxide layer 120 may comprise, for example, silicon oxide (SiO.sub.2). The supporting substrate 110 may comprise (100)-oriented silicon or (111)-oriented silicon, for example.

[0041] According to exemplary methods, gallium nitride layers 220, 230 may be grown as epitaxial layers using a metalorganic chemical vapor deposition (MOCVD) process. It will be appreciated, however, that other techniques known in the art may be used to deposit the gallium nitride layers including molecular beam epitaxy (MBE), hydride vapor phase epitaxy (HVPE), and the like.

[0042] The MOCVD process involves introducing different source gases into an environment (e.g., a process chamber) proximate to a substrate and providing conditions that support a reaction between the gases to form a layer on the substrate surface. The reaction proceeds until a layer of desired thickness is achieved. Characteristics of the deposited layer may be controlled by various parameters including gas composition and concentration, and the reaction conditions such as substrate temperature and chamber pressure. In embodiments, the surface of the substrate onto which a gallium nitride layer is deposited comprises a semiconductor material.

[0043] Examples of suitable source gases for the MOCVD growth of gallium nitride include trimethylgallium (TMG) or triethylgallium (TEG) as sources of gallium; ammonia (NH.sub.3) as a source of nitrogen; CBr.sub.4 or CCl.sub.4 as sources of carbon; trimethylaluminum (TMA) or triethylaluminum (TEA) as sources of aluminum; and trimethylindium (TMI) or triethylindium (TEI) as sources of indium. The particular combination of source gases used depends, for example, upon the desired composition of the deposited layer. For example, an aluminum source (e.g., TMA or TEA), a gallium source (TMG or TEG), together with a nitrogen source may be used to deposit films having an Al.sub.xGa.sub.1-xN composition.

[0044] The flow rates and relative ratios of the source gases may be controlled to provide gallium nitride layers having the desired composition. For the growth of Al.sub.xGa.sub.1-xN layers, typical TMA flow rates are between 20 sccm and 100 sccm; typical TMG flow rates are between 20 sccm and 100 sccm; and the flow rate of ammonia is typically between 2 slm and 10 slm. The substrate temperature may range from 900.degree. C. to 1200.degree. C. and the chamber pressure may range from 1 torr to 760 torr, e.g., 10 torr to 100 torr. In embodiments, the process parameters are maintained constant so as to provide respective layers having a constant composition.

[0045] The terms "epitaxy," "epitaxial" and/or "epitaxial growth and/or deposition" refer to the growth of a semiconductor material layer on a deposition surface of a semiconductor material, in which the semiconductor material layer being grown assumes the same crystalline habit as the semiconductor material of the deposition surface. For example, in an epitaxial deposition process, chemical reactants provided by source gases are controlled and the system parameters are set so that depositing atoms alight on the deposition surface and remain sufficiently mobile via surface diffusion to orient themselves according to the crystalline orientation of the atoms of the deposition surface. Therefore, an epitaxial semiconductor material has the same crystalline characteristics as the deposition surface on which it is formed. For example, an epitaxial semiconductor material deposited on a (100) crystal surface will take on a (100) orientation.

[0046] The epitaxial layers and/or the substrate may be doped. Doping changes the electron and hole carrier concentrations of an intrinsic semiconductor at thermal equilibrium. A doped layer or region may be p-type or n-type.

[0047] As used herein, "p-type" refers to the addition of impurities to an intrinsic semiconductor that creates a deficiency of valence electrons. For gallium nitride, an example p-type dopant, i.e., impurity, is magnesium. As used herein, "n-type" refers to the addition of impurities that contribute free electrons to an intrinsic semiconductor. For gallium nitride, example n-type dopants, i.e., impurities, include but are not limited to, carbon, silicon and germanium. The dopant(s) may be introduced by ion implantation or may be introduced, for example, in situ, i.e., during a process sequence used to form the layer.

[0048] By way of example, carbon may be implanted into a gallium nitride layer such as gallium nitride layer 230 to form an n-type layer. Alternatively, a carbon source may be incorporated into the gas phase chemistry used to deposit the gallium nitride layer. The dopant concentration may range from 1.times.10.sup.18 atoms/cm.sup.3 to 5.times.10.sup.21 atoms/cm.sup.3, e.g., 5.times.10.sup.19 atoms/cm.sup.3 to 1.times.10.sup.21 atoms/cm.sup.3.

[0049] As shown in FIGS. 2A and 2B, according to various embodiments, device layers including AlN seed layer 210, AlGaN layer 220 and GaN layer 230 (collectively GaN-HEMT stack 200) are successively deposited within recessed regions formed in the substrate. To form recessed regions, a photoresist layer (not shown) can be applied over the substrate 100, and can be lithographically patterned to form openings in the photoresist layer that correspond to the areas of one or more recessed regions to be subsequently formed using, for example, an anisotropic etch. A recessed region can be formed for each opening in the photoresist layer. Recessed regions are formed by etching through each of the top semiconductor layer 130 and the intermediate buried oxide (BOX) layer 120, and optionally into the supporting substrate 110. In embodiments where recessed region-defining etch extends into the supporting substrate 110, at least a portion of the sidewalls of the recessed region will comprise a semiconductor material. The photoresist can be removed by ashing, or can be consumed during the etch process that forms one or more recessed regions. In further embodiments, prior to depositing the GaN-HEMT stack materials into the recessed region, a layer of dielectric material such as silicon nitride can be deposited onto the recessed region sidewalls. In an example process, a conformal dielectric layer can be deposited over exposed surfaces of the substrate, including within the recessed region, followed by an anisotropic etch of the dielectric layer that removes the dielectric layer from horizontal surfaces.

[0050] The recessed regions may have a prismatic shape, such as a square or rectangular prism having a length and width measured in directions parallel to a major surface of the substrate, and a depth measured in a direction normal to a major surface of the substrate 100.

[0051] The depth of each recessed region, as measured from the topmost surface of the substrate 100 to the bottom surface of the recessed region, can be from 0.9 to 2.5 microns, although lesser and greater depths are contemplated. The length and width dimensions of the recessed regions may independently range from 1 to 200 microns, e.g., 1, 2, 5, 10, 20, 50, 100, 150 or 200 microns.

[0052] Deposition of the device layers into the recessed regions can be selective such that seed layer 210, for example, is deposited only on an exposed surface of the supporting substrate 110 and not on the buried oxide layer 120 or the top semiconductor layer 130, and each successive gallium nitride layer 220, 230 is deposited only on the previously-deposited device layer.

[0053] With reference still to FIGS. 2A and 2B, seed layer 210, such as an AlN seed layer, is formed directly over a semiconductor layer such as supporting substrate 110. The thickness of seed layer 210 may range from 50 to 500 nm, though lesser and greater thicknesses may be used. In addition to or in lieu of AlN, the seed layer 210 may comprise, for example, GaN.

[0054] Formed directly over seed layer 210 is an optional buffer layer 220. An example buffer layer 220 comprises a Group III metal nitride. The buffer layer 220 may be deposited to a thickness of up to 1000 nm, e.g., 0, 100, 200, 500 or 1000 nm, including ranges between any of the foregoing values. The Group III metal nitride may be a compound including or more metal selected from Ga, Al and In, and may comprise, for example, GaN, AlN, AlGaN, InGaN, InAlN, InAlGaN or the like. The buffer layer 220 may contain intentional or unintended impurities. For example, the buffer layer may include one or more dopants including Si, Ge, Be, Mg, Zn, Cd or the like.

[0055] Formed directly over the buffer layer 220, if provided, or directly over the seed layer 210 is a gallium nitride layer 230. The gallium nitride layer 230 may be doped. For example, in embodiments the gallium nitride layer 230 comprises carbon-doped GaN. The thickness of the gallium nitride layer may range from 500 to 1500 nm, e.g., 500, 800, 1000, 1200, 1400 or 1500 nm, including ranges between any of the foregoing values.

[0056] In embodiments, both the composition and the thickness of the seed layer 210, the optional buffer layer 220, and the gallium nitride layer 230 may be selected independently. In embodiments, the layered structure comprising the gallium nitride layer 230, buffer layer 220 and seed layer 210 has a thickness of at least 1 micron.

[0057] The structures described herein may be disposed as a pattern that is periodic at least in one dimension, where the length and width (and the depth) of the recessed regions are constant over the substrate, and the succession of the stack architecture in one or more directions is periodic, which enables the formation of a transistor array of minimal area. The areal dimensions of the stacks with the recessed regions and their interspaces are thus continually repeated in one or more (e.g., orthogonal) directions of periodic succession. The length of one of these periods is called the pitch of the pattern.

[0058] Within the recessed regions, the layered structure 200 may have a length dimension of 1 to 200 microns (e.g., 1, 2, 5, 10, 50, 100 or 200 microns, including ranges between any of the foregoing values) and a width dimension of 1 to 200 microns (e.g., 1, 2, 5, 10, 50, 100 or 200 microns, including ranges between any of the foregoing values). Limiting the areal dimensions of the layered structure minimizes the propensity for cracking within the deposited layers.

[0059] In embodiments, the spacing between adjacent patterned regions may range from 50 to 200 microns, e.g., 50, 100, 150 or 200 microns, and may be less than, equal to, or greater than the length and width dimensions of the patterned region. The areal density of the patterned region may range from 25% to 50%.

[0060] FIGS. 3A and 3B are top-down, plan view optical micrographs of carbon-doped GaN structures grown on hybrid SOI substrates. The structures in FIG. 3A have length and width dimensions of 200 microns. The structures in FIG. 3B have length and width dimensions of 150 microns. FIG. 4 is a top-down plan view scanning electron microscope (SEM) micrograph of the GaN structure of FIGS. 3A-3B.

[0061] FIG. 5 is a cross-sectional SEM micrograph showing a HEMT structure including an aluminum nitride seed layer, aluminum gallium nitride buffer layer, and a carbon-doped GaN layer formed within a recessed region that extends into the bottom supporting substrate 110 of a hybrid SOI substrate. FIG. 6 is a cross-sectional transmission electron microscope (TEM) micrograph of the HEMT structure of FIG. 5.

[0062] FIG. 7 is a plot of drain current versus source-drain voltage for patterned GaN HEMTs having various areal dimensions.

[0063] FIG. 8 is a plot of drain current versus source-drain voltage exemplifying current collapse for a blanket carbon-doped GaN HEMT having a GaN layer thickness of 1 micron.

[0064] The upper trace is pulsed in a non-stressed manner. The quiescent point for the upper trace is Vg=0, Vds=0. The lower trace is pulsed in a stressed manner. The quiescent point for the lower trace is Vg=-3V, Vds=40V. For a given bias, the current is lower for the device pulsed to off-state conditions.

[0065] FIGS. 9 and 10 are plots of maximum drain current under different stress states for different GaN HEMT devices formed from gallium nitride patterns measuring 200 micron.times.200 micron and having a GaN layer thickness of 1 micron (FIG. 9), and 50 micron.times.50 micron and having a GaN layer thickness of 1.2 to 1.4 micron (FIG. 10). Current collapse can be calculated as the difference in maximum current between a non-stressed pulsed condition (quiescent point: V.sub.g=0, V.sub.ds=0) and a stressed pulsed condition (quiescent point: V.sub.g=-3V, V.sub.ds=10V).

[0066] With reference first to FIG. 9, the calculated current collapse is greater than 20% for a majority of the 200 micron.times.200 micron samples. Turning to FIG. 10, current collapse is dramatically improved for the 50 micron.times.50 micron samples. For a majority of the samples evaluated, the current collapse is less than 20%. In embodiments, by engineering the dimensions of the gallium nitride layers, the measured current collapse can be less than 20%, e.g., less than 15% or less than 10%.

[0067] FIG. 11 is a series of micro Raman plots for patterned carbon-doped GaN structures showing no measureable variation in GaN-related peak position as a function of pattern size.

[0068] The absence of a relative peak shift as among the GaN/Si samples (for different pattern sizes) is consistent with a conclusion that the observed changes in current collapse are not attributable to variations in the stress states of the GaN. Secondary ion mass spectrometry (SIMS) data from various patterned carbon-doped GaN windows (100 micron.times.100 micron; 150 micron.times.150 micron; and 200 micron.times.200 micron) show no measurable variation in the carbon doping as a function of pattern size.

[0069] Without wishing to be bound by theory, it is believed that the improved current collapse response is attributed to GaN stacks having maximum areal dimensions, even for a stack thickness greater than 1 micron, as compared with larger area, thinner stacks.

[0070] The GaN transistor structures disclosed herein may be incorporated into a broad range of equipment including power supplies, inverters in consumer appliances, and electric vehicles.

[0071] As used herein, the singular forms "a," "an" and "the" include plural referents unless the context clearly dictates otherwise. Thus, for example, reference to a "buffer layer" includes examples having two or more such "buffer layers" unless the context clearly indicates otherwise.

[0072] Unless otherwise expressly stated, it is in no way intended that any method set forth herein be construed as requiring that its steps be performed in a specific order. Accordingly, where a method claim does not actually recite an order to be followed by its steps or it is not otherwise specifically stated in the claims or descriptions that the steps are to be limited to a specific order, it is no way intended that any particular order be inferred. Any recited single or multiple feature or aspect in any one claim can be combined or permuted with any other recited feature or aspect in any other claim or claims.

[0073] It will be understood that when an element such as a layer, region or substrate is referred to as being formed on, deposited on, or disposed "on" or "over" another element, it can be directly on the other element or intervening elements may also be present. In contrast, when an element is referred to as being "directly on" or "directly over" another element, no intervening elements are present.

[0074] While various features, elements or steps of particular embodiments may be disclosed using the transitional phrase "comprising," it is to be understood that alternative embodiments, including those that may be described using the transitional phrases "consisting" or "consisting essentially of," are implied. Thus, for example, implied alternative embodiments to a gallium nitride layer that comprises gallium nitride (GaN) include embodiments where a gallium nitride layer consists essentially of GaN and embodiments where a gallium nitride layer consists of GaN.

[0075] It will be apparent to those skilled in the art that various modifications and variations can be made to the present invention without departing from the spirit and scope of the invention. Since modifications, combinations, sub-combinations and variations of the disclosed embodiments incorporating the spirit and substance of the invention may occur to persons skilled in the art, the invention should be construed to include everything within the scope of the appended claims and their equivalents.

* * * * *

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.