Method, Electronic Device And Computer Program Product For Data Processing

Wang; Haiyang ; et al.

U.S. patent application number 15/395228 was filed with the patent office on 2019-11-07 for method, electronic device and computer program product for data processing. The applicant listed for this patent is Lenovo (Beijing) Limited. Invention is credited to Xingzhong Mao, Haiyang Wang, Bibo Yang.

| Application Number | 20190339875 15/395228 |

| Document ID | / |

| Family ID | 56189827 |

| Filed Date | 2019-11-07 |

| United States Patent Application | 20190339875 |

| Kind Code | A9 |

| Wang; Haiyang ; et al. | November 7, 2019 |

METHOD, ELECTRONIC DEVICE AND COMPUTER PROGRAM PRODUCT FOR DATA PROCESSING

Abstract

A method, device and computer program product are disclosed. The method includes: receiving a command that reads data; parsing the command to obtain information sets; reading data based on the information sets; and sending the data and the information sets. The device includes: a memory that stores data in physical pages; and a controller that receives a command that reads data, parses the command to obtain information sets, reads data based on the information sets, and sends the data and the information sets. The computer program product includes code to: receive a command that reads data; parse the command to obtain information sets; read data based on the information sets; and send the data and the information sets.

| Inventors: | Wang; Haiyang; (Beijing, CN) ; Mao; Xingzhong; (Beijing, CN) ; Yang; Bibo; (Beijing, CN) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Prior Publication: |

|

||||||||||

| Family ID: | 56189827 | ||||||||||

| Appl. No.: | 15/395228 | ||||||||||

| Filed: | December 30, 2016 |

| Current U.S. Class: | 1/1 |

| Current CPC Class: | G06F 3/0659 20130101; G06F 3/0688 20130101; G06F 3/061 20130101; G06F 3/0608 20130101 |

| International Class: | G06F 3/06 20060101 G06F003/06 |

Foreign Application Data

| Date | Code | Application Number |

|---|---|---|

| Dec 31, 2015 | CN | 201511023587.9 |

Claims

1. A method, comprising: receiving a first command that reads data, the first command comprising one or more sets of first information and second information; parsing the first command to obtain the one or more sets of first information and second information; reading data corresponding to one or more LBA's (Logical Block Addresses) from a physical page based on the one or more sets of first information and second information; sending the data corresponding to the one or more LBAs; and sending the first information and second information.

2. The method of claim 1, wherein: the first information comprises an identification of a second command, and the second information comprises an offset of an LBA.

3. The method of claim 2, further comprising: receiving one or more second commands sent by a host; parsing each of the second commands to obtain identification and LBA offsets corresponding to each of the second commands; using the identification corresponding to the second command as first information; using the LBA offsets corresponding to the second command as second information; and writing the first and second information into the first command.

4. The method of claim 3, further comprising: receiving from the host and storing one or more third commands for writing data; selecting, from the one or more third commands, third commands meeting a predetermined condition; and writing data corresponding to the third commands meeting the predetermined condition onto the same physical page.

5. The method of claim 4, wherein: the selecting, from the one or more third commands, third commands meeting a predetermined condition comprises: parsing the one or more third commands to determine respective LBAs of the third commands; selecting one or more LBAs with distances therebetween no greater than a predetermined threshold based on the respective LBAs of the third commands; and selecting third commands corresponding to the selected one or more LBAs.

6. The method of claim 4, further comprising: determining whether the number of the stored third commands reaches a threshold value while the stored third commands do not include any third command meeting the predetermined condition; and continuously receiving and storing the third commands sent by the host until the number of the stored third commands reaches the threshold value.

7. The method of claim 6, further comprising: selecting, from the stored third commands, a third command with a minimum distance among the LBAs after the number of the stored third commands reaches the threshold value; and writing data corresponding to the selected third command onto the same physical page.

8. An electronic device, comprising: a memory that stores data in terms of physical pages; and a controller that receives a first command that reads data, the first command comprising one or more sets of first information and second information; parses the first command to obtain the one or more sets of first information and second information; reads data corresponding to one or more LBA's (Logical Block Addresses) from a physical page based on the one or more sets of first information and second information; sends the data corresponding to the one or more LBA's; and sends the first information and second information.

9. The device of claim 8, wherein: the first information comprises an identification of a second command, and the second information comprises an offset of an LBA.

10. The device of claim 9, wherein the electronic device further comprises: a processor, that receives one or more second commands sent by a host; parses each of the second commands to obtain identification and LBA offsets corresponding to each of the second commands; uses the identification corresponding to the second command as first information; uses the LBA offsets corresponding to the second command as second information; and writes the first and second information into the first command.

11. The device of claim 10, wherein the processor receives from the host one or more third commands for writing data; the processor selects, from the one or more third commands, third commands meeting a predetermined condition; and the controller writes data corresponding to the third commands meeting the predetermined condition onto the same physical page.

12. The device of claim 11, wherein the processor parses the one or more third commands to determine the respective LBAs of the third commands; selects one or more LBAs with distances therebetween no greater than a predetermined threshold according to the respective LBAs of the third commands; and selects third commands corresponding to the selected one or more LBAs.

13. The device of claim 11, wherein the processor: determines whether the number of the stored third commands reaches a threshold value while the stored third commands do not include any third command meeting the predetermined condition; and continuously receives and stores the third commands sent by the host until the number of the stored third commands reaches the threshold value.

14. The device of claim 13, wherein the processor selects, from the one or more third commands, a third command with a minimum distance among the LBAs after the number of the stored third commands reaches the threshold value; and the controller writes data corresponding to the selected third command onto the same physical page.

15. A computer program product comprising a computer readable storage medium that stores code executable by a processor, the executable code comprising code to perform: receiving a first command that reads data, the first command comprising one or more sets of first information and second information; parsing the first command to obtain the one or more sets of first information and second information; reading data corresponding to one or more LBA's (Logical Block Addresses) from a physical page based on the one or more sets of first information and second information; sending the data corresponding to the one or more LBAs; and sending the first information and second information.

16. The computer program product of claim 15, wherein: the first information comprises an identification of a second command, and the second information comprises an offset of an LBA.

17. The computer program product of claim 16, further comprising code to perform: receiving one or more second commands sent by a host; parsing each of the second commands to obtain identification and LBA offsets corresponding to each of the second commands; using the identification corresponding to the second command as first information; using LBA offsets corresponding to the second command as second information; and writing the first and second information into the first command.

18. The computer program product of claim 17, further comprising code to perform: receiving from the host and storing one or more third commands for writing data; selecting, from the one or more third commands, third commands meeting a predetermined condition; and writing data corresponding to the third commands meeting the predetermined condition onto the same physical page.

19. The computer program product of claim 18, wherein: the selecting, from the one or more third commands, third commands meeting a predetermined condition comprises: parsing the one or more third commands to determine respective LBAs of the third commands selecting one or more LBAs with distances therebetween no greater than a predetermined threshold according to the respective LBAs of the third commands; and selecting third commands corresponding to the selected one or more LBAs.

20. The computer program product of claim 18, further comprising code to perform: determining whether the number of the stored third commands reaches a threshold value while the one or more stored third commands do not include any third command meeting the predetermined condition; continuously receiving and storing the third commands sent by the host until the number of the stored third commands reaches the threshold value; selecting, from the one or more third commands, a third command with a minimum distance among the LBAs after the number of the stored third commands reaches the threshold value; and writing data corresponding to the selected third command onto the same physical page.

Description

FIELD

[0001] The present application relates to the field of data processing technologies, and more particularly to a method, electronic device and computer program product for data processing.

BACKGROUND

[0002] At present, SSDs (Solid State Drives) are becoming more popular in the consumer sector, and design of SSD controllers, especially those supporting NVMe (Non-Volatile Memory Express) protocol, have become popular.

[0003] Among current mainstream SSD controllers, 4K mapping technology is becoming more popular as well. Due to the characteristics of 4K mapping, data corresponding to a plurality of LBAs (Logical Block Addresses) may be stored on multiple physical pages.

[0004] When arranged in this way, addresses are dispersed as data written on the Nand Flash. In other words, the plurality of LBAs on one physical page are not continuous, so the same physical page may be read many times in response to different NVMe read commands when a SSD controller reads data, resulting in lower efficiency.

SUMMARY

[0005] A method, device and computer program product for data processing are disclosed.

[0006] The method includes: receiving a first command that reads data, the first command comprising one or more sets of first information and second information; parsing the first command to obtain the one or more sets of first information and second information; reading data corresponding to one or more LBA's (Logical Block Addresses) from a physical page based on the one or more sets of first information and second information; sending the data corresponding to the one or more LBAs; and sending the first information and second information.

[0007] The device includes: a memory that stores data in terms of physical pages; and a controller that receives a first command that reads data, the first command comprising one or more sets of first information and second information, parses the first command to obtain the one or more sets of first information and second information, reads data corresponding to one or more LBA's (Logical Block Addresses) from a physical page based on the one or more sets of first information and second information; sends the data corresponding to the one or more LBA's; and sends the first information and second information.

[0008] The computer program product includes code executable by a processor, the executable code comprising code to perform: receiving a first command that reads data, the first command comprising one or more sets of first information and second information; parsing the first command to obtain the one or more sets of first information and second information; reading data corresponding to one or more LBA's (Logical Block Addresses) from a physical page based on the one or more sets of first information and second information; sending the data corresponding to the one or more LBAs; and sending the first information and second information.

BRIEF DESCRIPTION OF THE DRAWINGS

[0009] To describe the disclosed technical solutions more clearly, accompanying drawings used for describing the embodiments are hereinafter briefly introduced. It is apparent that the accompanying drawings hereinafter are only intended to illustrate some embodiments of the present application.

[0010] FIG. 1 is a schematic flow diagram of one embodiment of a data processing method;

[0011] FIG. 2 is a schematic flow diagram of one embodiment of a data processing method;

[0012] FIG. 3 is an information correspondence diagram of four sets of NVMe read commands in one embodiment;

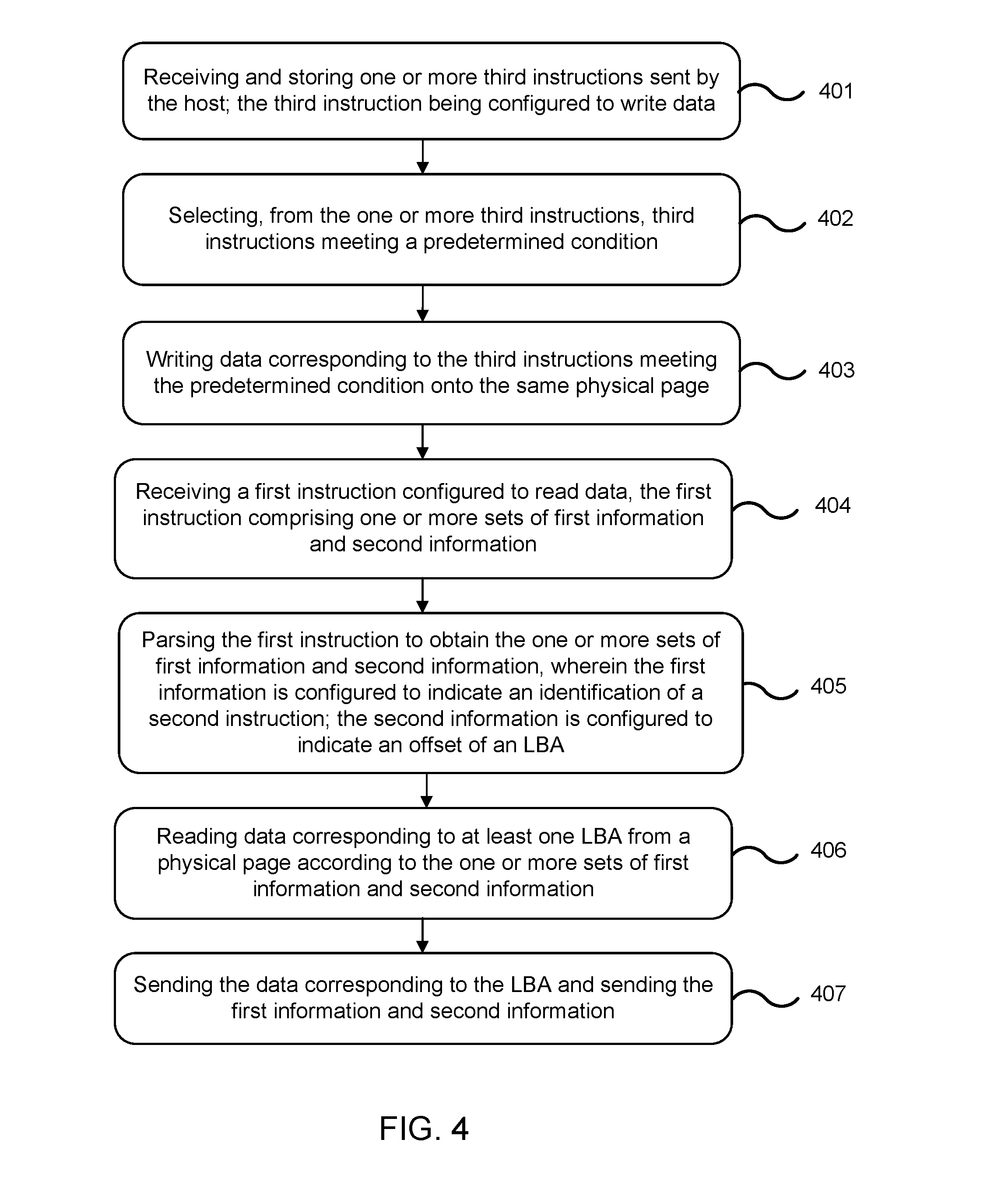

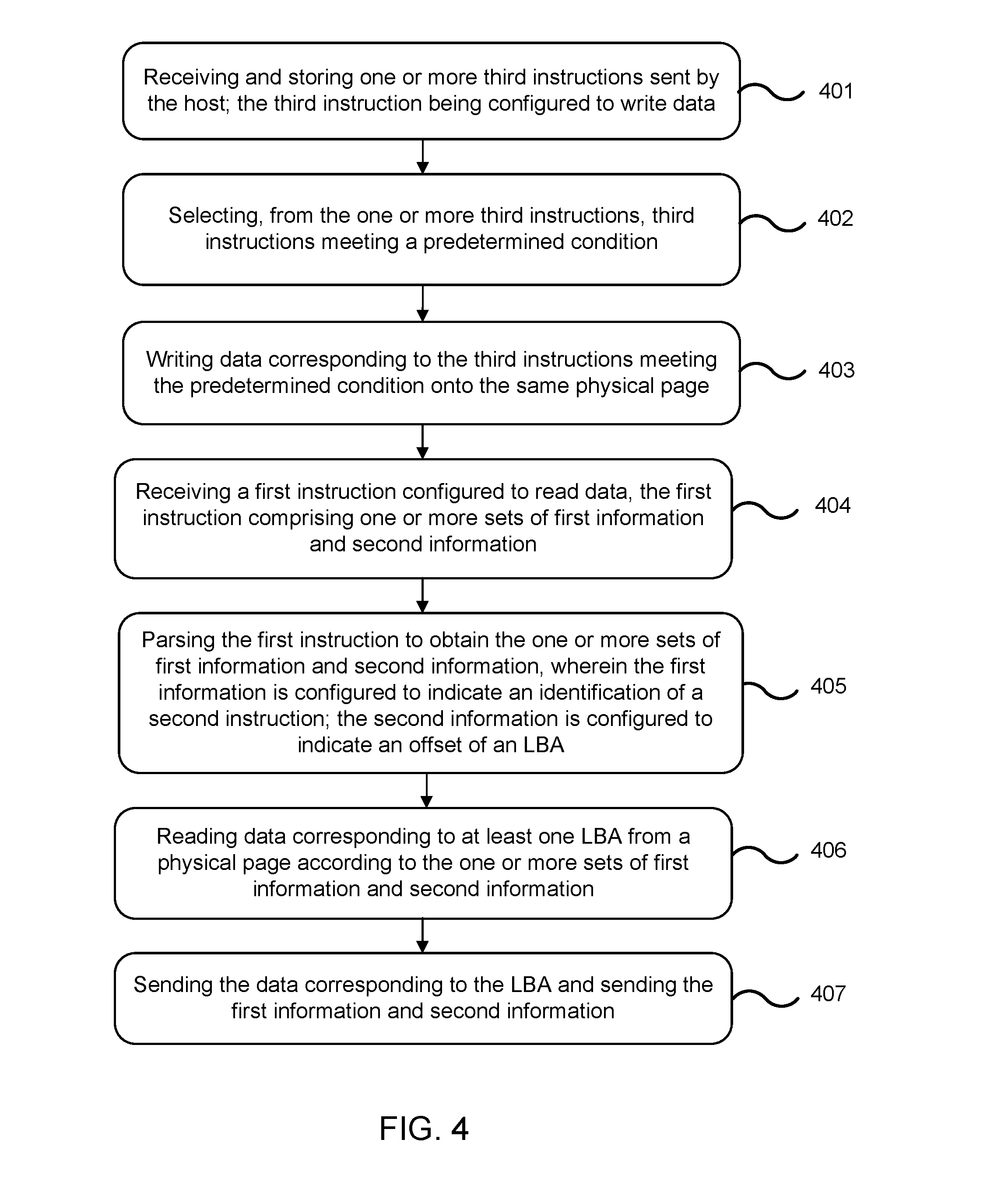

[0013] FIG. 4 is a schematic flow diagram of one embodiment of a data processing method;

[0014] FIG. 5 is a schematic flow diagram of one embodiment of a data processing method;

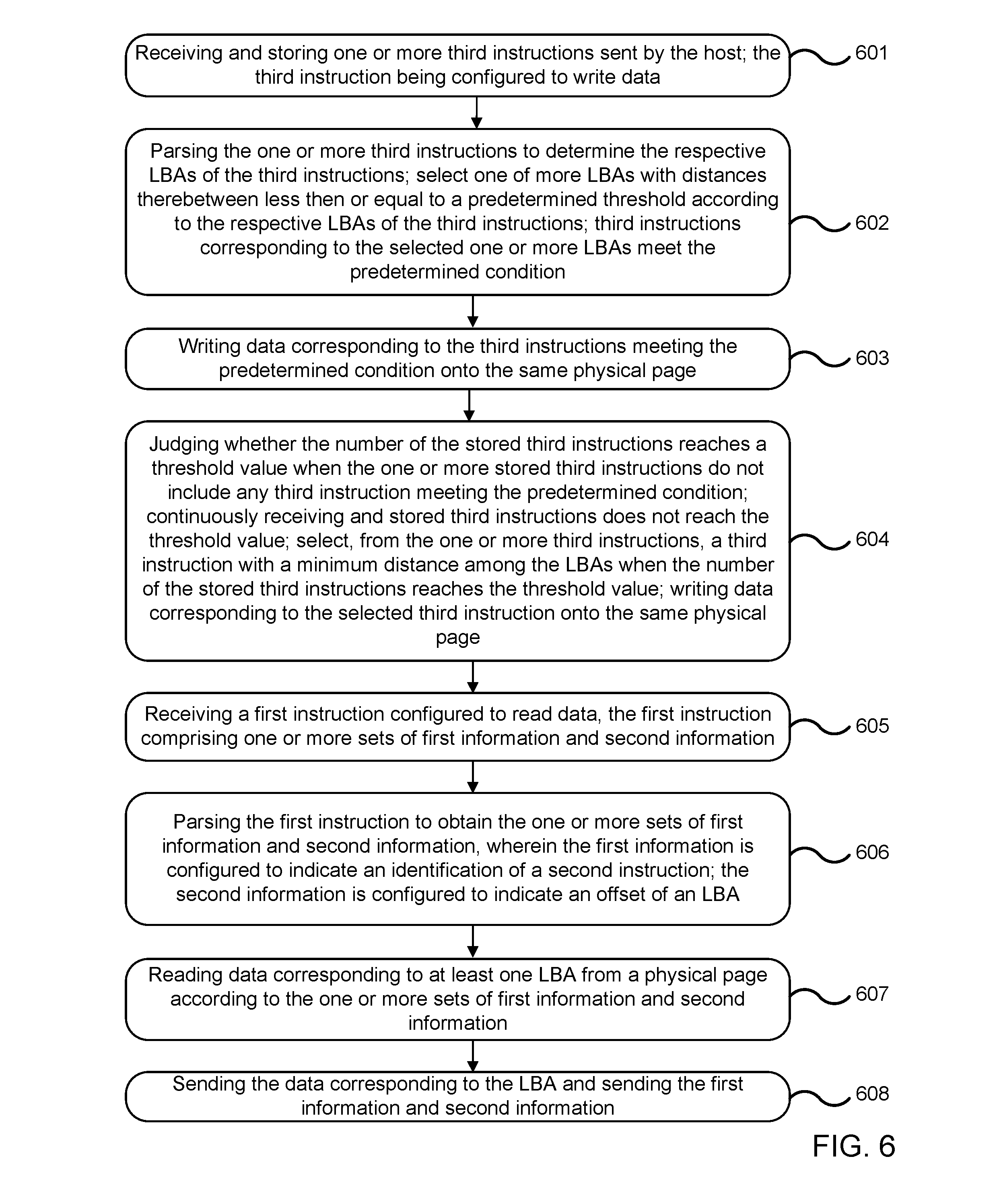

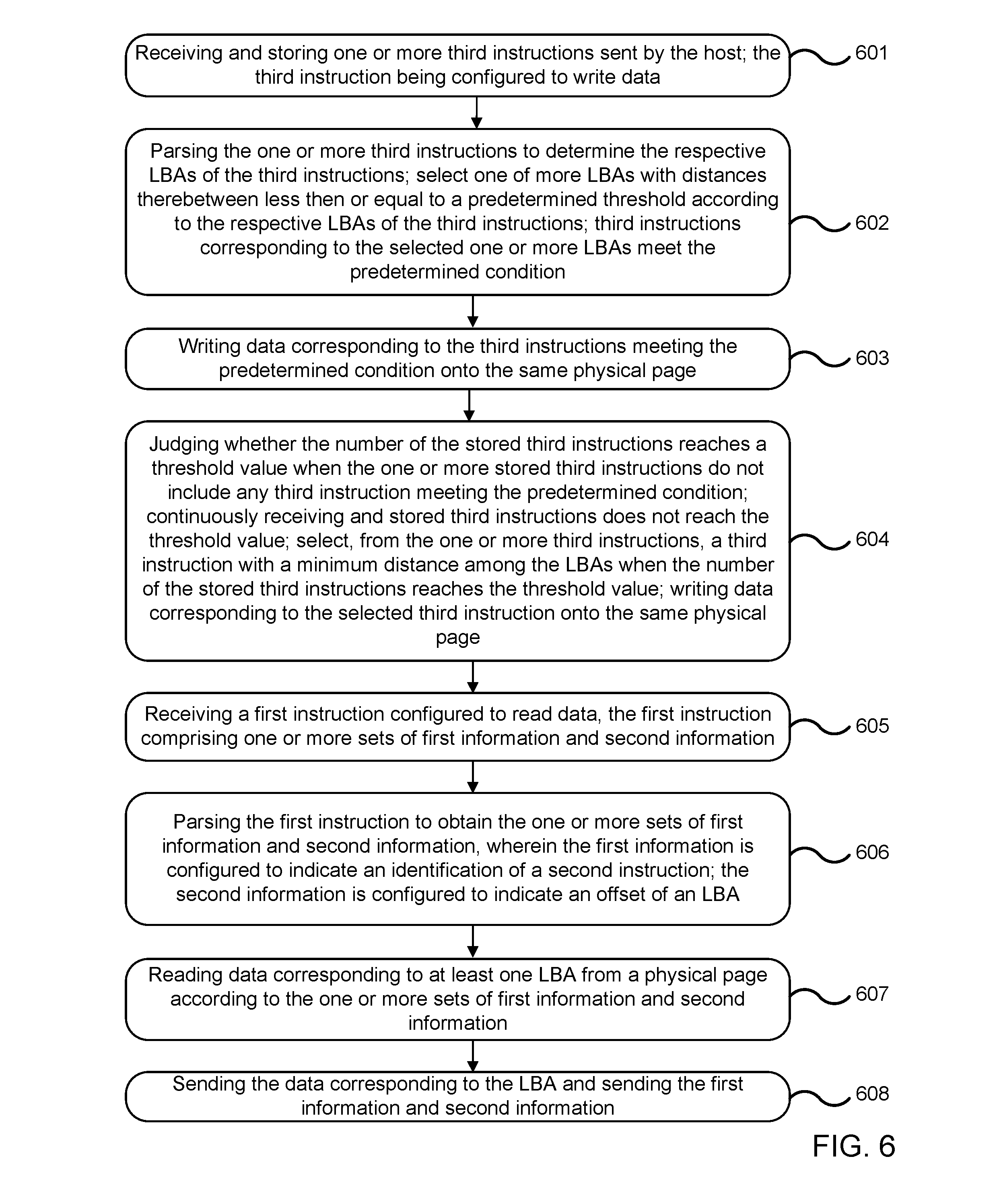

[0015] FIG. 6 is a schematic flow diagram of one embodiment of a data processing method;

[0016] FIG. 7 is a schematic structural composition diagram of one embodiment of an electronic device; and

[0017] FIG. 8 is a schematic structural composition diagram of one embodiment of an electronic device.

DETAILED DESCRIPTION

[0018] To provide a thorough understanding of features and technical contents, some embodiments are explained in detail in conjunction with the drawings below, which are provided for reference only and are to be exemplary rather than limiting of the embodiments of the present disclosure.

[0019] FIG. 1 is a schematic flow diagram of one embodiment of a data processing method. The exemplary data processing method is applied to an electronic device. As shown in FIG. 1, this embodiment of the data processing method comprises Steps 101, 102, 103 and 104, which will now be described.

[0020] Step 101 comprises receiving a first command configured to read data, the first command comprising one or more sets of first information and second information.

[0021] In the embodiments, the electronic device may be a notebook, a host, an all-in-one machine, and the like. The electronic device has a processor, such as a CPU. The electronic device further has a solid-state drive, which comprises: a memory and a controller. The memory is configured to store data, and in some embodiments, comprises a Nand Flash. Generally, the Nand Flash stores data in terms of physical pages. The controller is configured to control read-in and write-out of data, and in some embodiments, comprises a Flash controller.

[0022] In the Flash controller, the size of a physical page of the Nand Flash is greater than that of mapping due to the characteristics of 4K mapping. Accordingly, data corresponding to a plurality of LBAs may be stored in every physical page. Due to randomness of data writing, the plurality of LBAs written on one physical page is not continuous. Currently, to read data, a plurality of Nand Flash commands is used to read data from the same physical page several times. For each NVMe command, data is returned. For example, when 4 stored LBAs are not located continuously in one 16K physical page, 4 Nand Flash commands are required to read data from the same physical page 4 times, resulting in low efficiency.

[0023] In one embodiment, a processor, such as a CPU, receives a second command, configured to read data sent from the host. The second command comprises an NVMe read command. The processor performs a unified schedule for LBAs requested by a plurality of second commands. Respective offsets of the LBAs requested by the second commands are determined according to specific values stored on the physical page in the Nand Flash. After that, using the identification corresponding to the second command as first information and using the offsets of the LBA corresponding to the second command as second information, the first and second information are written into the first command, which is a Nand Flash read command. As such, the first command comprises one or more sets of first information and second information. The processor sends the first command to the controller, such as a Flash controller, which executes the first command after receiving the first command. Accordingly, the first information and the second information corresponding to the one or more second commands are included in the first command.

[0024] Step 102 comprises parsing the first command to obtain the one or more sets of first information and second information, wherein the first information is configured to indicate an identification of a second command; the second information is configured to indicate an offset of an LBA.

[0025] In one embodiment, the controller parses the first command to obtain the one or more sets of first information and second information, wherein the first information indicates an identification of a second command, and the second information is configured to indicate an offset of an LBA.

[0026] Each set of first information and second information corresponds to a mapping block, and each mapping block corresponds to one LBA. As such, the first command indicates data corresponding to a plurality of LBAs.

[0027] Step 103 comprises reading data corresponding to at least one LBA from a physical page according to the one or more sets of first information and second information.

[0028] In one embodiment, wherein, as an example, the second command is the Nand Flash read command, and the first command is the NVMe read command, one Nand Flash read command acknowledges a plurality of NVMe read commands.

[0029] Each Nand Flash read command comprises one or more NVMe command identities ("Command IDs"), and corresponding offsets ("Block Offsets") of LBAs. Each set of a Command ID and an LBA offset of an NVMe command corresponds to one mapping block (Mapping Block). After each Nand Flash read command reads data from one physical page, the corresponding data is sent to a corresponding NVMe command in terms of the corresponding NVMe Command ID and the offset of LBA thereof.

[0030] Step 104 comprises sending the data corresponding to the LBA and sending the first information and second information.

[0031] In one embodiment, the controller in the electronic device sends the data corresponding to the LBA and the first information and the second information to the processor, and the processor calculates the address of the host according to the first information and the second information and sends the data to the host. Thus, one Nand Flash read command acknowledges a plurality of NVMe read commands, such that repetitive reading of one physical page is avoided and the issue of lower efficiency is eliminated. Accordingly, the efficiency of accessing Nand Flash is improved significantly.

[0032] FIG. 2 is a schematic flow diagram of one embodiment of a data processing method. The exemplary data processing method is applied to an electronic device. As shown in FIG. 2, one embodiment of the data processing method comprises Steps 201, 202, 203, 204, 205, 206 and 207, which will now be described.

[0033] Step 201 comprises receiving one or more second commands sent by a host.

[0034] In the embodiments, the electronic device may be a notebook, a host, an all-in-one machine, or other similar device. The electronic device has a processor, such as a CPU. The electronic device further has a solid-state drive, which comprises: a memory and a controller. The memory may comprise a Nand Flash, for example, and it is configured to store data. Generally, the Nand Flash stores data in terms of physical pages. The controller, which may be a Flash controller, for example, is configured to control read-in and write-out of data.

[0035] In the Flash controller, the size of a physical page of the Nand Flash is greater than that of mapping due to the characteristics of 4K mapping. Accordingly, data corresponding to a plurality of LBAs may be stored in every physical page. Due to the randomness of data writing, the plurality of LBAs written on one physical page is not continuous. Currently, to read data, a plurality of Nand Flash commands is used to read data from the same physical page several times. For each NVMe command, data is returned. For example, 4 stored LBAs are not located continuously in one 16K physical page, and, therefore, 4 Nand Flash commands are required to read data from the same physical page 4 times, resulting in low efficiency.

[0036] In one embodiment, a processor, such as a CPU, receives a second command, which is configured to read data sent from the host. The second command comprises an NVMe read command. The processor performs a unified schedule for LBAs requested by a plurality of second commands. Respective offsets of the LBAs requested by the second commands are determined according to specific values stored on the physical page in the Nand Flash.

[0037] Step 202 comprises parsing each of the second commands to obtain identification and offsets of the LBAs corresponding to the second commands.

[0038] Step 203 comprises using the identification corresponding to the second command as a first information, using the offsets of the LBA corresponding to the second command as a second information, and writing the first and second information into the first command, so as to form the first command.

[0039] The identification corresponding to the second command is used as a first information and the offset amounts of the LBA corresponding to the second command are used as a second information, and the first and second information are written into the first command, so as to form the first command, which comprises a Nand Flash read command. As such, the first command comprises one or more sets of first information and second information.

[0040] Step 204 comprises receiving a first command configured to read data, the first command comprising one or more sets of first information and second information.

[0041] In some embodiments, the processor sends the first command to the controller, a Flash controller, which executes the first command after receiving the first command. The first information and the second information corresponding to the one or more second commands are included in the first command.

[0042] Step 205 comprises parsing the first command to obtain the one or more sets of first information and second information, wherein the first information is configured to indicate an identification of a second command; the second information is configured to indicate an offset of an LBA.

[0043] In one embodiment, the controller parses the first command to obtain the one or more sets of first information and second information, wherein the first information is configured to indicate an identification of a second command; the second information is configured to indicate an offset of an LBA.

[0044] Each set of first information and second information corresponds to a mapping block, and each mapping block corresponds to one LBA. As such, the first command indicates data corresponding to a plurality of LBAs.

[0045] Step 206 comprises reading data corresponding to at least one LBA from a physical page according to the one or more sets of first information and second information.

[0046] In one exemplary embodiment, wherein the second command is the Nand Flash read command and the first command is the NVMe read command, one Nand Flash read command acknowledges a plurality of NVMe read commands.

[0047] Each Nand Flash read command comprises one or more NVMe command identities (Command IDs), and corresponding offsets (Block Offsets) of LBAs; wherein each set of a Command ID and an offset of LBA of an NVMe command corresponds to one mapping block (Mapping Block). After each Nand Flash read command reads data from one physical page, the corresponding data is sent to a corresponding NVMe command in terms of the corresponding NVMe Command ID and the LBA offset thereof.

[0048] Step 207 comprises sending the data corresponding to the LBA and sending the first information and second information.

[0049] In one embodiment, the controller in the electronic device sends the data corresponding to the LBA, the first information and the second information to the processor, after which the processor calculates the address of the host according to the first information and the second information and sends the data to the host. Thus, one Nand Flash read command acknowledges a plurality of NVMe read commands, such that repetitive reading of one physical page is avoided and the issue of lower efficiency is eliminated, significantly improving the efficiency of accessing Nand Flash.

[0050] FIG. 3 is an information correspondence diagram of four sets of NVMe read commands of one embodiment. In this embodiment, a plurality of sets of "Command ID (or Instruction ID) and Block Offset" pieces of information are stored in a Nand Flash read command. In an example that assumes the use of 4K mapping and a 16 KB physical page as an example, 4 sets of "NVMe Command ID and Block Offset" sets may be stored. The Command ID (also referred to as an Instruction ID) is an identification of an NVMe read command, which may determine a unique NVMe command, and the Block Offset is used to mark the offset of a corresponding data block from the data block corresponding to the NVMe read command. As shown in FIG. 3, the Command ID and Block Offset of NVMe Command A are command_id A and block_offset A, wherein command_id A uniquely determines command_id A and block_offset A uniquely determines a data block; NVMe Command B, NVMe Command C, NVMe Command D are structured similarly, each with their respective set of a command_id and a block_offset.

[0051] When an NVMe read command of the host is received, a CPU performs unified scheduling according to the LBA and the size of data block requested by the NVMe read command.

[0052] The CPU fills "Command ID (or Instruction Id) and Block Offset" information of each Nand Flash read command according to a specific value of LBA stored in a physical page in Nand Flash. A plurality of sets of "Command ID (or Instruction ID) and Block Offset" information may be filled for each Nand Flash read command.

[0053] The CPU then sends the Nand Flash read command with "Command ID and Block Offset" information that has been filled out to a Flash controller.

[0054] The Flash controller executes the Nand Flash read command to read the data in the physical page from the Nand Flash, and sends each mapping block and corresponding "Command ID and Block Offset" to the CPU.

[0055] The CPU calculates a corresponding host address in terms of "Command ID and Block Offset", and sends the data to the host.

[0056] When the current cached NVMe read command includes an LBA of one physical page, one Nand Flash command may be used to acknowledge a plurality of NVMe read commands. Hence, a corresponding LBA must be included in the current cached NVMe read command. To this end, a data processing method is provided in another embodiment, as shown in FIG. 4.

[0057] FIG. 4 is a schematic flow diagram of one embodiment of a data processing method. As shown in FIG. 4, this embodiment of the data processing method comprises Steps 401, 402, 403, 404, 405, 406 and 407, which will now be described.

[0058] Step 401 comprises receiving and storing one or more third commands sent by the host, the third command being configured to write data.

[0059] In some embodiments, the electronic device may be a notebook, a host, an all-in-one machine, or other similar device. The electronic device comprises a processor, such as a CPU. The electronic device further comprises a solid-state drive, which itself comprises: a memory and a controller. The memory, such as a Nand Flash, is configured to store data. Generally, the Nand Flash stores data in terms of physical pages. The controller, such as a Flash controller, is configured to control read-in and write-out of data. In some embodiments, the third command is an NVMe write command. The CPU receives and caches the one or more third commands sent by the host.

[0060] Step 402 comprises electing, from the one or more third commands, third commands that meet a predetermined condition.

[0061] In one embodiment, the data to be written into the Nand Flash are categorized in terms of LBA. In this embodiment, distances between LBAs (i.e., differences between LBAs) on the same physical page for writing are intentionally limited to optimize later sequential reads without compromising random writing performance significantly.

[0062] Step 403 comprises writing data corresponding to the third commands meeting the predetermined condition onto the same physical page.

[0063] Step 404 comprises receiving a first command configured to read data, the first command comprising one or more sets of first information and second information.

[0064] In the Flash controller, the size of a physical page of the Nand Flash is greater than that of mapping due to characteristics of 4K mapping. Accordingly, data corresponding to a plurality of LBAs may be stored in a physical page. Due to the randomness of data writing, the plurality of LBAs written on one physical page are not continuous. Currently, to read data, a plurality of Nand Flash commands is used to read data from the same physical page several times. For each NVMe command, data is returned. For example, when 4 stored LBAs are not located continuously in one 16K physical page, 4 Nand Flash commands are required to read data from the same physical page 4 times, resulting in low efficiency.

[0065] In one embodiment, a processor, such as a CPU, receives a second command, which is configured to read data sent from the host. The second command comprises an NVMe read command. The processor performs a unified schedule for LBAs requested by a plurality of second commands. Respective offsets of the LBAs requested by the second commands are determined according to specific values stored on the physical page in the Nand Flash. The respective identities, which act as the first information and correspond to the second commands, and the offsets of the LBAs, which act as the second information and correspond to the second commands, are written into and form the first command, which is a Nand Flash read command. As such, the first command comprises one or more sets of first information and second information. The processor sends the first command to the controller, such as a Flash controller, which executes the first command after receiving the first command. Accordingly, the first information and the second information corresponding to the one or more second commands are included in the first command.

[0066] Step 405 comprises parsing the first command to obtain the one or more sets of first information and second information, wherein the first information is configured to indicate an identification of a second command and the second information is configured to indicate an offset of an LBA.

[0067] In one embodiment, the controller parses the first command to obtain the one or more sets of first information and second information, wherein the first information is configured to indicate an identification of a second command and the second information is configured to indicate an offset of an LBA.

[0068] Each set of first information and second information corresponds to a mapping block, and each mapping block corresponds to one LBA. As such, the first command indicates data corresponding to a plurality of LBAs.

[0069] Step 406 comprises reading data corresponding to at least one LBA from a physical page according to the one or more sets of first information and second information.

[0070] In one embodiment, assuming, as an example, that the second command is the Nand Flash read command and the first command is the NVMe read command, one Nand Flash read command acknowledges a plurality of NVMe read commands.

[0071] Each Nand Flash read command comprises one or more NVMe command identities (Command IDs or Instruction IDs), and corresponding offsets (Block Offsets) of LBAs; wherein each set of a Command ID and an LBA offset of an NVMe command corresponds to one mapping block (Mapping Block). After each Nand Flash read command reads data from one physical page, the corresponding data is sent to a corresponding NVMe command in terms of the corresponding NVMe Command ID and the offset of LBA thereof.

[0072] Step 407 comprises sending the data corresponding to the LBA and sending the first information and second information.

[0073] In one embodiment, the controller in the electronic device sends the data corresponding to the LBA, the first information and the second information to the processor, after which the processor calculates the address of the host according to the first information and the second information and sends the data to the host. Thus, one Nand Flash read command acknowledges a plurality of NVMe read commands, such that repetitive reading of one physical page is avoided and the efficiency of accessing Nand Flash is improved significantly.

[0074] FIG. 5 is a schematic flow diagram of one embodiment of a data processing method. As shown in FIG. 5, this embodiment of the data processing method comprises: Steps 501, 502, 503, 504, 505, 506, and 507, which will now be described.

[0075] Step 501 comprises receiving and storing one or more third commands sent by the host, the third command being configured to write data. In the various embodiments, the electronic device may be a notebook, a host, an all-in-one machine, or similar device. The electronic device comprises a processor, such as a CPU. The electronic device further comprises a solid-state drive, which itself comprises: a memory and a controller. The memory, such as a Nand Flash, is configured to store data. Generally, the Nand Flash stores data in terms of physical pages. The controller (for example, a Flash controller) is configured to control read-in and write-out of data.

[0076] In one embodiment, the third command is an NVMe write command. The CPU receives and caches the one or more third commands sent by the host.

[0077] Step 502 comprises parsing the one or more third commands to determine the respective LBAs of the third commands; selecting one or more LBAs with distances therebetween less than or equal to a predetermined threshold; and selecting third commands corresponding to the selected one or more LBAs that meet the predetermined condition.

[0078] In one embodiment, the data to be written into the Nand Flash are categorized in terms of LBA. Distances between LBAs (i.e., differences between LBAs) on the same physical page for writing are as intentionally limited to optimize later sequential reads without compromising random writing performance significantly.

[0079] Assuming that the size of the physical page is 16 KB, the size of mapping is 4 KB, and the size of LBA data block is 4 KB, 4 different LBA data blocks can be included on 1 physical page, while the minimum data unit for each access of Nand Flash is 4 KB.

[0080] When an NVMe write command of the host is reached, the CPU stores the reached NVMe write command in a buffer pool. The CPU then selects LBAs meeting a condition from the buffer pool of NVMe write commands to form and send a Nand Flash write command to the Flash controller. Assuming that there are 4 LBA data blocks, which are set as LBA0, LBA1, LBA2, LBA3, on each physical page, the condition comprises the following: |LBAi-LBAj|.ltoreq.128K if the solution of "one Nand Flash read command acknowledging a plurality of NVMe read commands" is not used; |LBAi-LBAj|.ltoreq.512 KB if the solution of "one Nand Flash read command acknowledging a plurality of NVMe read commands" is used; where i, j=0, 1, 2, 3.

[0081] Step 503 comprises writing data corresponding to the third commands that meet the predetermined condition onto the same physical page.

[0082] Step 504 comprises receiving a first command configured to read data, the first command comprising one or more sets of first information and second information.

[0083] In the Flash controller, the size of a physical page of the Nand Flash is greater than that of mapping due to characteristics of 4K mapping. Accordingly, data corresponding to a plurality of LBAs may be stored in a physical page. Due to the randomness of data writing, the plurality of LBAs written on one physical page are not continuous. Currently, to read data, a plurality of Nand Flash commands is used to read data from the same physical page several times. For each NVMe command, data is returned. For example, when 4 stored LBAs are not located continuously in one 16K physical page, 4 Nand Flash commands are required to read data from the same physical page 4 times, resulting in low efficiency.

[0084] In one embodiment, a processor, such as a CPU, receives a second command, which is configured to read data sent from the host. The second command comprises an NVMe read command. The processor performs a unified schedule for LBAs requested by a plurality of second commands. Respective offsets of the LBAs requested by the second commands are determined according to specific values stored on the physical page in the Nand Flash. The respective identities, which act as the first information and correspond to the second commands, and the offsets of the LBAs, which act as the second information and correspond to the second commands, are written into and form the first command, which is a Nand Flash read command. As such, the first command comprises one or more sets of first information and second information. The processor sends the first command to the controller (which, as an example, may comprise a Flash controller), which executes the first command after receiving the first command. Accordingly, the first information and the second information corresponding to the one or more second commands are included in the first command.

[0085] Step 505 comprises parsing the first command to obtain the one or more sets of first information and second information, wherein the first information is configured to indicate an identification of a second command and the second information is configured to indicate an offset of an LBA.

[0086] In one embodiment, the controller parses the first command to obtain the one or more sets of first information and second information, wherein the first information is configured to indicate an identification of a second command and the second information is configured to indicate an offset of an LBA.

[0087] Herein, each set of first information and second information corresponds to a mapping block, and each mapping block corresponds to one LBA. As such, the first command indicates data corresponding to a plurality of LBAs.

[0088] Step 506 comprises reading data corresponding to at least one LBA from a physical page according to the one or more sets of first information and second information.

[0089] In one embodiment, assuming that, as an example, the second command comprises the Nand Flash read command and the first command comprises the NVMe read command, one Nand Flash read command acknowledges a plurality of NVMe read commands.

[0090] Each Nand Flash read command comprises one or more NVMe command identities (Command IDs or Instruction IDs), and corresponding offsets (Block Offsets) of LBAs. Each set of a Command ID (or Instruction IDs) and an LBA offset of an NVMe command corresponds to one mapping block (Mapping Block). After each Nand Flash read command reads data from one physical page, the corresponding data is sent to a corresponding NVMe command in terms of the corresponding NVMe Command ID (or Instruction ID) and the offset of LBA thereof.

[0091] Step 507 comprises sending the data corresponding to the LBA and sending the first information and second information.

[0092] In one embodiment, the controller in the electronic device sends the data corresponding to the LBA, the first information and the second information to the processor, after which the processor calculates the address of the host according to the first information and the second information and sends the data to the host. Thus, one Nand Flash read command acknowledges a plurality of NVMe read commands, such that repetitive reading of one physical page is avoided and the efficiency of accessing Nand Flash is improved significantly.

[0093] FIG. 6 is a schematic flow diagram of one embodiment of a data processing method. As shown in FIG. 6, one embodiment of the data processing method comprises Step 601, Step 602, Step 603, Step 604, Step 605, Step 606, Step 607, and Step 608, all of which will now be described.

[0094] Step 601 comprises receiving and storing one or more third commands sent by the host, the third command being configured to write data.

[0095] In one embodiment, the electronic device may be a notebook, a host, an all-in-one machine, or other similar device. The electronic device comprises a processor, such as a CPU. The electronic device further comprises a solid-state drive, which itself comprises: a memory and a controller. The memory, which may comprise, as an example, a Nand Flash, is configured to store data. Generally, the Nand Flash stores data in terms of physical pages. The controller is configured to control read-in and write-out of data, and may comprises, as an example, a Flash controller.

[0096] In one embodiment, the third command comprises an NVMe write command, and the CPU receives and caches the one or more third commands sent by the host.

[0097] Step 602 comprises: parsing the one or more third commands to determine the respective LBAs of the third commands; selecting one or more LBAs with distances therebetween less than or equal to a predetermined threshold according to the respective LBAs of the third commands; and selecting the third commands corresponding to the selected one or more LBAs that meet the predetermined condition.

[0098] In one embodiment, the data to be written into the Nand Flash are categorized in terms of LBA. Distances between LBAs (i.e., differences between LBAs) on the same physical page for writing are as intentionally limited to optimize later sequential reads without compromising random writing performance significantly.

[0099] Assuming that the size of the physical page is 16 KB, the size of mapping is 4 KB, and the size of LBA data block is 4 KB, 4 different LBA data blocks can be included on 1 physical page, while the minimum data unit for each access of Nand Flash is 4 KB.

[0100] When an NVMe write command of the host is reached, the CPU stores the reached NVMe write command in a buffer pool. The CPU then selects LBAs meeting a condition from the buffer pool of NVMe write commands to form and send a Nand Flash write command to the Flash controller. Assuming that there are 4 LBA data blocks, which are set as LBA0, LBA1, LBA2, LBA3, on each physical page, the condition comprises the following: |LBAi-LBAj|.ltoreq.128K if the solution of "one Nand Flash read command acknowledging a plurality of NVMe read commands" is not used; |LBAi-LBAj|.ltoreq.512 KB if the solution of "one Nand Flash read command acknowledging a plurality of NVMe read commands" is used; where i, j=0, 1, 2, 3.

[0101] Step 603 comprises writing data corresponding to the third commands that meet the predetermined condition onto the same physical page.

[0102] Step 604 comprises: judging whether the number of the stored third commands reaches a threshold value in a state wherein the one or more stored third commands do not include any third command meeting the predetermined condition; continuously receiving and storing the third commands sent by the host when the number of the stored third commands does not reach the threshold value; selecting, from the one or more third commands, a third command with a minimum distance among the LBAs when the number of the stored third commands reaches the threshold value; and writing data corresponding to the selected third command onto the same physical page.

[0103] In one embodiment, if no LBA meeting the predetermined condition is selected, but the NVMe write command buffer pool is not full, then, temporarily, there is no further processing done until a new NVMe command is reached for continuing execution of step 602.

[0104] If no LBA meeting the predetermined condition is selected, and the NVMe write command buffer pool is full, then a set of LBAs with relatively small distances are selected to form a Nand Flash write command to be sent to the Flash controller. After that, processing waits until receipt of a new NVMe write command.

[0105] Step 605 comprises receiving a first command configured to read data, the first command comprising one or more sets of first information and second information.

[0106] In the Flash controller, the size of a physical page of the Nand Flash is greater than that of mapping due to characteristics of 4K mapping. Accordingly, data corresponding to a plurality of LBAs may be stored in a physical page. Due to the randomness of data writing, the plurality of LBAs written on one physical page are not continuous. Currently, to read data, a plurality of Nand Flash commands is used to read data from the same physical page several times. For each NVMe command, data is returned. For example, when 4 stored LBAs are not located continuously in one 16K physical page, 4 Nand Flash commands are required to read data from the same physical page 4 times, resulting in low efficiency.

[0107] In one embodiment, a processor, such as a CPU, receives a second command, which is configured to read data sent from the host. The second command comprises an NVMe read command. The processor performs a unified schedule for LBAs requested by a plurality of second commands. Respective offsets of the LBAs requested by the second commands are determined according to specific values stored on the physical page in the Nand Flash. The respective identities, which act as the first information and correspond to the second commands, and the offsets of the LBAs, which act as the second information and correspond to the second commands, are written into and form the first command, which is a Nand Flash read command. As such, the first command comprises one or more sets of first information and second information. The processor sends the first command to the controller (which, as an example, may comprise a Flash controller), which executes the first command after receiving the first command. Accordingly, the first information and the second information corresponding to the one or more second commands are included in the first command.

[0108] Step 606 comprises parsing the first command to obtain the one or more sets of first information and second information, wherein the first information is configured to indicate an identification of a second command and the second information is configured to indicate an LBA offset.

[0109] In one embodiment, the controller parses the first command to obtain the one or more sets of first information and second information, wherein the first information is configured to indicate an identification of a second command and the second information is configured to indicate an offset of an LBA.

[0110] Herein, each set of first information and second information corresponds to a mapping block, and each mapping block corresponds to one LBA. As such, the first command indicates data corresponding to a plurality of LBAs.

[0111] Step 607 comprises reading data corresponding to at least one LBA from a physical page according to the one or more sets of first information and second information.

[0112] In one embodiment, assuming that, as an example, the second command comprises the Nand Flash read command and the first command comprises the NVMe read command, one Nand Flash read command acknowledges a plurality of NVMe read commands.

[0113] Each Nand Flash read command comprises one or more NVMe command identities (Command IDs or Instruction IDs), and corresponding offsets (Block Offsets) of LBAs. Each set of a Command ID (or Instruction IDs) and an LBA offset of an NVMe command corresponds to one mapping block (Mapping Block). After each Nand Flash read command reads data from one physical page, the corresponding data is sent to a corresponding NVMe command in terms of the corresponding NVMe Command ID (or Instruction ID) and the offset of LBA thereof.

[0114] Step 608 comprises sending the data corresponding to the LBA and sending the first information and second information.

[0115] In one embodiment, the controller in the electronic device sends the data corresponding to the LBA, the first information and the second information, to the processor, after which the processor calculates the address of the host according to the first information and the second information and sends the data to the host. Thus, one Nand Flash read command acknowledges a plurality of NVMe read commands, such that repetitive reading of one physical page is avoided and the efficiency of accessing Nand Flash is improved significantly.

[0116] FIG. 7 is a schematic structural composition diagram of one embodiment of an electronic device.

[0117] The electronic device comprises: a memory 71, configured to store data in terms of physical pages. The electronic device further comprises a controller 72, configured to: receive a first command used to read data, the first command comprising one or more sets of first information and second information; parse the first command to obtain the one or more sets of first information and second information, wherein the first information is configured to indicate an identification of a second command and the second information is configured to indicate an offset of an LBA; read data corresponding to at least one LBA from a physical page according to the one or more sets of first information and second information; and send the data corresponding to the LBA and send the first information and second information.

[0118] It should be understood by persons of skill in the art that reference can be made to the descriptions related to the data processing method mentioned above regarding the function implementation of various units in the electronic device shown in FIG. 7.

[0119] FIG. 8 is a schematic structural composition diagram of one embodiment of an electronic device.

[0120] The electronic device comprises a memory 71, configured to store data in terms of physical pages. The electronic device further comprises a controller 72, configured to: receive a first command used to read data, the first command comprising one or more sets of first information and second information; parse the first command to obtain the one or more sets of first information and second information, wherein the first information is configured to indicate an identification of a second command and the second information is configured to indicate an offset of an LBA; read data corresponding to at least one LBA from a physical page according to the one or more sets of first information and second information; and send the data corresponding to the LBA and send the first information and second information.

[0121] The electronic device further comprises a processor 73, configured to: receive one or more second commands sent by a host; parse each of the second commands to obtain respective identification and LBA offsets corresponding to each of the second commands; use the identification corresponding to the second command as a first information and use the offsets of the LBA corresponding to the second command as second information; and write the first and second information into the first command, so as to form the first command.

[0122] It should be understood by persons of skill in the art that reference can be made to the descriptions related to the data processing method mentioned above regarding function implementation of various units in the electronic device shown in FIG. 8.

[0123] In another embodiment, the electronic device comprises a memory 71, configured to store data in terms of physical pages. The electronic device further comprises a controller 72, configured to: receive a first command used to read data, the first command comprising one or more sets of first information and second information; parse the first command to obtain the one or more sets of first information and second information, wherein the first information is configured to indicate an identification of a second command and the second information is configured to indicate an LBA offset; read data corresponding to at least one LBA from a physical page according to the one or more sets of first information and second information; and send the data corresponding to the LBA and send the first information and second information.

[0124] The electronic device further comprises a processor 73, configured to: receive one or more second commands sent by a host; parse each of the second commands to obtain respective identification and offsets of the LBAs corresponding to each of the second commands; use the identification corresponding to the second command as first information and using the offsets of the LBA corresponding to the second command as second information and writing the first and second information into the first command, so as to form the first command.

[0125] The processor 73 is further configured to: receive and store one or more third commands sent by the host, the third command being configured to write data; and select, from the one or more third commands, third commands meeting a predetermined condition.

[0126] The controller 72 is further configured to write data corresponding to the third commands meeting the predetermined condition, onto the same physical page.

[0127] In yet another embodiment, the electronic device comprises: a memory 71, configured to store data in terms of physical pages.

[0128] This electronic device further comprises a controller 72, configured to: receive a first command used to read data, the first command comprising one or more sets of first information and second information; parse the first command to obtain the one or more sets of first information and second information, wherein the first information is configured to indicate an identification of a second command and the second information is configured to indicate an offset of an LBA; read data corresponding to at least one LBA from a physical page according to the one or more sets of first information and second information; and send the data corresponding to the LBA and send the first information and second information.

[0129] The electronic device further comprises a processor 73, configured to: receive one or more second commands sent by a host; parse each of the second commands to obtain respective identification and offsets of the LBAs corresponding to each of the second commands; use the identification corresponding to the second command as first information and use the offsets of the LBA corresponding to the second command as second information; and write the first and second information into the first command, so as to form the first command.

[0130] The processor 73 is further configured to: receive and store one or more third commands sent by the host, the third command being configured to write data; and select, from the one or more third commands, third commands meeting a predetermined condition.

[0131] The controller 72 is further configured to write data, corresponding to the third commands meeting the predetermined condition onto the same physical page.

[0132] The processor 73 is further configured to: parse the one or more third commands to determine the respective LBAs of the third commands; select one or more LBAs with distances therebetween less than or equal to a predetermined threshold according to the respective LBAs of the third commands; and select the third commands corresponding to the selected one or more LBAs meet the predetermined condition.

[0133] In another embodiment, the electronic device comprises: a memory 71, configured to store data in terms of physical pages.

[0134] This electronic device further comprises: a controller 72, configured to: receive a first command used to read data, the first command comprising one or more sets of first information and second information; parse the first command to obtain the one or more sets of first information and second information, wherein the first information is configured to indicate an identification of a second command and the second information is configured to indicate an LBA offset; read data corresponding to at least one LBA from a physical page according to the one or more sets of first information and second information; send the data corresponding to the LBA; and send the first information and second information.

[0135] The electronic device further comprises a processor 73, configured to: receive one or more second commands sent by a host; parse each of the second commands to obtain respective identification and offsets of the LBAs corresponding to each of the second commands; use the identification corresponding to the second command as first information and using the offsets of the LBA corresponding to the second command as second information; and write the first and second information into the first command, so as to form the first command.

[0136] The processor 73 is further configured to receive and store one or more third commands sent by the host, the third command(s) being configured to write data; and select, from the one or more third commands, third commands meeting a predetermined condition.

[0137] The controller 72 is further configured to write data, corresponding to the third commands meeting the predetermined condition, onto the same physical page.

[0138] The processor 73 is further configured to: determine whether the number of the stored third commands reaches a threshold value in state wherein none of the one or more stored third commands meet the predetermined condition; continuously receive and store the third commands sent by the host when the number of the stored third commands does not reach the threshold value; and select, from the one or more third commands, a third command with a minimum distance among the LBAs after the number of the stored third commands reaches the threshold value.

[0139] The controller 72 is further configured to write data corresponding to the selected third command onto the same physical page.

[0140] Different technical solutions recorded in the various embodiments may be combined arbitrarily without conflict therebetween.

[0141] In the several embodiments provided, it should be understood that the disclosed method and electronic device may be implemented in other manners. The above described device embodiments are merely illustrative. For example, the unit division is merely one logical function division and may be in other division manners in actual practice. For example, a plurality of units or components may be combined or integrated into another system, or some features can be omitted or disabled. Additionally, coupling, direct coupling, or communication connections among the parts as shown or discussed may be implemented through an interface or interfaces, and indirect coupling or communication connections of devices or units may be electrical, mechanical, or in other forms.

[0142] The units used as separate components may or may not be physically independent of each other. The element illustrated as a unit may or may not be a physical unit. For example, the illustrated element may be located at one position or deployed among a plurality of network units. A part or all of the units may be selected according to the actual needs to achieve the objectives of the solutions of the embodiments.

[0143] In addition, the functional units in the various embodiments may be integrated in one second processing unit, or may separately and physically exist as a single unit, or two or more units may be integrated into one unit. The integrated unit may be implemented by means of hardware, or may also be implemented in a form of hardware plus software functional unit.

[0144] The above embodiments are used only for illustration, and are not intended to limit the scope of the present disclosure. Various modifications and replacements readily derived by persons of skill in the art shall fall within the scope of the present disclosure.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.