Information Processing Device, Information Processing Method, And Program

SAITO; Kimihiro ; et al.

U.S. patent application number 16/460435 was filed with the patent office on 2019-10-24 for information processing device, information processing method, and program. This patent application is currently assigned to SONY CORPORATION. The applicant listed for this patent is SONY CORPORATION. Invention is credited to Nobuyoshi KOBAYASHI, Noriaki NISHI, Kimihiro SAITO, Junya SHIRAISHI, Kenji YAMAMOTO.

| Application Number | 20190325908 16/460435 |

| Document ID | / |

| Family ID | 59500656 |

| Filed Date | 2019-10-24 |

View All Diagrams

| United States Patent Application | 20190325908 |

| Kind Code | A1 |

| SAITO; Kimihiro ; et al. | October 24, 2019 |

INFORMATION PROCESSING DEVICE, INFORMATION PROCESSING METHOD, AND PROGRAM

Abstract

Provided are a device and a method which are capable of performing crosstalk-removed high-quality data reproduction from a high-density recording type optical disc. The device includes a photo detector that outputs a readout signal from a reproduction track of an information recording disc, an adjacent track reproduction binary signal supply unit that outputs a binary signal (binary data) which is a reproduction signal of an adjacent track of the reproduction track, a multi-input adaptive equalizer that includes an equalizer unit that receives the readout signal from the reproduction track and an adjacent track reproduction binary signal and outputs an equalization signal by an adaptive equalization process based on an input signal, and a binarization processing unit that executes a binarization process based on the equalization signal and generates a reproduction signal of the reproduction track.

| Inventors: | SAITO; Kimihiro; (Saitama, JP) ; YAMAMOTO; Kenji; (Kanagawa, JP) ; NISHI; Noriaki; (Kanagawa, JP) ; SHIRAISHI; Junya; (Kanagawa, JP) ; KOBAYASHI; Nobuyoshi; (Kanagawa, JP) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Assignee: | SONY CORPORATION Tokyo JP |

||||||||||

| Family ID: | 59500656 | ||||||||||

| Appl. No.: | 16/460435 | ||||||||||

| Filed: | July 2, 2019 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 15780090 | May 30, 2018 | 10373640 | ||

| PCT/JP2017/000779 | Jan 12, 2017 | |||

| 16460435 | ||||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | G11B 7/131 20130101; G11B 7/133 20130101; G11B 20/10009 20130101; G11B 7/005 20130101; G11B 20/10046 20130101 |

| International Class: | G11B 7/005 20060101 G11B007/005; G11B 20/10 20060101 G11B020/10; G11B 7/131 20060101 G11B007/131; G11B 7/133 20060101 G11B007/133 |

Foreign Application Data

| Date | Code | Application Number |

|---|---|---|

| Feb 5, 2016 | JP | 2016-021294 |

Claims

1. An information processing device, comprising: a photo detector that outputs a readout signal from a reproduction track of an information recording disc; and circuitry configured to: obtain a binary signal (binary data) from a reproduction signal of an adjacent track of the reproduction track; perform an adaptive equalization process on the readout signal and the adjacent track reproduction binary signal; obtain an equalization signal, based on an input signal, by adding results of the adaptive equalization process performed on the readout signal and the adjacent track reproduction binary signal; and execute a binarization process based on the equalization signal, and generate a reproduction signal of the reproduction track.

2. The information processing device according to claim 1, wherein the circuitry is further configured to: obtain a binary signal (binary data) of at least one adjacent track of the reproduction track.

3. The information processing device according to claim 1, wherein the circuitry is further configured to: obtain binary signals (binary data) of two adjacent tracks of the reproduction track.

4. The information processing device according to claim 1, wherein the circuitry is further configured to: generate an adjacent track reproduction binary signal based on a read signal of an adjacent track read via an optical pickup.

5. The information processing device according to claim 1, wherein the circuitry is further configured to: acquire an adjacent track reproduction binary signal previously stored in a record data storage memory from the record data storage memory.

6. The information processing device according to claim 1, further comprising: a memory that stores the adjacent track reproduction binary signal; and a memory controller that executes data input control on the multi-input adaptive equalizer from the memory.

7. The information processing device according to claim 6, wherein the memory controller executes data input control of simultaneously inputting a readout signal from the reproduction track and an adjacent track reproduction binary signal at a position nearest to the readout signal to the multi-input adaptive equalizer.

8. The information processing device according to claim 1, wherein the photo detector is a multi-signal output type photo detector that outputs a plurality of signals corresponding to an amount of received light of a split region, and wherein the circuitry is further configured to: perform an adaptive equalization process on the plurality of signals output from the photo detector and an adjacent track reproduction binary signal; and obtain an equalization signal by the adaptive equalization process based on an input signal.

9. The information processing device according to claim 8, wherein the photo detector is a multi-signal output type photo detector that has a plurality of split regions along a track direction (tangential direction) and outputs a plurality of signals corresponding to the amount of received light of each split region of the plurality of split regions.

10. The information processing device according to claim 8, wherein the photo detector is a multi-signal output type photo detector that has a plurality of split regions along a disc radial direction (radial direction) and outputs a plurality of signals corresponding to the amount of received light of each split region of the plurality of split regions.

11. The information processing device according to claim 1, wherein the circuitry is further configured to: receive an output of the photo detector; generate a plurality of signals corresponding to an amount of received light of a split region unit of the photo detector; perform an adaptive equalization process on the plurality of signals and an adjacent track reproduction binary signal; and obtain an equalization signal by the adaptive equalization process based on the input signal.

12. The information processing device according to claim 1, wherein the circuitry is further configured to: execute a partial response equalization process based on the input signal; and execute a maximum likelihood decoding process as the binarization process for the equalization signal.

13. The information processing device according to claim 1, wherein the circuitry is further configured to: generate an equalization target signal based on the binary signal; calculate an equalization error from the equalization target signal and the equalization signal output from the multi-input adaptive equalizer; and execute an adaptive equalization process based on the equalization error.

14. The information processing device according to claim 1, wherein the information recording disc is a disc in which data recording is performed on both a land and a groove, and wherein the reproduction track and the adjacent track are a combination of a land track and a groove track.

15. The information processing device according to claim 1, further comprising: a configuration that executes data reproduction in parallel from the adjacent track; a first photo detector that outputs a readout signal from a first reproduction track of the information recording disc; a second photo detector that outputs a readout signal from a second reproduction track adjacent to the first reproduction track; and a decoder that generates a binary signal (binary data) serving as a reproduction signal of the first reproduction track and a binary signal (binary data) serving as a reproduction signal of the second reproduction track, wherein the circuitry is further configured to: receive the readout signal from the first reproduction track and the binary signal serving as the reproduction signal of the second reproduction track generated by the decoder; obtain an equalization signal by an adaptive equalization process performed on the readout signal from the first reproduction track and the binary signal serving as the reproduction signal of the second reproduction track, based on an input signal; receive the readout signal from the second reproduction track and the binary signal serving as the reproduction signal of the first reproduction track generated by the decoder; obtain an equalization signal by an adaptive equalization process performed on the readout signal from the second reproduction track and the binary signal serving as the reproduction signal of the first reproduction track, based on an input signal; execute a binarization process based on the equalization signal obtained by the adaptive equalization process performed on the readout signal from the first reproduction track and the binary signal serving as the reproduction signal of the second reproduction track and generate a first track compatible reproduction binary signal; and execute a binarization process based on the equalization signal obtained by the adaptive equalization process performed on the readout signal from the second reproduction track and the binary signal serving as the reproduction signal of the first reproduction track and generate a second track compatible reproduction binary signal.

16. An information processing method executed in an information processing device, the method comprising: outputting, by a photo detector, a readout signal from a reproduction track of an information recording disc; obtaining a binary signal (binary data) from a reproduction signal of an adjacent track of the reproduction track; performing an adaptive equalization process on the readout signal from the reproduction track and the adjacent track reproduction binary signal; obtaining an equalization signal, based on an input signal, by adding results of the adaptive equalization process performed on the readout signal and the adjacent track reproduction binary signal; and executing a binarization process based on the equalization signal and generate a reproduction signal of the reproduction track.

17. A non-transitory computer-readable medium having embodied thereon a program, which when executed by a computer causes the computer to execute an information processing method, the method comprising: outputting, by a photo detector, a readout signal from a reproduction track of an information recording disc; obtaining a binary signal (binary data) from a reproduction signal of an adjacent track of the reproduction track; performing an adaptive equalization process on the readout signal from the reproduction track and the adjacent track reproduction binary signal; obtaining an equalization signal, based on an input signal, by adding results of the adaptive equalization process performed on the readout signal and the adjacent track reproduction binary signal; and executing a binarization process based on the equalization signal and generate a reproduction signal of the reproduction track.

Description

CROSS REFERENCE TO PRIOR APPLICATION

[0001] This application is a continuation of U.S. patent application Ser. No. 15/780,090 (filed on May 30, 2018), which is a National Stage patent application of PCT International Patent Application No. PCT/JP2017/000779 (filed on Jan. 12, 2017) under 35 U.S.C. .sctn. 371, which claims priority to Japanese Patent Application No. 2016-021294 (filed on Feb. 5, 2016), which are all hereby incorporated by reference in their entirety.

TECHNICAL FIELD

[0002] The present disclosure relates to an information processing device, an information processing method, and a program. More specifically, the present disclosure relates to an information processing device, an information processing method, and a program which are capable of implementing high-quality data reproduction from a disc in which high-density data recording is performed.

BACKGROUND ART

[0003] Optical discs such as digital versatile discs (DVDs) or Blu-ray (a registered trademark) discs (BD) have been widely used as media for recording various data in addition to images and programs.

[0004] The optical discs such as BDs are required to perform high-density information recording.

[0005] As a method of increasing the density of optical discs, there are a method of reducing a channel bit length, that is, a mark length, and increasing a density in a linear density direction and a method of narrowing a track pitch.

[0006] However, in a case where the density is increased in the linear density direction, there arises a problem that inter-symbol interference increases.

[0007] Further, if the track pitch is narrowed, information leaking from an adjacent track (an adjacent track crosstalk) increases.

[0008] In order to reduce the adjacent track crosstalk (hereinafter referred to simply as a "crosstalk"), various methods have been proposed.

[0009] For example, Patent Document 1 (International Publication No. WO 2016/006157) discloses a configuration of generating a reproduction signal in which the crosstalk is reduced by dividing a light receiving region of a photo detector and performing an adaptive equalization process using a plurality of light receiving signals obtained from respective split regions.

[0010] However, in this method, it is difficult to reliably analyze a recording signal of an adjacent track, and it is difficult to remove the crosstalk sufficiently.

[0011] Further, a technique of cancelling the crosstalk by supplying a reproduction signal of a track of a reproduction target and reproduction signals of tracks on both sides thereof to an adaptive equalizer unit and controlling a tap coefficient of the adaptive equalizer unit is disclosed in Patent Document 2 (Japanese Patent Application Laid-Open No. 2015-057753), Patent Document 3 (Japanese Patent Application Laid-Open No. 2012-079385), Patent Document 4 (Japanese Patent Application No. 4184585), and the like.

[0012] However, in the configuration described in Patent Documents mentioned above, in order to acquire a signal from which the crosstalk signal has been removed from a read signal of a current reproduction track, it is necessary to adjust phases of the read signal of the current reproduction track and the read signals of the tracks on both sides thereof and then input the resulting signal to the adaptive equalizer unit.

[0013] For this process, a memory for temporarily storing the read signal of the track adjacent to the current reproduction track or a delay processing configuration is required, and thus the required memory capacity increases, and there is a problem in that the circuit size increases.

CITATION LIST

Patent Document

[0014] Patent Document 1: International Publication No. WO 2016/006157 [0015] Patent Document 2: Japanese Patent Application Laid-Open No. 2015-057753 [0016] Patent Document 3: Japanese Patent Application Laid-Open No. 2012-079385 [0017] Patent Document 4: Japanese Patent Application No. 4184585

SUMMARY OF THE INVENTION

Problems to be Solved by the Invention

[0018] The present disclosure was made, for example, in light of the above-mentioned problems, and it is an object of the present disclosure to provide an information processing device, an information processing method, and a program which are capable of implementing a reproduction process of high-quality data in which the crosstalk caused by the recording signal of the adjacent track or the like is suppressed.

[0019] In one embodiment of the present disclosure, it is an object to provide an information processing device, an information processing method, and a program which are capable of implementing a reproduction process of high-quality data in which the crosstalk is suppressed while suppressing a necessary capacity of the memory for temporary storing the read data of the adjacent track to be small without increasing a circuit size.

Solutions to Problems

[0020] A first aspect of the present disclosure is an information processing device, including:

[0021] a photo detector that outputs a readout signal from a reproduction track of an information recording disc;

[0022] an adjacent track reproduction identification signal supply unit that outputs a reproduction identification signal obtained from a reproduction signal of an adjacent track of the reproduction track;

[0023] a multi-input adaptive equalizer that includes an equalizer unit that receives the readout signal from the reproduction track and an adjacent track reproduction identification signal and outputs an equalization signal by an adaptive equalization process based on an input signal; and

[0024] a reproduction signal generating unit that executes a reproduction signal generation process based on the equalization signal and generates a reproduction signal of the reproduction track.

[0025] Furthermore, a second aspect of the present disclosure is an information processing method executed in an information processing device, the method including:

[0026] outputting, by a photo detector, a readout signal from a reproduction track of an information recording disc;

[0027] outputting, by an adjacent track reproduction identification signal supply unit, a reproduction identification signal obtained from a reproduction signal of an adjacent track of the reproduction track;

[0028] inputting, by a multi-input adaptive equalizer, the readout signal from the reproduction track and an adjacent track reproduction identification signal to an equalizer unit and outputting an equalization signal by an adaptive equalization process based on an input signal; and

[0029] executing, by a reproduction signal generating unit, a reproduction signal generation process based on the equalization signal and generating a reproduction signal of the reproduction track.

[0030] Furthermore, a third aspect of the present disclosure is a program causing an information processing device to execute information processing including:

[0031] a process of outputting, by a photo detector, a readout signal from a reproduction track of an information recording disc;

[0032] a process of outputting, by an adjacent track reproduction identification signal supply unit, a reproduction identification signal obtained from a reproduction signal of an adjacent track of the reproduction track;

[0033] a process of inputting, by a multi-input adaptive equalizer, the readout signal from the reproduction track and an adjacent track reproduction identification signal to an equalizer unit and outputting an equalization signal by an adaptive equalization process based on an input signal; and

[0034] a process of generating, by a reproduction signal generating unit, a reproduction signal of the reproduction track by executing a reproduction signal generation process based on the equalization signal.

[0035] Further, for example, a program of the present disclosure is a program which can be provided to an information processing device or a computer system which is capable of executing various program codes through a storage medium or a communication medium provided in a computer readable format. As the program is provided in a computer readable format, a process according to the program is implemented on the information processing device or the computer system.

[0036] Still other objects, features, and advantages of the present disclosure will become apparent from detailed description based on an embodiment of the present disclosure to be described later or the appended drawings. Further, in this specification, a system refers to a logical aggregate configuration of a plurality of devices and is not limited to a configuration in which devices of respective components are in the same housing.

Effects of the Invention

[0037] According to a configuration of one embodiment of the present disclosure, a device and a method which are capable of performing crosstalk-removed high-quality data reproduction from a high-density recording type optical disc are realized.

[0038] Specifically, the device includes a photo detector that outputs a readout signal from a reproduction track of an information recording disc, an adjacent track reproduction binary signal supply unit that outputs a binary signal (binary data) which is a reproduction signal of an adjacent track of the reproduction track, a multi-input adaptive equalizer that includes an equalizer unit that receives the readout signal from the reproduction track and an adjacent track reproduction binary signal and outputs an equalization signal by an adaptive equalization process based on an input signal, and a binarization processing unit that executes a binarization process based on the equalization signal and generates a reproduction signal of the reproduction track.

[0039] With this configuration, a device and a method which are capable of performing crosstalk-removed high-quality data reproduction from a high-density recording type optical disc are realized.

[0040] Further, the effects described in this specific area are merely examples and not intended to be limited and may have additional effects.

BRIEF DESCRIPTION OF DRAWINGS

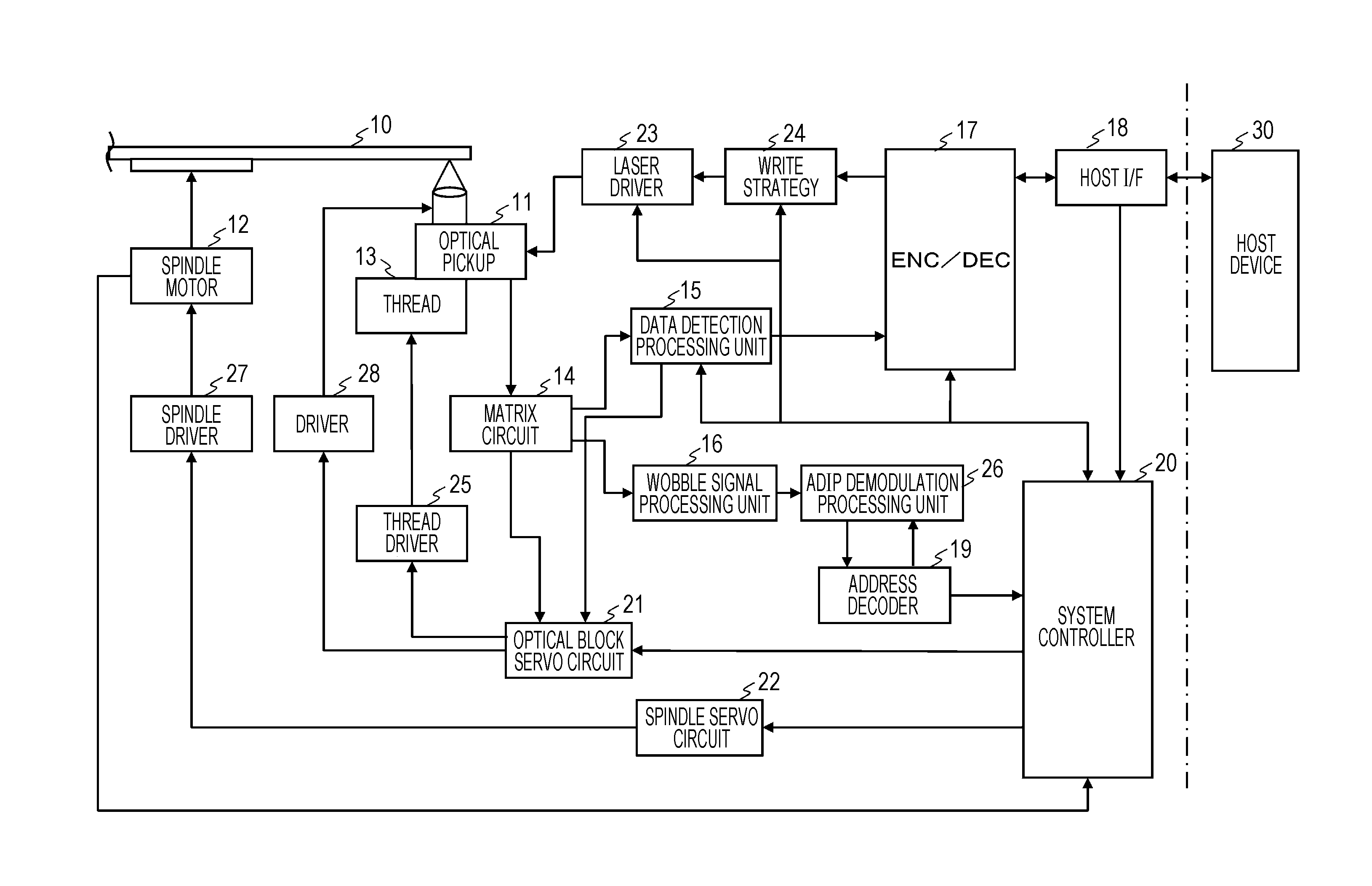

[0041] FIG. 1 is a diagram illustrating a configuration example of an information processing device.

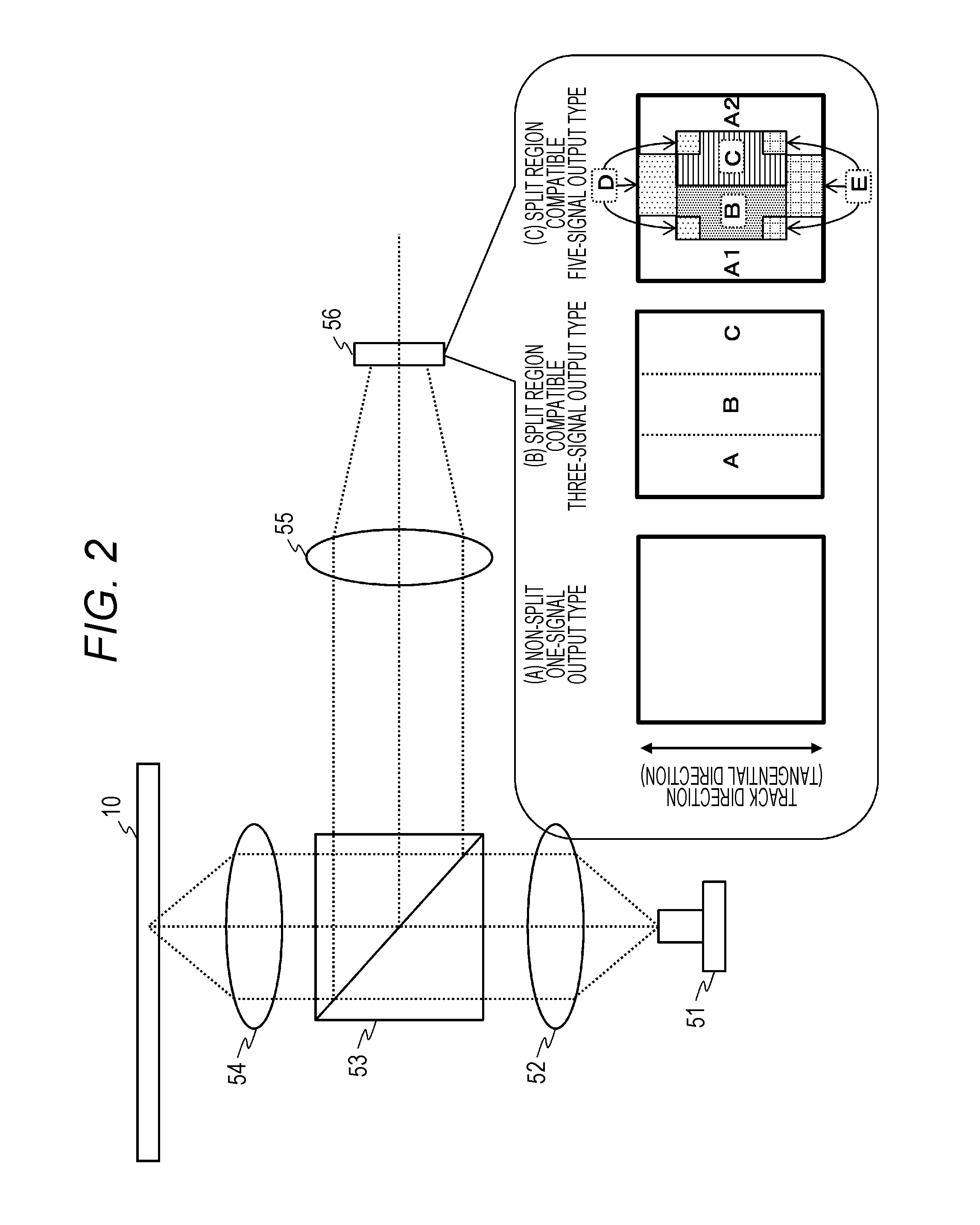

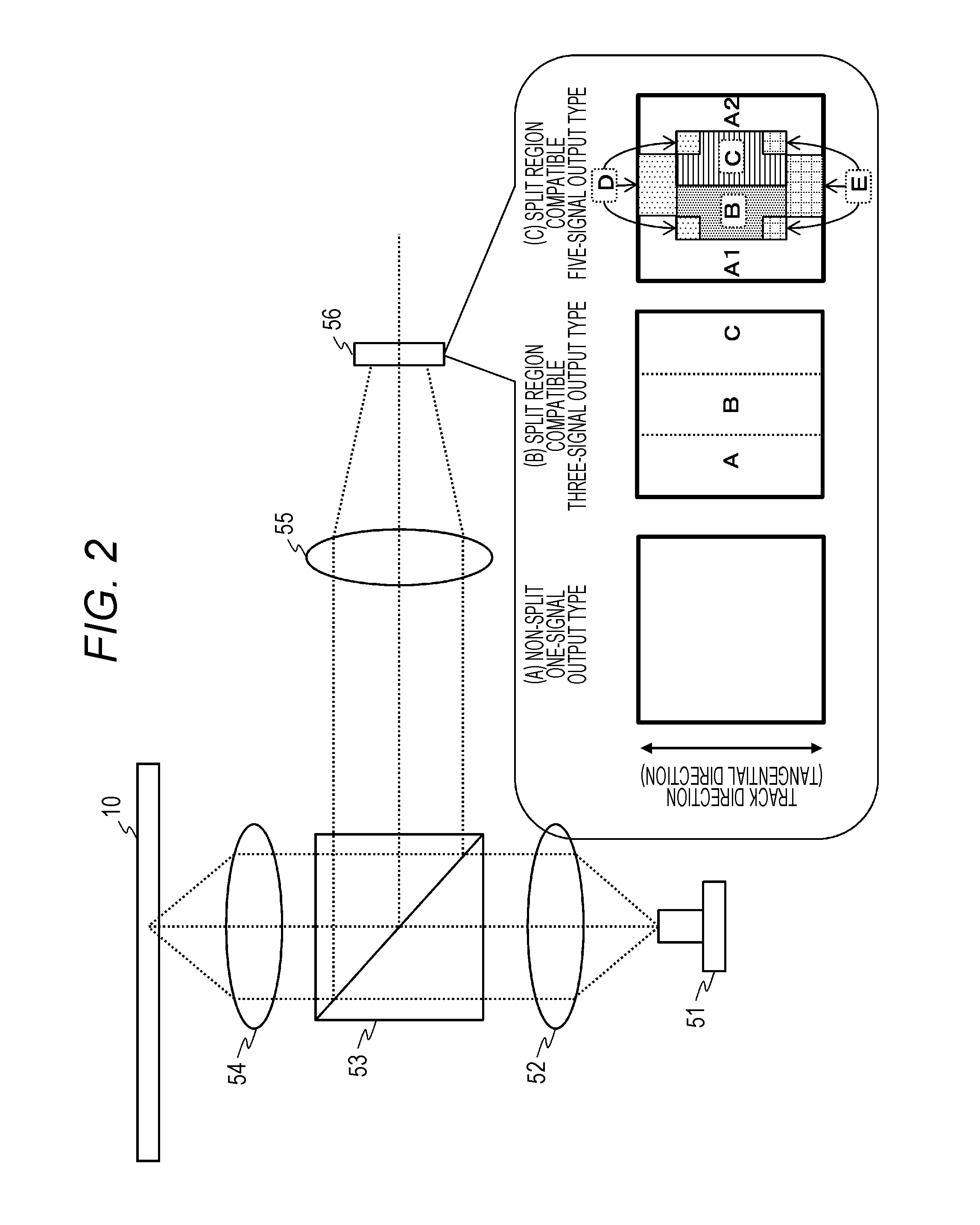

[0042] FIG. 2 is a diagram illustrating a configuration example of an optical pickup.

[0043] FIG. 3 is a diagram illustrating a configuration example of a split region compatible five-signal output type optical pickup.

[0044] FIG. 4 is a diagram illustrating a configuration example of a data detection processing unit.

[0045] FIG. 5 is a diagram illustrating an example of a multi-input adaptive equalizer.

[0046] FIG. 6 is a diagram illustrating an example of an adaptive equalizer unit.

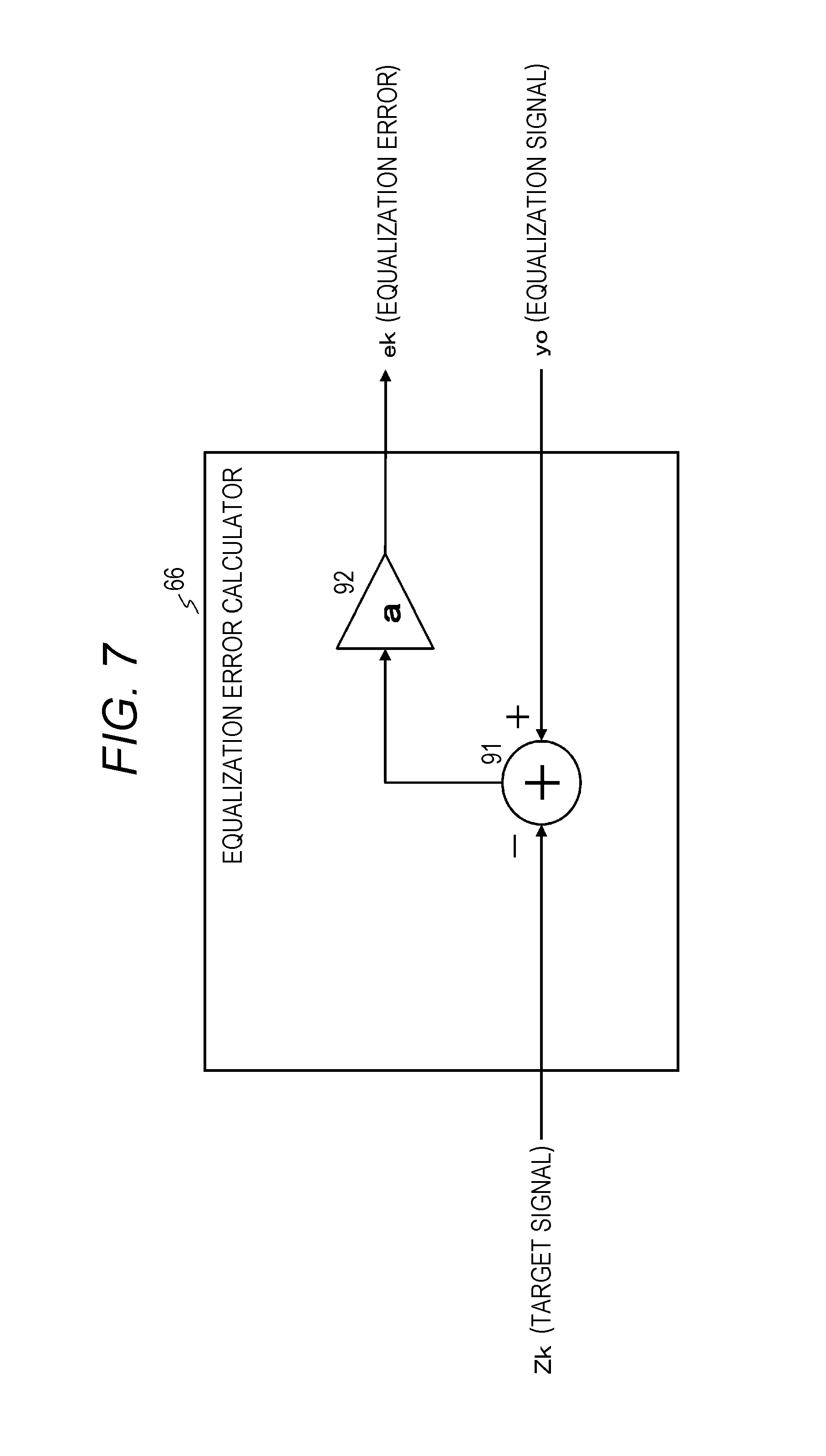

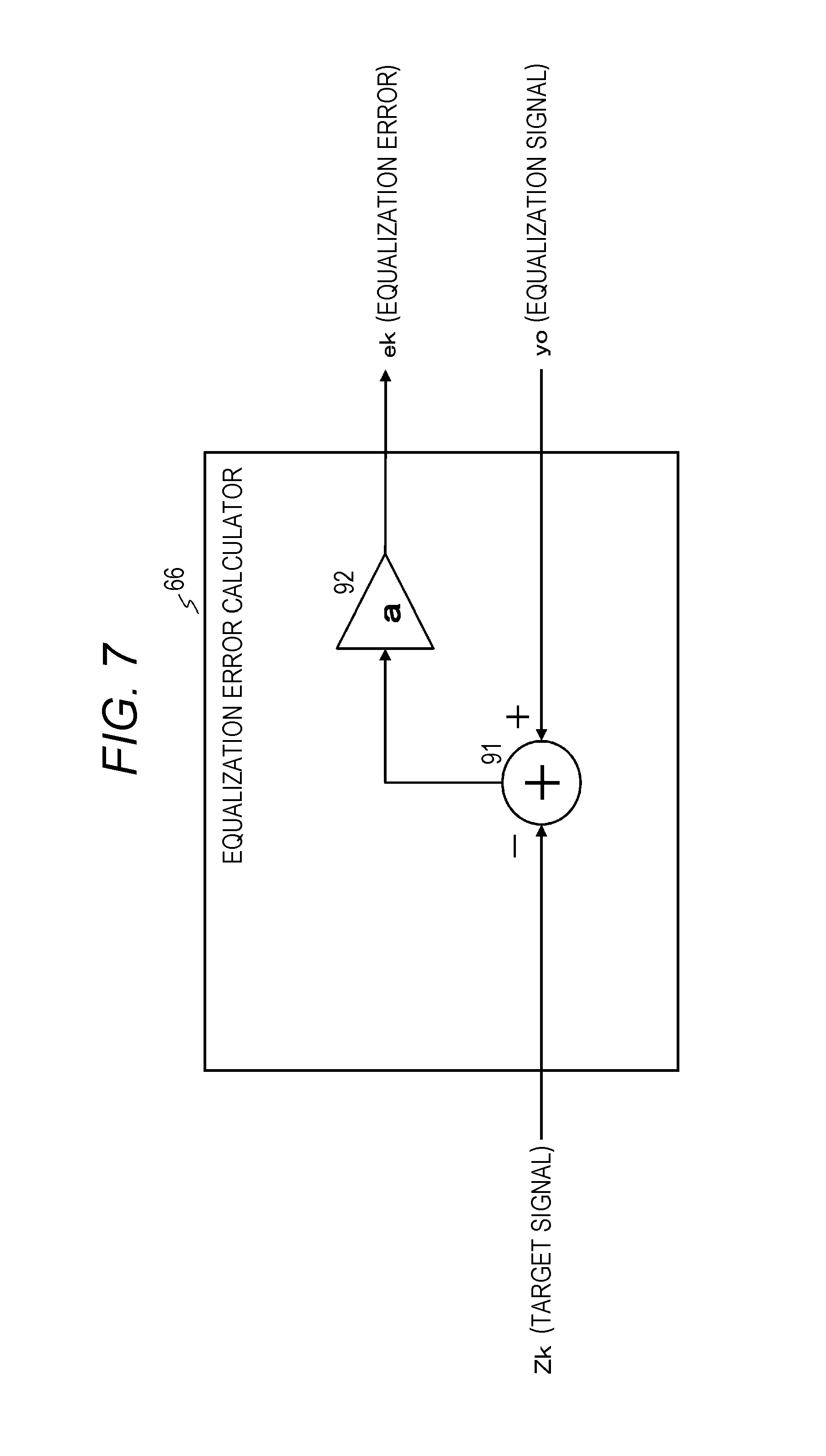

[0047] FIG. 7 is a diagram illustrating an example of equalization error calculator.

[0048] FIG. 8 is a diagram illustrating a configuration example of an information processing device (a reproducing device) that performs crosstalk cancellation using a read signal of an adjacent track.

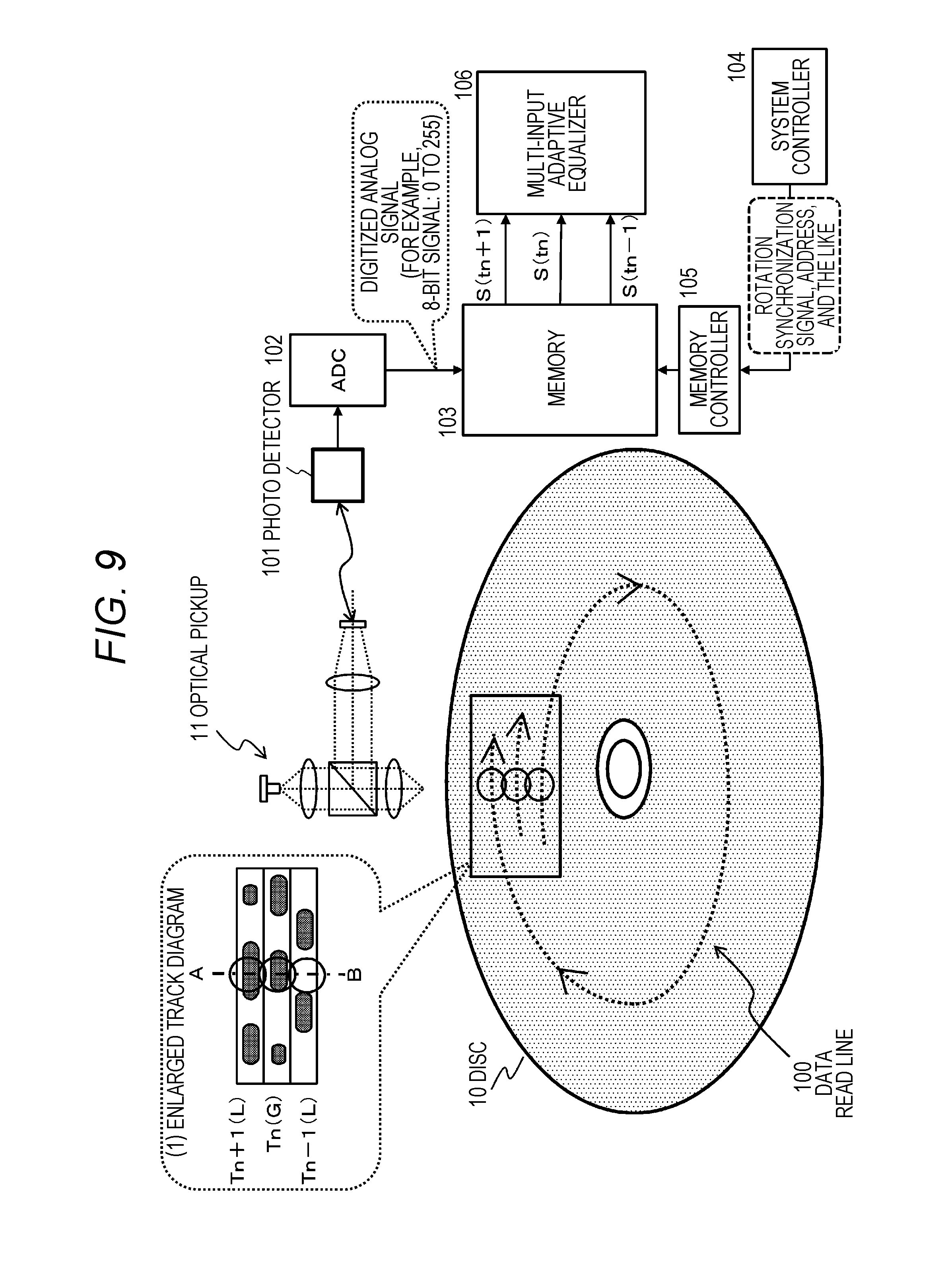

[0049] FIG. 9 is a diagram illustrating a configuration example of an information processing device (a reproducing device) that performs crosstalk cancellation using a read signal of an adjacent track.

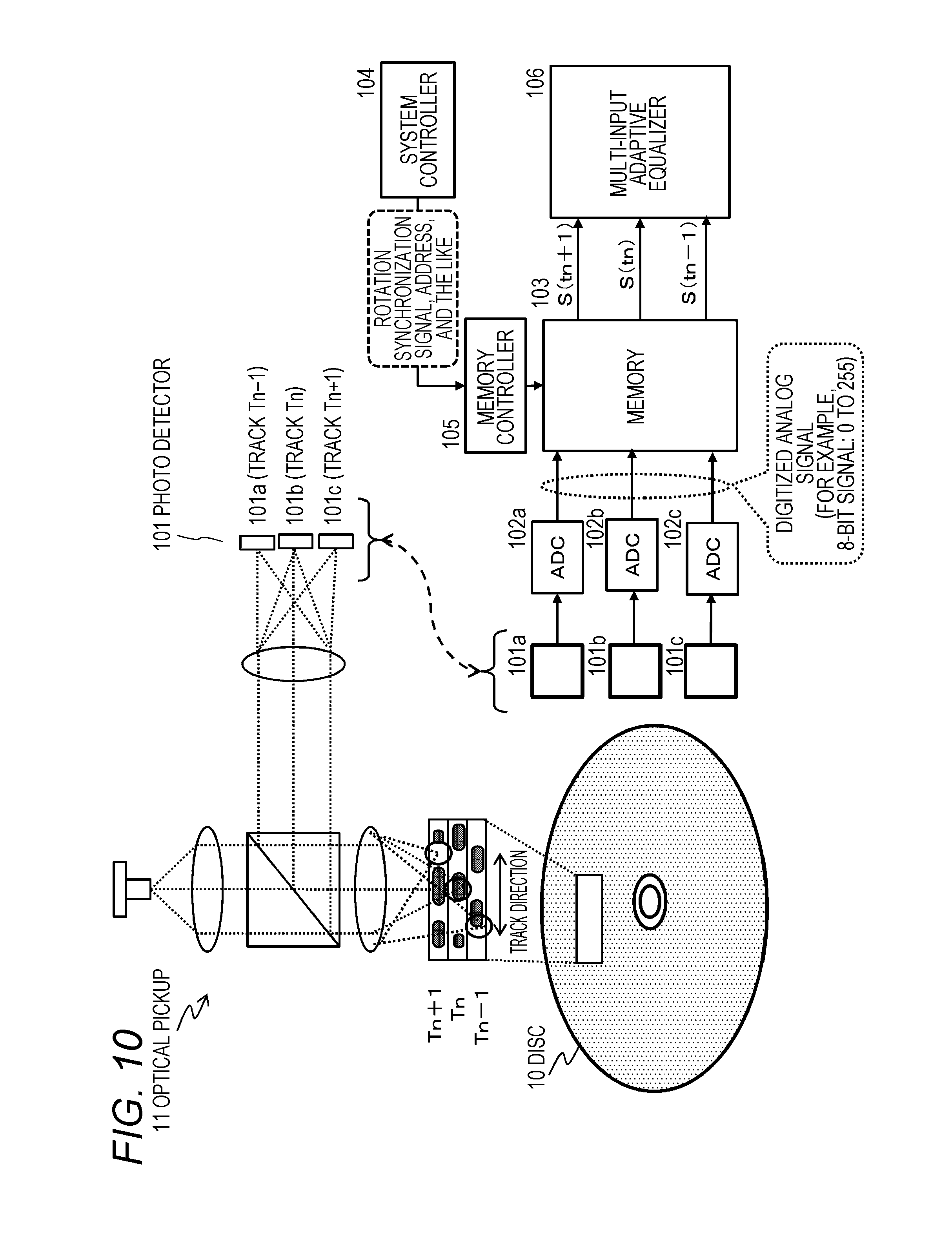

[0050] FIG. 10 is a diagram illustrating a configuration example of an information processing device (reproducing device) for performing crosstalk cancellation using a read signal of an adjacent track.

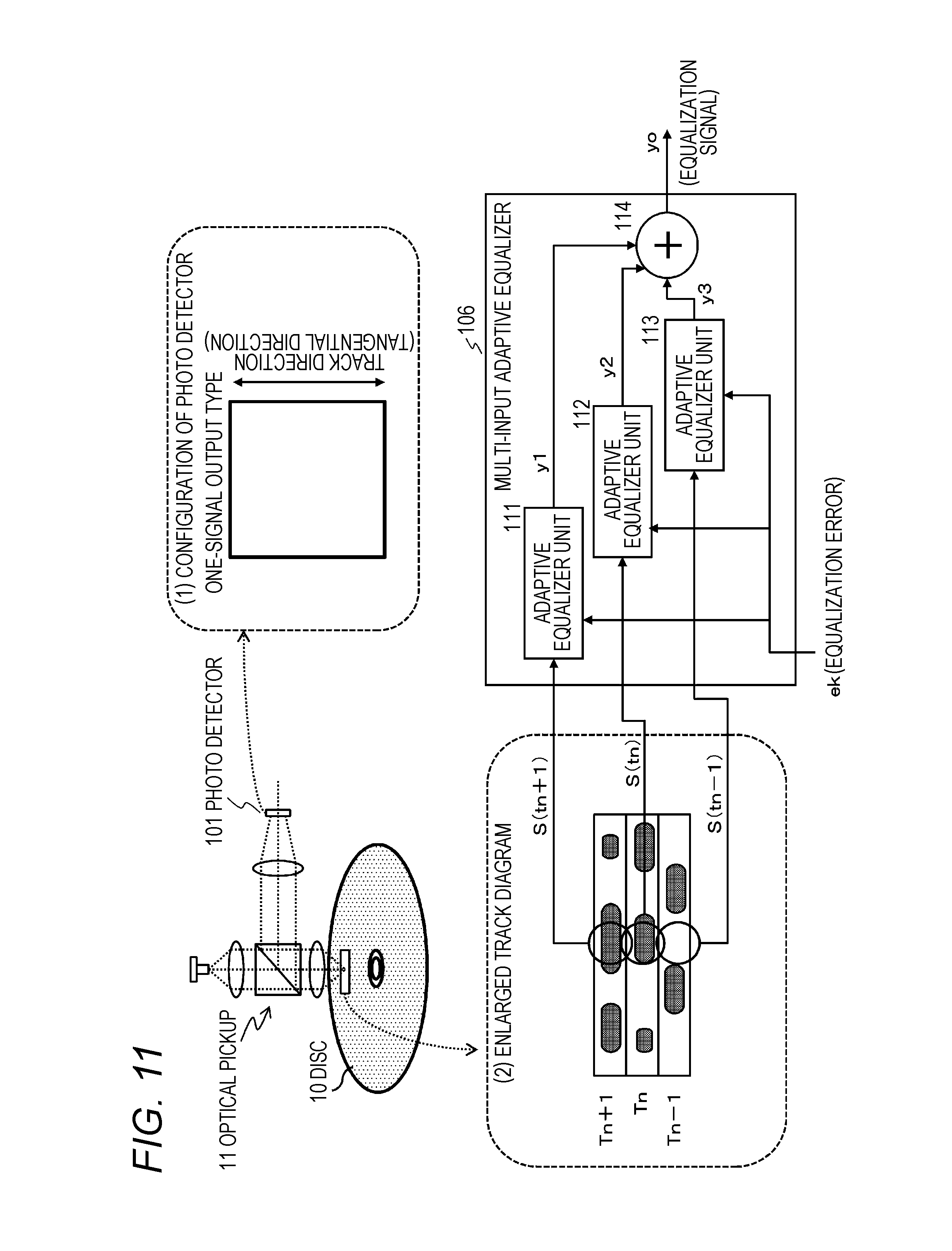

[0051] FIG. 11 is a diagram for describing a specific example of a multi-input adaptive equalizer of an information processing device (a reproducing device) that performs crosstalk cancellation using a read signal of an adjacent track.

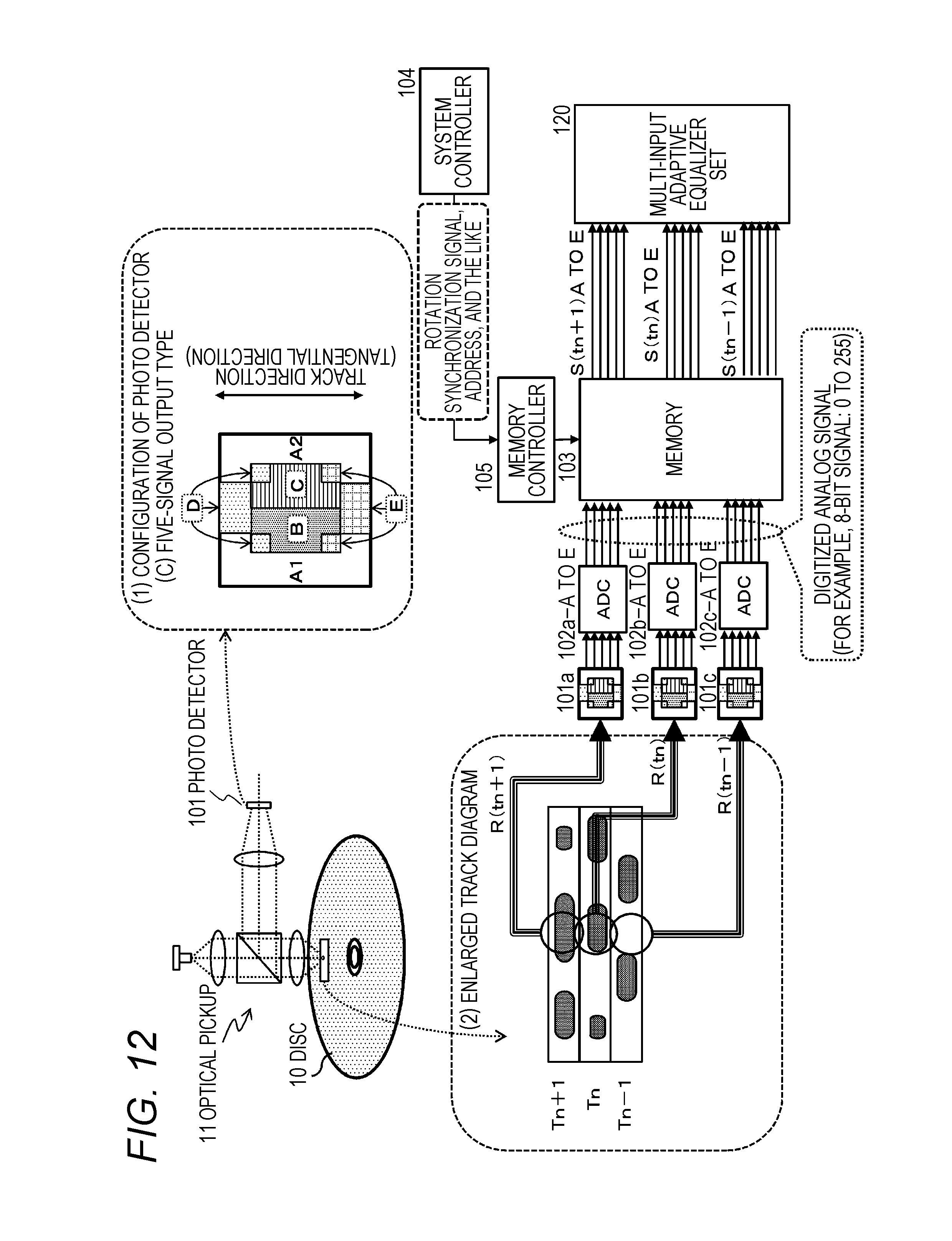

[0052] FIG. 12 is a diagram illustrating a configuration example of an information processing device (a reproducing device) that executes crosstalk cancellation by applying read data of an adjacent track using a five-signal output type photo detector.

[0053] FIG. 13 is a diagram illustrating an example of a multi-input adaptive equalizer set.

[0054] FIG. 14 is a diagram illustrating a configuration of each of multi-input adaptive equalizers 121 to 123.

[0055] FIG. 15 is a diagram for describing an overview of a configuration and a process of an information processing device that executes crosstalk cancellation using a binary reproduction signal (binary data) of an adjacent track.

[0056] FIG. 16 is a diagram illustrating a configuration of a multi-input adaptive equalizer 205 illustrated in FIG. 15.

[0057] FIGS. 17A and 17B illustrate an overview of a configuration and a process of an information processing device that executes crosstalk cancellation using a binary reproduction signal (binary data) of one adjacent track (Tn-1) adjacent to a current reproduction track (Tn).

[0058] FIG. 18 is a diagram illustrating a configuration of a multi-input adaptive equalizer 205 illustrated in FIG. 17.

[0059] FIG. 19 is a diagram for describing a configuration of an adjacent track reproduction binary signal supply unit that generates a reproduction binary signal (binary data) of one track (Tn-1) adjacent to a current reproduction track (Tn).

[0060] FIG. 20 is a diagram for describing a process example of a reproducing device that sets two irradiation spots and performs reproduction through two optical pickups 11a and 11b.

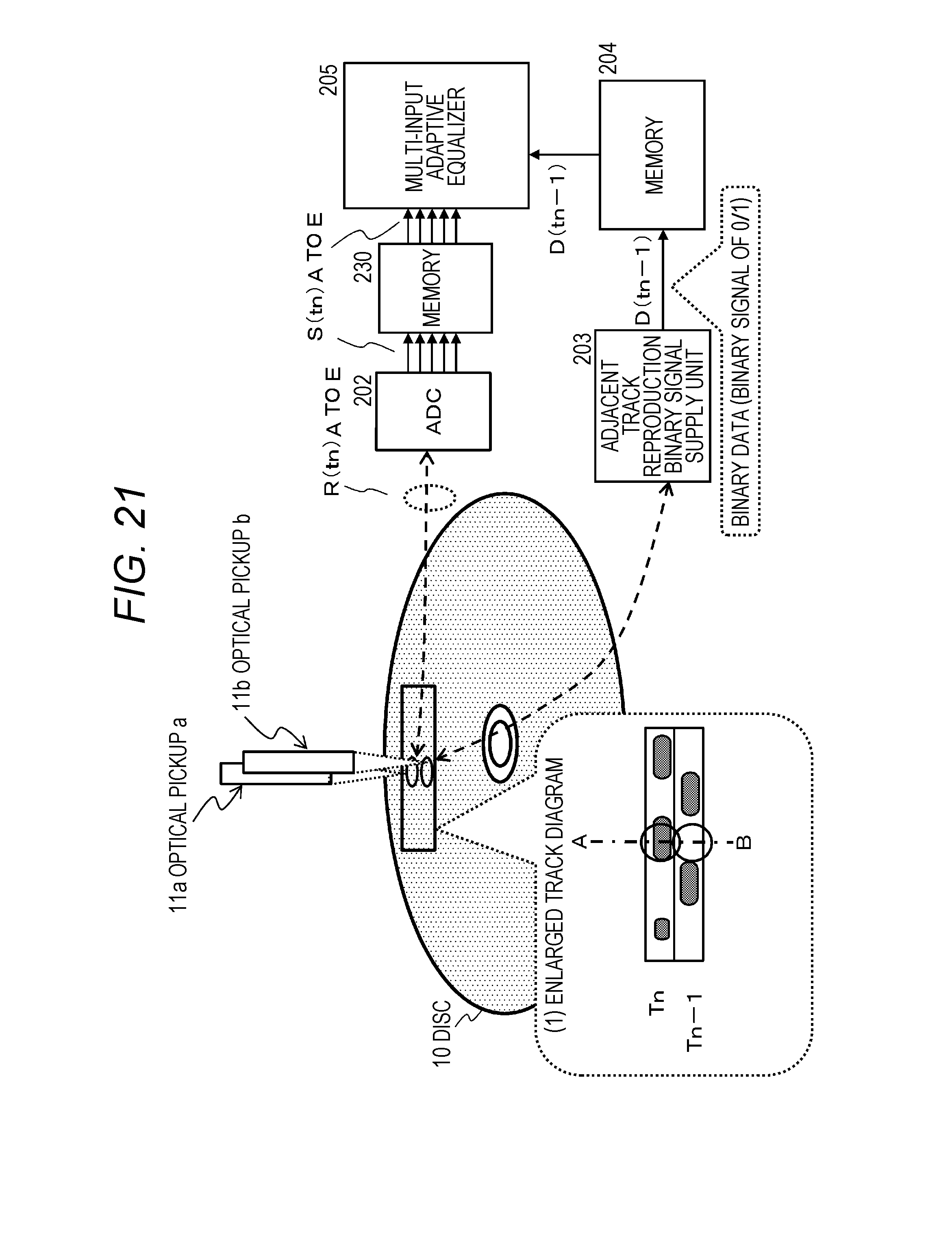

[0061] FIG. 21 is a diagram for describing a process example of a reproducing device that sets two irradiation spots and performs reproduction through two optical pickups 11a and 11b.

[0062] FIG. 22 is a diagram illustrating a configuration example of an information processing device in an example in which a reproduction signal of one adjacent track is applied.

[0063] FIG. 23 is a diagram for describing a configuration and a process of an information processing device (a reproducing device) in a case where a signal (binary data) recorded in a disc is known and stored in a record data storage memory.

[0064] FIG. 24 is a diagram illustrating a configuration example of an information processing device a (reproducing device) to which a memory 230 for controlling a timing at which a read signal of a current reproduction track (Tn) is input to a multi-input adaptive equalizer 205 is added.

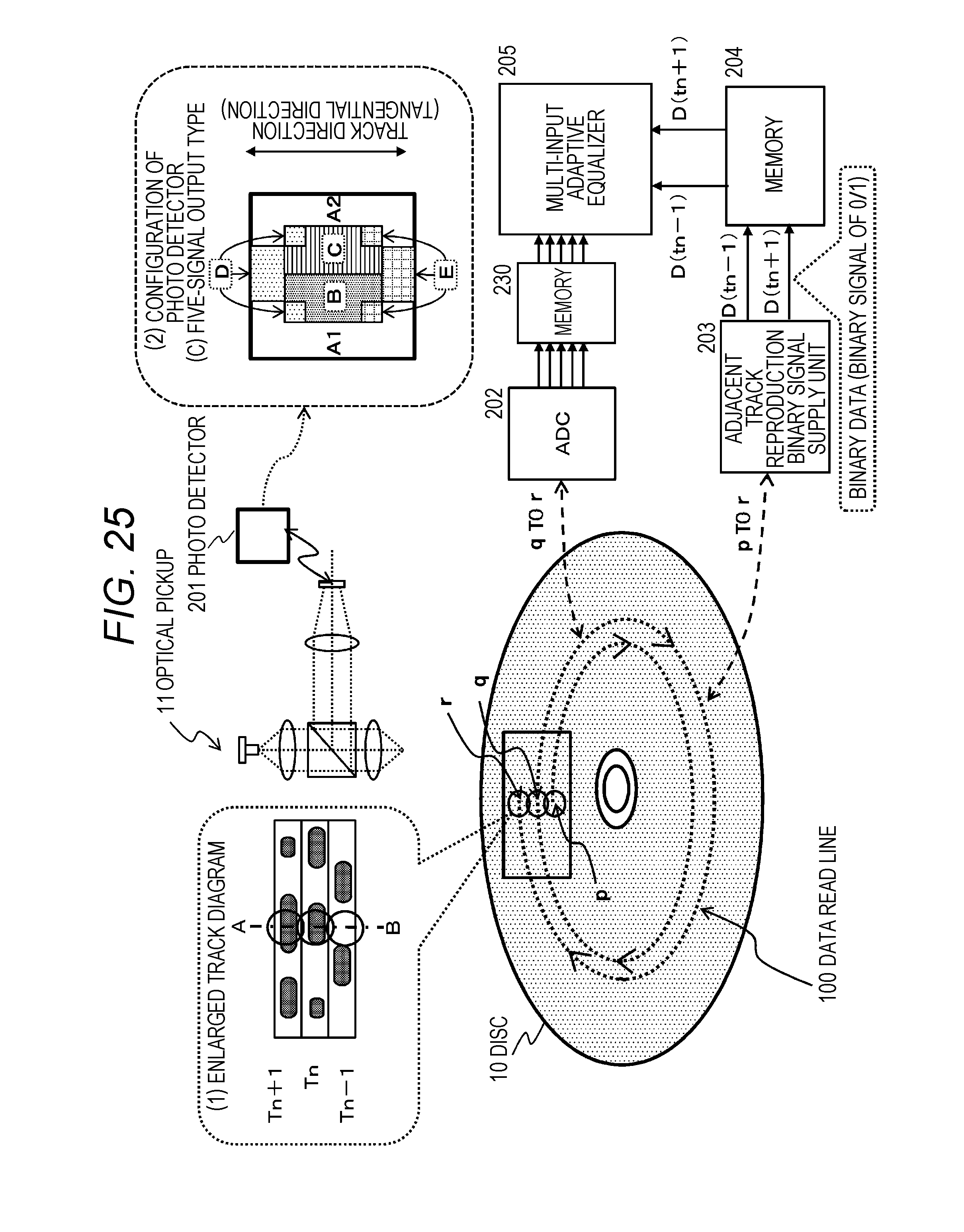

[0065] FIG. 25 is a diagram for describing a configuration of an adjacent track reproduction binary signal supply unit that generates reproduction binary signals (binary data) of two tracks adjacent to a current reproduction track (Tn).

[0066] FIG. 26 is a diagram for describing a process example of a reproducing device that sets three irradiation spots and performs reproduction through three optical pickups 11a to 11c.

[0067] FIG. 27 is a diagram for describing a process example of a reproducing device that sets three irradiation spots and performs reproduction through three optical pickups 11a to 11c.

[0068] FIG. 28 is a diagram for describing a configuration example of an information processing device in an example in which reproduction signals of two adjacent tracks are applied.

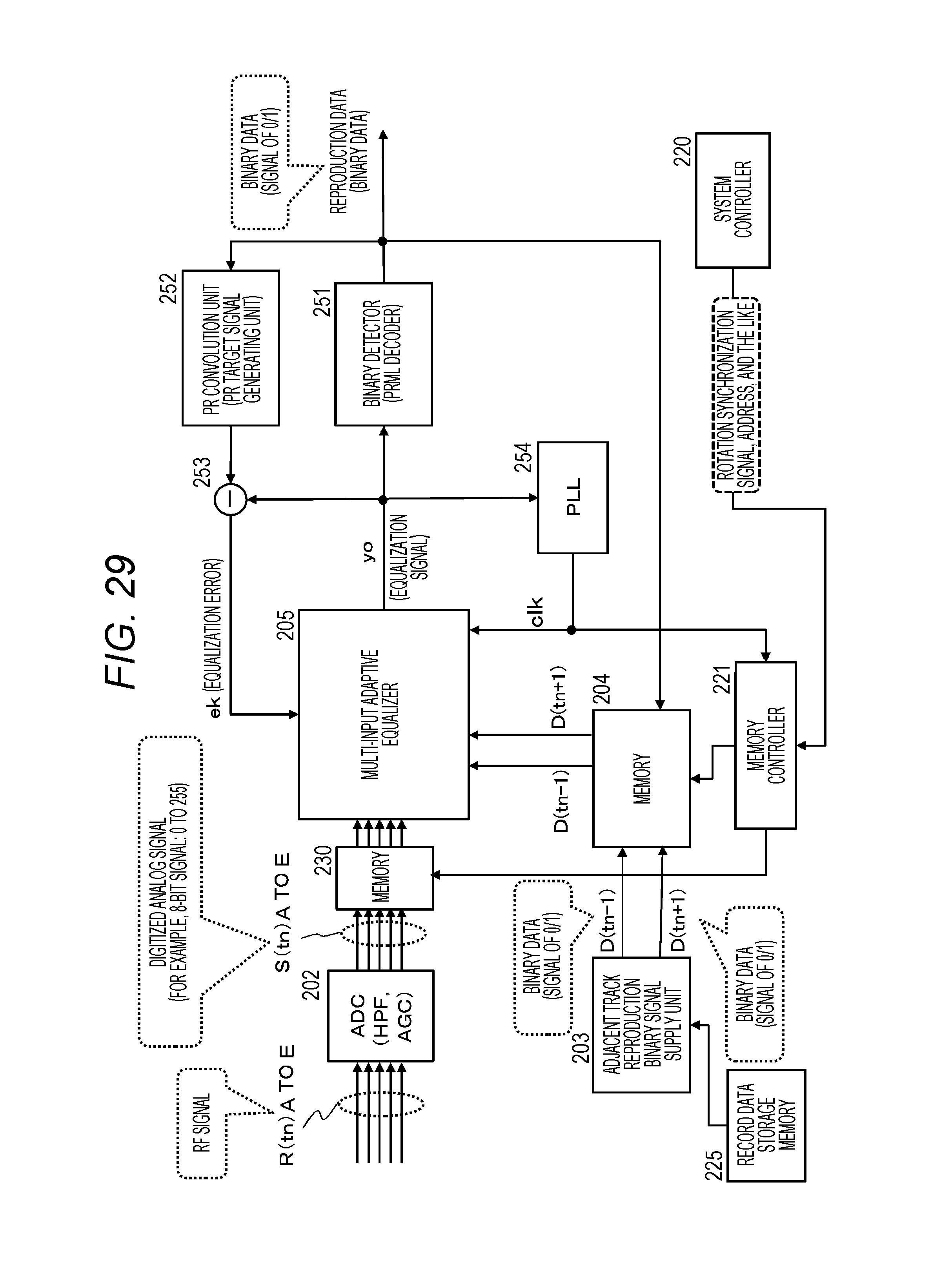

[0069] FIG. 29 is a diagram for describing a configuration and a process of an information processing device (a reproducing device) in a case where a signal (binary data) recorded in a disc is known and stored in a record data storage memory.

[0070] FIG. 30 is a diagram for describing a configuration of an information processing device that applies a reproduction signal of an adjacent track to a crosstalk cancellation processing and implements simultaneous reproduction of a plurality of tracks.

[0071] FIG. 31 is a diagram illustrating a configuration of a second multi-input adaptive equalizer 316.

[0072] FIG. 32 is a diagram illustrating a configuration of a second multi-input adaptive equalizer 326.

[0073] FIG. 33 is a diagram for describing a configuration of an information processing device that applies a reproduction signal of an adjacent track to a crosstalk cancellation processing and implements simultaneous reproduction of a plurality of tracks.

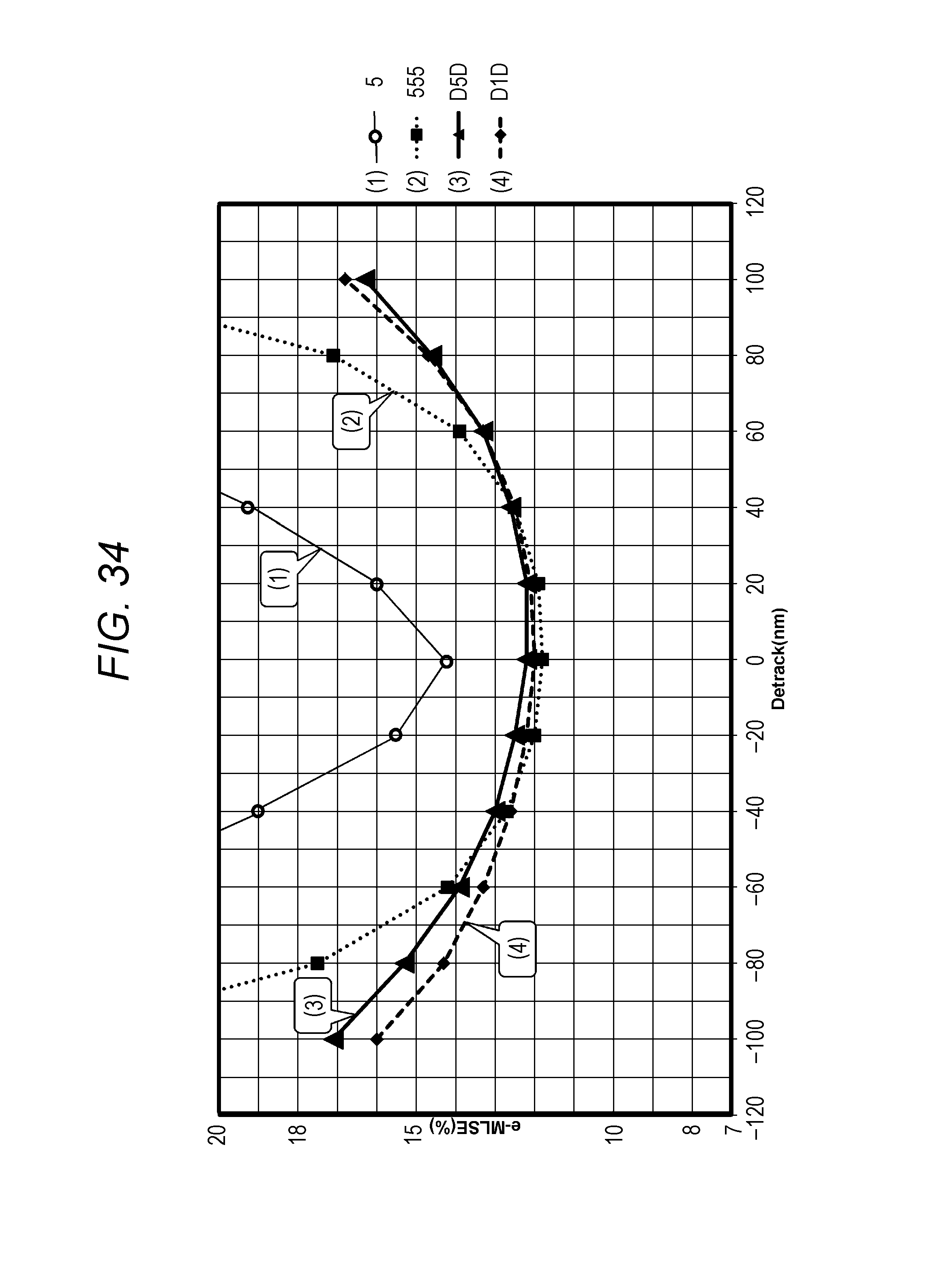

[0074] FIG. 34 is a diagram for describing quality evaluation data of reproduction data.

[0075] FIG. 35 is a diagram illustrating each data illustrated in FIG. 34.

[0076] FIG. 36 is a diagram for describing quality evaluation data of reproduction data.

[0077] FIG. 37 is a diagram illustrating each piece of data illustrated in FIG. 34.

MODE FOR CARRYING OUT THE INVENTION

[0078] Hereinafter, an information processing device, an information processing method, and a program according to the present disclosure will be described with reference to the appended drawings. Further, the description proceeds in accordance with the following items.

[0079] 1. Configuration and reproduction process example of information processing device

[0080] 1-1. Configuration example of optical pickup

[0081] 1-2. Configuration example of data detection processing unit

[0082] 2. Basic configuration example of crosstalk cancellation process using read signal of adjacent track

[0083] 3. Configuration and process of executing crosstalk cancellation using binary reproduction signal (binary data) of adjacent track

[0084] 3-1. Example in which reproduction signals of two adjacent tracks on both sides are applied

[0085] 3-2. Example in which reproduction signal of one adjacent track is applied

[0086] 3-3. Specific configuration example of adjacent track reproduction binary signal supply unit in example in which reproduction signal of one adjacent track is applied and configuration example of information processing device

[0087] 3-4. Specific configuration example of adjacent track reproduction binary signal supply unit in example in which reproduction signals of two adjacent tracks are applied and configuration example of information processing device

[0088] 3-5. Configuration example in which parallel reproduction process of plurality of tracks is executed

[0089] 4. Quality evaluation of reproduction signal using binary reproduction signal (binary data) of adjacent track

[0090] 5. Conclusion of configuration of present disclosure

[0091] [1. Configuration and Reproduction Process Example of Information Processing Device]

[0092] First, a configuration and a process example of an information processing device that executes a data recording/reproducing process to which an optical disc, for example, a Blu-ray (a registered trademark) disc (BD) is applied will be described.

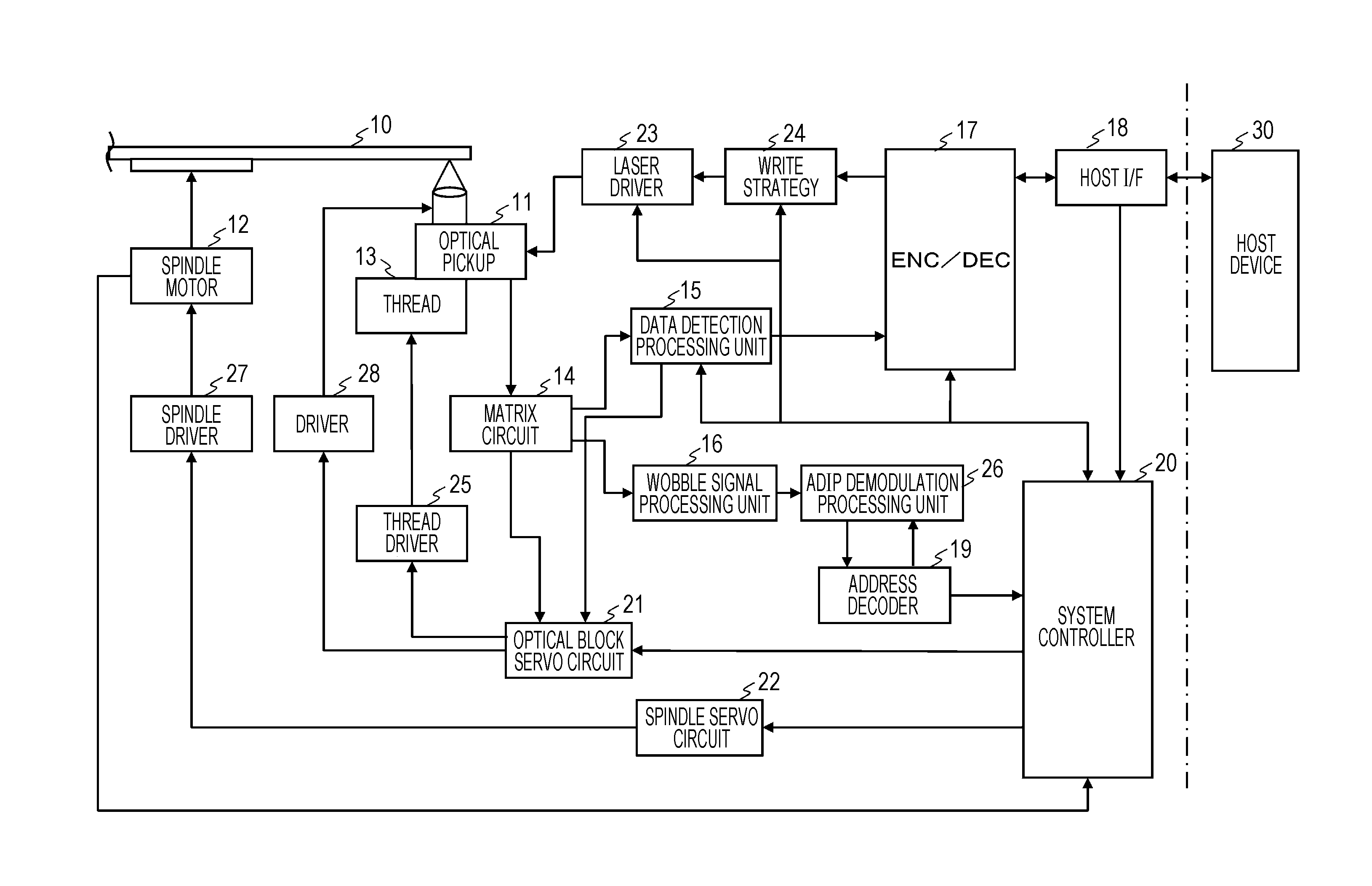

[0093] FIG. 1 is a block diagram illustrating a configuration example of an information processing device that executes a data reproducing process and a recording process on an optical disc 10.

[0094] As illustrated in FIG. 1, the information processing device includes an optical pickup 11 that records or reproduces information in or from the optical disc 10 serving as an optical recording medium and a spindle motor 12 that rotates the optical disc 10.

[0095] In order to move the optical pickup 11 in a radial direction of the optical disc 10, a thread (feed motor) 13 is installed.

[0096] The optical disc 10 is, for example, a high-density optical disc such as a Blu-ray (a registered trademark) disc (BD).

[0097] For example, the BD is a high-density optical disc having a recording capacity of about 25 GB in one layer on one side and about 50 GB in two layers on one side.

[0098] Further, in the BD standard, in order to reduce a beam spot diameter, a light source wavelength is set to 405 nm, and a numerical aperture NA of an objective lens is increased to 0.85. According to the BD standard, the spot diameter can be reduced to 0.58 .mu.m.

[0099] Further, in recent years, for the Blu-ray (a registered trademark) disc (BD), BDXL (a registered trademark) in which the channel bit length, that is, the mark length is reduced, the density is increased in the linear density direction, and a large capacity of 100 GB in three layers and 128 GB in 4 layers is implemented has been put into practical use.

[0100] Further, in order to increase the recording capacity, a method of recording data in both a groove track and a land track (a land/groove recording method) has been also employed.

[0101] Further, a groove set along the recording track of the disc is referred to as a groove (G), and a track formed by the groove is referred to as a groove track.

[0102] Further, an area serving as a mountain portion sandwiched between two grooves is referred to as a land (L), and a track formed by the land is referred to as a land track.

[0103] In the high-density recording type disc, data is recorded in either the groove (G) or the land (L). With this configuration, more data can be recorded in the disc.

[0104] However, in such a high-density recording disc, there is a problem that the crosstalk is highly likely to occur in the data reproducing process.

[0105] In other words, there is a problem that the crosstalk in which data of an adjacent track is mixed into readout data of a current readout track as noise is likely to occur.

[0106] If the optical disc 10 is loaded into the information processing device, it is rotationally driven at a constant linear velocity (CLV) or a constant angular velocity (CAV) by the spindle motor 12 at the time of recording/reproducing.

[0107] A CAV or a zone CAV is preferable in order to align a phase of a wobble groove uniform in a half radial direction of the optical disc 10.

[0108] At the time of reproducing, mark information recorded on a track on the optical disc 10 is read out by the optical pickup (optical head) 11.

[0109] At the time of data recording to the optical disc 10, the optical pickup 11 records user data on a track on the optical disc 10 as a change of a phase change mark, a dye change mark, or the like in brightness (reflectance) or a reflection phase (complex reflectance).

[0110] In the case of a recordable disc, a recording mark according to the phase change mark is recorded on the track formed by the wobbling groove, but the phase change mark is recorded with a linear density of 0.12 .mu.m/bit and 0.08 .mu.m/channel bit in the case of a BD of 23.3 GB per layer in accordance with a run length limited (RLL) (1, 7) parity preserve/prohibit repeated minimum transition run length (rmtr) (PP) modulation scheme or the like.

[0111] Similarly, the phase change mark is recorded with a density corresponding to a channel bit length depending on a disc type such as a linear density of 0.0745 .mu.m/channel bit in the case of a BD of 25 GB/layer, with a linear density of 0.05826 .mu.m/channel bit in the case of BDXL of 32 GB/layer, or a linear density of 0.05587 .mu.m/channel bit in the case of BDXL of 33.4 GB/layer.

[0112] If a channel clock cycle is indicated by "T," the mark length is 2T to 8T.

[0113] In the case of a read only disc, no groove is formed, but data modulated in accordance with the RLL (1, 7) PP modulation scheme is similarly recorded as an embossed pit sequence.

[0114] In an inner circumference area and the like of the optical disc 10, for example, physical information of a disc or the like is recorded by an embossed pit or a wobbling groove as reproduction-only management information.

[0115] Such information is also read out by the optical pickup 11.

[0116] Further, ADIP information embedded as a wobbling of the groove track on the optical disc 10 is also read by the optical pickup 11.

[0117] In the optical pickup 11, a laser diode serving as a laser beam source, a photo detector for detecting reflected light, an objective lens serving as a laser beam output end, and an optical system that irradiates a disc recording surface with laser beams through the objective lens and guides the reflected light to the photodetector, and the like are configured.

[0118] In the optical pickup 11, the objective lens is held to be movable in a tracking direction and a focus direction by a two-axis mechanism.

[0119] The entire optical pickup 11 is movable in the half radial direction of the disc by the thread mechanism 13.

[0120] A driving current from a laser driver 23 is supplied to the laser diode of the optical pickup 11, and the laser diode generates a laser.

[0121] The reflected light from the optical disc 10 is detected by the photo detector, and converted into an electric signal corresponding to an amount of received light, and the electric signal is supplied to a matrix circuit 14.

[0122] The matrix circuit 14 includes a current voltage conversion circuit, a matrix calculation/amplification circuit, and the like are provided corresponding to output currents from a plurality of light receiving elements serving as the photo detectors, and generates a necessary signal through a matrix calculation process.

[0123] A current-voltage conversion circuit may be formed in the photo detector element in view of a signal transmission quality.

[0124] For example, a reproduction information signal (RF signal) corresponding to reproduction data, a focus error signal for servo control, a tracking error signal, and the like are generated.

[0125] Further, a signal related to wobbling of a groove, that is, a push-pull signal is generated as a signal for detecting the wobbling.

[0126] The reproduction information signal output from the matrix circuit 14 is supplied to a data detection processing unit 15, the focus error signal and the tracking error signal are supplied to an optical block servo circuit 21, and the push-pull signal is supplied to a wobble signal processing unit 16.

[0127] The data detection processing unit 15 performs a binarization process of the reproduction information signal.

[0128] For example, the data detection processing unit 15 performs an A/D conversion process of the RF signal, a reproduction clock generation process by a PLL, a partial response (PR) equalization process, Viterbi decoding (maximum likelihood decoding), and the like, and obtains a binary data string through a partial response maximum likelihood decoding process (a PRML detection scheme).

[0129] The data detection processing unit 15 supplies a binary data string serving as information read from the optical disc 10 to an encoding/decoding unit 17 at a subsequent stage.

[0130] The encoding/decoding unit 17 performs demodulation of the reproduction data at the time of reproducing and performs a modulation process of the record data at the time of recording.

[0131] In other words, the encoding/decoding unit 17 performs data demodulation, deinterleaving, ECC decoding, address decoding, and the like at the time of reproducing, and performs ECC encoding, interleaving, data modulation, and the like at the time of recording.

[0132] At the time of reproducing, the binary data string decoded by the data detection processing unit 15 is supplied to the encoding/decoding unit 17.

[0133] The encoding/decoding unit 17 performs the demodulation process on the binary data string and obtains the reproduction data from optical disc 10.

[0134] For example, the encoding/decoding unit 17 performs the demodulation process on the data which is recorded on the optical disc 10 by performing the run-length limited code modulation such as the RLL (1, 7) PP modulation, performs the ECC decoding process for the error correction, and obtains the reproduction data from the optical disc 10.

[0135] The data decoded up to reproduction data by the encoding/decoding unit 17 is transferred to a host interface 18 and transferred to a host device 30 on the basis of an instruction of a system controller 20.

[0136] The host device 30 is, for example, a computer device, an audio-visual (AV) system device, or the like.

[0137] At the time of recording/reproducing for the optical disc 10, processing of ADIP information is performed.

[0138] In other words, the push-pull signal output from the matrix circuit 14 as the signal related to the groove wobbling is converted into wobble data digitalized in a wobble signal processing circuit 16.

[0139] A clock synchronized with the push-pull signal is generated by the PLL process.

[0140] An ADIP demodulation processing unit 26 demodulates the wobble data into a data stream constituting an ADIP address, and the data stream is supplied to an address decoder 19.

[0141] The address decoder 19 decodes the supplied data, obtains an address value, and supplies the address value to the system controller 20.

[0142] At the time of recording, the record data is transferred from the host device 30, and the record data is supplied to the encoding/decoding unit 17 via the host interface 18.

[0143] The encoding/decoding unit 17 performs addition error correction code addition (ECC encoding), interleaving, sub code addition, and the like as the encoding process of the record data.

[0144] The run-length limited code modulation such as the RLL (1-7) PP scheme is performed on the processed data.

[0145] The record data processed by the encoding/decoding unit 17 is supplied to a write strategy unit 24.

[0146] The write strategy unit 24 performs a laser driving pulse waveform adjustment on a characteristic of a recording layer, a spot shape of the laser beams, a recording linear velocity, and the like as a recording compensation process.

[0147] Then, the laser driving pulse is output to the laser driver 23.

[0148] The laser driver 23 causes a current to flow through the laser diode in the optical pickup 11 on the basis of the laser drive pulse which has undergone the recording compensation process, and performs laser emission.

[0149] Accordingly, a mark corresponding to the record data is formed on the optical disc 10.

[0150] The optical block servo circuit 21 generates various servo drive signals of focus, tracking, and thread from the focus error signal and the tracking error signal from the matrix circuit 14 and execute the servo operation.

[0151] In other words, the optical block servo circuit 21 generates the focus drive signal and the tracking drive signal in accordance with the focus error signal and the tracking error signal, and drives a focus coil and a tracking coil of the two-axis mechanism in the optical pickup 11 through a driver 28.

[0152] Accordingly, a tracking servo loop and a focus servo loop by the optical pickup 11, the matrix circuit 14, the optical block servo circuit 21, the driver 28, the two-axis mechanism are formed.

[0153] Further, the optical block servo circuit 21 executes a track jump operation by turning off the tracking servo loop in accordance with a track jump command from the system controller 20 and outputting a jump drive signal.

[0154] Further, the optical block servo circuit 21 generates a thread drive signal on the basis of the thread error signal obtained as a low frequency component of the tracking error signal, access execution control from the system controller 20, and the like, and drives the thread mechanism 13 through a thread driver 25.

[0155] A spindle servo circuit 22 performs control such that the spindle motor 12 performs CLV rotation or CAV rotation.

[0156] The spindle servo circuit 22 obtains the clock generated by the PLL for the wobble signal as current rotating speed information of the spindle motor 12, compares the clock with predetermined reference speed information, and generate a spindle error signal.

[0157] Further, at the time of data reproduction, since a reproduction clock generated by the PLL in the data detection processing unit 15 is the current rotating speed information of the spindle motor 12, it is compared with the predetermined reference speed information, and the spindle error signal is generated.

[0158] Then, the spindle servo circuit 22 outputs the spindle drive signal generated in accordance with the spindle error signal, and executes the CLV rotation or the CAV rotation of the spindle motor 12 through a spindle driver 27.

[0159] The spindle servo circuit 22 generates the spindle drive signal in accordance with a spindle kick/brake control signal from the system controller 20, and also performs operations of, for example, starting, stopping, accelerating, and decelerating the spindle motor 12.

[0160] Various kinds of operations of the servo system and the recording/reproducing system described above are controlled by the system controller 20 constituted by a microcomputer.

[0161] The system controller 20 executes various kinds of processes in accordance with a command given from the host device 30 via the host interface 18.

[0162] For example, if a write command is issued from the host device 30, the system controller 20 first moves the optical pickup 11 to an address at which writing is performed.

[0163] Then, the encoding/decoding unit 17 executes an encoding process on data (for example, video data, audio data, or the like) transferred from the host device 30 as described above.

[0164] Then, the laser driver 23 drives the laser emission and performs the recording in accordance with the encoded data.

[0165] Further, for example, in a case where a read command for requesting transfer of certain data recorded on the optical disc 10 is supplied from the host device 30, the system controller 20 first performs seek operation control on the instructed address.

[0166] In other words, the command is issued to the optical block servo circuit 21, and an access operation of the optical pickup 11 on an address specified by the seek command as is executed.

[0167] Thereafter, operation control necessary for transferring data of an instructed data section to the host device 30 is performed.

[0168] In other words, reading of data from the optical disc 10 is performed, a reproduction process in the data detection processing unit 15 and the encoding/decoding unit 17 is executed, and requested data is transferred.

[0169] Further, the example of FIG. 1 has been described as an optical disc device connected to the host device 30, but the optical disc device may not be connected to other devices.

[0170] In this case, a manipulating unit and a display unit are provided, and a configuration of an interface part of data input/output is different from that in FIG. 1.

[0171] In other words, recording or reproduction is performed in accordance with a manipulation of the user, and a terminal portion for input and output of various kinds of data are formed.

[0172] Of course, various configurations can be considered as a configuration example of the optical disc device.

[0173] [1-1. Configuration Example of Optical Pickup]

[0174] Next, a specific configuration example of the optical pickup 11 used for the optical disc device will be described with reference to FIG. 2.

[0175] The optical pickup 11 records information on the optical disc 10, for example, using laser beams having a wavelength .lamda. of 405 nm, and reproduces information from the optical disc 10.

[0176] The laser beams are emitted from a semiconductor laser (a laser diode (LD)) 51.

[0177] The laser beams pass through an collimator lens 52, a polarizing beam splitter (PBS) 53, and an objective lens 54 and are irradiated to the optical disc 10.

[0178] The polarizing beam splitter 53 has, for example, a splitting surface that transmits approximately 100% of P polarized light and reflects approximately 100% of S polarized light.

[0179] The reflected light from the recording layer of the optical disc 10 returns to the same optical path and enters the polarizing beam splitter 53.

[0180] A .lamda./4 element (not illustrated) is interposed, and approximately 100% of the incident laser beams are reflected by the polarizing beam splitter 53.

[0181] The laser beams reflected by the polarizing beam splitter 53 are converged onto a light receiving surface of a photo detector 56 via a lens 55.

[0182] The photo detector 56 includes a light receiving cell which is installed on the light receiving surface and performs photoelectric conversion on the incident light.

[0183] There are various types of photo detector 56 as illustrated in FIG. 2. FIG. 2 illustrates an example of the following three types:

[0184] (A) a non-split one-signal output type;

[0185] (B) a split region compatible three-signal output type; and

[0186] (C) a split region compatible five-signal output type.

[0187] (A) The non-split one-signal output type outputs one electric signal corresponding to an amount of light received by the light receiving cell on the entire surface of the photo detector 56.

[0188] (B) The split region compatible three-signal output type is constituted by light receiving cells obtained by dividing the light receiving surface of the photo detector 56, and outputs three electric signals corresponding to an amount of light received by the light receiving cells of the respective split regions.

[0189] (C) The split region compatible five-signal output type is also constituted by light receiving cells obtained by dividing the light receiving surface of the photo detector 56, and outputs five electric signals corresponding to an amount of light received by the light receiving cells of the respective split regions.

[0190] The light receiving cells of (B) the split region compatible three-signal output type and (C) the split region compatible five-signal output type are divided into a plurality of regions by a dividing line extending in a radial direction (disc radial direction) and a tangential direction (track direction) of the optical disc 10.

[0191] The split type photo detector 56 outputs electric signals of a plurality of channels in accordance with the amount of received light of each region of the light receiving cell.

[0192] Further, the split configuration can have various configurations in addition to the configurations described above.

[0193] FIG. 3 illustrates a detailed configuration of (C) the split region compatible five-signal output type photo detector 56 illustrated in FIG. 2.

[0194] As illustrated in FIG. 3, the photo detector 56 is constituted by light receiving cells divided into a plurality of regions.

[0195] In the example illustrated in FIG. 3, it is divided into regions A1, A2, B, C, D1, D2, D3, E1, E2, and E3. In each split region, each electric signal corresponding to the amount of received light is output individually.

[0196] However, signals applied to the generation of the reproduction signal are the following five signals corresponding to five channels.

[0197] a signal A=A1+A2

[0198] a signal B=B

[0199] a signal C=C

[0200] a signal D=D1+D2+D3

[0201] a signal E=E1+E2+E3

[0202] The reproduction signal is generated using the five signals.

[0203] Further, a signal including addition signals of a plurality of regions may be configured to generate a signal by multiplying by a weight coefficient of a preset region unit.

[0204] For example, an output signal may be generated by multiplying the following weight coefficients p and q:

A=p*A1+q*A2

[0205] Using such split type photo detector, it is possible to obtain a high-quality reproduction signal by performing an adaptive equalization process on each signal using multi-input adaptive equalizer.

[0206] The adaptive equalization process configuration using the multi-input adaptive equalizer will be described later.

[0207] Each of signals A to E is a characteristic signal corresponding to a light receiving region such as a signal in which a signal component of a current read track is large or a signal in which a ratio of an adjacent track in the crosstalk is high. A high-quality reproduction signal can be obtained by executing the adaptive equalization process in accordance with a characteristic of each signal.

[0208] Further, the generation process configuration of the reproduction signal using the split type photo detector is disclosed in Patent Document 1 (International Publication No. WO 2016/006157) which is a prior application filed by the present applicant.

[0209] The multi-signal output type photo detector used in the present disclosure has a similar configuration to that in disclosed in the publication, and setting of a plurality of signals output from the photo detector and a configuration and a process of inputting each of a plurality of signals to the multi-input adaptive equalizer and obtaining an equalization signal and a binary signal are similarly applied even in the present disclosure.

[0210] Further, the configuration of the optical pickup 11 illustrated in FIG. 2 indicates the minimum constituent elements for describing the present disclosure, and the focus error signal and the tracking error signal output to the optical block servo circuit 21 via the matrix circuit 14, the signal for generating the push-pull signal output to the wobble signal processing circuit 16 via the matrix circuit 14, and the like are omitted.

[0211] Further, various configurations other than the configuration illustrated in FIG. 2 are possible.

[0212] Further, an embodiment of the present disclosure to be described below will be mainly described as an example using the split region-compatible five-signal output type photo detector described above with reference to FIG. 3.

[0213] However, the present disclosure processing is not limited to the split region compatible five-signal output type photo detector described with reference to FIG. 3 but can also be applied to the non-split one-signal output type illustrated in FIG. 2, the split region compatible three-signal output type, other configurations using photo detectors having different division configurations can be also applied.

[0214] In a case where the split type photo detector such as the split region compatible three-signal output type photo detector or the split region compatible five-signal output type photo detector is used, it is possible to divide luminous flux of return beams from the optical disc 10 into a plurality of regions and obtain the reproduction information signals of a plurality of channels corresponding to the respective regions.

[0215] The high-quality reproduction signal can be obtained through data processing using the signals of the region units.

[0216] Further, as a method of obtaining the reproduction information signal for each region, a method other than the method of dividing the photo detector 56 can also be used.

[0217] For example, a method in which, in the optical pickup 11 illustrated in FIG. 2, an optical path conversion element for separating a plurality of regions is arranged in an optical path passing through the objective lens 54 and reaching the photo detector 56, and a plurality of beams separated by the optical path conversion element are supplied to different photo detector may be used.

[0218] As the optical path conversion element, a diffraction element such as a holographic optical element, a refraction element such as a micro lens array or a micro prism, or the like can be used.

[0219] [1-2. Configuration Example of Data Detection Processing Unit]

[0220] Next, a configuration example of the data detection processing unit 15 in the configuration illustrated in FIG. 1 will be described with reference to FIG. 4.

[0221] As described above, the detection signals corresponding to the respective regions which are reproduced from the optical disc 10 by the optical pickup 11 are supplied to the matrix circuit 14 and converted into the reproduction information signals of a plurality of channels corresponding to the respective regions.

[0222] As illustrated in FIG. 4, the data detection processing unit 15 includes an A/D converter 61 to which the reproduction information signals supplied from the matrix circuit 14 are supplied.

[0223] Further, FIG. 4 illustrates a configuration example of the data detection processing unit 15 that receives the five signals A to E obtained by using the split region compatible five-signal output type photo detector 56 illustrated in FIG. 3 and generates the reproduction signals.

[0224] A clock for the A/D converter 61 is formed by a PLL 62. The reproduction information signals supplied from the matrix circuit 14 are converted into digital data by the A/D converter 61.

[0225] The reproduction information signals of the five channels obtained by digitizing the signals A to E are indicated by Sa to Se.

[0226] A signals obtained by adding the reproduction information signals Sa to Se by an addition circuit 67 is supplied to the PLL 62.

[0227] Further, the signals A to E are the following electric signals corresponding to the amount of received light of the regions described above with reference to FIG. 3.

[0228] the signal A=A1+A2

[0229] the signal B=B

[0230] the signal C=C

[0231] the signal D=D1+D2+D3

[0232] the signal E=E1+E2+E3

[0233] As illustrated in FIG. 4, the data detection processing unit 15 includes a multi-input adaptive equalizer 63, a binary detector 64, a pertial response (PR) convolution unit 65, and an equalization error calculator 66.

[0234] The multi-input adaptive equalizer 63 performs a PR adaptive equalization process on the basis of the reproduction information signals Sa to Se.

[0235] In other words, the reproduction information signals Sa to Se are output via the adaptive equalizer unit, and an added equalization signal y0 is equalized to approximate a desired PR waveform.

[0236] Further, an output of the multi-input adaptive equalizer may be used as the signal input to the PLL 62. In this case, an initial coefficient of the multi-input adaptive equalizer is set to a predetermined value.

[0237] The binary detector 64 is, for example, a Viterbi decoder, and obtains binary data DT by performing the maximum likelihood decoding process on the PR equalized equalization signal y0.

[0238] The binary data DT is supplied to the encoding/decoding unit 17 illustrated in FIG. 1, and undergoes a reproduction data demodulation process.

[0239] For Viterbi decoding, a Viterbi detector constituted by a plurality of states configured using consecutive bits of a predetermined length as units and branches indicated by transitions therebetween is used, and it is configured to detect a desired bit sequence efficiently from all possible bit sequences.

[0240] Two registers, that is, a register that stores a partial response sequence which is called a path metric register and reaches up to each state and a path metric of signal for each state and a register that stores a flow of a bit sequence which is called a path memory register and reaches the state are prepared in an actual circuit.

[0241] Further, a calculation unit that calculates a partial response sequence which is called a branch metric unit and a path metric of a signal for each branch is prepared.

[0242] In the Viterbi decoder, it is possible to associate various bit sequences with each other with a one-to-one relation using one of paths passing through states.

[0243] Further, the path metric between the partial response sequence passing through the paths and the actual signal (reproduction signal) is obtained by sequentially adding the branch metric in the inter-state transition constituting the path, that is, the branch.

[0244] Further, selection of a path in which the path metric is minimized can be implemented by sequentially selecting the paths with the small path metrics while comparing the magnitudes of the path metrics of two or less branches reaching each state.

[0245] The selection information is transferred to the path memory register, and information indicating the path reaching each state with the bit sequence is stored.

[0246] Since a value of the path memory register converges onto a bit sequence which eventually minimizes the path metric while being sequentially updated, the result is output.

[0247] In the PR convolution unit 65, the convolution process of the binarization result is performed to generate a target signal Zk.

[0248] Since the target signal Zk is an ideal signal having no noise since the binary detection result is convoluted.

[0249] For example, in the case of PR (1, 2, 2, 2, 1), a value P of each channel clock is (1, 2, 2, 2, 1). A constraint length is 5.

[0250] Further, in the case of PR (1, 2, 3, 3, 3, 2, 1), the value P of each channel clock is (1, 2, 3, 3, 3, 2, 1). The constraint length is 7.

[0251] In a case where the recording density is increased to the extent that the capacity exceeds 35 GB when the wavelength .lamda. of the laser beams is 405 nm, the NA of the objective lens is 0.85, and the track pitch is constant to be 0.32 .mu.m, if the constraint length of the partial response is increased from 5 to 7, and the detection capability is not increased, it is difficult to detect it.

[0252] The equalization error calculator 66 obtains an equalization error ek from the equalization signal y0 from the multi-input adaptive equalizer 63 and the target signal Zk and supplies the equalization error ek to the multi-input adaptive equalizer 63 for tap coefficient control.

[0253] As illustrated in FIG. 7, the equalization error calculator 66 includes a subtracter 91 and a coefficient multiplier 92.

[0254] The subtracter 81 subtracts the target signal Zk from the equalization signal y0.

[0255] The equalization error ek is generated by multiplying the subtraction result by a predetermined coefficient a through the coefficient multiplier 82.

[0256] As illustrated in FIG. 5, the multi-input adaptive equalizer 63 includes adaptive equalizer units 71 to 75 and an adder 76.

[0257] The above-described reproduction information signal Sa is input to the adaptive equalizer unit 71, the reproduction information signal Sb is input to the adaptive equalizer unit 72, the reproduction information signal Sc is input to the adaptive equalizer unit 73, the reproduction information signal Sd is input to the adaptive equalizer unit 74, and the reproduction information signal Se is input to the adaptive equalizer unit 75.

[0258] The adaptive equalizer units are installed corresponding to the number of divided signals A to E obtained from the split regions.

[0259] Each of the adaptive equalizer units 71 to 75 has a finite impulse response (FIR) filter tap number, a calculation accuracy (bit resolution), and a parameter of an update gain of adaptive operation, and an optimal value is set in each of the adaptive equalizer units 71 to 75.

[0260] The equalization error ek is supplied to each of the adaptive equalizer units 71 to 75 as a coefficient control value for adaptive control.

[0261] Outputs y1 to y5 of the adaptive equalizer units 71 to 75 are added by an adder 76 and output as the equalization signal y0 of the multi-input adaptive equalizer 63.

[0262] The output target of the multi-input adaptive equalizer 63 is an ideal PR waveform in which binary detection result is convoluted into the partial response (PR).

[0263] The adaptive equalizer unit 71 includes, for example, an FIR filter illustrated in FIG. 6.

[0264] The adaptive equalizer unit 71 is a filter with (n+1) taps including delay elements 80-1 to 80-n, coefficient multipliers 81-0 to 81-n, and adder 84.

[0265] The coefficient multipliers 81-0 to 81-n multiply an input x at each time point by tap coefficients C0 to Cn.

[0266] Outputs of the coefficient multipliers 81-0 to 81-n are added by an adder 84 and sent out as an output y.

[0267] In order to perform the adaptive equalization process, the tap coefficients C0 to Cn are controlled. To this end, calculators 82-0 to 82-n that receive the equalization error ek and each tap input and perform a calculation are installed.

[0268] Further, integrators 83-0 to 83-n that integrate outputs of the calculators 82-0 to 82-n are installed.

[0269] Each of the calculators 82-0 to 82-n performs, for example, a calculation of -1.times.ek.times.x.

[0270] The outputs of the calculators 82-0 to 82-n are integrated by integrators 83-0 to 83-n, and the tap coefficients C0 to Cn of the coefficient multipliers 81-0 to 81-n are changed and controlled on the basis of the integration result.

[0271] Further, the integration of the integrators 83-0 to 83-n is performed to adjust the responsiveness of adaptive coefficient control.

[0272] The data detection processing unit 15 having the above configuration reduces unnecessary signals such as the crosstalk and then decodes the binary data.

[0273] The other adaptive equalizer units 72 to 75 illustrated in FIG. 5 also have the similar configuration as the adaptive equalizer unit 71.

[0274] The common equalization error ek is supplied to the adaptive equalizer units 71 to 75, and the adaptive equalization is performed.

[0275] In other words, the adaptive equalizer units 71 to 75 performs optimization of the error and the phase distortion of the input signal frequency components of the reproduction information signals Sa, Sb, Sc, Sd, and Se, that is, the adaptive PR equalization.

[0276] In other words, the tap coefficients C0 to Cn are adjusted in accordance with the calculation result of -1.times.ek.times.x in the calculators 82-0 to 82-n.

[0277] This means that the tap coefficients C0 to Cn are adjusted in the direction in which the equalization error is eliminated.

[0278] As described above, the adaptive equalizer units 71 to 75 adaptively control the tap coefficients C0 to Cn in a direction in which a desired frequency characteristic is obtained using the equalization error ek.

[0279] The equalization signal y0 of the multi-input adaptive equalizer 63 obtained by adding the outputs y1, y2, y3, y4, and y5 of the adaptive equalizer units 71 to 75 by the adder 76 is the signal in which the crosstalk and the like is reduced.

[0280] Further, a specific example of the tap coefficient control process and the like corresponding to the respective signals A to E are described in Patent Document 1 (International Publication No. WO 2016/006157) which is a prior application of the same applicant as the present applicant. In the configuration of the present application, a tap coefficient setting process corresponding to each signal similar to that described in the prior application can be applied.

[0281] [2. Basic Configuration Example of Crosstalk Cancellation Process Using Read Signal of Adjacent Track]

[0282] Next, a basic configuration example of the crosstalk cancellation process using the read signal of the adjacent track will be described.

[0283] As described above, the optical discs such as the BDs are required to perform the high-density information recording. One method of increasing the density of optical discs is a method of narrowing the track pitch.

[0284] Specifically, for example, the land (L)/groove (G) recording method of recording data in both the groove track and the land track is effective.

[0285] However, in such a high-density recording disc, there is a problem that the crosstalk is highly likely to occur in the data reproducing process.

[0286] In other words, there is a problem that the crosstalk in which data of an adjacent track is mixed into readout data of a current readout track as noise is likely to occur.

[0287] As a technique of removing the crosstalk, there is a crosstalk cancellation technique to which the read signal of the adjacent track is applied.

[0288] Further, a configuration example of executing the crosstalk cancellation using the read signal of the adjacent track is disclosed in Patent Document 2 (Japanese Patent Application Laid-Open No. 2015-057753), which is the prior application by the present applicant.

[0289] A basic configuration example of the crosstalk cancellation process using the read signal of the adjacent track will be described below.

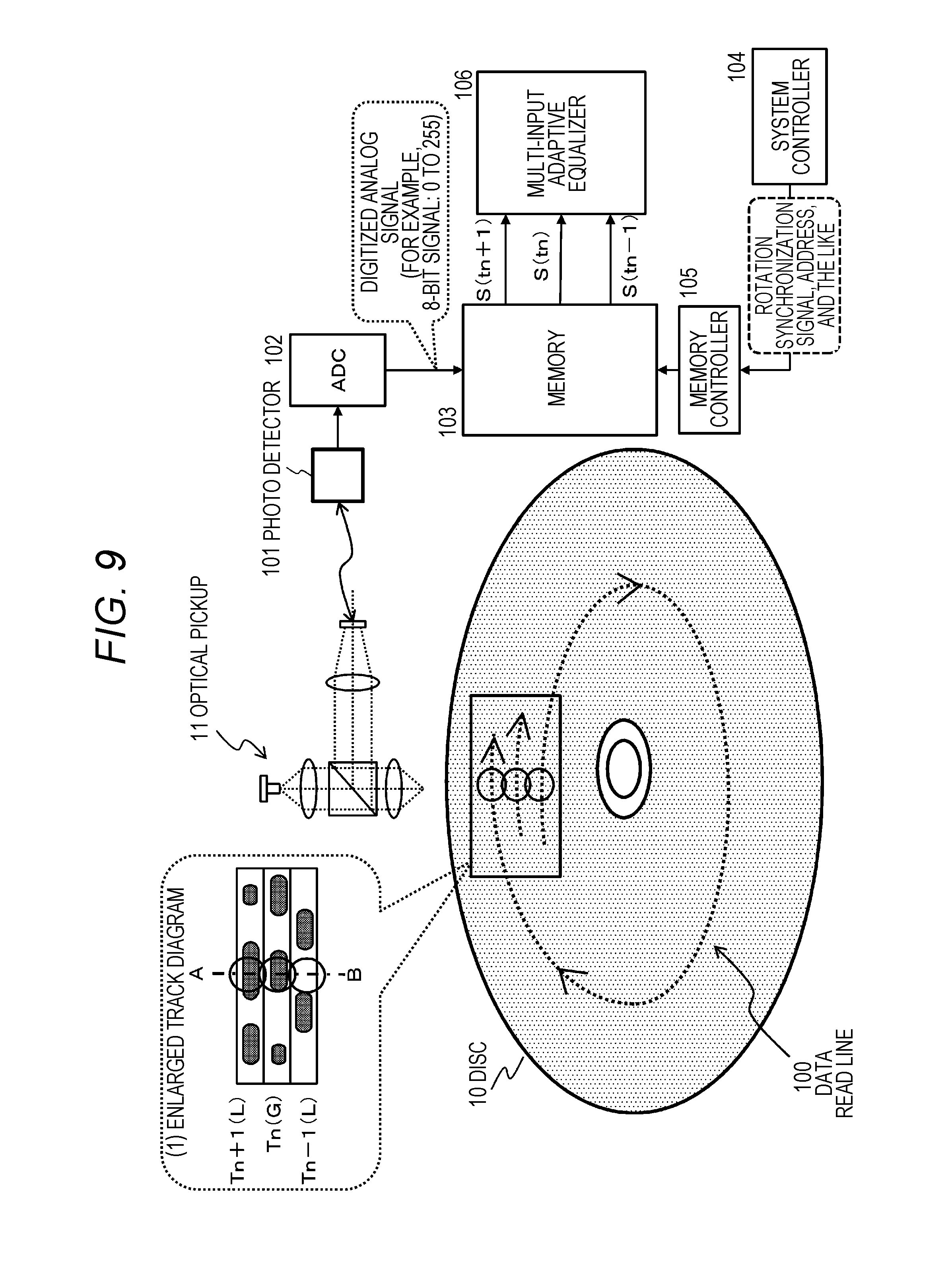

[0290] FIG. 8 is a diagram illustrating a configuration example of an information processing device (a reproducing device) that performs the crosstalk cancellation using the read signal of the adjacent track.

[0291] The optical pickup 11 reads data from a disc 10.

[0292] The optical pickup 11 reads track data along a data read line 100 of disc 10 illustrated in FIG. 8.

[0293] As illustrated in an enlarged track diagram of FIG. 8(1), three adjacent tracks Tn-1, Tn, and Tn+1 centered on the track Tn are read along the data read line 100.

[0294] Read data from the disc 10 is input from a photo detector 101 to an AD converter (ADC) 102, converted into a digital signal, and stored in a memory 103.

[0295] Further, the data stored in the memory 103 is a digital signal generated on the basis of an analog signal which is a read signal (RF signal) from the disc 10, for example, a digitized analog signal of 8 bits (0 to 255).

[0296] The data read along the data read line 100 of the disc 10 illustrated in FIG. 8 is stored in the memory 103.

[0297] If the read data of adjacent regions of three tracks of an A-B line in the enlarged track diagram of FIG. 8(1) is stored in the memory 103, the read signals corresponding to the three tracks of the A-B line are input to a multi-input adaptive equalizer 106.

[0298] Signals S(tn+1) to S(tn-1) illustrated in FIG. 8 correspond to the read signals of the tracks Tn+1, Tn, and Tn-1.

[0299] Further, it is necessary to perform the data input from the memory 103 to the multi-input adaptive equalizer 106 in a state in which the three signals of the A-B line of FIG. 8(1) are synchronized with one another. This control is performed by a memory controller 105 on the basis of a rotation synchronization signal, an address, or the like provided from a system controller 104 to the memory controller 105.

[0300] For example, the multi-input adaptive equalizer 106 has a configuration similar to that described above with reference to FIGS. 5 and 6.

[0301] In FIG. 5, the five signals of the split region compatible five-signal output type detector are input, but in the example illustrated in FIG. 8, three read signals of the tracks Tn-1 to Tn+1 are input.

[0302] However, this is a case where a non-split detector is used, that is, a case where (A) the non-split one-signal output type detector described with reference to FIG. 2 is used.

[0303] For example, in a case where the split region compatible five-signal output type detector is used, it is necessary to input 15 (=5.times.3) signals. This example will be described later.

[0304] The multi-input adaptive equalizer 106 includes a plurality of adaptive equalizer units that receive the three read signals of the tracks Tn-1 to Tn+1.

[0305] Each adaptive equalizer unit has a configuration similar to that described above with reference to FIG. 6.

[0306] The read signal S(tn) of the center track Tn which is one adaptive reproduction target is input to one adaptive equalizer unit.

[0307] Further, the read signals S(tn-1) and S(tn+1) of the adjacent tracks Tn-1 and Tn+1 which cause the crosstalk component are input to each individual adaptive equalizer unit.

[0308] The output of each adaptive equalizer unit is calculated, the equalization signal, and the binarization process is performed on the equalization signal to generate the binary data.

[0309] With this process, it is possible to obtain the high-quality data from which the crosstalk component is removed from the read signal S(tn) of the track Tn.

[0310] Further, a configuration and a process of the multi-input adaptive equalizer 106 will be described later with reference to FIG. 11.

[0311] Using the configuration illustrated in FIG. 8, it is possible to remove the crosstalk component by inputting the read signals of the current reproduction track and the adjacent track to the multi-input adaptive equalizer 106.

[0312] However, in the configuration illustrated in FIG. 8, it is necessary to accumulate the read data along the data read line 100 shown in the disc 10 of FIG. 8, that is, the read data corresponding to almost two rounds of the disc in the memory 103.

[0313] As described above, the data stored in the memory 103 is a digital signal generated on the basis of an analog signal which is the read signal (RF signal) from the disc 10, for example, the digitalized analog signal of 8 bits (0 to 255), and since the data amount is large, there is a problem that the memory capacity required for the memory 103 increases.

[0314] Further, in a case where data is recorded in both the land (L) and the groove (G), and data reading is executed by an individual pickup, data corresponding to one round of track may be stored in the memory as illustrated in FIG. 9.

[0315] In the configuration illustrated in FIG. 9, the read data of adjacent land tracks Tn-1 (L) and Tn+1 (L) is necessary for the crosstalk reduction process of the read data of the track Tn (G) which is a central groove track.

[0316] In the example illustrated in FIG. 9, the land (L) and the groove (G) are reproduced using an individual pickup, and in this case, data to be accumulated for the crosstalk reduction of the read data of the track Tn (G) which is the central groove track is read data corresponding to one round of track of the land (L).

[0317] Further, G and L illustrated in FIG. 9 indicate a groove and a land, respectively. The present example is an example using the disc 10 in which data is recorded in both the groove (G) and the land (L).

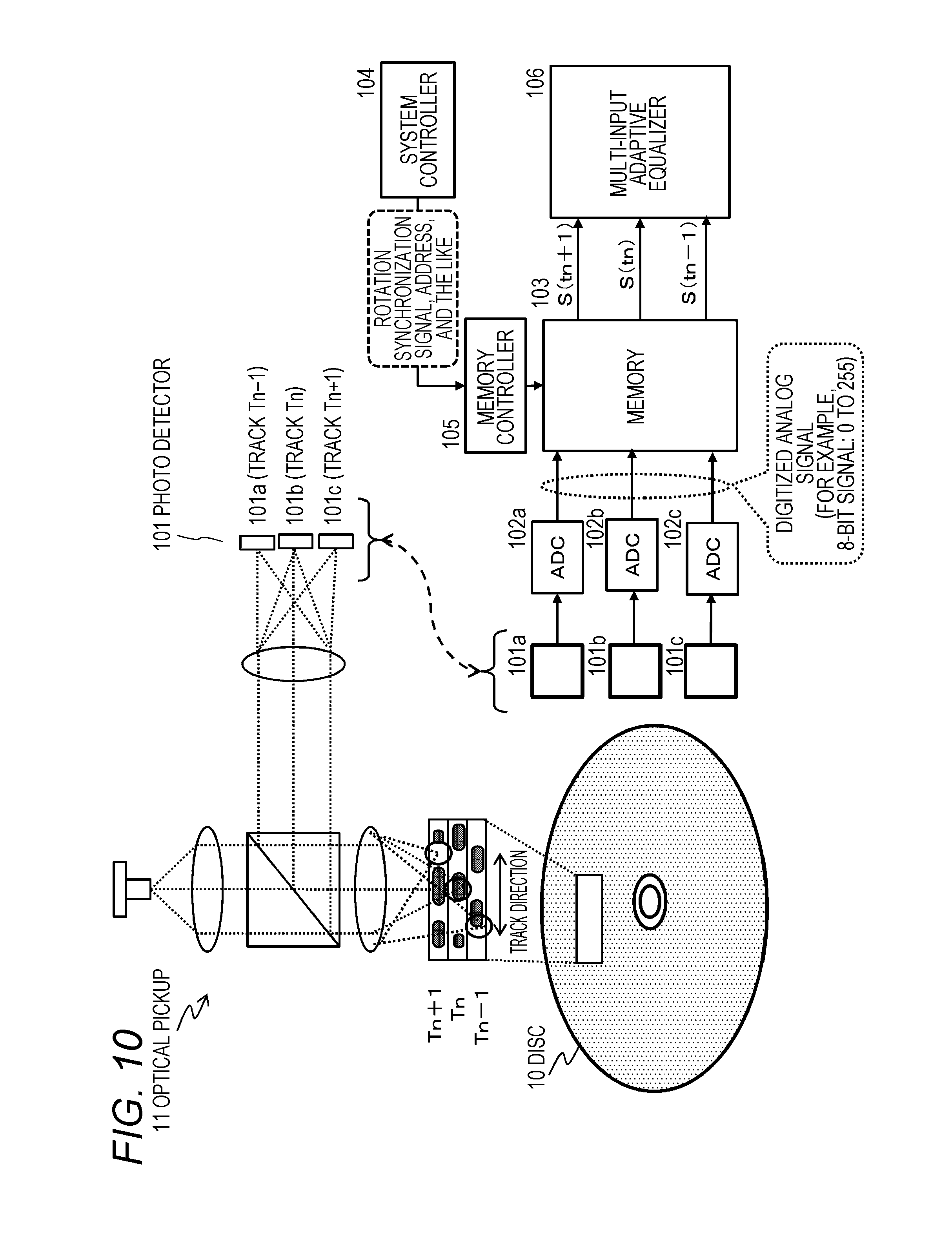

[0318] In the configuration illustrated in FIG. 8, it is necessary to accumulate track read data corresponding to almost two rounds in the memory. Further, in the configuration illustrated in FIG. 9, it is necessary to store the track read data corresponding to almost one round in the memory. As a configuration for solving such a problem, a configuration illustrated in FIG. 10 is provided.

[0319] The example illustrated in FIG. 10 is a configuration in which a pickup 11 irradiates each of three adjacent tracks with spot light at a time, and reflected light from the respective tracks are detected through three photo detectors 101a to 101c.

[0320] Further, as illustrated in FIG. 10, a configuration in which three spot lights are irradiated, and detection light from each spot light is detected by an individual photodetector is described, for example, in Patent Document 4 (Japanese Patent Application No. 4184585).

[0321] However, if the positions of the spot lights irradiated to the three adjacent tracks are arranged in the half radial direction of the disc, interference or the like based on overlapping of the spot lights or the like occurs, and noise increases, and thus it is necessary to set the respective spot lights at non-overlapping positions, and the three spot lights are set at positions at which the spot lights deviate from one another in the track direction.

[0322] In the configuration illustrated in FIG. 10, the read data from the disc 10, that is, the read data from the three adjacent tracks Tn-1, Tn, and Tn+1 are input from photo detector 101a to 101c to AD converters (ADCs) 102a to 102c, converted into digital signals, and stored in the memory 103.

[0323] Further, in this case, the data stored in the memory 103 is a digital signal generated on the basis of an analog signal which is the read signal (RF signal) from the disc 10, for example, a digitized analog signal of 8 bits (0 to 255).

[0324] The data read from the three adjacent tracks are stored in the memory 103.

[0325] The read data deviates in the track direction.

[0326] As described above, it is necessary to input the data of the three adjacent tracks with no deviation in the track direction to the multi-input adaptive equalizer 106.

[0327] Therefore, it is necessary to store the data of the three adjacent tracks with no deviation in the track direction in the memory 103, and it is necessary to store the data corresponding to the three tracks in a section corresponding to the deviation of the three spot lights irradiated to the three tracks in the track direction.

[0328] If the read data of the adjacent regions of the three tracks of the A-B line of the enlarged track diagram of FIG. 8(1) described above is stored in the memory 103, the read signals corresponding to the three tracks of the A-B line are stored in the multi-input adaptive equalizer 106.

[0329] In FIG. 10, the signals S(tn+1) to S(tn-1) correspond to the read signals of the tracks Tn+1, Tn, and Tn-1, respectively, similarly to FIG. 8.

[0330] Further, it is necessary to perform the data input from the memory 103 to the multi-input adaptive equalizer 106 in a state in which the signals of the three tracks at the nearest positions, that is, the three signals of the A-B line in FIG. 8(1) described above are synchronized with one another. This control is performed by a memory controller 105 on the basis of a rotation synchronization signal, an address, or the like provided from a system controller 104 to the memory controller 105.

[0331] In FIG. 10, the memory 103 also stores it is necessary to store the signals read from the three adjacent tracks, that is, the digital signal generated on the basis of an analog signal which is the read signal (RF signal) from the disc 10, for example, a digitized analog signal of 8 bits (0 to 255) in the memory 103, and thus there is a problem in that a necessary memory capacity increases.

[0332] Further, in the configuration illustrated in FIG. 10, circuits for processing the signals from the three adjacent tracks in parallel, for example, ADCs which correspond in number to the read data are required, and thus there arises a problem in that the circuit configuration is complicated.

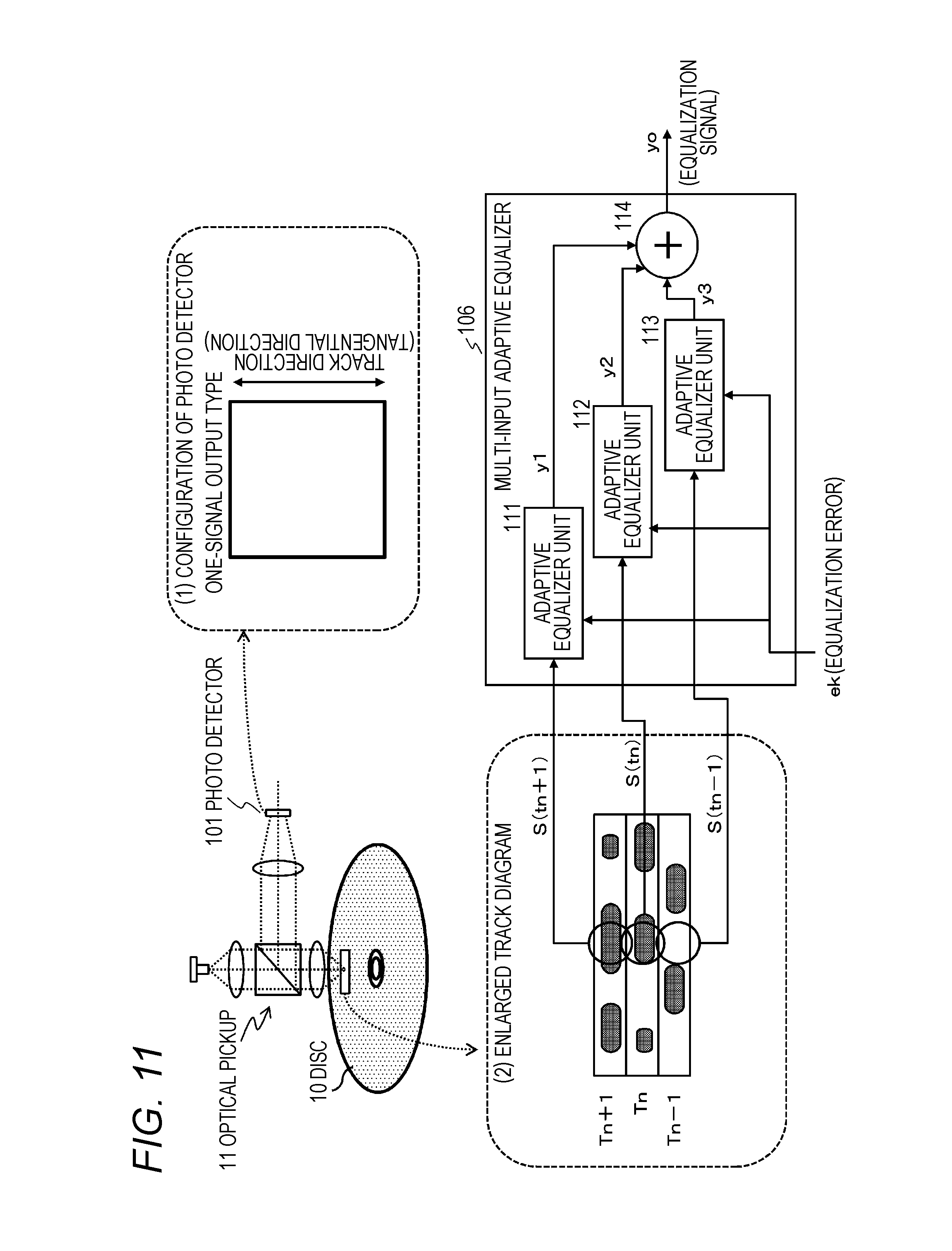

[0333] A specific configuration example and a process example of the multi-input adaptive equalizer 106 in the configuration described above with reference to FIGS. 8 and 10 will be described with reference to FIG. 11.

[0334] The multi-input adaptive equalizer 106 includes adaptive equalizer units 111, 112, and 113 and an adder 114.

[0335] The reproduction signal S(tn+1) corresponding to the track Tn+1 is input to the adaptive equalizer unit 111.

[0336] The reproduction signal S (tn) corresponding to the track Tn is input to the adaptive equalizer unit 112.

[0337] The reproduction signal S(tn-1) corresponding to the track Tn-1 is input to the adaptive equalizer unit 113.

[0338] Each of the adaptive equalizer units 111, 112, and 113 has an FIR filter tap number, a calculation accuracy (bit resolution), and a parameter of an update gain of adaptive operation, and an optimal value is set in each of the adaptive equalizer units 111, 112, and 113.