Boost And Ldo Hybrid Converter With Dual-loop Control

SHI; Chunlei ; et al.

U.S. patent application number 15/937947 was filed with the patent office on 2019-10-03 for boost and ldo hybrid converter with dual-loop control. The applicant listed for this patent is QUALCOMM Incorporated. Invention is credited to Jongrit LERDWORATAWEE, Yu PU, Chunlei SHI.

| Application Number | 20190305683 15/937947 |

| Document ID | / |

| Family ID | 67845347 |

| Filed Date | 2019-10-03 |

| United States Patent Application | 20190305683 |

| Kind Code | A1 |

| SHI; Chunlei ; et al. | October 3, 2019 |

BOOST AND LDO HYBRID CONVERTER WITH DUAL-LOOP CONTROL

Abstract

A boost and LDO hybrid converter with dual-loop control is disclosed. In some implementations, a hybrid converter includes an inductor having a first terminal to receive an input voltage and a second terminal; an n-type metal oxide semiconductor device (nMOS) having a drain coupled to the second terminal of the inductor; a p-type metal oxide semiconductor device (pMOS) having a gate, a drain, and a source, the source coupled to the second terminal of the inductor; an output capacitor having a first terminal coupled to the drain of the first pMOS; and a controller having a switch driver and a buffer, wherein the controller is configured to use the switch driver to drive the gate of the first pMOS in a boost mode and to use the buffer to drive the gate of the first pMOS in a low drop out (LDO) mode.

| Inventors: | SHI; Chunlei; (San Diego, CA) ; LERDWORATAWEE; Jongrit; (San Diego, CA) ; PU; Yu; (San Diego, CA) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 67845347 | ||||||||||

| Appl. No.: | 15/937947 | ||||||||||

| Filed: | March 28, 2018 |

| Current U.S. Class: | 1/1 |

| Current CPC Class: | G05F 1/452 20130101; H02M 2001/0032 20130101; G05F 1/62 20130101; G05F 1/575 20130101; H02M 3/158 20130101; H02M 2001/0045 20130101; G05F 1/26 20130101; H02M 3/1582 20130101 |

| International Class: | H02M 3/158 20060101 H02M003/158; G05F 1/26 20060101 G05F001/26 |

Claims

1. (canceled)

2. (canceled)

3. A hybrid converter, comprising: an inductor having a first terminal to receive an input voltage and a second terminal; an n-type metal oxide semiconductor device (nMOS) having a drain coupled to the second terminal of the inductor and a source coupled to ground; a p-type metal oxide semiconductor device (pMOS) having a gate, a drain, and a source, the source coupled to the drain of the first nMOS and the second terminal of the inductor; an output capacitor having a first and a second terminal, the first terminal coupled to the drain of the pMOS and the second terminal coupled to ground; a controller having a switch driver and a buffer, wherein the controller is configured to use the switch driver to drive the gate of the pMOS to configure the hybrid converter as a boost converter if the input voltage is less than an output voltage of the hybrid converter and to use the buffer to drive the gate of the pMOS to configure the hybrid converter as a low drop out linear voltage regulator (LDO) if the input voltage is greater than the output voltage; a current sensor coupled across the inductor to provide a feedback current signal to a positive terminal of the controller; and a compensation network coupled to an input of the buffer.

4. The hybrid converter of claim 3, wherein the current sensor, the inductor, the compensation network, and the controller are configured as a current loop in the LDO mode.

5. The hybrid converter of claim 4, further comprising: an error amplifier coupled between the output capacitor and a negative input terminal of the controller to provide a feedback voltage to the controller.

6. The hybrid converter of claim 5, wherein the error amplifier, the controller, the pMOS, and the output capacitor are configured as a voltage loop in the LDO mode.

7. (canceled)

8. (canceled)

9. (canceled)

10. A method comprising: receiving an input voltage at a first terminal of an inductor of a hybrid converter; if the input voltage is less than an output voltage of the hybrid converter, configuring the hybrid converter as a boost converter, wherein the configuring the hybrid converter as the boost converter comprises driving a gate of a p-type metal oxide semiconductor device (pMOS) with a switch driver, wherein a source of the pMOS is coupled to a second terminal of the inductor, and a drain of the pMOS is coupled to a first terminal of an output capacitor; if the input voltage is greater than the output voltage, configuring the hybrid converter as a low drop out linear voltage regulator (LDO) by driving the gate of the pMOS with a buffer; controlling the LDO using a voltage loop and a current loop; sensing a current through the inductor, wherein the inductor is part of the current loop; and providing a feedback signal based on the current sensed to a controller of the hybrid converter.

11. The method of claim 10, further comprising: providing a feedback voltage from the output capacitor through an error amplifier to the controller, wherein the error amplifier is part of the voltage loop.

12. An apparatus, comprising: means for receiving an input voltage at a first terminal of an inductor of a hybrid converter; means for configuring the hybrid converter as a boost converter if the input voltage is less than an output voltage of the hybrid converter; means for configuring the hybrid converter as a low drop out linear voltage regulator (LDO) if the input voltage is greater than the output voltage; and means for controlling the LDO using a voltage loop and a current loop.

13. The apparatus of claim 12, further comprising: means for sensing a current through the inductor, wherein the inductor is part of the current loop; and means for providing a feedback signal based on the current sensed to a controller of the hybrid converter.

14. The apparatus of claim 13, wherein the means for configuring the hybrid converter as the boost converter comprises: a switch driver to drive a gate of a p-type metal oxide semiconductor device (pMOS) of the hybrid converter, wherein a source of the pMOS is coupled to a second terminal of the inductor, and a drain of the pMOS is coupled to a first terminal of an output capacitor.

15. The apparatus of claim 14, wherein the means for configuring the hybrid converter as the LDO comprises: a buffer having an input and an output, the output coupled to the gate of the pMOS to drive the pMOS; and a compensation network coupled to the input of the buffer.

16. The apparatus of claim 15, further comprising: means for providing a feedback voltage from the output capacitor to the controller.

17. The apparatus of claim 16, wherein the means for providing the feedback voltage comprises an error amplifier.

18. The apparatus of claim 17, wherein the error amplifier is part of the voltage loop.

19. (canceled)

Description

FIELD OF DISCLOSURE

[0001] Aspects of the present disclosure relate generally to voltage converters, and more particularly to a boost and low drop out (LDO) hybrid converter with dual-loop control.

BACKGROUND

[0002] In many electronic systems today, a boost converter is commonly used to convert a low input voltage to a higher output voltage. The boost converter is particularly useful in low power mobile applications and/or Internet-of-Things (IoT) applications, for example, charging circuit in Bluetooth headphone. There are many applications where the input voltage has a wide range and could either be lower or higher than the output voltage. A single boost converter is not able to cover the entire voltage range in those scenarios.

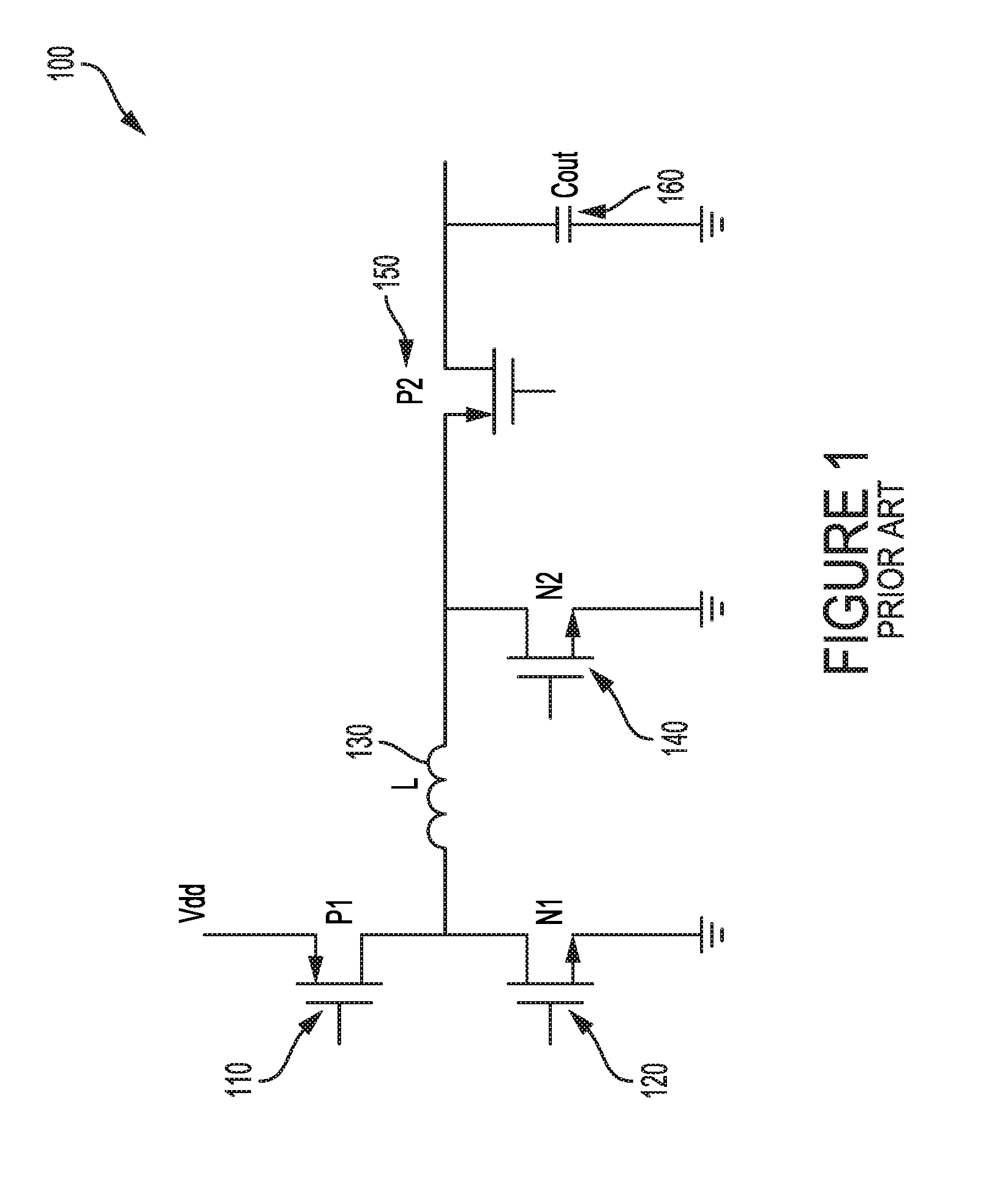

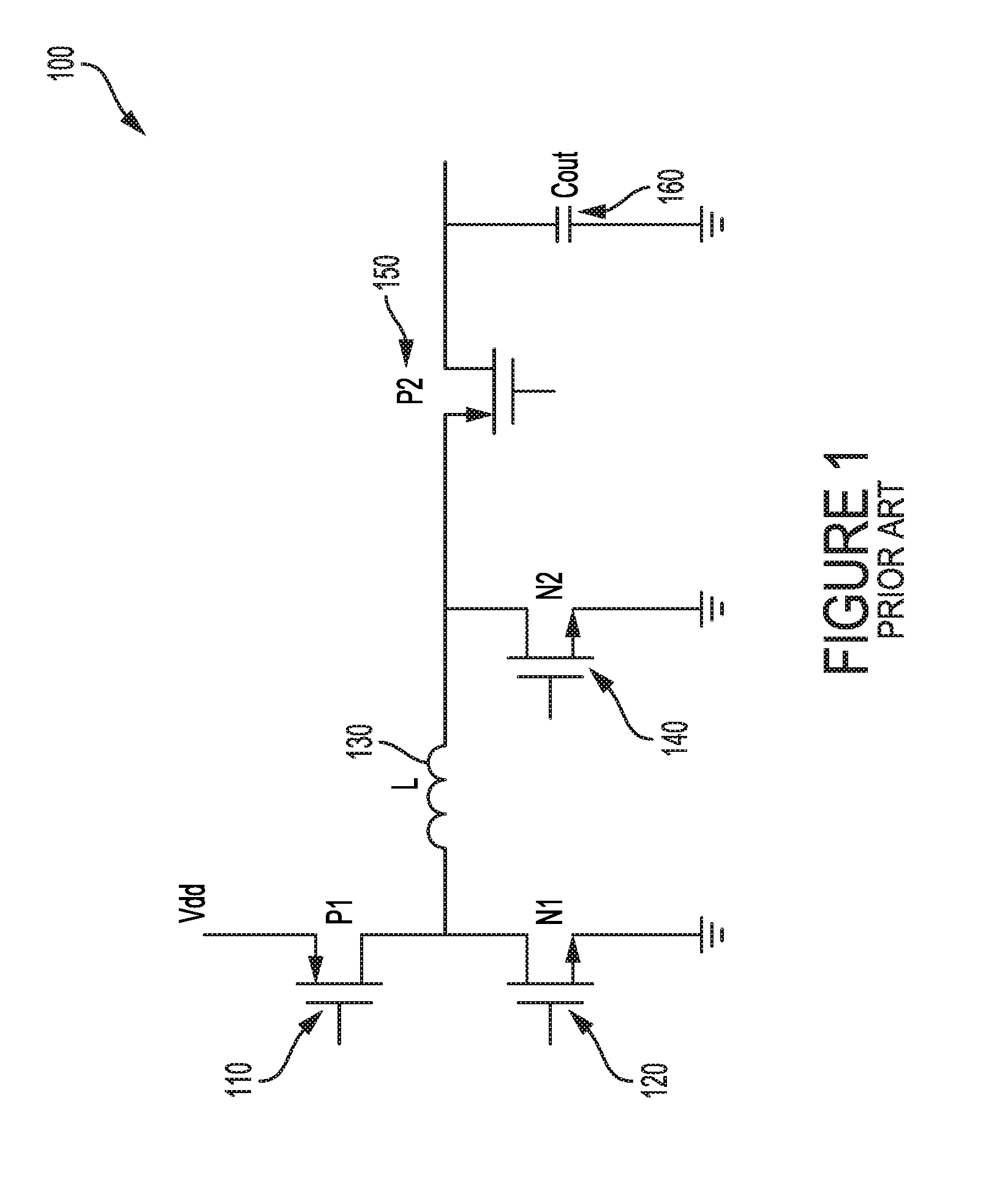

[0003] Conventionally, several types of converters are developed to address the above problem. One such design is to use a non-inverting buck-boost converter to cover the entire range. FIG. 1 shows an example of a conventional non-inverting buck-boost converter. The buck-boost converter 100 includes a first p-type switch P1 110, a first n-type switch N1 120, an inductor L 130, a second n-type switch N2 140, a second p-type switch P2 150, and an output capacitor Cout 160. A source of P1 110 is coupled to an input voltage supply Vdd, and a drain of P1 is coupled to a first terminal of L 130 and a drain of N1 120. A source of N1 120 is coupled to ground. A second terminal of L 130 is coupled to a source of P2 150 and a drain of N2 140. A source of N2 140 is coupled to ground. A drain of P2 150 is coupled to one end of Cout 160. The other end of Cout 160 is coupled to ground.

[0004] The buck-boost converter 100 can be configured as either a buck down converter or a boost up converter to convert the input voltage Vdd. However, a complex control scheme is needed to control the four switches, namely, P1 110, P2 150, N1 120, and N2 140, to configure the converter 100 as a buck converter or a boost converter or a buck-boost converter. The four switches needed for power delivery also impose penalties on silicon area and efficiency. Further, the number of pins required in such design is one more than the number of pins required in a conventional regular boost converter.

[0005] Another prior design uses a boost converter and a low drop out converter (LDO) in series. FIG. 2 shows a conventional converter 200 having a boost converter and a LDO coupled in series. The converter 200 includes an inductor 210, a first n-type switch N1 220, a first p-type switch P1 230, a boost capacitor C_bst 240, a second p-type switch P2 260, a driver 250, and a LDO capacitor C_ldo 270. Specifically, the inductor 210, N1 220, P1 230, C_bst 240 can be configured as a boost converter 202; while P2 260, driver 250, and C_ldo 270 can be configured as a LDO 204. An input voltage Vin is applied to the inductor 210 and an output voltage Vout is taken at the drain of P2 160.

[0006] When input voltage Vin is less than output voltage Vout, boost converter 202 becomes active and boosts up the input voltage Vin. Then LDO 204 down converts the voltage or goes into bypass mode. When Vin is greater than Vout, boost converter 202 goes into bypass mode, and LDO 204 down converts the input voltage Vin.

[0007] As shown in FIG. 2, converter 200 needs three (3) switches for power delivery, namely, P1 230, N1 220, and P2 260. Like converter 100 in FIG. 1, the number of pins converter 200 requires is one more than the number of pins required in a conventional regular boost converter. Moreover, two (2) capacitors (i.e., C_bst 240 and C_ldo 270) are required in converter 200, that is one more than the converter 100 shown in FIG. 1. Thus, this design also uses large area on silicon. Further, the arrangement of boost converter 202 and LDO 204 in series imposes an efficiency penalty on the entire design.

[0008] FIG. 3 shows a third conventional converter design that uses a boost converter and a LDO in parallel. Converter 300 includes a boost converter 302 having an inductor 310, a n-type switch N1 320, a p-type switch 330, and an output capacitor C_out 360. Converter 300 further includes a LDO 304 having a p-type switch P2 340 and a driver 350. When input voltage Vin is less than output voltage Vout, boost converter 302 is turned on and LDO 304 is turned off. When input voltage Vin is greater than output voltage Vout, boost converter 302 is turned off and LDO 304 is turned on.

[0009] Like converter 200 in FIG. 2, converter 300 uses three (3) switches for power delivery, namely, N1 320, P1 330, and P2 340. Thus, converter 300 still requires a large area on silicon. Further, both P1 330 and P2 340 need to have bi-directional block capability due to the parallel configuration.

[0010] Because of the various shortfalls of the existing converters discussed above, there is a need in the art to provide a more efficient hybrid boost and LDO converter design that occupies smaller area, especially for the mobile and IoT applications that demand compact design.

SUMMARY OF THE DISCLOSURE

[0011] The following presents a simplified summary of one or more implementations in order to provide a basic understanding of such implementations. This summary is not an extensive overview of all contemplated implementations and is intended to neither identify key or critical elements of all implementations nor delineate the scope of any or all implementations. The sole purpose of this summary is to present some concepts of one or more implementations in a simplified form as a prelude to the more detailed description that is presented later.

[0012] In some implementations, a hybrid converter includes an inductor having a first terminal to receive an input voltage and a second terminal; a first n-type metal oxide semiconductor device (nMOS) having a drain coupled to the second terminal of the inductor and a source coupled to ground; a first p-type metal oxide semiconductor device (pMOS) having a gate, a drain, and a source, the source coupled to the drain of the first nMOS and the second terminal of the inductor; an output capacitor having a first and a second terminal, the first terminal coupled to the drain of the first pMOS and the second terminal coupled to ground; and a controller having a switch driver and a buffer, wherein the controller is configured to use the switch driver to drive the gate of the first pMOS in a boost mode and to use the buffer to drive the gate of the first pMOS in a low drop out (LDO) mode.

[0013] The hybrid converter can further include a current sensor coupled across the inductor to provide a feedback current signal to a positive terminal of the controller. In some implementations, the hybrid converter further includes a compensation network coupled to an input of the buffer. The current sensor, the inductor, the compensation network, and the controller are configured as a current loop in the LDO mode.

[0014] In some implementations, the hybrid converter further includes an error amplifier coupled between the output capacitor and a negative input terminal of the controller to provide a feedback voltage to the controller. The error amplifier, the controller, the first pMOS, and the output capacitor are configured as a voltage loop in the LDO mode.

[0015] In some implementations, a method to provide a hybrid converter includes receiving an input voltage at a first terminal of an inductor of a hybrid converter. If the input voltage is less than an output voltage of the hybrid converter, configuring the hybrid converter as a boost converter. If the input voltage is greater than the output voltage, configuring the hybrid converter as a low drop out linear voltage regulator (LDO), and controlling the LDO using a voltage loop and a current loop.

[0016] The method can further include sensing a current through the inductor, wherein the inductor is part of the current loop; and providing a feedback signal based on the current sensed to a controller of the hybrid converter.

[0017] In some implementations, configuring the hybrid converter as the boost converter comprises driving a gate of a p-type metal oxide semiconductor device (pMOS) with a switch driver, wherein a source of the pMOS is coupled to a second terminal of the inductor, and a drain of the pMOS is coupled to a first terminal of an output capacitor. Furthermore, configuring the hybrid converter as the LDO comprises driving the gate of the pMOS with a buffer.

[0018] In some implementations, the method further includes providing a feedback voltage from the output capacitor through an error amplifier to the controller, wherein the error amplifier is part of the voltage loop.

[0019] To the accomplishment of the foregoing and related ends, the one or more implementations include the features hereinafter fully described and particularly pointed out in the claims. The following description and the annexed drawings set forth in detail certain illustrative aspects of the one or more implementations. These aspects are indicative, however, of but a few of the various ways in which the principles of various implementations may be employed and the description implementations are intended to include all such aspects and their equivalents.

BRIEF DESCRIPTION OF THE DRAWINGS

[0020] FIG. 1 shows an example of a conventional non-inverting buck-boost converter.

[0021] FIG. 2 shows a conventional converter 200 having a boost converter and a LDO coupled in series.

[0022] FIG. 3 shows a third conventional converter design that uses a boost converter and a LDO in parallel.

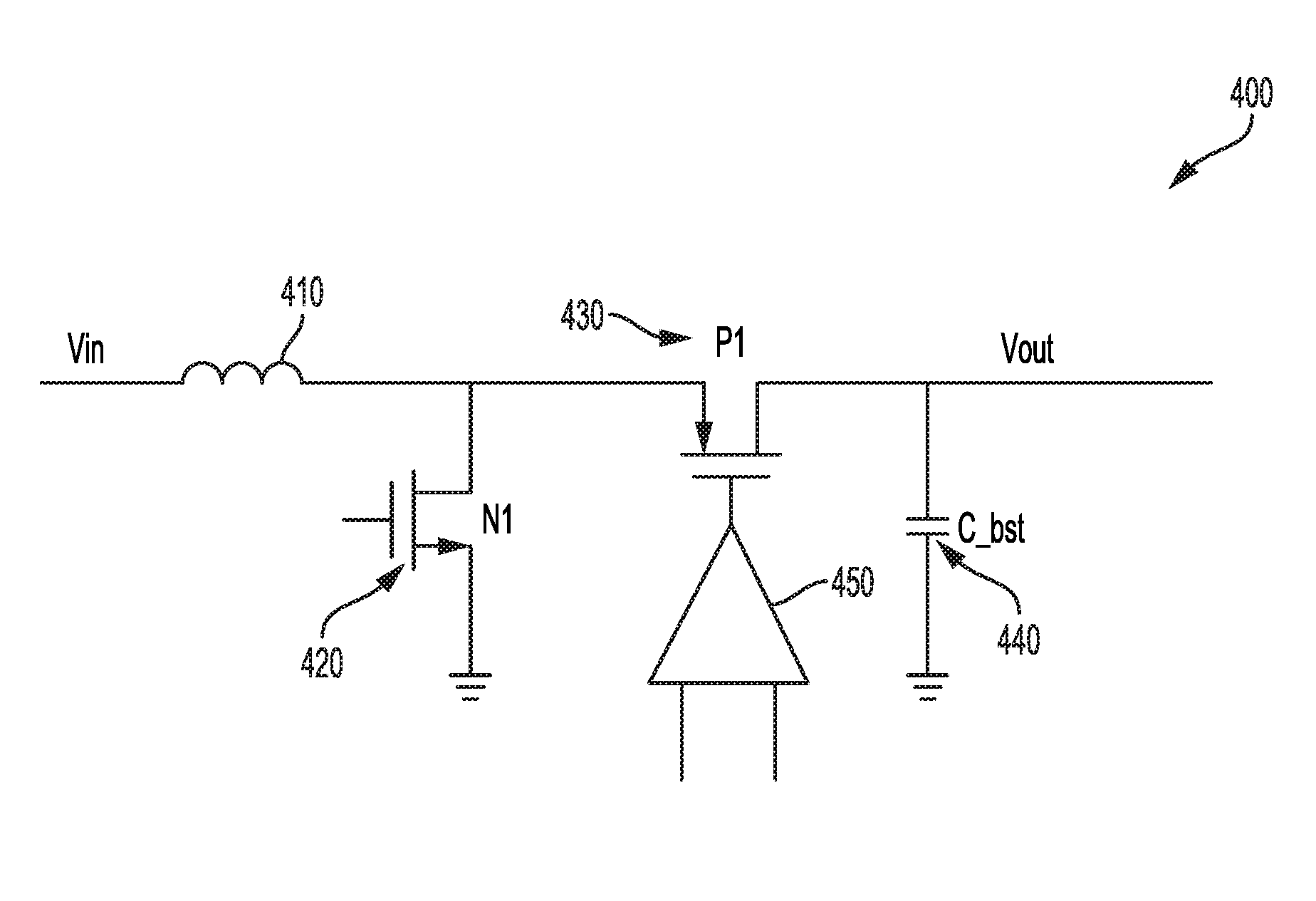

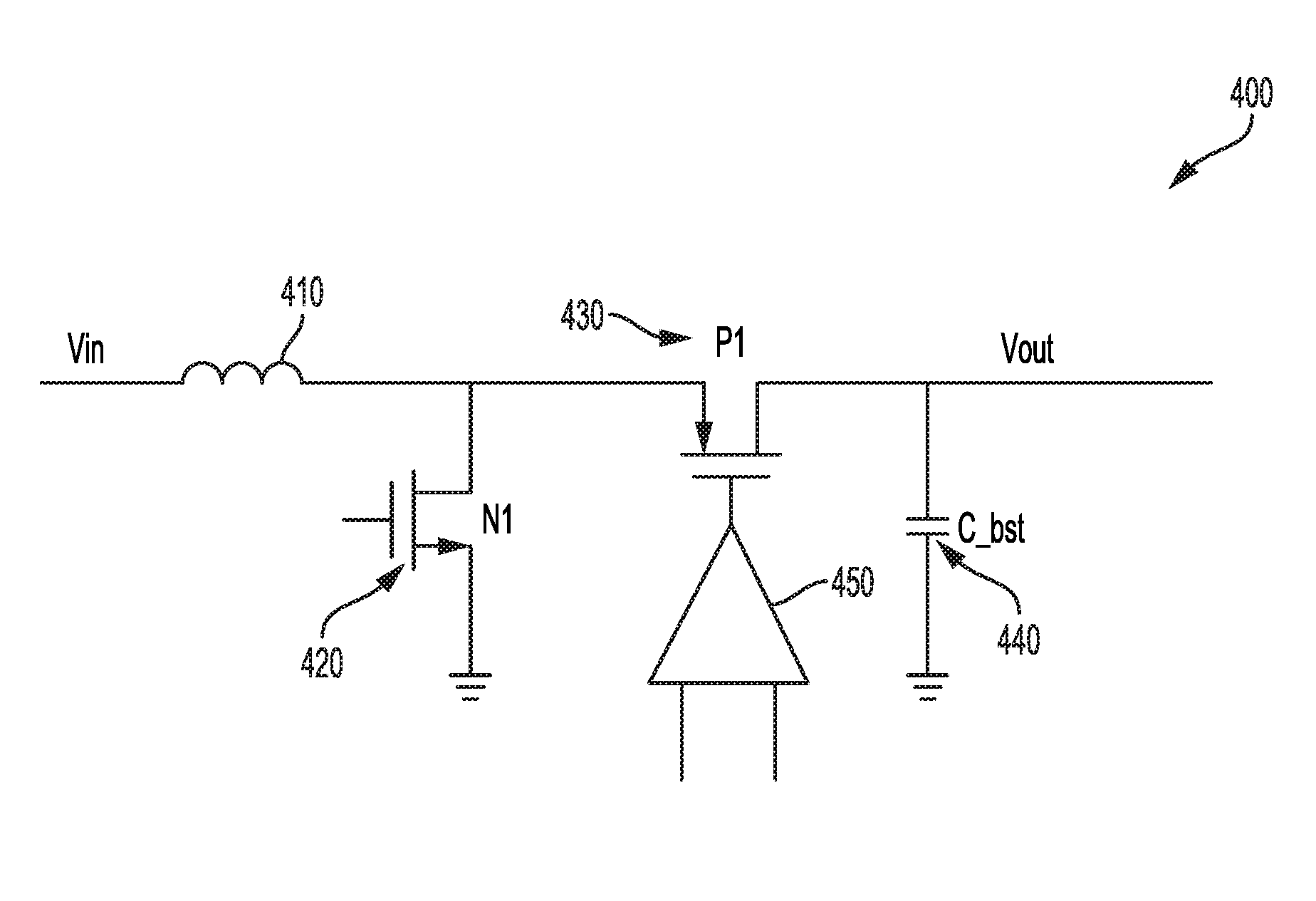

[0023] FIG. 4 below shows one implementation of a boost LDO hybrid converter.

[0024] FIG. 5 shows one implementation of a circuit model illustrating C_gs in the LDO configuration of the boost LDO hybrid converter shown in FIG. 4.

[0025] FIG. 6 shows one implementation of a hybrid boost converter with compensation that does not severely limit bandwidth.

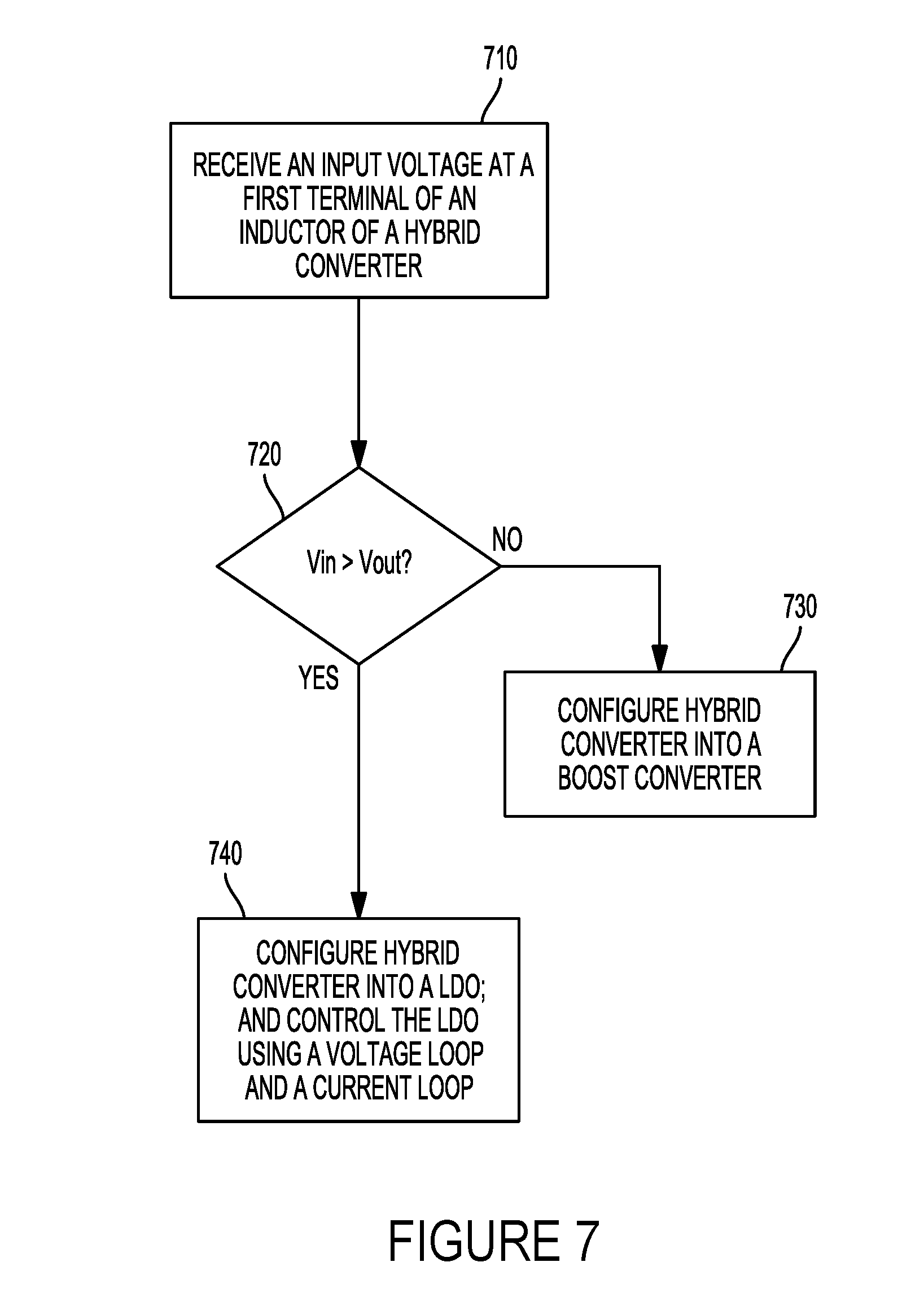

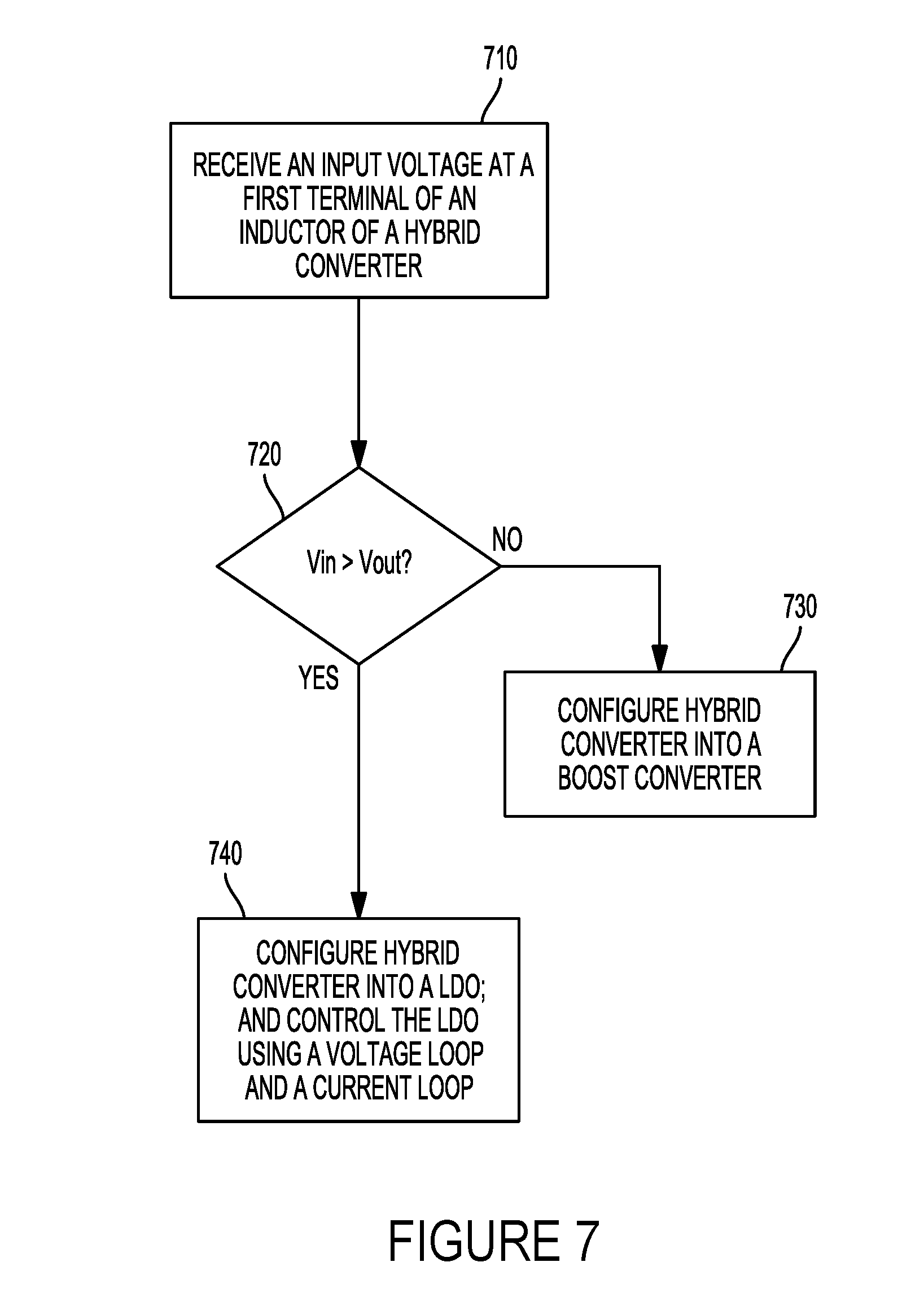

[0026] FIG. 7 shows a flow diagram of one implementation of a process to provide a hybrid converter.

DETAILED DESCRIPTION

[0027] The detailed description set forth below, in connection with the appended drawings, is intended as a description of various configurations and is not intended to represent the only configurations in which the concepts described herein may be practiced. The detailed description includes specific details for the purpose of providing a thorough understanding of the various concepts. However, it will be apparent to those skilled in the art that these concepts may be practiced without these specific details. In some instances, well-known structures and components are shown in block diagram form in order to avoid obscuring such concepts.

[0028] FIG. 4 shows one implementation of a boost LDO hybrid converter. Boost LDO hybrid converter 400 includes an inductor 410, an n-type switch, such as an n-type metal oxide semiconductor device (nMOS) 420, a p-type switch, such as a p-type metal oxide semiconductor device (pMOS) 430, an output capacitor C_bst 440, and a controller 450. A first terminal of inductor 410 is configured to receive an input voltage Vin and a second terminal of inductor 410 is coupled to a drain of nMOS 420. A source of nMOS 420 is coupled to ground. The drain of nMOS 420 is further coupled to a source of pMOS 430. A gate of pMOS 430 is coupled to an output of controller 450. A drain of pMOS 430 is coupled to a first terminal of C_bst 440 to provide an output voltage Vout. A second terminal of C_bst 440 is coupled to ground. In some implementations, controller 450 can include a switch driver to drive the gate of pMOS 430 when the boost LDO hybrid converter 400 is configured as a boost converter. Controller 450 can further include a buffer to drive the gate of pMOS 430 when the converter 400 is configured as a LDO. In an alternate implementation, controller 450 can include a configurable circuit that can be configured as a switch driver when the converter 400 is in a boost mode or as a buffer when the converter 400 is in a LDO mode.

[0029] In operation, when Vin is less than Vout, boost LDO hybrid converter 400 is configured as a regular boost converter. Inductor 410, nMOS 420, pMOS 430, and C_bst are all on (or active) to boost Vin in order to generate Vout. When Vin is close to Vout, boost LDO hybrid converter 400 effectively goes into burst mode. In other words, boost LDO hybrid converter 400 may turn boost converter on for a few cycles, then turn boost converter off and wait for Vout to decay.

[0030] When Vout falls below Vin, boost LDO hybrid converter 400 is configured as a LDO with inductor 410 in the loop, pMOS 430 remains on, and nMOS 420 is switched off. In other words, inductor 410, pMOS 430, and C_bst 440 are re-used in the LDO configuration. By re-using inductor 410, pMOS 430, and C_bst 440 in the LDO configuration, boost LDO hybrid converter 400 does not require as much silicon area as the conventional hybrid converter designs discussed above.

[0031] Note that the LDO configuration retains inductor 410 in the loop. Furthermore, even though nMOS 420 is turned off, nMOS 420 still has parasitic gate source capacitance (C_gs). FIG. 5 shows one implementation of a circuit model illustrating C_gs in the LDO configuration of the boost LDO hybrid converter 400 shown in FIG. 4. In FIG. 5, circuit model 500 includes an inductor 510, a capacitor modeling a parasitic gate source capacitance C_gs 520, a pMOS P1 530, an output capacitor C_bst 540, and a controller 550. While inductor 510, P1 530, C_bst 540, and controller 550 are similar to inductor 410, P1 430, C_bst 440, and controller 450, respectively, C_gs 520 is added in the circuit model 500 to represent the parasitic gate source capacitance of nMOS N1 420. Inductor 510 and parasitic gate source capacitance C_gs 520 create double poles in the transfer function of the circuit model 500 as shown below:

Gm=gm/(1+s*gm*L+s{circumflex over ( )}2*L*C_gs)

[0032] The additional phase lag caused by the double poles severely affects the stability of the LDO loop. To compensate the loop, the bandwidth of circuit model 500 may be limited to a very low value, resulting in very poor transient performance. Accordingly, a hybrid boost converter with compensation is provided to mitigate the impact on bandwidth as discussed in detail below.

[0033] FIG. 6 shows one implementation of a hybrid boost converter with compensation that does not severely limit bandwidth. Hybrid converter 600 includes an inductor 610, an nMOS 620, a pMOS 630, an output capacitor 640, a controller 650, an error amplifier 660, a buffer 670, a compensation network 680, and a current sensor 690. Inductor 610, nMOS 620, pMOS 630, output capacitor 640, and controller 650 are coupled to each other in a way similar to the hybrid boost converter 400 shown in FIG. 4. An output node 609 is further coupled to a negative input terminal of error amplifier 660. A positive input terminal of error amplifier 660 is configured to receive a reference voltage Vref. An output of error amplifier 660 is coupled to a negative input terminal of controller 650. Current sensor 690 is coupled across inductor 610 to measure a current through inductor 610. Then current sensor 690 generates a voltage signal proportional to, or indicative of, the inductor current measured and input the voltage signal to a positive terminal of controller 650. Buffer 670 is added between an output of controller 650 and pMOS 630 to drive a gate of pMOS 630. In some implementations, buffer 670 and controller 650 can be part of a controller 655 of hybrid converter 600. Alternatively, controller 655 can include a circuit configurable as a buffer in a LDO mode or a driver in a boost mode. Furthermore, compensation network 680 is coupled to the output of controller 650 to create one (1) zero and one (1) pole to compensate for the phase lag caused by inductor 610 and the parasitic gate source capacitance of nMOS 520 as discussed above with reference to FIG. 5. For example, compensation network 680 can include a RC (resistor-capacitor) network Type II compensator.

[0034] It should be appreciated that the components of hybrid boost converter 600 described above form two control loops to control hybrid converter 600 when operating as LDO. The two control loops are a voltage loop 602 and a current loop 604. The voltage loop 602 is formed by error amplifier 660, controller 650, buffer 670, pMOS 630, and output capacitor 640. The voltage loop 602 is configured to regulate the output voltage Vout and to set a current reference or threshold for the current loop. The current loop 604 is formed by inductor 610, current sensor 690, compensation network 680, and controller 650. The current loop 604 is configured to regulate the inductor current to the current reference set by the voltage loop 602.

[0035] With the current loop 604, the hybrid converter 600 can compensate the parasitic capacitance when operating in LDO mode with the boost inductor 610 in the current loop 604. Such dual loop control also helps stabilizing hybrid converter 600, allowing inductor 610 to be re-used in LDO mode. Further, the bandwidth achieved in this configuration can be orders of magnitude higher than the bandwidth of some of the conventional designs discussed above.

[0036] FIG. 7 shows a flow diagram of one implementation of a process to provide a hybrid converter. The process can be implemented using semiconductor devices and circuits such as those shown in FIGS. 4 and 6. The process begins at block 710, where an input voltage is received at a first terminal of an inductor of a hybrid converter. At block 720, the process determines if an input voltage (Vin) is greater than an output voltage (Vout) of the hybrid converter. If Vin is not greater than Vout, then the process transitions to block 730, where the hybrid converter is configured into a boost converter to boost up Vin. If Vin is greater than Vout, then the process transitions to block 740, where the hybrid converter is configured into a LDO. In some implementations, the hybrid converter includes a current loop and a voltage loop to control the LDO such that the LDO can reuse the inductor of the hybrid converter while remaining substantially stable.

[0037] The previous description of the disclosure is provided to enable any person skilled in the art to make or use the disclosure. Various modifications to the disclosure will be readily apparent to those skilled in the art, and the generic principles defined herein may be applied to other variations without departing from the spirit or scope of the disclosure. Thus, the disclosure is not intended to be limited to the examples described herein but is to be accorded the widest scope consistent with the principles and novel features disclosed herein.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.