Electromagnetic Radiation Detector Based On Wafer Bonding

VON KAENEL; Hans

U.S. patent application number 16/430581 was filed with the patent office on 2019-09-19 for electromagnetic radiation detector based on wafer bonding. The applicant listed for this patent is G-RAY INDUSTRIES SA. Invention is credited to Hans VON KAENEL.

| Application Number | 20190288026 16/430581 |

| Document ID | / |

| Family ID | 61911637 |

| Filed Date | 2019-09-19 |

View All Diagrams

| United States Patent Application | 20190288026 |

| Kind Code | A1 |

| VON KAENEL; Hans | September 19, 2019 |

ELECTROMAGNETIC RADIATION DETECTOR BASED ON WAFER BONDING

Abstract

Monolithic pixel detectors, systems and methods for the detection and imaging of electromagnetic radiation with high spectral and spatial resolution comprise a Si wafer with a CMOS processed pixel readout bonded to an absorber wafer in wafer bonds comprising conducting bonds between doped, highly conducting charge collectors in the readout and highly conducting regions in the absorber wafer and poorly conducting bonds between regions of high resistivity.

| Inventors: | VON KAENEL; Hans; (Wallisellen, CH) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 61911637 | ||||||||||

| Appl. No.: | 16/430581 | ||||||||||

| Filed: | June 4, 2019 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| PCT/IB2018/000166 | Mar 1, 2018 | |||

| 16430581 | ||||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 27/14636 20130101; H01L 27/14659 20130101; H01L 31/1832 20130101; H01L 31/028 20130101; H01L 27/14696 20130101; H01L 27/1463 20130101; H01L 27/14634 20130101; H01L 31/1804 20130101; H01L 27/14649 20130101; H01L 2223/54493 20130101; H01L 27/14689 20130101; H04N 5/378 20130101; H01L 27/14661 20130101; H01L 31/02966 20130101; H01L 31/1892 20130101; G01N 23/046 20130101; H01L 27/1464 20130101; H01L 27/14658 20130101; H01L 27/1469 20130101; H01L 31/03046 20130101; H01L 27/14638 20130101; H01L 31/107 20130101; H01L 27/14694 20130101; H01L 27/14676 20130101; H01L 27/1465 20130101; H01L 23/544 20130101; H01L 2223/54426 20130101; H01L 31/1812 20130101; H01L 31/1844 20130101 |

| International Class: | H01L 27/146 20060101 H01L027/146; H01L 31/107 20060101 H01L031/107; H04N 5/378 20060101 H04N005/378; G01N 23/046 20060101 G01N023/046 |

Foreign Application Data

| Date | Code | Application Number |

|---|---|---|

| Mar 1, 2018 | IB | PCT/IB2018/000166 |

Claims

1. A monolithic CMOS integrated pixel detector for the detection of electromagnetic radiation configured for backside illumination, comprising a silicon readout wafer made from silicon of a first doping type, comprising CMOS pixel readout electronics processed in a thin silicon layer and including highly conducting doped regions of a second doping type acting as charge collectors spaced at a pixel size L, the charge collectors communicating with the readout electronics; said readout wafer being bonded by wafer bonds to an absorber wafer made from at least one single crystal semiconductor material, the absorber wafer further comprising highly conducting doped regions; the pixel detector further comprising the readout wafer bonded, in an aligned manner, to the absorber wafer; wherein said wafer bonds comprise highly conducting bonds between the readout wafer and the absorber wafer and poorly conducting bonds between the readout wafer and the absorber wafer, the poorly conducting bonds having a resistance exceeding that of the highly conducting bonds at least by a factor of 10.sup.2 thereby electrically isolating neighboring pixels so as to force charges generated in the absorber wafer to cross the conducting bonds and to be received by the charge collectors for processing by the pixel readout electronics when the detector is in operation.

2. The monolithic CMOS integrated pixel detector of claim 1, wherein the conducting bonds between the readout wafer and the absorber wafer are conducting covalent semiconductor bonds and wherein the poorly conducting bonds between the readout wafer and the absorber wafer are bonds between regions at least one of which is a highly resistive or insulating region or a p-n junction polarized in reverse direction when the detector is in operation, and wherein the poorly conducting bonds have a resistance exceeding that of the conducting covalent bonds at least by a factor selected from one of the group of ranges of factors consisting of 10.sup.2-10.sup.4, 10.sup.4-10.sup.6 and 10.sup.6-10.sup.8.

3. The monolithic CMOS integrated pixel detector of claim 1, wherein the thin silicon layer has a thickness selected from one of the group of thicknesses consisting of 10-30 .mu.m, 5-10 .mu.m and 3-5 .mu.m.

4. The monolithic CMOS integrated pixel detector of claim 1, wherein the highly conducting doped regions of the readout wafer and the highly conducting doped regions of the absorber wafer have a doping range selected from one of the group of doping ranges consisting of 1.times.10.sup.18-1.times.10.sup.19 cm.sup.-3, 1.times.10.sup.19-1.times.10.sup.20 cm.sup.-3 and 1.times.10.sup.20-5.times.10.sup.20, cm.sup.-3.

5. The monolithic CMOS integrated pixel detector of claim 1, further including wafer alignment features aligning the readout wafer with the absorber wafer selected from one of the group of features consisting of wafer notches, wafer flats and alignment marks.

6. The monolithic CMOS integrated pixel detector of claim 1 adapted for the detection of infrared radiation.

7. The monolithic CMOS integrated pixel detector of claim 6, wherein the pixel size L is in the range of 2-40 .mu.m.

8. The monolithic CMOS integrated pixel detector of claim 7, wherein the absorber wafer is pixelated in the form of absorber patches mutually isolated by insulating regions.

9. The monolithic CMOS integrated pixel detector of claim 8, wherein the absorber patches are spaced by the pixel size L of the detector pixels.

10. The monolithic CMOS integrated pixel detector of claim 8, wherein the absorber patches have a first width and the insulating regions have a second width, and wherein the sum of widths and is equal the pixel size L of the detector or a multiple thereof.

11. The monolithic CMOS integrated pixel detector of claim 7, wherein highly resistive regions in the silicon readout wafer provide electrical isolation between neighboring pixels.

12. The monolithic CMOS integrated pixel detector of claim 7, wherein the at least one single crystal semiconductor material of the absorber wafer is made of at least one of the group of materials consisting of Si, Ge, SiGe alloys, SiGeSn alloys, InAs, InGaAs alloys, InSb, the lead salts PbS, PbSe, PbTe and their alloys, and HgCdTe alloys.

13. The monolithic CMOS integrated pixel detector of claim 12, wherein the at least one single crystal semiconductor material of the absorber wafer is made from an epitaxial wafer comprising at least one epitaxial layer on a single crystal substrate.

14. The monolithic CMOS integrated pixel detector of claim 13, wherein the at least one epitaxial layer is a Ge, SiGe, SiGeSn, InGaAs, PbSeTe or HgCdTe alloy layer.

15. The monolithic CMOS integrated pixel detector of claim 12, wherein the absorber wafer comprises a charge multiplication layer.

16. The monolithic CMOS integrated pixel detector of claim 1, wherein the silicon readout wafer comprises a charge multiplication layer.

17. The monolithic CMOS integrated pixel detector of claim 1, wherein an at least one alignment feature of the readout wafer is superimposed on an at least one alignment feature of the absorber wafer with the rotational misalignment of the two wafers kept within about 0.1 to 0.2 degrees, and the lateral displacement within about 200-400 .mu.m.

18. The monolithic CMOS integrated pixel detector of claim 1, wherein an at least one alignment feature of the readout wafer is superimposed on an at least one alignment feature of the absorber wafer with the rotational misalignment of 200 mm wafers kept within about (2-5).times.10.sup.-4 degrees and the lateral misalignment within about 0.1-1 .mu.m.

19. The monolithic CMOS integrated pixel detector of claim 1, wherein the second doping type is of an opposite doping type to that of the first doping type.

20. The monolithic CMOS integrated pixel detector of claim 1, wherein the second doping type is of a similar doping type to that of the first doping type.

21. A method for forming a monolithic CMOS integrated pixel detector for the detection of electromagnetic radiation, the method comprising a) providing a pixel readout electronics by CMOS processing of a silicon readout wafer; b) forming highly conducting regions in the readout wafer spaced at a pixel size L acting as charge collectors and communicating with the pixel readout electronics; c) forming at least one alignment feature in the readout wafer; d) forming an absorber wafer from at least one single crystal semiconductor material; e) forming highly conducting doped regions in the absorber wafer; ff) forming at least one alignment feature in the absorber wafer; g) bonding a carrier wafer to the CMOS stack of the readout wafer after planarizing the CMOS stack; h) thinning and planarizing the readout wafer; i) superimposing the at least one alignment feature of the readout wafer and the absorber wafer; j) forming wafer bonds comprising highly conducting bonds and poorly conducting bonds between the readout wafer and the absorber wafer; wherein the poorly conducting bonds have a resistance exceeding that of the highly conducting bonds at least by at least 10.sup.2; and k) partially or completely removing the carrier wafer from the CMOS stack and opening bonding pads on the CMOS stack.

22. The method of claim 21, wherein the forming of the highly conducting wafer bonds comprises forming covalent conducting bonds and wherein the forming of poorly conducting bonds between the readout wafer and the absorber wafer comprises forming bonds between regions at least one of which is a highly resistive or insulating region or forming bonds between semiconductor regions of opposite doping which become poorly conducting when the p-n junction is polarized in reverse direction during detector operation.

23. The method of claim 22, wherein forming the absorber wafer comprises forming the absorber wafer in the form of absorber patches separated by insulating regions.

24. The method of claim 22, wherein the forming of the absorber wafer from the at least one single crystal semiconductor material comprises forming an absorber wafer adapted for infrared detection from at least one material selected from one of the group of materials consisting of Si, Ge, SiGe alloys, SiGeSn alloys, InAs, InGaAs alloys, InSb, PbS, PbSe, PbTe, PbSeTe alloys and HgCdTe alloys.

25. The method of claim 24, wherein forming the absorber wafer comprises forming at least one epitaxial layer on a single crystal substrate.

26. The method of claim 25, wherein forming the at least one epitaxial layer on a single crystal substrate comprises forming the epitaxial layer on one substrate selected from one of the group of substrates consisting of Si, Ge, GaAs, InSb, CdTe and CdZnTe.

27. The method of claim 26, wherein forming the absorber wafer with the at least one epitaxial layer on the single crystal substrate comprises steps of: a) providing a dielectric layer on the single crystal substrate; b) opening windows in the dielectric layer consisting of first windows of narrower width extending to the single crystal substrate and second windows of wider width with dielectric sidewalls of a first height; c) growing a first layer into first narrow windows and subsequently overgrowing the dielectric in the wider second windows to a second height by a selective epitaxy process; d) growing a second layer in the wider second windows to a third height, such that the sum of the second height and third height is below the first height of the dielectric sidewalls of said windows; e) growing a third layer in wider second windows with a faceted surface to a level above the dielectric sidewalls; f) planarizing the faceted surface to remove the facets so as to generate a planar, smooth and essentially particle-free surface of the absorber wafer with a surface roughness of 0.3-0.5 nm or 0.1-0.3 nm, suitable for low temperature wafer bonding to a thinned CMOS processed readout wafer.

28. The method of claim 26, wherein forming the absorber wafer with the at least one epitaxial layer on the single crystal substrate comprises the steps of: a) providing a patterned substrate for epitaxy in the form of pillars separated by trenches; b) epitaxially growing SiGe alloy crystals with gaps on top of the pillars; c) filling trenches and gaps between the SiGe crystals with insulating material; and d) providing a flat and smooth surface with an RMS roughness below 0.5 nm or preferably about 0.1-0.3 nm of the absorber wafer by planarizing the surface of the SiGe alloy crystals by CMP to make it suitable for wafer bonding with a thinned CMOS processed readout wafer.

29. The method of claim 27, wherein forming the at least one epitaxial layer comprises forming a charge multiplication layer.

30. The method of claim 28, wherein forming the at least one epitaxial layer comprises forming a charge multiplication layer.

31. The method of claim 23, wherein the CMOS processing of the readout wafer includes forming a charge multiplication layer.

32. The method of claim 25, wherein forming the monolithic CMOS integrated pixel detector includes removing the single crystal substrate.

33. The method of claim 23, wherein forming the monolithic CMOS integrated pixel detector further includes forming a metallic back contact.

34. A detector made according to the method of claim 21, the detector having single photon detection capability when operated in Geiger mode.

35. The detector of claim 34, wherein the absorber comprises an absorber region and an avalanche region made from a semiconductor with a larger bandgap than that of the absorber region, and wherein the avalanche region of the absorber communicates with the charge collectors of the readout wafer.

36. The detector of claim 34, wherein the readout wafer comprises a Si avalanche region communicating with the charge collectors, and wherein the absorber comprises at least one semiconductor with a lower bandgap than that of the avalanche region.

37. A device for non-destructive testing having the detector of claim 1, wherein the device includes: a) at least one switchable X-ray source with power supply b) at least one X-ray detector communicating with readout unit, c) one computerized control, data processing and display unit, one sample rotatable around at least one of the rotation axes, wherein the power supply of the at least one X-ray source and the readout unit of the at least one X-ray detector communicate with and are synchronized by the computerized control, data processing and display unit controlling also the sample rotation in order to generate, process and display computed tomography images.

38. A device for non-destructive testing having a plurality of the detectors of claim 1, wherein the device includes at least: a) one switchable X-ray source with power supply, b) one array of X-ray detectors communicating with readout units, c) one computerized control, data processing and display unit, and d) data communication and control lines, wherein the power supply of the at least one X-ray source and the readout units of the at least one array of X-ray detectors are interconnected by the communication and control lines and communicate with and are synchronized by the computerized control, data processing and display unit to generate, process and display computed tomography images.

39. A vehicle equipped for assisted or autonomous driving having detectors of claim 1, wherein the equipment of the vehicle includes at least: a) an array of spatially separated infrared detectors communicating with readout units, and b) data communications and power supply lines interconnecting all readout units and detectors to an on-board control and data processing center communicating with the data communications and power supply lines, wherein the array of spatially separated and interconnected infrared detectors permits real time distance measurements from static and moving objects through triangulation.

Description

CROSS REFERENCE TO RELATED APPLICATIONS

[0001] This application is a continuation in part of PCT application no. PCT/IB2018/000166, filed 1 Mar. 2018, of the same title, which claims priority to and benefit of U.S. Provisional Application No. 62/465,199 filed 1 Mar. 2017, which is incorporated herein by reference and relied upon.

FIELD OF THE INVENTION

[0002] The invention relates to pixel detectors made from monolithic, Complementary Metal Oxide Semiconductor (CMOS) integrated structures for the detection and imaging of electromagnetic radiation, and to methods for forming such structures.

BACKGROUND OF THE INVENTION

[0003] Digital imaging devices for electromagnetic radiation detection, also called pixel detectors, convert the energy of absorbed photons into electrical signals. For high-energy (i.e., typically much greater than 1 keV) electromagnetic radiation detection, current digital imaging devices can be classified into two broad classes, distinguished by the way in which impacting photons are converted into electrical signals. Taking X-ray photons as an example, in the first one of these classes, the conversion happens indirectly in the sense that X-ray photons are first down-converted in energy to visible photons in a scintillation layer. The visible photons are subsequently detected by an array of photodiodes, in which the optical generation of electron-hole pairs gives rise to electrical signals which are then further processed by a readout electronics and represented as an image on a computer screen. The two-stage conversion process of indirect X-ray imaging devices suffers from the drawback of limited conversion efficiency and spatial resolution because of losses and scattering occurring both during the conversion of X-rays into visible photons and in the detection of those. Typically about 25 electron-hole pairs are finally measured by the readout electronics per keV of incident X-ray energy.

[0004] In the second class of these pixel detectors semiconductor absorbers permit the direct conversion of X-rays into electron-hole pairs which can then be measured as an electrical signal by a readout electronics. In addition to superior sensitivity and higher spatial and temporal resolution compared to scintillator-based indirect conversion, such absorbers offer also spectral resolution, since the energy of an incident X-ray photon is proportional to the number of generated electron-hole pairs and thus measurable by a pulse height analysis. In silicon (Si), one needs on average 3.6 eV to create a single electron-hole pair (see for example R. C. Alig et al. in Phys. Rev. B 22, 5565 (1980); and R. C. Alig in Phys. Rev. B 27, 968 (1983), the entire disclosures of which are hereby incorporated by reference). On average this leads to 280 electron-hole pairs per keV of absorbed X-ray energy, from which it can be seen that the conversion efficiency exceeds that of a scintillator-photodiode combination by more than a factor of ten.

[0005] X-ray imaging detectors, or pixel sensors in general, employing direct conversion by means of semiconductor absorbers, can be implemented in different ways. One approach used in commercial flat panel fabrication is based on polycrystalline or amorphous materials directly deposited on the readout electronics made from thin film transistors. For example flat panel X-ray imaging detectors with amorphous selenium absorbers for medical applications are relatively inexpensive to make and offered in large sizes (see for example S. Kasap et al. in Sensors 11, 5112 (2011), the entire disclosure of which is hereby incorporated by reference). Materials in the form of single crystals offer, however, much better transport properties compared with their polycrystalline and amorphous counterparts. They therefore should provide improved detector performance. Single crystal absorbers are on the other hand incompatible with readout electronics made up of amorphous thin film transistors. They can in principle be epitaxially grown on CMOS processed readout wafers, but usually only at the expense of an intolerably high thermal budget, requiring special metallization schemes compatible with elevated process temperatures (see for example U.S. Pat. No. 8,237,126 to von Kanel, the entire disclosure of which is hereby incorporated by reference). Typically, with standard aluminium metallization, temperatures have to be kept below 450.degree. C.

[0006] Pixel detectors for visible and near infrared radiation detection are well known for example from mobile phones. In such detectors absorber and readout unit are both fabricated from a common silicon substrate. They are therefore true monolithic structures which do not require any bonding process in order to establish electrical connections between absorber and readout. Such monolithic detectors are also used for high-energy elementary particle detection.

[0007] On the other hand, pixel detectors consisting of a CMOS processed readout and an absorber made from a semiconductor other than silicon, require a low-temperature bonding process to establish electrical connections between every absorber pixel and the pixel electronics of the readout wafer. A low-temperature bonding process is required to be compatible with the CMOS processed readout electronics. Direct epitaxial growth of the absorber onto the readout electronics may be a possible exception, provided that the temperature can be kept sufficiently low. The most common bonding technique is bump bonding, as used for example by the Medipix collaboration (medipix.web.cern.ch) or by Dectris AG (dectris.ch). Bump bonding of detector areas beyond a few cm.sup.2 is not only a costly technique but also limits the pixel size typically to about 50 pin. The absorber can in principle consist of any semiconductor material suitable for energetic particle detection from which large single crystals can be grown, for example Si, Ge, GaAs and CdTe or CdZnTe alloys (see for example European Patent No. 0571135 to Collins et al., the entire disclosure of which is hereby incorporated by reference). The higher the order number Z of an absorber of given thickness, the more photons of a given energy it will absorb. Hence a 1 mm thick Si absorber will absorb more than 90% of incident photons up to an energy of about 15 keV, a Ge or GaAs absorber of the same thickness absorbs at least 90% photons with energies below about 45 keV, and finally an equally thick CdTe absorber manages more than 90% absorption up to photon energies of about 72 keV.

[0008] Bump bonding for example with In micro-bumps is also used for the fabrication of infrared focal plane arrays, where a pixel size of 15 .mu.m is in production and 10 .mu.m or even smaller appears feasible. Typically, these arrays are much smaller in area than the ones used for X-ray imaging, hardly ever exceeding about 1 cm.sup.2 (see for example P. Bensussan et al. in Proc. of SPIE, Vol. 7298, pp. 72982N-1-72982N-31 (2009), the entire disclosure of which is hereby incorporated by reference). For infrared imaging, additional absorber materials are in use, such as InGaAs alloys, InSb and HgCdTe alloys or also lead salts.

[0009] While for large X-ray detectors it is hard to push the pixel size to below about 50 .mu.m with ordinary bump bonding, there are other bonding technologies potentially offering higher detector resolution. One of them is for example known from the vertical integration of integrated circuits, so-called 3D-IC technology. Here, bump bonding is replaced by fusion bonding, made up of oxide-to-oxide fusion bonding along with metal-to-metal bonding of metallic pads surrounded by oxide. The resulting structures are indistinguishable from genuine monolithic configurations (see for example G. W. Deptuch et al. in IEEE Trans. Nucl. Sci. 57, 2178 (2010), the entire disclosure of which is hereby incorporated by reference). For this reason we shall in the following consider heterostructures made by direct wafer bonding as monolithic as if they were fabricated for example in the form of epitaxial wafer stacks.

[0010] In yet another bonding technique, an electrically conductive, covalent semiconductor bond is formed at low temperature between the absorber wafer and the readout wafer. Covalent semiconductor bonding essentially leads again to a monolithic structure (see for example U.S. Pat. No. 10,163,957 to von Kanel, the entire disclosure of which is hereby incorporated by reference). In contrast to the well-known hydrophobic and hydrophilic bonding techniques in which the surfaces are respectively hydrogen or oxide covered prior to the bonding, covalent semiconductor bonding requires the surfaces to be atomically clean, especially when silicon is one of the bonding partners. Covalent semiconductor bonding can therefore only be carried out in a high vacuum or even ultra-high vacuum tool. In an ideal situation, when two essentially perfectly flat semiconductor wafers to be covalently bonded are very accurately aligned, neither with any mutual twist nor tilt, the dangling bonds on the two surfaces form covalent bonds that are indistinguishable from the bonds formed during epitaxial growth once the two wafers are brought into contact. Evidently, in practice such an ideal situation never occurs, and finite surface roughness and misalignment always lead to a finite number of interfacial defects, even when the two wafers are made from the same semiconductor material. Depending on the CMOS process used the pixel size can vary in a wide range for example of about 100-200 .mu.m, 50-100 .mu.m, 20-50 .mu.m, or 5-20 .mu.m, or even 2-5 .mu.m.

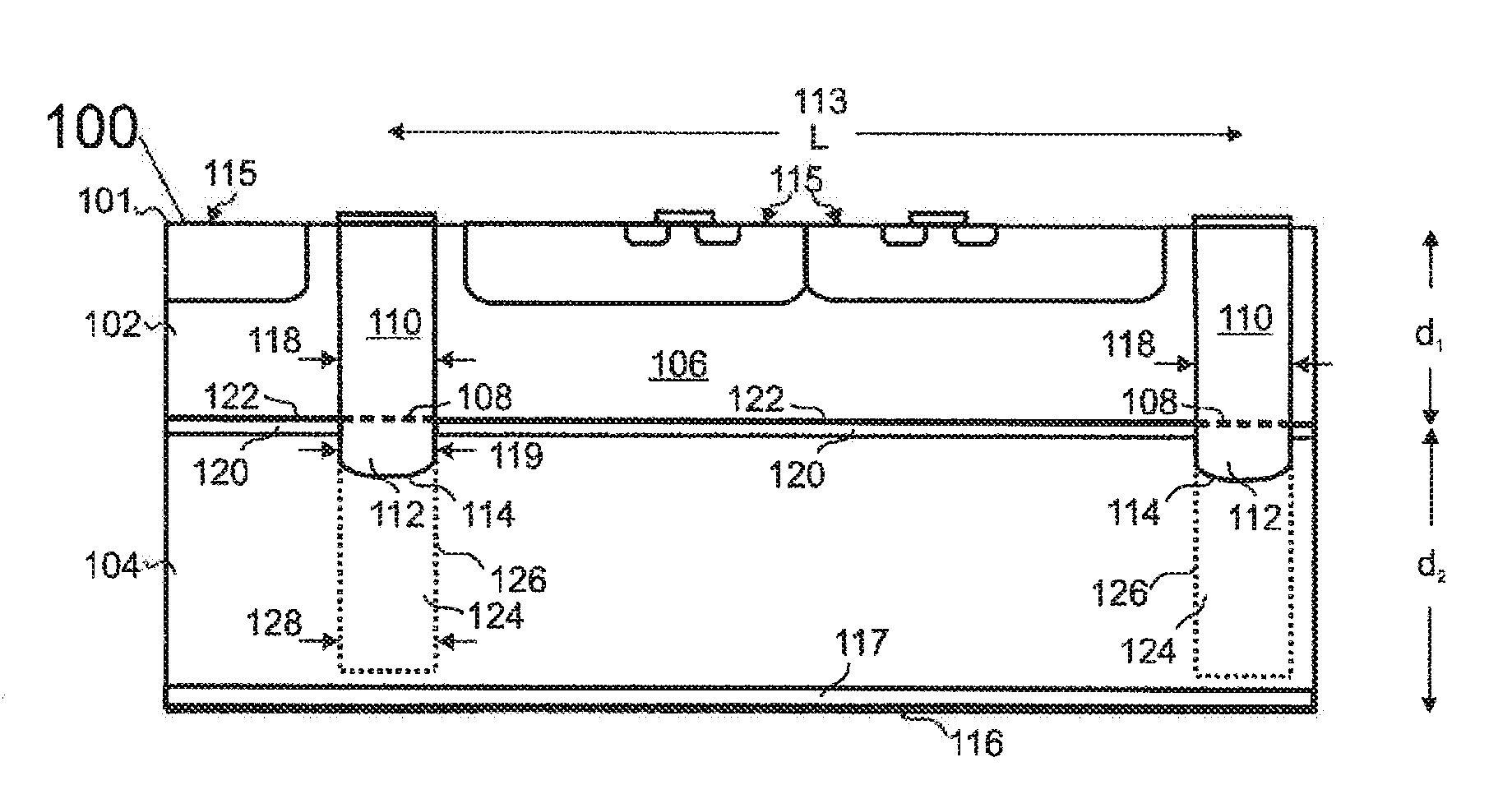

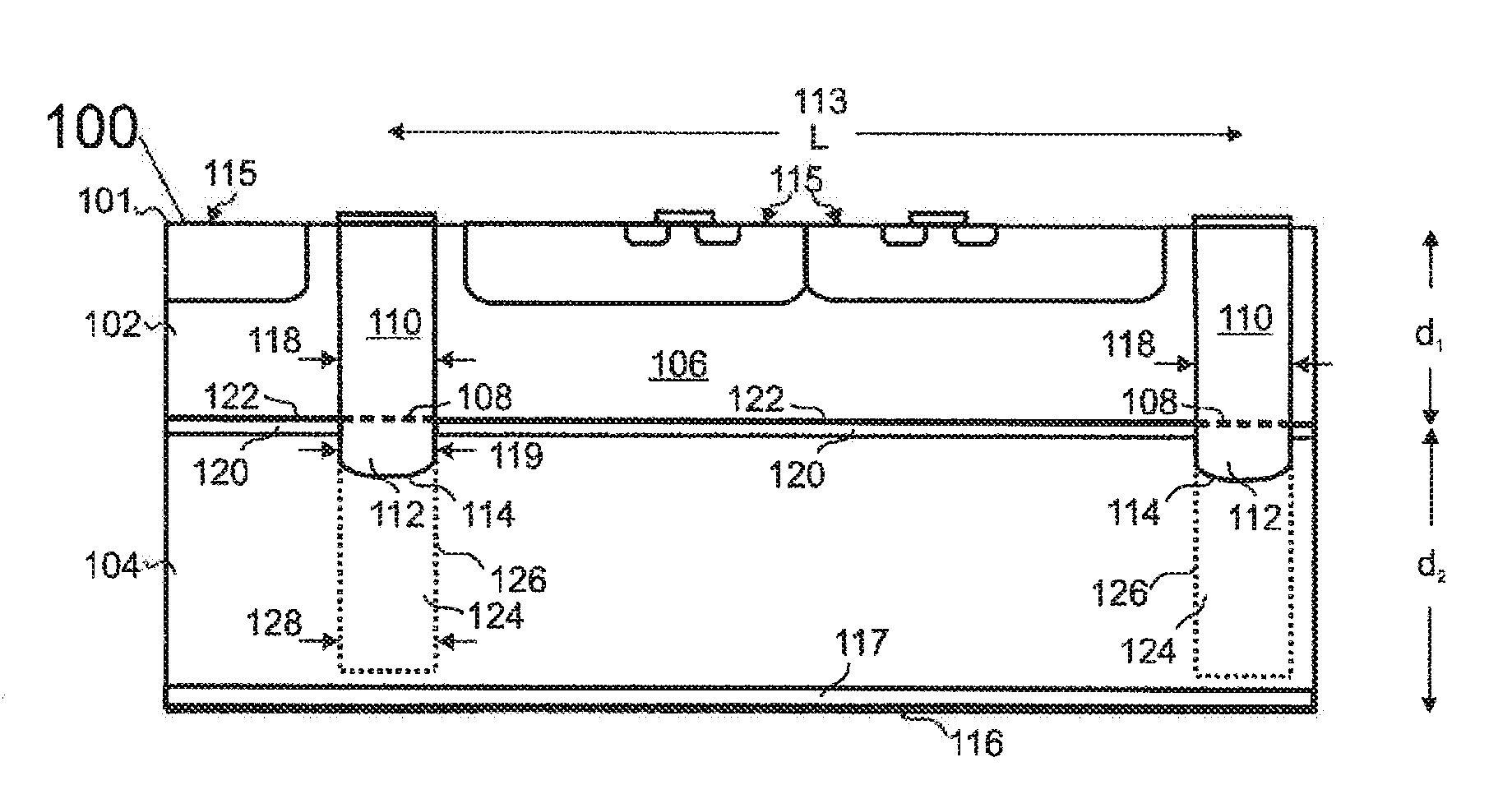

[0011] In this bonding approach, charge carriers are generated by backside illumination, wherein the absorber wafer is bonded on the thinned Si substrate of the readout wafer on the opposite side of the CMOS stack consisting of metal and dielectric layers. The charges then have to cross the covalently bonded semiconductor interface in order to be collected by charge collectors on the readout wafer. As a result of the backside illumination, the pixel detectors of the invention may have a fill factor (sensitive detector area) close to 100%. In one of the simplest approaches, adapted in particular to X-ray or .gamma.-ray detection, the electric field required to separate electron-hole pairs excited by electromagnetic radiation in the absorber is thereby generated by a reverse-biased p-n junction present between the readout wafer and the absorber wafer both of which are lightly doped and of opposite doping type. Examples of prior art may be seen in FIGS. 1A-1C showing three different embodiments 10, 20 and 30 of covalently bonded detector structures (see for example International Patent Application No. PCT/IB2017/001032 to von Kanel, the entire disclosure of which is hereby incorporated by reference). The silicon layer 12, 22, 32 with the CMOS processed pixel readout electronics is indicated schematically in these figures while the CMOS stack on top of it, made up of multiple oxide and metal layers, is not shown. The Si substrate of the readout wafer has to be thinned to typically 10-20 .mu.m in order to facilitate its depletion along with that of absorber wafer 14, 24, 34 when a reverse voltage 17, 27, 37 is applied across p-n junction 16, 26, 36 so that charges stemming from electron-hole pairs generated by X-ray absorption can cross bonded interfaces 18, 28, 38 in order to be collected by charge collectors 19, 29, 39 and processed by the readout electronics. In order to permit the thinning of the Si substrate of the readout wafer, the CMOS stack on its front side is first planarized and bonded to a carrier wafer (also called handling wafer). After this mechanical stabilization step, the backside of the Si substrate can then be thinned to the required thickness (see for example International Patent Application No. PCT/IB2017/001032 to von Kanel, the entire disclosure of which is hereby incorporated by reference). The pixel size of the detector is given by the spacing of charge collectors 19, 29, 39, only one of which is shown in FIGS. 1A-1C. In embodiments 10-30, the p-n junction is located right at the bonded interface (FIG. 1A, FIG. 1C) or either in the readout (FIG. 1B) or in the absorber wafer. Therefore, the bonded interface necessarily lies in the depletion region of the reverse biased p-n junction. Even under optimal conditions, the bonded interface contains defects, such as dislocations arising from slight wafer misalignment (see for example T. Akatsu et al. in J. Mat. Sci, 39, 3031 (2004), the entire disclosure of which is hereby incorporated by reference). Interfacial defects may cause potential barriers which negatively affect charge transport across a bonded interface (see for example S. Bengtsson et al. in J. Appl. Phys. 66, 1.231 (1989), the entire disclosure of which is hereby incorporated by reference). Moreover, crystal defects are usually associated with electronic states in the band gap. If they are for example located within the depletion region of a p-n junction, they may act as generation-recombination centers which enhance reverse leakage currents (see for example W. Shockley et al. in Phys. Rev. 87, 835 (1952), the entire disclosure of which is hereby incorporated by reference). Such defects are generated also during the removal of the surface oxide of the bonding partners by sputtering, causing their surfaces to be amorphized, which in turn results in a thin amorphous layer at the bonded interface (see for example C. Flotgen et al. in ECS Transactions 64, 103 (2014), the entire disclosure of which is hereby incorporated by reference). The electronic states associated with such defects may be passivated to some extent by hydrogen (see for example A. Loshachenko et al. in Phys. Status Solidi C 10, 36 (2013) and International Publication No. WO 2017/141103 to von Kanel, the entire disclosures of which are hereby incorporated by reference). It is neither certain, however, that hydrogen passivation will cause fully unimpeded charge transport across the bonded interface between lightly doped bonding partners, nor is there a guarantee for long term stability of the passivation under detector operation.

[0012] There is hence a need for covalently bonded detector structures which do not suffer from increased leakage currents generated by defect related states in the band gap. There is a need for structures and processes capable of minimizing the effect of generation/recombination currents generated by defect states created during surface activation and wafer bonding.

SUMMARY OF THE INVENTION

[0013] A monolithic CMOS integrated pixel detector is provided for the detection of electromagnetic radiation configured for backside illumination with a fill factor (sensitive area) close to 100%. The detector is made up of a silicon readout wafer, and an absorber wafer. The silicon readout wafer is made from silicon of a first doping type, made up of CMOS pixel readout electronics processed in a thin silicon layer and including highly conducting doped regions of a second doping type acting as charge collectors spaced at the pixel size which communicate with the readout electronics, and at least one wafer alignment feature. The absorber wafer is made from at least one single crystal semiconductor material. The absorber wafer also includes highly conducting doped regions, and at least one wafer alignment feature. The monolithic CMOS integrated pixel detector consists of the readout wafer bonded, in an aligned manner, to the absorber wafer. The wafer bonds include conducting bonds between the readout wafer and the absorber wafer and poorly conducting bonds between the readout wafer and the absorber wafer, the poorly conducting bonds electrically isolating neighboring pixels to force charges generated in the absorber wafer to cross the conducting bonds and to be received by the charge collectors for processing by the pixel readout electronics when the detector is in operation.

[0014] Even better isolation of neighboring pixels is achieved by pixelated absorbers consisting of absorber patches separated by dielectric regions and/or existing dielectric regions in the readout wafer serving for the same purpose.

[0015] It is an object of the invention to provide a monolithic CMOS integrated pixel sensor suitable for electromagnetic radiation detection and imaging.

[0016] It is another object of the invention to provide a monolithic pixel sensor suitable for electromagnetic radiation detection and imaging, wherein the readout electronics and a single crystalline absorber are juxtaposed on opposite sides of a CMOS processed silicon wafer.

[0017] It is yet another object of the invention to provide a monolithic CMOS integrated pixel sensor suitable for electromagnetic radiation detection and imaging which is fabricated by low temperature direct wafer bonding of readout and absorber wafers.

[0018] It is a further object of the invention to provide a monolithic pixel sensor suitable for the detection and imaging of infrared, visible, ultraviolet or soft X-ray radiation which is fabricated by bonding a thin absorber layer onto a CMOS processed wafer with the readout electronics.

[0019] It is a further object of the invention to provide a monolithic pixel sensor suitable for high-energy X-ray detection and imaging which is fabricated by bonding a CMOS processed wafer with the readout electronics onto a high-Z absorber layer.

[0020] It is yet a further object of the invention to provide a monolithic pixel sensor suitable for energy-resolved X-ray detection and imaging.

[0021] It is yet another object of the invention to provide a monolithic pixel sensor capable of single-photon detection.

[0022] It is yet a further object of the invention to provide simple processes for the fabrication of monolithic pixel detectors made up of a thin readout wafer covalently bonded to an absorber wafer of the opposite conduction type (i.e. opposite effective doping type).

[0023] It is an object of the invention to provide covalently bonded pixel sensors in which defects present at or near the bonding interface do not affect detector leakage.

[0024] The invention teaches the structure and fabrication methods of monolithic pixel detectors for electromagnetic radiation. The pixel detectors include a thin Si wafer with CMOS processed readout electronics communicating with a single crystalline absorber forming a monolithic unit. This monolithic unit is formed by wafer bonding a thinned, CMOS processed Si readout wafer onto an absorber wafer to collect and process the electrical signals generated by electromagnetic radiation incident on the absorber. These and other objects of the invention are described in the drawings, specification and claims.

[0025] In the description of this invention, the terms "pixel detector" and "pixel sensor" are considered as synonyms describing the detector as a whole. Likewise, the terms "absorber wafer" and "sensor wafer" are considered synonyms of the detector part in which electromagnetic radiation is absorbed.

BRIEF DESCRIPTION OF THE DRAWINGS

[0026] FIG. 1A is a cross-section of a monolithic pixel detector of the invention with the p-n junction between n.sup.--doped readout wafer and p.sup.--doped absorber wafer at the bonded interface.

[0027] FIG. 1B is a cross-section of a monolithic pixel detector of the invention with the p-n junction inside the n.sup.--doped readout wafer which is bonded to a p.sup.--doped absorber wafer.

[0028] FIG. 1C is a cross-section of a monolithic pixel detector of the invention with the p-n junction between p.sup.--doped readout wafer and n.sup.--doped absorber wafer at the bonded interface.

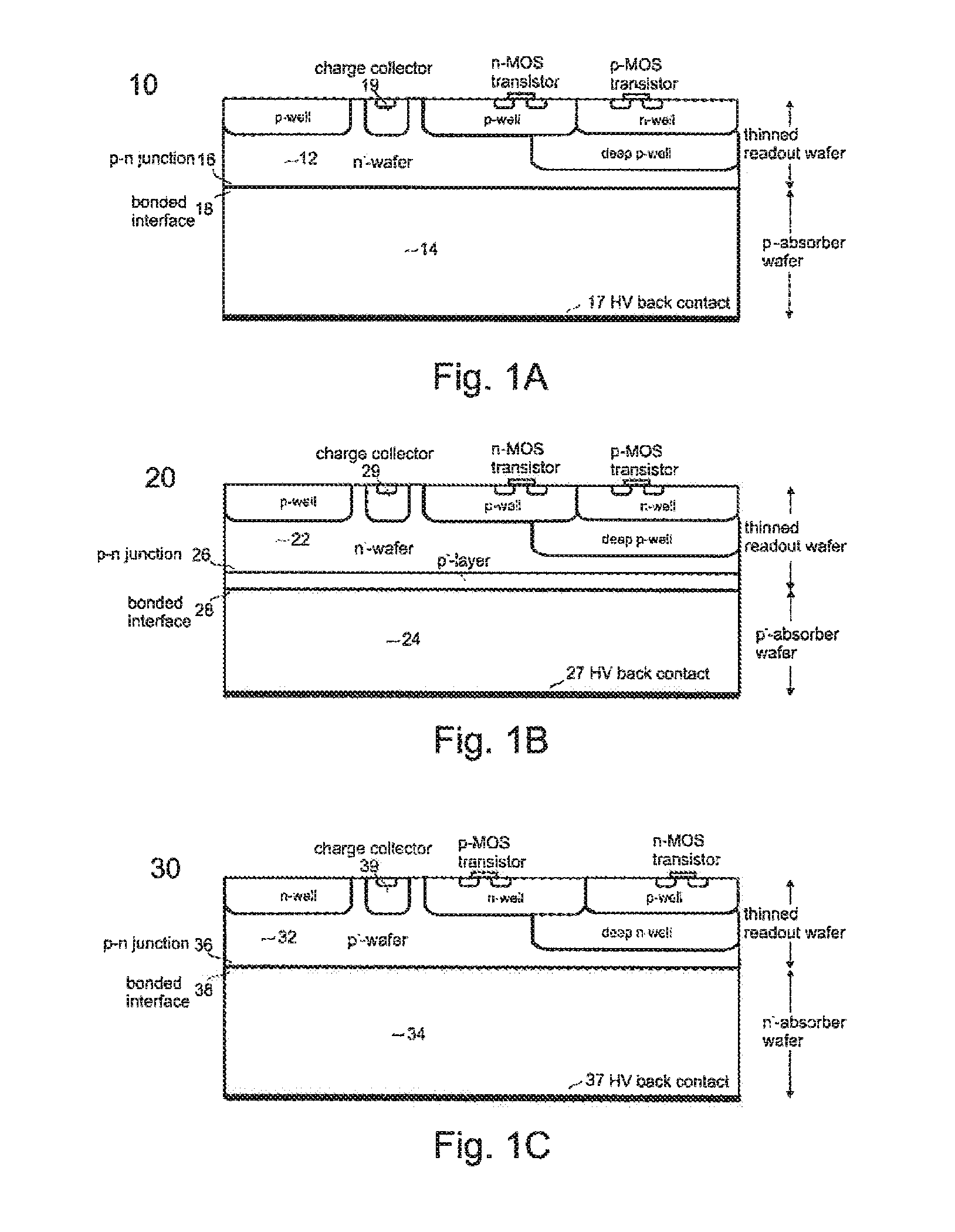

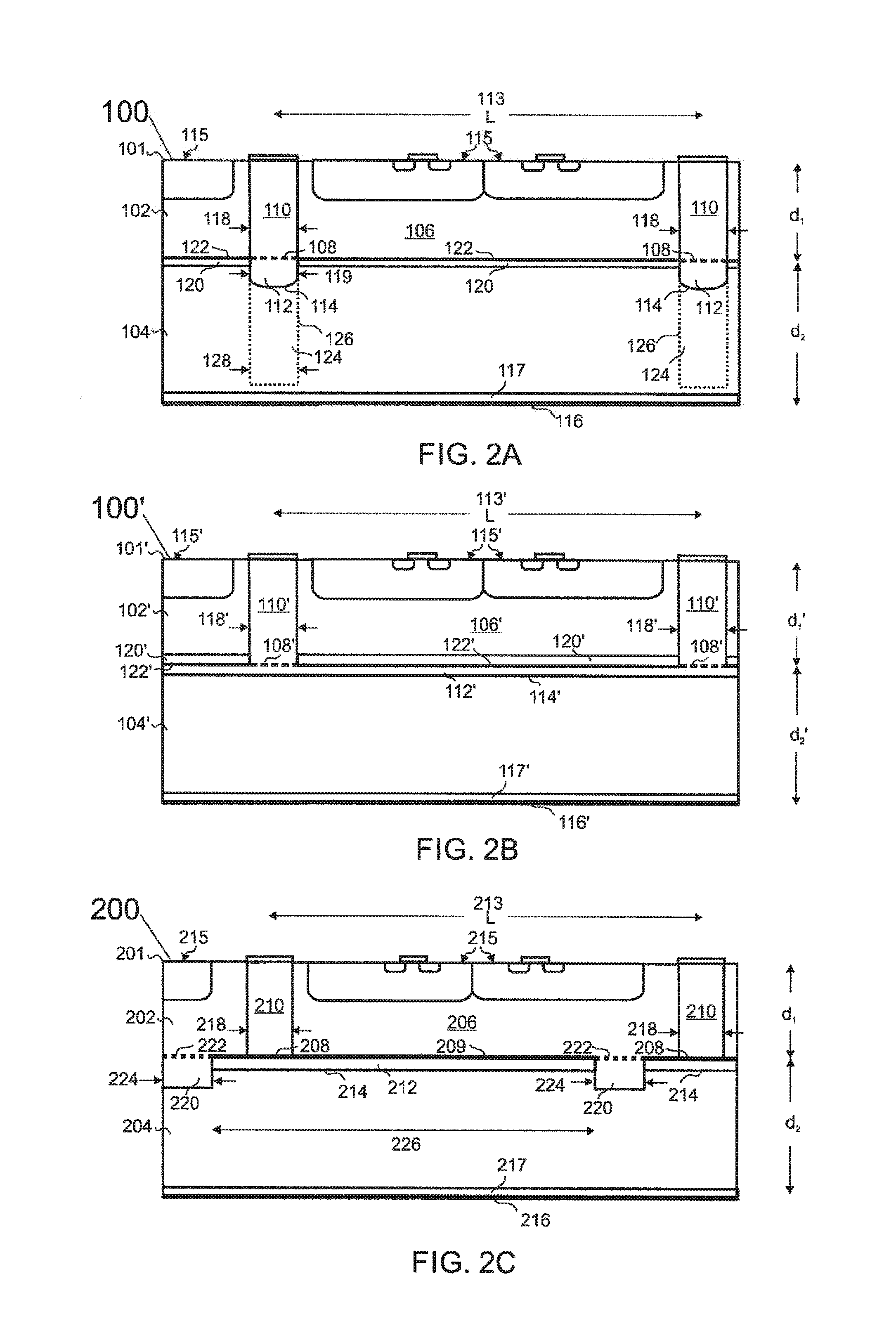

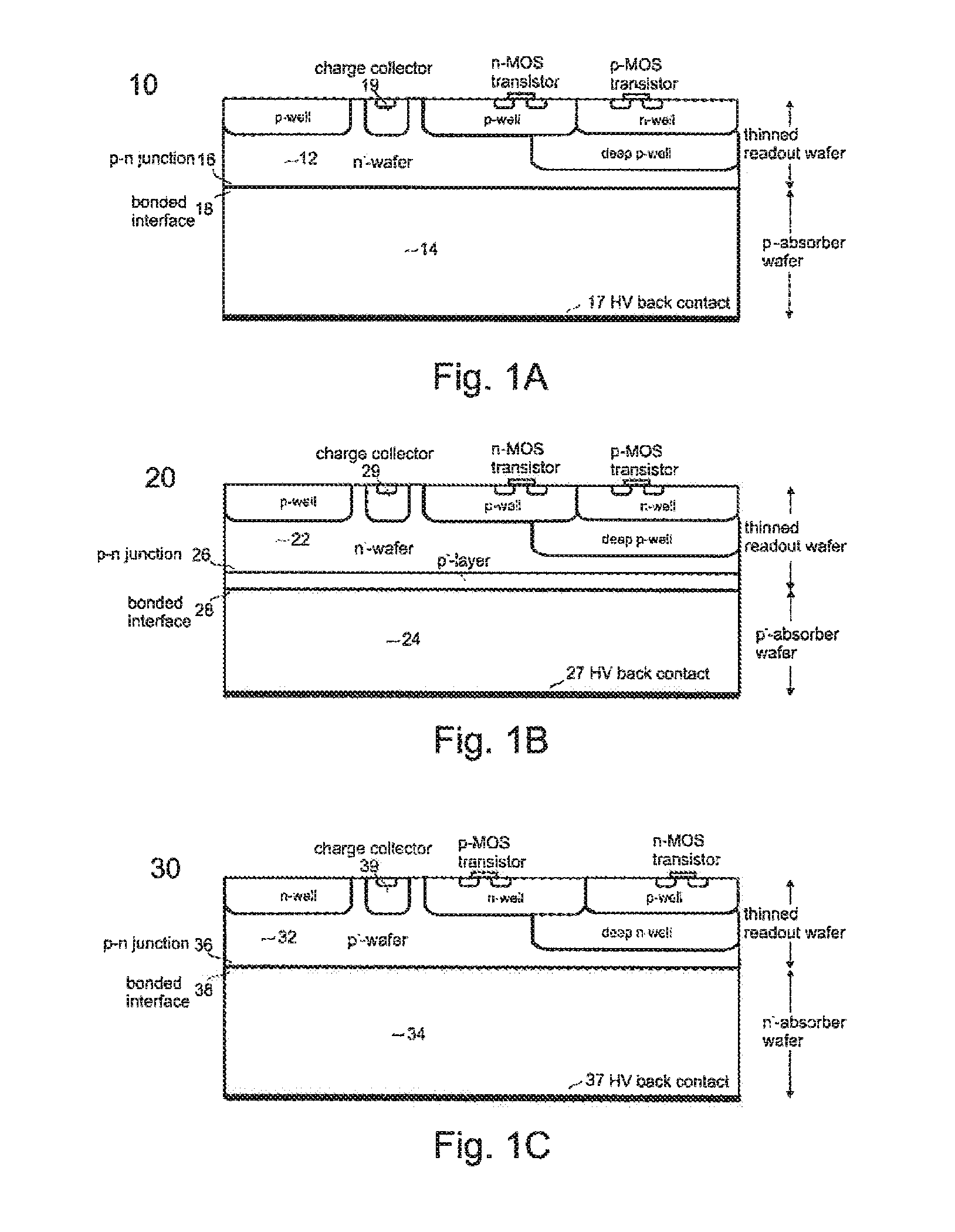

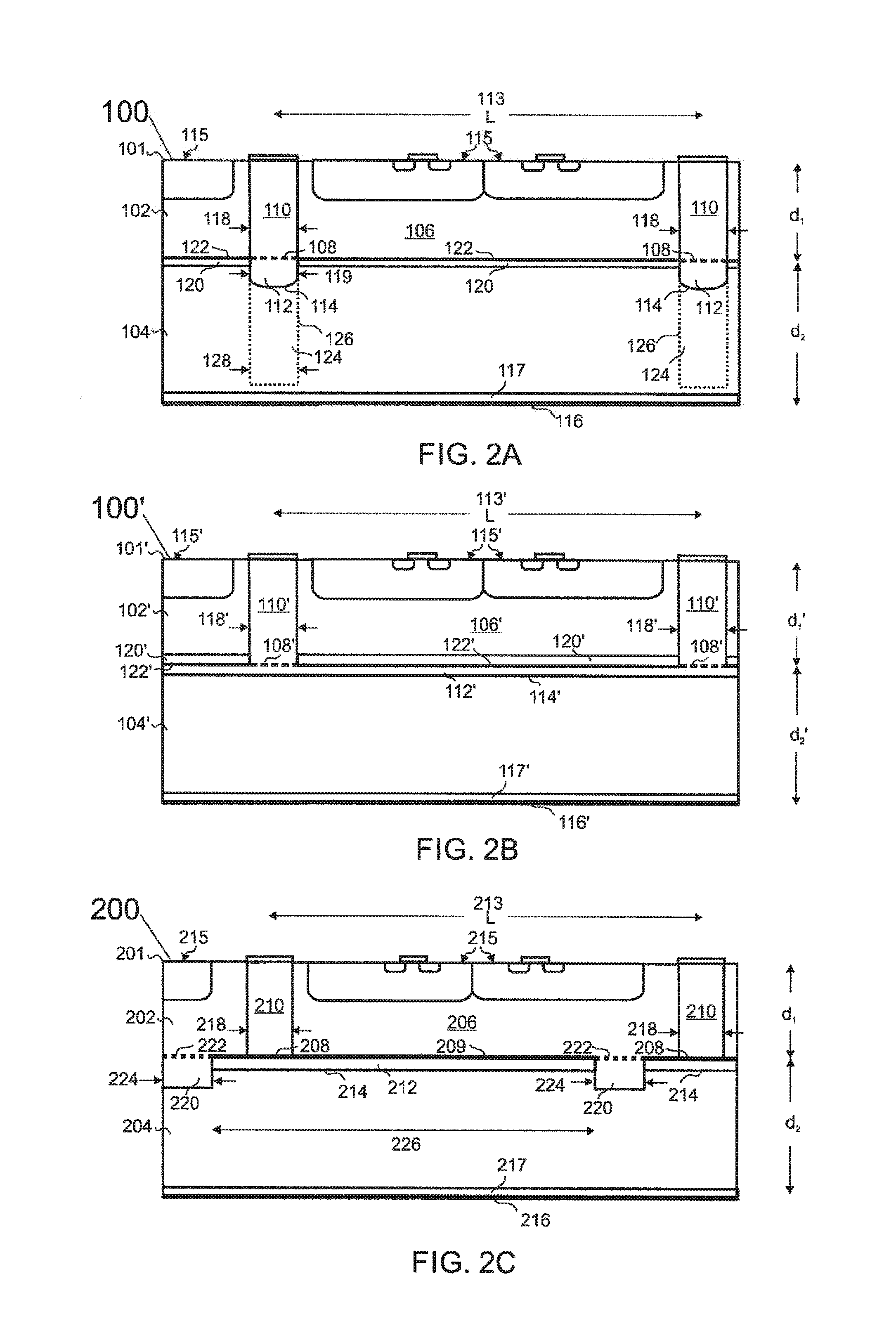

[0029] FIG. 2A is a cross-section of a monolithic pixel detector of the invention with charge collection through covalent semiconductor bonds between n.sup.+-doped regions in readout and absorber wafer and oxide-to-oxide bonds for pixel isolation.

[0030] FIG. 2B is a cross-section of a monolithic pixel detector of the invention with charge collection through covalent semiconductor bonds between n.sup.+-doped regions in readout and absorber wafer and non-conducting bonds for pixel separation.

[0031] FIG. 2C is a cross-section of a monolithic pixel detector of the invention with charge collection through covalent semiconductor bonds between n.sup.+-doped regions in readout and absorber wafer and non-conducting bonds between oxide regions of the absorber wafer and the readout wafer for pixel separation.

[0032] FIG. 2D is a cross-section of a monolithic pixel detector of the invention with charge collection through covalent semiconductor bonds between n.sup.+-doped regions in readout and absorber wafer, covalent p.sup.--n.sup.+ bonds and trench isolation for pixel separation.

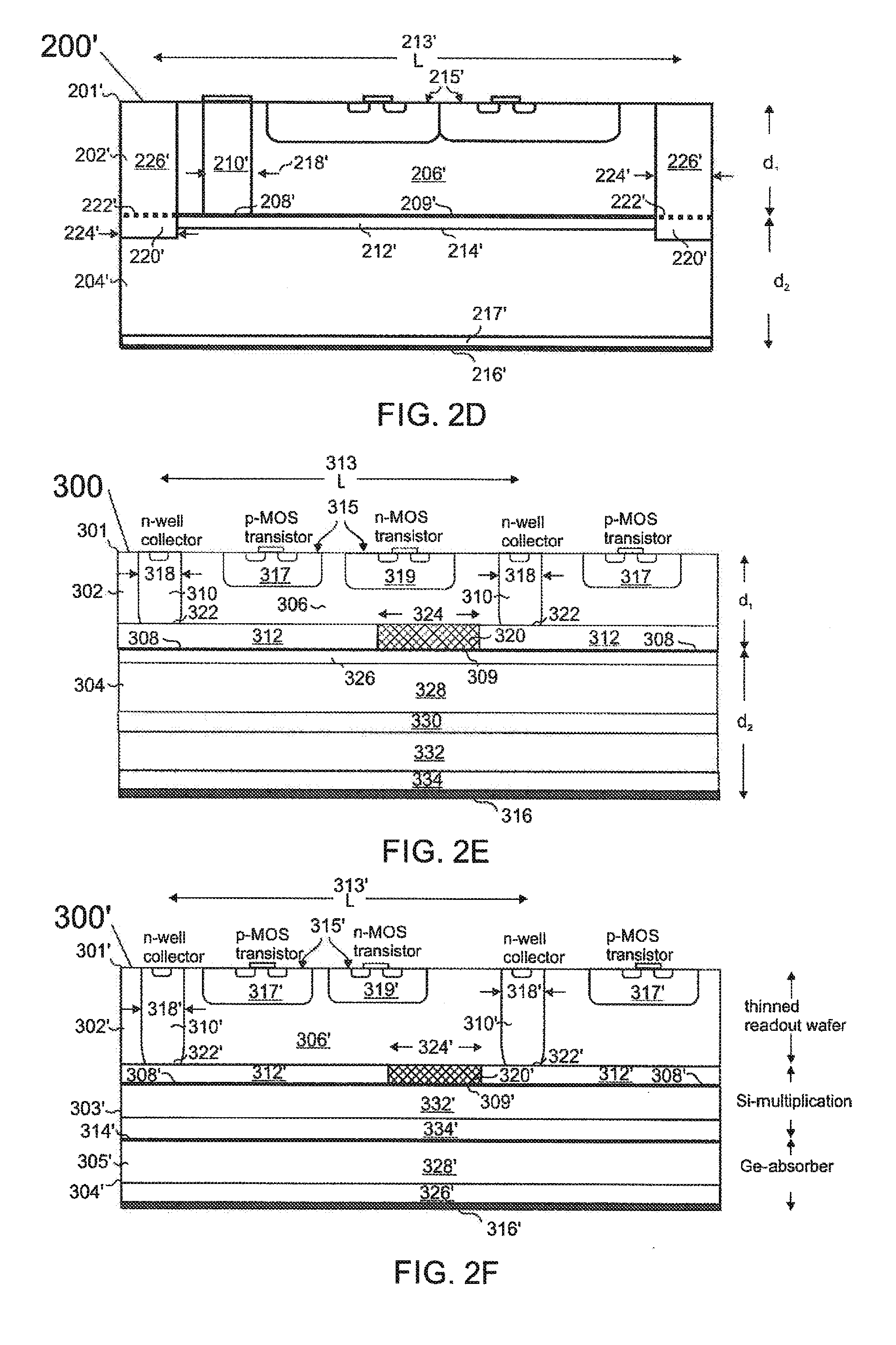

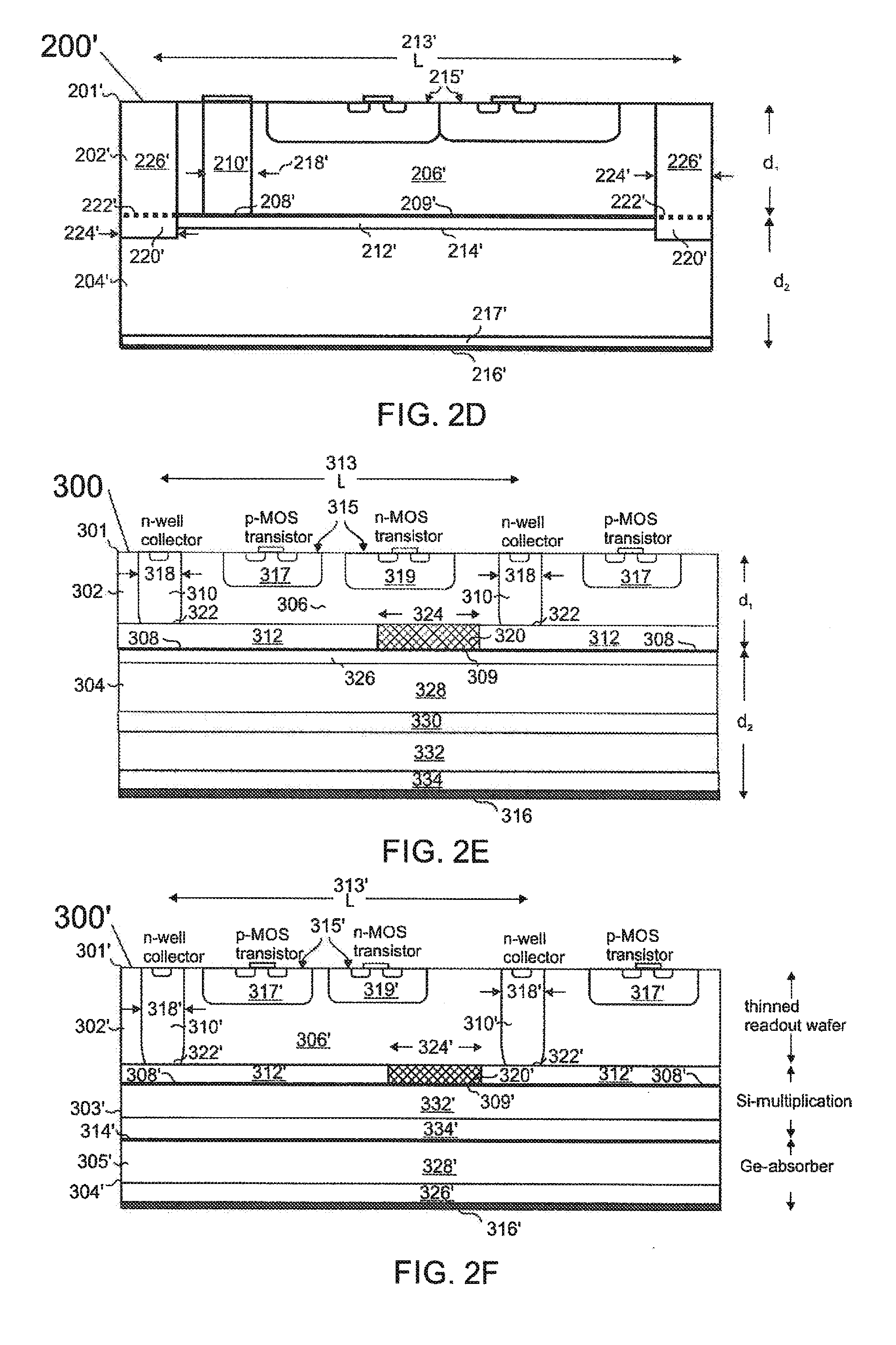

[0033] FIG. 2E is a cross-section of a monolithic pixel detector of the invention with charge collection through covalent semiconductor bonds between n.sup.+-doped regions in readout and absorber wafer and non-conducting bonds between highly resistive regions of the readout wafer and n.sup.+-doped regions in the absorber wafer, wherein the absorber wafer contains a region for charge multiplication.

[0034] FIG. 2F is a cross-section of a monolithic pixel detector of the invention with charge collection through a first covalent semiconductor bond between n.sup.+-doped regions in a readout wafer and the charge multiplication region of a silicon wafer, and a second covalent semiconductor bond between the silicon wafer and an absorber wafer.

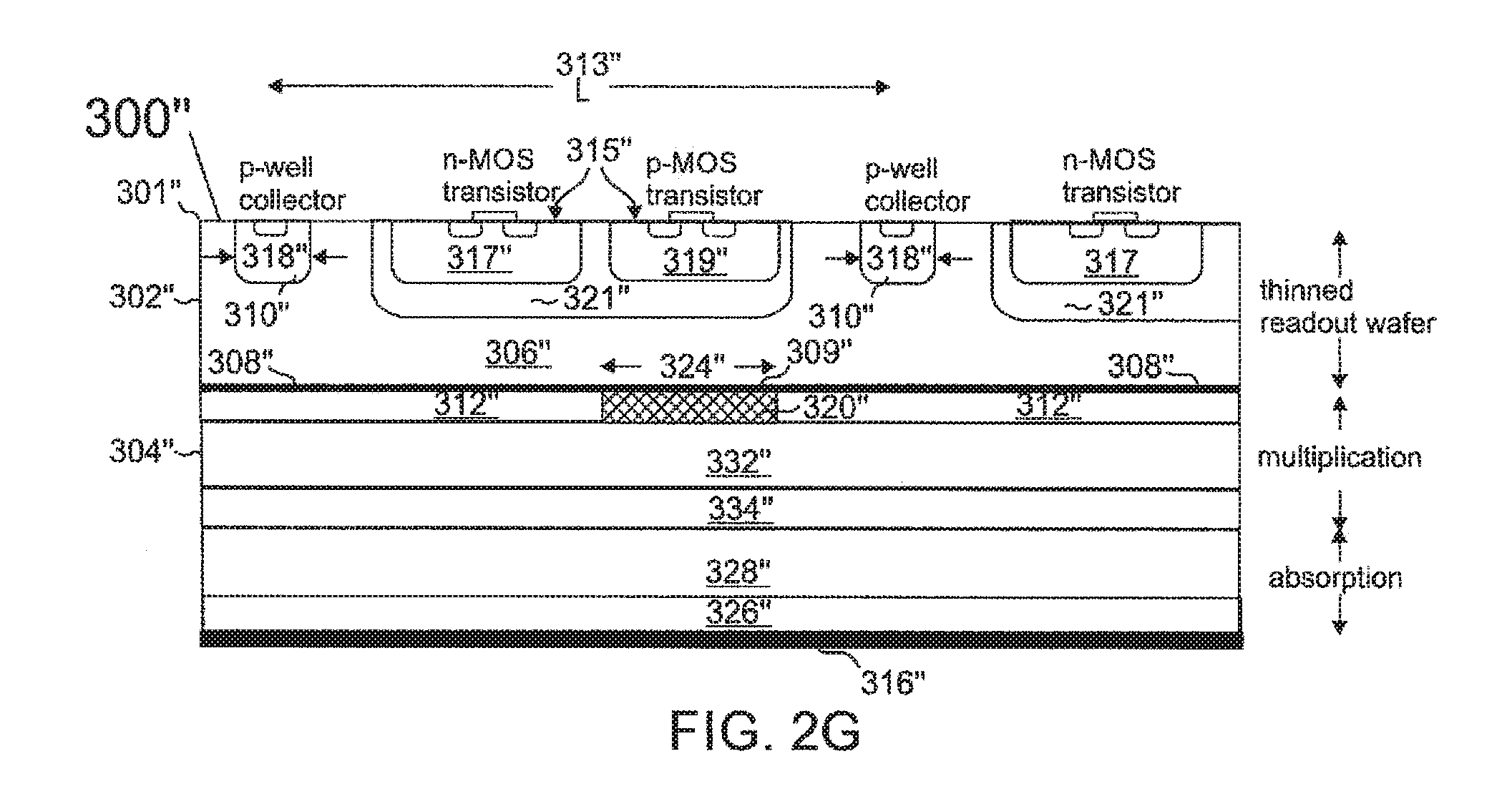

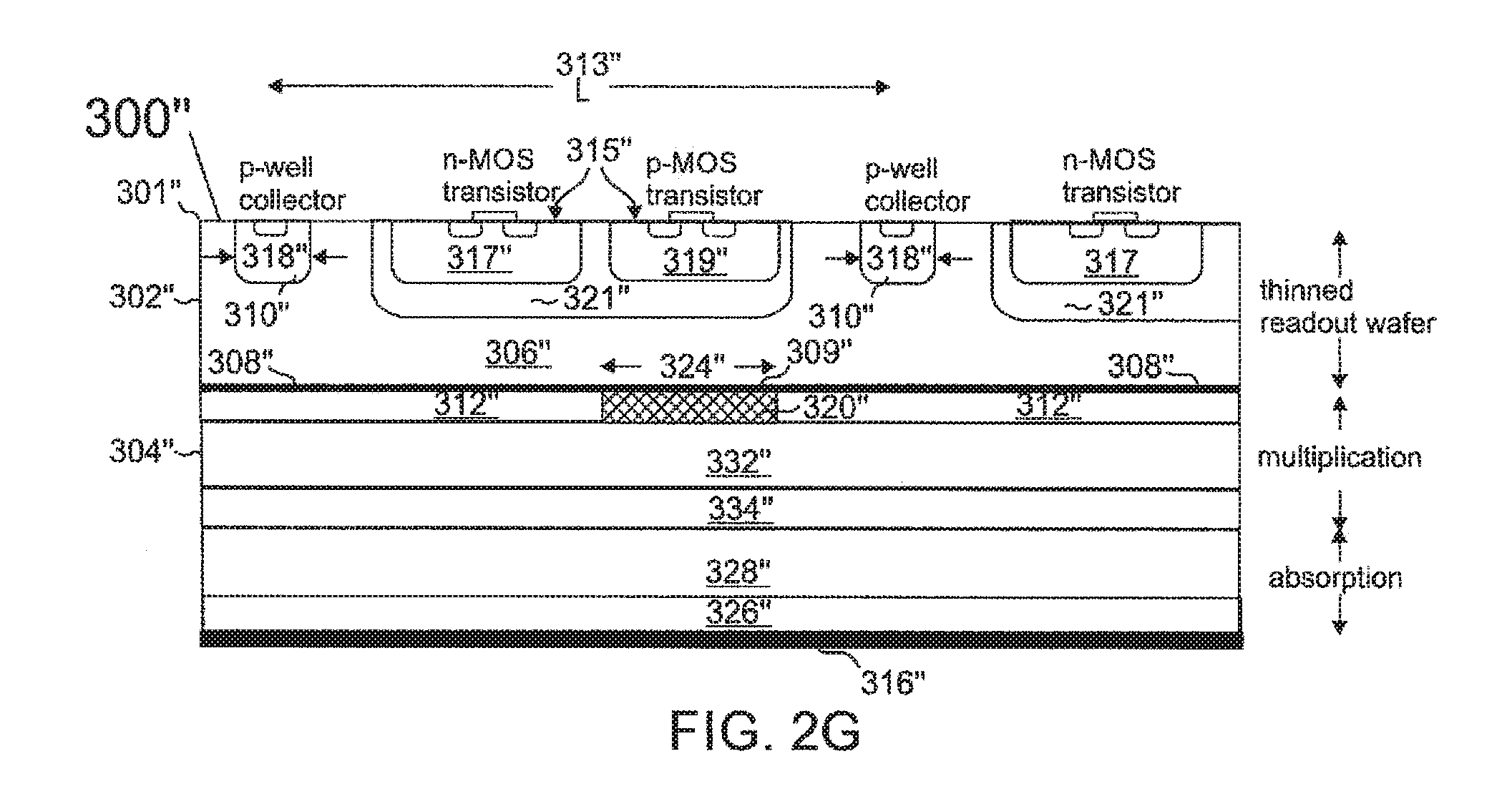

[0035] FIG. 2G is a cross-section of a monolithic pixel detector of the invention with charge collection through covalent semiconductor bonds between weakly p-doped regions of a readout wafer and p.sup.+-doped regions of an absorber wafer, non-conducting bonds between highly resistive regions of the absorber wafer and a weakly p-doped region of the readout wafer, wherein the absorber wafer contains a region for charge multiplication.

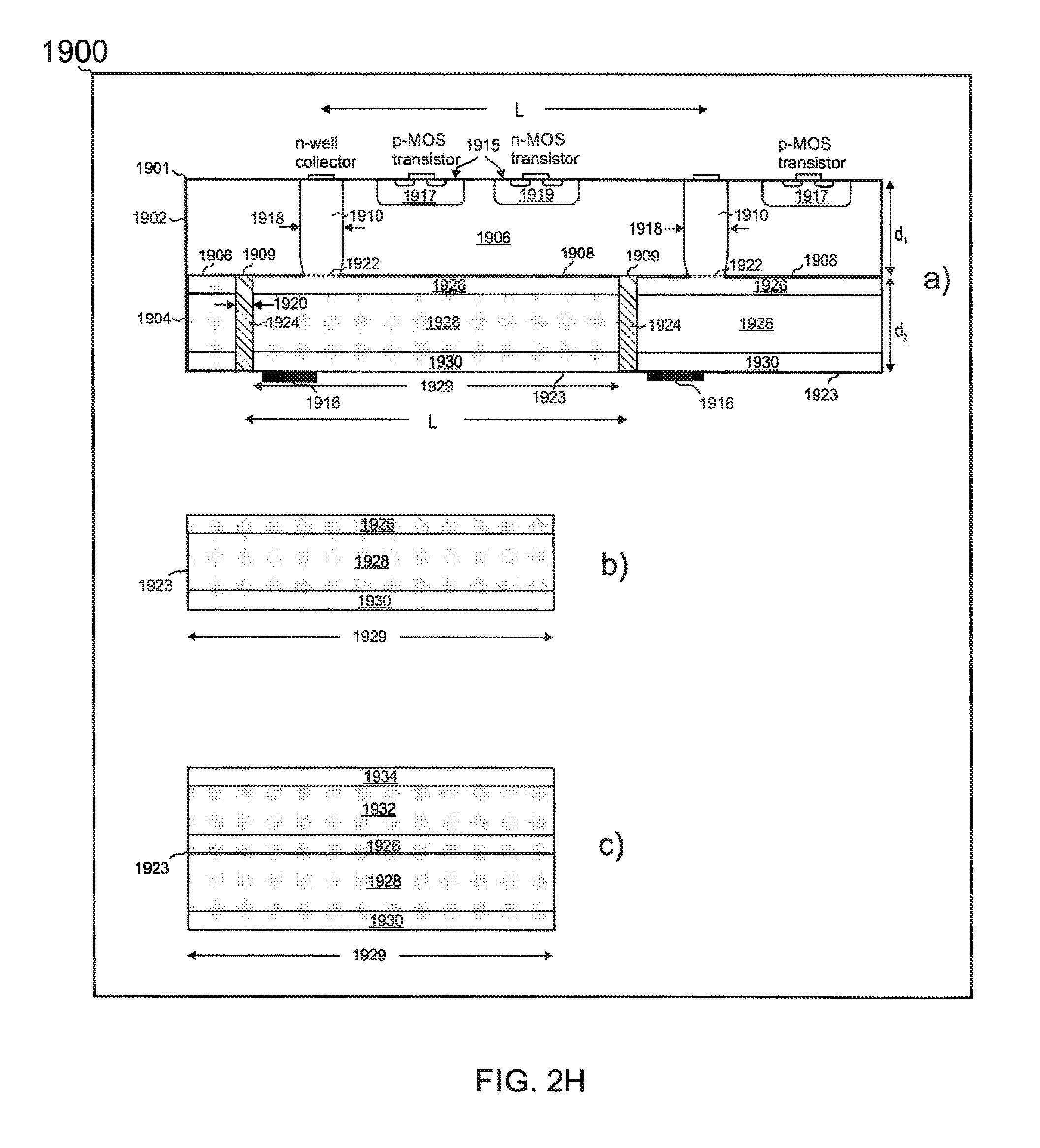

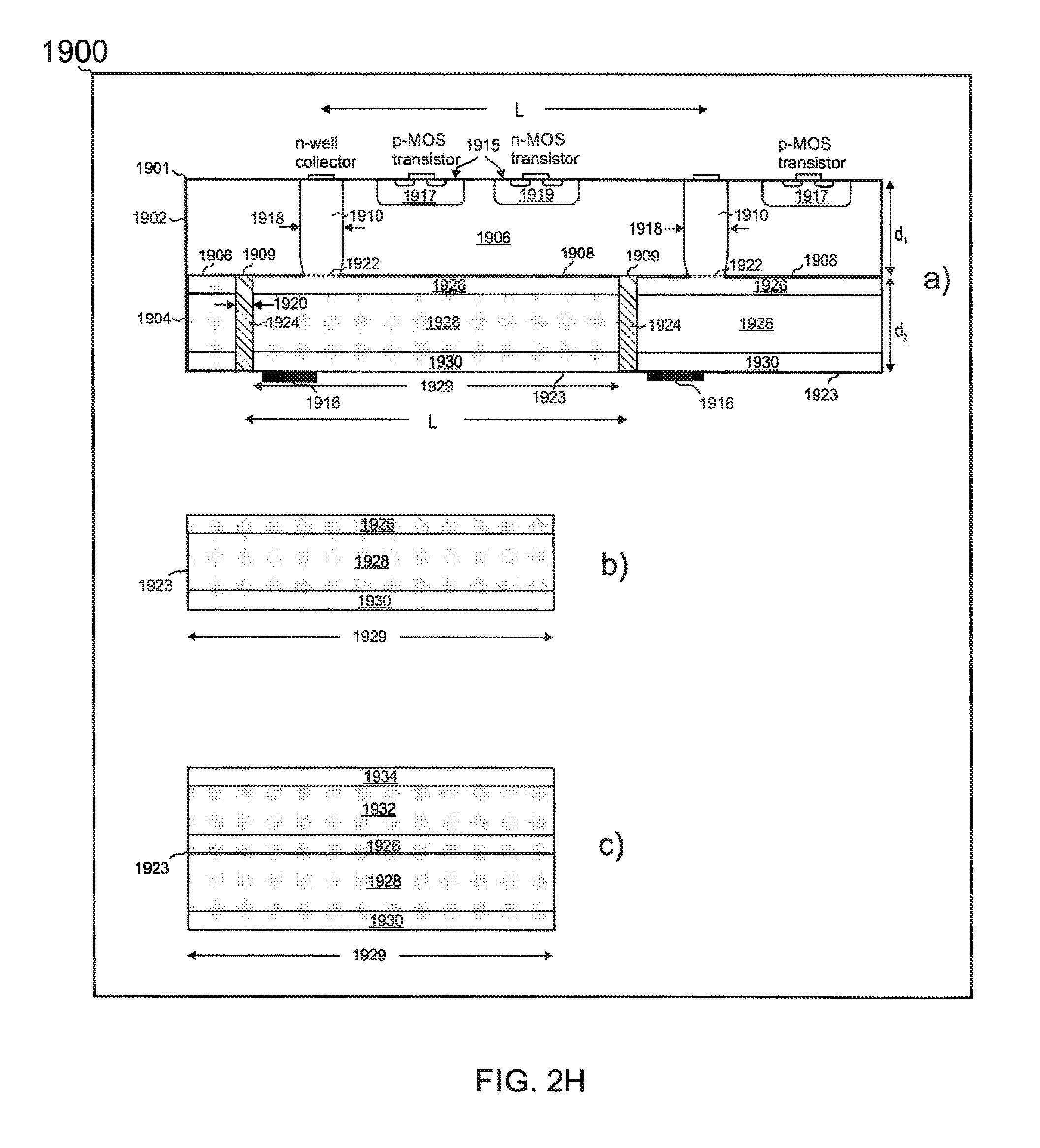

[0036] FIG. 2H is a schematic diagram showing a cross-section of a monolithic pixel detector of the invention with charge collection through covalent semiconductor bonds between mutually aligned n.sup.+-doped regions of a readout wafer and the pixels of a pixelated absorber wafer made up of p-i-n junctions or absorber and multiplication regions mutually isolated by insulating regions.

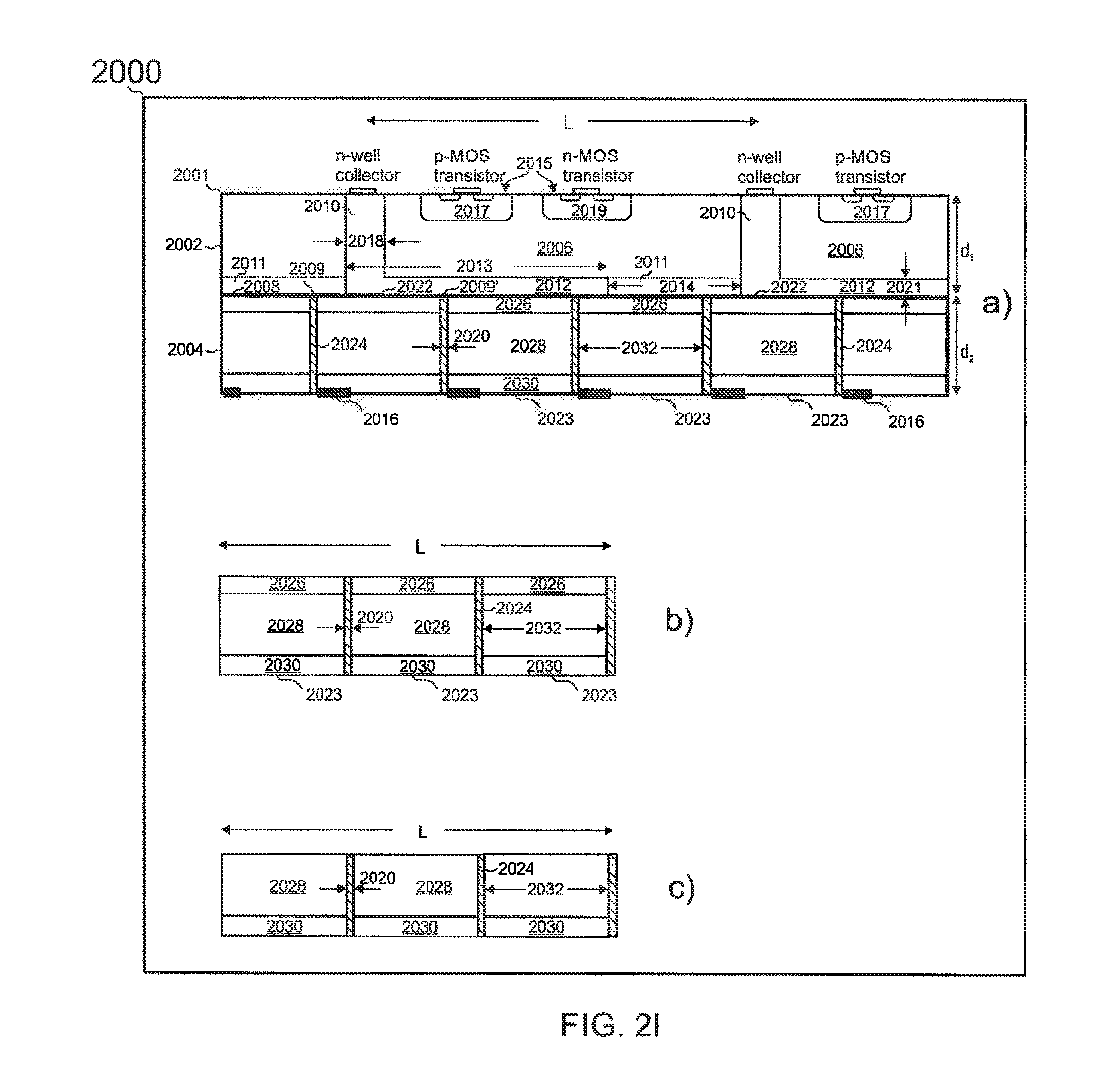

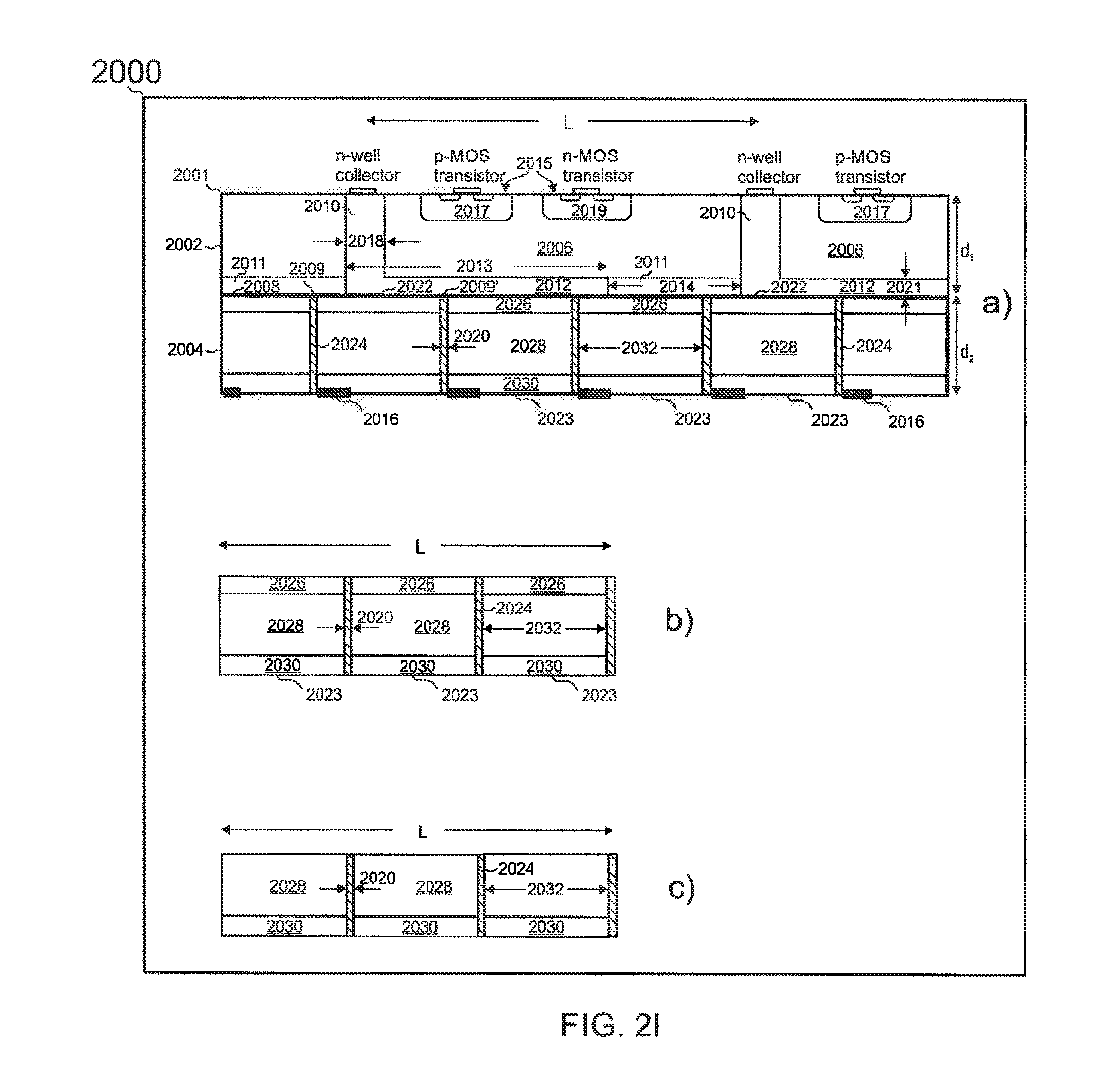

[0037] FIG. 2I is a schematic diagram showing a cross-section of a monolithic pixel detector of the invention with charge collection through covalent semiconductor bonds between n.sup.+-doped regions of a readout wafer and a pixelated absorber wafer made up of doped layers and pixels mutually isolated by insulating regions.

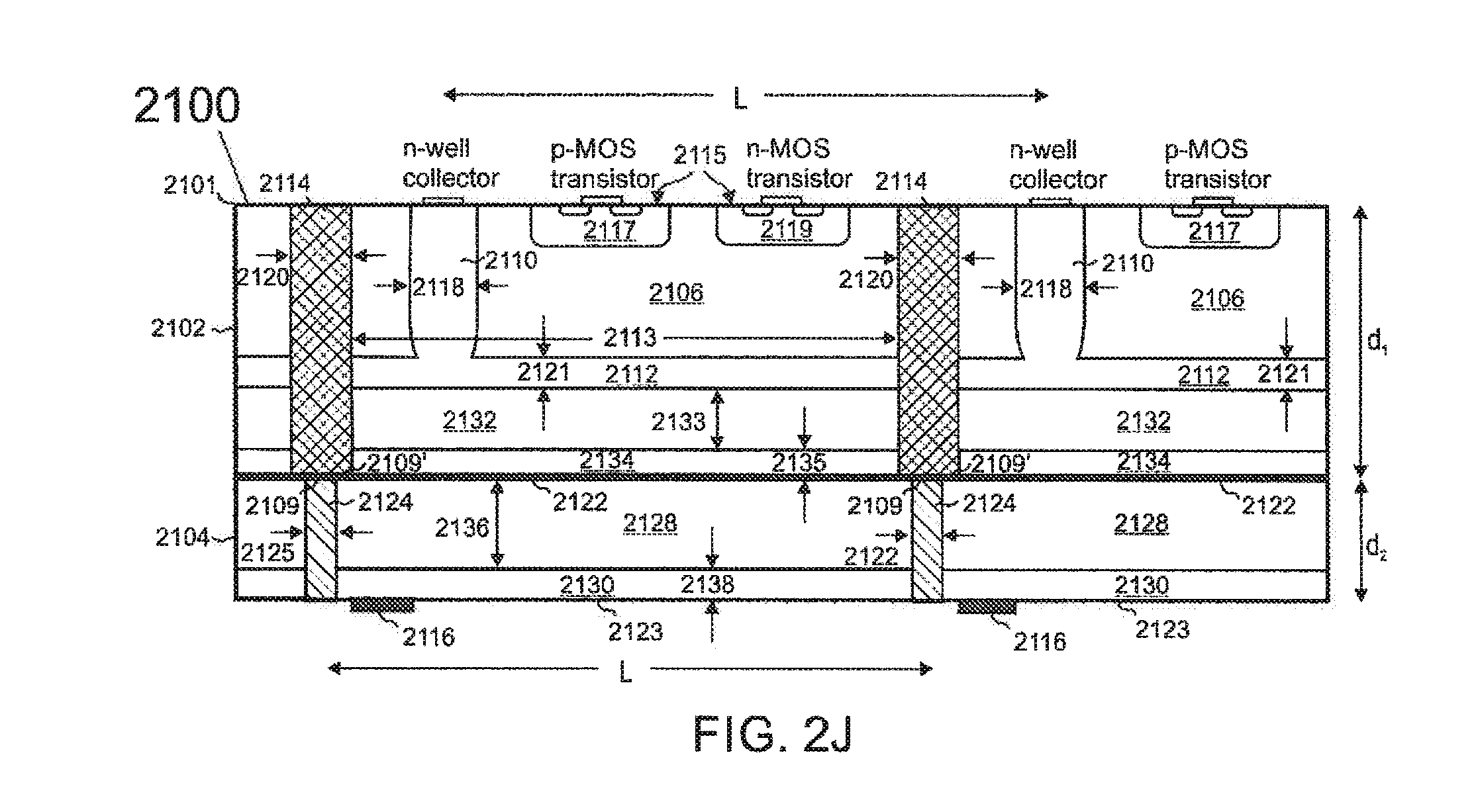

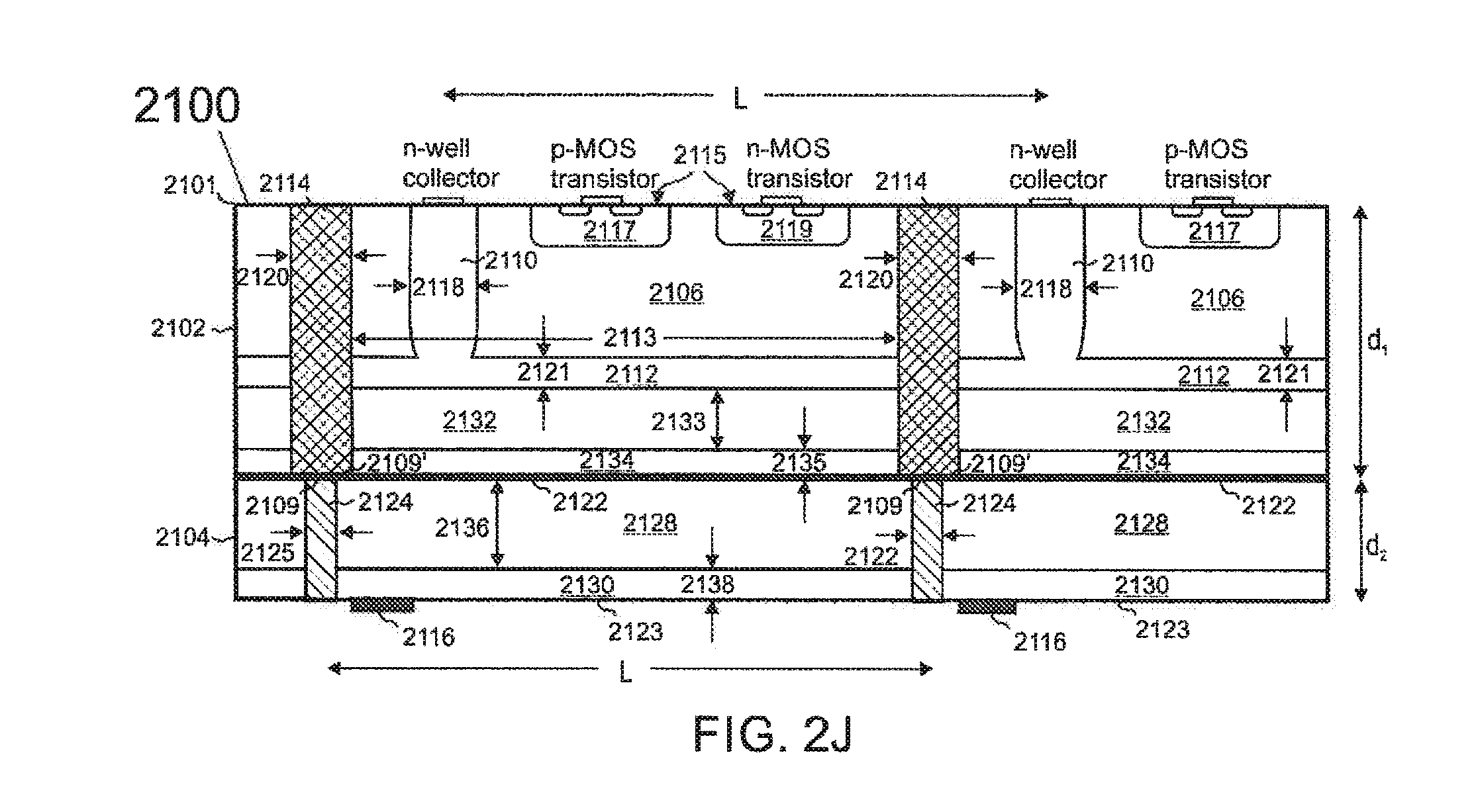

[0038] FIG. 2J is a cross-section of a monolithic pixel detector of the invention with charge collection both through covalent semiconductor bonds between a readout wafer containing multiplication regions and the pixels of a pixelated absorber wafer, wherein the pixels of readout and absorber wafers are mutually aligned and isolated by insulating regions.

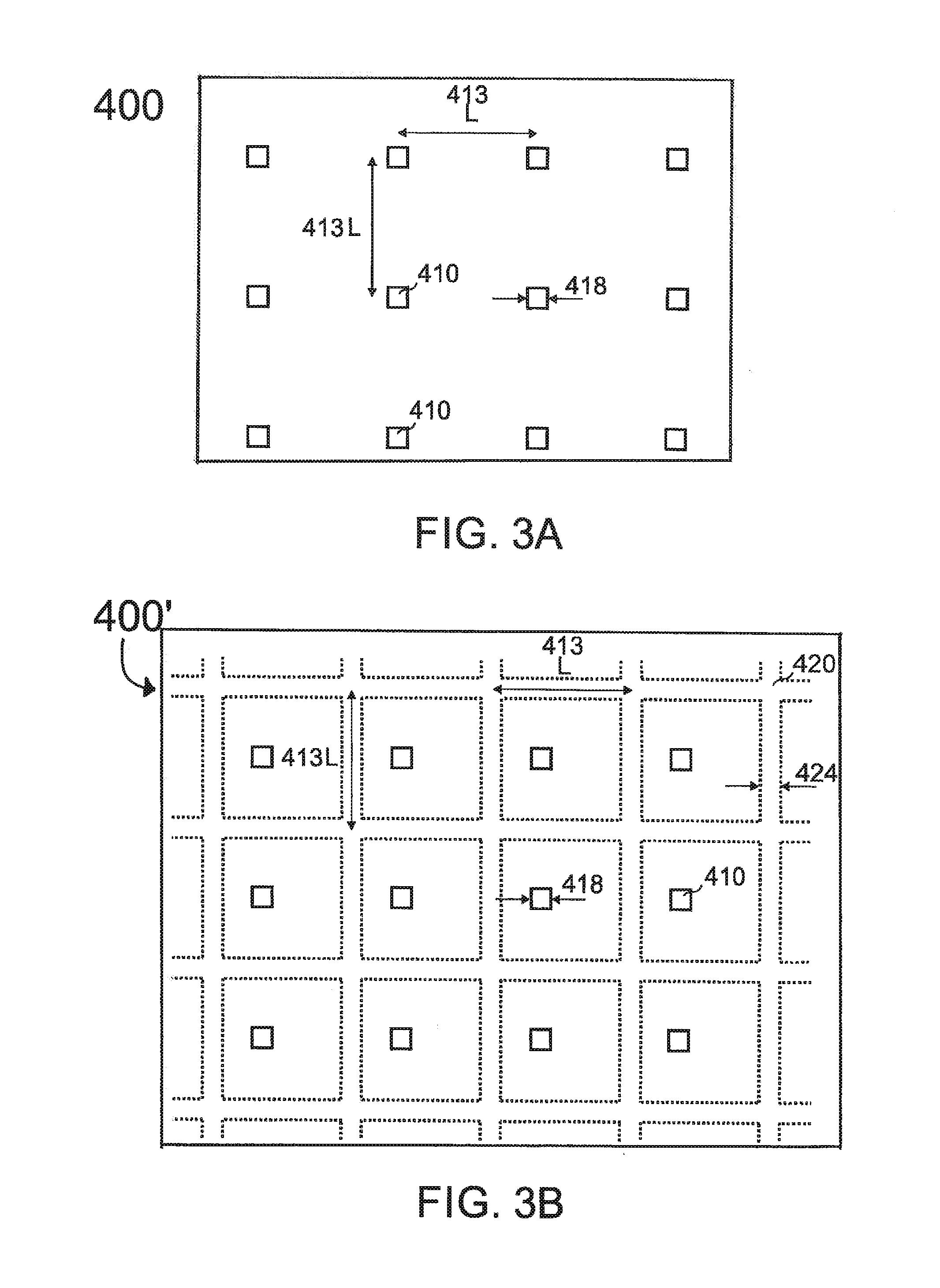

[0039] FIG. 3A is a plan-view of the charge collectors of a monolithic pixel detector of the invention.

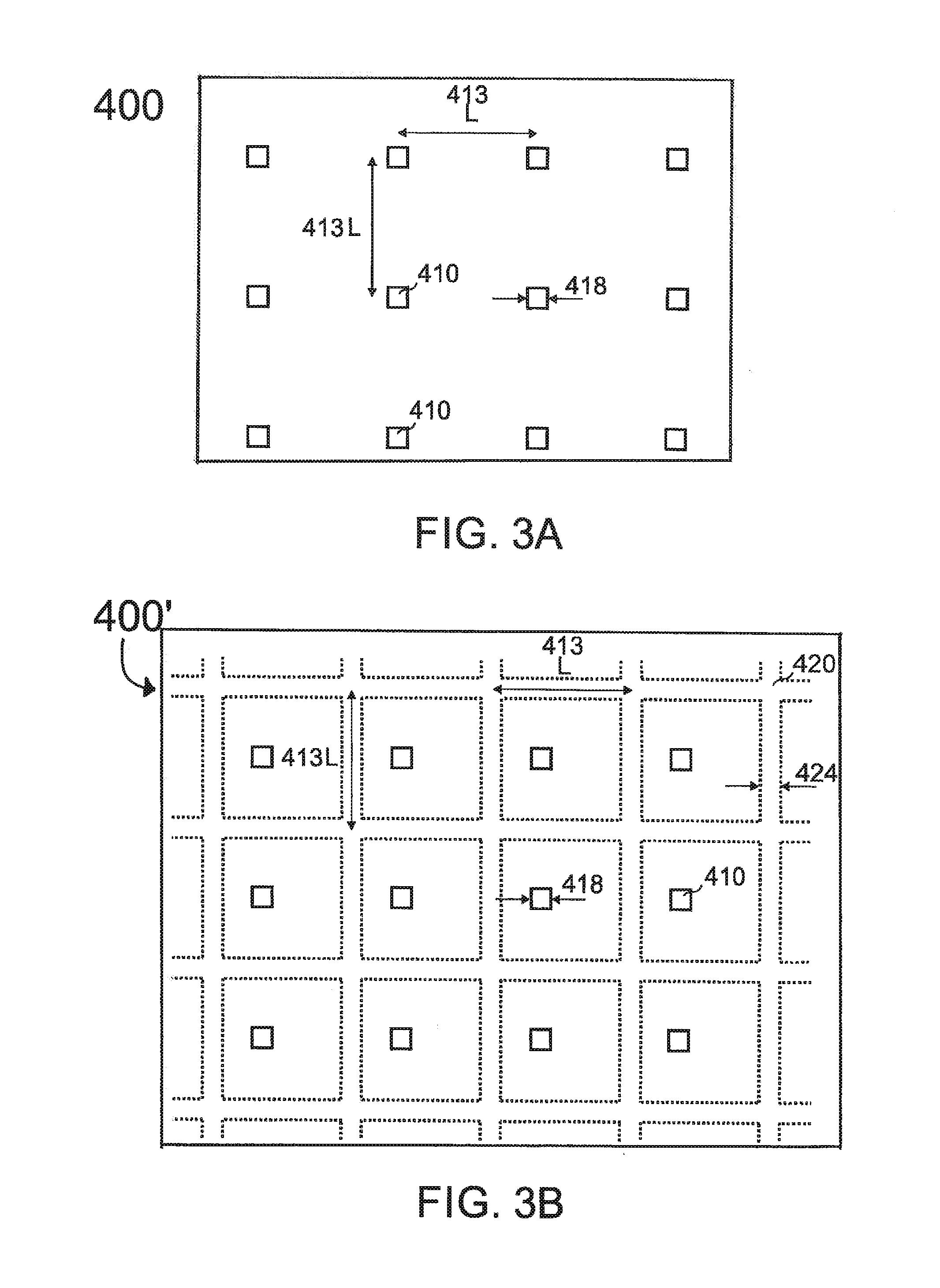

[0040] FIG. 3B is a plan-view of the charge collectors and the oxide regions surrounding the pixels of a monolithic pixel detector of the invention.

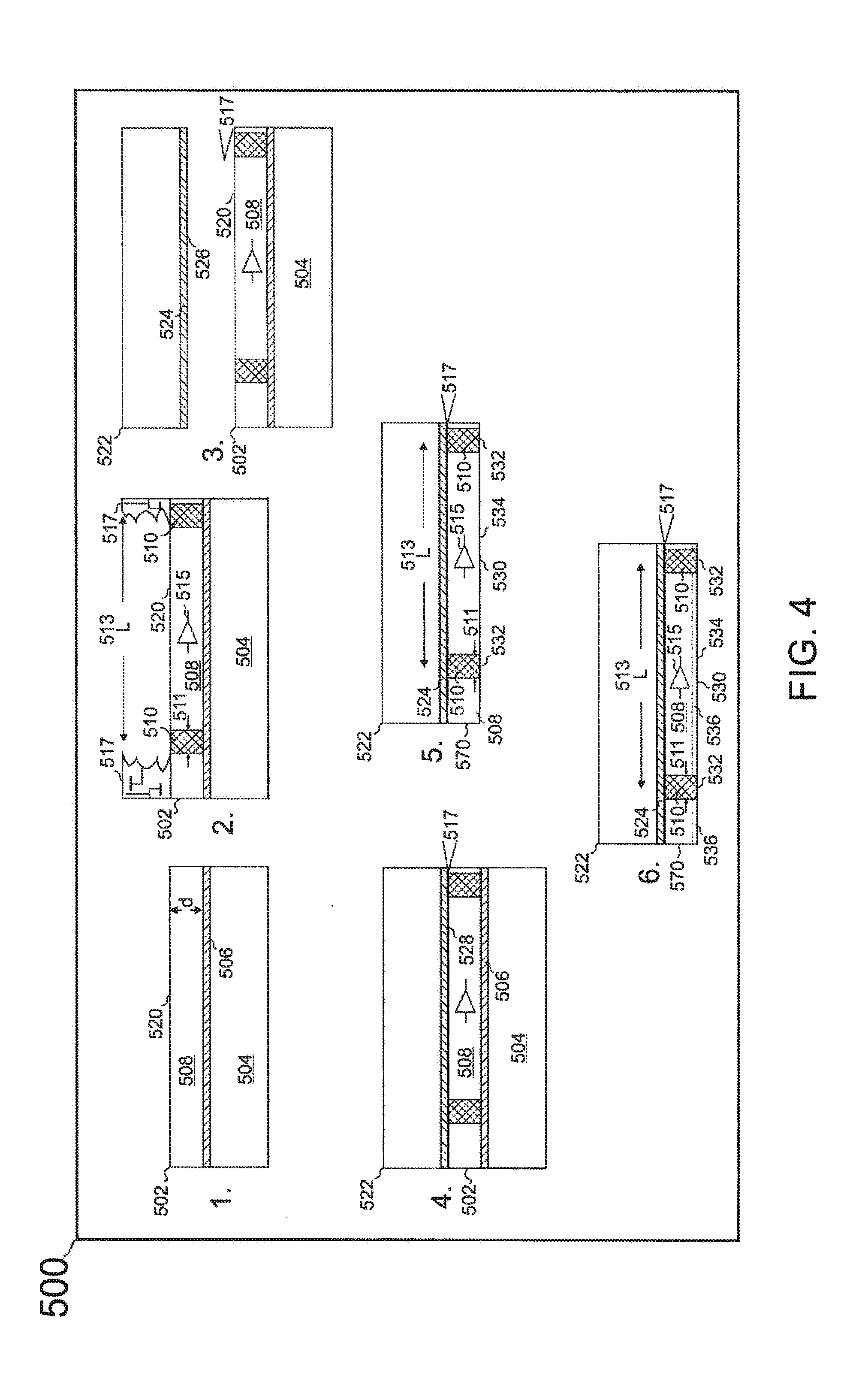

[0041] FIG. 4 is a schematic diagram showing the process flow of the invention for the fabrication of a thin readout wafer of the invention with highly doped charge collector plugs.

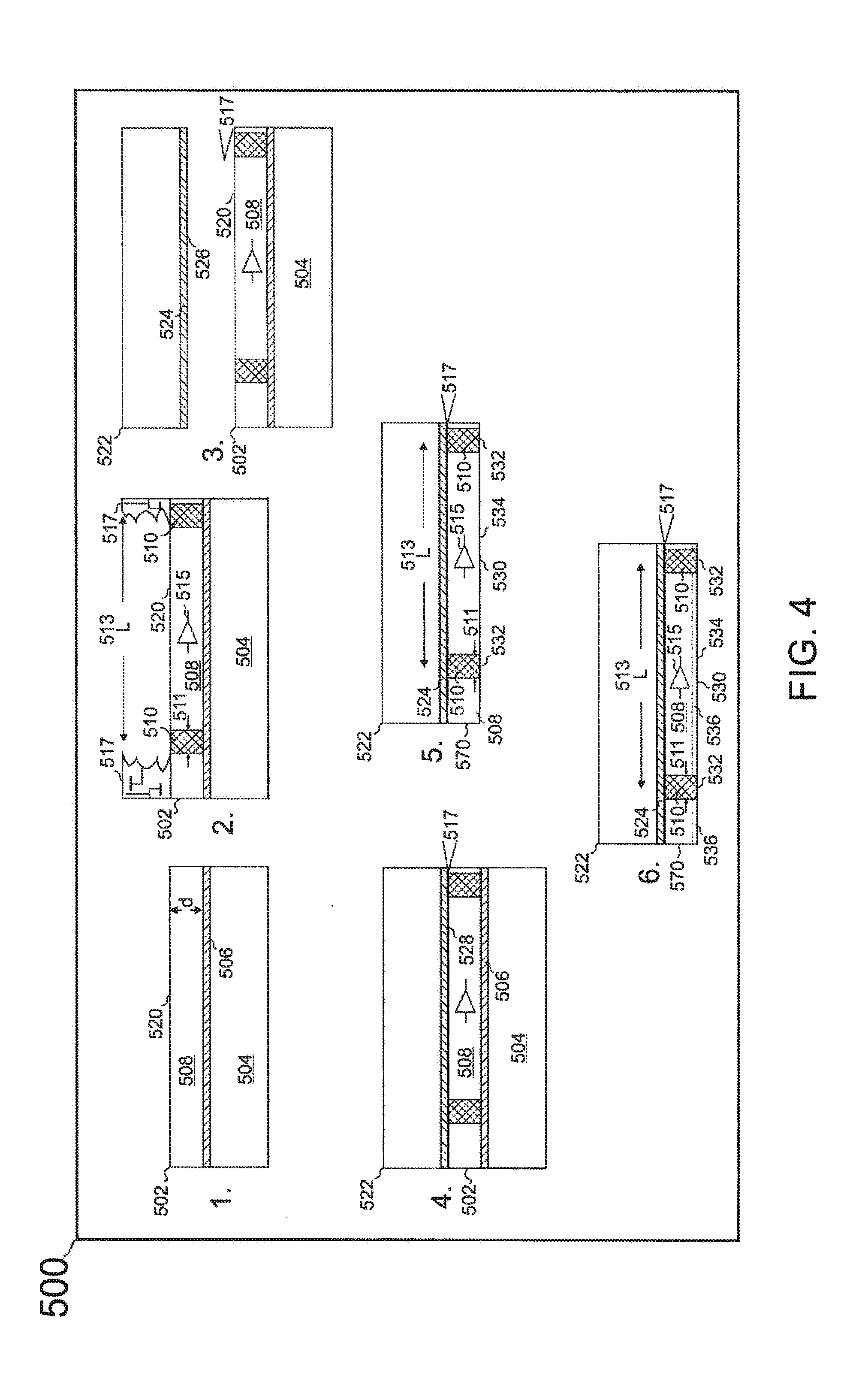

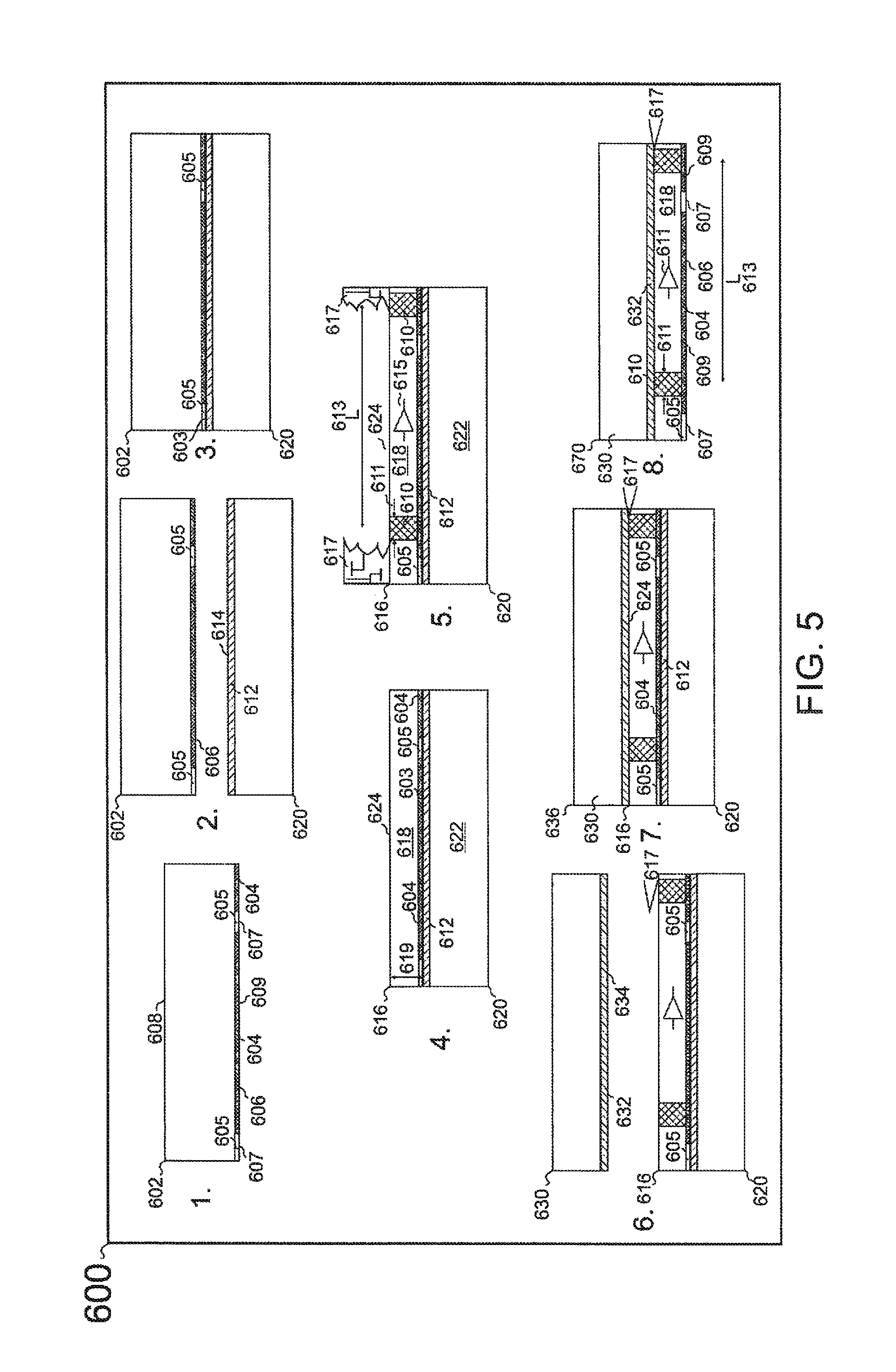

[0042] FIG. 5 is a schematic diagram showing the process flow of the invention for the fabrication of a thin readout wafer of the invention with highly doped charge collector plugs and implants.

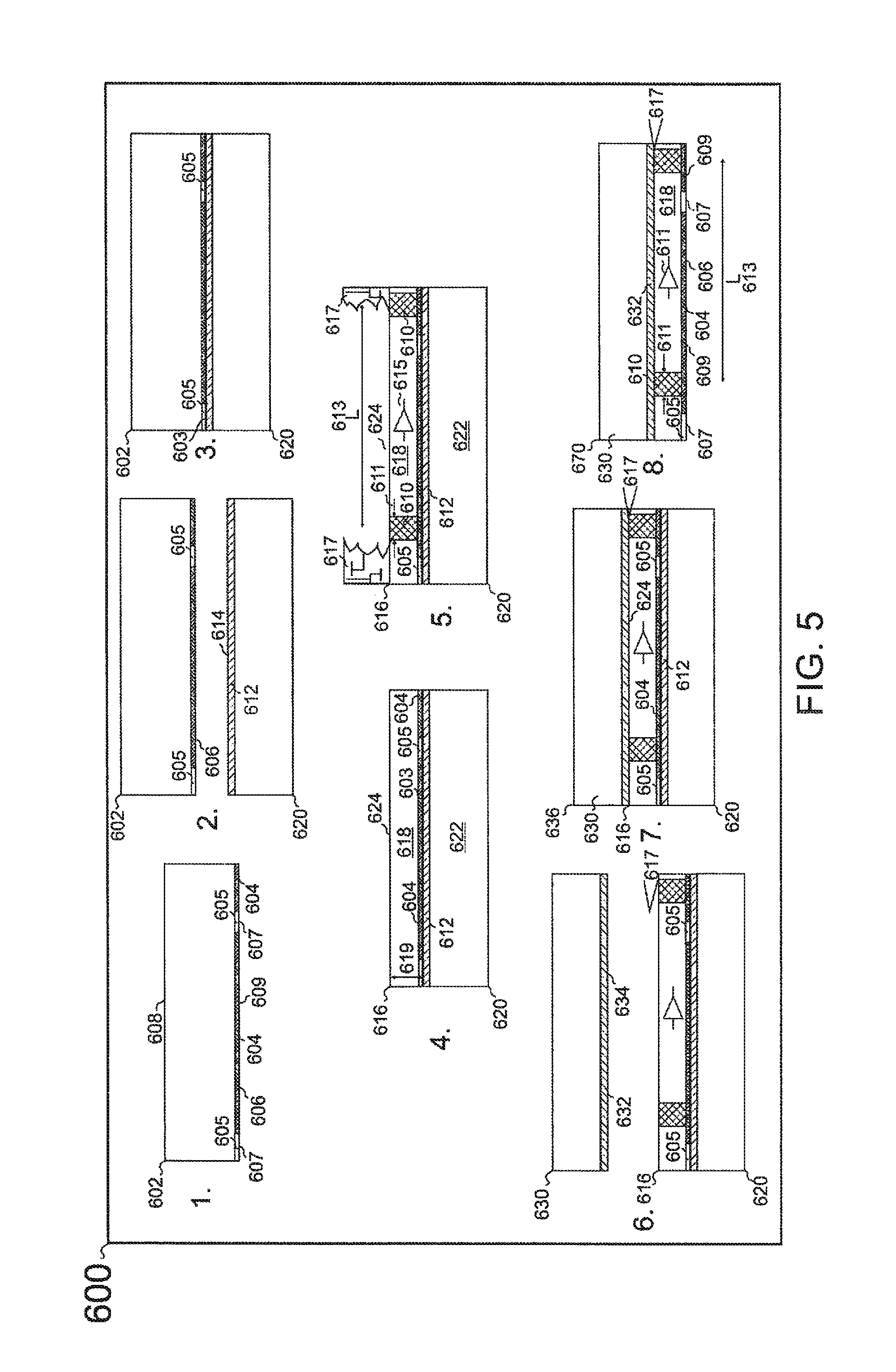

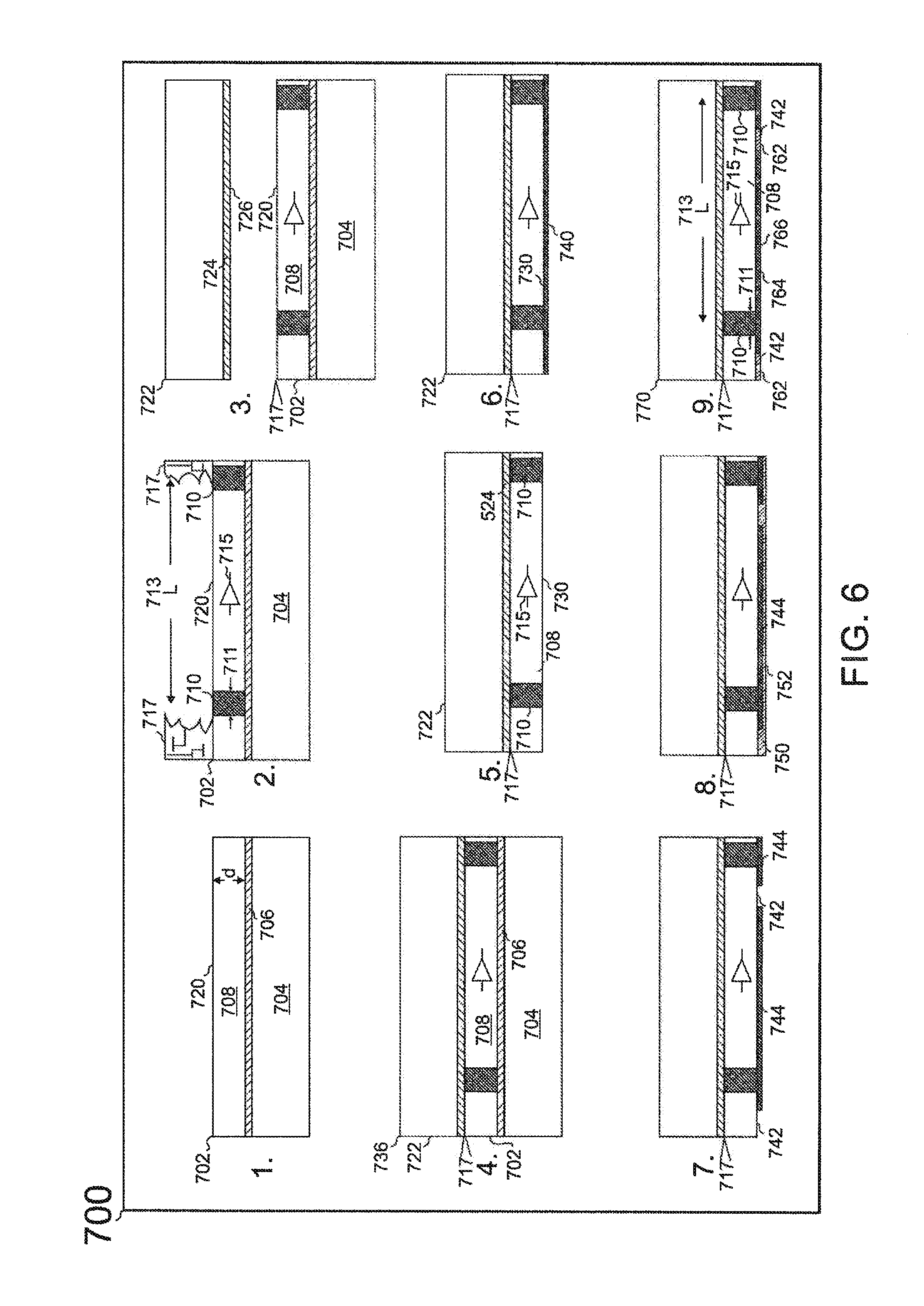

[0043] FIG. 6 is a schematic diagram showing the process flow of the invention for the fabrication of a thin readout wafer of the invention with metallic charge collector plugs and metal layers.

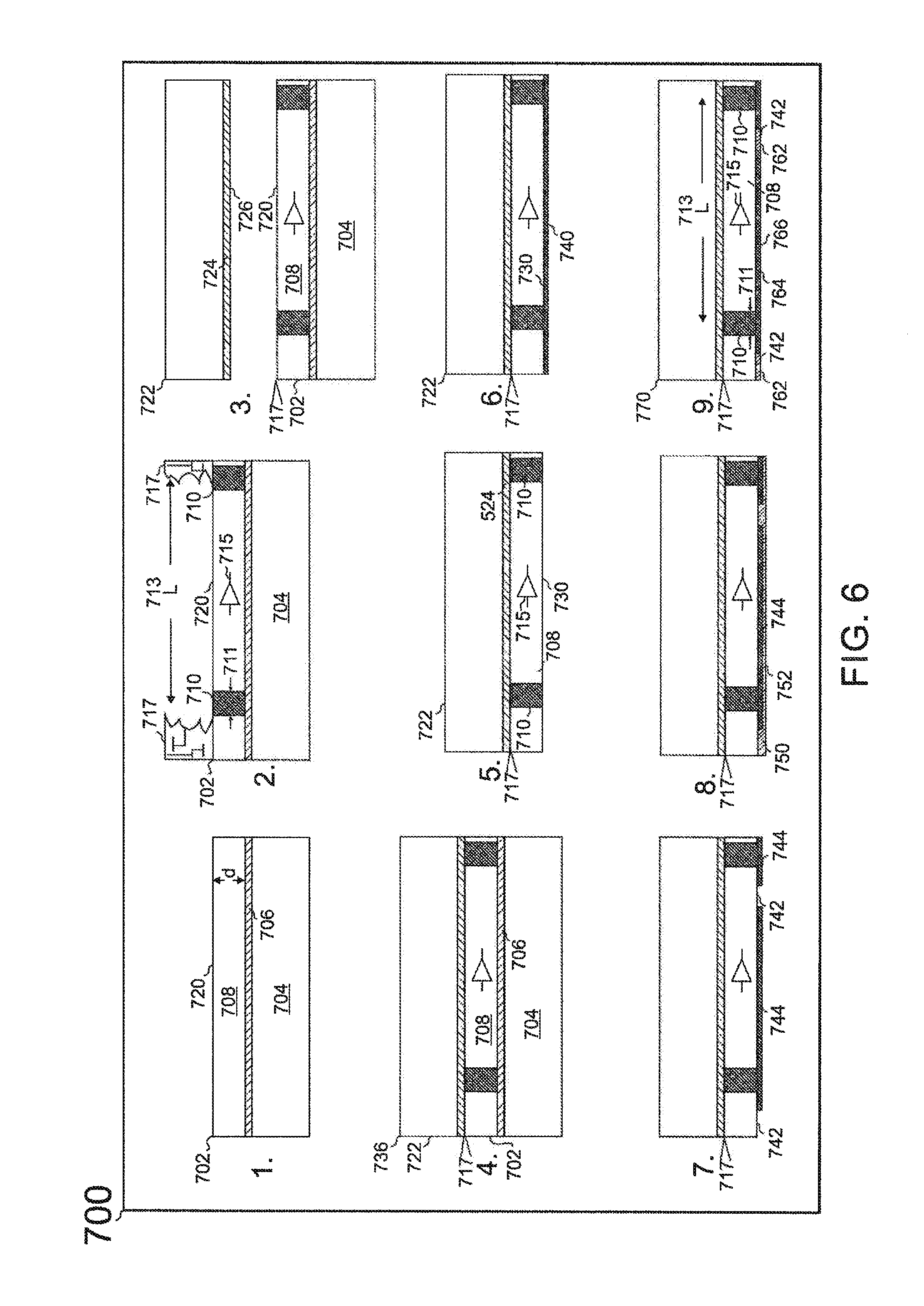

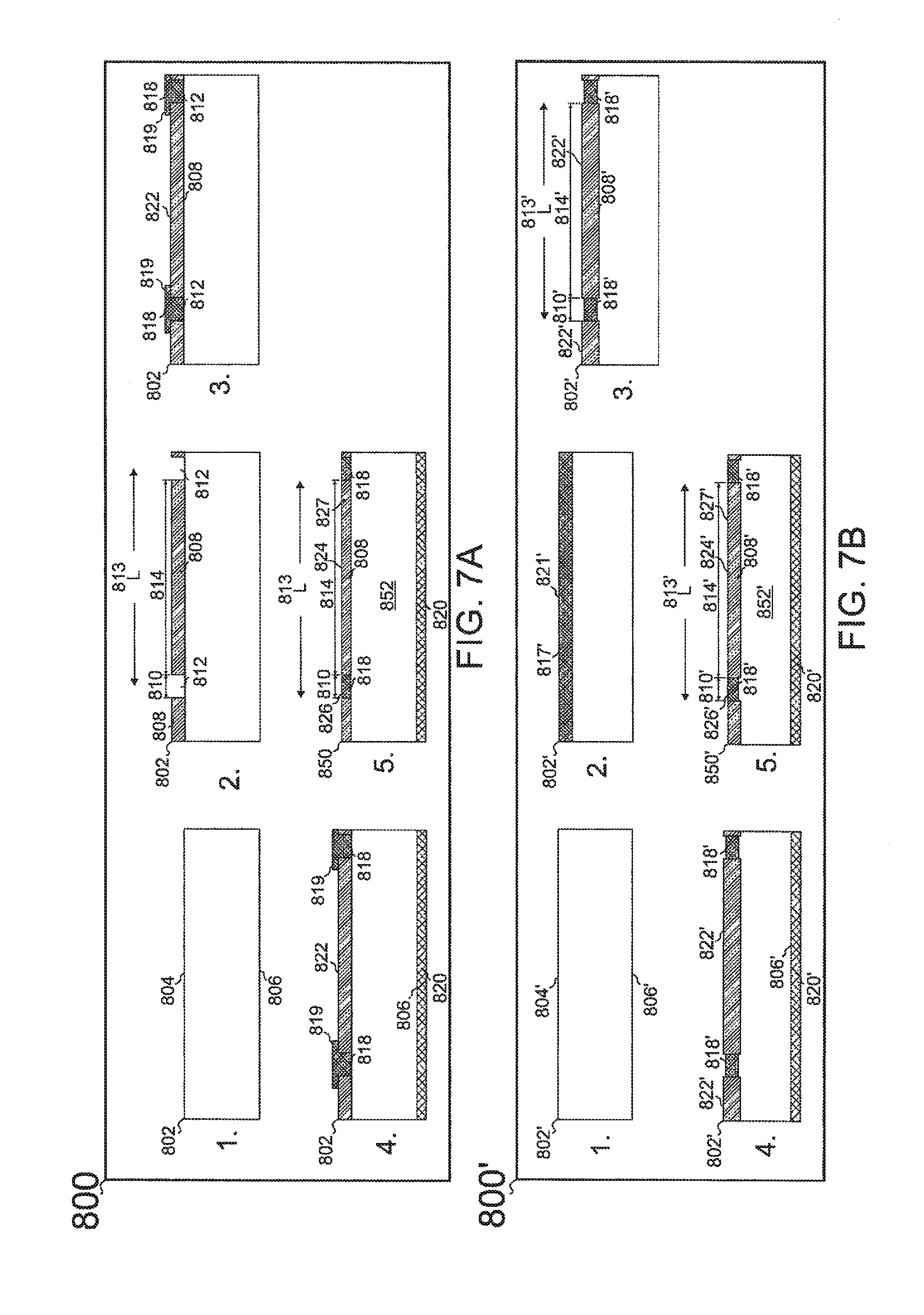

[0044] FIG. 7A is a schematic diagram showing the process flow of the invention for the fabrication of an absorber wafer of the invention made up of implants and oxide regions for pixel isolation.

[0045] FIG. 7B is a schematic diagram showing the process flow of the invention for the fabrication of an absorber wafer of the invention made up of metal regions along with oxide regions for pixel isolation.

[0046] FIG. 7C is a schematic diagram showing the process flow of the invention for the fabrication of an unpatterned absorber wafer of the invention.

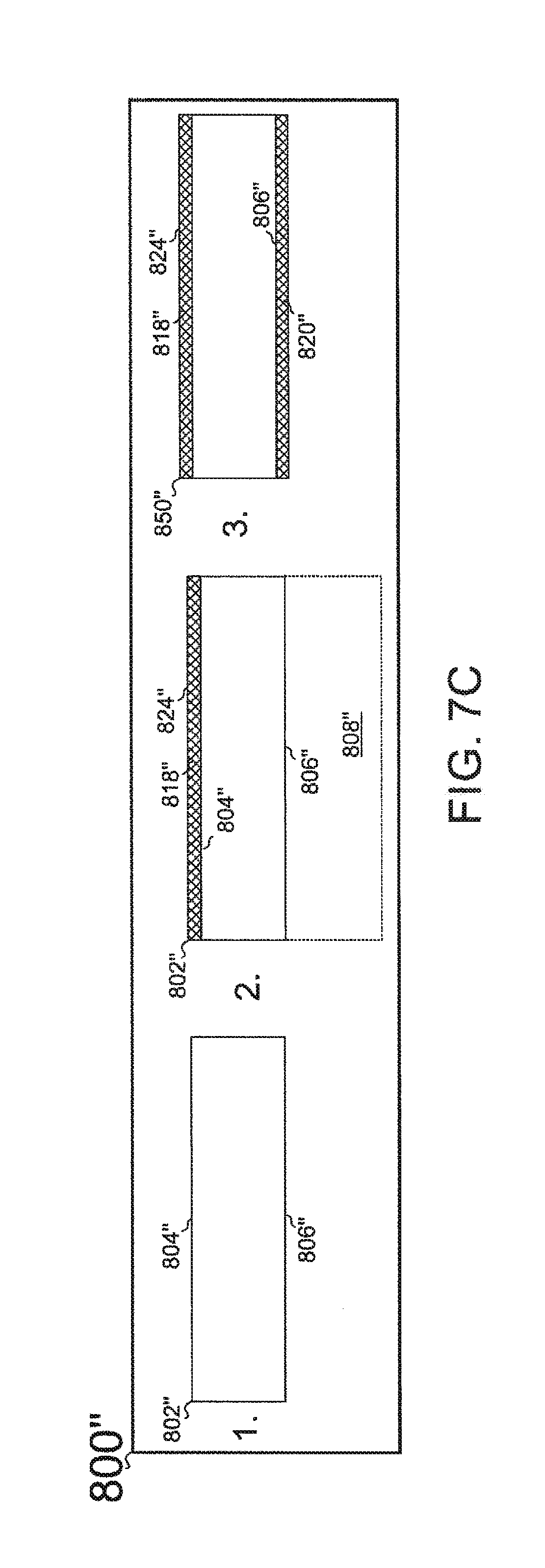

[0047] FIG. 8 is a schematic diagram showing the process flow of the invention for the fabrication of an absorber wafer of the invention made up of epitaxial pillars with highly doped caps.

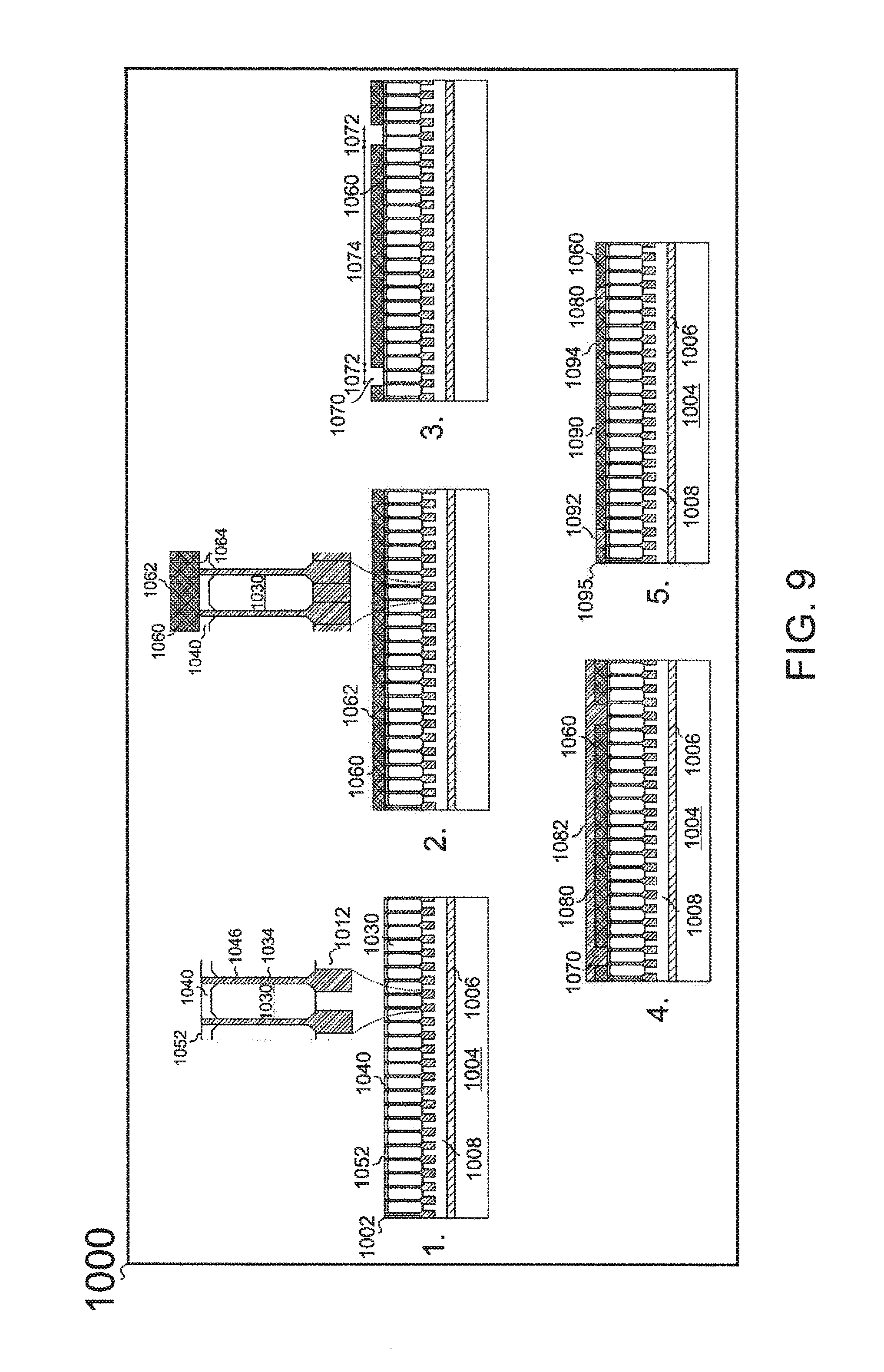

[0048] FIG. 9 is a schematic diagram showing the process flow of the invention for the fabrication of an absorber wafer of the invention made up of epitaxial pillars with highly doped caps, epilayer and oxide regions for pixel isolation.

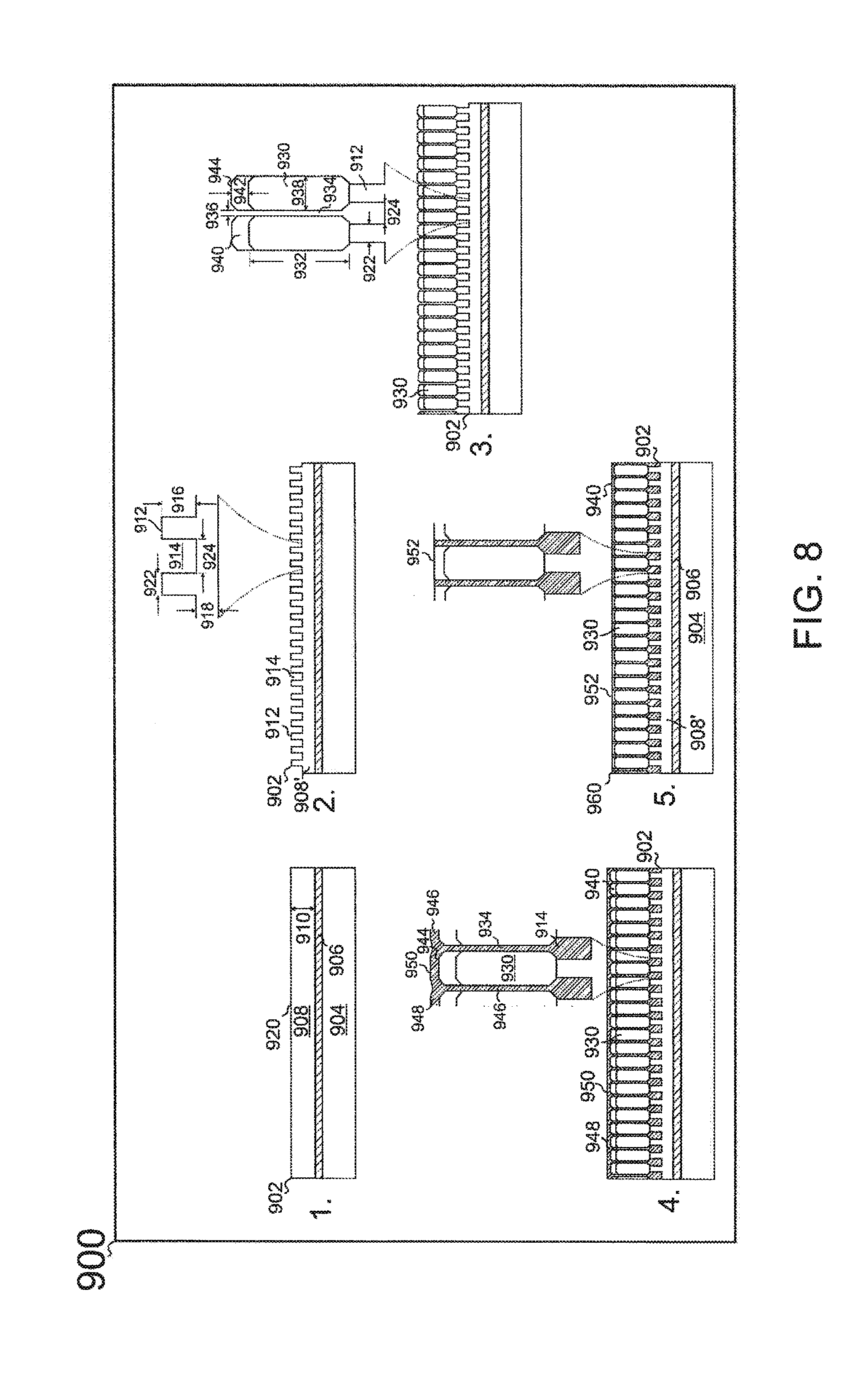

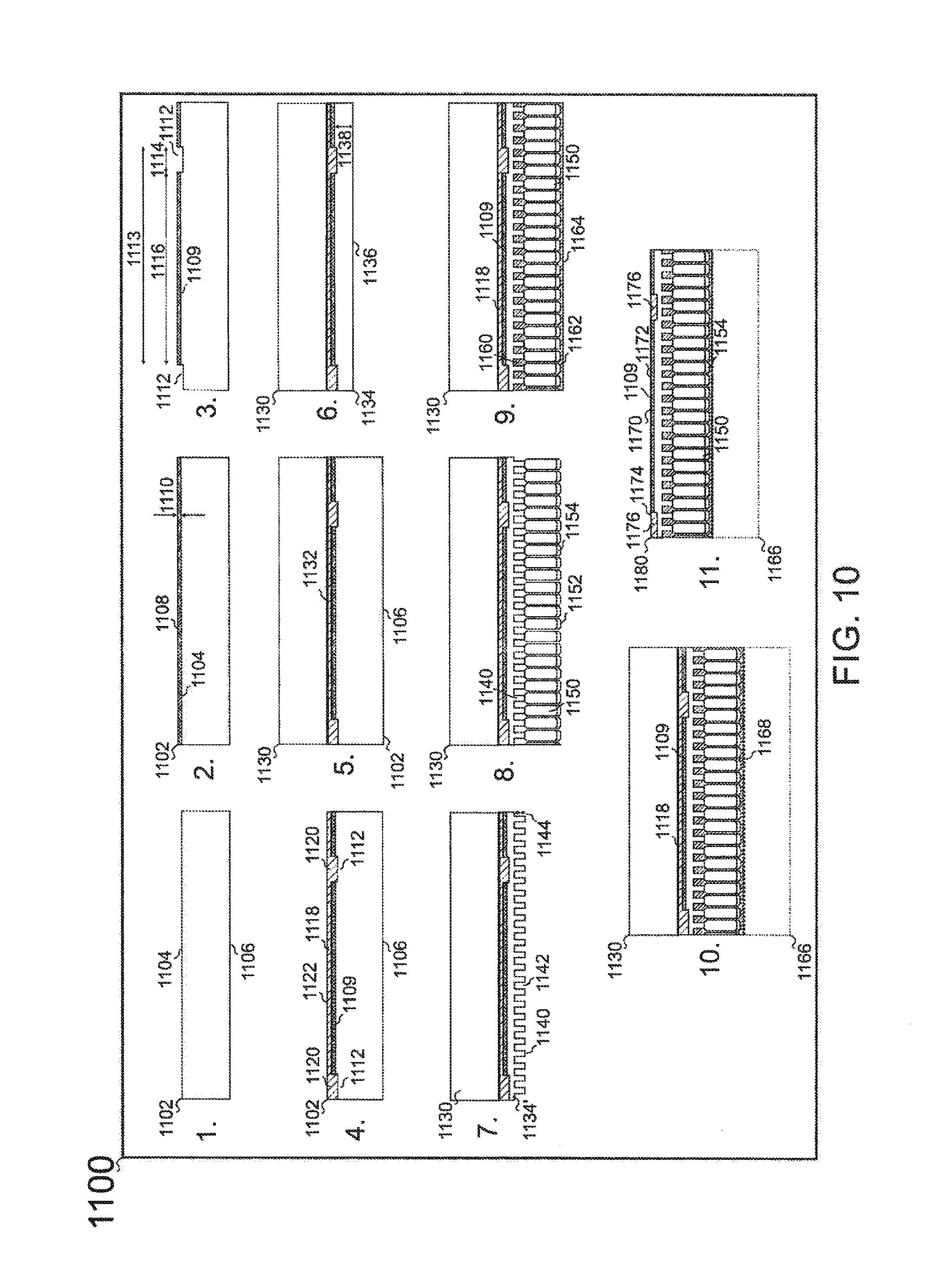

[0049] FIG. 10 is a schematic diagram showing the process flow of a variant of the invention for the fabrication of an absorber wafer made up of epitaxial pillars with highly doped caps, metal layer and oxide regions for pixel isolation.

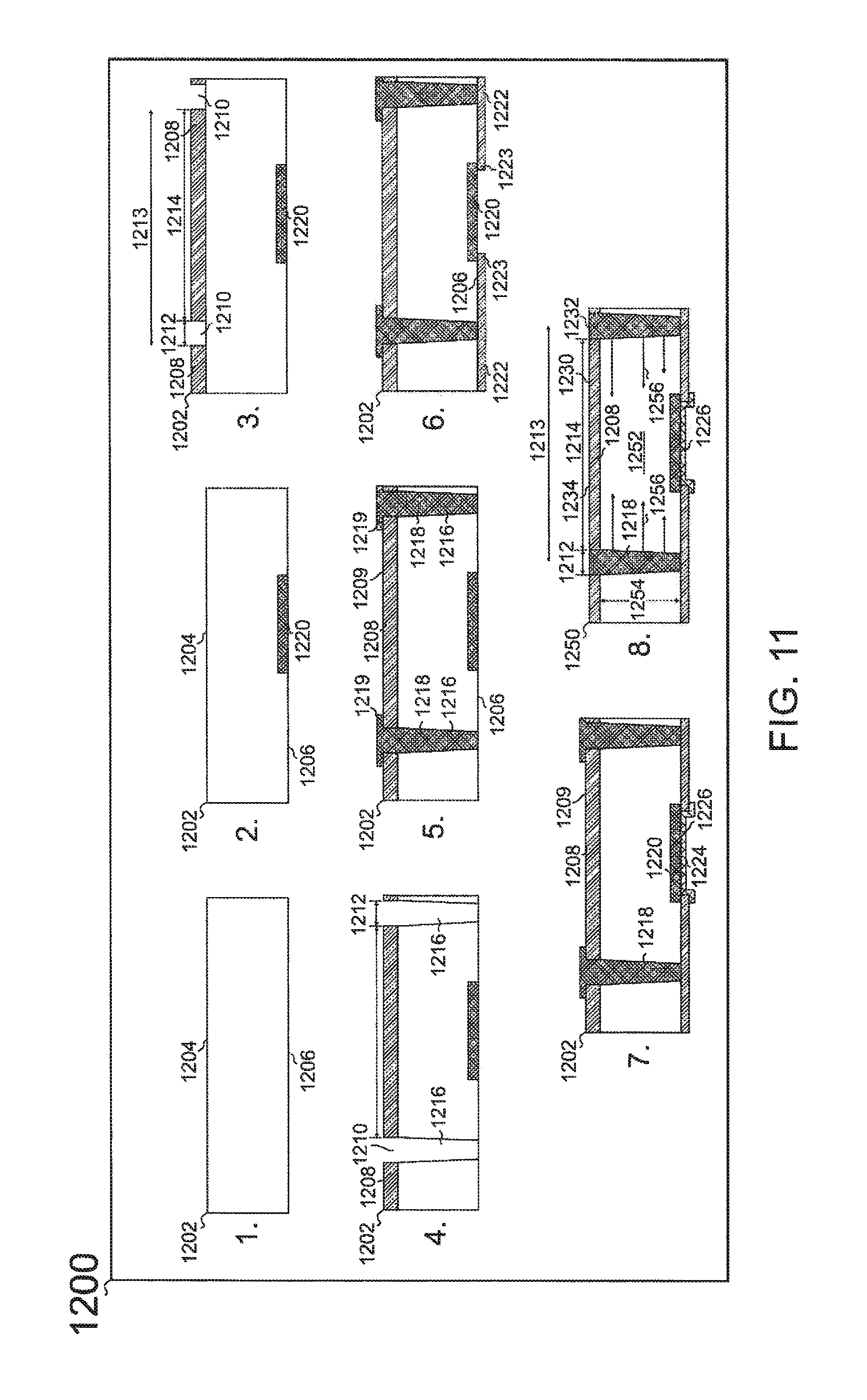

[0050] FIG. 11 a schematic diagram showing is the process flow of the invention for the fabrication of an absorber wafer of the invention with holes filled with epitaxial material.

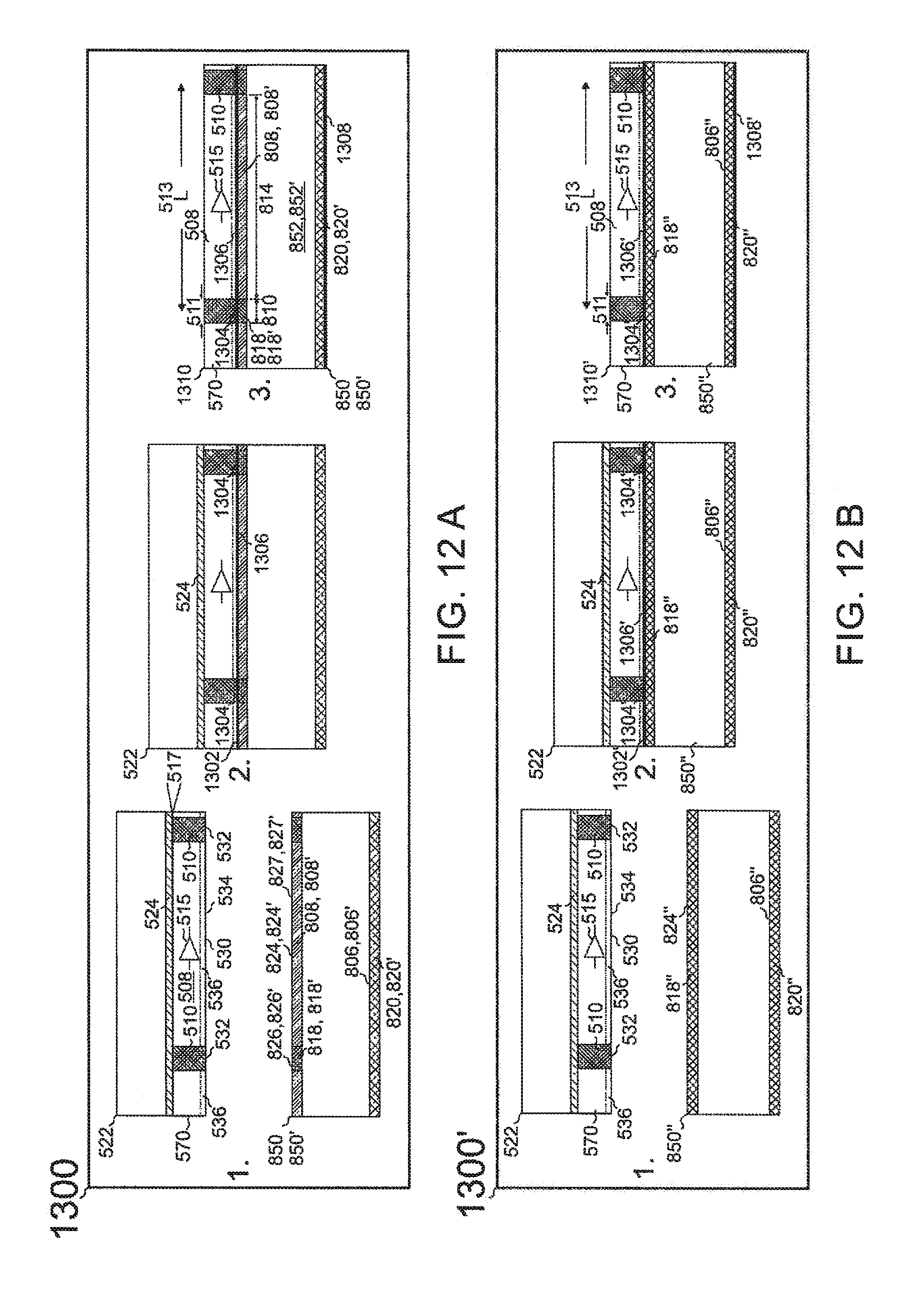

[0051] FIG. 12A a schematic diagram showing is the process flow of the invention for the fabrication of a detector structure of the invention with a bonded absorber wafer.

[0052] FIG. 12B a schematic diagram showing is the process flow of the invention for the fabrication of a detector structure of the invention with a bonded unpatterned absorber wafer.

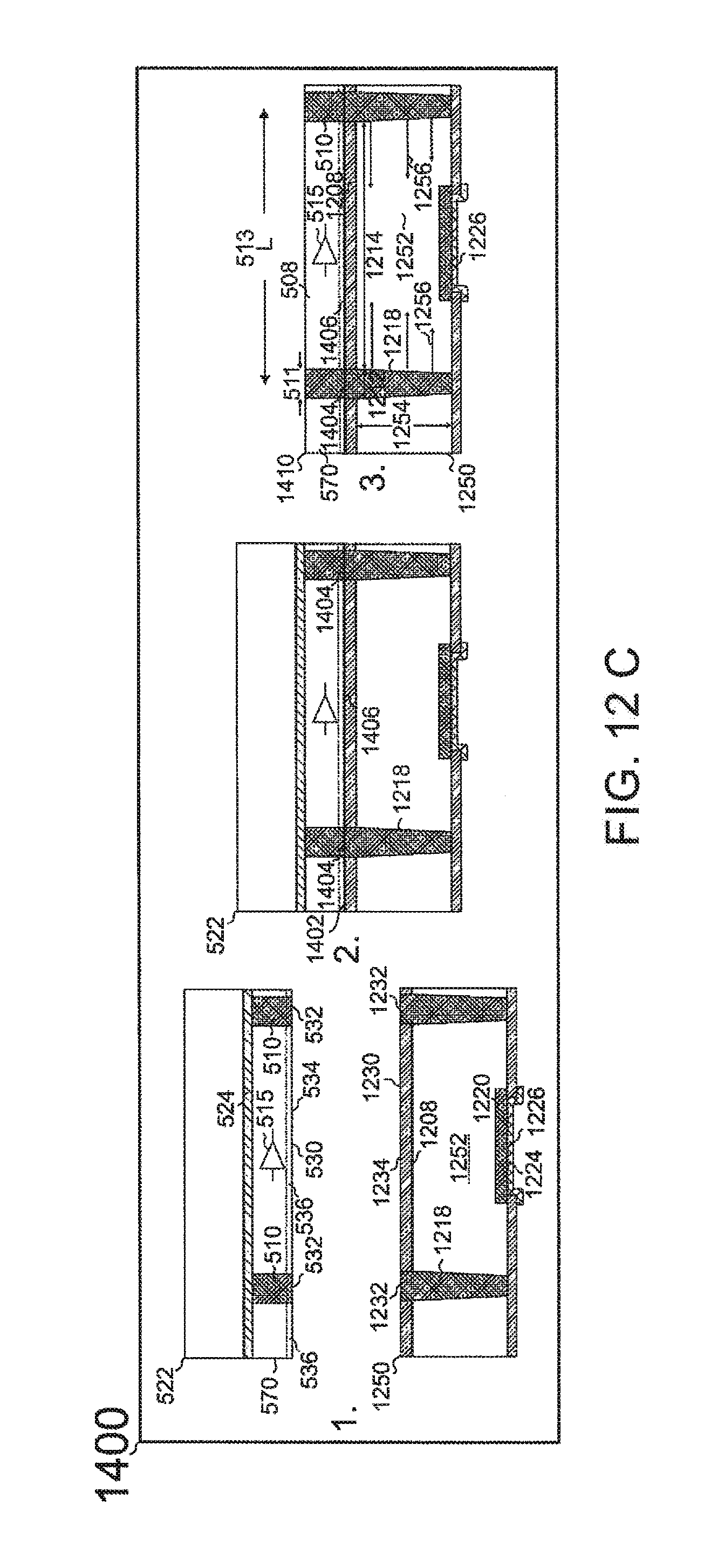

[0053] FIG. 12C a schematic diagram showing is the process flow of the invention for the fabrication of a detector structure of the invention with a bonded absorber wafer made up of holes filled with epitaxial material.

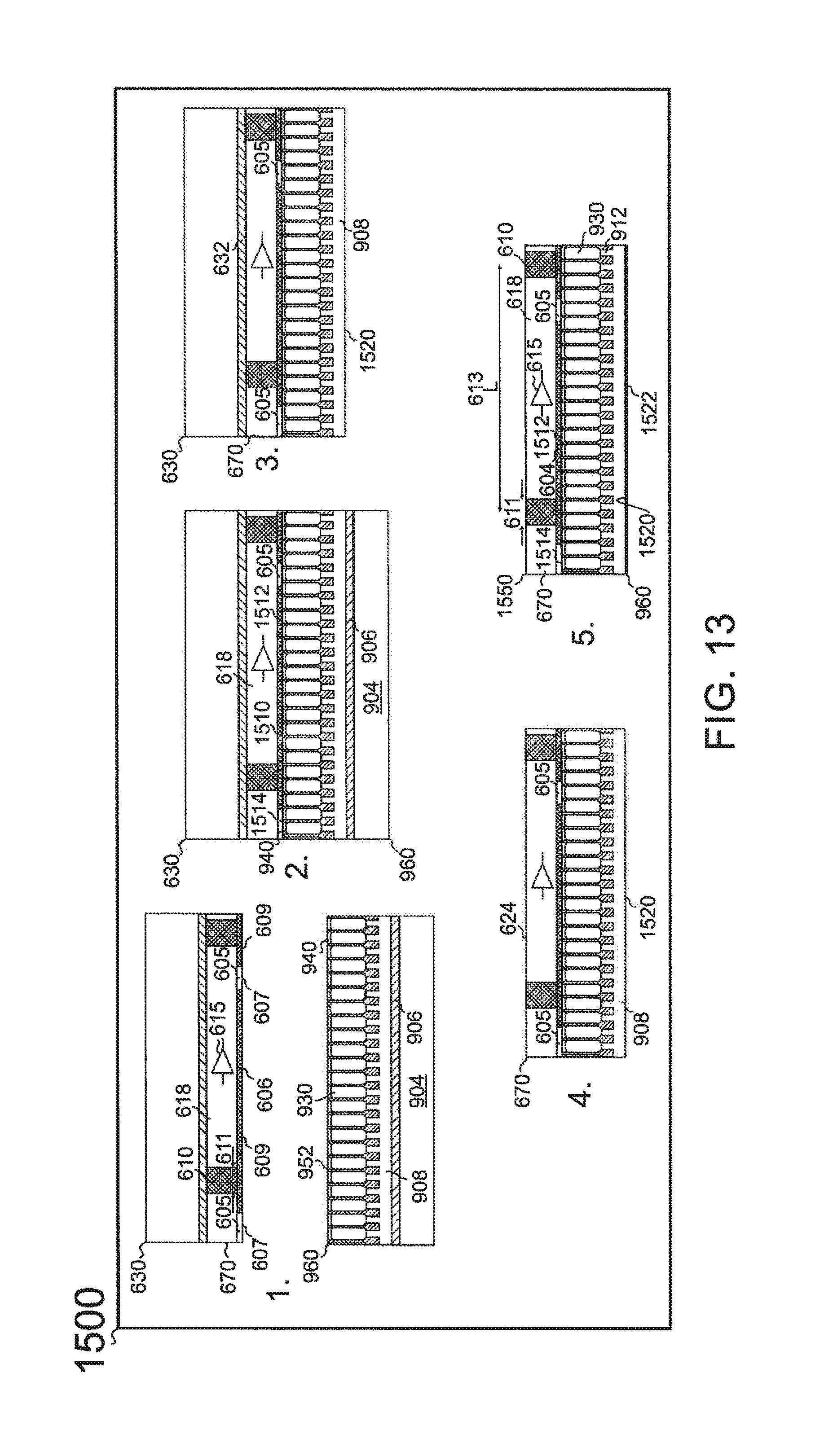

[0054] FIG. 13 is a schematic diagram showing a detector structure of the invention with epitaxial pillars bonded to highly doped regions of a thin readout wafer.

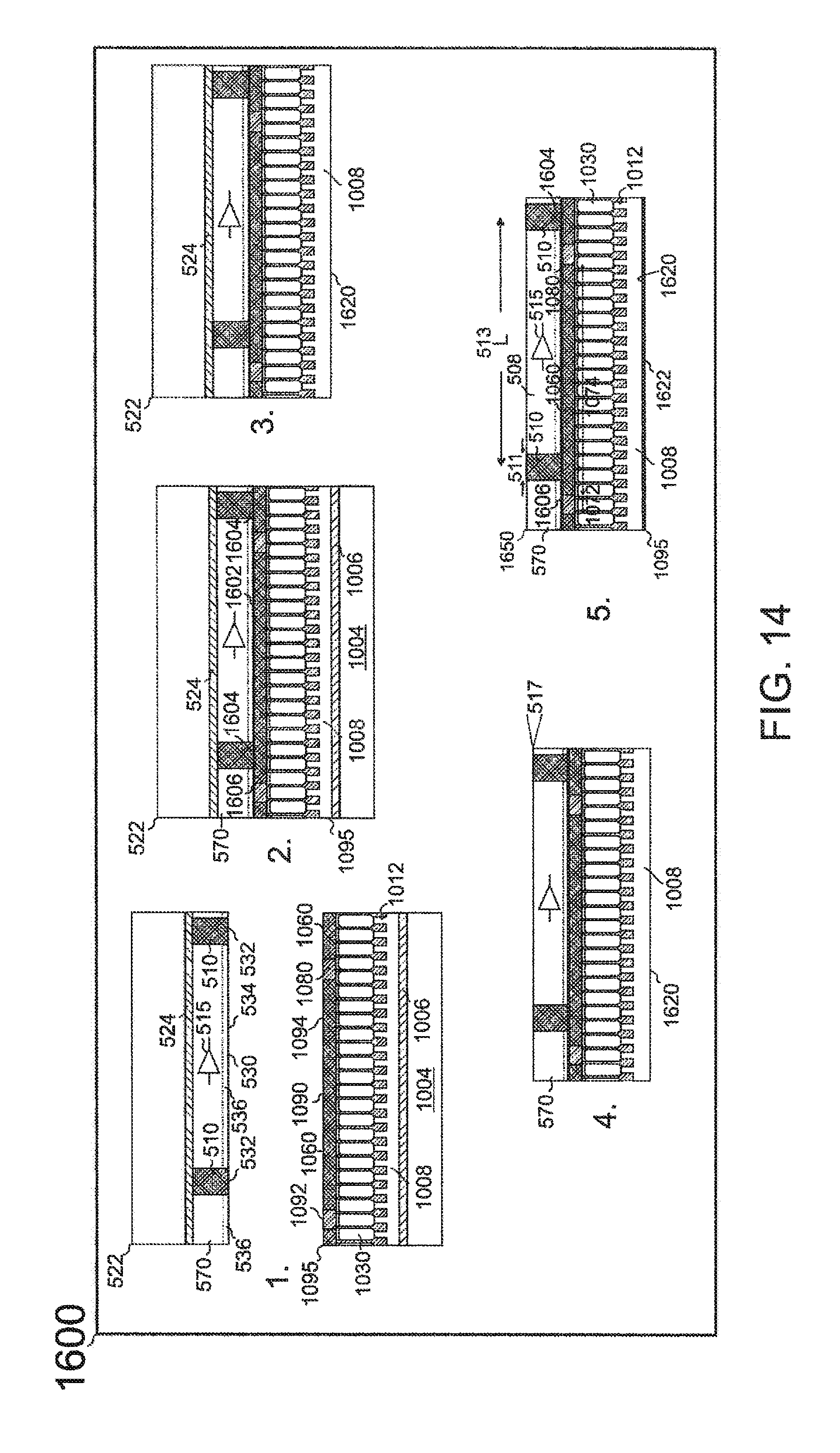

[0055] FIG. 14 is a schematic diagram showing a detector structure of the invention with highly doped regions on epitaxial pillars bonded to a thin readout wafer with highly doped regions.

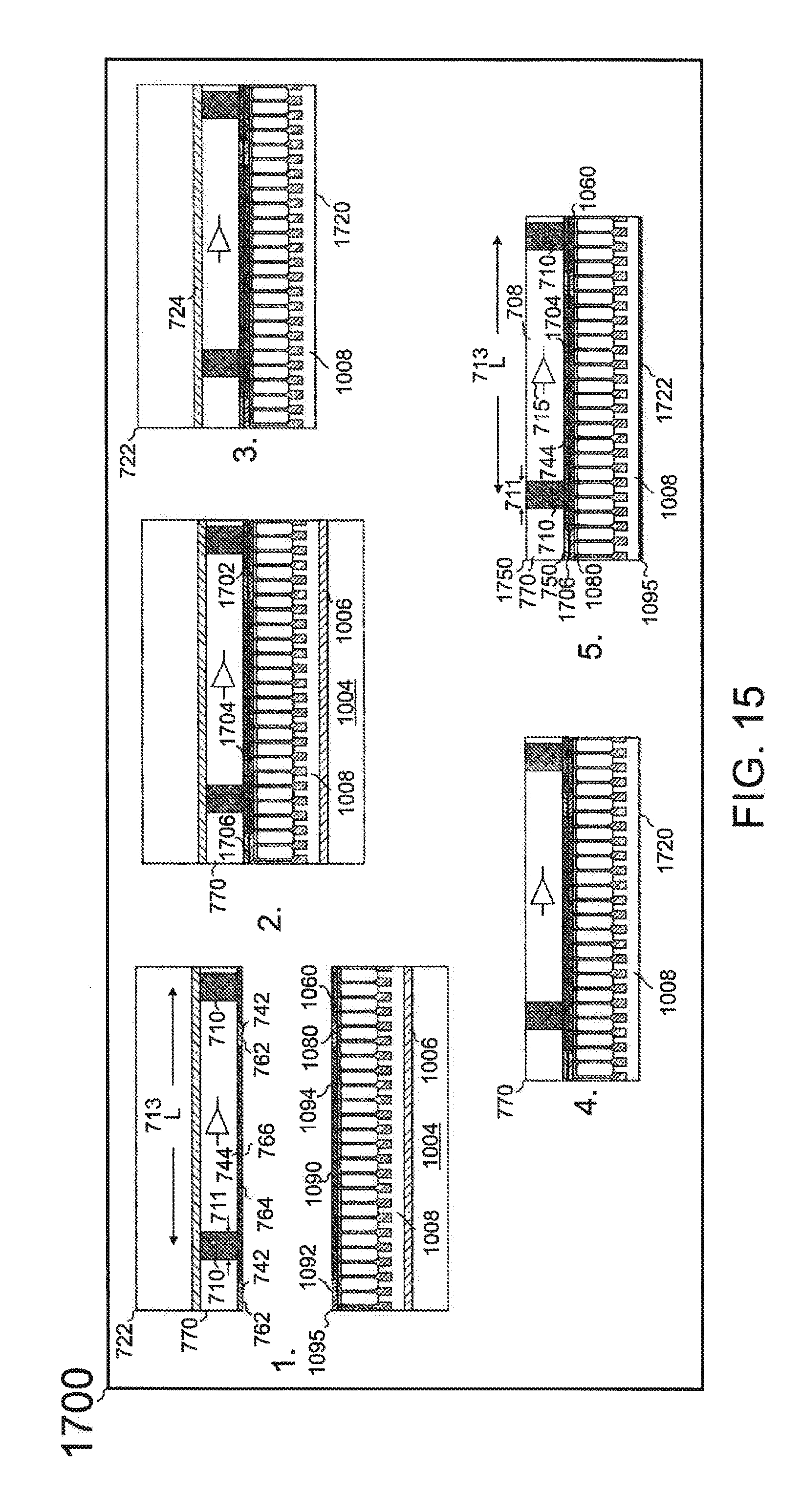

[0056] FIG. 15 is a schematic diagram showing a detector structure of the invention with metallized epitaxial pillar regions bonded to metal regions on a thin readout wafer.

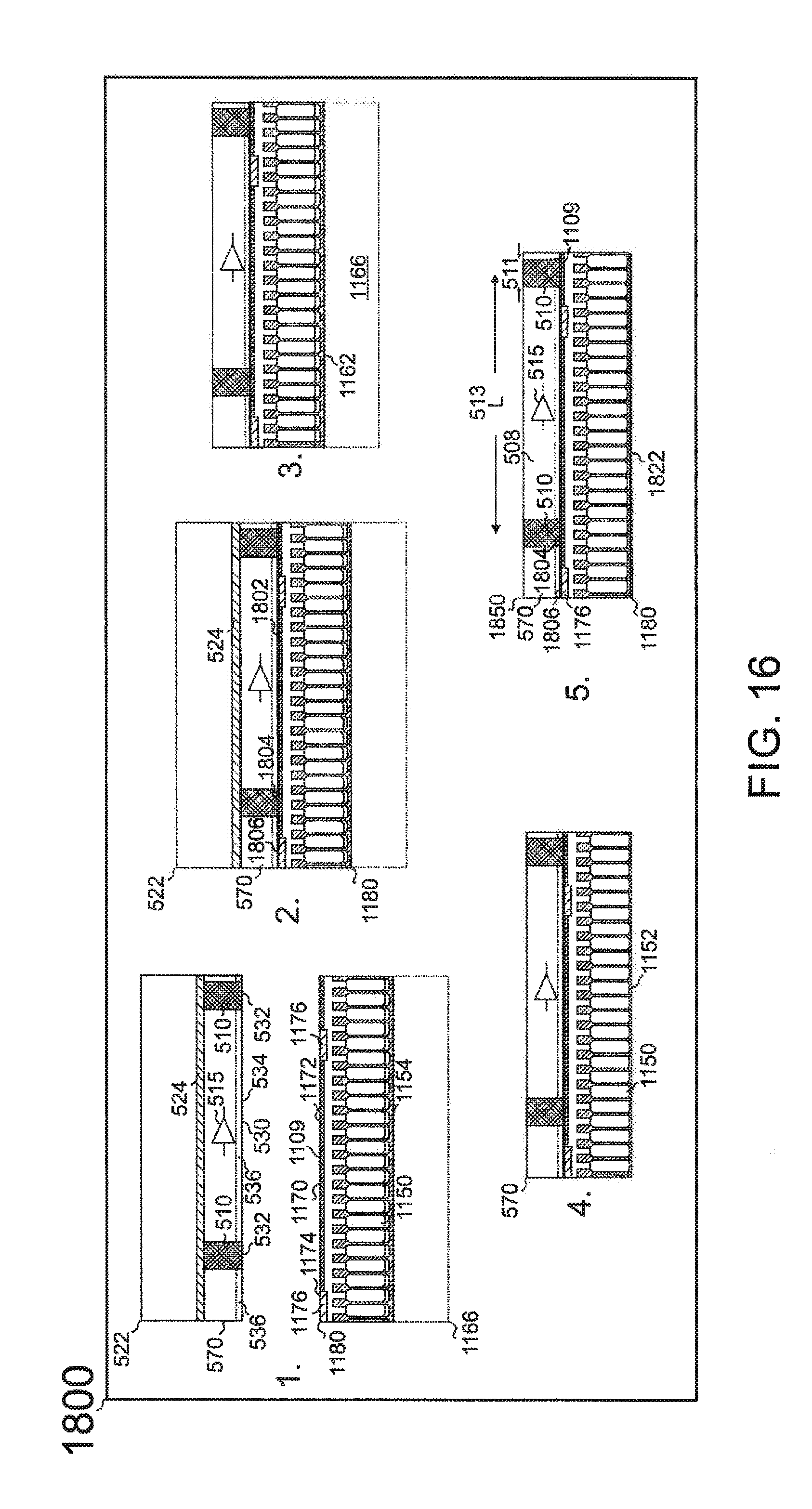

[0057] FIG. 16 is a schematic diagram showing a detector structure of the invention made up of epitaxial pillars on a thin substrate which is bonded to a thin readout wafer.

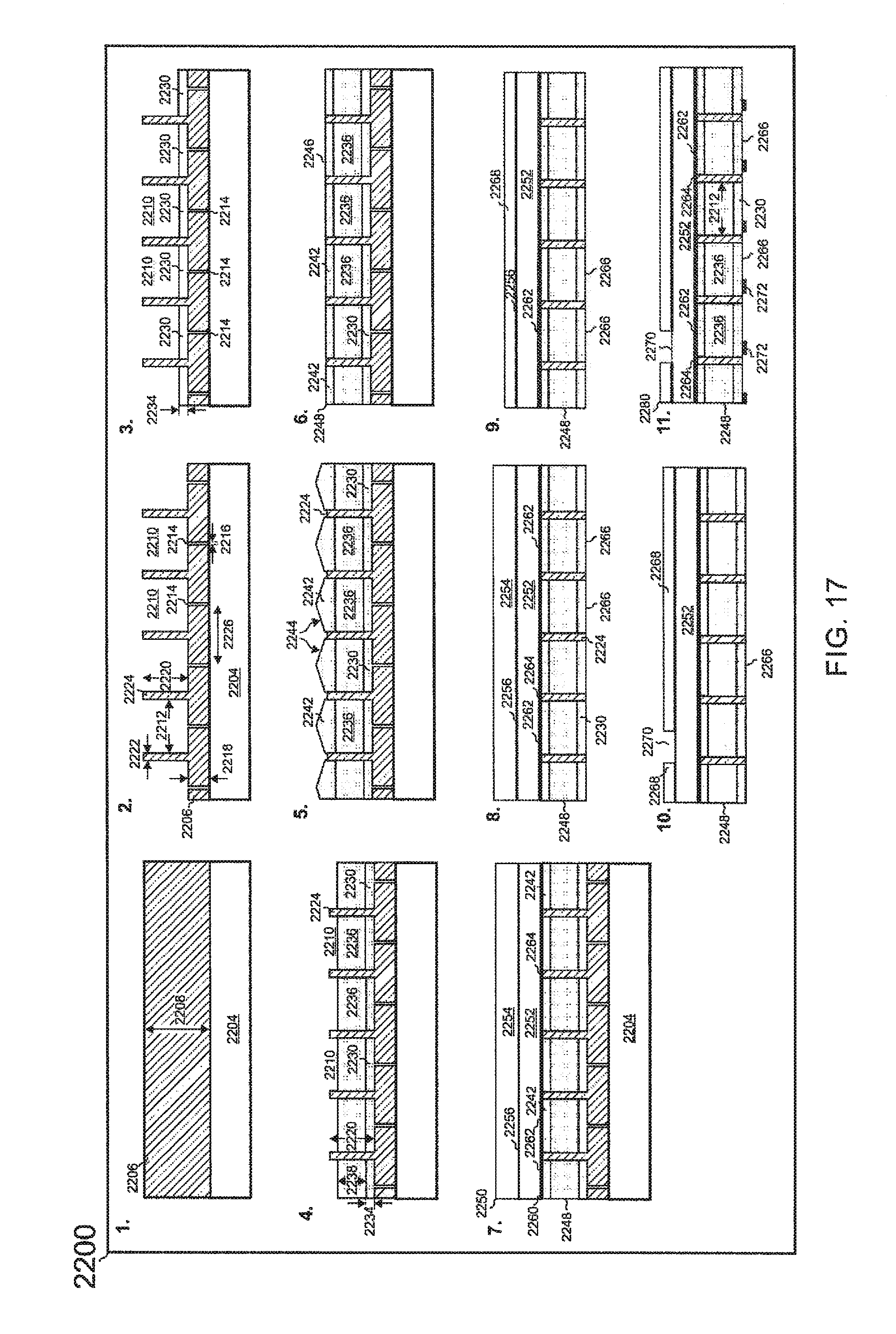

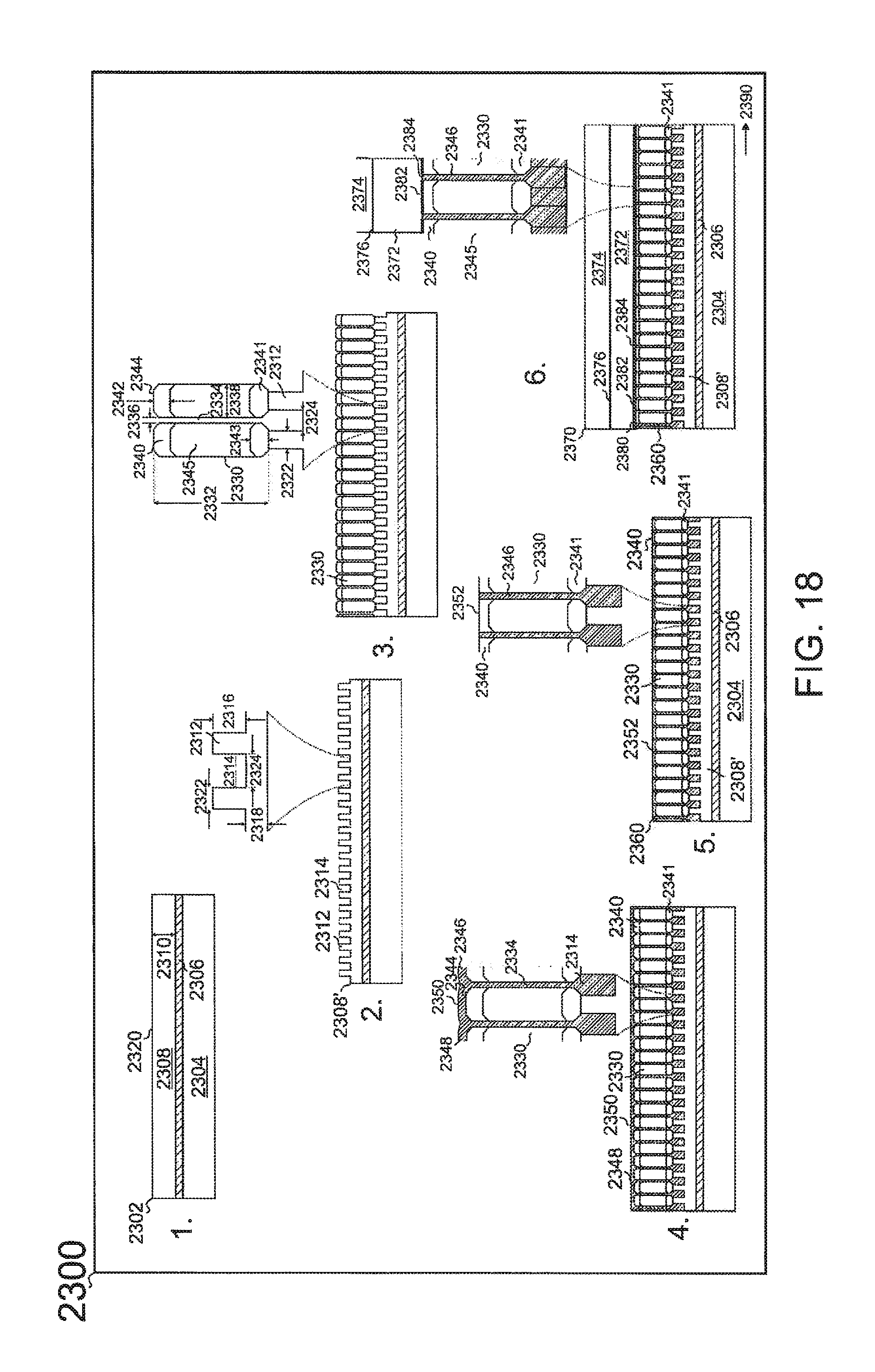

[0058] FIG. 17 is a schematic diagram showing the process flow of the invention for the fabrication of absorber pixels by aspect ratio trapping and their covalent bonding to a readout wafer.

[0059] FIG. 18 is a schematic diagram showing the process flow of the invention for the fabrication of absorber pixels by epitaxial growth on substrate pillars and their covalent bonding to a readout wafer.

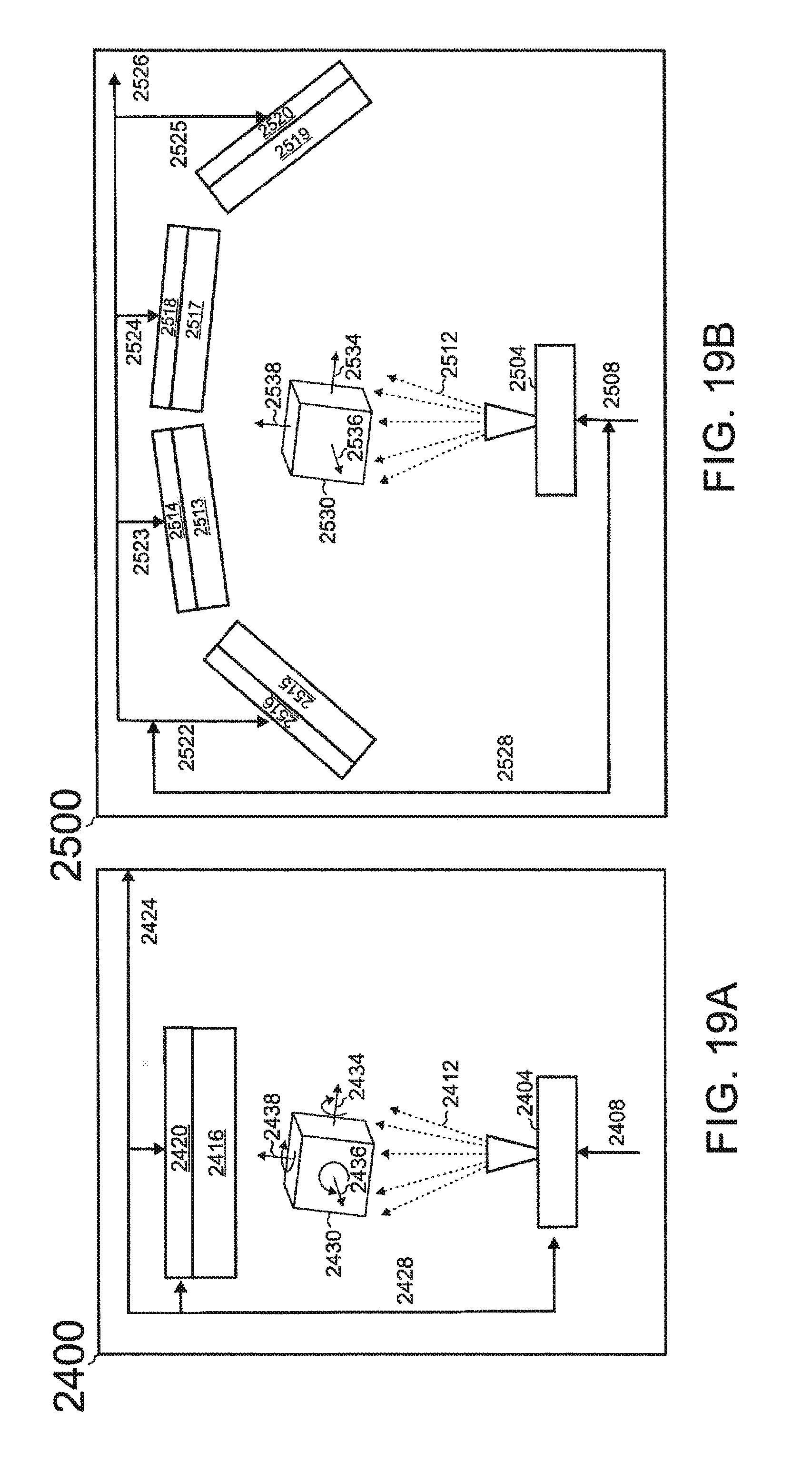

[0060] FIG. 19A is a device for non-destructive testing using the pixel detectors of the invention in combination with a rotatable object for generating computed tomography images.

[0061] FIG. 19B is a device for non-destructive testing using an array of pixel detectors of the invention in combination with a static object for generating computed tomography images.

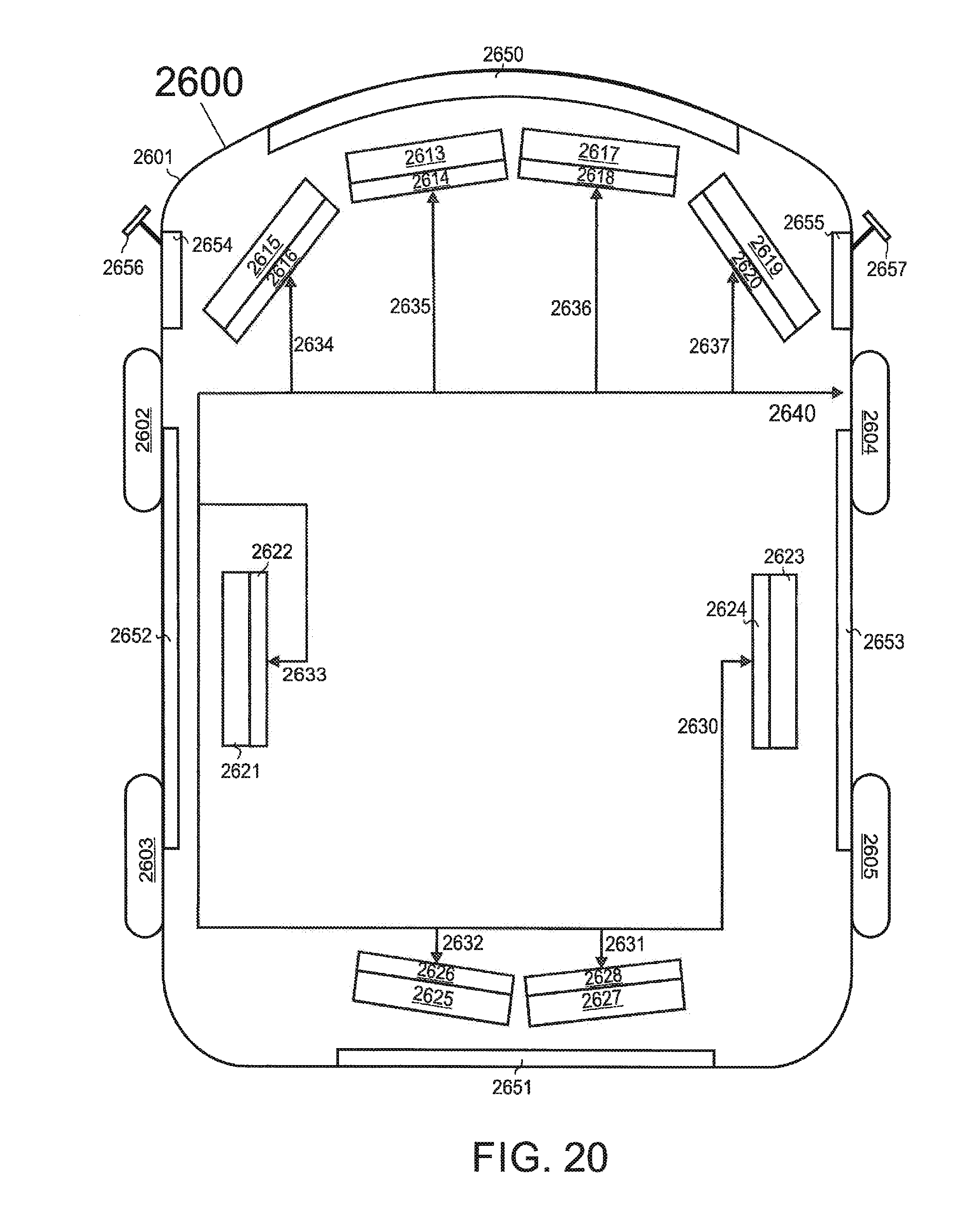

[0062] FIG. 20 is a vehicle equipped with an array of pixel detectors of the invention for collision control and tracking.

DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0063] It is the aim of this invention to provide simple structures and methods for the fabrication of sensitive pixel detectors for the detection of electromagnetic radiation, such as for example flat panel X-ray detectors with sizes up to about 20.times.20 cm.sup.2 or even about 40.times.40 cm.sup.2 and high-resolution detectors for the detection of infrared radiation. The detectors are composed of a readout unit processed in a thin CMOS wafer the backside of which is bonded to an absorber wafer, also called sensor wafer. These detectors are all configured for backside illumination, where electromagnetic radiation is incident on the absorber from the opposite side of the CMOS stack. The bonding happens on a wafer scale, and at least the bonds serving for charge collection are made between electrically highly conducting regions of the readout wafer and/or the absorber wafer, such as for example covalent semiconductor bonds between heavily doped semiconductors. The readout electronics is processed for example in an epitaxial Si layer with a thickness of about 10-30 .mu.m or preferably about 5-10 .mu.m or even 3-5 .mu.m and a resistivity above about 500 .OMEGA.cm or preferably about 1-2 k.OMEGA. cm or more preferably 2-5 k.OMEGA. cm or even above 5 k.OMEGA. cm, for example 5-50 k.OMEGA. cm, the resistivity being due to a low doping level in between about 10.sup.11 to 10.sup.13 cm.sup.-3 of a first conduction type (for example p-conduction induced by p-doping). For ease of detector manufacturing it may be advantageous to use silicon-on-insulator (SOI) wafers or epitaxial wafers made up of at least one epitaxial layer on a CZ or FZ wafer for the CMOS processing of the readout electronics. The use of such wafers may facilitate the thinning of the Si substrate of the CMOS wafer. The detectors can detect high-energy electromagnetic radiation in a single photon detection mode. Similar single photon detection capability may be achieved for example for infrared, visible or ultraviolet photons by incorporating an avalanche multiplication region into the monolithic detector structure. The sensor material can include any semiconductor available in the form of high purity wafers or in the faun of epitaxial layers grown on a substrate, whereby the substrate can for example be Si, Ge, GaAs, CdTe, a CdZnTe alloy or InSb, which may optionally be removed during detector fabrication. The thickness and the material used for the sensor strongly depend on the energy of the electromagnetic radiation which is to be detected. For the detection of low energy radiation from about one tenth of an eV up to a few keV, covering a spectral range from infrared to visible, ultraviolet and soft X-rays, a thickness on the order of one .mu.m or even less may be sufficient. There are many II/VI, III/V, IV/VI and group IV semiconductors covering this energy range, such as for example HgCdTe alloys, Pb salts, InSb, InGaAs alloys, Ge, Si, SiGe alloys, InP, GaAs, InGaN alloys, GaN, C (diamond), roughly in the order of increasing bandgap. As an example, for near infrared detection a Ge layer as thin as 0.5-1.5 .mu.m or even 0.3-0.5 .mu.m may be sufficient for efficient sensing up to a wavelength of about 1.6 .mu.m. Wafer bonding may be combined with wafer thinning, for example by hydrogen implantation and exfoliation (see for example I. P. Ferain et al., in J. Appl. Phys. 107, 054315 (2010), the entire disclosure of which is hereby incorporated by reference) or grinding and/or chemical etching. The sensitivity of infrared detectors may be further enhanced by incorporating an avalanche charge multiplication region communicating with the absorption region of the absorber wafer.

[0064] In the region between soft X-ray to hard X-ray detection, for example a SiC sensor with a thickness of about 3.5, 332 and 2310 .mu.m may absorb 90% of incident photons with energies of 2, 10 and 20 keV, respectively. A Si sensor with a thickness of about 3.9, 334 and 2330 .mu.m may absorb 90% of incident photons with energies of 2, 10 and 20 keV, respectively. For a Ge or GaAs sensor, the thickness necessary to absorb 90% of the incident photons with energy of 20, 30 and 40 keV is about 105, 320 and 710 .mu.m, respectively. For example a Si.sub.0.2Ge.sub.0.8 alloy would have to be about 25% thicker for the same absorption at these photon energies. Even harder X-rays of 40, 60 and 80 keV are absorbed to the same extent by a CdTe sensor or a CdZnTe alloy sensor whose thickness amounts to about 210, 610 and 1310 .mu.m, respectively (NIST X-ray attenuation data base, nist.gov/pml/data/ffast). The room temperature resistivity of intrinsic Ge is about 47 .OMEGA.cm and that of a Si.sub.0.25Ge.sub.0.75 alloy approximately 6.times.10.sup.4 .OMEGA.cm (see for example virginiasemi.com/pdf/generalpropertiesSi62002.pdf). X-ray detectors made up of Ge or SiGe absorbers therefore need to be cooled in order to lower dark leakage currents to acceptable levels for example of 1 nA per pixel or even between 10-100 pA. With respect to Ge and SiGe sensors, GaAs sensors have the advantage of much higher resistivity on the order of 10.sup.9 .OMEGA.cm (see for example M. C. Veale in Nucl Instr. Meth. Phys. Res, A 752, 6 (2014), the entire disclosure of which is hereby incorporated by reference). The same order of resistivity applies to CdTe sensors and even a higher one for CdZnTe alloy sensors (see for example S. Del Sordo et al. in Sensors 2009, 9, 3491-3526, the entire disclosure of which is hereby incorporated by reference).

[0065] The structures and methods of the invention refer to industrial scale wafers. High vacuum bonding equipment for 200 mm wafers is manufactured for example by EV Group (see for example C. Flotgen et al. in ECS Transactions 64, 103 (2014), the entire disclosure of which is hereby incorporated by reference).

[0066] For high-energy electromagnetic radiation, by its very construction, the monolithic pixel detectors of the invention offer single-photon detection. The monolithic X-ray pixel detectors of the invention are therefore suitable also for energy discrimination, whereby the energy of photons incident on the absorber can be measured by analysing the height of the electrical pulses processed by the readout electronics.

[0067] In contrast to prior art approaches (see for example U.S. Pat. No. 10,163,957 to von Kanel, and International Patent Application No. PCT/IB2017/001032 to von Kanel, the entire disclosures of which are hereby incorporated by reference) in the present invention charge carriers do not cross a bonding interface between lightly doped materials prior to arriving at charge collectors communicating with the readout electronics. The charges are instead channelled through bonding interfaces between electrically highly conducting regions where minority carrier generation and recombination does not occur. In all the following embodiments, the pixel detectors are configured for backside illumination, wherein electromagnetic radiation is incident on the absorber bonded on the backside of a thin silicon CMOS substrate with the CMOS stack on the opposite side, thereby offering fill factors close to 100%.

[0068] Referring now to FIG. 2A, first exemplary embodiment 100 of monolithic pixel detector 101 adapted to the detection of X-rays includes a bonding interface between thin readout wafer 102 of thickness d.sub.1 and absorber wafer 104 of thickness dz. The readout wafer is preferably fabricated for example by CMOS processing a weakly p-doped substrate 106 with a resistivity preferably of about 1-2 k.OMEGA. cm or even 2-5 k.OMEGA. cm which is thinned to a thickness of about 10-30 .mu.m or preferably about 5-10 .mu.m or even 3-5 .mu.m after all the processing has been completed. The thinning requires the planarization of the CMOS stack and the bonding of a carrier wafer before substrate 106 can be thinned. The bonding interface consists of conducting covalent semiconductor bond 108 between structures resembling silicon-through-vias 110 but filled with highly conducting n.sup.+-doped semiconductor material forming an n.sup.+-p junction with weakly p-doped substrate 106. In the following, these n.sup.+-doped vias, extending through substrate 106 will simply be called plugs 110. Plugs 110 form ohmic contacts with highly conducting n.sup.+-doped regions 112 in highly resistive p-conducting absorber wafer 104, which may for example be heavily doped implants. The doping level of highly conducting plugs 110 may for example be between 1.times.10.sup.18-1.times.10.sup.19 cm.sup.-3 or preferably 1.times.10.sup.19-1.times.10.sup.20 cm.sup.-3 or even 1.times.10.sup.20-5.times.10.sup.20 cm.sup.-3, corresponding to a resistivity between about 5-20 m.OMEGA. cm, 0.7-5 m.OMEGA. cm and 0.2-0.7 m.OMEGA. cm, respectively. Highly conducting regions 112 may have similar doping levels. Heavily doped plugs 110 may be formed for example by etching holes in lightly p-doped substrate 106 and their filling with n.sup.+-material in a subsequent epitaxy step known in the art. In another aspect of embodiment 100 a similar epitaxy process instead of implants 112 may result in heavily doped columns 124 doped to similar levels extending through most or all of absorber wafer 104. Optionally, absorber wafer 104 may further include heavily p-doped layer 117, facilitating ohmic contact formation with metallic back contact 116. Heavily doped plugs 110 bonded to heavily doped implants 112 or columns 124 serve as charge collectors, collecting electrons from electron-hole pairs which are generated by electromagnetic radiation incident on absorber wafer 104 and separated in the electric field of the reverse biased p-n junction 114, 126, formed by n.sup.+-doped regions 112, 124 and highly resistive p-conducting absorber wafer 104, upon applying a voltage to back contact 116 on absorber wafer 104. Minority carriers (electrons) thus never move across a bonding interface between low-doped wafers where trapping and recombination might occur. The charge collectors 110 communicate with the pixel readout electronics 115 of readout wafer 102 wherein the charge pulses generated by electromagnetic radiation are processed and forwarded to the off-pixel part of the readout electronics. The detector pixels are defined by the heavily doped plugs/regions 110/112, 110/124 the width 118, 119, 128 of which may for example range within about 0.5-2.5 .mu.m or preferably about 1-1.5 .mu.m. Width 118 of heavily doped plugs 110 in readout wafer 102 and width 119, 128 of heavily doped regions 112, 124 in absorber wafer 104 do not need to be equal but preferably at least one of them is in the range of at least 1-1.5 .mu.m to facilitate accurate alignment of wafers 102, 104 for bonding. In order to permit accurate alignment thin readout wafer 102 and absorber wafer 104 are both equipped with at least two special wafer alignment features in the form of alignment marks positioned for example close to the wafer edges on opposite sides. With the help of superimposing such alignment marks the rotational misalignment of 200 mm wafers may be kept within about (2-5).times.10.sup.-4 degrees and the lateral misalignment within about 0.5-1 .mu.m. Similar accuracy may be obtained in case of smaller wafer bonding. For example EVGroup offers an alignment tool with an accuracy below 1 .mu.m (see, e.g., evgroup.com/en/products/bonding/integrated_bonding/evg_combond, the entire disclosure of which is hereby incorporated by reference). The distance L between doped plugs 110 contacting regions 112/124 defines the pixel size 113 which can vary in a wide range within about 100-200 .mu.m, 50-100 .mu.m or 20-50 .mu.m or even 5-20 .mu.m. Using doped columns 124 instead of implants 112 has the advantage of easier depletion of absorber 104 at lower voltages applied to back contact 116 when the pixel size is smaller than the absorber thickness dz. Heavily doped implants 112 in absorber wafer 104 are surrounded by highly resistive regions 120 the resistivity of which is higher than that of implants 112 by at least a factor of 10.sup.4-10.sup.6. Regions 120 may even be insulating regions, such as oxide regions and form poorly conducting or electrically insulating semiconductor-to-oxide or oxide-to-oxide bond 122 between readout and absorber wafer the resistance of which is higher by at least a factor of 10.sup.2-10.sup.4, or preferably 10.sup.4-10.sup.6, or even more preferably 10.sup.6-10.sup.8 than that of bond 108. These highly resistive regions hence insulate the low-doped regions of readout wafer 102 (i.e. substrate 106) from low-doped, highly resistive absorber wafer 104, such that the only electrical connection between the two wafers is made between heavily doped regions 110 and 112, 124. At the same time regions 120 isolate adjacent pixels electrically from each other.

[0069] The pixel detector according to embodiment 100 is designed for detecting electrons from the electron-hole pairs generated by X-rays in absorber wafer 104. In an aspect of the embodiment the detector may be designed for hole collection by reversing the doping signs. The doping levels of p-doped regions may be about the same as the doping levels of n-doped regions discussed above. Somewhat higher doping by a factor of about 1.5 is needed for similar resistivity levels as for the n-doping case.

[0070] According to FIG. 2A, embodiment 100 requires precise mutual alignment of readout wafer 102 and absorber wafer 104 in order to form electrical contacts between heavily doped plugs 110 and heavily doped regions 112, 124.

[0071] The absorber wafer 104 may for example be a Si, SiC, Ge, GaAs, CdTe, or a CdZnTe alloy wafer obtained by bulk crystal growth. Alternatively, it may originate from at least one epitaxial layer of any of these materials on a single crystal substrate, which may optionally be removed after the covalent bonding step.

[0072] Referring now to FIG. 2B, second embodiment 100' of monolithic pixel detector 101' adapted to the detection of X-rays may include a bonding interface between thin readout wafer 102' of thickness d.sub.1' and absorber wafer 104' of thickness d.sub.2'. The readout wafer may have been fabricated for example by CMOS processing a weakly p-doped substrate 106' with a resistivity preferably of about 1-2 k.OMEGA. cm or even 2-5 k.OMEGA. cm which has a thickness d.sub.1' of about 10-30 .mu.m or preferably about 5-10 .mu.m or even 3-5 .mu.m. The thinning to such thicknesses may first require the planarization of the CMOS stack and the bonding of a carrier wafer to substrate 106'. Readout wafer 102' may contain highly conducting n.sup.+-doped plugs 110', extending through substrate 106' enclosed by highly resistive or insulating regions 120' the resistivity of which is higher than that of highly doped regions 110', 112' by at least a factor of 10.sup.4-10.sup.6. Highly resistive regions 120' may for example have been formed by local amorphization or local oxidation of wafer 102' before its bonding to highly resistive p-conducting absorber wafer 104'. Alternatively, for a resistivity of readout wafer 102' above about 2 k.OMEGA. cm, highly resistive regions 120' may not need to be especially formed. The doping level of highly conducting plugs 110' may for example be between 1.times.10.sup.18-1.times.10.sup.19 cm.sup.-3 or preferably 1.times.10.sup.19-1.times.10.sup.20 cm.sup.-3 or even 1.times.10.sup.20-5.times.10.sup.20 cm.sup.-3, corresponding to a resistivity between about 5-20 m.OMEGA. cm, 0.7-5 m.OMEGA. cm and 0.2-0.7 m.OMEGA. cm, respectively. Heavily doped plugs 110' may be formed for example by etching holes in lightly p-doped substrate 106' and their filling with n.sup.+-material in a subsequent epitaxy step known in the art. Absorber wafer 104' preferably contains heavily doped, highly conducting and unstructured surface layer 112', formed for example by ion implantation, which may have a similar doping type and doping level as plugs 110'. Optionally, absorber wafer 104' may further include heavily p-doped layer 117', facilitating ohmic contact formation with metallic back contact 116'. Heavily doped plugs 110' form ohmic contacts with heavily doped surface regions 112' of absorber wafer 104'. On the other hand, conducting surface layer 112' forms p-n junction 114' with the high resistivity, p-conducting bulk region of absorber wafer 104'. Heavily doped plugs 110' bonded to heavily doped regions 112' by conducting covalent semiconductor bonds 108', providing said ohmic contacts, serve as charge collectors, collecting electrons from electron-hole pairs which are generated by electromagnetic radiation incident on absorber wafer 104' and separated in the electric field of the reverse biased p-n junction 114', formed by heavily n-doped surface region 112' and p-conducting bulk region of absorber wafer 104', upon applying a voltage to back contact 116' on absorber wafer 104'. Electrons substantially do not, however, cross poorly conducting bonding interface 122' between highly resistive regions 120' of readout wafer 102' and doped regions 112' of absorber wafer 104' because its resistance exceeds that of conducting bonds by at least a factor of 10.sup.2-10.sup.4, or preferably 10.sup.4-10.sup.6, or even more preferably 10.sup.6-10.sup.8. Minority carriers (electrons) thus never move across a bonding interface between low-doped wafers where trapping and recombination might occur. Regions 120' therefore lead to pixel isolation and prevent the n-wells of the p-MOS transistors in pixel readout electronics 115' from acting as charge collectors along with n-doped plugs 110' which alone pick up the electrons generated by electromagnetic radiation in absorber wafer 104'. The charge collectors 110' communicate with the pixel readout electronics 115' of readout wafer 102' wherein the charge pulses generated by electromagnetic radiation are processed and forwarded to the off-pixel part of the readout electronics. The detector pixels are exclusively defined by the heavily doped plugs 110' in readout wafer 102', while absorber wafer 104' is unpatterned. The width 118' of plugs 110' should be substantially smaller than the pixel size 113' (for example by a factor of 5-10), the latter ranging within about 100-200 .mu.m, 50-100 .mu.m or 20-50 .mu.m or even 5-20 .mu.m. Width 118' may for example range within about 0.1-2.5 .mu.m.

[0073] The pixel detector according to embodiment 100' is designed for detecting electrons from the electron-hole pairs generated by X-rays in absorber wafer 104'. In an aspect of the embodiment the detector may be designed for hole collection by reversing appropriate doping signs. The doping levels of p-doped regions may be about the same as the doping levels of n-doped regions discussed above. Somewhat higher doping by a factor of about 1.5 is needed for similar resistivity levels as for the n-doping case.

[0074] According to its design (see FIG. 2B), made up of unpatterned absorber wafer 104', embodiment 100' does not require any precise alignment of readout wafer 102' and absorber wafer 104' in the bonding tool. It is sufficient to use approximate alignment as offered by superimposing wafer alignment features such as notches or flats supplied by wafer manufacturers which permit to keep the rotational misalignment of the two wafers within about 0.1 to 0.2 degrees, and the lateral displacement within about 200-400 .mu.m, as offered for example by the alignment and flipper module of the EVG580 ComBond tool. Embodiment 100' does not therefore require any additional alignment marks on readout and absorber wafer.

[0075] The absorber wafer 104' may for example be a Si, SiC, Ge, GaAs, CdTe, or a CdZnTe alloy wafer obtained by bulk crystal growth. Alternatively, it may originate from at least one epitaxial layer of any of these materials on a single crystal substrate, which may optionally be removed after the covalent bonding step.

[0076] Referring now to FIG. 2C, a third embodiment 200 of the monolithic pixel detector 201 adapted to the detection of X-rays may include a bonding interface between thin readout wafer 202 and absorber wafer 204. The readout wafer may have been fabricated for example by CMOS processing a weakly p-doped substrate 206 with a high resistivity preferably of about 1-2 k.OMEGA. cm or even 2-5 k.OMEGA. cm which is thinned to a thickness of about 10-30 .mu.m or preferably about 5-10 .mu.m or even 3-5 .mu.m after all the processing has been completed. The thinning may require the planarization of the CMOS stack and the bonding of a carrier wafer before substrate 206 can be thinned. Absorber wafer 204 is preferably highly resistive, lightly p-doped and may include highly conducting n.sup.+-doped regions 212 which may be a heavily doped implants or a heavily doped epitaxial layers. The doping level of highly conducting regions 212 may for example be between 1.times.10.sup.18-1.times.10.sup.19 cm.sup.-3 or preferably 1.times.10.sup.19-1.times.10.sup.20 cm.sup.-3 or even 1.times.10.sup.20-5.times.10.sup.20 cm.sup.-3, corresponding to a resistivity between about 5-20 m.OMEGA. cm, 0.7-5 m.OMEGA. cm and 0.2-0.7 m.OMEGA. cm, respectively. Optionally, absorber wafer 204 may further include heavily p-doped layer 217, facilitating ohmic contact formation with metallic back contact 216, The bonding interface may consist of conducting covalent semiconductor bond 208 between highly conducting n.sup.+-doped plugs 210 with similar doping levels extending through substrate 206 and conducting n.sup.+-doped regions 212 of the absorber wafer, thereby forming an ohmic contact, and poorly conducting covalent semiconductor bond 209 between the part of heavily doped regions 212 of the absorber wafer facing regions of low doped substrate 206. Poorly conducting covalent semiconductor bonds 209 have at least a 10.sup.2-10.sup.4, or preferably 10.sup.4-10.sup.6, or even more preferably 10.sup.6-10.sup.8 times higher resistivity than ohmic conducting bonds 208. Heavily doped plugs 210 may be formed for example by etching holes in lightly p-doped substrate 206 and their filling with n.sup.+-material in a subsequent epitaxy step known in the art. Heavily doped plugs 210 bonded to heavily n-doped regions 212 serve as charge collectors, collecting electrons from electron-hole pairs which are generated by electromagnetic radiation incident on absorber 204 and separated in the electric field of the reverse biased p-n junction 214 between n-doped regions 212 and the lightly p-doped bulk of wafer 204, upon applying a voltage to back contact 216 on absorber wafer 204. Minority carriers (electrons) thus never move across a poorly conducting bonding interface between low-doped wafers where trapping and recombination might occur. The charge collectors 210 communicate with the pixel readout electronics 215 of readout wafer 202 wherein the charge pulses generated by electromagnetic radiation are processed and forwarded to the off-pixel part of the readout electronics. The detector pixels are defined by the heavily doped plugs 210 the width 218 of which may for example range within about 0.5-2 .mu.m or preferably about 0.5-1 .mu.m. The distance L between plugs 210 defines the pixel size 213 which can vary in a wide range within about 100-200 .mu.m, 50-100 .mu.m or 20-50 .mu.m or even 5-20 .mu.m, Heavily doped regions 212 in absorber wafer 204 are surrounded by insulating oxide regions 220 forming substantially an electrically insulating semiconductor-to-oxide or oxide-to-oxide bond 222 between readout and absorber wafer with a resistance exceeding that of bond 208 by at least a factor of 10.sup.3-10.sup.4, or preferably 10.sup.4-10.sup.6, or even more preferably 10.sup.6-10.sup.8. The purpose of these oxide regions is to electrically isolate adjacent pixels from each other. Their width 224 may be smaller, equal or larger than width 226 of heavily doped regions 212 of absorber wafer 204, depending on the desired speed of pixel detector 200, which in turn depends on the size of the capacitor plate defined by width 226 of heavily doped region 212. Since width 226 of heavily doped regions 212 is preferably chosen to be larger that width 218 of heavily doped plugs 210, for example twice or three times as large or even as large as for example 90% of pixel size 213, the requirements for bonding alignment are more relaxed than in embodiment 100.

[0077] The pixel detector according to embodiment 200 is designed for detecting electrons from the electron-hole pairs generated by X-rays in absorber wafer 204. In an aspect of the embodiment the detector may be designed for hole collection by reversing the doping signs. The doping levels of p-doped regions may be about the same as the doping levels of n-doped regions discussed above. Somewhat higher doping by a factor of about 1.5 is needed for similar resistivity levels as for the n-doping case.

[0078] According to its design (see FIG. 2C), embodiment 200 requires precise mutual alignment of readout wafer 202 and absorber wafer 204 because oxide regions 220 in absorber wafer 204 are essentially spaced at pixel size 213 and serve as additional pixel isolation. Furthermore, heavily doped plugs 210 and heavily doped regions 212 need to be aligned in the bonding tool. In order to permit accurate alignment thin readout wafer 202 and absorber wafer 204 are both equipped with at least two special wafer alignment features in the form of alignment marks positioned for example close to the wafer edges on opposite sides. With the help of superimposing such alignment marks the rotational misalignment of 200 mm wafers may be kept below about 5.times.10.sup.-4 degrees and the lateral misalignment below 1 .mu.m. Similar accuracy may be obtained in case of smaller wafer bonding.

[0079] The absorber wafer 204 may for example be a Si, Sia Ge, GaAs, CdTe, or a CdZnTe alloy wafer obtained by bulk crystal growth. Alternatively, it may originate from at least one epitaxial layer of any of these materials on a single crystal substrate, which may optionally be removed after the covalent bonding step.

[0080] Referring now to FIG. 2D, fourth embodiment 200' of monolithic pixel detector 201' adapted to the detection of X-rays may include a bonding interface between thin readout wafer 202' and absorber wafer 204'. The readout wafer may have been fabricated for example by CMOS processing a weakly p-doped substrate 206' with a resistivity preferably of about 1-2 k.OMEGA. cm or even 2-5 k.OMEGA. cm which is thinned to a thickness of about 10-30 .mu.m or preferably about 5-10 .mu.m or even 3-5 .mu.m after all the processing has been completed. The thinning may require the planarization of the CMOS stack and the bonding of a carrier wafer before substrate 206' can be thinned. Absorber wafer 204' may include highly conducting n.sup.+-doped regions 212' which may be a heavily doped implants or a heavily doped epitaxial layers. The doping level of highly conducting regions 212' may for example be between 1.times.10.sup.18-1.times.10.sup.19 cm.sup.-3 or preferably 1.times.10.sup.19-1.times.10.sup.20 cm.sup.-3 or even 1.times.10.sup.20-5.times.10.sup.20 cm.sup.-3, corresponding to a resistivity between about 5-20 m.OMEGA. cm, 0.7-5 m.OMEGA. cm and 0.2-0.7 m.OMEGA. cm, respectively. Optionally, absorber wafer 204' may further include heavily p-doped layer 217', facilitating ohmic contact formation with metallic back contact 216'. The bonding interface may consist of conducting covalent semiconductor bond 208' between highly conducting n.sup.+-doped plugs 210' extending through substrate 206' and conducting n.sup.+-doped regions 212' of absorber wafer 204'. The doping level of plugs 210' is similar to that of regions 212', guaranteeing an ohmic contact between the two. The bonding interface between wafers 202', 204' furthermore includes poorly conducting covalent semiconductor bond 209' between the portion of heavily doped regions 212' of the absorber wafer facing regions of low doped substrate 206'. Poorly conducting covalent semiconductor bonds 209' have at least a 10.sup.2-10.sup.4, or preferably 10.sup.4-10.sup.6, or even more preferably 10.sup.6-10.sup.8 times higher resistivity than ohmic conducting bonds 208'. Heavily doped plugs 210', only one of which is shown in FIG. 2D, may be formed for example by etching holes in lightly p-doped substrate 206' and their filling with n.sup.+-material in a subsequent epitaxy step known in the art. Heavily doped plugs 210' bonded to heavily doped regions 212' form an ohmic contact between the two and serve as charge collectors, collecting electrons from electron-hole pairs which are generated by electromagnetic radiation incident on absorber 204' and separated in the electric field of the reverse biased p-n junction 214' between highly n-doped regions 212' and lightly p-doped substrate 206', upon applying a voltage to back contact 216' on absorber wafer 204'. Minority carriers (electrons) thus never move across a poorly conducting bonding interface between low-doped wafers where trapping and recombination might occur. The charge collectors 210' communicate with the pixel readout electronics 215' of readout wafer 202' wherein the charge pulses generated by electromagnetic radiation are processed and forwarded to the off-pixel part of the readout electronics. The detector pixels are defined by the heavily doped plugs 210' the width 218' of which may for example range within about 0.5-2 .mu.m or preferably about 0.5-1 .mu.m. The distance L between plugs 210' defines the pixel size 213' which can vary in a wide range within about 100-200 .mu.m, 50-100 .mu.m or 20-50 .mu.m or even 5-20 .mu.m. Heavily doped regions 212' in absorber wafer 204' are surrounded by oxide regions 220' of width 224' which may for example range within about 0.5-2 .mu.m or preferably about 0.5-1 .mu.m. Oxide regions 220' form electrically insulating oxide-to-oxide bonds 222' between absorber wafer 204' and oxide filled trenches 226' extending through readout wafer 202'. The width trenches 226' is preferably about the same as that of oxide regions 220'. Oxide regions 220', 226' isolate adjacent pixels from each other, and their spacing corresponds again to the pixel size L. Similar to embodiment 200 bonding alignment is facilitated here since heavily doped regions 212' cover most of pixel size 213'.

[0081] The pixel detector according to embodiment 200' is designed for detecting electrons from the electron-hole pairs generated by X-rays in absorber wafer 204'. In an aspect of the embodiment the detector may be designed for hole collection by reversing the appropriate doping signs. The doping levels of p-doped regions may be about the same as the doping levels of n-doped regions discussed above. Somewhat higher doping by a factor of about 1.5 is needed for similar resistivity levels as for the n-doping case.

[0082] According to its design (see FIG. 2D) embodiment 200' requires precise mutual alignment of readout wafer 202' and absorber wafer 204' for bonding, because oxide regions 220' in absorber wafer 204' and insulating oxide regions 226' of readout wafer 202' are essentially spaced at pixel size 213' and have to match during forming bonding interface 222'. Heavily doped plugs 210' and heavily doped regions 212' equally need to be aligned to form an ohmic contact at bonding interface 208'. In order to permit accurate alignment thin readout wafer 202' and absorber wafer 204' are both equipped with at least two special wafer alignment features in the form of alignment marks positioned for example close to the wafer edges on opposite sides. With the help of superimposing such alignment marks the rotational misalignment of 200 mm wafers may be kept within about (2-5).times.10.sup.-4 degrees and the lateral misalignment within about 0.5-1 .mu.m. Similar accuracy may be obtained in case of smaller wafer bonding.

[0083] The absorber wafer 204' may for example be a Si, SiC, Ge, GaAs, CdTe, or a CdZnTe alloy wafer obtained by bulk crystal growth. Alternatively, it may originate from at least one epitaxial layer of any of these materials on a single crystal substrate, which may optionally be removed after the covalent bonding step.