Average And Decimate Operations For Bang-bang Phase Detectors

Abramzon; Valentin ; et al.

U.S. patent application number 16/109645 was filed with the patent office on 2019-09-12 for average and decimate operations for bang-bang phase detectors. The applicant listed for this patent is Samsung Display Co., Ltd.. Invention is credited to Valentin Abramzon, Amir Amirkhany, Anup P. Jose.

| Application Number | 20190280591 16/109645 |

| Document ID | / |

| Family ID | 67843554 |

| Filed Date | 2019-09-12 |

| United States Patent Application | 20190280591 |

| Kind Code | A1 |

| Abramzon; Valentin ; et al. | September 12, 2019 |

AVERAGE AND DECIMATE OPERATIONS FOR BANG-BANG PHASE DETECTORS

Abstract

A system and method for a decimated phase detector circuit includes a bang bang phase detector (BBFD), an UP rolling counter connected to an UP output of the BBFD, and a DOWN rolling counter connected to a DOWN output of the BBFD. A charge pump is connected to the UP rolling counter and the DOWN rolling counter and is configured to receive a decimated UP signal from the UP rolling counter and a decimated DOWN signal from the DOWN rolling counter. The charge pump is further configured to provide a control voltage according to the received decimated UP signals and decimated DOWN signals.

| Inventors: | Abramzon; Valentin; (Mountain View, CA) ; Amirkhany; Amir; (Sunnyvale, CA) ; Jose; Anup P.; (San Jose, CA) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 67843554 | ||||||||||

| Appl. No.: | 16/109645 | ||||||||||

| Filed: | August 22, 2018 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 62641911 | Mar 12, 2018 | |||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H02M 3/07 20130101; H03K 21/08 20130101; H03K 21/16 20130101 |

| International Class: | H02M 3/07 20060101 H02M003/07; H03K 21/08 20060101 H03K021/08 |

Claims

1. A decimated phase detector circuit comprising: a bang bang phase detector (BBFD); an UP rolling counter connected to an UP output of the BBFD, wherein the UP rolling counter is configured to output the decimated UP signal each time the UP state of the UP rolling counter rolls over to zero; a DOWN rolling counter connected to a DOWN output of the BBFD, wherein the DOWN rolling counter is configured to output the decimated DOWN signal each time the DOWN state of the DOWN rolling counter rolls over to zero; and a charge pump connected to the UP rolling counter and the DOWN rolling counter and is configured to receive a decimated UP signal from the UP rolling counter each time the UP rolling counter rolls over to zero and a decimated DOWN signal from the DOWN rolling counter each time the DOWN rolling counter rolls over to zero, wherein the charge pump is further configured to provide a control voltage according to the received decimated UP signals and decimated DOWN signals.

2. The decimated phase detector circuit of claim 1, wherein the UP rolling counter is configured to incrementing an UP state each time an UP is provided by the UP output of the BBFD and the DOWN rolling counter is configured to incrementing a DOWN state each time a DOWN is provided by the DOWN output of the BBFD.

3. (canceled)

4. The decimated phase detector circuit of claim 1, wherein: the UP rolling counter comprises: an UP ripple counter connected to the UP output of the BBFD; and an UP falling edge detector connected to an output of the UP ripple counter, wherein the UP falling edge detector is configured to output the decimated UP signal when the UP ripple counter rolls over; and the DOWN rolling counter comprises: a DOWN ripple counter connected to the DOWN output of the BBFD; and a DOWN falling edge detector connected to an output of the ripple counter, wherein the DOWN falling edge detector is configured to output the decimated DOWN signal when the DOWN ripple counter rolls over.

5. The decimated phase detector circuit of claim 4, wherein the BBFD comprises a dual data rate BBFD and the UP and DOWN ripple counters comprise a dual data rate interface.

6. The decimated phase detector circuit of claim 1, wherein the charge pump comprises an integrator configured to store a value representative of a total of decimated UP signals minus a total of decimated DOWN signals.

7. The decimated phase detector circuit of claim 1, wherein: the UP rolling counter comprises an UP N-bit rolling counter configured to output the decimated UP signal after every 2.sup.Nth UP signal received from the BBPD; and the DOWN rolling counter comprises a DOWN N-bit rolling counter configured to output the decimated DOWN signal after every 2.sup.Nth DOWN signal received from the BBPD.

8. The decimated phase detector circuit of claim 7, wherein: the UP N-bit rolling counter comprises an UP 2-bit rolling counter configured to output the decimated UP signal after every fourth UP signal received from the BBPD; and the DOWN N-bit rolling counter comprises a DOWN 2-bit rolling counter configured to output the decimated DOWN signal after every fourth DOWN signal received from the BBPD.

9. The decimated phase detector circuit of claim 1, further comprising a voltage controlled oscillator configured to generate a clock according to the control voltage.

10. A method of decimating a bang bang phase detector comprising: receiving, at an UP rolling counter, UP signals from the bang bang phase detector (BBFD) and incrementing an UP state for each received UP signal; receiving, at a DOWN rolling counter, down signals from the BBFD, and incrementing a DOWN state for each received DOWN signal; providing to a charge pump, by the UP rolling counter, a decimated UP signal each time the UP state of the UP rolling counter rolls over to zero; and providing to the charge pump, by the DOWN rolling counter, a decimated DOWN signal each time the DOWN state of the DOWN rolling counter rolls over to zero.

11. The method of decimating a BBFD of claim 10, further comprising integrating, at the charge pump, a total of decimated UP signals minus a total of decimated DOWN signals.

12. The method of decimating a BBFD of claim 11, further comprising providing, by the charge pump, a control voltage according to the total of decimated UP signals minus the total of decimated DOWN signals.

13. The method of decimating a BBFD of claim 12, wherein the control voltage is provided to a voltage controlled oscillator.

14. The method of decimating a BBFD of claim 10, wherein: the UP rolling counter comprises: an UP ripple counter connected to an UP output of the BBFD; and an UP falling edge detector connected to an output of the UP ripple counter, wherein the UP falling edge detector is configured to output the decimated UP signal when the UP ripple counter rolls over to zero; and the DOWN rolling counter comprises: a DOWN ripple counter connected to a DOWN output of the BBFD; and a DOWN falling edge detector connected to an output of the ripple counter, wherein the DOWN falling edge detector is configured to output the decimated DOWN signal when the DOWN ripple counter rolls over to zero.

15. The method of decimating a BBFD of claim 10, wherein: the UP rolling counter comprises an UP N-bit rolling counter configured to output the decimated UP signal after every 2.sup.Nth UP signal received from the BBPD; and the DOWN rolling counter comprises a DOWN N-bit rolling counter configured to output the decimated DOWN signal after every 2.sup.Nth DOWN signal received from the BBPD.

16. A method of decimating a bang bang phase detector comprising: incrementing, at an UP rolling counter, an UP state based on a received UP signal from the bang bang phase detector (BBFD); incrementing, at a DOWN rolling counter, a DOWN state based on a received down signal from the BBFD; providing, by the UP rolling counter, a decimated UP signal to a charge pump, each time the UP state of the UP rolling counter rolls over to zero; providing, by the DOWN rolling counter, a decimated DOWN signal to the charge pump, each time the DOWN state of the DOWN rolling counter rolls over to zero; and integrating, at the charge pump, a total of decimated UP signals minus a total of decimated DOWN signals.

17. The method of decimating a BBFD of claim 16, wherein the UP rolling counter comprises: an UP ripple counter connected to an UP output of the BBFD; and an UP falling edge detector connected to an output of the UP ripple counter, wherein the UP falling edge detector is configured to output the decimated UP signal when the UP state of the UP ripple counter rolls over.

18. The method of decimating a BBFD of claim 17, wherein the DOWN rolling counter comprises: a DOWN ripple counter connected to a DOWN output of the BBFD; and a DOWN falling edge detector connected to an output of the ripple counter, wherein the DOWN falling edge detector is configured to output the decimated DOWN signal when the DOWN state of the DOWN ripple counter rolls over.

19. The method of decimating a BBFD of claim 16, further comprising providing, by the charge pump, a control voltage according to the total of decimated UP signals minus the total of decimated DOWN signals.

20. The method of decimating a BBFD of claim 16, wherein: the UP rolling counter comprises an UP N-bit rolling counter configured to output the decimated UP signal after every 2.sup.Nth UP signal received from the BBPD; and the DOWN rolling counter comprises a DOWN N-bit rolling counter configured to output the decimated DOWN signal after every 2.sup.Nth DOWN signal received from the BBPD.

Description

CROSS-REFERENCE TO RELATED APPLICATION

[0001] The present application claims priority to, and the benefit of, U.S. Provisional Patent Application No. 62/641,911, filed on Mar. 12, 2018, the contents of which are incorporated herein by reference in its entirety.

BACKGROUND

[0002] Some embodiments of the present disclosure relate generally to bang-bang phase detectors in analog clock data recovery (CDR).

[0003] Serial links include a transmitter connected to a receiver via a channel. The receiver generally includes a circuit configured to generate a clock that aligns with the phase of the incoming data.

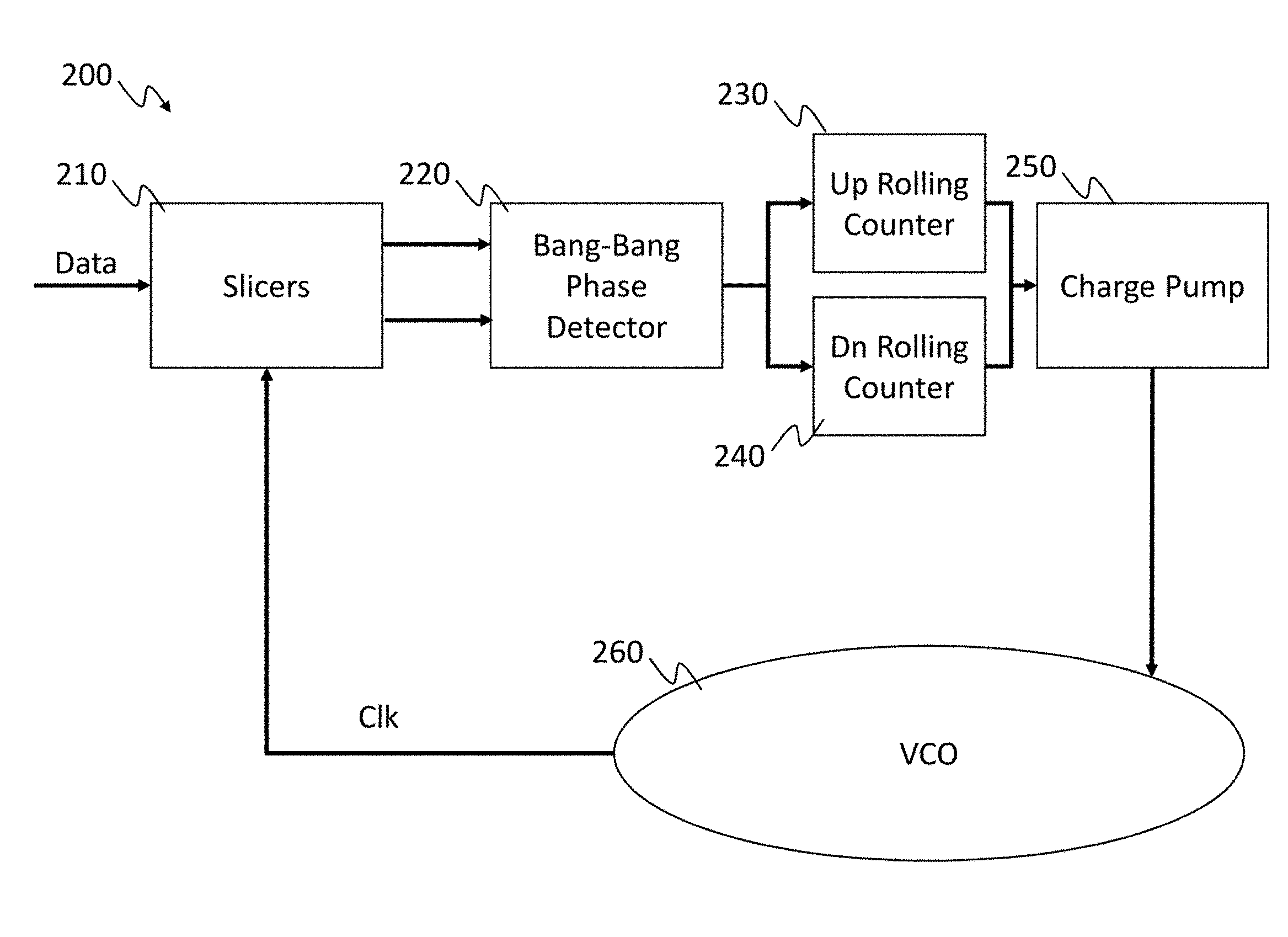

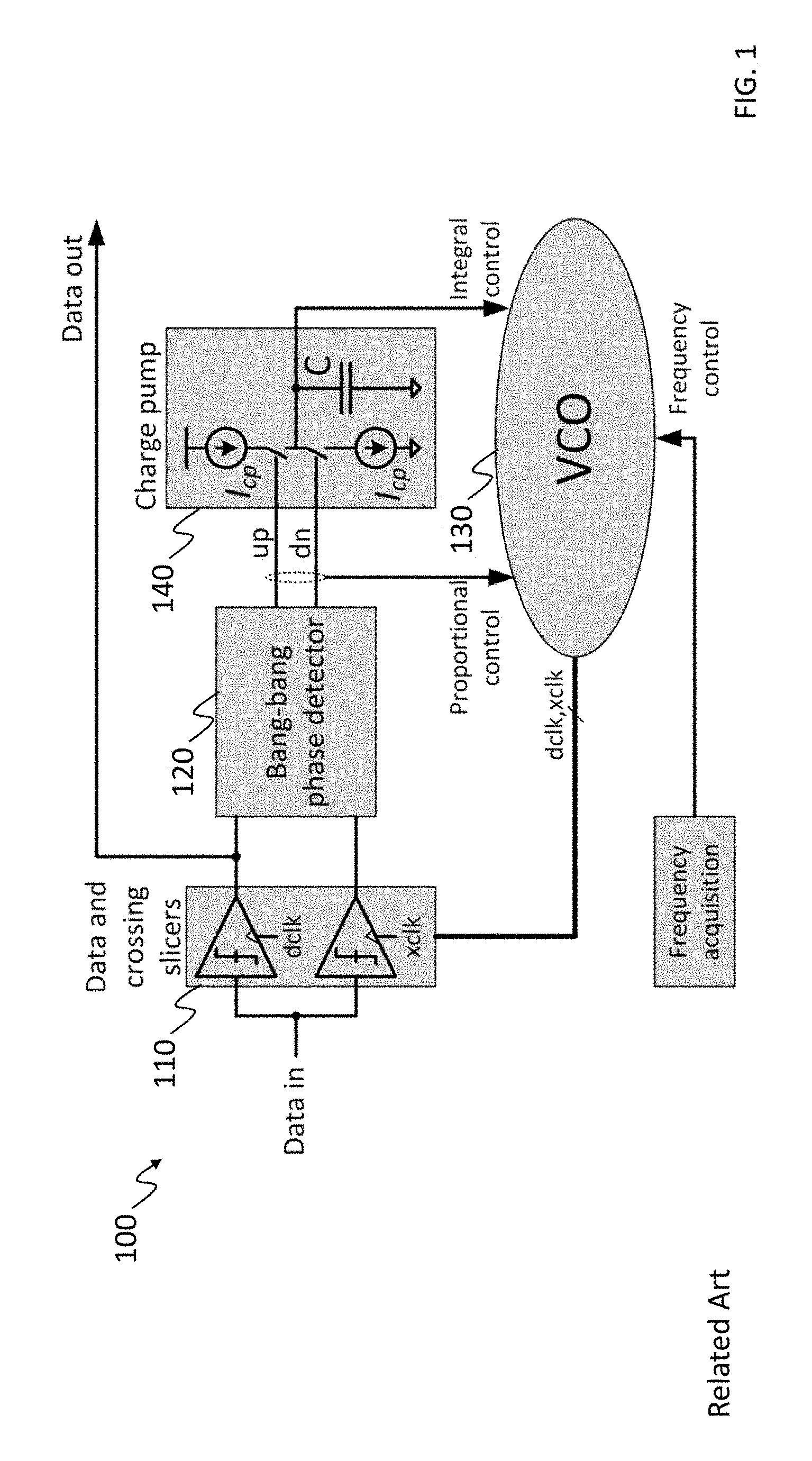

[0004] FIG. 1 depicts a related art CDR circuit configured to align a locally generated clock with an incoming data signal.

[0005] Referring to FIG. 1, a related art CDR system 100 includes data and crossing slicers 110 that sample the incoming data and provide the data to the bang-bang phase detector 120. The bang-bang phase detector 120 determines if the phase of the clock generated by a voltage controlled oscillator (VCO) 130 is in alignment (e.g., in phase) with the incoming data. A bang-bang phase detector has 3 states that include the phase being early, late, or that there is no useful information (e.g., there is no data transition required to determine phase alignment). Based on the current state, the bang-bang phase detector 120 outputs an up value or a down value. The up and down signals are provided to a charge pump 140 which activates a switch to increase or decrease the control voltage of the VCO 130. For example, when an up signal is received at the charge pump 140, the charge pump increases the control voltage of the VCO 130 and the speed of the clock generated is increased. Similarly, when a down signal is received at the charge pump 140, the charge pump 140 decreases the control voltage of the VCO 130 and the speed of the clock generated is decreased.

[0006] CDRs that use bang-bang phase detectors with charge pumps suffer from a number of problems. For example, the loop needs to have a low bandwidth to filter jitter due to inter-symbol interference (ISI), which requires either a large charge pump capacitor (C) or a small charge pump current (Icp), which causes the charge pump to be sensitive to mismatch, charge injection, and other non-idealities. Additionally, it may be difficult to operate a charge pump at a high frequency, especially with a small charge pump current (Icp) (e.g., the charge injection may overwhelm the Icp).

[0007] Thus, a method of decimating the number of ups and downs from the bang-bang phase detector is needed. Related art methods of decimating the output of a bang-bang phase detector often discard information. For example, some systems decimate the bang-bang phase detector by a factor N (e.g., every Nth output is provided). Some systems decimate by adding all the ups and subtracting all the downs for a period of time and outputting the sign of the result. This summing method, however, discards how many more ups than downs or downs than ups occurred. Thus, an improved system and method that requires less power, space, and maintains the fidelity of the number of ups and downs output by the bang-bang phase detector is desired.

[0008] The above information is only for enhancement of understanding of the background of embodiments of the present disclosure, and therefore may contain information that does not form the prior art.

SUMMARY

[0009] Some embodiments of the present disclosure provide a system and method for a decimated phase detector circuit. The decimated phase detector circuit may include a bang bang phase detector (BBFD), an UP rolling counter connected to an UP output of the BBFD, and a DOWN rolling counter connected to a DOWN output of the BBFD. The decimated phase detector circuit also includes a charge pump connected to the UP rolling counter and the DOWN rolling counter and is configured to receive a decimated UP signal from the UP rolling counter and a decimated DOWN signal from the DOWN rolling counter, wherein the charge pump is further configured to provide a control voltage according to the received decimated UP signals and decimated DOWN signals.

[0010] In various embodiments, the UP rolling counter is configured to incrementing an UP state each time an UP is provided by the UP output of the BBFD and the DOWN rolling counter is configured to incrementing a DOWN state each time a DOWN is provided by the DOWN output of the BBFD.

[0011] In various embodiments, the UP rolling counter is configured to output the decimated UP signal each time the UP state of the UP rolling counter rolls over to zero; and the DOWN rolling counter is configured to output the decimated DOWN signal each time the DOWN state of the DOWN rolling counter rolls over to zero.

[0012] In various embodiments, the UP rolling counter includes an UP ripple counter connected to the UP output of the BBFD and an UP falling edge detector connected to an output of the UP ripple counter. In various embodiments, the UP falling edge detector is configured to output the decimated UP signal when the UP ripple counter rolls over.

[0013] In various embodiments, the DOWN rolling counter includes a DOWN ripple counter connected to the DOWN output of the BBFD and a DOWN falling edge detector connected to an output of the ripple counter. In various embodiments, the DOWN falling edge detector is configured to output the decimated DOWN signal when the DOWN ripple counter rolls over.

[0014] In various embodiments, the BBFD comprises a dual data rate BBFD and the UP and DOWN ripple counters comprise a dual data rate interface.

[0015] In various embodiments, the charge pump is an integrator configured to store a value representative of a total of decimated UP signals minus a total of decimated DOWN signals.

[0016] In various embodiments, the UP rolling counter is an UP N-bit rolling counter configured to output the decimated UP signal after every 2Nth UP signal received from the BBPD and the DOWN rolling counter is a DOWN N-bit rolling counter configured to output the decimated DOWN signal after every 2Nth DOWN signal received from the BBPD.

[0017] In various embodiments, the UP N-bit rolling counter is an UP 2-bit rolling counter configured to output the decimated UP signal after every fourth UP signal received from the BBPD.

[0018] In various embodiments, the DOWN N-bit rolling counter is a DOWN 2-bit rolling counter configured to output the decimated DOWN signal after every fourth DOWN signal received from the BBPD.

[0019] In various embodiments, the decimated phase detector circuit further includes a voltage controlled oscillator configured to generate a clock according to the control voltage.

[0020] In various embodiments, a method of decimating a bang bang phase detector includes receiving, at an UP rolling counter, UP signals from the bang bang phase detector (BBFD) and incrementing an UP state for each received UP signal; receiving, at a DOWN rolling counter, down signals from the BBFD, and incrementing a DOWN state for each received DOWN signal; providing, by the UP rolling counter, a decimated UP signal each time the UP state of the UP rolling counter rolls over to zero; and providing, by the DOWN rolling counter, a decimated DOWN signal each time the DOWN state of the DOWN rolling counter rolls over to zero.

[0021] In various embodiments, the method further includes integrating, at a charge pump, a total of decimated UP signals minus a total of decimated DOWN signals.

[0022] In various embodiments, the method further includes providing, by the charge pump, a control voltage according to the total of decimated UP signals minus the total of decimated DOWN signals.

[0023] In various embodiments, the control voltage is provided to a voltage controlled oscillator.

[0024] In various embodiments, the UP rolling counter includes an UP ripple counter connected to an UP output of the BBFD and an UP falling edge detector connected to an output of the UP ripple counter.

[0025] In various embodiments, the UP falling edge detector is configured to output the decimated UP signal when the UP ripple counter rolls over to zero.

[0026] In various embodiments, the DOWN rolling counter includes a DOWN ripple counter connected to a DOWN output of the BBFD and a DOWN falling edge detector connected to an output of the ripple counter.

[0027] In various embodiments, the DOWN falling edge detector is configured to output the decimated DOWN signal when the DOWN ripple counter rolls over to zero.

[0028] In various embodiments, the UP rolling counter is an UP N-bit rolling counter configured to output the decimated UP signal after every 2.sup.Nth UP signal received from the BBPD.

[0029] In various embodiments, the DOWN rolling counter includes a DOWN N-bit rolling counter configured to output the decimated DOWN signal after every 2.sup.Nth DOWN signal received from the BBPD.

[0030] In various embodiments, a method of decimating a bang bang phase detector includes: incrementing, at an UP rolling counter, an UP state based on a received UP signal from the bang bang phase detector (BBFD); incrementing, at a DOWN rolling counter, a DOWN state based on a received down signal from the BBFD; providing, by the UP rolling counter, a decimated UP signal to a charge pump, each time the UP state of the UP rolling counter rolls over to zero; providing, by the DOWN rolling counter, a decimated DOWN signal to the charge pump, each time the DOWN state of the DOWN rolling counter rolls over to zero; and integrating, at the charge pump, a total of decimated UP signals minus a total of decimated DOWN signals.

[0031] In various embodiments, the the UP rolling counter is an UP ripple counter connected to an UP output of the BBFD and an UP falling edge detector connected to an output of the UP ripple counter. In various embodiments, the UP falling edge detector is configured to output the decimated UP signal when the UP state of the UP ripple counter rolls over.

[0032] In various embodiments, the DOWN rolling counter includes a DOWN ripple counter connected to a DOWN output of the BBFD and a DOWN falling edge detector connected to an output of the ripple counter. In various embodiments, the DOWN falling edge detector is configured to output the decimated DOWN signal when the DOWN state of the DOWN ripple counter rolls over.

[0033] In various embodiments, the method further includes providing, by the charge pump, a control voltage according to the total of decimated UP signals minus the total of decimated DOWN signals.

[0034] In various embodiments, the UP rolling counter includes an UP N-bit rolling counter configured to output the decimated UP signal after every 2Nth UP signal received from the BBPD.

[0035] In various embodiments, the DOWN rolling counter includes a DOWN N-bit rolling counter configured to output the decimated DOWN signal after every 2Nth DOWN signal received from the BBPD.

BRIEF DESCRIPTION OF THE DRAWINGS

[0036] Some embodiments can be understood in more detail from the following description taken in conjunction with the accompanying drawings, in which:

[0037] FIG. 1 depicts a related art CDR;

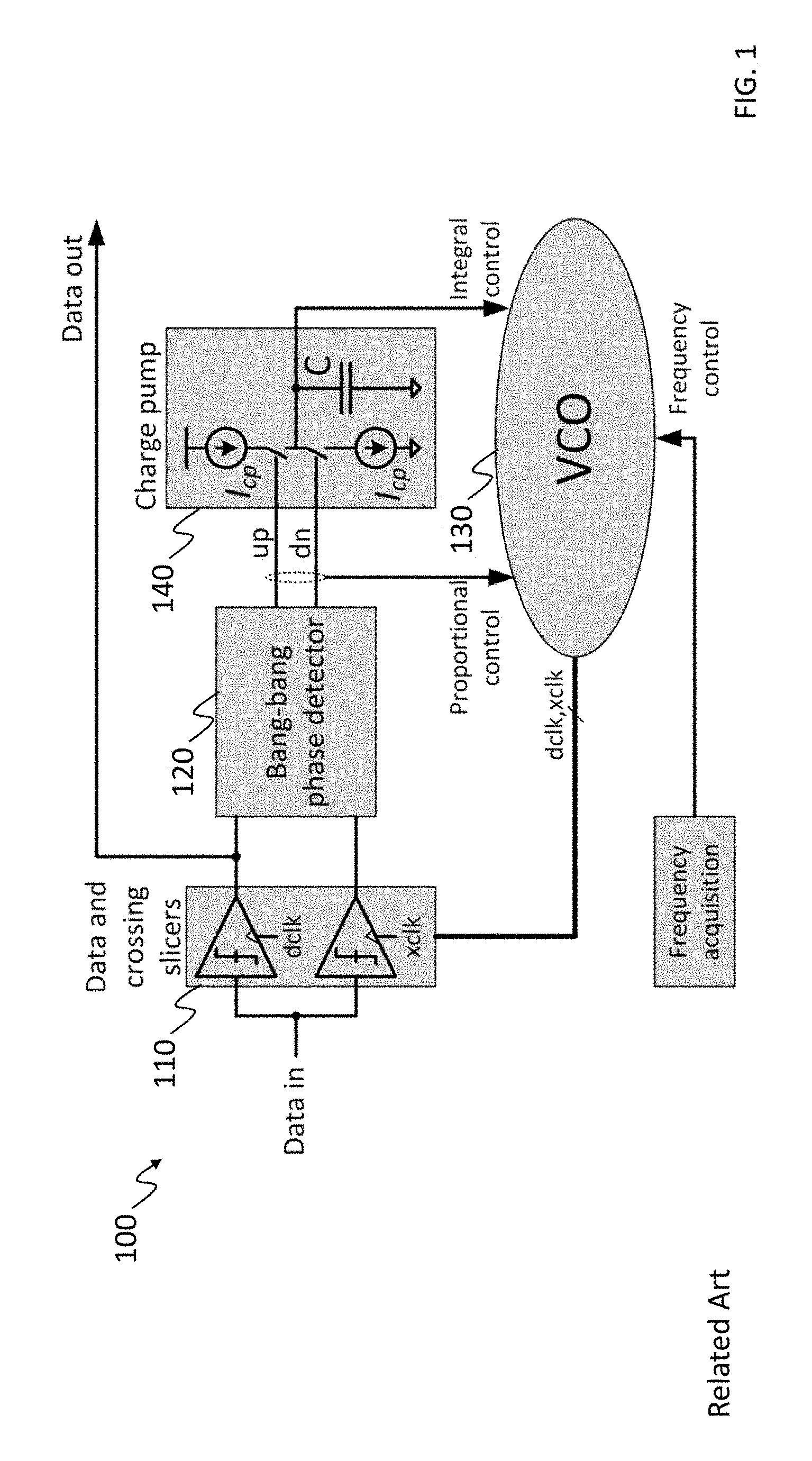

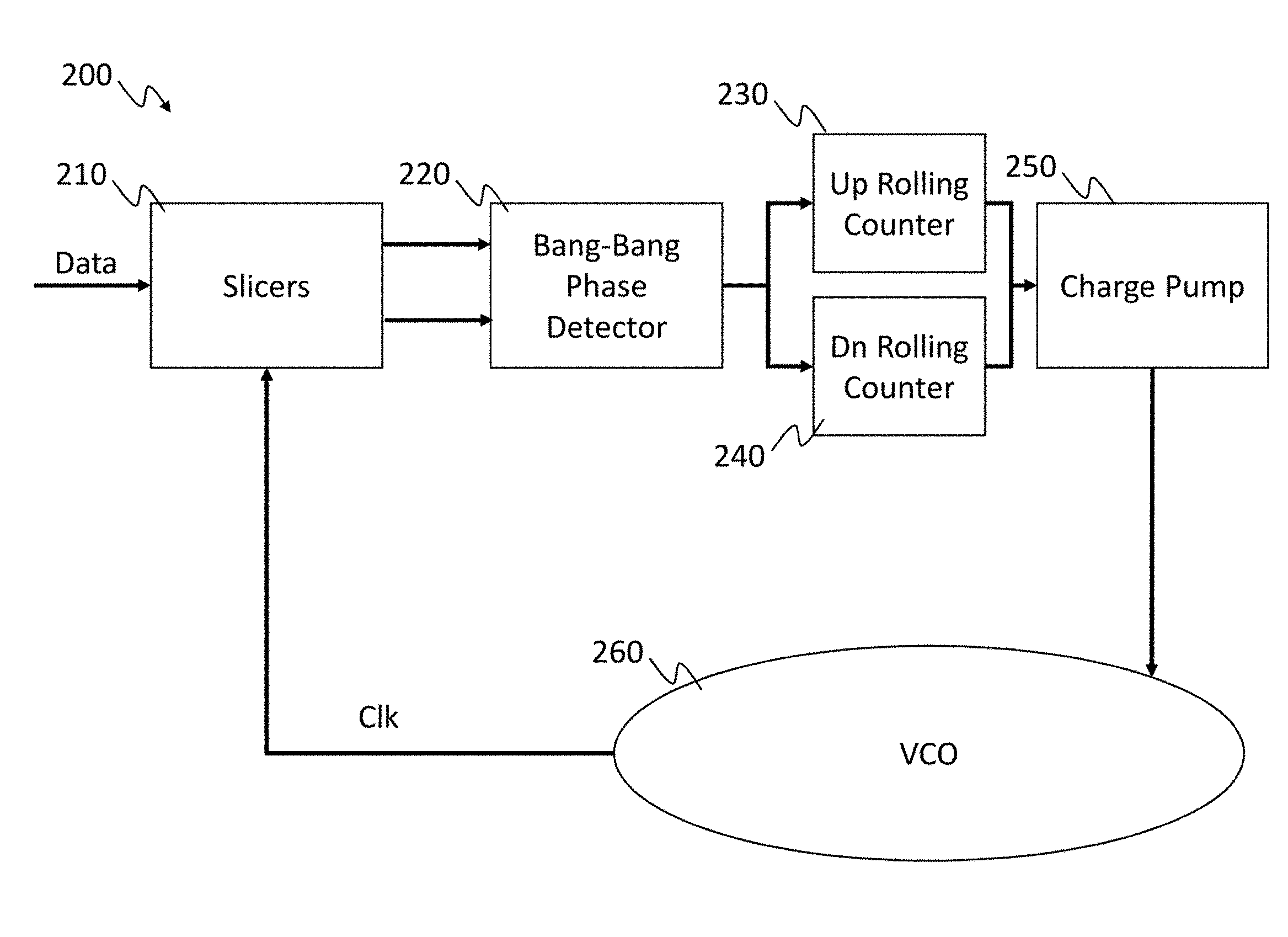

[0038] FIG. 2A depicts a CDR with a decimated BBPD circuit according to various embodiments of the present disclosure;

[0039] FIG. 2B depicts a timing diagram of the operation rolling counters of FIG. 2A according to various embodiments of the present disclosure;

[0040] FIG. 2C depicts a flow chart of the operation of the decimated BBPD according to various embodiments of the present disclosure;

[0041] FIG. 3 depicts a timing diagram according to various embodiments of the present disclosure;

[0042] FIG. 4 depicts a simulated plot of the output of UP/DOWN signals of a BBPD, decimated using several decimation techniques and integrated by the charge pump;

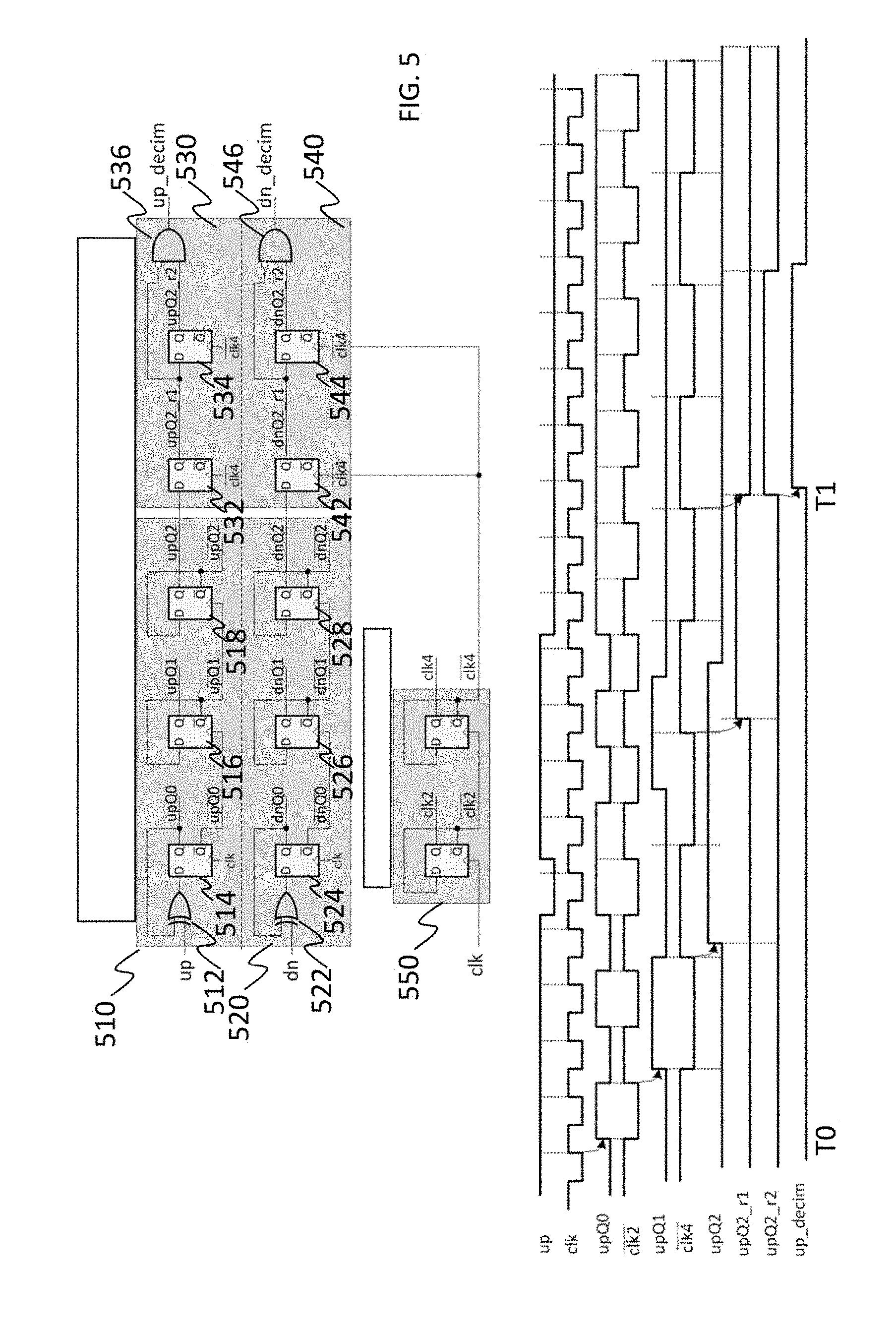

[0043] FIG. 5 depicts an embodiment of UP and DOWN rolling counters according to various embodiments;

[0044] FIG. 6 depicts a dual data rate (DDR) interface in a first rolling counter stage according to various embodiments.

DETAILED DESCRIPTION

[0045] Features of the inventive concept and methods of accomplishing the same may be understood more readily by reference to the following detailed description of embodiments and the accompanying drawings. Hereinafter, embodiments will be described in more detail with reference to the accompanying drawings, in which like reference numbers refer to like elements throughout. The present disclosure, however, may be embodied in various different forms, and should not be construed as being limited to only the illustrated embodiments herein. Rather, these embodiments are provided as examples so that this disclosure will be thorough and complete, and will fully convey the aspects and features of the present disclosure to those skilled in the art. Accordingly, processes, elements, and techniques that are not necessary to those having ordinary skill in the art for a complete understanding of the aspects and features of the present disclosure may not be described. Unless otherwise noted, like reference numerals denote like elements throughout the attached drawings and the written description, and thus, descriptions thereof will not be repeated. In the drawings, the relative sizes of elements, layers, and regions may be exaggerated for clarity.

[0046] Embodiments of the present disclosure include a system and method for decimating the output of a bang-bang phase detector (BBPD). In various embodiments, the system and method allows for the decimation of the BBPD output while still integrating the decimated up and down signals so that there is no error accumulation while using a standard charge pump (i.e., without the need for a multi-bit DAC to drive the charge pump). In various embodiments, a first rolling counter is used to count the number of up pulses generated by the BBPD and a second rolling counter is used to count the number of down pulses generated by the BBPD. Once either rolling counter reaches its maximum value, the rolling counter provides a decimated output to the charge pump, rolls over to the initial zero count, and continues counting from zero.

[0047] FIG. 2A depicts a CDR with a decimated BBPD circuit according to various embodiments of the present disclosure. FIG. 2B depicts a timing diagram of the operation of rolling counters of FIG. 2A according to various embodiments of the present disclosure. FIG. 2C depicts a flow chart of the operation of the decimated BBPD according to various embodiments of the present disclosure.

[0048] Referring to FIGS. 2A-C, in various embodiments a CDR 200 includes a decimated phase detector circuit with rolling counters to provide accurate decimation. In various embodiments, the CDR 200 includes a slicer 210 for receiving incoming data, a BBPD 220 for comparing the phase of the incoming data with the current clock (CLK), an UP rolling counter 230 for counting each UP output of the BBPD 220, a DOWN rolling counter 240 for counting each DOWN output of the BBPD 220, a charge pump 250 for maintaining and modifying the control voltage for the VCO 260 to generate the clock (CLK). In various embodiments, the charge pump 250 includes an integrator (e.g., a capacitor-based circuit for maintaining a voltage for controlling the VCO 260).

[0049] In various embodiments, the slicers 210 receive data from a transmitter and the BBFD 220 outputs UP signals, DOWN signals, and no output signals based on the slicer output (e.g. based on the phase alignment of the clock produced by the VCO 260). In various embodiments, the UP rolling counter 230 and DOWN rolling counter 240 are each N-bit (e.g., 2-bit) counters configured to drive the charge pump 250. Using an N-bit counter allows for the decimation of the output of the BBPD 220 by 2.sup.N (e.g., by 4 for a 2-bit counter). For example, referring to FIG. 2B, a timing diagram showing an example BBPD output and the corresponding states of the up rolling counter 230, down rolling counter 240, and charge pump integrator when using 2-bit rolling counters. In various embodiments, the BBPD 220 may output an UP when the VCO 260 should increase the clock speed, output a DOWN when the VCO 260 should decrease the clock speed, and output neither (e.g., no output) when a decision cannot be made (S200). In various embodiments, the UP rolling counter 230 and the DOWN rolling counter are configured to increment their state according to the number of UP and DOWN signals output by the BBFD (S210). For example, Each UP output by the BBPD 220 results in the UP rolling counter 230 incrementing its state once. Similarly, each DOWN output by the BBPD 220 results in the DOWN rolling counter 240 incrementing its state once. Since the UP rolling counter 230 and the DOWN rolling counter are 2-bit counters, they can count up to 3 Ups/3 DOWNs before their state rolls over to a value of zero (e.g., on the 4th up, the state of the rolling counter rolls over to zero). Each time a rollover occurs, the UP rolling counter 230 and the DOWN rolling counter 240 provide a decimated UP/DOWN signal to the charge pump 250 (e.g., to the charge pump integrator) (S220). The charge pump 250 maintains a control voltage according to the number of UP/DOWN signals and provides the control voltage to the VCO 260 to modify the clock output of the VCO 260 (S230).

[0050] In this embodiment, because the UP and DOWN rolling counters 230, 240 are 2-bit counters, each decimated UP or DOWN output provided to the charge pump has a corresponding effect that is equivalent to four UP/DOWN outputs from a BBFD. For example, in a non-decimated BBPD, the charge pump would incrementally increase the control voltage at the charge pump integrator with each UP or DOWN by either applying a capacitor current Icp or removing a capacitor current Icp. Therefore, in various embodiments, Icp should be increased according to the decimation (e.g., a factor of 4 since the BBPD is being decimated by 4). In various other embodiments, Icp may be the same and the VCO 260 may have an increased sensitivity to account for the decimation (e.g., VCO 260 may be 4 times more sensitive to changes in the control voltage). Similarly, if a 3-bit counter was used instead of a 2-bit counter, the BBPD 220 would be decimated by 8 (e.g., there would need to be 8 UPs before the UP rolling counter 230 would roll over to 0) and decimated UP and DOWN signals are equivalent to 8 regular BBPD UP/DOWN signals.

[0051] As shown by FIG. 2B, after a fourth UP is output by the BBPD at TO, the UP rolling counter 230 rolls over to zero and the decimated UP pulse is provided. As the UP values are being accumulated, DOWN values are also being supplied by the BBPD and being accumulated in the DOWN rolling counter 240. Once a fourth DOWN is output by the BBPD 220 at T1, the DOWN rolling counter 240 rolls over to zero and a decimated DOWN pulse is provided.

[0052] FIG. 3 depicts a timing diagram according to various embodiments of the present disclosure.

[0053] Referring to FIG. 3, in various embodiments, the system keeps track of the running sum of UPs and DOWNs provided by the BBPD. For example, as discussed above, the charge pump 250 includes an integrator. The charge pump integrator includes the coarse (e.g., decimated) UP/DOWN pulses while the UP rolling counter and the DOWN rolling counter include the fine UP/DOWN pulses. For example, at TO the UP rolling counter, the DOWN rolling counter, and the charge pump are each initially 0. The first line of the timing diagram includes the full-rate output of the BBPD. The output includes two initial UP outputs, a zero output, a DOWN output, four UP outputs, a zero output, and three down outputs. Each of the UP and DOWN outputs is tracked by the UP rolling counter and the DOWN rolling counter. At T1 the BBPD outputs the fourth UP output and the UP rolling counter rolls over to 0 and a decimated up pulse is provided to the charge pump integrator which stores a value of 4. After T1, the BBPD continues to output UP, DOWN, and zero outputs until at T2, a fourth DOWN output is received. At T2, the DOWN rolling counter rolls over to zero and a decimated down pulse is provided to the charge pump integrator and the charge pump integrator's stored value is reduced back to zero. The bottom line of the timing diagram depicts how the system maintains a full accounting for every received up and down pulse between the UP and DOWN rolling counters and the charge pump integrator. For example, at TO the cumulative value is at zero (e.g., the UP/DOWN rolling counters and the charge pump integrator are each at zero). At T1, the cumulative value is at 3 since the UP counter has rolled over to zero, the DOWN rolling counter is at 1, and the charge pump integrator is at 4 (e.g., 0-1+4=3). At T2, the cumulative value is at 2 since the UP rolling counter has a value of 2, and the DOWN rolling counter and the charge pump integrator are both at zero (e.g., 2-0+0). Thus, at any given time a running sum of the number of UP minus the number of DOWN signals is maintained.

[0054] FIG. 4 depicts a simulated plot of integrated UP/DOWN signals of a BBPD decimated using several decimation techniques.

[0055] Referring to FIG. 4, in various embodiments, the integrated UP/DOWN output of the BBPD is depicted. The plot includes an ideal undecimated plot 400. In various embodiments, the plot includes a proposed decimated system plot 410, a simple decimate by 4 plot 420, and a majority vote of 4 plot 430. As shown by FIG. 4, the proposed decimated system plot 410 closely tracks the ideal undecimated plot 400, while simple decimate by 4 and majority vote of 4 plots 420, 430 are not nearly as accurate.

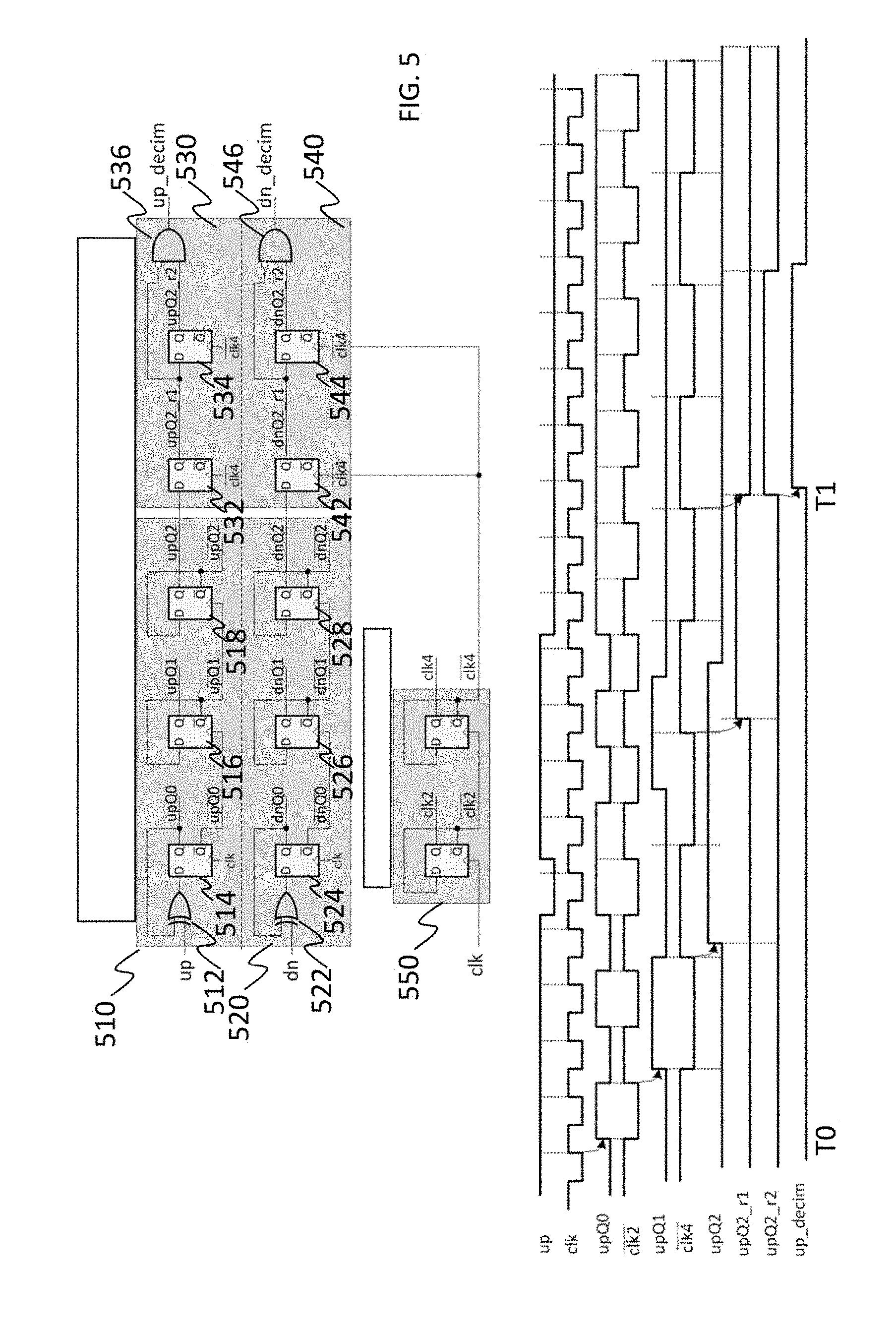

[0056] FIG. 5 depicts an embodiment of UP and DOWN rolling counters according to various embodiments.

[0057] Referring to FIG. 5, the UP and DOWN rolling counters 500 may be implemented using ripple counters. In various embodiments, the use of ripple counters may simplify the timing of the rolling counters and reduce the power consumed by the rolling counters. In the depicted embodiment, the system implements a decimate-by-8 operation, however, in various embodiments, the ripple counters may be implemented as N-bit ripple counters. FIG. 5 also includes a corresponding timing diagram showing the operation of the ripple counters with respect to UP signals from the BBPD. It should be understood that the system would operate similarly with respect with DOWN signals from the BBPD.

[0058] In various embodiments, the UP ripple counter 510 may include an exclusive OR gate 512 at an UP input and 3 flip-flops 514, 516, 518 (e.g, for counting up to 3 bits to decimate by 8). Similarly, the DOWN ripple counter 520 includes an exclusive OR gate 522 at a DOWN input and 3 flip-flops 524, 526, 528. The outputs of the UP and DOWN ripple counters 510, 520 are each connected to falling edge detectors 530, 540 which are configured to provide the decimated UP and DOWN signals when the ripple counters 510, 520 roll over to zero (e.g., after 8 UP or DOWN signals from the BBPD). In various embodiments, the falling edge detectors 530, 540 are provided with a decimated clock produced by a ripple counter clock 550. The ripple counter clock may be configured to output a clock based on the input clock that is operating a lower frequency. For example, as shown by the timing diagram, clk4 operates at one fourth the frequency of the input clock clk. The slower clock allows for the flip-flops in the falling edge detectors to not update their states as quickly.

[0059] In various embodiments, the UP falling edge detector 530 includes two flip-flops 532, 534 and an AND gate 536 with an inverter connected to the output of the first flip-flop 532 and a second output connected to the second flip flop 534. In various embodiments, the DOWN falling edge detector 540 also includes two flip-flops 542, 544 and an AND gate 546 with an inverter connected to the output of the first flip-flop 542 and a second output connected to the second flip flop 544. Falling edge detectors 530, 540 output a decimated UP or decimated DOWN signal each time the ripple counters roll over. For example, referring to the timing diagram at TO, the UP ripple counter 510 begins counting the UP signals (e.g., by incrementing its state) from the BBPD. After 8 UPs (e.g., at T1) have been received at the UP ripple counter 510, the UP falling edge detector 530 detects the ripple counter 530 rolling over and decimated UP signal is output.

[0060] FIG. 6 depicts a dual data rate (DDR) interface in a first rolling counter stage according to various embodiments.

[0061] Referring to FIG. 6, in various embodiments, the UP and DOWN ripple counters may be modified to accept DDR UPs and DOWNs. For example, a DDR BBPD may include four outputs, UP_odd, UP_even, DOWN_odd, and DOWN_even. In various embodiments, the UP and DOWN ripple counters (e.g., the UP and DOWN ripple counters of FIG. 5) may be configured with UP_odd, UP_even, DOWN_odd, and DOWN_even inputs. For example, the first counting stage (e.g., exclusive OR gates 512, 522 and flip flops 514, 524) may be replaced by two first counting stages that each include an exclusive OR 610, 612, and a flip flop 620, 622 and operate on complementary clocks. The exclusive OR and flip flop operate in the same manner as above, and the output of each of the flip flops 620, 622 are provided to an exclusive OR 630 that merges the counting from both of the initial counting stages.

[0062] In the preceding description, for the purposes of explanation, numerous specific details are set forth to provide a thorough understanding of various embodiments. It is apparent, however, that various embodiments may be practiced without these specific details or with one or more equivalent arrangements. In other instances, well-known structures and devices are shown in block diagram form in order to avoid unnecessarily obscuring various embodiments.

[0063] It will be understood that when an element, layer, region, or component is referred to as being "on," "connected to," or "coupled to" another element, layer, region, or component, it can be directly on, connected to, or coupled to the other element, layer, region, or component, or one or more intervening elements, layers, regions, or components may be present. However, "directly connected/directly coupled" refers to one component directly connecting or coupling another component without an intermediate component. Meanwhile, other expressions describing relationships between components such as "between," "immediately between" or "adjacent to" and "directly adjacent to" may be construed similarly. In addition, it will also be understood that when an element or layer is referred to as being "between" two elements or layers, it can be the only element or layer between the two elements or layers, or one or more intervening elements or layers may also be present.

[0064] The terminology used herein is for the purpose of describing particular embodiments only and is not intended to be limiting of the present disclosure. As used herein, the singular forms "a" and "an" are intended to include the plural forms as well, unless the context clearly indicates otherwise. It will be further understood that the terms "comprises," "comprising," "have," "having," "includes," and "including," when used in this specification, specify the presence of the stated features, integers, steps, operations, elements, and/or components, but do not preclude the presence or addition of one or more other features, integers, steps, operations, elements, components, and/or groups thereof. As used herein, the term "and/or" includes any and all combinations of one or more of the associated listed items.

[0065] As used herein, the term "substantially," "about," "approximately," and similar terms are used as terms of approximation and not as terms of degree, and are intended to account for the inherent deviations in measured or calculated values that would be recognized by those of ordinary skill in the art. "About" or "approximately," as used herein, is inclusive of the stated value and means within an acceptable range of deviation for the particular value as determined by one of ordinary skill in the art, considering the measurement in question and the error associated with measurement of the particular quantity (i.e., the limitations of the measurement system). For example, "about" may mean within one or more standard deviations, or within .+-.30%, 20%, 10%, 5% of the stated value. Further, the use of "may" when describing embodiments of the present disclosure refers to "one or more embodiments of the present disclosure." As used herein, the terms "use," "using," and "used" may be considered synonymous with the terms "utilize," "utilizing," and "utilized," respectively. Also, the term "exemplary" is intended to refer to an example or illustration.

[0066] When a certain embodiment may be implemented differently, a specific process order may be performed differently from the described order. For example, two consecutively described processes may be performed substantially at the same time or performed in an order opposite to the described order.

[0067] Various embodiments are described herein with reference to sectional illustrations that are schematic illustrations of embodiments and/or intermediate structures. As such, variations from the shapes of the illustrations as a result, for example, of manufacturing techniques and/or tolerances, are to be expected. Further, specific structural or functional descriptions disclosed herein are merely illustrative for the purpose of describing embodiments according to the concept of the present disclosure. Thus, embodiments disclosed herein should not be construed as limited to the particular illustrated shapes of regions, but are to include deviations in shapes that result from, for instance, manufacturing. For example, an implanted region illustrated as a rectangle will, typically, have rounded or curved features and/or a gradient of implant concentration at its edges rather than a binary change from implanted to non-implanted region. Likewise, a buried region formed by implantation may result in some implantation in the region between the buried region and the surface through which the implantation takes place. Thus, the regions illustrated in the drawings are schematic in nature and their shapes are not intended to illustrate the actual shape of a region of a device and are not intended to be limiting.

[0068] The electronic or electric devices and/or any other relevant devices or components according to embodiments of the present disclosure described herein may be implemented utilizing any suitable hardware, firmware (e.g. an application-specific integrated circuit), software, or a combination of software, firmware, and hardware. For example, the various components of these devices may be formed on one integrated circuit (IC) chip or on separate IC chips. Further, the various components of these devices may be implemented on a flexible printed circuit film, a tape carrier package (TCP), a printed circuit board (PCB), or formed on one substrate. Further, the various components of these devices may be a process or thread, running on one or more processors, in one or more computing devices, executing computer program instructions and interacting with other system components for performing the various functionalities described herein. The computer program instructions are stored in a memory which may be implemented in a computing device using a standard memory device, such as, for example, a random access memory (RAM). The computer program instructions may also be stored in other non-transitory computer readable media such as, for example, a CD-ROM, flash drive, or the like. Also, a person of skill in the art should recognize that the functionality of various computing devices may be combined or integrated into a single computing device, or the functionality of a particular computing device may be distributed across one or more other computing devices without departing from the spirit and scope of the exemplary embodiments of the present disclosure.

[0069] Unless otherwise defined, all terms (including technical and scientific terms) used herein have the same meaning as commonly understood by one of ordinary skill in the art to which the present disclosure belongs. It will be further understood that terms, such as those defined in commonly used dictionaries, should be interpreted as having a meaning that is consistent with their meaning in the context of the relevant art and/or the present specification, and should not be interpreted in an idealized or overly formal sense, unless expressly so defined herein.

[0070] The foregoing is illustrative of example embodiments, and is not to be construed as limiting thereof. Although a few example embodiments have been described, those skilled in the art will readily appreciate that many modifications are possible in the example embodiments without materially departing from the novel teachings and advantages of example embodiments. Accordingly, all such modifications are intended to be included within the scope of example embodiments as defined in the claims. In the claims, means-plus-function clauses are intended to cover the structures described herein as performing the recited function and not only structural equivalents but also equivalent structures. Therefore, it is to be understood that the foregoing is illustrative of example embodiments and is not to be construed as limited to the specific embodiments disclosed, and that modifications to the disclosed example embodiments, as well as other example embodiments, are intended to be included within the scope of the appended claims. The inventive concept is defined by the following claims, with equivalents of the claims to be included therein.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.