High-speed Superjunction Lateral Insulated Gate Bipolar Transistor

LIN; Zhi ; et al.

U.S. patent application number 16/264654 was filed with the patent office on 2019-08-15 for high-speed superjunction lateral insulated gate bipolar transistor. The applicant listed for this patent is Chongqing University. Invention is credited to Shu HAN, Shengdong HU, Zhi LIN, Fang TANG, Qi YUAN, Jianlin ZHOU, Xichuan ZHOU.

| Application Number | 20190252531 16/264654 |

| Document ID | / |

| Family ID | 63005827 |

| Filed Date | 2019-08-15 |

View All Diagrams

| United States Patent Application | 20190252531 |

| Kind Code | A1 |

| LIN; Zhi ; et al. | August 15, 2019 |

HIGH-SPEED SUPERJUNCTION LATERAL INSULATED GATE BIPOLAR TRANSISTOR

Abstract

The present disclosure relates to a high-speed superjunction lateral insulated gate bipolar transistor, and belongs to the technical field of semiconductor power devices. Fast turn-off can be achieved by replacing the lightly doped substrate of the existing bulk silicon superjunction lateral insulated gate bipolar transistor with heavily doped substrate, breakdown voltage of the device is ensured by reasonably setting the total number of impurities in each drift region of the over junction-sustaining voltage layer, and further application thereof in integrated circuits is realized by providing the semiconductor second substrate region and the semiconductor isolation region. A high speed superjunction laterally insulated gate bipolar transistor according to the present disclosure solves the contradiction between cost of the superjunction laterally insulated gate bipolar transistor and achievement of fast turn-off on a bulk silicon substrate.

| Inventors: | LIN; Zhi; (Chongqing, CN) ; YUAN; Qi; (Chongqing, CN) ; HAN; Shu; (Chongqing, CN) ; HU; Shengdong; (Chongqing, CN) ; ZHOU; Jianlin; (Chongqing, CN) ; TANG; Fang; (Chongqing, CN) ; ZHOU; Xichuan; (Chongqing, CN) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 63005827 | ||||||||||

| Appl. No.: | 16/264654 | ||||||||||

| Filed: | January 31, 2019 |

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 29/1095 20130101; H01L 29/7393 20130101; H01L 29/36 20130101; H01L 29/0821 20130101; H01L 29/7394 20130101; H01L 29/0619 20130101; H01L 29/0834 20130101; H01L 29/0808 20130101; H01L 29/0634 20130101; H01L 29/66325 20130101 |

| International Class: | H01L 29/739 20060101 H01L029/739; H01L 29/06 20060101 H01L029/06; H01L 29/08 20060101 H01L029/08; H01L 29/36 20060101 H01L029/36 |

Foreign Application Data

| Date | Code | Application Number |

|---|---|---|

| Feb 10, 2018 | CN | 201810137194.8 |

Claims

1. A high-speed superjunction lateral insulated gate bipolar transistor, characterized in that a cell structure of the transistor comprises: a semiconductor first substrate region; a voltage-sustaining region, which is located on a surface of the semiconductor first substrate region, and comprises mutually alternating semiconductor first drift regions and semiconductor second drift regions of different conductivity types, the semiconductor first drift region has a conductivity type the same as that of the semiconductor first substrate region, and the semiconductor second drift region has a conductivity type opposite to that of the semiconductor first substrate region, the conductivity type being N type or P type; a semiconductor field stop region having a conductivity type the same as that of the semiconductor first substrate region and located on a surface of the semiconductor first substrate region, wherein at least one semiconductor collector region having a conductivity type opposite to that of the semiconductor first substrate region is provided in the semiconductor field stop region, and a portion of a surface of the semiconductor collector region is covered with a conductor to form a collector of the transistor; a semiconductor body region having a conductivity type opposite to that of the semiconductor first substrate region; a semiconductor emitter region having a conductivity type the same as that of the semiconductor first substrate region and located in the semiconductor body region, a portion of the semiconductor body region and a portion of the semiconductor emitter region being connected by a conductor to form an emitter of the transistor; a gate insulating layer covering a portion of a surface of the semiconductor emitter region, a portion of a surface of the semiconductor body region, and a portion of a surface of the voltage-sustaining region, wherein a semiconductor polysilicon gate region covering a surface of the gate insulating layer and a conductor covering the semiconductor polysilicon gate region form a gate electrode of the transistor, the gate region has a conductivity type the same as that of the semiconductor first substrate region; and a portion of the semiconductor emitter region, a portion of the semiconductor body region, the gate insulating layer, the semiconductor polysilicon gate region, the gate electrode and a portion of the voltage-sustaining region form a gate structure of the transistor; wherein the semiconductor first drift region and the semiconductor second drift region are in contact with each other and contact surfaces are perpendicular to the semiconductor first substrate region and the semiconductor field stop region; the voltage-sustaining region and the semiconductor field stop region are in contact with each other and a contact surface is perpendicular to the semiconductor first substrate region.

2. The high-speed superjunction lateral insulated gate bipolar transistor of claim 1 wherein: the semiconductor field stop region is in contact with the semiconductor collector region through a semiconductor buffer region having a conductivity type the same as that of the semiconductor first substrate region, wherein the semiconductor buffer region is located in the semiconductor field stop region, and the semiconductor collector region is located in the semiconductor buffer region.

3. The high-speed superjunction lateral insulated gate bipolar transistor of claim 1 wherein: the semiconductor field stop region is in contact with the semiconductor collector region through a semiconductor auxiliary region having a conductivity type opposite to that of the semiconductor first substrate region, wherein a contact surface is perpendicular to the semiconductor first substrate region, the semiconductor collector region is located in the semiconductor auxiliary region, and the semiconductor auxiliary region adopts an impurity concentration distribution the same as that of the semiconductor second drift region.

4. The high-speed superjunction lateral insulated gate bipolar transistor of claim 1 wherein: the cell structure further comprises a second substrate region located on a bottom surface of the semiconductor first substrate region and having a doping concentration lower than that of the semiconductor first substrate region.

5. The high-speed superjunction lateral insulated gate bipolar transistor of claim 4 wherein: the semiconductor field stop region is further in contact with the semiconductor collector region by a semiconductor buffer region having a conductivity type the same as the semiconductor first substrate region, wherein the semiconductor buffer region is located in the semiconductor field stop region, and the semiconductor collector region is located in the semiconductor buffer region.

6. The high-speed superjunction lateral insulated gate bipolar transistor of claim 4 wherein: the semiconductor field stop region is further in contact with the semiconductor collector region through a semiconductor auxiliary region having a conductivity type opposite to that of the semiconductor first substrate region, wherein a contact surface is perpendicular to the semiconductor first substrate region, the semiconductor collector region is located in the semiconductor auxiliary region, and the semiconductor auxiliary region adopts an impurity concentration distribution the same as that of the semiconductor second drift region.

7. The high-speed superjunction lateral insulated gate bipolar transistor of claim 4 wherein: the semiconductor field stop region is provided with at least one semiconductor first isolation region having a conductivity type the same as that of the semiconductor first substrate region, the semiconductor first isolation region and the semiconductor first substrate region are in contact with each other; a contact surface of the semiconductor field stop region and the semiconductor first isolation region is perpendicular to the semiconductor first substrate region.

8. The high-speed superjunction lateral insulated gate bipolar transistor of claim 7 wherein: the semiconductor field stop region is further in contact with the semiconductor collector region through a semiconductor buffer region having a conductivity type the same as that of the semiconductor first substrate region, wherein the semiconductor buffer region is located in the semiconductor field stop region, and the semiconductor collector region is located in the semiconductor buffer region.

9. The high-speed superjunction lateral insulated gate bipolar transistor of claim 6 wherein: the semiconductor auxiliary region is provided with at least one semiconductor second isolation region having a conductivity type the same as that of the semiconductor first substrate region, the semiconductor second isolation region and the semiconductor first substrate region are in contact with each other; a contact surface of the semiconductor auxiliary region and the semiconductor second isolation region is perpendicular to the semiconductor first substrate region.

10. The high-speed superjunction lateral insulated gate bipolar transistor of claim 1 wherein: the semiconductor first substrate region is a heavily doped region having a doping concentration greater than 10.sup.18 cm.sup.-3.

Description

CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application claims the benefit of priority from Chinese Patent Application No. CN201810137194.8, filed on Feb. 10, 2018. The content of the aforementioned application, including any intervening amendments thereto, is incorporated herein by reference in its entirety.

TECHNICAL FIELD

[0002] The present disclosure belongs to the technical field of semiconductor power devices, and in particular relates to a high-speed superjunction lateral insulated gate bipolar transistor.

BACKGROUND

[0003] In a superjunction lateral insulated gate bipolar transistor (LIGBT), electrons and holes participate in conduction at the same time. These two carriers form conductance modulation, which greatly reduces the specific on-resistance of the device. The chip region occupied by the device is reduced, and the typical structure can be referred to the transistor structure shown in FIG. 1. However, in devices fabricated with bulk silicon-based substrates, carriers can enter the lightly doped substrate to form unbalanced carriers. In this way, it takes a certain time to extract these carriers when the device is turned off, which increases the turn-off time and increases the power consumption.

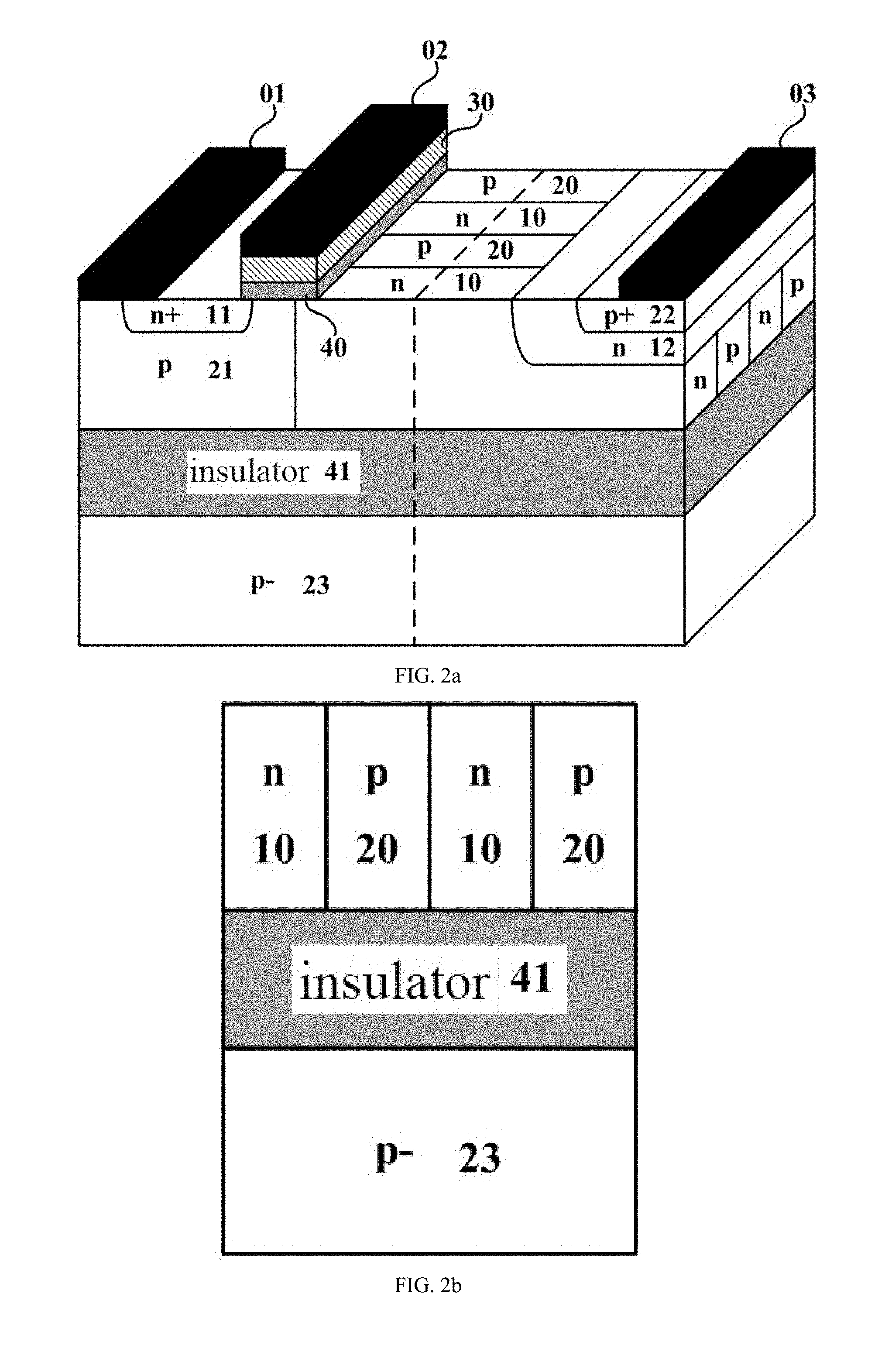

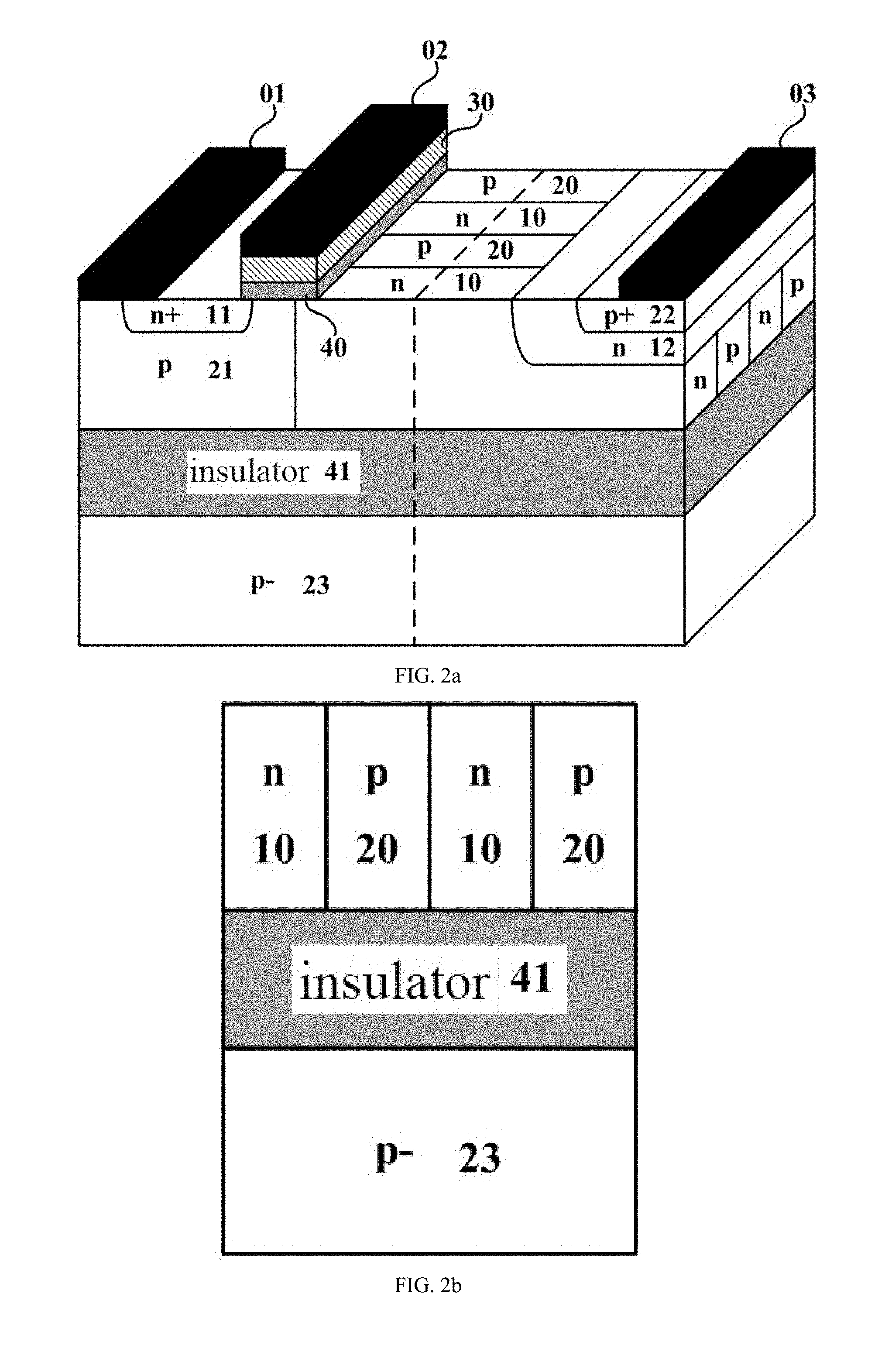

[0004] At present, the most common solution is to use silicon-on-insulator (SOI) substrate instead of a bulk silicon substrate. As shown in FIG. 2, an insulator, which is typically a silica material, is inserted between the superjunction structure portion and the lightly doped substrate. The insulator layer can effectively block carriers from entering the lightly doped substrate, thereby avoiding the extraction of carriers in the lightly doped substrate during turn-off, shortening the turn-off time and reducing the turn-off power consumption. However, this solution has the disadvantages that the SOI substrate process is complicated and the cost is several times that of the bulk silicon material.

[0005] Another solution is to use an insulating substrate instead of a bulk silicon substrate, such as a sapphire substrate. As shown in FIG. 3, a semiconductor superjunction structure is fabricated on an intrinsic sapphire substrate. The intrinsic sapphire substrate is non-conductive and is a good insulator, so that the carriers in the semiconductor superjunction structure do not enter the intrinsic sapphire substrate, thus avoiding the extraction of carriers in the substrate during turn-off. Accordingly, the superjunction LIGBT fabricated on an insulating substrate such as sapphire has a short turn-off time and a low off-power consumption. However, the cost of the sapphire substrate in this solution is higher.

[0006] In summary, in the prior art, an insulator layer is inserted between the superjunction structure portion and the lightly doped substrate or the insulator substrate is directly used instead of the bulk silicon substrate to solve the problem that carriers in the LIGBT device will enter the lightly doped substrate. However, these solutions will lead to the problem of long turn-off time and high power consumption of the device, and cannot effectively cope with complicated process and high cost of the insulating substrate.

SUMMARY

[0007] In view of the defects of the prior art, the object of the present disclosure is to provide a high-speed superjunction lateral insulated gate bipolar transistor, which achieves the purpose of achieving fast turn-off of a superjunction LIGBT on a bulk silicon substrate at low cost.

[0008] In order to achieve the above object, the technical solution of the present disclosure:

[0009] A high-speed superjunction lateral insulated gate bipolar transistor, characterized in that a cell structure of the transistor comprises:

[0010] a semiconductor first substrate region;

[0011] a voltage-sustaining region, which is located on a surface of the semiconductor first substrate region, and comprises mutually alternating semiconductor first drift regions and semiconductor second drift regions of different conductivity types, the semiconductor first drift region has a conductivity type the same as that of the semiconductor first substrate region, and the semiconductor second drift region has a conductivity type opposite to that of the semiconductor first substrate region, the conductivity type being N type or P type;

[0012] a semiconductor field stop region having a conductivity type the same as that of the semiconductor first substrate region and located on a surface of the semiconductor first substrate region, wherein at least one semiconductor collector region having a conductivity type opposite to that of the semiconductor first substrate region is provided in the semiconductor field stop region, and a portion of a surface of the semiconductor collector region is covered with a conductor to form a collector of the transistor;

[0013] a semiconductor body region having a conductivity type opposite to that of the semiconductor first substrate region;

[0014] a semiconductor emitter region having a conductivity type the same as that of the semiconductor first substrate region and located in the semiconductor body region, a portion of the semiconductor body region and a portion of the semiconductor emitter region being connected by a conductor to form an emitter of the transistor;

[0015] a gate insulating layer covering a portion of a surface of the semiconductor emitter region, a portion of a surface of the semiconductor body region, and a portion of a surface of the voltage-sustaining region, wherein a semiconductor polysilicon gate region covering a surface of the gate insulating layer and a conductor covering the semiconductor polysilicon gate region form a gate electrode of the transistor, the gate region has a conductivity type the same as that of the semiconductor first substrate region; and a portion of the semiconductor emitter region, a portion of the semiconductor body region, the gate insulating layer, the semiconductor polysilicon gate region, the gate electrode and a portion of the voltage-sustaining region form a gate structure of the transistor;

[0016] wherein the semiconductor first drift region and the semiconductor second drift region are in contact with each other and contact surfaces are perpendicular to the semiconductor first substrate region and the semiconductor field stop region;

[0017] the voltage-sustaining region and the semiconductor field stop region are in contact with each other and a contact surface is perpendicular to the semiconductor first substrate region.

[0018] Further, the conductivity type is N type or P type.

[0019] Further, the semiconductor material used in the transistor includes, but is not limited to, any one of silicon, gallium arsenide, gallium nitride, or silicon carbide.

[0020] Further, the semiconductor field stop region is in contact with the semiconductor collector region through a semiconductor buffer region having a conductivity type the same as that of the semiconductor first substrate region, wherein the semiconductor buffer region is located in the semiconductor field stop region, and the semiconductor collector region is located in the semiconductor buffer region.

[0021] Further, the semiconductor field stop region is in contact with the semiconductor collector region through a semiconductor auxiliary region having a conductivity type opposite to that of the semiconductor first substrate region, wherein a contact surface is perpendicular to the semiconductor first substrate region, the semiconductor collector region is located in the semiconductor auxiliary region, and the semiconductor auxiliary region adopts an impurity concentration distribution the same as that of the semiconductor second drift region.

[0022] Further, the cell structure further comprises a second substrate region located on a bottom surface of the semiconductor first substrate region and having a doping concentration lower than that of the semiconductor first substrate region.

[0023] Further, the semiconductor field stop region is provided with at least one semiconductor first isolation region having a conductivity type the same as that of the semiconductor first substrate region, the semiconductor first isolation region and the semiconductor first substrate region are in contact with each other; a contact surface of the semiconductor field stop region and the semiconductor first isolation region is perpendicular to the semiconductor first substrate region. Further, the semiconductor field stop region is provided with at least one semiconductor second isolation region having a conductivity type the same as that of the semiconductor first substrate region, the semiconductor second isolation region and the semiconductor first substrate region are in contact with each other; a contact surface of the semiconductor field stop region and the semiconductor second isolation region is perpendicular to the semiconductor first substrate region.

[0024] Further, the gate structure is a planar gate structure or a trench type gate structure.

[0025] Further, the semiconductor first substrate region is a heavily doped region.

[0026] Compared with the prior art, the beneficial effects of the present disclosure are as follows:

[0027] The present disclosure effectively realizes the purpose of constructing a superjunction LIGBT on a bulk silicon substrate at a low cost to achieve fast turn-off. Specifically, this is achieved by making the semiconductor first substrate region a heavily doped region, thereby making the minority carriers injected from the semiconductor collector region are quickly compounded by the Auger effect, avoiding the accumulation of a large number of unbalanced carriers in the substrate and achieving the purpose of fast turn-off. In addition, since the total number of impurities in the semiconductor first drift region in the voltage-sustaining region is smaller than the total number of impurities in the semiconductor second drift region, the equivalent impurity in the voltage-sustaining layer is the second conductivity type. Specifically, along the direction in which the N-column and the P-column are arranged, by dividing the total number of impurities of the semiconductor second drift region minus the total number of impurities of the semiconductor first drift region by the length of the voltage-sustaining layer, the dose of the average impurity obtained is about 10.sup.12 cm.sup.-2; when the device is in the forward blocking state, an electric field is established between these equivalent impurities and the impurities in the semiconductor first substrate region and the impurities in the semiconductor field stop region to obtain a high breakdown voltage.

BRIEF DESCRIPTION OF THE DRAWINGS

[0028] FIG. 1a is a schematic structural view of a conventional superjunction LIGBT;

[0029] FIG. 1b is a schematic cross-sectional view corresponding to the broken line in FIG. 1a;

[0030] FIG. 2a is a schematic structural view of an SOI substrate superjunction LIGBT;

[0031] FIG. 2b is a schematic cross-sectional view corresponding to the broken line in FIG. 2a;

[0032] FIG. 3a is a schematic structural view of a sapphire substrate superjunction LIGBT;

[0033] FIG. 3b is a schematic cross-sectional view corresponding to the broken line in FIG. 3a;

[0034] FIG. 4a is a schematic structural view of a superjunction LIGBT corresponding to Example 1 of the present disclosure;

[0035] FIG. 4b is a schematic cross-sectional view corresponding to the broken line in FIG. 4a;

[0036] FIG. 5a is a schematic structural view of a superjunction LIGBT corresponding to Example 2 of the present disclosure;

[0037] FIG. 5b is a schematic cross-sectional view corresponding to the broken line in FIG. 5a;

[0038] FIG. 6a is a schematic structural view of a superjunction LIGBT corresponding to Example 3 of the present disclosure;

[0039] FIG. 6b is a schematic cross-sectional view corresponding to the broken line in FIG. 6a;

[0040] FIG. 7a is a schematic structural view of a superjunction LIGBT corresponding to Example 4 of the present disclosure;

[0041] FIG. 7b is a schematic cross-sectional view corresponding to the broken line in FIG. 7a;

[0042] FIG. 8a is a schematic structural view of a superjunction LIGBT corresponding to Example 5 of the present disclosure;

[0043] FIG. 8b is a schematic cross-sectional view corresponding to the broken line in FIG. 8a;

[0044] FIG. 9a is a schematic structural view of a superjunction LIGBT corresponding to Example 6 of the present disclosure;

[0045] FIG. 9b is a schematic cross-sectional view corresponding to the broken line in FIG. 9a;

[0046] FIG. 10a is a schematic structural view of a superjunction LIGBT corresponding to Example 7 of the present disclosure;

[0047] FIG. 10b is a schematic cross-sectional view corresponding to the broken line in FIG. 10a;

[0048] FIG. 11a is a schematic structural view of a superjunction LIGBT corresponding to Example 8 of the present disclosure;

[0049] FIG. 11b is a schematic cross-sectional view corresponding to the broken line in FIG. 11a;

[0050] FIG. 12a is a schematic structural view of a superjunction LIGBT corresponding to Example 9 of the present disclosure;

[0051] FIG. 12b is a schematic cross-sectional view corresponding to the broken line in FIG. 12a.

[0052] In the drawings: 01, emitter, 02, gate electrode, 03, collector, 10, semiconductor first drift region, 11, semiconductor emitter region, 12, semiconductor buffer region, 13, semiconductor field stop region, 14, semiconductor first substrate region, 15, semiconductor first isolation region, 16, semiconductor second isolation region, 20, semiconductor second drift region, 21, semiconductor body region, 22, semiconductor collector region, 23, semiconductor second substrate region, 24, semiconductor auxiliary region, 30, polysilicon gate region, 40, gate insulation layer, 41, insulator, 50, sapphire.

DETAILED DESCRIPTION OF EMBODIMENTS

[0053] In order to make the objects, technical solutions and advantages of the present disclosure clearer, the present disclosure will be clearly and completely described in conjunction with the drawings in the embodiments of the present disclosure. It is apparent that the described embodiments are part of the embodiments of the present disclosure, and not all of the embodiments. All other embodiments obtained by a person of ordinary skill in the art based on the embodiments of the present disclosure without creative efforts are within the scope of the present disclosure.

[0054] It is to be understood that the terms "first", "second", and the like in the specification and claims of the present disclosure are used to distinguish similar objects, and are not necessarily used to describe a particular order or sequence. It will be understood that the data so used may be interchanged where appropriate to facilitate the embodiments of the present disclosure described herein. In addition, the terms "comprise" and "include" and variations thereof are intended to cover a non-exclusive inclusion, for example, a process, method, system, product, or device that comprises a series of steps or units is not necessarily limited to those steps or units explicitly listed and may include other steps or units not explicitly listed or inherent to such processes, methods, products or devices.

[0055] Embodiments of the present disclosure provide a cell structure corresponding to a superjunction LIGBT. The cell structure of the superjunction LIGBT includes: a semiconductor first substrate region, the semiconductor first substrate region is a heavily doped region having a doping concentration greater than 10.sup.18 cm.sup.-3; and a voltage-sustaining region, which is located on a surface of the semiconductor first substrate region, and comprises mutually alternating semiconductor first drift regions and semiconductor second drift regions of different conductivity types, the semiconductor first drift region has a conductivity type the same as that of the semiconductor first substrate region, and the semiconductor second drift region has a conductivity type opposite to that of the semiconductor first substrate region, the conductivity type being N type or P type;

[0056] a semiconductor field stop region having a conductivity type the same as that of the semiconductor first substrate region and located on a surface of the semiconductor first substrate region, wherein at least one semiconductor collector region having a conductivity type opposite to that of the semiconductor first substrate region is provided in the semiconductor field stop region, and a portion of a surface of the semiconductor collector region is covered with a conductor to form a collector of the transistor; a semiconductor body region having a conductivity type opposite to that of the semiconductor first substrate region; a semiconductor emitter region having a conductivity type the same as that of the semiconductor first substrate region and located in the semiconductor body region, a portion of the semiconductor body region and a portion of the semiconductor emitter region being connected by a conductor to form an emitter of the transistor; a gate insulating layer covering a portion of a surface of the semiconductor emitter region, a portion of a surface of the semiconductor body region, and a portion of a surface of the voltage-sustaining region, wherein a semiconductor polysilicon gate region covering a surface of the gate insulating layer and a conductor covering the semiconductor polysilicon gate region form a gate electrode of the transistor, the gate region has a conductivity type the same as that of the semiconductor first substrate region; and a portion of the semiconductor emitter region, a portion of the semiconductor body region, the gate insulating layer, the semiconductor polysilicon gate region, the gate electrode and a portion of the voltage-sustaining region form a gate structure of the transistor; wherein the semiconductor first drift region and the semiconductor second drift region are in contact with each other and contact surfaces are perpendicular to the semiconductor first substrate region and the semiconductor field stop region; the voltage-sustaining region and the semiconductor field stop region are in contact with each other and a contact surface is perpendicular to the semiconductor first substrate region.

[0057] In an alternative embodiment, the cell structure further includes a second substrate region located on a bottom surface of the semiconductor first substrate region and having a doping concentration lower than the semiconductor first substrate region, preferably the doping concentration is lower than 10.sup.17 cm.sup.-3; so as to realize its application in integrated circuits.

[0058] In an alternative embodiment, the semiconductor material used in the transistor includes, but is not limited to, any one of silicon, gallium arsenide, gallium nitride, or silicon carbide.

[0059] In an alternative embodiment, the semiconductor field stop region is in contact with the semiconductor collector region through a buffer region having a conductivity type the same as that of the semiconductor first substrate region, wherein the buffer region is located in the semiconductor field stop region, and the semiconductor collector region is located in the semiconductor buffer region.

[0060] In an alternative embodiment, the semiconductor field stop region is in contact with the semiconductor collector region through a semiconductor auxiliary region having a conductivity type opposite to that of the semiconductor first substrate region, wherein a contact surface is perpendicular to the semiconductor first substrate region, the semiconductor collector region is located in the semiconductor auxiliary region, and the semiconductor auxiliary region adopts an impurity concentration distribution the same as that of the semiconductor second drift region. In an alternative embodiment, the semiconductor field stop region is provided with at least one semiconductor first isolation region having a conductivity type the same as that of the semiconductor first substrate region to achieve a better isolation effect, the semiconductor first isolation region and the semiconductor first substrate region are in contact with each other; a contact surface of the semiconductor field stop region and the semiconductor first isolation region is perpendicular to the semiconductor first substrate region. Preferably, the first isolation region of the semiconductor has a doping concentration greater than 10.sup.18 cm.sup.-3.

[0061] In an alternative embodiment, the semiconductor field stop region is provided with at least one semiconductor second isolation region having a conductivity type the same as that of the semiconductor first substrate region, the semiconductor second isolation region and the semiconductor first substrate region are in contact with each other; a contact surface of the semiconductor field stop region and the semiconductor second isolation region is perpendicular to the semiconductor first substrate region. Preferably, the semiconductor auxiliary region and the semiconductor second isolation region have a doping concentration greater than 10.sup.18 cm.sup.-3.

[0062] In the above alternative embodiments, the present disclosure has two important principles: on the one hand, the semiconductor first substrate region is a heavily doped region, thereby making the minority carriers injected from the semiconductor collector region are quickly compounded by the Auger effect, avoiding the accumulation of a large number of unbalanced carriers in the substrate and achieving the purpose of fast turn-off. On the other hand, since the total number of impurities in the semiconductor first drift region in the voltage-sustaining region is smaller than the total number of impurities in the semiconductor second drift region, the equivalent impurity in the voltage-sustaining layer is the second conductivity type. Specifically, along the direction in which the N-column and the P-column are arranged, by dividing the total number of impurities of the semiconductor second drift region minus the total number of impurities of the semiconductor first drift region by the length of the voltage-sustaining layer, the dose of the average impurity obtained is about 10.sup.12 cm.sup.-2; when the device is in the forward blocking state, an electric field is established between these equivalent impurities and the impurities in the semiconductor first substrate region and the impurities in the semiconductor field stop region to obtain a high breakdown voltage.

[0063] The following content is explained by several alternative embodiments:

[0064] In Example 1 shown in FIG. 4a to FIG. 4b, the superjunction LIGBT has a cell structure including: a semiconductor first substrate region 14, which is a heavily doped region and has a doping concentration that is greater than 10.sup.18 cm.sup.-3; a voltage-sustaining region, which is located on a surface of the semiconductor first substrate region, and comprises mutually alternating semiconductor first drift regions 10 and semiconductor second drift regions 20 of different conductivity types, the semiconductor first drift region 10 has a conductivity type the same as that of the semiconductor first substrate region 14, which conductivity type being N type, and the semiconductor second drift region 20 has a conductivity type of P type; a semiconductor field stop region 13 having a conductivity type the same as that of the semiconductor first substrate region 14, that is N type, and located on a surface of the semiconductor first substrate region 14, wherein at least one semiconductor collector region 22 having a conductivity type of P type is provided in the semiconductor field stop region 13, and a portion of a surface of the semiconductor collector region 22 is covered with a conductor to form a collector 3 of the transistor; a semiconductor body region 21 having a conductivity type of P type; a semiconductor emitter region 11 having a conductivity type of N type and is located in the semiconductor body region 21, a portion of the semiconductor body region 21 and a portion of the semiconductor emitter region 11 being connected by a conductor to form an emitter 1 of the transistor; a gate insulating layer 40 covering a portion of a surface of the semiconductor emitter region 11, a portion of a surface of the semiconductor body region 21, and a portion of a surface of the voltage-sustaining region, wherein a semiconductor polysilicon gate region 30 covering a surface of the gate insulating layer 40 and a conductor covering the semiconductor polysilicon gate region 30 form a gate electrode 2 of the transistor, the polysilicon gate region 30 has a conductivity type of N type; and a portion of the semiconductor emitter region 11, a portion of the semiconductor body region 21, the gate insulating layer 40, the semiconductor polysilicon gate region 30, the gate electrode 2 and a portion of the voltage-sustaining region form a gate structure of the transistor, and the gate structure is a planar gate structure or a trench gate structure; wherein the semiconductor first drift region 10 and the semiconductor second drift region 20 are in contact with each other and contact surfaces are perpendicular to the semiconductor first substrate region 14 and the semiconductor field stop region 13; the voltage-sustaining region and the semiconductor field stop region 13 are in contact with each other and a contact surface is perpendicular to the semiconductor first substrate region 14.

[0065] As shown in FIG. 5a to FIG. 5b, the superjunction LIGBT has a cell structure including: a semiconductor first substrate region 14, which is a heavily doped region and has a doping concentration that is greater than 10.sup.18 cm.sup.-3; a voltage-sustaining region, which is located on a surface of the semiconductor first substrate region, and comprises mutually alternating semiconductor first drift regions 10 and semiconductor second drift regions 20 of different conductivity types, the semiconductor first drift region 10 has a conductivity type the same as that of the semiconductor first substrate region 14, which conductivity type being N type, and the semiconductor second drift region 20 has a conductivity type of P type; a semiconductor field stop region 13 having a conductivity type the same as that of the semiconductor first substrate region 14, that is N type, and located on a surface of the semiconductor first substrate region 14, wherein at least one semiconductor collector region 22 having a conductivity type of P type is provided in the semiconductor field stop region 13, and a portion of a surface of the semiconductor collector region 22 is covered with a conductor to form a collector 3 of the transistor; a semiconductor body region 21 having a conductivity type of P type; a semiconductor emitter region 11 having a conductivity type of N type and is located in the semiconductor body region 21, a portion of the semiconductor body region 21 and a portion of the semiconductor emitter region 11 being connected by a conductor to form an emitter 1 of the transistor; a gate insulating layer 40 covering a portion of a surface of the semiconductor emitter region 11, a portion of a surface of the semiconductor body region 21, and a portion of a surface of the voltage-sustaining region, wherein a semiconductor polysilicon gate region 30 covering a surface of the gate insulating layer 40 and a conductor covering the semiconductor polysilicon gate region 30 form a gate electrode 2 of the transistor, the polysilicon gate region 30 has a conductivity type of N type; and a portion of the semiconductor emitter region 11, a portion of the semiconductor body region 21, the gate insulating layer 40, the semiconductor polysilicon gate region 30, the gate electrode 2 and a portion of the voltage-sustaining region form a gate structure of the transistor, and the gate structure is a planar gate structure or a trench gate structure; wherein the semiconductor first drift region 10 and the semiconductor second drift region 20 are in contact with each other and contact surfaces are perpendicular to the semiconductor first substrate region 14 and the semiconductor field stop region 13; the voltage-sustaining region and the semiconductor field stop region 13 are in contact with each other and a contact surface is perpendicular to the semiconductor first substrate region 14; the semiconductor field stop region 13 is in contact with the semiconductor collector region 22 through a semiconductor buffer region 12 having a conductivity type of N type, wherein the semiconductor buffer region 12 is located in the semiconductor field stop region 13, and the semiconductor collector region 22 is located in the semiconductor buffer region 12.

[0066] As shown in FIG. 6a to FIG. 6b, the superjunction LIGBT has a cell structure including: a semiconductor first substrate region 14, which is a heavily doped region and has a doping concentration that is greater than 10.sup.18 cm.sup.-3; a voltage-sustaining region, which is located on a surface of the semiconductor first substrate region, and comprises mutually alternating semiconductor first drift regions 10 and semiconductor second drift regions 20 of different conductivity types, the semiconductor first drift region 10 has a conductivity type the same as that of the semiconductor first substrate region 14, which conductivity type being N type, and the semiconductor second drift region 20 has a conductivity type of P type; a semiconductor field stop region 13 having a conductivity type the same as that of the semiconductor first substrate region 14, that is N type, and located on a surface of the semiconductor first substrate region 14, wherein at least one semiconductor collector region 22 having a conductivity type of P type is provided in the semiconductor field stop region 13, and a portion of a surface of the semiconductor collector region 22 is covered with a conductor to form a collector 3 of the transistor; a semiconductor body region 21 having a conductivity type of P type; a semiconductor emitter region 11 having a conductivity type of N type and is located in the semiconductor body region 21, a portion of the semiconductor body region 21 and a portion of the semiconductor emitter region 11 being connected by a conductor to form an emitter 1 of the transistor; a gate insulating layer 40 covering a portion of a surface of the semiconductor emitter region 11, a portion of a surface of the semiconductor body region 21, and a portion of a surface of the voltage-sustaining region, wherein a semiconductor polysilicon gate region 30 covering a surface of the gate insulating layer 40 and a conductor covering the semiconductor polysilicon gate region 30 form a gate electrode 2 of the transistor, the polysilicon gate region 30 has a conductivity type of N type; and a portion of the semiconductor emitter region 11, a portion of the semiconductor body region 21, the gate insulating layer 40, the semiconductor polysilicon gate region 30, the gate electrode 2 and a portion of the voltage-sustaining region form a gate structure of the transistor, and the gate structure is a planar gate structure or a trench gate structure; wherein the semiconductor first drift region 10 and the semiconductor second drift region 20 are in contact with each other and contact surfaces are perpendicular to the semiconductor first substrate region 14 and the semiconductor field stop region 13; the voltage-sustaining region and the semiconductor field stop region 13 are in contact with each other and a contact surface is perpendicular to the semiconductor first substrate region 14; the semiconductor field stop region 13 is in contact with the semiconductor collector region 22 through a semiconductor auxiliary region 24 having a conductivity type of P type, wherein a contact surface is perpendicular to the semiconductor first substrate region 14, the semiconductor collector region 22 is located in the semiconductor auxiliary region 24, and the semiconductor auxiliary region 24 adopts an impurity concentration distribution the same as that of the semiconductor second drift region 20.

[0067] As shown in FIG. 7a-FIG. 7b, the superjunction LIGBT has a cell structure including: a semiconductor first substrate region 14, which is a heavily doped region and has a doping concentration that is greater than 10.sup.18 cm.sup.-3; a voltage-sustaining region, which is located on a surface of the semiconductor first substrate region, and comprises mutually alternating semiconductor first drift regions 10 and semiconductor second drift regions 20 of different conductivity types, the semiconductor first drift region 10 has a conductivity type the same as that of the semiconductor first substrate region 14, which conductivity type being N-type, and the semiconductor second drift region 20 has a conductivity type of P-type; a semiconductor field stop region 13 having a conductivity type the same as that of the semiconductor first substrate region 14, that is N-type, and located on a surface of the semiconductor first substrate region 14, wherein at least one semiconductor collector region 22 having a conductivity type of P-type is provided in the semiconductor field stop region 13, and a portion of a surface of the semiconductor collector region 22 is covered with a conductor to form a collector 3 of the transistor; a semiconductor body region 21 having a conductivity type of P-type; a semiconductor emitter region 11 having a conductivity type of N-type and is located in the semiconductor body region 21, a portion of the semiconductor body region 21 and a portion of the semiconductor emitter region 11 being connected by a conductor to form an emitter 1 of the transistor; a gate insulating layer 40 covering a portion of a surface of the semiconductor emitter region 11, a portion of a surface of the semiconductor body region 21, and a portion of a surface of the voltage-sustaining region, wherein a semiconductor polysilicon gate region 30 covering a surface of the gate insulating layer 40 and a conductor covering the semiconductor polysilicon gate region 30 form a gate electrode 2 of the transistor, the polysilicon gate region 30 has a conductivity type of N-type; and a portion of the semiconductor emitter region 11, a portion of the semiconductor body region 21, the gate insulating layer 40, the semiconductor polysilicon gate region 30, the gate electrode 2 and a portion of the voltage-sustaining region form a gate structure of the transistor, and the gate structure is a planar gate structure or a trench gate structure; wherein the semiconductor first drift region 10 and the semiconductor second drift region 20 are in contact with each other and contact surfaces are perpendicular to the semiconductor first substrate region 14 and the semiconductor field stop region 13; the voltage-sustaining region and the semiconductor field stop region 13 are in contact with each other and a contact surface is perpendicular to the semiconductor first substrate region 14; the cell structure further includes a second substrate region 23 located at a bottom surface of the semiconductor first substrate region 14 and having a doping concentration lower than that of the semiconductor first substrate region 14.

[0068] As shown in FIG. 8a to FIG. 8b, the superjunction LIGBT has a cell structure including: a semiconductor first substrate region 14, which is a heavily doped region and has a doping concentration that is greater than 10.sup.18 cm.sup.-3; a voltage-sustaining region, which is located on a surface of the semiconductor first substrate region, and comprises mutually alternating semiconductor first drift regions 10 and semiconductor second drift regions 20 of different conductivity types, the semiconductor first drift region 10 has a conductivity type the same as that of the semiconductor first substrate region 14, which conductivity type being N-type, and the semiconductor second drift region 20 has a conductivity type of P-type; a semiconductor field stop region 13 having a conductivity type the same as that of the semiconductor first substrate region 14, that is N-type, and located on a surface of the semiconductor first substrate region 14, wherein at least one semiconductor collector region 22 having a conductivity type of P-type is provided in the semiconductor field stop region 13, and a portion of a surface of the semiconductor collector region 22 is covered with a conductor to form a collector 3 of the transistor; a semiconductor body region 21 having a conductivity type of P-type; a semiconductor emitter region 11 having a conductivity type of N-type and is located in the semiconductor body region 21, a portion of the semiconductor body region 21 and a portion of the semiconductor emitter region 11 being connected by a conductor to form an emitter 1 of the transistor; a gate insulating layer 40 covering a portion of a surface of the semiconductor emitter region 11, a portion of a surface of the semiconductor body region 21, and a portion of a surface of the voltage-sustaining region, wherein a semiconductor polysilicon gate region 30 covering a surface of the gate insulating layer 40 and a conductor covering the semiconductor polysilicon gate region 30 form a gate electrode 2 of the transistor, the polysilicon gate region 30 has a conductivity type of N-type; and a portion of the semiconductor emitter region 11, a portion of the semiconductor body region 21, the gate insulating layer 40, the semiconductor polysilicon gate region 30, the gate electrode 2 and a portion of the voltage-sustaining region form a gate structure of the transistor, and the gate structure is a planar gate structure or a trench gate structure; wherein the semiconductor first drift region 10 and the semiconductor second drift region 20 are in contact with each other and contact surfaces are perpendicular to the semiconductor first substrate region 14 and the semiconductor field stop region 13; the voltage-sustaining region and the semiconductor field stop region 13 are in contact with each other and a contact surface is perpendicular to the semiconductor first substrate region 14; the semiconductor field stop region 13 is in contact with the semiconductor collector region 22 by a semiconductor buffer region 12 having a conductivity type of N type, wherein the semiconductor buffer region 12 is located in the semiconductor field stop region 13, and the semiconductor collector region 22 is located in the semiconductor buffer region 12; the cell structure further comprises a second substrate region 23 located on a bottom surface of the semiconductor first substrate region 14 and having a doping concentration lower than that of the semiconductor first substrate region 14.

[0069] As shown in FIG. 9a-FIG. 9b, the superjunction LIGBT has a cell structure including: a semiconductor first substrate region 14, which is a heavily doped region and has a doping concentration that is greater than 10.sup.18 cm.sup.-3; a voltage-sustaining region, which is located on a surface of the semiconductor first substrate region, and comprises mutually alternating semiconductor first drift regions 10 and semiconductor second drift regions 20 of different conductivity types, the semiconductor first drift region 10 has a conductivity type the same as that of the semiconductor first substrate region 14, which conductivity type being N type, and the semiconductor second drift region 20 has a conductivity type of P type; a semiconductor field stop region 13 having a conductivity type the same as that of the semiconductor first substrate region 14, that is N type, and located on a surface of the semiconductor first substrate region 14, wherein at least one semiconductor collector region 22 having a conductivity type of P type is provided in the semiconductor field stop region 13, and a portion of a surface of the semiconductor collector region 22 is covered with a conductor to form a collector 3 of the transistor; a semiconductor body region 21 having a conductivity type of P type; a semiconductor emitter region 11 having a conductivity type of N type and is located in the semiconductor body region 21, a portion of the semiconductor body region 21 and a portion of the semiconductor emitter region 11 being connected by a conductor to form an emitter 1 of the transistor; a gate insulating layer 40 covering a portion of a surface of the semiconductor emitter region 11, a portion of a surface of the semiconductor body region 21, and a portion of a surface of the voltage-sustaining region, wherein a semiconductor polysilicon gate region 30 covering a surface of the gate insulating layer 40 and a conductor covering the semiconductor polysilicon gate region 30 form a gate electrode 2 of the transistor, the polysilicon gate region 30 has a conductivity type of N type; and a portion of the semiconductor emitter region 11, a portion of the semiconductor body region 21, the gate insulating layer 40, the semiconductor polysilicon gate region 30, the gate electrode 2 and a portion of the voltage-sustaining region form a gate structure of the transistor, and the gate structure is a planar gate structure or a trench gate structure; wherein the semiconductor first drift region 10 and the semiconductor second drift region 20 are in contact with each other and contact surfaces are perpendicular to the semiconductor first substrate region 14 and the semiconductor field stop region 13; the voltage-sustaining region and the semiconductor field stop region 13 are in contact with each other and a contact surface is perpendicular to the semiconductor first substrate region 14; the semiconductor field stop region 13 is in contact with the semiconductor collector region 22 through a semiconductor auxiliary region 24 having a conductivity type of P type, wherein a contact surface is perpendicular to the semiconductor first substrate region 14, the semiconductor collector region 22 is located in the semiconductor auxiliary region 24, and the semiconductor auxiliary region 24 adopts an impurity concentration distribution the same as that of the semiconductor second drift region 20; the cell structure further comprises a second substrate region 23 located on a bottom surface of the semiconductor first substrate region 14 and having a doping concentration lower than that of the semiconductor first substrate region 14.

[0070] As shown in FIG. 10a to FIG. 10b, the superjunction LIGBT has a cell structure including: a semiconductor first substrate region 14, which is a heavily doped region and has a doping concentration that is greater than 10.sup.18 cm.sup.-3; a voltage-sustaining region, which is located on a surface of the semiconductor first substrate region, and comprises mutually alternating semiconductor first drift regions 10 and semiconductor second drift regions 20 of different conductivity types, the semiconductor first drift region 10 has a conductivity type the same as that of the semiconductor first substrate region 14, which conductivity type being N type, and the semiconductor second drift region 20 has a conductivity type of P type; a semiconductor field stop region 13 having a conductivity type the same as that of the semiconductor first substrate region 14, that is N type, and located on a surface of the semiconductor first substrate region 14, wherein at least one semiconductor collector region 22 having a conductivity type of P type is provided in the semiconductor field stop region 13, and a portion of a surface of the semiconductor collector region 22 is covered with a conductor to form a collector 3 of the transistor; a semiconductor body region 21 having a conductivity type of P type; a semiconductor emitter region 11 having a conductivity type of N type and is located in the semiconductor body region 21, a portion of the semiconductor body region 21 and a portion of the semiconductor emitter region 11 being connected by a conductor to form an emitter 1 of the transistor; a gate insulating layer 40 covering a portion of a surface of the semiconductor emitter region 11, a portion of a surface of the semiconductor body region 21, and a portion of a surface of the voltage-sustaining region, wherein a semiconductor polysilicon gate region 30 covering a surface of the gate insulating layer 40 and a conductor covering the semiconductor polysilicon gate region 30 form a gate electrode 2 of the transistor, the polysilicon gate region 30 has a conductivity type of N type; and a portion of the semiconductor emitter region 11, a portion of the semiconductor body region 21, the gate insulating layer 40, the semiconductor polysilicon gate region 30, the gate electrode 2 and a portion of the voltage-sustaining region form a gate structure of the transistor, and the gate structure is a planar gate structure or a trench gate structure; wherein the semiconductor first drift region 10 and the semiconductor second drift region 20 are in contact with each other and contact surfaces are perpendicular to the semiconductor first substrate region 14 and the semiconductor field stop region 13; the voltage-sustaining region and the semiconductor field stop region 13 are in contact with each other and a contact surface is perpendicular to the semiconductor first substrate region 14; the semiconductor field stop region 13 is provided with at least one semiconductor first isolation region 15 having a conductivity type of N type, the semiconductor first isolation region 15 and the semiconductor first substrate region 14 are in contact with each other; a contact surface of the semiconductor field stop region 13 and the semiconductor first isolation region 15 is perpendicular to the semiconductor first substrate region 14; the cell structure further comprises a second substrate region 23 located on a bottom surface of the semiconductor first substrate region 14 and having a doping concentration lower than that of the semiconductor first substrate region 14.

[0071] As shown in FIG. 11a to FIG. 11b, the superjunction LIGBT has a cell structure including: a semiconductor first substrate region 14, which is a heavily doped region and has a doping concentration that is greater than 10.sup.18 cm.sup.-3; a voltage-sustaining region, which is located on a surface of the semiconductor first substrate region, and comprises mutually alternating semiconductor first drift regions 10 and semiconductor second drift regions 20 of different conductivity types, the semiconductor first drift region 10 has a conductivity type the same as that of the semiconductor first substrate region 14, which conductivity type being N type, and the semiconductor second drift region 20 has a conductivity type of P type; a semiconductor field stop region 13 having a conductivity type the same as that of the semiconductor first substrate region 14, that is N type, and located on a surface of the semiconductor first substrate region 14, wherein at least one semiconductor collector region 22 having a conductivity type of P type is provided in the semiconductor field stop region 13, and a portion of a surface of the semiconductor collector region 22 is covered with a conductor to form a collector 3 of the transistor; a semiconductor body region 21 having a conductivity type of P type; a semiconductor emitter region 11 having a conductivity type of N type and is located in the semiconductor body region 21, a portion of the semiconductor body region 21 and a portion of the semiconductor emitter region 11 being connected by a conductor to form an emitter 1 of the transistor; a gate insulating layer 40 covering a portion of a surface of the semiconductor emitter region 11, a portion of a surface of the semiconductor body region 21, and a portion of a surface of the voltage-sustaining region, wherein a semiconductor polysilicon gate region 30 covering a surface of the gate insulating layer 40 and a conductor covering the semiconductor polysilicon gate region 30 form a gate electrode 2 of the transistor, the polysilicon gate region 30 has a conductivity type of N type; and a portion of the semiconductor emitter region 11, a portion of the semiconductor body region 21, the gate insulating layer 40, the semiconductor polysilicon gate region 30, the gate electrode 2 and a portion of the voltage-sustaining region form a gate structure of the transistor, and the gate structure is a planar gate structure or a trench gate structure; wherein the semiconductor first drift region 10 and the semiconductor second drift region 20 are in contact with each other and contact surfaces are perpendicular to the semiconductor first substrate region 14 and the semiconductor field stop region 13; the voltage-sustaining region and the semiconductor field stop region 13 are in contact with each other and a contact surface is perpendicular to the semiconductor first substrate region 14; the semiconductor field stop region 13 is in contact with the semiconductor collector region 22 through a semiconductor buffer region 12 having a conductivity type of N type, wherein the semiconductor buffer region 12 is located in the semiconductor field stop region 13, and the semiconductor collector region 22 is located in the semiconductor buffer region 12; the semiconductor field stop region 13 is provided with at least one semiconductor first isolation region 15 having a conductivity type of N type, the semiconductor first isolation region 15 and the semiconductor first substrate region 14 are in contact with each other; a contact surface of the semiconductor field stop region 13 and the semiconductor first isolation region 15 is perpendicular to the semiconductor first substrate region 14; the cell structure further comprises a second substrate region 23 located on a bottom surface of the semiconductor first substrate region 14 and having a doping concentration lower than that of the semiconductor first substrate region 14.

[0072] As shown in FIG. 12a to FIG. 12b, the superjunction LIGBT has a cell structure including: a semiconductor first substrate region 14, which is a heavily doped region and has a doping concentration that is greater than 10.sup.18 cm.sup.-3; a voltage-sustaining region, which is located on a surface of the semiconductor first substrate region, and comprises mutually alternating semiconductor first drift regions 10 and semiconductor second drift regions 20 of different conductivity types, the semiconductor first drift region 10 has a conductivity type the same as that of the semiconductor first substrate region 14, which conductivity type being N type, and the semiconductor second drift region 20 has a conductivity type of P type; a semiconductor field stop region 13 having a conductivity type the same as that of the semiconductor first substrate region 14, that is N type, and located on a surface of the semiconductor first substrate region 14, wherein at least one semiconductor collector region 22 having a conductivity type of P type is provided in the semiconductor field stop region 13, and a portion of a surface of the semiconductor collector region 22 is covered with a conductor to form a collector 3 of the transistor; a semiconductor body region 21 having a conductivity type of P type; a semiconductor emitter region 11 having a conductivity type of N type and is located in the semiconductor body region 21, a portion of the semiconductor body region 21 and a portion of the semiconductor emitter region 11 being connected by a conductor to form an emitter 1 of the transistor; a gate insulating layer 40 covering a portion of a surface of the semiconductor emitter region 11, a portion of a surface of the semiconductor body region 21, and a portion of a surface of the voltage-sustaining region, wherein a semiconductor polysilicon gate region 30 covering a surface of the gate insulating layer 40 and a conductor covering the semiconductor polysilicon gate region 30 form a gate electrode 2 of the transistor, the polysilicon gate region 30 has a conductivity type of N type; and a portion of the semiconductor emitter region 11, a portion of the semiconductor body region 21, the gate insulating layer 40, the semiconductor polysilicon gate region 30, the gate electrode 2 and a portion of the voltage-sustaining region form a gate structure of the transistor, and the gate structure is a planar gate structure or a trench gate structure; wherein the semiconductor first drift region 10 and the semiconductor second drift region 20 are in contact with each other and contact surfaces are perpendicular to the semiconductor first substrate region 14 and the semiconductor field stop region 13; the voltage-sustaining region and the semiconductor field stop region 13 are in contact with each other and a contact surface is perpendicular to the semiconductor first substrate region 14; the semiconductor field stop region 13 is in contact with the semiconductor collector region 22 through a semiconductor auxiliary region 24 having a conductivity type of P type, wherein a contact surface is perpendicular to the semiconductor first substrate region 14, the semiconductor collector region 22 is located in the semiconductor auxiliary region 24, and the semiconductor auxiliary region 24 adopts an impurity concentration distribution the same as that of the semiconductor second drift region 20; the semiconductor auxiliary region 24 is provided with at least one semiconductor second isolation region 16 having a conductivity type of N type, the semiconductor second isolation region 16 and the semiconductor first substrate region 14 are in contact with each other; a contact surface of the semiconductor auxiliary region 24 and the semiconductor second isolation region 16 is perpendicular to the semiconductor first substrate region 14; the cell structure further comprises a second substrate region 23 located on a bottom surface of the semiconductor first substrate region 14 and having a doping concentration lower than that of the semiconductor first substrate region 14.

[0073] In addition, since in case that the first conductivity type is P type and the second conductivity type is N type, the structure and principle of the superjunction LIGBT is similar to the case that the first conductivity type is N type, this will not be described herein.

[0074] The above is only a preferred embodiment of the present disclosure, and the scope of the present disclosure is not limited thereto. Any equivalent substitutions and modifications made by one skilled in the art according to the technical solution and its inventive concept of the present disclosure within the technical scope disclosed by the present disclosure are intended to be included within the scope of the present disclosure.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

D00009

D00010

D00011

D00012

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.