Image Sensors With Deep Silicon Etch And Related Methods

BORTHAKUR; Swarnal ; et al.

U.S. patent application number 15/895668 was filed with the patent office on 2019-08-15 for image sensors with deep silicon etch and related methods. This patent application is currently assigned to SEMICONDUCTOR COMPONENTS INDUSTRIES, LLC. The applicant listed for this patent is SEMICONDUCTOR COMPONENTS INDUSTRIES, LLC. Invention is credited to Swarnal BORTHAKUR, Marc Allen SULFRIDGE.

| Application Number | 20190252333 15/895668 |

| Document ID | / |

| Family ID | 67394090 |

| Filed Date | 2019-08-15 |

| United States Patent Application | 20190252333 |

| Kind Code | A1 |

| BORTHAKUR; Swarnal ; et al. | August 15, 2019 |

IMAGE SENSORS WITH DEEP SILICON ETCH AND RELATED METHODS

Abstract

Implementations of image sensors may include a silicon layer having a first side and a second side opposite the first side, an opening extending into the silicon layer from the first side of the silicon layer toward the second side, a via extending into the silicon layer from the second side of the silicon layer, and a conductive pad within the opening. The conductive pad may be coupled to the via. The opening may include a fill material. At least a portion of the fill material may form a plane that is substantially parallel with the first side of the silicon layer. The conductive pad may be exposed through an opening in the fill material.

| Inventors: | BORTHAKUR; Swarnal; (Boise, ID) ; SULFRIDGE; Marc Allen; (Boise, ID) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Assignee: | SEMICONDUCTOR COMPONENTS

INDUSTRIES, LLC Phoenix AZ |

||||||||||

| Family ID: | 67394090 | ||||||||||

| Appl. No.: | 15/895668 | ||||||||||

| Filed: | February 13, 2018 |

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 2224/05562 20130101; H01L 2224/0557 20130101; H01L 24/05 20130101; H01L 21/76898 20130101; H01L 2224/05571 20130101; H01L 27/1464 20130101; H01L 2224/05557 20130101; H01L 23/481 20130101; H01L 2224/05567 20130101; H01L 27/14636 20130101 |

| International Class: | H01L 23/00 20060101 H01L023/00; H01L 27/146 20060101 H01L027/146; H01L 23/48 20060101 H01L023/48; H01L 21/768 20060101 H01L021/768 |

Claims

1. An image sensor comprising: a silicon layer comprising a first side and a second side opposite the first side; an opening extending into the silicon layer from the first side of the silicon layer toward the second side; a via extending into the silicon layer from the second side of the silicon layer; and a conductive pad within the opening, the conductive pad coupled to the via; wherein the opening comprises a fill material; wherein at least a portion of the fill material forms a plane that is substantially parallel with a plane formed by the first side of the silicon layer; and wherein the conductive pad is exposed through an opening in the fill material.

2. The image sensor of claim 1, further comprising a dielectric layer between the silicon layer and the via.

3. The image sensor of claim 1, further comprising a dielectric layer between the fill material and the silicon layer.

4. The image sensor of claim 1, further comprising a high dielectric constant dielectric layer between the fill material and the silicon layer.

5. The image sensor of claim 1, further comprising a second via extending into the silicon layer from the second side of the via, the second via coupled to the conductive pad.

6. The image sensor of claim 1, wherein the silicon layer is 6 micrometers thick and the opening is 2.5 micrometers deep.

7. The image sensor of claim 1, wherein the via comprises copper.

8. (canceled)

9. An image sensor comprising: a silicon layer comprising a first side and a second side opposite the first side; a first opening extending through the silicon layer; a second opening extending into the silicon layer from the first side of the silicon layer; a via extending into the silicon layer from the second side of the silicon layer; and a conductive pad within the second opening, the conductive pad coupled to the via; wherein the opening comprises a fill material; wherein at least a portion of the fill material forms a plane that is substantially parallel with a plane formed by the first side of the silicon layer; and wherein the conductive pad is exposed through an opening in the fill material.

10. (canceled)

11. The image sensor of claim 10, wherein the first opening further comprises a first portion wider than a second portion.

12. The image sensor of claim 9, wherein the silicon layer is 6 micrometers thick and the opening is 2.5 micrometers deep.

13. The image sensor of claim 9, further comprising a dielectric layer between the silicon layer and the via.

14. The image sensor of claim 9, further comprising a dielectric layer between the fill material and the silicon layer.

15. The image sensor of claim 9, further comprising a high dielectric constant dielectric layer between the fill material and the silicon layer.

16. A method for forming a conductive pad in an image sensor, the method comprising: etching an opening into a second side of a silicon layer; forming a via within the opening in the second side of the silicon layer; etching an opening into a first side of a silicon layer; forming a dielectric layer over the first side of the silicon layer; etching through the dielectric layer to expose the via; forming a conductive pad within the opening in the first side of the silicon layer, the conductive pad coupled to the via; filling the opening in the first side of the silicon layer with a fill material; planarizing the fill material to form a plane substantially parallel with a planed formed by the first side of the silicon layer; and etching an opening through the fill material to expose the conductive pad.

17. (canceled)

18. (canceled)

19. The method of claim 16, further comprising forming a dielectric layer between the via and the silicon layer.

20. The method of claim 16, wherein the silicon layer is 6 micrometers thick and the opening is 2.5 micrometers deep.

Description

BACKGROUND

1. Technical Field

[0001] Aspects of this document relate generally image sensor semiconductor packages (referred to herein as "image sensors"). More specific implementations involve the conductive pad region of backside illumination (BSI) image sensors.

2. Background

[0002] Image sensors convey information related to an image by communicating signals in response to incident electromagnetic radiation. Image sensors are used in a variety of devices including smart phones, digital cameras, night vision devices, medical imagers, and many others. BSI image sensors may be used to improve the light receiving efficiency of the image sensor, particularly for specific light wavelengths.

SUMMARY

[0003] Implementations of image sensors may include a silicon layer having a first side and a second side opposite the first side, an opening extending into the silicon layer from the first side of the silicon layer toward the second side, a via extending into the silicon layer from the second side of the silicon layer, and a conductive pad within the opening. The conductive pad may be coupled to the via. The opening may include a fill material. At least a portion of the fill material may form a plane that is substantially parallel with the first side of the silicon layer. The conductive pad may be exposed through an opening in the fill material.

[0004] Implementations of image sensors may include one, all, or any of the following:

[0005] A dielectric layer may be included between the silicon layer and the via.

[0006] A dielectric layer may be included between the fill material and the silicon layer.

[0007] A high dielectric constant dielectric layer may be included between the fill material and the silicon layer.

[0008] A second via may be included that extends into the silicon layer from the second side of the via, the second via electrically coupled to the conductive pad.

[0009] A perimeter etch may be included through the silicon layer.

[0010] The silicon layer may be substantially 6 micrometers thick and the opening may be substantially 2.5 micrometers deep.

[0011] The via may include copper.

[0012] Implementations of image sensors may include a silicon layer having a first side and a second side opposite the first side, a first opening extending through the silicon layer, a second opening extending into the silicon layer from the first side of the silicon layer, a via extending into the silicon layer from the second side of the silicon layer, and a conductive pad within the second opening. The conductive pad may be coupled to the via. The opening may include a fill material. At least a portion of the fill material may form a plane that is substantially parallel with the first side of the silicon layer. The conductive pad may be exposed through an opening in the fill material.

[0013] Implementations of image sensors may include one, all, or any of the following:

[0014] A dielectric layer may be included between the silicon layer and the via.

[0015] A dielectric layer may be included between the fill material and the silicon layer.

[0016] A high dielectric constant dielectric layer may be included between the fill material and the silicon layer.

[0017] The first opening may extend around a perimeter of the conductive pad.

[0018] The first opening may further include a first portion wider than a second portion.

[0019] The silicon layer may be substantially 6 micrometers thick and the opening may be substantially 2.5 micrometers deep.

[0020] Implementations of methods for forming conductive pad regions of image sensors may include etching an opening into a second side of a silicon layer, forming a via within the opening in the second side of the silicon layer, etching an opening into a first side of a silicon layer, forming a dielectric layer over the first side of the silicon layer, etching through the dielectric layer to expose the via, and forming a conductive pad within the opening in the first side of the silicon layer. The conductive pad may be coupled to the via. Implementations of methods for forming conductive pad regions of image sensors may also include filling the opening in the first side of the silicon layer with a fill material, planarizing the fill material to form a plane substantially parallel with the first side of the silicon layer, and etching an opening through the fill material to expose the conductive pad.

[0021] Implementations of methods for forming conductive pad regions of image sensors may include one, all, or any of the following:

[0022] The method may include forming a perimeter opening entirely through the silicon layer.

[0023] The method may include forming a dielectric layer between the via and the silicon layer.

[0024] The perimeter opening may be stepped.

[0025] The silicon layer may be substantially 6 micrometers thick and the opening may be substantially 2.5 micrometers deep.

[0026] The foregoing and other aspects, features, and advantages will be apparent to those artisans of ordinary skill in the art from the DESCRIPTION and DRAWINGS, and from the CLAIMS.

BRIEF DESCRIPTION OF THE DRAWINGS

[0027] Implementations will hereinafter be described in conjunction with the appended drawings, where like designations denote like elements, and:

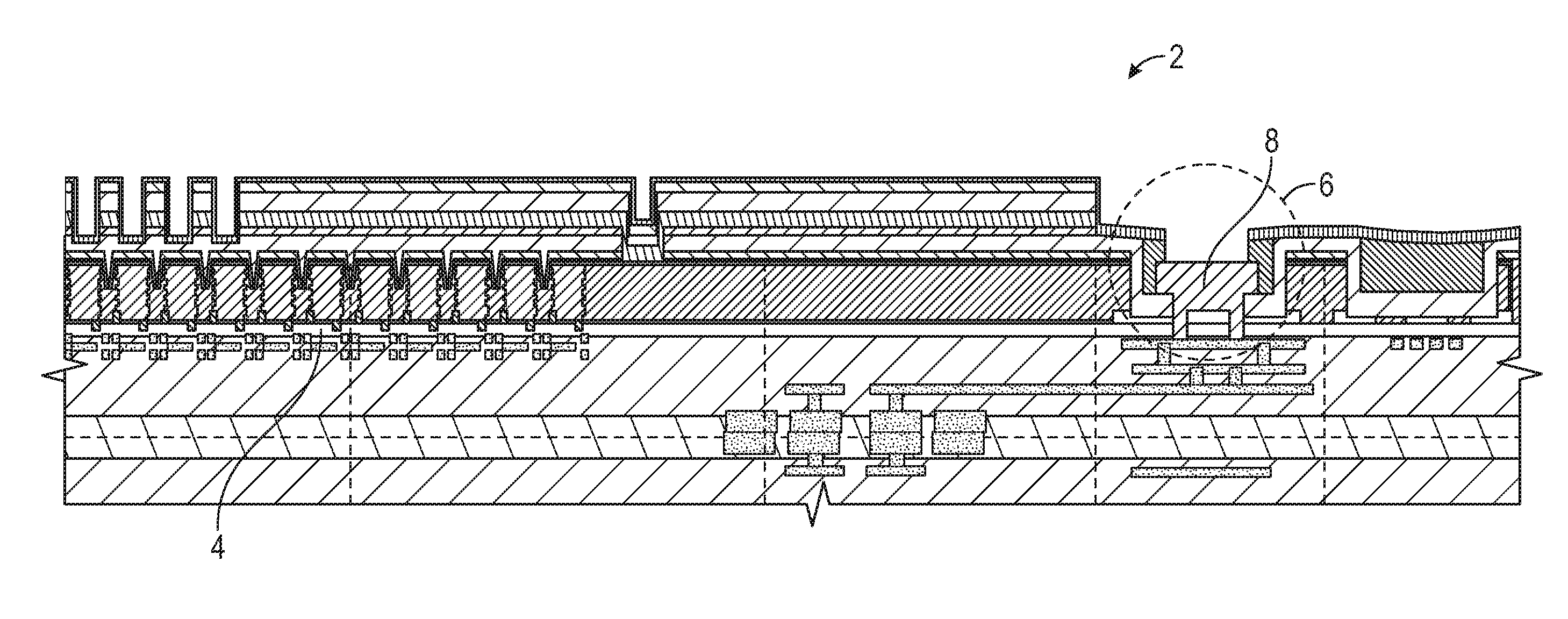

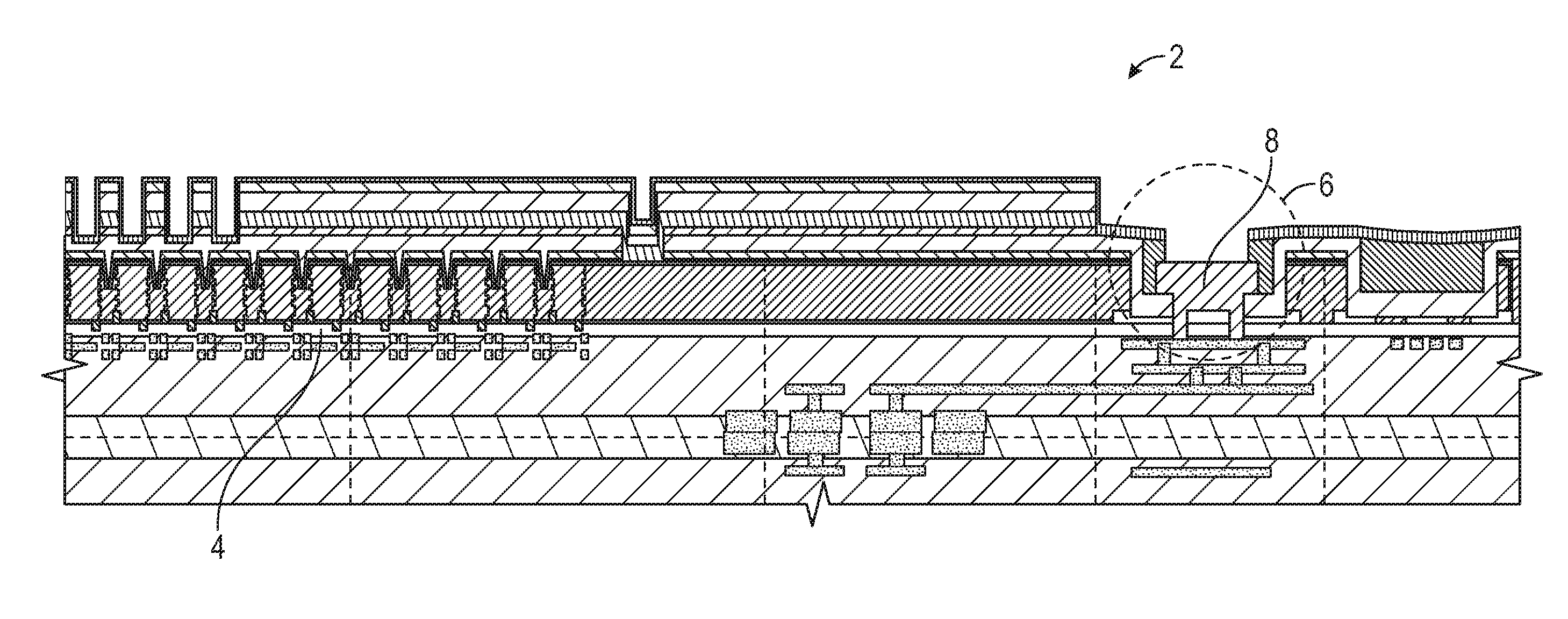

[0028] FIG. 1 is a cross-section side view of a portion of an image sensor;

[0029] FIG. 2A is a magnified cross-section side view of the conductive pad region of an image sensor;

[0030] FIG. 2B is a top view of FIG. 2A.

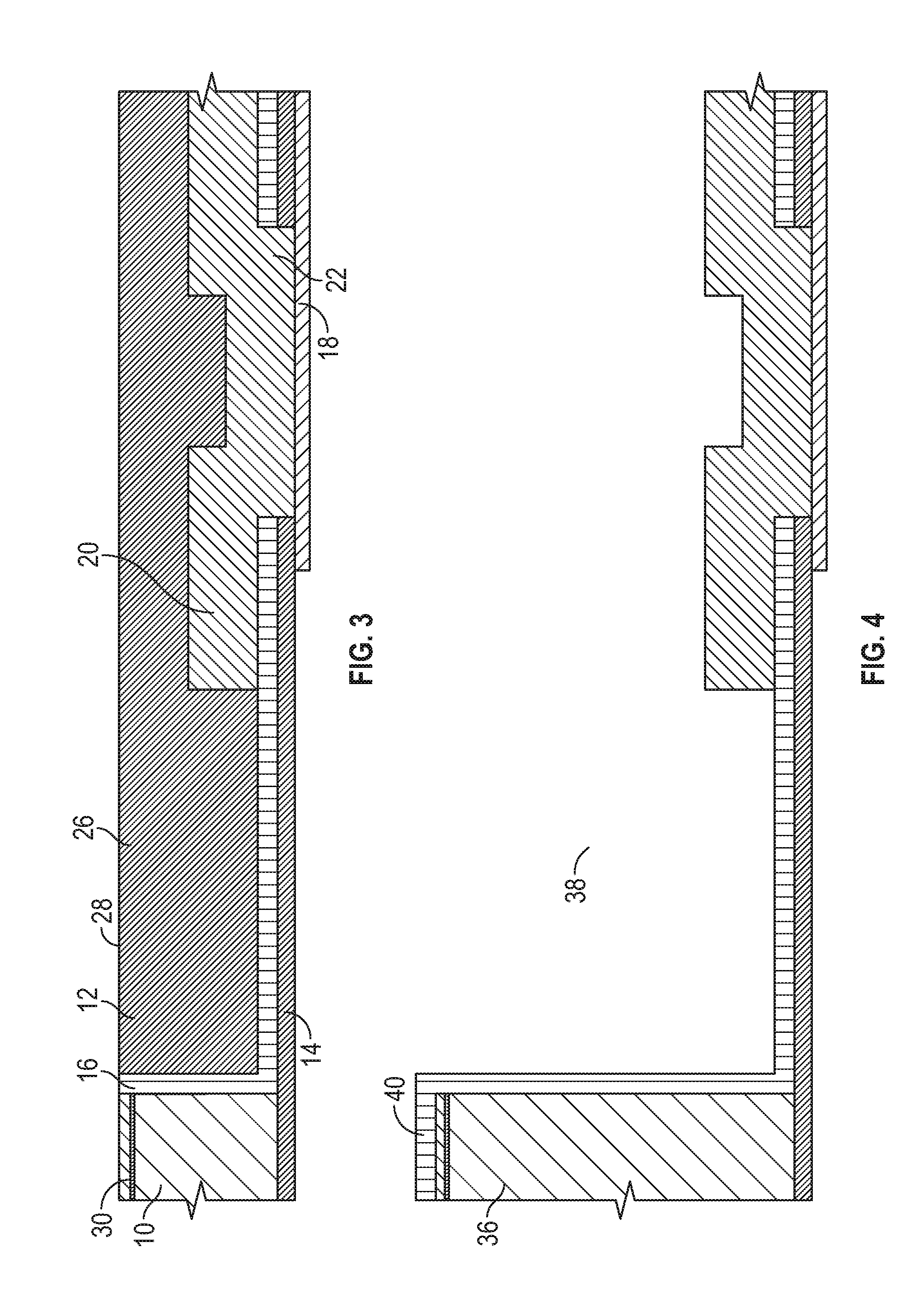

[0031] FIG. 3 is a cross-section side view of a portion of a conductive pad region of the image sensor of FIG. 2A;

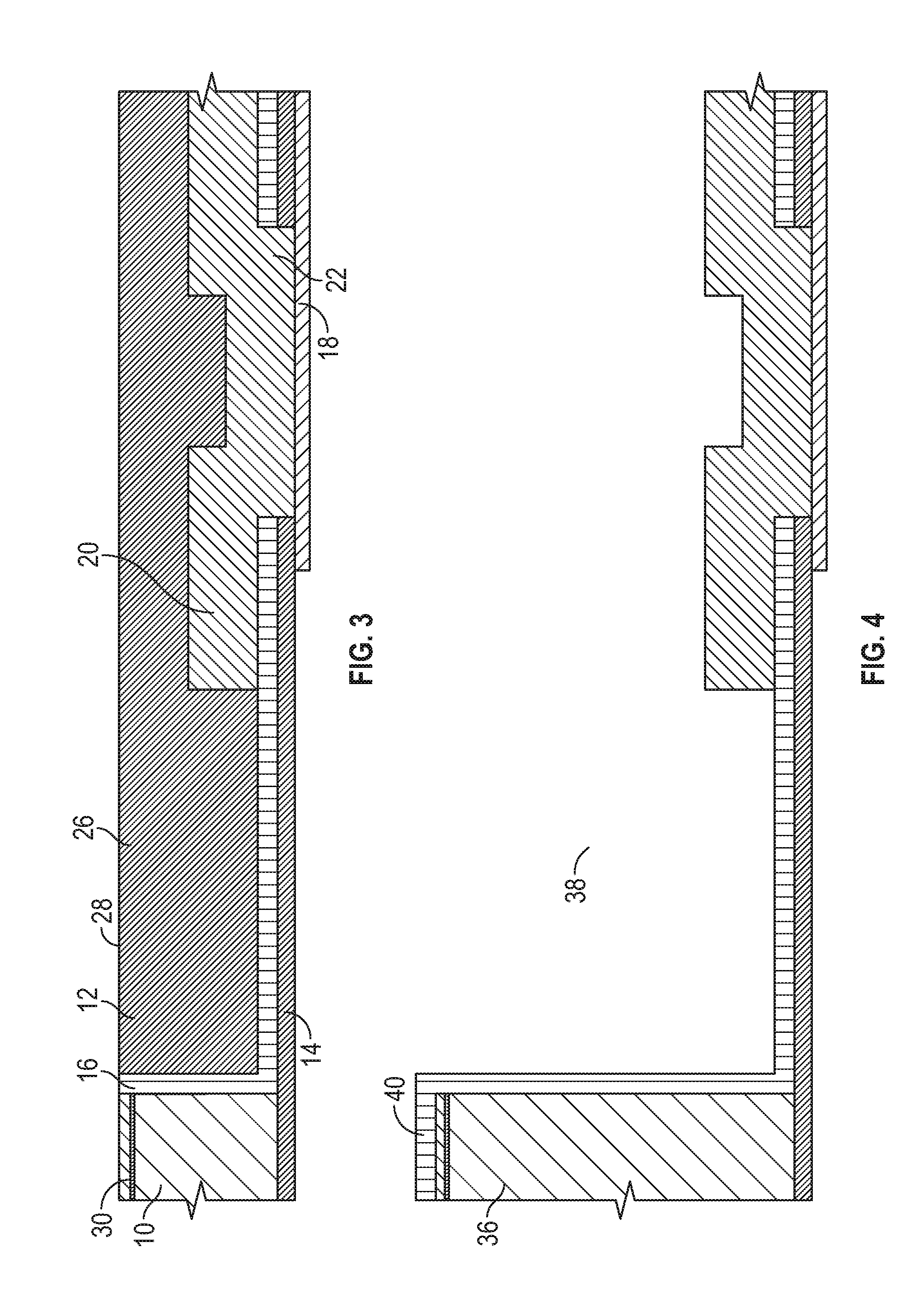

[0032] FIG. 4 is a cross-section side view of a portion of a conductive pad region of an image sensor with a deep silicon etch without a fill material;

[0033] FIG. 5 is a cross-section side view of a portion of an implementation of a conductive pad region of an image sensor with a deep silicon etch;

[0034] FIG. 6 is a cross-section side view of a portion of another implementation of a conductive pad region of an image sensor with a deep silicon etch;

[0035] FIG. 7 is a cross-section side view of a portion of an implementation of a conductive pad region of an image sensor with a deep silicon etch and a perimeter etch through the silicon layer;

[0036] FIG. 8 is a cross-section side view of a portion of an implementation of a conductive pad region of an image sensor with a deep silicon etch and a stepped perimeter etch through the silicon layer;

[0037] FIG. 9 is a cross-section side view of an implementation of a portion of an image sensor coupled with other conductive portions of the image sensor;

[0038] FIGS. 10A-10F are bottom and top views illustrating a process flow of the method for forming the image sensor of FIG. 5; and

[0039] FIGS. 11A-11I are cross-section side views illustrating a process flow of the method for forming the image sensor of FIG. 5.

DESCRIPTION

[0040] This disclosure, its aspects and implementations, are not limited to the specific components, assembly procedures or method elements disclosed herein. Many additional components, assembly procedures and/or method elements known in the art consistent with the intended image sensors will become apparent for use with particular implementations from this disclosure. Accordingly, for example, although particular implementations are disclosed, such implementations and implementing components may comprise any shape, size, style, type, model, version, measurement, concentration, material, quantity, method element, step, and/or the like as is known in the art for such image sensors, and implementing components and methods, consistent with the intended operation and methods.

[0041] Referring to FIG. 1, a cross-section side view of a portion of an image sensor is illustrated. While the FIG. 1 illustrates many components of an image sensor 2, such as a pixel array 4, this disclosure is primarily focused on region 6, referred to herein as the conductive pad region as it includes a conductive pad 8 that may be used to either test the image sensor or electrically couple the image sensor to external devices. This conductive pad is typically located on the edge or near the edge of the die or in the scribeline area of the die in various implementations, though in some implementations the conductive pad may be located in the interior of the die. While the components and methods of this document are primarily taught within the context of a BSI image sensor, it is understood that the devices and methods disclosed herein can be applied to image sensors that are not BSI image sensors, and even to semiconductor packages that are not image sensors.

[0042] Referring to FIGS. 2A-2B, magnified cross-section views of a conductive pad region, similar to region 6 of FIG. 1, are illustrated. Specifically, FIG. 2A illustrates a magnified cross-section side view of the conductive pad region of an image sensor. Referring to FIG. 2A, the image sensor may include a silicon layer 10. It is understood that where this disclosure refers to a silicon layer, the silicon layer could be any type of silicon layer including by non-limiting example, an epitaxial silicon layer, silicon on insulator, polysilicon, any combination thereof, or any other silicon-containing substrate material. Further, it is also understood that in various implementations a substrate other than a silicon-containing substrate may be used, such as, by non-limiting example, gallium arsenide, or a metal-containing substrate.

[0043] The image sensor includes an opening 12 within the silicon layer 10. In the implementation illustrated by FIG. 2A, the depth of the opening, as well as the thickness of the semiconductor layer 10, is shallow and may be about 2.5 micrometers (um). In various implementations, the length of the opening 12 may be about 100 um long and about 80 um wide. FIG. 2A is not drawn to scale for the purpose of clearly illustrating the different elements of FIG. 2A, however, region 34 is shown drawn to scale in FIG. 3.

[0044] In various implementations, the image sensor may include a first dielectric layer 14. The first dielectric layer may be an interlayer dielectric (ILD), and in particular implementations, may be SiO.sub.2. In various implementations, the image sensor may also include a second dielectric layer 16 that may be formed over the silicon layer 10 and within the opening 12. The second dielectric layer may be SiO.sub.2 and may act as a sidewall passivation layer as it covers the sidewalls of the opening 12. In various implementations, the second dielectric layer may be about 300 nanometers (nm) thick.

[0045] The image sensor includes a conductive layer 18 that may be within the first dielectric layer 14. In various implementations, the conductive layer 18 may be metallic. In such implementations, the conductive layer may be, by non-limiting example, copper, gold, silver, aluminum, any other metal or metallic alloy, and any combinations thereof. The conductive layer 18 may be coupled to a conductive pad 20. In various implementations, the conductive pad 20 is a bond pad which may be used to couple external devices to the image sensor. In other implementations, the conductive pad 20 may be a test pad used to electrically test the components of the image sensor. In such implementations, the test pad may not be used to couple the image sensor to external devices as would be done with a bond pad. In still other implementations, the conductive pad 20 may be used as both a test pad and a bond pad. In various implementations, and as illustrated by FIG. 2A, the conductive pad 20 may be directly coupled to the conductive layer 18. The conductive pad 20 illustrated in FIG. 2A includes a first portion 22 and a second portion 24 which extend through the first 14 and second 16 dielectric layers and couple to the conductive layer 18. In various implementations, the conductive pad may have only one or more than two portions that extend through the dielectric layers and couple to the conductive layer.

[0046] The opening 12 may include a fill material 26. The fill material may be the same material as or a different material from the dielectric materials disclosed herein but is generally selected of a material that is electrically insulative. As illustrated in FIG. 2A, the surface 28 of the fill material may form a plane substantially parallel with a plane formed by the surface 30 of the silicon layer 10. The fill material 26 may have an opening 32 therein and the conductive pad 20 may be exposed through the opening 32.

[0047] Referring to FIG. 2B, a top view of FIG. 2A is illustrated. Though FIG. 2A and FIG. 2B are not drawn to scale with respect to one another, FIG. 2B illustrates the perimeters of the elements of FIG. 2A, specifically the opening 32 in the fill material 26, the fill material 26, and the dielectric layer 16. Portions 22 and 24 of the conductive pad, though not technically exposed from a top view, are illustrated in FIG. 2B to show the relative position of such elements.

[0048] Referring now to FIG. 3, a cross-section side view of a portion of the conductive pad region of the image sensor of FIG. 2A is illustrated. FIG. 3 illustrates a magnified view of the region 34 of FIG. 2A, however, this region is drawn to scale in FIG. 3. As illustrated by FIG. 3, the image sensor includes the silicon layer 10, the opening 12, the fill material 26, the conductive pad 20, the conductive layer 18, the first dielectric layer 14, and the second dielectric layers 16, all of which are cut off on the right side of FIG. 3 in order to show the conductive pad region to scale. This view of the conductive pad region is used through the remaining figures in order to show what the conductive pad region looks like as drawn to scale. It is understood that the conductive pad region also includes an opening, which is not shown in FIG. 3, such as opening 32 of FIG. 2A, through which the conductive pad is exposed. It is also understood that the conductive pad may include multiple portions of a conductive pad that are coupled to a conductive layer rather than the one portion 22 illustrated in FIG. 3. Further, it is understood that though the left side of the conductive pad region is shown in FIG. 3, the conductive pad region may also include a symmetrical right side of the conductive pad region, as illustrated in FIG. 2A. Lastly, only a portion of the first dielectric layer 14 is illustrated by FIG. 3, though it is understood that the first dielectric layer may extend beyond what is shown in FIG. 3 (for example, the first dielectric layer 14 may encapsulate the conductive layer 18).

[0049] As previously discussed, the silicon layer 10 of FIG. 3 is substantially 2.5 um thick in various implementations. The surface 28 of the fill material 26 is planarized so that it is coplanar with the top of the dielectric material 16, or so that it forms a plane substantially parallel with a plane formed by the surface 30 of the silicon layer. Because the silicon layer is only about 2.5 um thick, it is feasible to include the fill material 26 in the opening 12 and have it planarized.

[0050] Referring to FIG. 4, a cross-section side view of a portion of a conductive pad region of an image sensor with a deep silicon etch without a fill material is illustrated. The image sensor of FIG. 4 is similar to the image sensor of FIG. 3, with the primary difference being that the silicon layer 36 is substantially 6 um thick rather than 2.5 um thick. In various implementations, it is desirable to increase the thickness of the silicon layer for, among other reasons, increasing the longer wavelengths (e.g. red, near-infrared) response of the image sensor. However, if the thickness of the silicon layer 36 is increased and the depth of the opening 38 within the silicon layer 36 is increased, the opening 38 may become too deep to fill with a fill material. As illustrated by FIG. 4, no fill material is included in the opening 38. The lack of fill material, specifically the lack of fill material that is coplanar with a surface of the dielectric layer 40 above the silicon layer, may result in streaks, bands, and framing defects in the image formed in subsequent processing of the image sensor and may ultimately result in poor topography which may increase yield loss by 6-18%.

[0051] Referring to FIG. 5, a cross-section side view of a portion of an implementation of a conductive pad region of an image sensor with a deep silicon etch is illustrated. The image sensor of FIG. 5 may include a silicon layer 42. The silicon layer 42 includes a first side 44 and a second side 46 opposite the first side 44. In various implementations, the silicon layer 42 is about 6 um thick, however, in other implementations the silicon layer may be more or less thick than about 6 um. The image sensor also includes an opening 48 extending into the silicon layer 42 from the first side 44 of the silicon layer toward the second side 46 of the silicon layer. In various implementations, the opening 48 may be about 2.5 um deep, and in various implementations, may be 100 um long and 80 um wide. In other implementations, the opening 48 may be more or less deep than about 2.5 um, may be longer or less long than about 100 um, and may be wider or less wide than about 80 um.

[0052] In various implementations, the image sensor may include a via 50 extending into the silicon layer 42 from the second side 46 of the silicon layer. In various implementations the via extends about 4 um deep into the silicon layer 42 and has a width of about 5 um, however, in other implementations the via 50 may have a width greater or less than about 5 um and may extend deeper or shallower than about 4 um into the silicon layer 42. The via 50 may have a length (extending into the page as illustrated by FIG. 5) that is about 52 um long, however, in other implementations the length may be more or less than about 52 um. The via 50 includes an electrically and/or thermally conductive material and may include, in various implementations, a metallic material. In such implementations, the via may include, by non-limiting example, copper, gold, silver, aluminum, any other metal or metallic alloy, and any combination thereof. In various implementations the via may be the same as or a different material from the material of the conductive layer 52. In various implementations, the image sensor may include only a single via 50 coupling the conductive layer 52 to a conductive pad 54, however, in other implementations, the image sensor may include two or more vias extending into the silicon layer 42 from the second side 46 of the silicon layer, coupling the conductive layer 52 to the conductive pad 54. In such implementations, the two or more vias may be similar to or the same as any via described herein.

[0053] Still referring to FIG. 5, in various implementations the image sensor may include a first dielectric layer 56. The first dielectric layer 56 may be an ILD layer. Though not illustrated by FIG. 5, the first dielectric layer 56 may at least partially encapsulate the conductive layer 52 as is illustrated by FIG. 2A. The first dielectric layer 56 may also separate the material of the via 50 from the silicon layer 42 as illustrated by FIG. 5. In various implementations, the thickness of the dielectric layer at the portion of the dielectric layer that separates the via 50 from the silicon layer 42 may be about 300 nm thick, however, in other implementations it may be more or less thick than about 300 nm. In various implementations, the dielectric layer may be SiO.sub.2, or any other type of dielectric material.

[0054] As illustrated by FIG. 5, the image sensor includes a conductive pad 54 within the opening 48. In various implementations, the conductive pad 54 is coupled directly to the via 50, however, in other implementations there may be other electrically/thermally conductive elements or layers between the via 50 and the conductive pad 54. In implementations where the conductive pad is directly coupled to the via, the conductive pad may extend through the first dielectric layer 56 and a second dielectric layer 66. The conductive pad is formed of a electrically/thermally conductive material, and may be, by non-limiting example, aluminum, gold, copper, titanium, other metals or metallic alloys, other conductive non-metal materials, or any combination thereof. In various implementations, the conductive pad 54 may include an opening 58 therein which may facilitate adhesion of a fill material 60 to the conductive pad 54.

[0055] In various implementations, the image sensor may include a fill material 60 within the opening 48. At least a surface 62 of the fill material may form a plane that is substantially parallel with a plane formed by the first side of the silicon layer 44. Further, the surface 62 of the fill material may be substantially coplanar with a plane formed by the surface of the dielectric layer 64 over the first side 44 of the silicon layer 42. By having the fill material coplanar with the dielectric layer 64, yield loss due to poor topography may be reduced. The fill material may be, by non-limiting example, an epoxy, a resin, SiO.sub.2, or any other type of fill material. Though not illustrated by FIG. 5, the fill material includes an opening therein through which the conductive pad 54 is exposed, similar to the opening 32 of FIG. 2A.

[0056] In various implementations, the image sensor may include a second dielectric layer 66 which extends along the sides of the opening 48 and separates the fill material 60 from the silicon layer 42. In such implementations the second dielectric layer 66 may serve as a sidewall passivation layer for the sidewalls of the opening 48. The second dielectric layer may also separate the conductive pad 54 from the silicon layer 42. In various implementations, the second dielectric layer 66 may be an adhesion layer to facilitate bonding of the conductive pad 54 to the silicon layer 42. In various implementations, the second dielectric layer 66 may be the same as or include similar materials to any other dielectric layer disclosed herein. Further, in various implementations, the second dielectric layer 66 may include the structure of the dielectric layer 64 over the first side 44 of the silicon layer 42.

[0057] Referring to FIG. 6, a cross-section side view of a portion of another implementation of a conductive pad region of an image sensor with a deep silicon etch is illustrated. The conductive pad region illustrated in FIG. 6 is essentially the same in structure as the conductive pad region illustrated in FIG. 5, with the difference being that the image sensor of FIG. 6 includes a high dielectric constant dielectric layer 68 lining the silicon layer 70. As used herein, a high dielectric constant layer means a dielectric layer having a dielectric constant which is higher than the dielectric constant of SiO.sub.2, which is approximately 3.9. Use of a high dielectric constant layer may reduce the amount of dark current traveling through the image sensor. In various implementations, the high dielectric constant material may include, by non-limiting example, tantalum pentoxide (Ta.sub.2O.sub.5), aluminum oxide (Al.sub.2O.sub.3), hafnium dioxide (HfO.sub.2), HfO.sub.x, any combination thereof, and any other material with a dielectric constant higher than that of SiO.sub.2.

[0058] Referring to FIG. 7, a cross-section side view of a portion of an implementation of a conductive pad region of an image sensor with a deep silicon etch and a perimeter etch through the silicon layer is illustrated. Similar to the image sensor of FIG. 5, the image sensor illustrated by FIG. 7 includes a silicon layer 72 which has a first side 74 and a second side 76. The thickness of the silicon layer may be about 6 um, however, in other implementations the thickness of the silicon layer may be more or less than about 6 um. In various implementations, the image sensor includes a first opening 78 which extends through the silicon layer 72. The first opening 78 isolates the conductive pad 80 from the bulk of the silicon layer 72. In various implementations, the first opening may be lined with a high dielectric constant dielectric layer which may facilitate the reduction of dark current flowing within the image sensor. The high dielectric constant material may be any high dielectric material disclosed herein. The opening may be filled with a fill material. The fill material may be SiO.sub.2. In various implementations, the first opening is not lined with the high dielectric constant material but may just be filled with the fill material. Though not illustrated in FIG. 7, the first opening 78 may surround the conductive pad 80, and may be formed as a perimeter etch around the conductive pad. This is more easily visualized by imagining a trench etched into the silicon layer all around the perimeter of the conductive pad as viewed from above, such as the view of FIG. 2B. In this manner, the conductive pad 80 may be completely isolated from the remainder of the silicon layer 72. In various implementations, the first opening may be about 3 um wide, while in other implementations it may be more or less wide than about 3 um.

[0059] In various implementations, the first opening may be fully included within the full thickness of the silicon layer 72. For example, in implementations where the thickness of the silicon layer is about 6 um, the entirety of the first opening may extend through the about 6 um portion of the silicon layer. In other implementations, the first opening may partially or fully extend through the thinner portion of the silicon layer 72 which the second opening 82 is over. In such an implementation, the image sensor would not include the portion 94 of the silicon layer separating the first opening 78 from the second opening 82.

[0060] The remainder of the conductive pad region illustrated by FIG. 7 may be the same structure and material or of similar structure and material to the conductive pad region illustrated by FIG. 5. Specifically, the image sensor includes a second opening 82, a via 84, a conductive layer 86, a first dielectric layer 88, a conductive pad 80, a second dielectric layer 90 or a high dielectric constant layer 68 like that illustrated in FIG. 6, and a fill material 92. In various implementations, because the conductive pad and the via are isolated from the remainder of the silicon layer 72 due to the first opening 78, the image sensor may not necessarily include a first dielectric layer 88 which separates the via 84 from the silicon layer 72 or a second dielectric layer 90 which separates the conductive pad 80 from the silicon layer 72.

[0061] Referring to FIG. 8, a cross-section side view of a portion of another implementation of a conductive pad region of an image sensor with a deep silicon etch and a perimeter etch through the silicon layer is illustrated. The conductive pad region illustrated by FIG. 8 is similar in structure and materials to the conductive pad region of FIG. 7, with the only differences found in the first opening 96. Unlike the first opening 78 of FIG. 7, the first opening 96 is not separated from the second opening 98 by a portion of the silicon layer similar to portion 94 of FIG. 7. Further, the first opening 96 of FIG. 8 is stepped. In the implementation illustrated by FIG. 8, a first portion 100 of the first opening 96 adjacent to the first side 102 of the silicon layer 104 may be wider than the second portion 106 of the first opening adjacent to the second side 108 of the silicon layer. In other implementations, the second portion 106 may be the same size as, or wider, than the first portion 100. Further, in the implementation illustrated by FIG. 8, a high dielectric constant dielectric layer 110 is illustrated as separating the first portion 100 from the second portion 106. In various implementations, however, the dielectric layer 110 may not be used to separate the first portion 100 from the second portion 106. Further, in various implementations, the dielectric layer 110 may extend into the second portion 106 and cover the sidewalls of the portion 106 of the first opening 96. In various implementations, the second portion 106 may be formed from the second side 108, and may be formed during processing of the first side 102 of the silicon layer. Likewise, the first portion 100 may be formed from the first side 102, and may be formed during processing of the second side 108. In various implementations, the opening necessary to form the first portion 100 may be etched into the silicon layer. In such implementations, the second portion 106 may serve as an etch stop. The etched opening may then be coated with dielectric layer 110, which may be a high dielectric constant dielectric material, filled with an oxide as described later herein, and planarized through using chemical mechanical polishing (CMP) techniques as described later herein.

[0062] Referring to FIG. 9, a cross-section side view of the portion of the image sensor coupled with other conductive portions of the image sensor is illustrated. In various implementations, the image sensor may include a via 150 directly coupled to a conductive pad 152 and coupled to one or more other vias 154 extending from other conductive layers. In this manner, an entire network of conductive elements, such as conductive layer 156, may be electrically coupled to the conductive pad 152. The vias and conductive layers or traces illustrated by FIG. 9 may be similar to or the same as any other via or conductive layer or trace disclosed herein. Further, in various implementations, the via 150 may be coated with a barrier layer 158 to prevent migration of copper and other metals from the via into the silicon and other structures of the device. In implementations where the second opening in the silicon layer and the opening in the dielectric layer are etched, the barrier layer 158 may also act as an etch stop during the backside etch of the silicon layer and the dielectric layer. This may prevent the exposure of the vias during the etch, and may prevent contamination of the etch chamber by the vias. The barrier layer may also serve as an adhesion layer for the via. In various implementations, the barrier layer may include tantalum, tantalum nitride, titanium, titanium nitride, tungsten, tungsten nitride, or any other barrier layer material. In particular implementations, the barrier layer may coat portions of multiple vias and conductive layers.

[0063] FIGS. 10-11 illustrate a method of forming the conductive pad region illustrated in FIG. 5. Specifically, FIGS. 10A-10F illustrate a process flow of the method for forming the image sensor of FIG. 5 as seen from bottom and top views. Referring to FIG. 10A, the method for forming a conductive pad region in an image sensor may include forming one or more openings 112 into a second side 114 of a silicon layer 116. In various implementations, the openings may be etched. In such implementations, the openings may be etched using, by non-limiting example, plasma etching, deep-reactive ion etching, or wet chemical etching. In various implementations, a process marketed under the tradename BOSCH.RTM. by Robert Bosch GmbH, Stuttgart Germany (the "Bosch process"), may be used to form the openings 112 in the silicon layer 116. As the conductive pad region is oriented in FIG. 5, the view of FIG. 10A corresponds to a bottom view. The method includes forming one or more vias 118 within the one or more openings 112.

[0064] Referring to FIG. 10B, the method includes forming an opening 120 within the first side 122 of the silicon layer 116. The opening may be formed using any etching technique disclosed herein. The view of FIG. 10B (as well as FIGS. 10C-10F) corresponds to a top view of FIG. 5 based on the orientation illustrated in FIG. 5. In various implementations, the opening may be formed deep enough to expose the vias 118 from the first side 122 of the silicon layer 116.

[0065] Referring to FIG. 10C, the method may include forming a dielectric layer 124 over the first side 122 of the silicon layer 116. The dielectric layer covers the one or more vias, though the vias are still visible in FIG. 10C. Referring to FIG. 10D, the method of forming the conductive pad region may include etching through the dielectric layer to expose the vias. In various implementations, and as illustrated by FIG. 10D, a portion of the dielectric layer may remain over the edges of the vias 118, thus only a middle portion of the vias 118 are exposed.

[0066] Referring to FIG. 10E, the method for forming a conductive pad region includes forming a conductive pad 126 over the vias 118. Though the vias 118 are still illustrated in FIG. 10E, it is understood that the conductive pad covers the vias 118. The method may also include filling the opening 114 in the first side of the silicon layer 116 with a fill material 128, and etching through the fill material 128 to expose the conductive pad 126, as illustrated by FIG. 10F. In various implementations, the method may include planarizing the fill material in a manner that allows it to be coplanar with the dielectric layer 124 covering the silicon layer. In other implementations, the fill material may be planarized in a manner that allows it to be coplanar with a separate dielectric layer over the silicon layer 116. The surface of the fill material seen in FIG. 10F may form a plane substantially parallel with the semiconductor layer.

[0067] In various implementations, the method for forming the conductive pad region may include forming an opening around a perimeter of the conductive pad using a perimeter etch. The opening may be etched using any etching technique previously disclosed herein. This may be formed before or after the conductive pad is coupled to the one or more vias. In various implementations, the opening around the perimeter of the conductive pad extends entirely through the silicon layer and may be etched from either the first side, the second side, or both the first and the second side.

[0068] Referring to FIGS. 11A-11I, cross section side views illustrating a process flow of the method for forming the conductive pad region illustrated by FIG. 5 is shown. The process flow illustrated by FIGS. 11A-11I essentially covers the same process illustrated by FIGS. 10A-10F, just from a different perspective. Referring to FIG. 11A, a cross-section side view of a silicon layer 130 is illustrated. In this particular implementation, the silicon layer may be an epitaxial silicon layer which may be part of a much thicker wafer made of silicon. The silicon layer includes a first side 132 and a second side 134. The silicon layer may be about 6 um thick, though in other implementations it may be more or less thick than about 6 um. Referring to FIG. 11B, the method may include forming a first opening 136 into a second side 134 of the silicon layer 130. The opening may be etched using any etching technique previously disclosed herein. In various implementations, and as illustrated by FIG. 11C, the method for forming the conductive pad region may include forming a first dielectric layer 138 over the second side 134 of the silicon layer 136. The first dielectric layer may also extend along the sides of the opening 136 as illustrated by FIG. 11C. The first dielectric layer may be an ILD and may be any type of material previously disclosed herein. In other implementations, the method may not include forming a first dielectric layer.

[0069] Referring to FIG. 11D, the method may include forming the material of a via within the opening 136 in the second side 134 of the silicon layer 130. While only a single via is illustrated in FIG. 11D, it is understood that the method may include forming other vias not illustrated by FIG. 11D. The materials included in the via may be the same as or similar to any type of via previously disclosed herein. The perimeter of the via may be, by non-limiting example, circular, ovate, elliptical, a square, rectangular, or any other closed shape.

[0070] Referring to FIG. 11E, the method may include etching an opening 142 into the first side 132 of the silicon layer 130. In various implementations, the depth of the opening 142 may be etched about 2.5 um into the silicon layer 130, while in other implementations it may be etched deeper or less deep than about 2.5 um. The opening may be etched deep enough to expose the first dielectric layer 138 in implementations with a first dielectric layer. In implementations without a first dielectric layer, the opening may be etched deep enough to expose the via 140. The opening may be etched using any etching technique disclosed herein.

[0071] Referring to FIG. 11F, the method may include forming a second dielectric layer 144 over the first side 132 of the silicon layer 130. The second dielectric layer may be the same as or similar to any type of dielectric layer previously disclosed herein. In particular implementations, the second dielectric layer may include a high dielectric constant dielectric layer. Referring to FIG. 11G, the method for forming the conductive pad region illustrated in FIG. 5 includes etching through the first dielectric layer 138 and the second dielectric layer 144 to expose the via 140. In various implementations the etch will stop at a barrier or adhesion layer (not illustrated) that encapsulates the via 140. Referring to FIG. 11H, the method may include forming a conductive pad 146 within the opening 142 within the first side 132 of the silicon layer 130. In the implementation illustrated, the conductive pad 146 is directly coupled to the via 140. The conductive pad may be the same as or similar to any conductive pad disclosed herein.

[0072] Referring to FIG. 11I, the method may include filling the opening 142 in the first side 132 of the silicon layer 130 with a fill material 148. The fill material may be the same as or similar to any fill material disclosed herein. The method may include planarizing the fill material 148 to form a plane substantially parallel with the first side 132 of the silicon layer 130. In various implementations, the fill material 148 is planarized to be coplanar with a surface of a dielectric layer 144 over the first side 132 of the silicon layer 130. While FIG. 11I illustrates the dielectric layer 144 being over the first side 132 of the silicon layer 130, in other implementations a dielectric layer separate from the second dielectric layer 144 may be over the first side 132 of the silicon layer 130. The fill material may be planarized using chemical mechanical polishing CMP techniques or any other planarizing technique. Though not illustrated by FIG. 11I, the method may also include etching an opening through the fill material 148 to expose the conductive pad 146.

[0073] The method for forming a conductive pad region like those illustrated in FIGS. 7-8 may be carried out using processes similar to the method illustrated by FIGS. 10A-10I, with the difference being that the method may include forming a perimeter etch through the entire thickness of the silicon layer which extends around the conductive pad. In various implementations, it may be formed before or after the conductive pad is coupled to the via. Specifically, referring to FIG. 11B and FIG. 11E, it may be formed at the same time the opening 136 is formed into the second side 134 of the silicon layer 130, at the same time the opening 142 is formed into the first side 132 of the silicon layer, or at both the time the opening 136 and the opening 142 are formed. In other implementations, the perimeter etch may be formed before and/or after either the opening 136 or the opening 142 is formed. Further, the perimeter etch may be formed from the first side of the silicon layer, the second side of the silicon layer, or from both the first and the second side of the silicon layer. In various implementations, the perimeter etch may be formed using any etching technique disclosed herein or any etching technique disclosed in U.S. Pat. No. 7,544,592 to Kirby et al., entitled "Method for increasing etch rate during deep silicon dry etch," issued Jun. 9, 2009, and U.S. Pat. No. 8,110,488 to Kirby et al., entitled "Method for increasing etch rate during deep silicon dry etch," issued Feb. 7, 2012, the disclosures of each of which are hereby incorporated entirely herein by reference. In other implementations, the perimeter etch may be stepped. In such implementations, the perimeter etch may be formed by partially etching through the silicon layer from the first side, and partially etching through the silicon layer from the second side in a manner that the etch from the second side connects with the etch from the first side, thus forming an opening through the entirety of the silicon layer. The etch from the first side may be wider than, smaller than, or the same size as the etch from the second side of the silicon layer. In other implementations the stepped etch may be formed from a single side of the silicon layer.

[0074] In places where the description above refers to particular implementations of image sensors and implementing components, sub-components, methods and sub-methods, it should be readily apparent that a number of modifications may be made without departing from the spirit thereof and that these implementations, implementing components, sub-components, methods and sub-methods may be applied to other image sensors.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

D00009

D00010

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.