Multi-resistance Mram

CHOI; YOUNG-SUK ; et al.

U.S. patent application number 15/959837 was filed with the patent office on 2019-08-08 for multi-resistance mram. This patent application is currently assigned to SanDisk Technologies LLC. The applicant listed for this patent is SanDisk Technologies LLC. Invention is credited to WON HO CHOI, YOUNG-SUK CHOI.

| Application Number | 20190245137 15/959837 |

| Document ID | / |

| Family ID | 67476938 |

| Filed Date | 2019-08-08 |

View All Diagrams

| United States Patent Application | 20190245137 |

| Kind Code | A1 |

| CHOI; YOUNG-SUK ; et al. | August 8, 2019 |

MULTI-RESISTANCE MRAM

Abstract

Apparatuses, systems, and methods are disclosed for magnetoresistive random access memory. A magnetic tunnel junction (MTJ) for storing data may include a reference layer. A free layer of an MTJ may be separated from a reference layer by a barrier layer. A free layer may be configured such that one or more resistance states for an MTJ correspond to one or more positions of a magnetic domain wall within the free layer. A domain stabilization layer may be coupled to a portion of a free layer, and may be configured to prevent migration of a domain wall into the portion of the free layer.

| Inventors: | CHOI; YOUNG-SUK; (Los Gatos, CA) ; CHOI; WON HO; (San Jose, CA) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Assignee: | SanDisk Technologies LLC Plano TX |

||||||||||

| Family ID: | 67476938 | ||||||||||

| Appl. No.: | 15/959837 | ||||||||||

| Filed: | April 23, 2018 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 15891370 | Feb 8, 2018 | |||

| 15959837 | ||||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | G11C 11/401 20130101; G11C 11/161 20130101; H01L 43/08 20130101; G11C 11/1675 20130101; G11C 11/54 20130101; G11C 11/005 20130101; G06N 3/063 20130101; H01L 43/02 20130101; G06N 3/04 20130101; H01L 27/222 20130101 |

| International Class: | H01L 43/02 20060101 H01L043/02; H01L 43/08 20060101 H01L043/08; H01L 27/22 20060101 H01L027/22; G11C 11/16 20060101 G11C011/16; G06N 3/063 20060101 G06N003/063; G06N 3/04 20060101 G06N003/04 |

Claims

1. An apparatus comprising: a magnetic tunnel junction (MTJ) for storing data, the magnetic tunnel junction comprising: a reference layer; a free layer separated from the reference layer by a barrier layer, the free layer configured such that one or more resistance states for the MTJ correspond to one or more positions of a magnetic domain wall within the free layer; and a domain stabilization layer coupled to a portion of the free layer, the domain stabilization layer configured to prevent migration of the domain wall into the portion of the free layer.

2. The apparatus of claim 1, wherein the domain stabilization layer comprises an antiferromagnetic layer.

3. The apparatus of claim 2, wherein the antiferromagnetic layer is configured to induce a unidirectional magnetic anisotropy in the portion of the free layer.

4. The apparatus of claim 1, wherein the domain stabilization layer comprises a multilayer.

5. The apparatus of claim 4, wherein the multilayer comprises one or more of: a cobalt/platinum multilayer and a cobalt/palladium multilayer.

6. The apparatus of claim 4, wherein the multilayer is configured to induce a coercivity increase in the portion of the free layer.

7. The apparatus of claim 1, wherein the domain stabilization layer is configured to prevent migration of the domain wall into the portion of the free layer by stabilizing a magnetization direction for the portion of the free layer.

8. The apparatus of claim 1, further comprising a controller configured to increase the resistance state of the MTJ by applying a first write current to move the domain wall in a first direction.

9. The apparatus of claim 8, wherein the controller is further configured to decrease the resistance state of the MTJ by applying a second write current in a direction opposite to the first write current, to move the domain wall in a second direction opposite to the first direction.

10. The apparatus of claim 1, wherein the free layer comprises a nucleation region configured to form the domain wall, and an arm extending from the nucleation region, the arm comprising a plurality of pinning sites for pinning the domain wall.

11. The apparatus of claim 1, further comprising a second domain stabilization layer configured to prevent migration of the domain wall into a second portion of the free layer, wherein the free layer comprises an elongate arm comprising a plurality of pinning sites for pinning the domain wall, the portion of the free layer comprises a first end portion of the arm, and the second portion of the free layer comprises a second end portion of the arm opposite to the first end portion.

12. A system comprising: a neuromorphic computing die, the neuromorphic computing die comprising a plurality of artificial neurons and a synapse array of multi-state magnetic memory cells coupling the artificial neurons, wherein a multi-state magnetic memory cell comprises: a fixed layer; a magnetic storage layer separated from the fixed layer by a barrier layer, the magnetic storage layer configured such that one or more states for the multi-state magnetic memory cell correspond to one or more positions of a magnetic domain wall within the magnetic storage layer; and a domain stabilization layer coupled to a portion of the magnetic storage layer, the domain stabilization layer configured to provide a fixed magnetization for the portion of the magnetic storage layer.

13. The system of claim 12, wherein the domain stabilization layer comprises an antiferromagnetic layer configured to induce a unidirectional magnetic anisotropy in the portion of the magnetic storage layer.

14. The system of claim 12, wherein the domain stabilization layer comprises a multilayer configured to induce a coercivity increase in the portion of the magnetic storage layer.

15. The system of claim 14, wherein the multilayer comprises one or more of: a cobalt/platinum multilayer and a cobalt/palladium multilayer.

16. The system of claim 12, further comprising a controller configured to change the resistance state of the multi-state magnetic memory cell by applying a write current to move the domain wall, wherein changing the resistance state comprises one of: applying a first write current to move the domain wall in a first direction, and applying a second write current in a direction opposite to the first write current, to move the domain wall in a second direction opposite to the first direction.

17. The system of claim 12, wherein the magnetic storage layer comprises a nucleation region configured to form the domain wall, and an arm extending from the nucleation region, the arm comprising a plurality of pinning sites for pinning the domain wall.

18. An apparatus comprising: means for moving a magnetic domain wall in a free layer for a magnetic tunnel junction; means for preventing the magnetic domain wall from entering a portion of the free layer.

19. The apparatus of claim 18, further comprising means for forming the magnetic domain wall.

20. The apparatus of claim 18, further comprising means for pinning the domain wall at one or more predetermined locations in the free layer.

21. An apparatus comprising: a magnetoresistive random access memory (MRAM) die, the MRAM die comprising a plurality of memory cells, a memory cell comprising a fixed layer, a barrier layer, and a free layer, the barrier layer disposed between the fixed layer and the free layer, the free layer comprising: a wall extension region configured to provide a plurality of resistance states for the memory cell corresponding to positions of a magnetic domain wall within the wall extension region; and an end region configured to exclude the domain wall.

22. The apparatus of claim 21, further comprising a domain stabilization layer coupled to the end region of the free layer, the domain stabilization layer configured to stabilize a magnetization direction for the end region of the free layer.

23. The apparatus of claim 21, wherein the free layer further comprises a nucleation region configured to form the magnetic domain wall in response to a write current

24. The apparatus of claim 23, further comprising a plurality of pinning sites formed at predetermined locations in the wall extension region and configured to pin the domain wall such that the domain wall migrates from one pinning site to another pinning site in response to a changed write current.

25. A method comprising: applying a first write current to a magnetic tunnel junction to move a magnetic domain wall to a pinning site in a wall extension region of a free layer of the magnetic tunnel junction; applying a second write current to the magnetic tunnel junction to move the domain wall from the pinning site to a boundary between the wall extension region and an end region of the free layer; applying a third write current to the magnetic tunnel junction to move the domain wall back to the pinning site.

26. The method of claim 25, wherein applying a third write current to move the domain wall back to the pinning site comprises moving the domain wall without applying an erase current.

Description

CROSS-REFERENCES TO RELATED APPLICATIONS

[0001] This is a continuation-in-part application of and claims priority to U.S. patent application Ser. No. 15/891,370 entitled "MULTI-RESISTANCE MRAM" and filed on Feb. 8, 2018, for Young-suk Choi et al., which is incorporated herein by reference

TECHNICAL FIELD

[0002] The present disclosure, in various embodiments, relates to magnetoresistive random access memory and more particularly relates to multi-resistance magnetoresistive random access memory.

BACKGROUND

[0003] Various types of magnetoresistive random access memory (MRAM) store data using magnetic tunnel junctions. A magnetic tunnel junction (MTJ) may include "fixed" and "free" magnetic layers, where a magnetic moment of the free layer may be switched to be parallel or antiparallel to a magnetic moment of the fixed layer. A thin dielectric or barrier layer may separate the fixed and free layers, and current may flow across the barrier layer due to quantum tunneling. A difference in resistance between parallel and antiparallel states allows data to be stored. For example, a low resistance may correspond to a binary "1" and a high resistance may correspond to a binary "0," Alternatively, a low resistance may correspond to a binary "0" and a high resistance may correspond to a binary "1." However, a memory device that uses an array of MTJs to store one bit of data per MTJ may have a low storage density, or a low capacity for the area the array occupies.

SUMMARY

[0004] Apparatuses are presented for magnetoresistive random access memory. In one embodiment, a magnetic tunnel junction (MTJ) for storing data includes a reference layer. In a certain embodiment, a magnetic tunnel junction includes a free layer separated from a reference layer by a barrier layer. In a further embodiment, a free layer may be configured such that one or more resistance states for an MTJ correspond to one or more positions of a magnetic domain wall within the free layer. In certain embodiments, a domain stabilization layer may be coupled to a portion of a free layer, and may be configured to prevent migration of a domain wall into the portion of the free layer.

[0005] Systems are presented for neuromorphic computing. In one embodiment, a system includes a neuromorphic computing die. In a certain embodiment, a neuromorphic computing die includes a plurality of artificial neurons and a synapse array of multi-state magnetic memory cells coupling the artificial neurons. In a further embodiment, a multi-state magnetic memory cell includes a fixed layer. In one embodiment, a multi-state magnetic memory cell includes a magnetic storage layer separated from a fixed layer by a barrier layer. In a certain embodiment, a magnetic storage layer may be configured such that one or more states for a multi-state magnetic memory cell correspond to one or more positions of a magnetic domain wall within the magnetic storage layer. In a further embodiment, a domain stabilization layer may be coupled to a portion of a magnetic storage layer, and may be configured to provide a fixed magnetization for the portion of the magnetic storage layer.

[0006] An apparatus, in another embodiment, includes means for moving a magnetic domain wall in a free layer for a magnetic tunnel junction. In a certain embodiment, an apparatus includes means for preventing a magnetic domain wall from entering a portion of a free layer.

[0007] In another embodiment, a magnetoresistive random access memory die includes a plurality of memory cells. In one embodiment, a memory cell includes a fixed layer, a barrier layer, and a free layer. In a further embodiment, a barrier layer is disposed between a fixed layer and a free layer. A free layer, in one embodiment, includes a wall extension region configured to provide a plurality of resistance states for a memory cell corresponding to positions of a magnetic domain wall within the wall extension region. In a further embodiment, a free layer includes an end region configured to exclude a domain wall.

[0008] Methods are presented for magnetoresistive random access memory. A method, in one embodiment, includes applying a first write current to a magnetic tunnel junction, to move a magnetic domain wall to a pinning site in a wall extension region of a free layer of the magnetic tunnel junction. In a certain embodiment, a method includes applying a second write current to a magnetic tunnel junction to move a domain wall from a pinning site to a boundary between a wall extension region and an end region of a free layer. In a further embodiment, a method includes applying a third write current to a magnetic tunnel junction to move a domain wall back to a pinning site.

BRIEF DESCRIPTION OF THE DRAWINGS

[0009] A more particular description is included below with reference to specific embodiments illustrated in the appended drawings. Understanding that these drawings depict only certain embodiments of the disclosure and are not therefore to be considered to be limiting of its scope, the disclosure is described and explained with additional specificity and detail through the use of the accompanying drawings, in which:

[0010] FIG. 1 is a schematic block diagram of one embodiment of a system comprising magnetoresistive random access memory (MRAM);

[0011] FIG. 2 is a schematic block diagram illustrating one embodiment of an MRAM die;

[0012] FIG. 3 is a schematic block diagram illustrating a portion of an artificial neural network, in one embodiment;

[0013] FIG. 4 is a schematic block diagram illustrating one embodiment of a neuromorphic computing die;

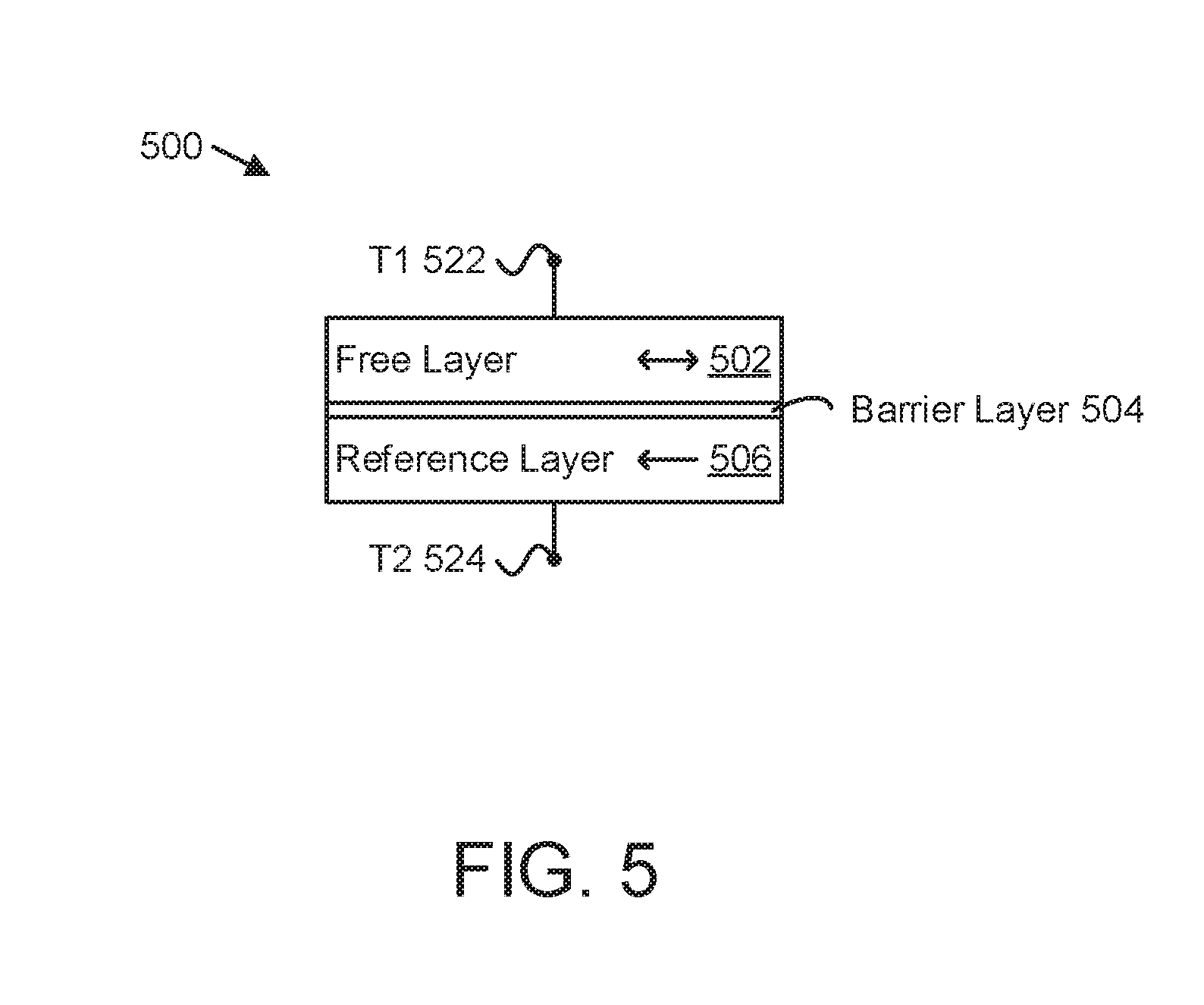

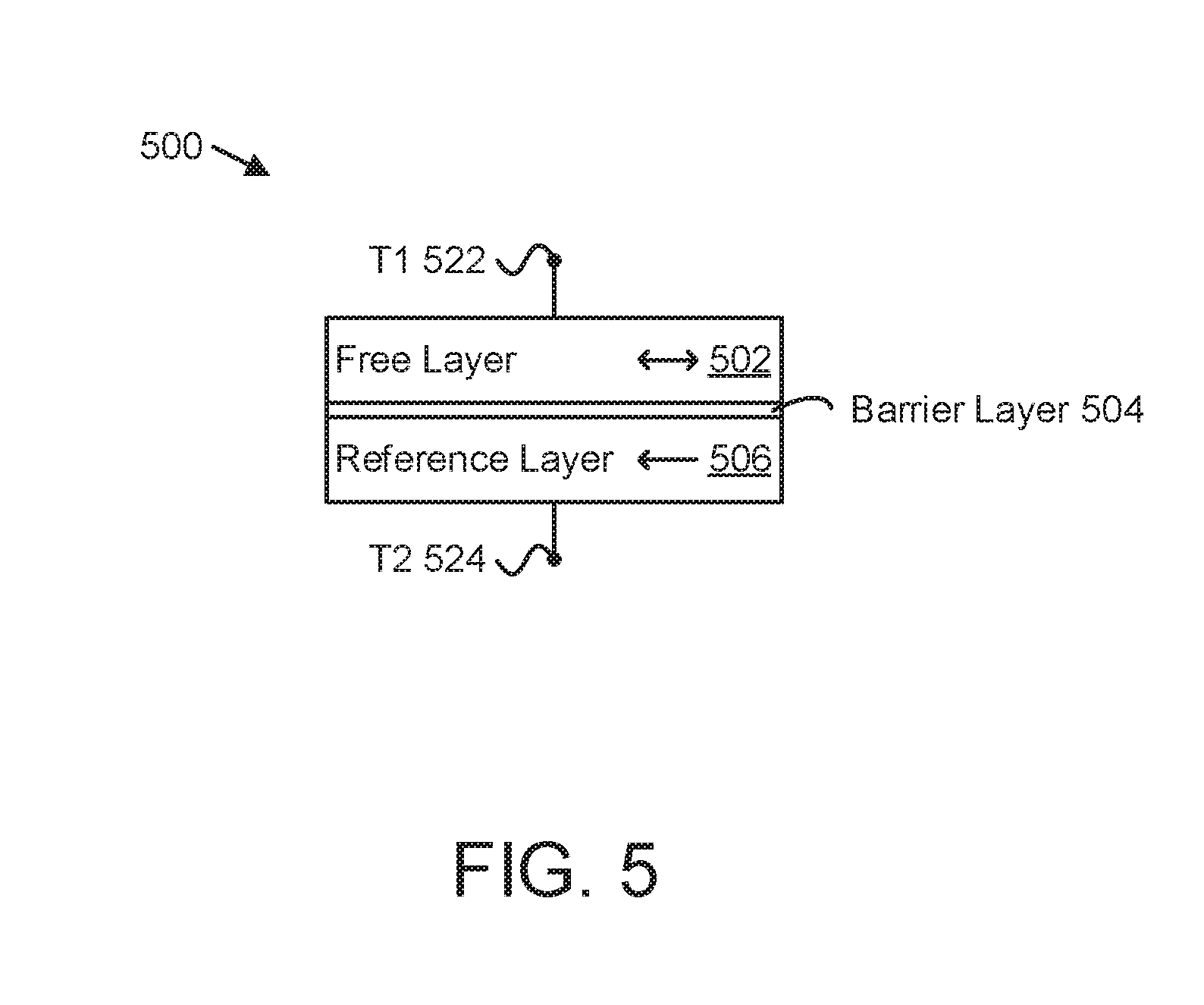

[0014] FIG. 5 is a schematic block diagram illustrating one embodiment of a magnetic tunnel junction;

[0015] FIG. 6A is a top view illustrating one embodiment of a free layer for a magnetic tunnel junction, in a first resistance state;

[0016] FIG. 6B is a top view illustrating the free layer of FIG. 6A, in a second resistance state;

[0017] FIG. 6C is a top view illustrating the free layer of FIG. 6A, in a third resistance state;

[0018] FIG. 6D is a top view illustrating the free layer of FIG. 6A, in a fourth resistance state;

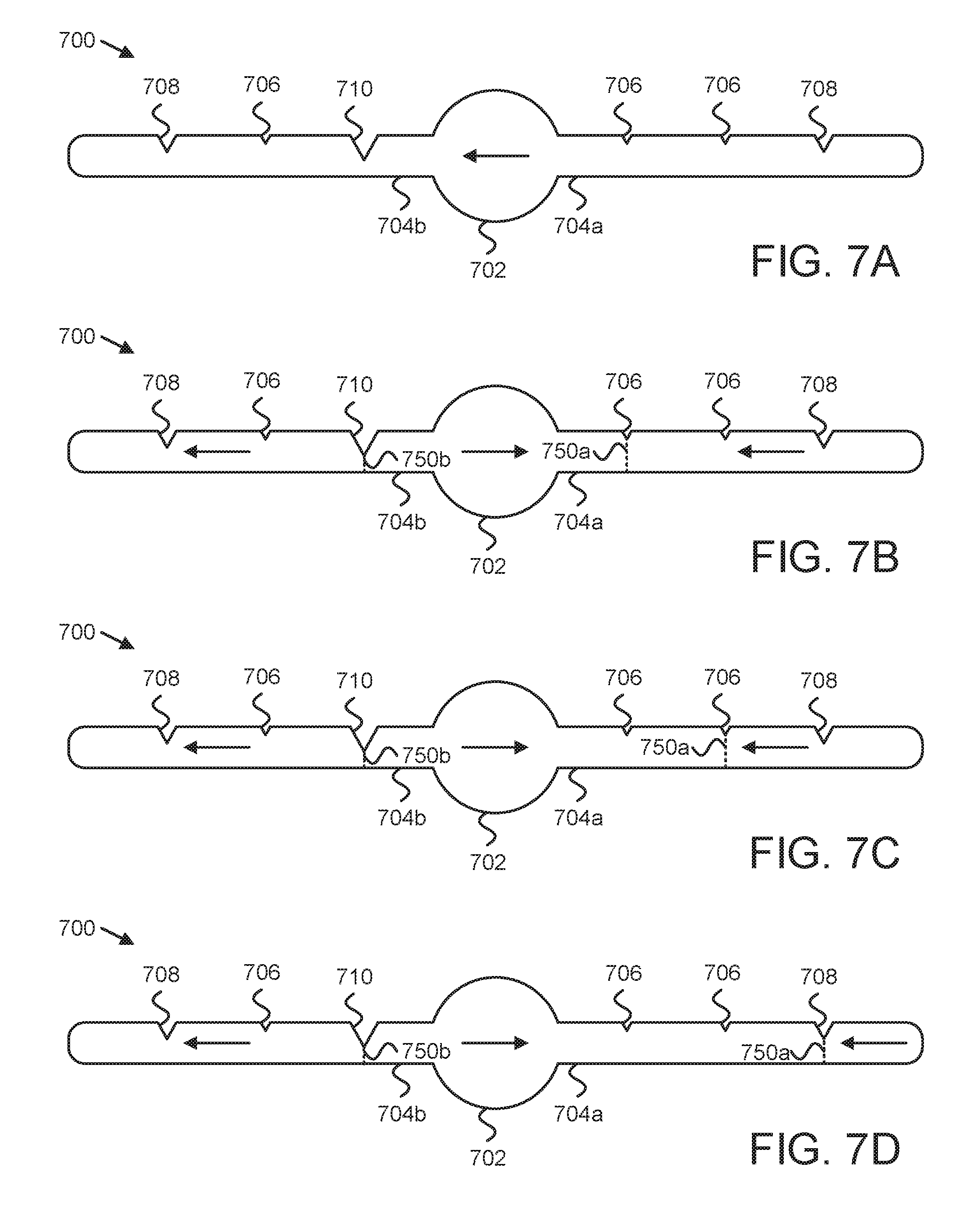

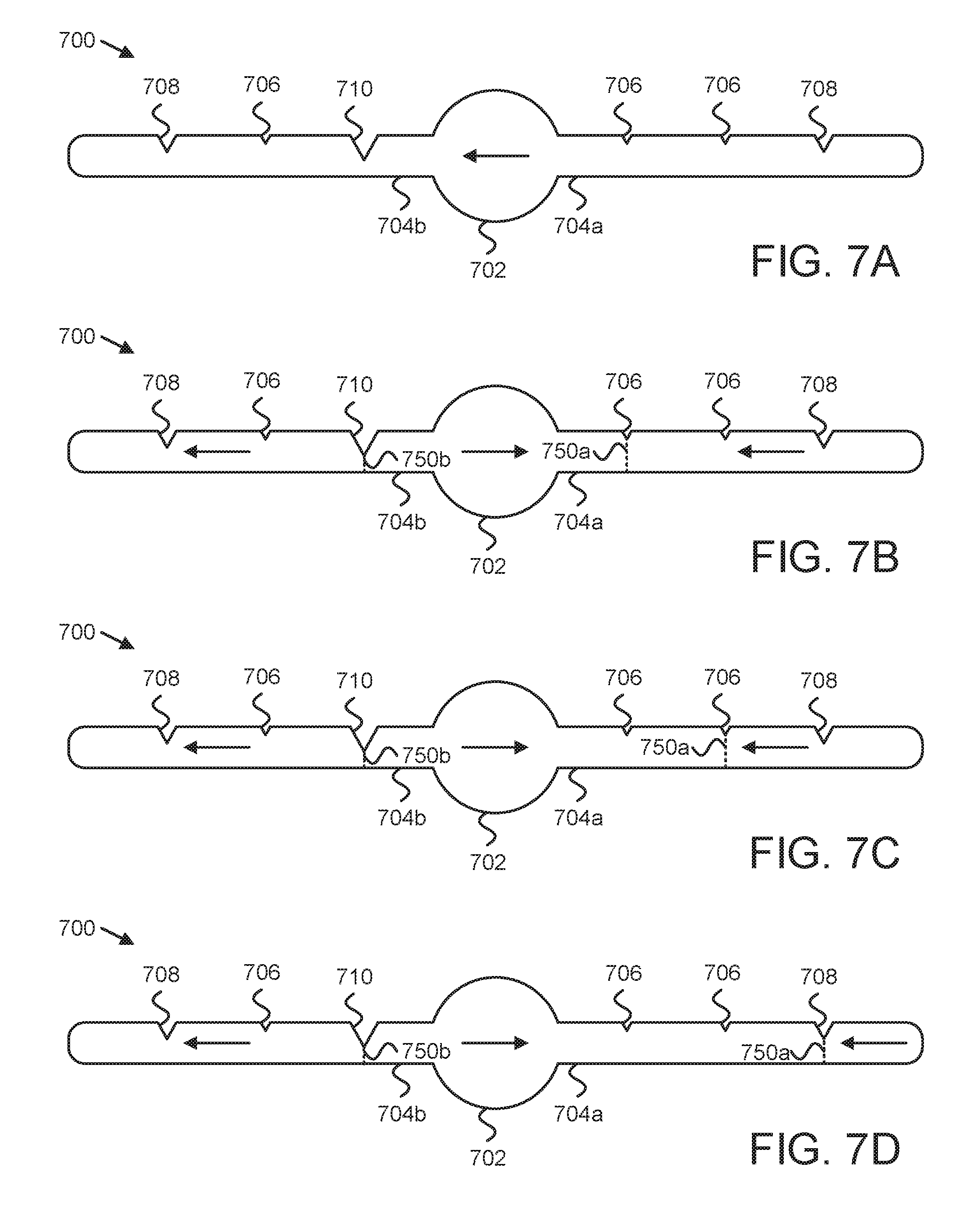

[0019] FIG. 7A is a top view illustrating another embodiment of a free layer for a magnetic tunnel junction, in a first resistance state;

[0020] FIG. 7B is a top view illustrating the free layer of FIG. 7A, in a second resistance state;

[0021] FIG. 7C is a top view illustrating the free layer of FIG. 7A, in a third resistance state;

[0022] FIG. 7D is a top view illustrating the free layer of FIG. 7A, in a fourth resistance state;

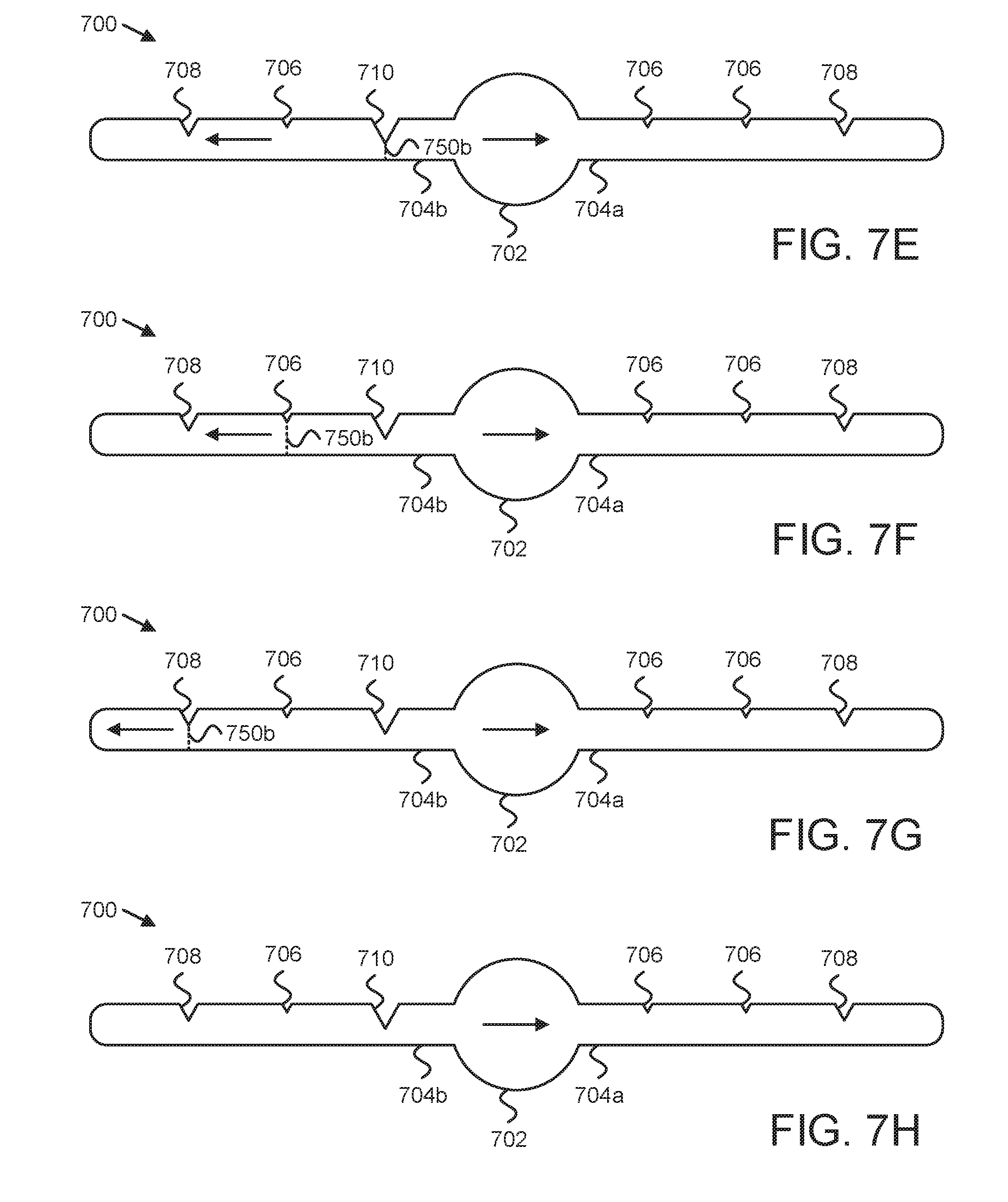

[0023] FIG. 7E is a top view illustrating the free layer of FIG. 7A, in a fifth resistance state;

[0024] FIG. 7F is a top view illustrating the free layer of FIG. 7A, in a sixth resistance state;

[0025] FIG. 7G is a top view illustrating the free layer of FIG. 7A, in a seventh resistance state;

[0026] FIG. 7H is a top view illustrating the free layer of FIG. 7A, in an eighth resistance state;

[0027] FIG. 8 is a top view illustrating another embodiment of a free layer for a magnetic tunnel junction;

[0028] FIG. 9 is a schematic block diagram illustrating a further embodiment of a magnetic tunnel junction;

[0029] FIG. 10A is a top view illustrating one embodiment of a free layer for a magnetic tunnel junction, in a first resistance state;

[0030] FIG. 10B is a top view illustrating the free layer of FIG. 10A, in a second resistance state;

[0031] FIG. 10C is a top view illustrating the free layer of FIG. 10A, in a third resistance state;

[0032] FIG. 10D is a top view illustrating the free layer of FIG. 10A, in a fourth resistance state;

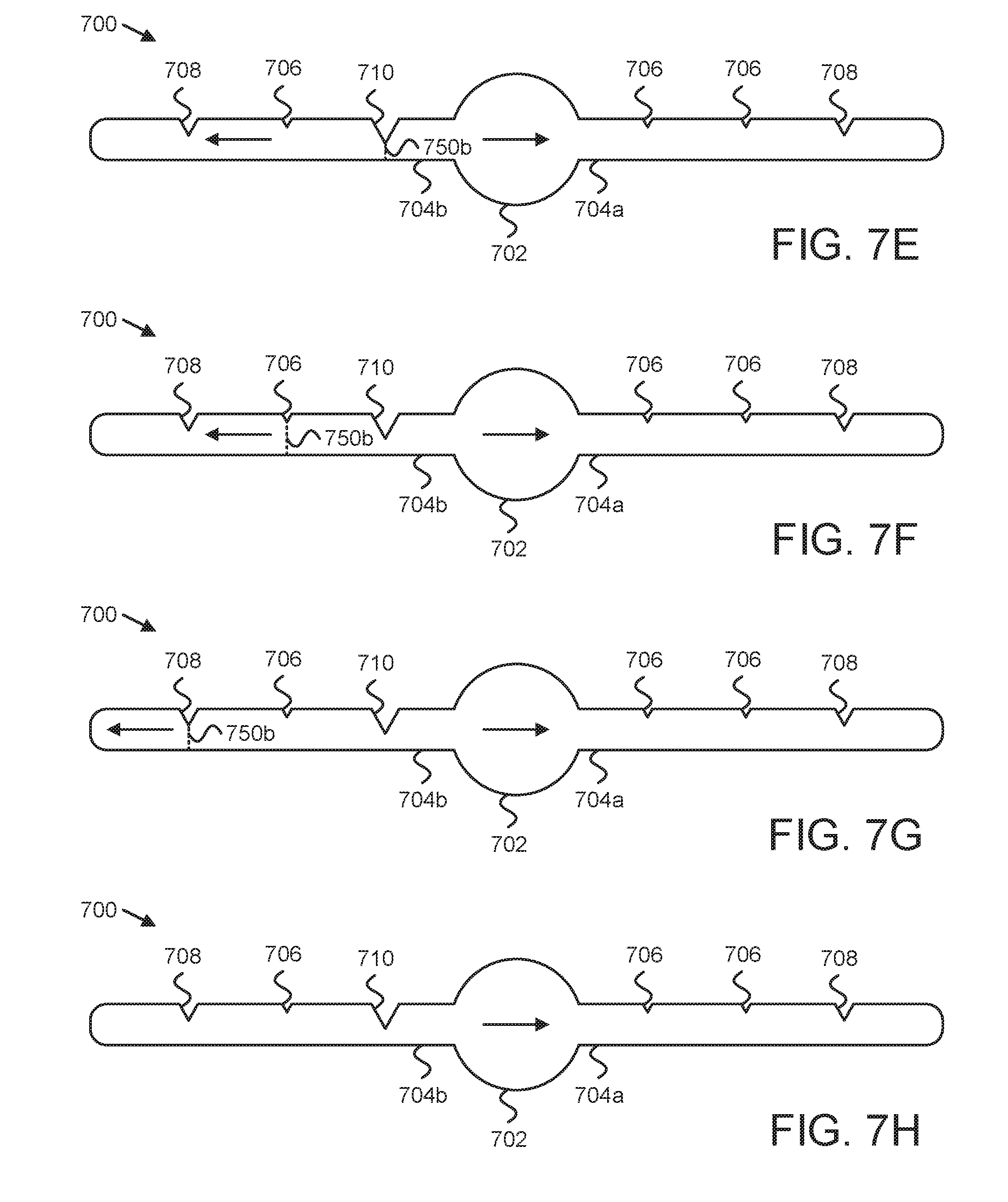

[0033] FIG. 11A is a side view illustrating another embodiment of a free layer for a magnetic tunnel junction, in a first resistance state;

[0034] FIG. 11B is a side view illustrating the free layer of FIG. 11A, in a second resistance state;

[0035] FIG. 11C is a side view illustrating the free layer of FIG. 11A, in a third resistance state;

[0036] FIG. 11D is a side view illustrating the free layer of FIG. 11A, in a fourth resistance state;

[0037] FIG. 11E is a side view illustrating the free layer of FIG. 11A, in a fifth resistance state;

[0038] FIG. 11F is a side view illustrating the free layer of FIG. 11A, in a sixth resistance state;

[0039] FIG. 11G is a side view illustrating the free layer of FIG. 11A, in a seventh resistance state;

[0040] FIG. 11H is a side view illustrating the free layer of FIG. 11A, in an eighth resistance state;

[0041] FIG. 11I is a side view illustrating the free layer of FIG. 11A, returned to the seventh resistance state;

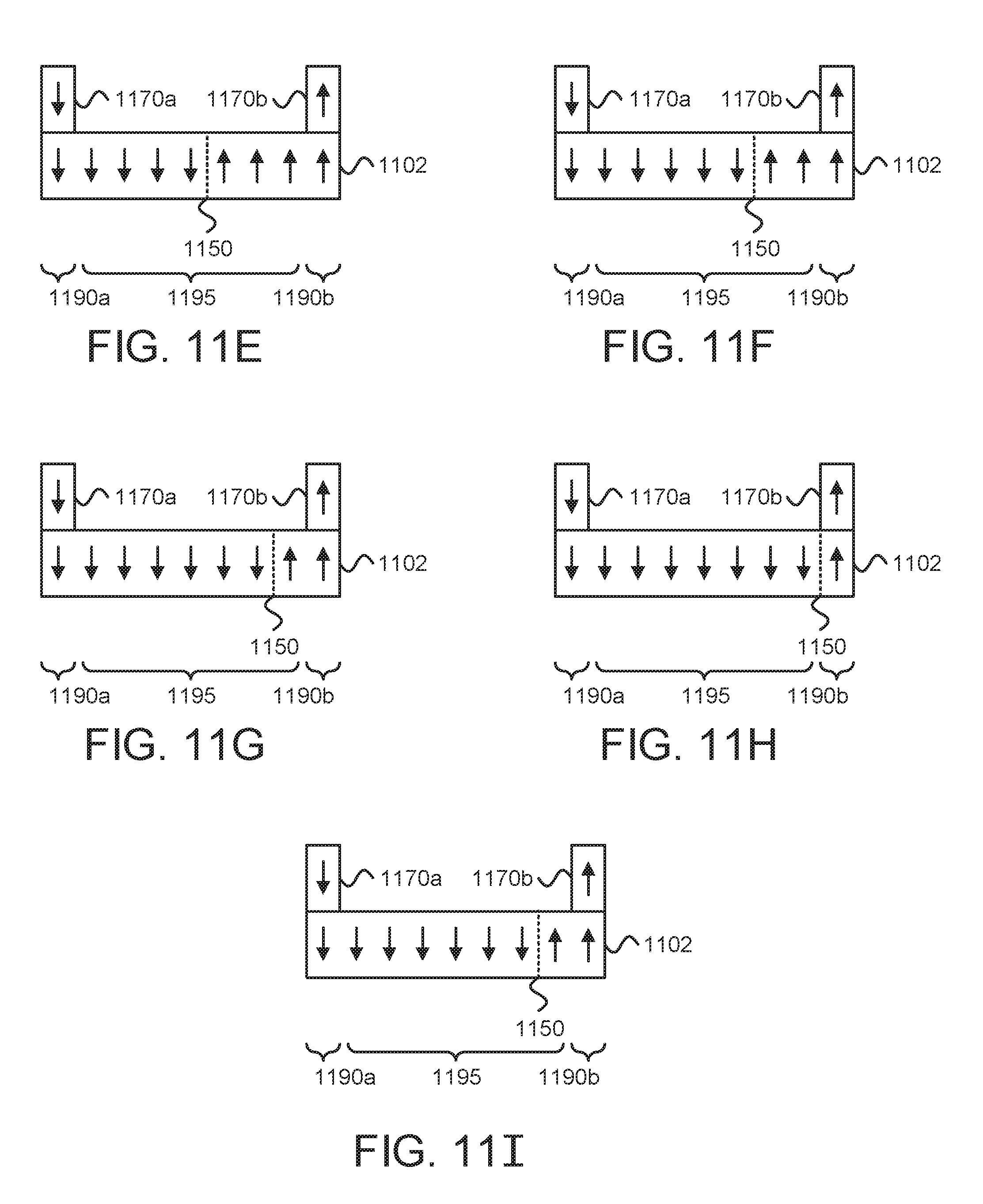

[0042] FIG. 12A is a schematic block diagram illustrating one embodiment of a domain stabilization layer;

[0043] FIG. 12B is a schematic block diagram illustrating another embodiment of a domain stabilization layer;

[0044] FIG. 12C is a schematic block diagram illustrating another embodiment of a domain stabilization layer;

[0045] FIG. 13 is a schematic flow chart diagram illustrating one embodiment of a method for writing data to magnetoresistive memory;

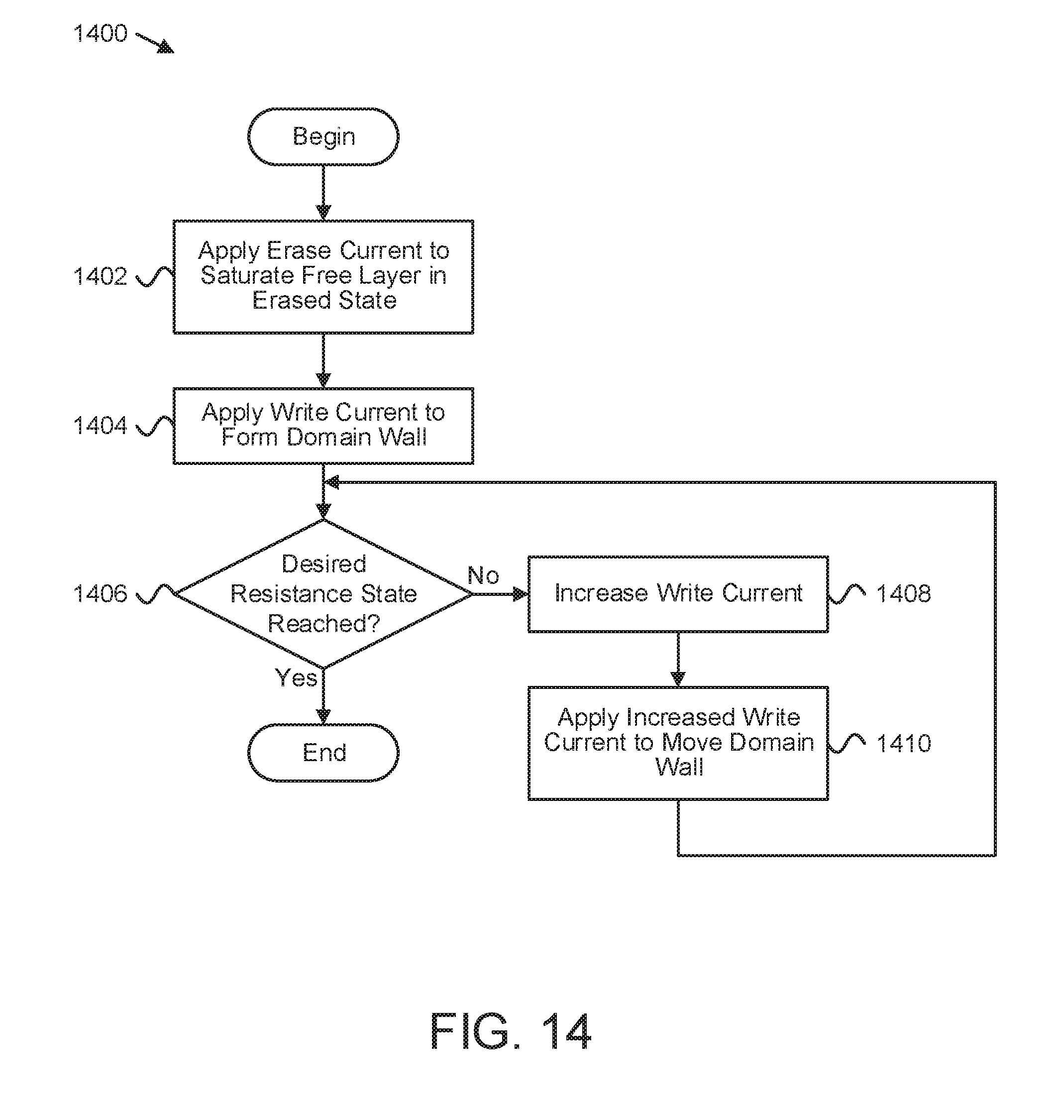

[0046] FIG. 14 is a schematic flow chart diagram illustrating another embodiment of a method for writing data to magnetoresistive memory; and

[0047] FIG. 15 is a schematic flow chart diagram illustrating another embodiment of a method for writing data to magnetoresistive memory.

DETAILED DESCRIPTION

[0048] Aspects of the present disclosure may be embodied as an apparatus, system, method, or computer program product. Accordingly, aspects of the present disclosure may take the form of an entirely hardware embodiment, an entirely software embodiment (including firmware, resident software, micro-code, or the like) or an embodiment combining software and hardware aspects that may all generally be referred to herein as a "circuit," "module," "apparatus," or "system." Furthermore, aspects of the present disclosure may take the form of a computer program product embodied in one or more non-transitory computer readable storage media storing computer readable and/or executable program code.

[0049] Many of the functional units described in this specification have been labeled as modules, in order to more particularly emphasize their implementation independence. For example, a module may be implemented as a hardware circuit comprising custom VLSI circuits or gate arrays, off-the-shelf semiconductors such as logic chips, transistors, or other discrete components. A module may also be implemented in programmable hardware devices such as field programmable gate arrays, programmable array logic, programmable logic devices, or the like.

[0050] Modules may also be implemented at least partially in software for execution by various types of processors. An identified module of executable code may, for instance, comprise one or more physical or logical blocks of computer instructions which may, for instance, be organized as an object, procedure, or function. Nevertheless, the executables of an identified module need not be physically located together, but may comprise disparate instructions stored in different locations which, when joined logically together, comprise the module and achieve the stated purpose for the module.

[0051] Indeed, a module of executable code may include a single instruction, or many instructions, and may even be distributed over several different code segments, among different programs, across several memory devices, or the like. Where a module or portions of a module are implemented in software, the software portions may be stored on one or more computer readable and/or executable storage media. Any combination of one or more computer readable storage media may be utilized. A computer readable storage medium may include, for example, but not limited to, an electronic, magnetic, optical, electromagnetic, infrared, or semiconductor system, apparatus, or device, or any suitable combination of the foregoing, but would not include propagating signals. In the context of this document, a computer readable and/or executable storage medium may be any tangible and/or non-transitory medium that may contain or store a program for use by or in connection with an instruction execution system, apparatus, processor, or device.

[0052] Computer program code for carrying out operations for aspects of the present disclosure may be written in any combination of one or more programming languages, including an object oriented programming language such as Python, Java, Smalltalk, C++, C#, Objective C, or the like, conventional procedural programming languages, such as the "C" programming language, scripting programming languages, and/or other similar programming languages. The program code may execute partly or entirely on one or more of a user's computer and/or on a remote computer or server over a data network or the like.

[0053] A component, as used herein, comprises a tangible, physical, non-transitory device. For example, a component may be implemented as a hardware logic circuit comprising custom VLSI circuits, gate arrays, or other integrated circuits; off-the-shelf semiconductors such as logic chips, transistors, or other discrete devices; and/or other mechanical or electrical devices. A component may also be implemented in programmable hardware devices such as field programmable gate arrays, programmable array logic, programmable logic devices, or the like. A component may comprise one or more silicon integrated circuit devices (e.g., chips, die, die planes, packages) or other discrete electrical devices, in electrical communication with one or more other components through electrical lines of a printed circuit board (PCB) or the like. Each of the modules described herein, in certain embodiments, may alternatively be embodied by or implemented as a component.

[0054] A circuit, as used herein, comprises a set of one or more electrical and/or electronic components providing one or more pathways for electrical current. In certain embodiments, a circuit may include a return pathway for electrical current, so that the circuit is a closed loop. In another embodiment, however, a set of components that does not include a return pathway for electrical current may be referred to as a circuit (e.g., an open loop). For example, an integrated circuit may be referred to as a circuit regardless of whether the integrated circuit is coupled to ground (as a return pathway for electrical current) or not. In various embodiments, a circuit may include a portion of an integrated circuit, an integrated circuit, a set of integrated circuits, a set of non-integrated electrical and/or electrical components with or without integrated circuit devices, or the like. In one embodiment, a circuit may include custom VLSI circuits, gate arrays, logic circuits, or other integrated circuits; off-the-shelf semiconductors such as logic chips, transistors, or other discrete devices; and/or other mechanical or electrical devices. A circuit may also be implemented as a synthesized circuit in a programmable hardware device such as field programmable gate array, programmable array logic, programmable logic device, or the like (e.g., as firmware, a netlist, or the like). A circuit may comprise one or more silicon integrated circuit devices (e.g., chips, die, die planes, packages) or other discrete electrical devices, in electrical communication with one or more other components through electrical lines of a printed circuit board (PCB) or the like. Each of the modules described herein, in certain embodiments, may be embodied by or implemented as a circuit.

[0055] Reference throughout this specification to "one embodiment," "an embodiment," or similar language means that a particular feature, structure, or characteristic described in connection with the embodiment is included in at least one embodiment of the present disclosure. Thus, appearances of the phrases "in one embodiment," "in an embodiment," and similar language throughout this specification may, but do not necessarily, all refer to the same embodiment, but mean "one or more but not all embodiments" unless expressly specified otherwise. The terms "including," "comprising," "having," and variations thereof mean "including but not limited to" unless expressly specified otherwise. An enumerated listing of items does not imply that any or all of the items are mutually exclusive and/or mutually inclusive, unless expressly specified otherwise. The terms "a," "an," and "the" also refer to "one or more" unless expressly specified otherwise.

[0056] Aspects of the present disclosure are described below with reference to schematic flowchart diagrams and/or schematic block diagrams of methods, apparatuses, systems, and computer program products according to embodiments of the disclosure. It will be understood that each block of the schematic flowchart diagrams and/or schematic block diagrams, and combinations of blocks in the schematic flowchart diagrams and/or schematic block diagrams, can be implemented by computer program instructions. These computer program instructions may be provided to a processor of a computer or other programmable data processing apparatus to produce a machine, such that the instructions, which execute via the processor or other programmable data processing apparatus, create means for implementing the functions and/or acts specified in the schematic flowchart diagrams and/or schematic block diagrams block or blocks.

[0057] It should also be noted that, in some alternative implementations, the functions noted in the block may occur out of the order noted in the figures. For example, two blocks shown in succession may, in fact, be executed substantially concurrently, or the blocks may sometimes be executed in the reverse order, depending upon the functionality involved. Other steps and methods may be conceived that are equivalent in function, logic, or effect to one or more blocks, or portions thereof, of the illustrated figures. Although various arrow types and line types may be employed in the flowchart and/or block diagrams, they are understood not to limit the scope of the corresponding embodiments. For instance, an arrow may indicate a waiting or monitoring period of unspecified duration between enumerated steps of the depicted embodiment.

[0058] In the following detailed description, reference is made to the accompanying drawings, which form a part thereof. The foregoing summary is illustrative only and is not intended to be in any way limiting. In addition to the illustrative aspects, embodiments, and features described above, further aspects, embodiments, and features will become apparent by reference to the drawings and the following detailed description. The description of elements in each figure may refer to elements of proceeding figures. Like numbers may refer to like elements in the figures, including alternate embodiments of like elements.

[0059] FIG. 1 depicts a system 100 comprising magnetoresistive random access memory (MRAM) 150. In the depicted embodiment, the system includes a computing device 110. In various embodiments, a computing device 110 may be any electronic device capable computing by performing arithmetic or logical operations on electronic data. For example, a computing device 110 may be a server, a workstation, a desktop computer, a laptop computer, a tablet, a smartphone, a control system for another electronic device, a network attached storage device, a block device on a storage area network, a router, a network switch, or the like. In certain embodiments, a computing device 110 may include a non-transitory, computer readable storage medium that stores computer readable instructions configured to cause the computing device 110 to perform steps of one or more of the methods disclosed herein.

[0060] In the depicted embodiment, the computing device 110 includes a processor 115, a memory 130, and storage 140. In various embodiments, a processor 115 may be any electronic element that carries out the arithmetic or logical operations performed by the computing device. For example, in one embodiment, the processor 115 may be a general-purpose processor that executes stored program code. In another embodiment, a processor 115 may be a field-programmable gate array (FPGA), an application-specific integrated circuit (ASIC), or the like, that operates on data stored by the memory 130 and/or the storage 140. In a certain embodiment, a processor 115 may be a controller for a storage device (e.g., on a storage area network) a networking device, or the like.

[0061] In the depicted embodiment, the processor 115 includes a cache 120. In various embodiments, a cache 120 may store data for use by the processor 115. In certain embodiments, a cache 120 may be smaller and faster than the memory 130, and may duplicate data in frequently-used locations of the memory 130, or the like. In certain embodiments, a processor 115 may include a plurality of caches 120. In various embodiments, a cache 120 may include one or more types of memory media for storing data, such as static random access memory (SRAM) 122, magnetoresistive random access memory (MRAM) 150, or the like. For example, in one embodiment, a cache 120 may include SRAM 122. In another embodiment, a cache 120 may include MRAM 150. In a certain embodiment, a cache 120 may include a combination of SRAM 122, MRAM 150, and/or other memory media types.

[0062] The memory 130, in one embodiment, is coupled to the processor 115 by a memory bus 135. In certain embodiments, the memory 130 may store data that is directly addressable by the processor 115. In various embodiments, a memory 130 may include one or more types of memory media for storing data, such as dynamic random access memory (DRAM) 132, MRAM 150, or the like. For example, in one embodiment, a memory 130 may include DRAM 132. In another embodiment, a memory 130 may include MRAM 150. In a certain embodiment, a memory 130 may include a combination of DRAM 132, MRAM 150, and/or other memory media types.

[0063] The storage 140, in one embodiment, is coupled to the processor 115 by a storage bus 145. In certain embodiments, the storage bus 145 may be a peripheral bus of the computing device 110, such as a peripheral component interconnect express (PCI Express or PCIe) bus, a serial Advanced Technology Attachment (SATA) bus, a parallel Advanced Technology Attachment (PATA) bus, a small computer system interface (SCSI) bus, a FireWire bus, a Fibre Channel connection, a Universal Serial Bus (USB), a PCIe Advanced Switching (PCIe-AS) bus, or the like. In various embodiments, the storage 140 may store data that is not directly addressable by the processor 115, but that may be accessed via one or more storage controllers. In certain embodiments, the storage 140 may be larger than the memory 130. In various embodiments, a storage 140 may include one or more types of storage media for storing data, such as a hard disk drive, NAND flash memory 142, MRAM 150, or the like. For example, in one embodiment, a storage 140 may include NAND flash memory 142. In another embodiment, a storage 140 may include MRAM 150. In a certain embodiment, a storage 140 may include a combination of NAND flash memory 142, MRAM 150, and/or other storage media types.

[0064] In various embodiments, MRAM 150 may be used to store data in a cache 120, memory 130, storage 140, and/or another component that stores data. For example, in the depicted embodiment, the computing device 110 includes MRAM 150 in the cache 120, memory 130, and storage 140. In another embodiment, a computing device 110 may use MRAM 150 for memory 130, and may use other types of memory or storage media for cache 120 or storage 140. Conversely, in another embodiment, a computing device 110 may use MRAM 150 for storage 140, and may use other types of memory media for cache 120 and memory 130. Additionally, some types of computing device 110 may include memory 130 without storage 140 (e.g., in a microcontroller) if the memory 130 is non-volatile, may include memory 130 without a cache 120 for specialized processors 115, or the like. Various combinations of cache 120, memory 130, and/or storage 140, and uses of MRAM 150 for cache 120, memory 130, storage 140, and/or other applications will be clear in view of this disclosure.

[0065] In various embodiments, the MRAM 150 may include one or more chips, packages, die, or other integrated circuit devices comprising magnetoresistive memory, disposed on one or more printed circuit boards, storage housings, and/or other mechanical and/or electrical support structures. For example, one or more dual inline memory modules (DIMMs), one or more expansion cards and/or daughter cards, a solid-state-drive (SSD) or other storage device, and/or another memory and/or storage form factor may comprise the MRAM 150. The MRAM 150 may be integrated with and/or mounted on a motherboard of the computing device 110, installed in a port and/or slot of the computing device 110, installed on a different computing device 110 and/or a dedicated storage appliance on a network, in communication with a computing device 110 over an external bus, or the like.

[0066] The MRAM 150, in various embodiments, may include one or more MRAM die, including a plurality of magnetic tunnel junctions (MTJs) for storing data. In certain embodiments, an MTJ includes a reference layer, a barrier layer, and a free layer. In further embodiments, a free layer may include a nucleation region and one or more arms. A nucleation region may be configured to form a magnetic domain wall, and an arm may include a plurality of pinning sites formed at predetermined locations along the arm for pinning the domain wall. In certain embodiments, an MTJ that includes a nucleation region and one or more arms with pinning sites may provide intermediate resistance states between a low resistance or parallel state and a high resistance or antiparallel state. In further embodiments, an MTJ or magnetic memory cell that provides more than two resistance states, or magnetization states, may be used to store more than one bit of data. For example, an MTJ that provides four resistance states may store two bits of data, so that the four states correspond to binary numbers 00, 01, 10, and 11. Similarly, an MTJ that provides eight resistance states may store three bits of data; an MTJ that provides sixteen resistance states may store four bits of data, and so on. MRAM 150 is described in further detail below with regard to FIGS. 2 through 10.

[0067] FIG. 2 depicts one embodiment of an MRAM die 150. The MRAM die 150 may be substantially similar to the MRAM 150 described with reference to FIG. 1. The MRAM die 150, in the depicted embodiment, includes an array 200 of MRAM cells, row circuits 202, column circuits 204, and a die controller 206.

[0068] In various embodiments, an MRAM die 150 may be an integrated circuit that includes both a core array 200 of memory cells (e.g., MTJs) for magnetoresistive data storage, and peripheral components (e.g., row circuits 202, column circuits 204, and/or die controller 206) for communicating with the array 200. In certain embodiments, one or more MRAM die 150 may be included in a memory module, a storage device, or the like.

[0069] In the depicted embodiment, the array 200 includes a plurality of memory cells (e.g., MRAM cells, MTJs, or the like). In one embodiment, the array 200 may be a two-dimensional array. In another embodiment, the array 200 may be a three-dimensional array that includes multiple planes and/or layers of MRAM cells. In various embodiments, the array 200 may be addressable by rows via row circuits 202, and by columns via column circuits 204.

[0070] The die controller 206, in certain embodiments, cooperates with the row circuits 202 and the column circuits 204 to perform memory operations on the array 200. In various embodiments, the die controller 206 may include components such as a power control circuit that controls the power and voltages supplied to the row circuits 202 and column circuits 204 during memory operations, an address decoder that translates a received address to a hardware address used by the row circuits 202 and column circuits 204, a state machine that implements and controls the memory operations, and the like. The die controller 206 may communicate with a computing device 110, a processor 115, a bus controller, a storage device controller, a memory module controller, or the like, via bus 208, to receive command and address information, transfer data, or the like.

[0071] FIG. 3 depicts a portion 300 of an artificial neural network, in one embodiment. In the depicted embodiment, a portion 300 of an artificial neural network includes an artificial neuron 306, and a plurality of synapses 304. Arrows in FIG. 3 represent the flow of information, from inputs 302 on the left, to an output 312 on the right.

[0072] In various embodiments, an artificial neuron 306 may be analogous to a biological neuron. A biological neuron may include a plurality of dendrites that receive excitatory or inhibitory signals across synapses, weighted by synaptic neurotransmitters, a soma where ions corresponding to the weighted excitatory or inhibitory signals mix, and an axon that transmits an output signal based on an electrical potential of the mixed ions. Similarly, an artificial neuron 306 may produce a signal at an output 312 (analogous to a biological axon) based on a summation of weighted inputs 302 (where the inputs are analogous to biological dendrites and the weighting is analogous to biological synapses).

[0073] In various embodiments, an artificial neural network may include a plurality of interconnected artificial neurons 306, analogous to interconnected biological neurons in a brain or nervous system. In various embodiments, artificial neurons 306 may receive inputs 302 from other artificial neurons 306 and/or from external sources. Similarly, the output 312 of an artificial neuron 306 may be provided to an external component, or may be provided to one or more further artificial neurons 306. Thus, the depicted portion 300, including an artificial neuron 306 and synapses 304 may be repeated many times in an artificial neural network.

[0074] In the depicted embodiment, the inputs 302 may receive binary or analog signals x.sub.1 through x.sub.n from other artificial neurons 306, or from sources external to an artificial network. For example, in one embodiment, an input 302 may receive a signal to be processed by artificial neural network. In a further embodiment, an input 302 may receive a signal from another artificial neuron 306. In a certain embodiment, an input 302 may be a bias input that is set to a fixed bias level (or to 1, so that the bias level is controlled by a synapse 304. Inputs 302 may be electrical lines, optical lines, or any other hardware capable of conveying the input signals x.sub.1 through x.sub.n.

[0075] Synapses 304, in various embodiments, provide weighted input signals to the artificial neuron 306. For example, the synapses 304 may provide a plurality of weights w.sub.1 through w.sub.n that are multiplied by corresponding input signals x.sub.1 through x.sub.n, so that the artificial neuron 306 receives a first weighted input w.sub.1x.sub.1, a second weighted input w.sub.2x.sub.2, and so on. In one embodiment, synapses 304 may include latches, registers, SRAM memory cells, volatile memory cells, non-volatile memory cells, or any other hardware capable of storing weights w.sub.1 through w.sub.n. In one embodiment, a synapse 304 may further include logic hardware for multiplying the input signals x.sub.1 through x.sub.n by the weights w.sub.1 through w.sub.n. In another embodiment, the synapses 304 may store the weights, and the multiplication may be performed by logic hardware separate from the synapses 304, such as a processor 115, an FPGA, an ASIC, a state machine, or the like. In another embodiment, the inputs x.sub.1 through x.sub.n may be binary inputs, or may be converted to binary by comparison to a threshold, and a synapse 304 for input x.sub.k may output a weight w.sub.k (e.g., the weight w.sub.k may be read from a synapse 304 storage location) if the input is 1, or may output a 0 (e.g., a read operation for synapse 304 storage locations does not read from that synapse 304) if the input is zero. Various further types and configurations of hardware for synapses 304 will be clear in view of this disclosure.

[0076] In the depicted embodiment, the artificial neuron 306 includes a summation component 308. The summation component 308, in various embodiments, may receive and sum the weighted input signals w.sub.1x.sub.1 through w.sub.nx.sub.n. The summation component 308 may include an adder, or any other hardware capable of summing inputs, or may be implemented by a processor 115 executing code. In a further embodiment, the artificial neuron 306 includes an activation component 310 that produces a signal at the output 312 based on the summed weighted input signals. The activation component 310 may output a function of the summed weighted input signals, such as a step function (for a perceptron), a sigmoid function (for a sigmoid neuron), a rectified linear function (for a ReLU neuron), or another non-linear function. In certain embodiments, the activation component 310 may produce an output signal as a function of the summed weighted input signals and of time. For example, the activation component 310 may output a spike that decays back to zero. The activation component 310 may include a comparator or other logic hardware to produce the output signal, or may be implemented by a processor 115 executing code. Various types and configurations of hardware for summation components 308 and activation components 310 will be clear in view of this disclosure.

[0077] In certain embodiments, an artificial neural network may include many portions similar to the depicted portion 300. For example, an artificial neural network may include a plurality of artificial neurons 306, and synapses 304 that store weights for couplings between artificial neurons 306. For example, in one embodiment, an artificial neural network may include a number N of artificial neurons 306, and an array of N*N synapses 304 that store weights for couplings between artificial neurons 306. A weight of zero may be equivalent to two corresponding artificial neurons 306 not being coupled together. A neuromorphic computing die may include artificial neurons 306 and an array of synapses 304.

[0078] FIG. 4 depicts one embodiment of a neuromorphic computing die 450. The neuromorphic computing die 450, in the depicted embodiment, includes a synapse array 400, row/axon circuits 402, column/dendrite circuits 404, a plurality of artificial neurons 410, and a die controller 206.

[0079] In various embodiments, the neuromorphic computing die 450 may be an integrated circuit that includes artificial neurons 410 and a synapse array 400, and peripheral circuits (e.g., row/axon circuits 402, column/dendrite circuits 404, and/or die controller 206) for computing using the artificial neurons 410. In various embodiments, one or more neuromorphic computing dies 450 may be included in a computing device 110, and may be used in place of, or in addition to, a processor 115.

[0080] A plurality of artificial neurons 410, in certain embodiments, may be substantially similar to the artificial neurons 306 described above with reference to FIG. 3, including summation components 308 and activation components 310. Similarly, the synapse array 400 may be an array of synapses 304, substantially as described above with reference to FIG. 3. The synapses 304 may store weights for connections between neurons 410. For example, a synapse 304 in row i and column j of the array 400 may store a weight that couples the output 312 (or axon) of neuron i to an input 302 (or dendrite) of neuron j. Thus, rows of the synapse array 400 may correspond to outputs 312 or axons, and columns of the array 400 may correspond to inputs 302 or dendrites. The synapse array 400 may be addressable by rows via row/axon circuits 402, and by columns via column/dendrite circuits 404. In one embodiment, the row/axon circuits 402 and column/dendrite circuits 404 may be substantially similar to the row circuits 202 and column circuits 204 of the MRAM die 150 described above with reference to FIG. 2. In a further embodiment, the synapse array 400, row/axon circuits 402, and column/dendrite circuits 404 may be transposable, so that a row of weights or a column of weights may be read or written together.

[0081] The die controller 206, may be substantially similar to the die controller 206 described above with reference to FIG. 2, and may communicate with a computing device 110, a processor 115, a bus controller, or the like, via bus 208, to receive commands and transfer data.

[0082] In various embodiments, the neuromorphic computing die 450 may compute by receiving inputs for the artificial neurons 410 via the bus 208, processing the inputs through a network of neurons 410 interconnected by synapses 304 of the synapse array 400 (as described above with reference to FIG. 3), and providing outputs via the bus 208. The die controller 206 may receive the inputs, provide the outputs, and may control the row/axon circuits 402 and column/dendrite circuits 404 to access or modify weights stored by the synapse array 400. The die controller 206 may modify weights according to a learning algorithm, or may use existing weights for computation.

[0083] As used herein, the term "neuromorphic" may refer to artificial neurons 410, to components associated with artificial neurons 410, such as synapses 304, or a synapse array 400, and to systems, apparatuses, or methods that include or use artificial neurons 410 for computation. Thus, referring to a computing die 450 as "neuromorphic" may indicate that the neuromorphic computing die uses an artificial neural network for computing instead of, or in addition to, logic hardware that executes instructions. Similarly, a "neuromorphic" computing array may include artificial neurons 410 and synapses 304 coupling the neurons, whether on a neuromorphic computing die 150, or as part of another computing device.

[0084] In general, in various embodiments, a neuromorphic computing device may compute by processing signals through a network of interconnected artificial neurons 410. Thus, the transformation of input signals to output signals may be based on the type and number of neurons 410, the connections between those neurons 410, and the synaptic weights stored in the synapse array 400. A neuromorphic computing device may be programmed by setting synaptic weights. In certain embodiments, a die controller 206 may apply a learning algorithm to iteratively set and adjust synaptic weights in the synapse array 400.

[0085] In certain embodiments, a synapse array 400 may be an array of storage cells or MRAM cells substantially similar to a storage array (e.g., the MRAM array 200 of FIG. 2). A synapse 304 may be a storage cell or set of storage cells that stores a synaptic weight, and may be said to "couple" two artificial neurons 306 if the output signal of one artificial neuron 306 is multiplied by the stored synaptic weight and provided as an input signal to another artificial neuron 306. Thus, a synapse 304 may be referred to as "coupling" two artificial neurons 306 based on a physical configuration that physically couples the output 312 of one artificial neuron 306 to an input 302 of another artificial neuron 306 via the synapse 304, or based on a logical configuration that references the synapse 304 when propagating an output signal of one artificial neuron 306 as an input signal to another artificial neuron 306. For example, a die controller 206 may read a synaptic weight from a synapse 304 at row i and column j of the synapse array 400, multiply the synaptic weight by the output signal of neuron i, and provide the weighted signal as an input signal to neuron j. The synapse 304 at row i and column j may then be referred to as "coupling" neuron i and neuron j, regardless of whether the synapse 304 is physically coupled to those artificial neurons 306.

[0086] A multi-weight synapse 304, in various embodiments, may be a synapse 304 that stores or represents multiple intermediate weight states between a lowest weight state and a highest weight state. Increasing the number of possible states, or possible synaptic weights per synapse 304 may increase computing capacity, robustness, and precision, for a given number of artificial neurons 306. In one embodiment, a multi-weight synapse 304 may include a plurality of single-bit storage cells, such as SRAM cells, SLC Flash cells, or the like, which each store one bit, either a 1 or a 0. In another embodiment, however, a multi-weight synapse 304 may include one or more multi-state memory cells. Although even a single-bit cell provides two states, corresponding to a 1 or a 0, the term "multi-state" cell is used herein to refer to a cell that provides more than two states, and that stores more than one bit per cell. For example, a multi-state cell may provide four states for storing two bits, eight states for storing three bits, sixteen states for storing four bits, or the like. For the same precision, a synapse array 400 that stores two bits per cell may be half the size or area of a synapse array 400 that stores one bit per cell.

[0087] In various embodiments, feed-forward classification for an artificial neural network involves reading and applying synaptic weights, and is facilitated by synapses 304 that can be read quickly, with low read energy, and with low read disturbance (e.g., without changing weights stored by other synapses 304). In further embodiments, back-propagated learning for an artificial neural network involves changing synaptic weights, and is facilitated by synapses 304 that provide fast write operations with low write energy, and with high endurance. MRAM memory cells based on magnetic tunnel junctions may provide fast, low-energy read and write operations, with high retention, high endurance, and low read disturbance. However, a synapse array 400 of two-state (parallel and antiparallel) magnetic tunnel junctions may use multiple cells to represent a multi-weight synapse 304, and may be large compared to an array of multi-state cells. Instead, in certain embodiments, a synapse array 400 may include multi-state magnetic memory cells (e.g., MTJs), as described with reference to subsequent Figures, as synapses 304, to provide the same precision as an array of two-state cells, with less area. In certain embodiments, multi-state MTJs may provide higher endurance than certain other types of multi-state resistive memory cells.

[0088] FIG. 5 depicts one embodiment of a magnetic tunnel junction 500. The MTJ 500, in certain embodiments, may be a magnetic memory cell, or may be part of a magnetic memory cell. A memory cell, in various embodiments, may be the smallest data-storing structure of a memory or storage medium or array, such as the MRAM array 200 or the synapse array 400, and may have a physical or electrical property that is configured to be modified, to store data. A range of possible values for the data-storing physical property may be divided into states, corresponding to data values. In further embodiments, a magnetic memory cell may be a memory cell that uses a magnetic physical property, such as a magnetic moment, a magnetization, or the like, to store data. In certain embodiments, a magnetic memory cell may include an MTJ 500, which may store data based on the magnetization or magnetic moment of a free layer 502 relative to a reference layer 506. In another embodiment, a magnetic memory cell may be a cell other than an MTJ 500, which uses magnetization to store data.

[0089] The MTJ 500, in the depicted embodiment, includes a free layer 502, a barrier layer 504, and a reference layer 506. Two terminals 522, 524 are depicted for convenience in discussing current flows. In certain embodiments, an MTJ 500 may include or be coupled to metallic or other conductive terminals 522, 524 for coupling the MTJ 500 to lines of an MRAM array 200. In another embodiment, however, lines of an array 200 may be directly coupled to the MTJ 500.

[0090] In various embodiments, layers of the MTJ 500 may be formed or deposited by various techniques such as physical vapor deposition, sputtering, or the like. In certain embodiments, further layers not shown in FIG. 5, such as pinning layers, pinned layers, capping layers, or seed layers, may be included in an MTJ 500, in a memory cell that includes an MTJ 500, or in the process of making an MTJ 500 or memory cell.

[0091] An MTJ 500, in the depicted embodiment, includes a fixed or reference layer 506 with a fixed or pinned magnetic moment, indicated by a single-headed arrow. In a further embodiment, an MTJ 500 includes a storage or free layer 502, with a magnetic moment that can be changed or switched, indicated by a double-headed arrow. A thin dielectric or barrier layer 504 may separate the reference layer 506 from the free layer 502, and current may flow across the barrier layer 504 due to quantum tunneling. The probability of an electron tunneling through the barrier layer 504 is higher if the magnetic moments of the reference layer 506 and the free layer 502 are substantially parallel to each other (referred to herein as the parallel state for the MTJ 500), and lower if the magnetic moments of the reference layer 506 and the free layer 502 are substantially antiparallel to each other (referred to herein as the antiparallel state for the MTJ 500). Therefore, an electrical resistance through the MTJ 500 may be higher in the antiparallel state than in the parallel state.

[0092] In various embodiments, a difference in resistance between parallel and antiparallel states of an MTJ 500 allows data to be stored. For example, a low resistance may correspond to a binary "1" and a high resistance may correspond to a binary "0," Alternatively, a low resistance may correspond to a binary "0" and a high resistance may correspond to a binary "1."

[0093] In certain embodiments, a magnetic storage or free layer 502 may be magnetized as a single domain, which may be magnetized parallel or antiparallel to the reference layer 506, corresponding to a low resistance state and a high resistance state for the MTJ 500. In further embodiments, a storage or free layer 502 may include two or more magnetic domains, with one or more domain walls between domains in the free layer 502, so that at least one domain is magnetized parallel to the reference layer 506 and at least one domain is magnetized antiparallel to the reference layer 506. In certain embodiments, a controller such as a die controller 206 may apply a write current that forms, moves, or removes a domain wall from the free layer 502. A resistance through the MTJ 500 when the free layer 502 includes multiple domains may correspond to a ratio between parallel-magnetized volume of the free layer 502 and antiparallel-magnetized volume of the free layer 502. Thus, a partially parallel and partially antiparallel free layer 502 may provide one or more intermediate resistance states for an MTJ 500, between a low resistance state and a high resistance state. For example, in one embodiment, four resistance states may correspond (in order from highest to lowest resistance) to antiparallel, mostly antiparallel, mostly parallel, and parallel states for the free layer 502. An MTJ 500 that provides intermediate resistance states may store or encode more than one bit. For example, an MTJ 500 that provides four states (e.g., two intermediate states between high and low resistance states) may encode two bits, so that the binary values 00, 01, 10, and 11 each correspond to one of the four states.

[0094] The fixed or reference layer 506, in one embodiment, includes a ferromagnetic material with a fixed or pinned magnetic moment. As used herein, the term "ferromagnetic" may be used to refer to any material capable of spontaneous magnetization (e.g., remaining magnetized in the absence of an externally applied magnetic field). Thus, a "ferromagnetic" material may refer to a strictly ferromagnetic material (e.g., for which individual microscopic magnetic moments are fully aligned), or to a ferrimagnetic material (e.g., for which individual microscopic magnetic moments are partially anti-aligned).

[0095] In various embodiments, a "fixed" or "pinned" magnetic moment refers to a magnetic moment that is substantially constant, at least in orientation, when the magnetic moment of the free layer 502 is changed. Thus, for example, in one embodiment, a reference layer 506 may comprise a ferromagnetic material with a higher coercivity than a ferromagnetic material of a free layer 502. In such an embodiment, an external magnetic field may change the magnetization of both the reference layer 506 and the free layer 502, but with a larger effect on the free layer 502. In another embodiment, a reference layer 506 may comprise a ferromagnetic thin film with a magnetic moment pinned by exchange coupling with an antiferromagnet. For example, in one embodiment, a reference layer 506 may include a synthetic antiferromagnet (e.g., a cobalt/iron and ruthenium multilayer), a ruthenium or iridium spacer, and a ferromagnetic layer comprising a cobalt/iron/boron alloy (CoFeB).

[0096] The magnetic moment of the reference layer 506, in various embodiments, may provide a reference for the orientation of one or more magnetic moments of the free layer 502. For example, in various embodiments, one or more magnetic moments for domains of the free layer 502 may be parallel or antiparallel to the magnetic moment of the reference layer 506. Thus, the reference layer 506 is depicted with a reference magnetic moment indicated by a single-headed arrow, and the parallel or antiparallel magnetic moment(s) of the free layer 502 are indicated by a double-headed arrow.

[0097] In the depicted embodiment, the magnetic moments of the reference layer 506 and the free layer 502 are in-plane magnetic moments. In another embodiment, however, the magnetic moments of the reference layer 506 and the free layer 502 are in-plane magnetic moments. As used herein, terms such as "in-plane" and "perpendicular" may be used to describe a direction or orientation (e.g., for a vector quantity such as a magnetic moment, magnetization, current density, or the like), relative to a layer of an MTJ 500. In one embodiment, the term "perpendicular" refers to a direction at right angles to a surface of a layer (e.g., vertically in FIG. 5), and the term "in-plane" refers to a direction parallel to a surface of the layer (e.g., horizontally in FIG. 5). In another embodiment, however, a vector, orientation, or direction may include a combination of perpendicular and in-plane components, and but may be described as either "perpendicular" or "in-plane" based on whether the perpendicular component or the in-plane component has a greater magnitude. For example, in one embodiment, where a magnetic moment includes non-zero in-plane and perpendicular components, it may nevertheless be described as an "in-plane" magnetic moment if the in-plane component is greater than the perpendicular component.

[0098] For example, in the depicted embodiment, with in-plane magnetic moments, a magnetic moment for the reference layer 506 may point toward the left of FIG. 5, so that a parallel magnetic moment for a domain of the free layer 502 points toward the left of FIG. 5, and an antiparallel magnetic moment for a domain of the free layer 502 points toward the right of FIG. 5. In another embodiment, with magnetic moments perpendicular to the layers, a magnetic moment for the reference layer 506 may point toward the top of FIG. 5, so that a parallel magnetic moment for a domain of the free layer 502 points toward the top of FIG. 5, and an antiparallel magnetic moment for a domain of the free layer 502 points toward the bottom of FIG. 5.

[0099] The barrier layer 504, in various embodiments, is disposed between the fixed or reference layer 506 and the free layer 502. In certain embodiments, the barrier layer 504 comprises a dielectric material, such as magnesium oxide (MgO). In certain embodiments, the barrier layer 504 may be less than 20 angstroms thick, so that quantum tunneling of electrons across the barrier layer 504 allows current to flow through the MTJ 500.

[0100] In general, in various embodiments, the free layer 502 may comprise a ferromagnetic material, for which the magnetic moment of the free layer 502 as a single domain, or the magnetic moments of one or more magnetic domains within the free layer 502, can be changed, switched, or flipped, relative to the magnetic moment of the reference layer 506. Changing the magnetic moment(s) of the free layer 502 changes the electrical resistance of the MTJ 500, allowing data to be stored. In certain embodiments, a ferromagnetic material of the free layer 502 may include a CoFeB alloy. In some embodiments, the free layer 502 may include multilayers based on transition metals like cobalt and iron, and noble metals such as platinum, palladium, and gold. Some examples include cobalt/palladium, cobalt/platinum and cobalt/nickel.

[0101] Reading data from an MTJ 500, in various embodiments, may include measuring, detecting, or sensing a resistance of the MTJ 500 (e.g., indicating whether the MTJ 500 is in a parallel, antiparallel, or intermediate state). For example, in one embodiment, a known voltage may be applied across a first terminal T1 522 and a second terminal T2 524, and the resulting current through the free layer 502, the barrier layer 504, and the reference layer 506 may be measured or sensed to detect the resistance of the MTJ 500. In another embodiment, a known current may be applied through the free layer 502, the barrier layer 504, and the reference layer 506, and the resulting voltage drop between the first terminal T1 522 and the second terminal T2 524 may be measured or sensed to detect the resistance. In certain embodiments, an MRAM array 200, MRAM die 150, neuromorphic computing die 450, or the like may include sense amplifiers, latches, and the like, to convert a low power signal to a logic level representing a data value, and to store the converted data.

[0102] Writing data to an MTJ 500, in various embodiments, may include setting or changing magnetization in the free layer 502 so that the MTJ 500 is in the desired parallel, intermediate, antiparallel state. Various types of MRAM provide various ways to set the magnetic moment of the free layer 502. In spin-transfer torque (STT) MRAM, data may be written by passing a spin-polarized electrical current through an MTJ 500 (e.g., between the first terminal T1 522 and the second terminal T2 524), to change magnetization in the free layer 502. By contrast, in spin-orbit torque (SOT) MRAM, data may be written by applying an electrical current through a spin Hall effect material adjacent to the free layer 502 (e.g., from a first write terminal T1 522, parallel to the free layer 502, to a second write terminal, not shown in FIG. 5), thus generating a pure spin current for changing magnetization in the free layer 502. In another embodiment, data may be written by applying a magnetic field to the free layer 502, and so that the applied field exerts a torque on magnetic moment(s) of the free layer 502. For example, in one embodiment, data may be written by applying an electrical current through one or more write wires or write lines near or adjacent to the free layer 502, so that the current produces a magnetic field around the write lines in accordance with Ampere's law.

[0103] In various embodiments, a controller, such as the die controller 206, may supply an electrical write current for writing data to the MTJ 500. In one embodiment, the write current may control a magnetic field applied to the free layer 502. In another embodiment, the write current may control a spin current injected into the free layer 502, either in the form of a spin-polarized electrical current for STT MRAM, or in the form of a pure spin current for SOT MRAM. For example, in one embodiment, the magnitude of the applied magnetic field, or of the injected spin current, may be proportional to the write current, or may increase with the write current. In a certain embodiment, increasing the write current may increase the applied magnetic field, or the injected spin current. Thus, in one embodiment, a controller may use different write currents to program an MTJ 500 to different resistance states. In another embodiment, reversing the write current may reverse the direction of the applied magnetic field, or the injected spin current. Thus, in one embodiment, a controller may apply write currents in different directions to increase or decrease the resistance of the MTJ 500.

[0104] Thus, in one embodiment, a die controller 206 for a memory array such as the MRAM array 200 may write or modify data by controlling write currents for memory cells or MTJs 500 in the array 200 via the row circuits 202 and the column circuits 204. Similarly, in another embodiment, a die controller 206 for a synapse array 400 may modify synapse weights for the synapse array 400 by controlling write currents for multi-state magnetic memory cells (e.g., MTJs 500) of the array via the row/axon circuits 402 and the column/dendrite circuits 404.

[0105] A controller may include or communicate with power generating components such as current sources, voltage sources, level shifters or the like, switching components such as transistors for coupling currents to MTJs 500, sensing components such as sense amplifiers, latches to store sense amplifier outputs, and the like.

[0106] FIG. 6A through FIG. 8 depict top views of various embodiments of free layers 600, 700, 800, for a magnetic tunnel junction 500 or multi-state magnetic memory cell. The free layers 600, 700, 800, in certain embodiments, may be substantially similar to the free layer 502 described above with reference to FIG. 5. For convenience in depicting the shape, outline, or configurations of the free layers 600, 700, 800, further layers of an MTJ 500 such as a barrier layer 504 or a reference layer 506 are not shown in FIG. 6A through FIG. 8.

[0107] In various embodiments, a shaped free layer that provides multiple resistance states for an MTJ 500, such as the free layer 600 of FIGS. 6A-6D, the free layer 700 of FIGS. 7A-7H, or the free layer 800 of FIG. 8, may be formed by various techniques such as physical vapor deposition, sputtering, and may be shaped by using lithography to control where ferromagnetic material is deposited, using e-beam milling to control where ferromagnetic material is removed, or the like. In one embodiment, layers such as a barrier layer 504 or a reference layer 506 may be shaped to match a free layer 600, 700, 800. For example, material addition and removal processes may be similar for the fixed or reference layer 506, the barrier layer 504 and the free layer 600, 700, 800, so that the reference layer 506, the barrier layer 504 and the free layer 600, 700, 800 are similarly shaped. In another embodiment, layers such as a barrier layer 504 or a reference layer 506 may be shaped to extend beneath (or above) the free layer 600, 700, 800, but may also extend beyond the edges of the free layer 600, 700, 800. For example, material addition processes may be similar for the fixed or reference layer 506, the barrier layer 504 and the free layer 600, 700, 800, but material removal processes may be carried out only for the free layer 600, 700, 800, so that the barrier layer 504 and the reference layer 506 occupy more area than the free layer 600, 700, 800. As another example, lithographic masks may be simpler for the reference layer 506 and the barrier layer 504 than for the free layer 600, 700, 800 so that a rectangular, oval or other simply-shaped reference layer 506 and barrier layer 504 extend beneath a free layer 600, 700, 800 with a more complicated shape. In an array 200, 400, the space between cells, and space where ferromagnetic material is removed (or omitted) from the free layer 600, 700, 800 may be left empty, may be filled with a non-ferromagnetic dielectric material to provide structural support for the cells while avoiding short circuits between cells, or the like.

[0108] In FIGS. 6A-7H, arrows represent the magnetization of the free layers 600, 700, or of domains within the free layers 600, 700. Additionally, in FIGS. 6A-7H, the magnetization of the fixed or reference layer 506 is to the right of the Figure, so that a left-pointing arrow represents an antiparallel state for a free layer 600, 700, or for a domain within the free layers 600, 700, and so that a right-pointing arrow represents a parallel state for a free layer 600, 700, or for a domain within the free layers 600, 700. However, the depicted and described magnetizations are for exemplary purposes, and are not intended as limiting. For example, a magnetization for a reference layer 506 may be in another in-plane or perpendicular direction, with corresponding parallel and antiparallel directions in free layers 600, 700.

[0109] FIGS. 6A-6D depict different resistance states for a free layer 600 of a magnetic tunnel junction 500 or multi-state magnetic memory cell, in one embodiment. In the depicted embodiment, the free layer 600 includes a nucleation region 602, a wall extension region 604, and a plurality of pinning sites 606, 608. FIGS. 6A through 6D depict resistance states in descending order from a high resistance state in FIG. 6A to a lower resistance state in FIG. 6D.

[0110] In certain embodiments, the free layer 600 may provide a plurality of resistance states for an MTJ 500: a high resistance state, where the free layer 600 is magnetized antiparallel to the reference layer 506; a low resistance state, where the free layer 600 is magnetized parallel to the reference layer 506; and a plurality of intermediate resistance states where the free layer 600 includes at least one magnetic domain magnetized parallel to the reference layer 506, at least one magnetic domain magnetized antiparallel to the reference layer 506, and at least one domain wall 650 separating parallel and antiparallel domains. In a further embodiment, the plurality of intermediate resistance states may correspond to positions of the domain wall 650 within the free layer 600 (e.g., within the wall extension region 604). In certain embodiments, if a free layer 600 is in a fully parallel or fully antiparallel state, without a domain wall 650, a write current or erase current from a controller may cause a magnetic domain to form or nucleate in the nucleation region 602. As the write or erase current continues, or increases, a domain wall 650 for the newly-formed domain may migrate as the domain expands to saturate the nucleation region 602, leaving a domain wall 650 in the wall extension region 604. A first pinning site 606 may pin the domain wall 650 at a predetermined location in the free layer 600, providing a consistent intermediate resistance state. Additional energy (e.g., from an increased write current) may unpin the domain wall 650 from a first pinning site 606, and move the domain wall 650 to a second pinning site 608, corresponding to a second intermediate resistance state.

[0111] In FIG. 6A, the free layer 600 is magnetized as a single domain, antiparallel to the magnetic moment of the reference layer 506. A domain, or magnetic domain, in various embodiments, may be a region of uniform or substantially uniform magnetization for a magnetic material. Within a domain, individual microscopic magnetic moments may be aligned for strictly ferromagnetic materials, or partially anti-aligned for ferrimagnetic materials, resulting in a net magnetic moment for the domain. A domain wall 650 (present in FIGS. 6B and 6C but not in FIG. 6A or 6D), in various embodiments, may be a boundary region between different domains of a magnetic material. Individual microscopic magnetic moments may transition across a domain wall 650, from being aligned with a magnetic moment for a first domain, to being aligned with a magnetic moment for a second domain on the opposite side of the domain wall 650. Within the domain wall 650, between domains with two different magnetic moments, individual microscopic magnetic moments may be aligned with neither magnetic moment, but may point in intermediate directions between the first magnetic moment and the second magnetic moment. Various types of domains, and domain walls 650, such as Bloch walls, Neel walls, and hybrid walls, will be clear in view of this disclosure.

[0112] Terms such as "parallel" and "antiparallel" may be used herein to refer to an orientation for the magnetic moment or magnetization of the free layer 600, 700, 800, or of a domain within the free layer 600, 700, 800, relative to the magnetic moment or magnetization of the reference layer 506. Thus, a "parallel" magnetic moment or magnetization for a domain, or for the free layer 600, 700, 800, refers to a magnetic moment or magnetization parallel to the magnetic moment of the reference layer 506, even if the magnetic moment of the reference layer 506 is not explicitly referred to. Similarly, the free layer 600, 700, 800, or a domain within the free layer 600, 700, 800 may be referred to as "parallel" or "antiparallel" based on a corresponding parallel or antiparallel magnetization, without explicit reference to the magnetic moment of the reference layer 506.

[0113] In FIG. 6A, the single-domain free layer 600 has an antiparallel magnetic moment, corresponding to a high resistance state for the MTJ 500. In certain embodiments, a write current from a controller, such as the die controller 206, may control a magnetic field applied to the free layer 600, or a spin current injected into the free layer 600, and a new domain, and domain wall 650, may form in the nucleation region 602 in response to the write current.

[0114] The nucleation region 602, in certain embodiments, may be a region of the free layer 600 that is configured to form a domain wall 650, or to facilitate formation of a domain wall 650. In certain embodiments, the nucleation region 602 may be larger, in at least one dimension, than a wall extension region 604. For example, in the depicted embodiment, the wall extension region 604 is an elongate arm or track, and the nucleation region 602 is a circular region with a diameter approximately three times the width of the elongate arm. In certain embodiments, the increased dimension of the nucleation region 602, relative to a dimension of the wall extension region 604 may facilitate formation of a domain wall 650 in the nucleation region 602 rather than in the wall extension region 604.

[0115] In certain embodiments, the nucleation region 602 may be a pad-shaped region of the free layer 600. An area, such as a region of a free layer 600 may be referred to as "elongate" if a length (or longest dimension) of the region is substantially greater than the width (or shortest dimension) of the region (e.g., five times longer, ten times longer, twenty times longer, or the like), or as "pad-shaped" if a length (or longest dimension) of the region is comparable to the width (or shortest dimension) of the region (e.g., equal to the width, less than double the width, less than triple the width, less than quadruple the width or the like). In certain embodiments, a pad-shaped region may be convex. For example, a pad-shaped region may be a circle, oval, triangle, square, rectangle, rounded rectangle, oblong, pentagon, hexagon, or the like. Various shapes and sizes of pad-shaped regions suitable for use as a nucleation region 602 of a free layer 600 will be clear in view of this disclosure.