Three-dimensional vertical NOR Flash Thin-Film Transistor Strings

Harari; Eli

U.S. patent application number 16/252301 was filed with the patent office on 2019-08-08 for three-dimensional vertical nor flash thin-film transistor strings. This patent application is currently assigned to SUNRISE MEMORY CORPORATION. The applicant listed for this patent is SUNRISE MEMORY CORPORATION. Invention is credited to Eli Harari.

| Application Number | 20190244971 16/252301 |

| Document ID | / |

| Family ID | 67475152 |

| Filed Date | 2019-08-08 |

View All Diagrams

| United States Patent Application | 20190244971 |

| Kind Code | A1 |

| Harari; Eli | August 8, 2019 |

Three-dimensional vertical NOR Flash Thin-Film Transistor Strings

Abstract

A memory structure, includes active columns of polysilicon formed above a semiconductor substrate, each active column includes one or more vertical NOR strings, with each NOR string having thin-film storage transistors sharing a local source line and a local bit line, the local bit line is connected by one segment of a segmented global bit line to a sense amplifier provided in the semiconductor substrate.

| Inventors: | Harari; Eli; (Saratoga, CA) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Assignee: | SUNRISE MEMORY CORPORATION Los Gatos CA |

||||||||||

| Family ID: | 67475152 | ||||||||||

| Appl. No.: | 16/252301 | ||||||||||

| Filed: | January 18, 2019 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 16107732 | Aug 21, 2018 | 10249370 | ||

| 16252301 | ||||

| 62625818 | Feb 2, 2018 | |||

| 62630214 | Feb 13, 2018 | |||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 27/11573 20130101; H01L 23/53257 20130101; G11C 16/0483 20130101; H01L 27/11582 20130101; G11C 16/26 20130101; G11C 16/30 20130101; H01L 27/11565 20130101; H01L 29/0649 20130101; H01L 29/78642 20130101; H01L 23/528 20130101; H01L 23/5329 20130101; H01L 27/1157 20130101; H01L 29/1037 20130101; H01L 23/5226 20130101; G11C 16/14 20130101 |

| International Class: | H01L 27/11582 20060101 H01L027/11582; H01L 29/10 20060101 H01L029/10; H01L 23/528 20060101 H01L023/528; H01L 29/786 20060101 H01L029/786; H01L 27/11573 20060101 H01L027/11573; H01L 27/1157 20060101 H01L027/1157; G11C 16/30 20060101 G11C016/30; G11C 16/14 20060101 G11C016/14; H01L 29/06 20060101 H01L029/06; H01L 23/532 20060101 H01L023/532; H01L 23/522 20060101 H01L023/522; H01L 27/11565 20060101 H01L027/11565; G11C 16/04 20060101 G11C016/04; G11C 16/26 20060101 G11C016/26 |

Claims

1. A memory structure, comprising: a semiconductor substrate having a substantially planar surface and including circuitry formed therein for memory circuit operation; a plurality of active columns of semiconducting material formed above the semiconductor substrate, each active column extending along a first direction orthogonal to the planar surface of semiconductor substrate and including a first heavily doped region, a second heavily doped region, and one or more lightly doped regions each adjacent both the first and second heavily doped regions, wherein the active columns are arranged in a two-dimensional array having rows of active columns extending along a second direction and rows of active columns extending along a third direction, the second direction and the third direction each being parallel to the planar surface of the semiconductor substrate; charge-trapping material provided over one or more surfaces of each active columns; and a plurality of word line conductors that are electrically isolated from each other provided between the active columns in a plurality of stacks, each stack extending lengthwise along the third direction, wherein the active columns, the charge-trapping material and the word line conductors together form a plurality of variable-threshold thin-film transistors, each variable-threshold thin-film transistor comprising an associated one of the word line conductors, a portion of the lightly doped region of an active column, the charge-trapping material between the portion of the lightly doped region and the word line conductor, and the first and second heavily doped regions; first and second pluralities of interconnection conductors running lengthwise along the second direction above and beneath the active columns, respectively, wherein (i) the first heavily doped region forms a local bit line and serves as a first drain or source terminal of the variable-threshold thin-film transistor, the local bit line being selectably connected to an associated one of the second plurality of interconnection conductors, (ii) the associated word line conductor serves as a gate terminal to provide a control voltage to the variable-threshold thin-film transistor; and (iii) the second heavily doped region forms a local source line and serves as a second drain or source terminal of the variable-threshold thin-film transistor, the local source line being connected to an associated one of the first plurality of interconnection conductors.

2. The memory structure of claim 1, wherein the second pluralities of interconnection conductors comprise a plurality of bit line segments beneath each row of active columns along the second direction, wherein the bit line segments are selectably electrically isolated from each other and each connect a predetermined number of local bit lines in the row of active columns.

3. The memory structure of claim 2, further comprising a plurality of regional bit line segments, wherein a plurality of bit line segments are selectably connected to each regional bit line segment.

4. The memory structure of claim 2, further comprising a plurality of segment-select transistors each selectably connecting a corresponding bit line segment to the circuitry in the semiconductor substrate.

5. The memory structure of claim 4, wherein the circuitry in the semiconductor substrate comprises at least a plurality of sense amplifiers distributed throughout the planar surface of the semiconductor substrate, the sense amplifiers being each connected by a different group of one or more segment-select transistors to corresponding bit line segments.

6. The memory structure of claim 4, wherein the segment-select transistors are formed in the semiconductor substrate.

7. The memory structure of claim 2, wherein each word line conductor provides gate terminals for variable-threshold thin-film transistors in active columns on opposite sides of the word line conductor, and wherein the local bit lines in adjacent active columns on opposite side of the word conductor are associated with different bit line segments.

8. The memory structure of claim 1, wherein the first pluralities of interconnection conductors comprise a plurality of source line segments above each row of active columns along the second direction, wherein the source line segments each connect a predetermined number of local source lines in the row of active columns.

9. The memory structure of claim 8, wherein the source line segments are selectably electrically isolated from each other.

10. The memory structure of claim 9, further comprising a global source line and a plurality of segment-select transistors, each segment-select transistor connecting a predetermined number of source line segments to the global source line.

11. The memory structure of claim 10, further comprising in each active column a pre-charge transistor for electrically connecting the local source line of the active column to the local bit line of the active column.

12. The memory structure of claim 11, wherein the local source lines connected by each source line segment provide a capacitance that serves as a virtual voltage source during a read, programming, program-inhibit or erase operation on one or more variable-threshold thin-film transistors in the active columns associated with the source line segment.

13. The memory structure of claim 8, further comprising a body bias voltage source in the semiconductor substrate, wherein the lightly doped region of each active column is connected to the body bias voltage source by a conductor above or below the active column.

14. The memory structure of claim 13, wherein the conductor above the active column comprises one of the first plurality of interconnection conductors.

15. The memory structure of claim 13, wherein the conductor above the active column is routed along the third direction.

16. The memory structure of claim 8 further comprising a plurality of charging columns each being associated with one of the source line segments, each charging column having first and second heavily doped regions structurally substantially the same as the first and second heavily doped regions of one of the active columns, wherein each charging column further comprises a plurality of pass transistors each selectably connecting the first and second heavily doped regions of the charging column, wherein at least one of the first and second heavily doped regions is connected to the circuitry in the semiconductor substrate.

17. The memory structure of claim 16, wherein each charging column is formed between two neighboring source line segments.

18. The memory structure of claim 16, wherein one or more of the word line conductors activate one or more of the pass transistors in one or more of the charge columns.

19. The memory structure of claim 18, further comprising a global source line that connects one or more of the word lines that activate one or more of the pass transistors in the one or more charge columns.

20. The memory structure of claim 16, wherein each charging column is connected to a voltage source in the semiconductor substrate by a segment-select transistor in the semiconductor substrate.

21. The memory structure of claim 20, wherein the voltage source supplies an erase voltage for a source line during an erase operation.

22. The memory structure of claim 1, wherein the active columns are isolated from each other by an isolation dielectric material or by an air gap.

23. The memory structure of claim 1, wherein the word line conductors in a stack are insulated from each other by an isolation dielectric material or air gap.

24. The memory structure of claim 1, wherein the variable-threshold thin-film transistors associated with each active column are organized in parallel into one or more NOR thin-film transistor strings.

25. The memory structure of claim 1, wherein the word line conductors in each stack at different positions along the first direction form steps of a stair-case structure and wherein each word line conductor is connected at the stair-case structure by vias to a corresponding one of the first or second pluralities of interconnection conductors.

26. The memory structure of claim 25, wherein selected word line conductors at selected steps of the stair-case structures in different stacks are connected to a selected one of the first or second pluralities of interconnection conductors.

27. A memory structure comprising first and second modular memory structures provided one on top of the other, wherein each modular memory structure comprises the memory structure of claim 25.

28. The memory structure of claim 27, wherein the first and second modular memory structures are isolated from each other by a dielectric layer.

29. The memory structure of claim 28, wherein active columns in the first and second modular memory structures are aligned along the first direction and wherein in local source lines of corresponding active columns are connected by vias through the dielectric layer.

30. The memory structure of claim 1, further comprising metallic pylons embedded in either one or both of the local source line and the local bit line of one or more active columns,

31. The memory structure of claim 30, wherein the metallic pylons each comprises one or more of titanium nitride, tungsten nitride or tungsten.

32. The memory structure of claim 31, wherein the metallic pylon is formed using an atomic layer deposition technique.

33. The memory structure of claim 1, wherein the lightly doped region in each active column comprises a first section and a second section, and wherein the first section of the lightly doped region serves as channel regions for the variable-threshold thin-film transistors of the active columns and wherein the second section of the lightly doped region has a dopant concentration multiple times that of the first section of the lightly doped region.

Description

CROSS REFERENCE TO RELATED APPLICATIONS

[0001] The present application is a continuation-in-part application of copending U.S. patent application ("Non-Provisional application I"), Ser. No. 16/107,732, entitled "Three-dimensional vertical NOR Flash Thin-Film Transistor Strings," filed on Aug. 21, 2018, which is a continuation application of U.S. patent application Ser. No. 15/837,734 entitled "Three-dimensional vertical NOR Flash Thin-Film Transistor Strings," filed on Dec. 11, 2017, now U.S. Pat. No. 10,096,364, which is a divisional application of U.S. patent application, Ser. No. 15/343,332, entitled "Three-dimensional vertical NOR Flash Thin-Film Transistor Strings," filed on Nov. 4, 2016, now U.S. Pat. No. 9,842,651, which claims priority of (i) U.S. provisional patent application ("Provisional application I"), Ser. No. 62/260,137, entitled "Three-dimensional Vertical NOR Flash Thin-film Transistor Strings," filed on Nov. 25, 2015; (ii) copending U.S. non-provisional patent application ("Non-Provisional application II"), Ser. No. 15/220,375, entitled "Multi-Gate NOR Flash Thin-film Transistor Strings Arranged in Stacked Horizontal Active Strips With Vertical Control Gates," filed on Jul. 26, 2016, now U.S. Pat. No. 9,892,800; and (iii) copending U.S. provisional patent application ("Provisional application II"), Ser. No. 62/363,189, entitled "Capacitive Coupled Non-Volatile Thin-film Transistor Strings," filed Jul. 15, 2016; and (iv) copending U.S. non-provisional patent application ("Non-Provisional patent application III"), Ser. No. 15/248,420, entitled "Capacitive Coupled Non-Volatile Thin-film Transistor Strings in Three-Dimensional Array," filed Aug. 26, 2016.

[0002] The present application is also related to and claims priority of U.S. provisional application ("Provisional application III"), Ser. No. 62/625,818, entitled "Three-dimensional vertical NOR Flash Thin-Film Transistor Strings," filed on Feb. 2, 2018 and U.S. provisional patent application ("Provisional application IV"), Ser. No. 62/630,214, entitled "Three-dimensional vertical NOR Flash Thin-Film Transistor Strings," filed on Feb. 13, 2018.

[0003] The disclosures of Provisional Applications I-IV and Non-Provisional application I-III are hereby incorporated by reference in their entireties.

BACKGROUND OF THE INVENTION

1. Field of the Invention

[0004] The present invention relates to high-density memory structures. In particular, the present invention relates to high-density memory structures formed by interconnected thin film storage elements, such as thin film storage transistors formed in vertical strips with horizontal word lines.

2. Discussion of the Related Art

[0005] In this disclosure, memory circuit structures are described. These structures may be fabricated on planar semiconductor substrates (e.g., silicon wafers) using conventional fabrication processes. To facilitate clarity in this description, the term "vertical" refers to the direction perpendicular to the surface of a semiconductor substrate, and the term "horizontal" refers to any direction that is parallel to the surface of that semiconductor substrate.

[0006] A number of high-density non-volatile memory structures, such as "three-dimensional vertical NAND strings," are known in the prior art. Many of these high-density memory structures are formed using thin film storage transistors formed out of deposited thin films (e.g., polysilicon thin films), and organized as arrays of "memory strings." One type of memory strings is referred to as NAND memory strings or simply "NAND strings". A NAND string consists of a number of series-connected thin film storage transistors ("TFTs"). Reading or programming the content of any of the series-connected TFTs requires activation of all series-connected TFTs in the string. Thin film NAND transistors have lower conductivity than NAND transistors formed in single crystal silicon, therefore the low read current that is required to be conducted through a long string of NAND TFTs results in a relatively slow read access (i.e. long latency).

[0007] Another type of high density memory structures is referred to as the NOR memory strings or "NOR strings." A NOR string includes a number of storage transistors each of which is connected to a shared source region and a shared drain region. Thus, the transistors in a NOR string are connected in parallel, so that a read current in a NOR string is conducted over a much lesser resistance than the read current through a NAND string. To read or program a storage transistor in a NOR string, only that storage transistor needs to be activated (i.e., "on" or conducting), all other storage transistors in the NOR string may remain dormant (i.e., "off" or non-conducting). Consequently, a NOR string allows much faster sensing of the activated storage transistor to be read. Conventional NOR transistors are programmed by a channel hot-electron injection technique, in which electrons are accelerated in the channel region by a voltage difference between the source region and the drain region and are injected into the charge-trapping layer between the control gate and the channel region, when an appropriate voltage is applied to the control gate. Channel hot-electron injection programming requires a relatively large electron current to flow through the channel region, therefore limiting the number of transistors that can be programmed in parallel. Unlike transistors that are programmed by hot-electron injection, in transistors that are programmed by Fowler-Nordheim tunneling or by direct tunneling, electrons are injected from the channel region to the charge-trapping layer by a high electric field that is applied between the control gate and the source and drain regions. Fowler-Nordheim tunneling and direct tunneling are orders of magnitude more efficient than channel hot-electron injection, allowing massively parallel programming; however, such tunneling is more susceptible to program-disturb conditions.

[0008] 3-Dimensional NOR memory arrays are disclosed in U.S. Pat. No. 8,630,114 to H. T Lue, entitled "Memory Architecture of 3D NOR Array", filed on Mar. 11, 2011 and issued on Jan. 14, 2014.

[0009] U.S. patent Application Publication US2016/0086970 A1 by Haibing Peng, entitled "Three-Dimensional Non-Volatile NOR-type Flash Memory," filed on Sep. 21, 2015 and published on Mar. 24, 2016, discloses non-volatile NOR flash memory devices consisting of arrays of basic NOR memory groups in which individual memory cells are stacked along a horizontal direction parallel to the semiconductor substrate with source and drain electrodes shared by all field effect transistors located at one or two opposite sides of the conduction channel.

[0010] Three-dimensional vertical memory structures are disclosed, for example, in U.S. Pat. No. 8,878,278 to Alsmeier et al. ("Alsmeier"), entitled "Compact Three-Dimensional Vertical NAND and Methods of Making Thereof," filed on Jan. 30, 2013 and issued on Nov. 4, 2014. Alsmeier discloses various types of high-density NAND memory structures, such as "terabit cell array transistor" (TCAT) NAND arrays (FIG. 1A), "pipe-shaped bit-cost scalable" (P--BiCS) flash memory (FIG. 1B) and a "vertical NAND" memory string structure. Likewise, U.S. Pat. No. 7,005,350 to Walker et al. ("Walker I"), entitled "Method for Fabricating Programmable Memory Array Structures Incorporating Series--Connected Transistor Strings," filed on Dec. 31, 2002 and issued on Feb. 28, 2006, also discloses a number of three-dimensional high-density NAND memory structures.

[0011] U.S. Pat. No. 7,612,411 to Walker ("Walker II"), entitled "Dual-Gate Device and Method" filed on Aug. 3, 2005 and issued on Nov. 3, 2009, discloses a "dual gate" memory structure, in which a common active region serves independently controlled storage elements in two NAND strings formed on opposite sides of the common active region.

[0012] 3-Dimensional NOR memory arrays are disclosed in U.S. Pat. No. 8,630,114 to H.T Lue, entitled "Memory Architecture of 3D NOR Array," filed on Mar. 11, 2011 and issued on Jan. 14, 2014.

[0013] A three-dimensional memory structure, including horizontal NAND strings that are controlled by vertical polysilicon gates, is disclosed in the article "Multi-layered Vertical gate NAND Flash Overcoming Stacking Limit for Terabit Density Storage" ("Kim"), by W. Kim et al., published in the 2009 Symposium on VLSI Tech. Dig. of Technical Papers, pp 188-189. Another three-dimensional memory structure, also including horizontal NAND strings with vertical polysilicon gates, is disclosed in the article, "A Highly Scalable 8-Layer 3D Vertical-gate (VG) TFT NAND Flash Using Junction-Free Buried Channel BE-SONOS Device," by H.T. Lue et al., published in the 2010 Symposium on VLSI: Tech. Dig. Of Technical Papers, pp. 131-132.

[0014] FIG. 1a shows three-dimensional vertical NAND strings 111 and 112 in the prior art. FIG. 1b shows basic circuit representation 140 of a three-dimensional vertical NAND string in the prior art. Specifically, vertical NAND string 111 and 112 of FIG. 1a and their circuit representation 150 are each essentially a conventional horizontal NAND string which--rather than each connecting 32 or more transistors in series along the surface of a substrate--is rotated 90 degrees, so as to be perpendicular to the substrate. Vertical NAND strings 111 and 112 are serially-connected thin-film transistors (TFTs) in a string configuration that rises like a skyscraper from the substrate, with each TFT having a storage element and a control gate provided by one of the word line conductors in an adjacent stack of word line conductors. As shown in FIG. 1b, in the simplest implementation of a vertical NAND string, TFTs 15 and 16 are the first and last memory transistors of NAND string 150, controlled by separate word lines WL0 and WL31, respectively. Bit line select transistor 11, activated by signal BLS, and ground select transistor 12, activated by signal SS, serve to connect an addressed TFT in vertical NAND string 150 to corresponding global bit line GBL at terminal 14 and global source line (ground) GSL, at terminal 13, during read, program, program-inhibit and erase operations. Reading or programming the content of any one TFT, (e.g., TFT 17) requires activation of all 32 TFTs in vertical NAND string 150, which exposes each TFT to read-disturb and program-disturb conditions. Such conditions limit the number of TFTs that can be provided in a vertical NAND string to no more than 64 or 128 TFTs. Furthermore, the polysilicon thin films upon which a vertical NAND string is formed have much lower channel mobility--and therefore higher resistivity--than conventional NAND strings formed in a single-crystal silicon substrate, thereby resulting in a low read current relative to the read current of a conventional NAND string.

[0015] U.S. Patent Application Publication 2011/0298013 ("Hwang"), entitled "Vertical Structure Semiconductor Memory Devices And Methods OF Manufacturing. The Same," discloses three-dimensional vertical NAND strings. In its FIG. 4D, Hwang shows a block of three dimensional vertical NAND strings addressed by wrap-around stacked word lines 150 (reproduced herein as FIG. 1c).

[0016] U.S. Pat. No. 5,768,192 to Eitan, entitled "Memory Cell utilizing asymmetrical charge trapping" filed Jul. 23, 1996 and issued Jun. 16, 1998 discloses NROM type memory transistor operation of the type employed in an embodiment of the current invention.

[0017] U.S. Pat. No. 8,026,521 to Zvi Or-Bach et al, entitled "Semiconductor Device and Structure," filed on Oct. 11, 2010 and issued on Sep. 27, 2011 to Zvi-Or Bach et al discloses a first layer and a second layer of layer-transferred mono-crystallized silicon in which the first and second layers include horizontally oriented transistors. In that structure, the second layer of horizontally oriented transistors overlays the first layer of horizontally oriented transistors, each group of horizontally oriented transistors having side gates.

[0018] Transistors that have a conventional non-volatile memory transistor structure but short retention times may be referred to as "quasi-volatile." In this context, conventional non-volatile memories have data retention time exceeding tens of years. A planar quasi-volatile memory transistor on single crystal silicon substrate is disclosed in the article "High-Endurance Ultra-Thin Tunnel Oxide in Monos Device Structure for Dynamic Memory application", by H. C. Wann and C. Hu, published in IEEE Electron Device letters, Vol. 16, No. 11, November 1995, pp 491-493. A quasi-volatile 3-D NOR array with quasi-volatile memory is disclosed in the U.S. Pat. No. 8,630,114 to H. T Lue, mentioned above.

[0019] The Article "A 768 Gb 3b/cell 3D-Floating-Gate NAND Flash Memory," by T. Tanaka et al., published in the Digest of Technical Papers, the 2016 IEEE International Solid-State Circuits Conference, pp. 142-144, discloses placing CMOS logic circuits underneath a 3-dimensional NAND memory array.

SUMMARY

[0020] According to one embodiment of the present invention, a high-density memory structure, referred to as a three-dimensional vertical NOR Flash memory string ("multi-gate vertical NOR string," or simply "vertical NOR string"). The vertical NOR string includes a number of thin-film transistors ("TFTs") connected in parallel, having a shared source region and a shared drain region each extending generally in a vertical direction. In addition, the vertical NOR string includes multiple horizontal control gates each controlling a respective one of the TFTs in the vertical NOR string. As the TFTs in a vertical NOR string are connected in parallel, a read current in a vertical NOR string is conducted over a much lesser resistance than the read current through a NAND string of a comparable number of TFTs. To read or program any one of the TFTs in a vertical NOR string, only that TFT needs to be activated, all other TFTs in the vertical NOR string can remain non-conducting.

[0021] Consequently, a vertical NOR string may include many more TFTs (e.g., several hundreds or more), while allowing faster sensing and minimizing program-disturb or read-disturb conditions.

[0022] In one embodiment, the shared drain region of a vertical NOR string is connected to a global bit line ("voltage V.sub.bl") and the shared source region of the vertical NOR string is connected to a global source line ("voltage V.sub.ss"). Alternatively, in a second embodiment, only the shared drain region is connected to a global bit line biased to a supply voltage, while the shared source region is pre-charged to a voltage determined by a quantity of charge in the shared source region. To perform the pre-charge, one or more dedicated TFTs may be provided to pre-charge the parasitic capacitance C of the shared source region.

[0023] According to one embodiment of the present invention, multi-gate NOR flash thin-film transistor string arrays ("multi-gate NOR string arrays") are organized as arrays of vertical NOR strings each running perpendicular to the surface of a silicon substrate. Each multi-gate NOR string array includes a number of vertical active columns arranged in rows, each row extending along a first horizontal direction, with each active column having two vertical heavily-doped polysilicon regions of a first conductivity, which are separated by one or more vertical polysilicon regions that are undoped or lightly doped to a second conductivity. The heavily-doped regions each form a shared source or drain region and, in conjunction with one or more stacks of horizontal conductors each extending orthogonally to the first horizontal direction, the lightly-doped regions each form multiple channel regions. A charge-trapping material forms multiple storage elements, covering at least the channel regions of TFTs in the active column. The horizontal conductive lines in each stack are electrically isolated from each other and form control gates over the storage elements and the channel regions of the active column. In this manner, the multi-gate NOR string array forms a three-dimensional array of storage TFTs.

[0024] In one embodiment, support circuitry is formed in a semiconductor substrate to support multiple multi-gate NOR string arrays formed above the support circuitry and the semiconductor substrate. The support circuitry may include address encoders, address decoders, sense amplifiers, input/output drivers, shift registers, latches, reference cells, power supply lines, bias and reference voltage generators, inverters, NAND, NOR, Exclusive-Or and other logic gates, other memory elements, sequencers and state machines, among others. The multi-gate NOR string arrays may be organized as multiple blocks of circuits, with each block having multiple multi-gate NOR string arrays.

[0025] According to embodiments of the present invention, variations in threshold voltages of TFTs within a vertical NOR string may be compensated by providing one or more electrically programmable reference vertical NOR strings in the same or another multi-gate vertical NOR string array. Background leakage currents inherent to a vertical NOR string can be substantially neutralized during a read operation by comparing the results of the TFT being read to that of a TFT that is concurrently read on a programmable reference vertical NOR string. In some embodiments, each TFT of a vertical NOR string is shaped so as to amplify the capacitive coupling between each control gate and its corresponding channel region thereby to enhance tunneling from the channel regions into the charge-trapping material (i.e., the storage element) during programming, and to reduce the charge injection from the control gate to the charge-trapping material during erasing. This favorable capacitive coupling is particularly useful for storing more than one bit in each TFT of a vertical NOR string. In another embodiment, the charge-trapping material of each TFT may have its structure modified to provide a high write/erase cycle endurance, albeit at a lower retention time that requires refreshing of the stored data. However, as the refreshing required of a vertical NOR string array is expected to be much less frequently than in a conventional dynamic random-access memory (DRAM), the multi-gate NOR string arrays of the present invention may operate in some DRAM applications. Such use of the vertical NOR strings allows a substantially lower cost-per-bit figure of merit, as compared to conventional DRAMs, and a substantially lower read-latency, as compared to conventional NAND string arrays.

[0026] In another embodiment the vertical NOR string can be programmed, erased and read as NROM/Mirror-bit TFT string.

[0027] Organizing the TFTs as vertical NOR strings--rather than the prior art vertical NAND strings--results in (i) a reduced read-latency that can approach that of a dynamic random access memory (DRAM) array, (ii) reduced sensitivities to read-disturb and program-disturb conditions that are associated with long NAND Flash strings, and (iii) reduced cost per bit, as compared to a NAND Flash string.

[0028] According to an alternative embodiment of the present invention, each active column in the memory structure includes one or more vertical NOR strings, with each NOR string having thin-film storage transistors sharing a local source line and a local bit line, the local bit line is connected by one segment of a segmented global bit line to a sense amplifier provided in the semiconductor substrate. To significantly reduce the read sense latency, rather than a global bit line that spans a substantial distance (e.g., between a half to the complete length of the chip), multiple, shorter global bit line segments are provided. Each such global segment connects one or more neighboring local bit lines through a segment connector to a segment sense amplifier provided in the semiconductor substrate. In embodiments in which the local source lines are pre-charged to a virtual ground voltage (e.g., V.sub.ss), the parasitic capacitance of the virtual ground is increased substantially by providing a short global source line segment connector which connects a group of neighboring local source lines into one local source line segment. The number of local source lines included in the segment determines the combined parasitic capacitance (C).

[0029] The present invention is better understood upon consideration of the detailed description below, in conjunction with the accompanying drawings.

BRIEF DESCRIPTION OF THE DRAWINGS

[0030] FIG. 1a shows three-dimensional vertical NAND strings 111 and 112 in the prior art.

[0031] FIG. 1b shows basic circuit representation 140 of a three-dimensional vertical NAND string in the prior art.

[0032] FIG. 1c shows a three-dimensional representation of a block of three-dimensional vertical NAND strings addressed by wrap-around stacked word lines 150.

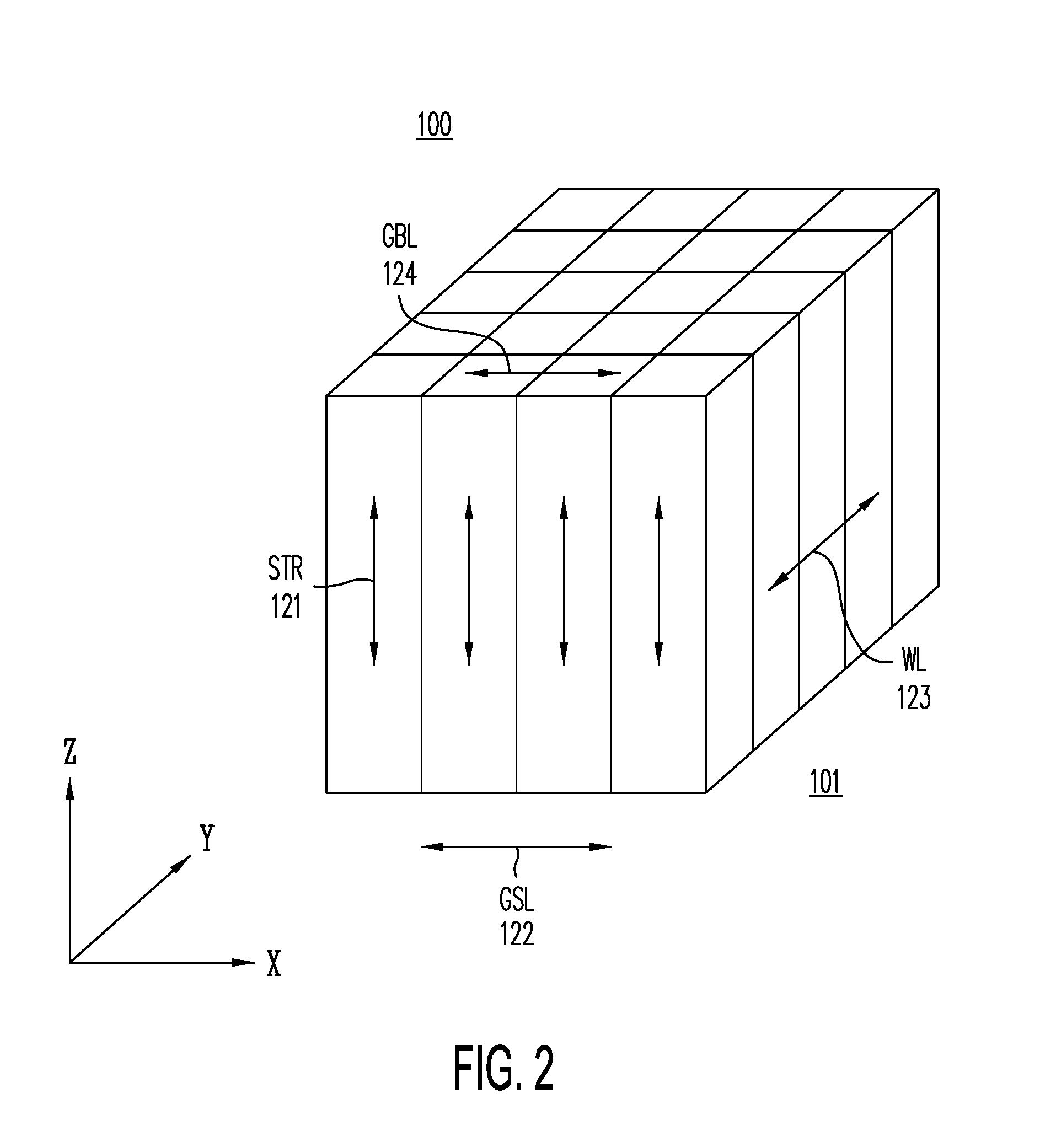

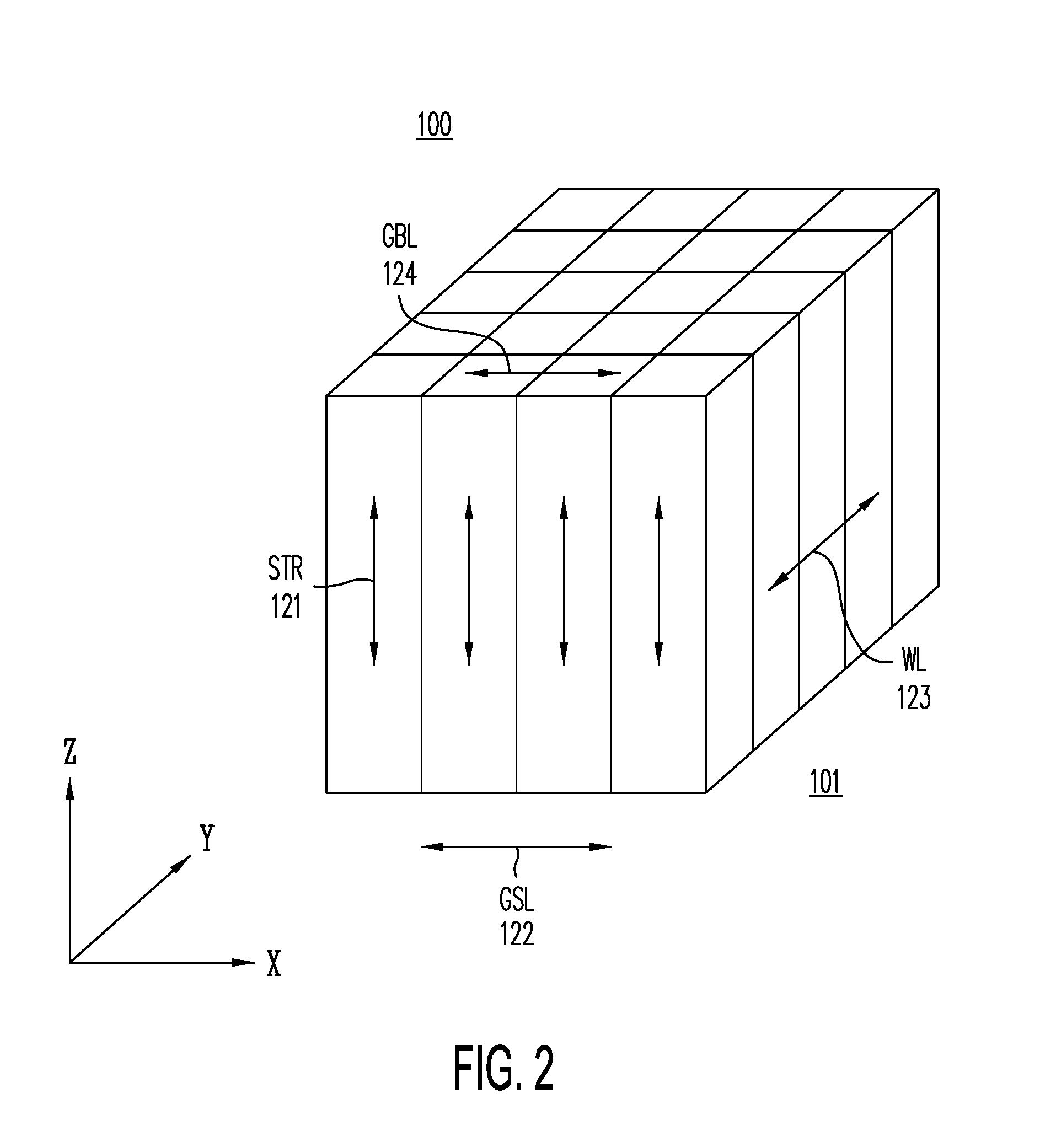

[0033] FIG. 2 shows conceptualized memory structure 100, which illustrates a 3-dimensional organization of memory cells; the memory cells are provided in vertical NOR strings, with each vertical NOR string having memory cells each being controlled by one of a number of horizontal word lines, according to one embodiment of the present invention.

[0034] FIG. 3a shows a basic circuit representation in a Z-Y plane of vertical NOR string 300 formed in an active column; vertical NOR string 300 represents a three-dimensional arrangement of non-volatile storage TFTs, with each TFT sharing local source line (LSL) 355 and local bit line (LBL) 354, being accessed respectively by global bit line (GBL) 314 and global source line (GSL) 313 according to one embodiment of the current invention.

[0035] FIG. 3b shows a basic circuit representation in a Z-Y plane of vertical NOR string 305 formed in an active column; vertical NOR string 305 represents a three-dimensional arrangement of non-volatile storage TFTs, including a dedicated pre-charge TFT 370 for setting a voltage ("V.sub.ss") on shared local source line 355, which has a parasitic capacitance C, according to one embodiment of the present invention.

[0036] FIG. 3c shows a basic circuit representation of dynamic non-volatile storage transistor 317 having one or more programmed threshold voltages and connected to parasitic capacitor 360; capacitor 360 is pre-charged to temporarily hold a virtual voltage V.sub.ss on source terminal 355 so as to allow the threshold voltage of transistor 317 to be dynamically detected by the discharging of voltage V.sub.ss, when control gate 323p is raised to a voltage that exceeds the threshold voltage.

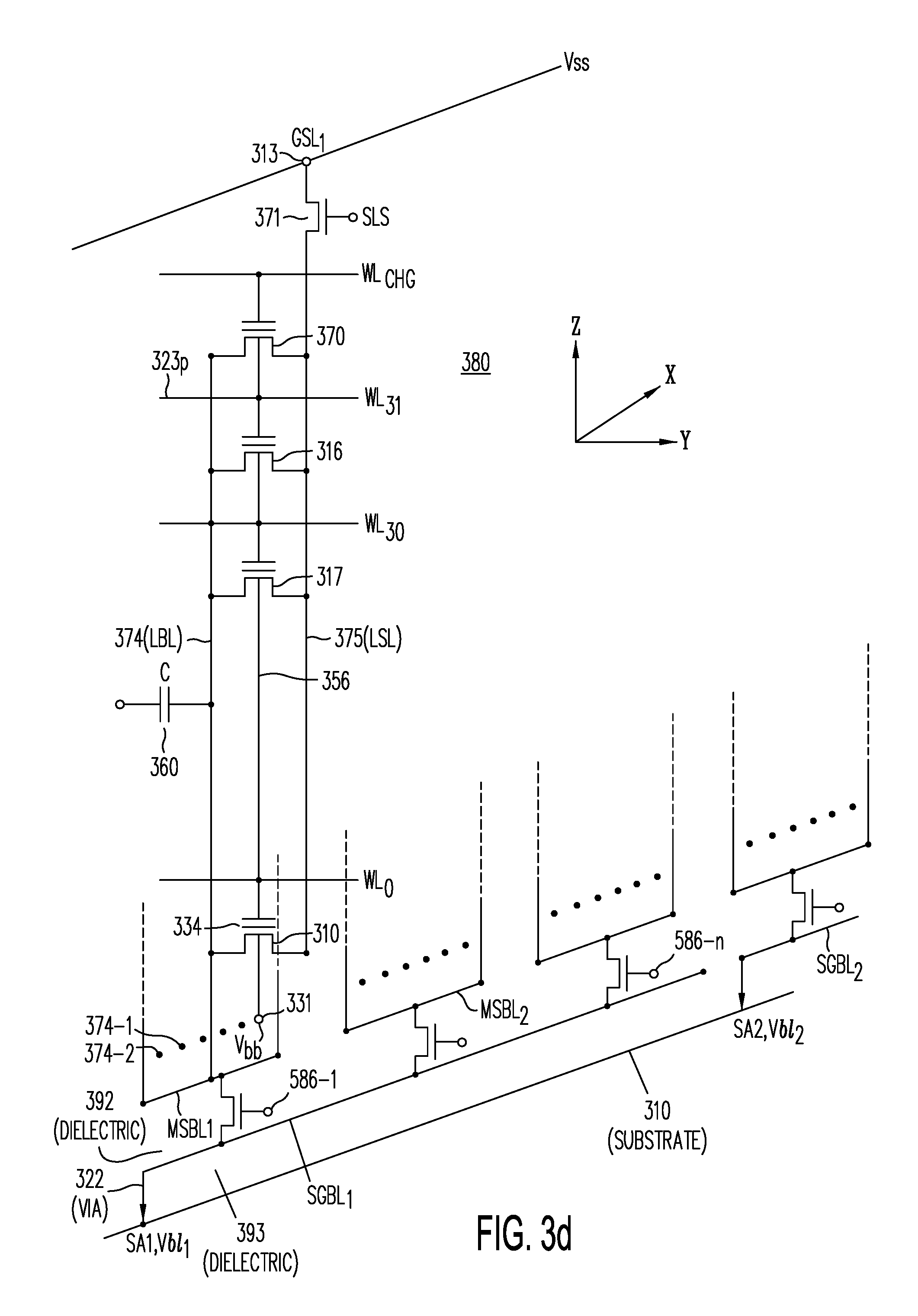

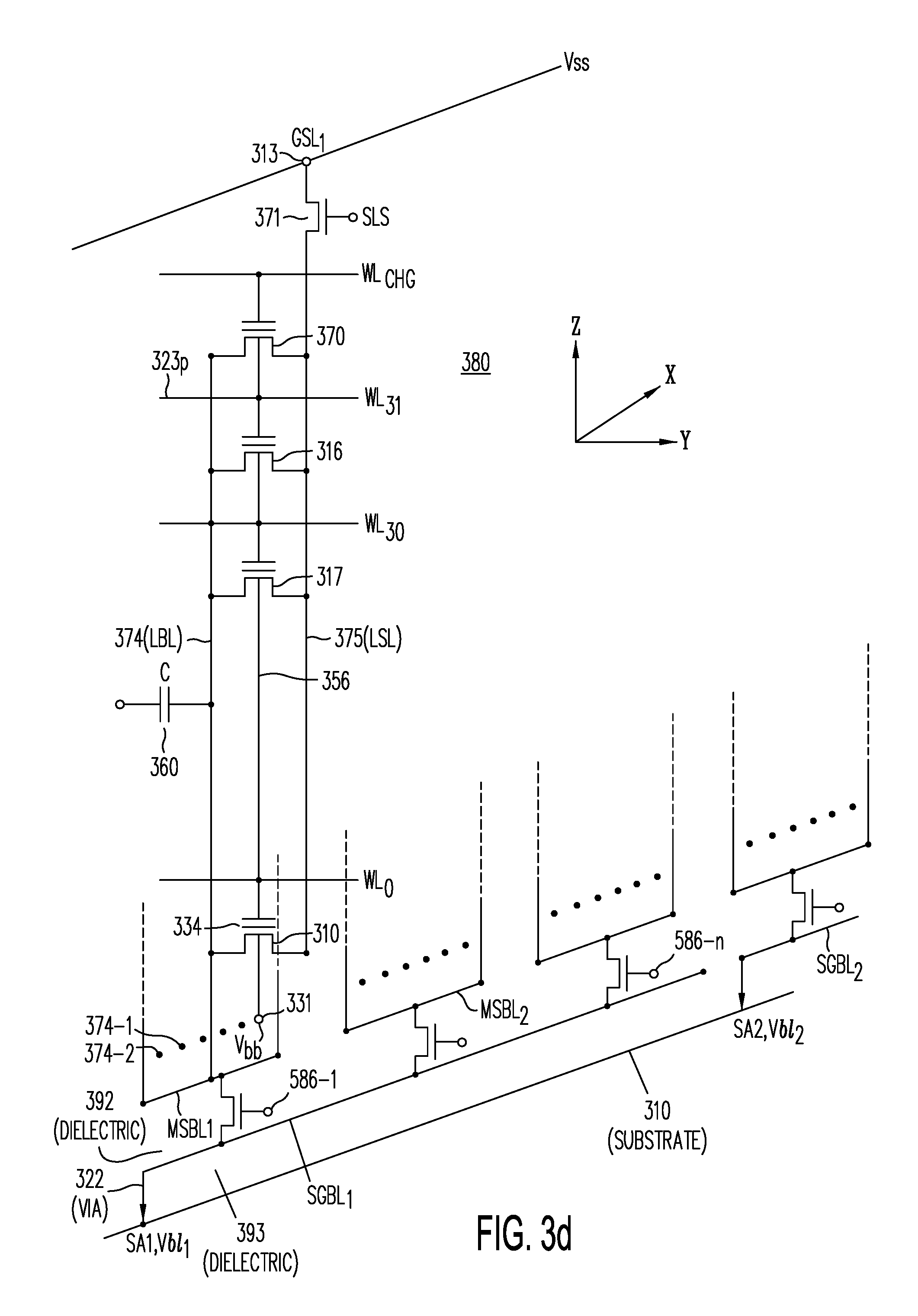

[0037] FIG. 3d shows a variation of the vertical NOR memory array circuit architecture in the embodiment of FIG. 3a, in which global bit line (GBL) 314 is replaced by bit line segments MSBL.sub.1, MSBL.sub.2, . . . , each connecting multiple neighboring local vertical bit lines 374-1, 374-2, . . . ; the segments are in turn connected through segment-select thin-film transistors 586-1, . . . , 586-n to regional bit line segments SGBL.sub.1, SGBL.sub.2, . . . that are each associated with multiple bit line segments, and that are isolated by dielectric 393 from the sense amplifiers and other circuitry in silicon substrate 310 below them.

[0038] FIG. 3e shows a variation in the circuit architecture in the embodiment of FIG. 3d, in which global source-select line 313 accesses, through source-select transistor SLS.sub.1, a group of neighboring vertical local source lines 375-1, 375-2, . . . that are associated with source line segment MSSL.sub.1.

[0039] FIG. 3f shows a variation in circuit architecture in the embodiment of FIG. 3e, in which global source line 313 is eliminated and replaced by local source line segment MSSL.sub.1 connecting vertical local source lines 375-1, 375-2, . . . , which are charged and held at virtual ground voltage Vss through pre-charge transistors (e.g., pre-charge transistor 370).

[0040] FIG. 3g shows a variation in circuit architecture in the embodiment of FIG. 3f, in which regional bit line segments SGBL.sub.1, SGBL.sub.2, . . . , are merged with bit line segments MSBL.sub.1, MSBL.sub.2, . . . , and are connected through vias 322 to segment-select transistors 315-1, 315-2 . . . , which are located in the substrate (thereby replacing segment-select thin-film transistors 586-1, 586-2, . . . , of FIG. 3d.

[0041] FIG. 3h shows a circuit architecture of the embodiment in FIG. 3g, in which two neighboring bit line segments MSBL.sub.1, MSBL.sub.2 have their local source line segments MSSL.sub.1, MSSL.sub.2 connected from substrate 310 through dedicated active vertical column 381 formed in the space labeled BL0 between the two bit line segments.

[0042] FIGS. 3i and 3i-1 (the the key to 3i and 3i-1) is show a top X-Y plane view of the embodiment of FIG. 3h, in which each vertical local source line in source segment MSSL.sub.1 is held at voltage Vss or Vbl supplied through column 381.

[0043] FIG. 4a is a cross section in a Z-Y plane showing side-by-side active columns 431 and 432, each of which may form a vertical NOR string that has a basic circuit representation illustrated in either FIG. 3a or FIG. 3b, according to one embodiment of the present invention.

[0044] FIG. 4a-1 is a top view of a vertical NOR string of FIG. 4a, in which the conductivity of the vertical local source line or drain line is enhanced by including metallic material 420(M) in the core of the pillars of the local source line or drain line.

[0045] FIG. 4b is a cross section in the Z-X plane showing active columns 430R, 430L, 431R and 431L, charge-trapping layers 432 and 434, and word lines 423p-L and 423p-R, according to one embodiment of the present invention.

[0046] FIG. 4c shows a basic circuit representation in the Z-X plane of vertical NOR string pairs 491 and 492, according to one embodiment of the present invention.

[0047] FIG. 5a is a cross section in the Z-Y plane showing connections of a vertical NOR string of active column 531 to global bit line 514-1 (GBL.sub.1), global source line 507 (GSL.sub.1), and common body bias source 506 (V.sub.bb), according to one embodiment of the present invention.

[0048] FIG. 5b is a cross section in the Z-Y plane showing, according to one embodiment of the present invention, connection of body region 556 (providing the P.sup.- channel material) to conductive pillar 591, which is formed in dielectric layer 592 out of P.sup.+ polysilicon, for example, to conductor 590 provided above active column 581 and running parallel to the word lines; conductor 590 receives body bias voltage V.sub.bb from voltage source 594 in substrate 505 through via 593 in an opening through dielectric isolation 509.

[0049] FIG. 6a is a cross section in the X-Y plane showing, according to one embodiment of the present invention, TFT 685 (T.sub.L) of vertical NOR string 451a and TFT 684 (T.sub.R) of vertical NOR string 451b in vertical NOR string pair 491, as discussed in conjunction with FIG. 4c; in FIG. 6a, global bit line 614-1 accesses alternate ones of local bit lines LBL-1, and predetermined curvature 675 of transistor channel 656L amplifies the capacitive coupling between each control gate and the corresponding channel during programming

[0050] FIG. 6b is a cross section in the X-Y plane showing, according to one embodiment of the current invention, TFT 685(T.sub.L) of vertical NOR string 451a sharing an active region with TFT 684 (T.sub.R) of vertical NOR string 451b in vertical NOR string pair 491, as discussed in conjunction with FIG. 4c; in FIG. 6b, global bit line 614-1 accesses alternate (odd) ones of local bit lines 654 (LBL-1), global bit line 614-2 addresses alternate (even) ones of local bit lines 657-2 (LBL-2), local source lines LSL-1 and LSL-2 are pre-charged to provide virtual supply voltage V.sub.ss.

[0051] FIG. 6c is a cross section in the X-Y plane showing, in accordance with one embodiment of the current invention, dedicated word line stacks 623p, each having word lines each surrounding ("wrapping around") a TFT of a vertical NOR string, and local vertical pillar bit line 654 (extending along the Z-direction) and local vertical pillar source line 655 (extending along the Z-direction), which are accessed by global horizontal bit line 614 and global horizontal source line 615, respectively; in FIG. 6c, adjacent word line stacks 623p are isolated from each other by air gap 610 or another dielectric isolation.

[0052] FIG. 6d is a cross section in the X-Y plan showing, according to the embodiment of the present invention, staggered close-packing of vertical NOR strings, similar to those shown in FIG. 6c, sharing word-line stacks 623p and with pre-charged parasitic capacitors 660 each providing a pre-charged virtual V.sub.ss supply voltage.

[0053] FIG. 6e shows in the X-Y plane providing body bias voltage V.sub.bb (e.g., through conductors 690-1 and 690-2) that is shared between body regions 656 (L+R) in adjacent rows of active columns, using the layout of the embodiment shown in FIG. 6b.

[0054] FIG. 6f illustrates one implementation of global word lines for connecting the local word lines on one plane (i.e., at one stair-case step) in conjunction with the bit line segmentation scheme of the present invention.

[0055] FIG. 6g illustrates one implementation of a vertical NOR string memory array that avoids doubling of the silicon area taken up by word line stair-case steps when the number of layers of storage transistors are doubled in the vertical direction, according to one embodiment of the present invention.

[0056] FIGS. 7a, 7b, 7c and 7d are cross sections of intermediate structures formed in a fabrication process for a multi-gate NOR string array, in accordance with one embodiment of the present invention.

[0057] FIG. 7d-1 shows in the X-Y plane the inclusion of conductive material 720(M) at the core of vertical pillars of the local source line or local bit line.

[0058] FIG. 8a is a schematic representation of a read operation for embodiments where the local source line (LSL) of a vertical NOR string is hard-wired; in FIG. 8a, "WLs" represents the voltage on the selected word line, and all non-select word lines ("WL.sub.NS") in the vertical NOR string are set at 0V during the read operation.

[0059] FIG. 8b is a schematic representation of a read operation for embodiments where the local source line is floating at pre-charge virtual voltage V.sub.ss; in FIG. 8b, "WL.sub.CHG" represents the gate voltage on the pre-charge transistor (e.g., pre-charge transistor 317 or 370 in FIG. 3c).

DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0060] FIG. 2 shows conceptualized memory structure 100, which illustrates a 3-dimensional organization of memory cells (or storage elements) provided in vertical NOR strings. In conceptualized memory structure 100, each vertical NOR string includes memory cells that are each controlled by a corresponding horizontal word line, according to one embodiment of the present invention. In conceptualized memory structure 100, each memory cell is formed in deposited thin films provided "vertically", i.e., along a direction perpendicular to the surface of substrate layer 101. Substrate layer 101 may be, for example, a conventional silicon wafer used for fabricating integrated circuits, familiar to those of ordinary skill in the art. In this detailed description, a Cartesian coordinate system (such as indicated in FIG. 2) is adopted solely for the purpose of facilitating discussion. Under this coordinate system, the surface of substrate layer 101 is considered a plane which is parallel to the X-Y plane. Thus, as used in this description, the term "horizontal" refers to any direction parallel to the X-Y plane, while "vertical" refers to the Z-direction.

[0061] In FIG. 2, each vertical column in the Z-direction represents storage elements or TFTs in a vertical NOR string (e.g., vertical NOR string 121). The vertical NOR strings are arranged in a regular manner in rows each extending along the X-direction. (Of course, the same arrangement may also be seen alternatively as an arrangement of rows each extending along the Y-directions). The storage elements of a vertical NOR string share a vertical local source line and a vertical local bit line (not shown). A stack of horizontal word lines (e.g., WL 123) run along the Y-direction, with each word line serving as control gates for corresponding TFTs of vertical NOR strings located adjacent the word line along the Y-direction. Global source lines (e.g., GSL 122) and global bit lines (e.g., GBL 124) are provided along the X-direction generally running either below the bottom of or on top of conceptualized memory structure 100. Alternatively, signal lines GSL 122 and GBL 124 can both be routed below (or both be routed on top of) conceptualized memory structure 100, each of these signal lines may be selectively connected by access transistors (not shown) to the local source lines and local bit lines of individual vertical NOR strings. Unlike a vertical NAND string of the prior art, in a vertical NOR string of the present invention, writing or reading any one of its storage elements does not involve activation of any other storage element in the vertical NOR string. As shown in FIG. 2, solely for illustrative purpose, conceptualized memory block 100 is a multi-gate vertical NOR string array consisting of a 4.times.5 arrangement of vertical NOR strings, with each NOR string typically having 32 or more storage elements and access selection transistors. As a conceptualized structure, memory block 100 is merely an abstraction of certain salient characteristics of a memory structure of the present invention. Although shown in FIG. 2 as a 4.times.5 arrangement of vertical NOR strings, with each vertical NOR strings having a number of storage elements, a memory structure of the present invention may have any number of vertical NOR strings in each row along either of the X- and Y-directions, and any number of storage elements in each vertical NOR string. For example, there may be thousands of vertical NOR strings arrayed in rows along both the X- and Y-directions, with each NOR string having, for example, 2, 4, 8, 16, 32, 64, 128, or more storage elements.

[0062] The number of storage elements in each vertical NOR string of FIG. 2 (e.g., vertical NOR string 121) corresponds to the number of word lines (e.g., WL 123) providing control gates to the vertical NOR string. The word lines are formed as narrow, long metallic strips each extending along the Y-direction. The word lines are stacked one on top of each other, and electrically isolated from each other by dielectric insulation layers there-between. The number of word lines in each stack may be any number, but preferably an integer power of 2 (i.e., 2.sup.n, where n is an integer). The selection of a power of 2 for the number of word lines follows a customary practice in conventional memory design. It is customary to access each addressable unit of memory by decoding a binary address. This custom is a matter of preference and need not be followed. For example, within the scope of the present invention, conceptualized memory structure 100 may have M vertical NOR strings along each row in the X- and Y-directions, with M being a number that is not necessarily 2.sup.n, for any integer n. In some embodiments to be described below, two vertical NOR strings may share a vertical local source line and a vertical local bit line, but their respective storage elements are controlled by two separate word line stacks. This effectively doubles the storage density of the vertical NOR string.

[0063] As conceptualized memory structure 100 of FIG. 2 is provided merely to illustrate an organization of memory cells, it is not drawn to specific scale in any of the X-, Y-, and Z-directions.

[0064] FIG. 3a shows a basic circuit representation in a Z-Y plane of vertical NOR string 300 formed in an active column; vertical NOR string 300 represents a three-dimensional arrangement of non-volatile storage TFTs, with each TFT sharing local source line 355 and local bit line 354, according to one embodiment of the current invention. In this detailed description, the term "active region," "active column" or "active strip" refers to a region, column or strip of one or more semiconductor materials on which an active device (e.g., a transistor or a diode) may be formed. As shown in FIG. 3a, vertical NOR string 300 runs along the Z-direction, with TFTs 316 and 317 connected in parallel between vertical local source line 355 and vertical local drain or bit line 354. Bit line 354 and source line 355 are spaced apart, with the region there-between (i.e., body region 356) providing channel regions for the TFTs in the vertical NOR string. Storage elements are formed at the intersections between channel region 356 and each horizontal word line 323p, where p is the index of the word line in the word line stack; in this example, p may take any value between 0 and 31. The word lines extend along the Y-direction. Local bit line 354 is connected through bit line access select transistor 311 to horizontal global bit line (GBL) 314, which runs along the X-direction and connects local bit line 354 to access bit line supply voltage V.sub.bl. Local source line 355 is connected through horizontal global source line (GSL) 313 to source supply voltage V.sub.ss. An optional source-select transistor (not shown in FIG. 3a) can be provided to connect between local source line 355 and GSL 313. The optional source-select transistor may be controlled by source decoding circuitry which can be implemented either in the substrate (e.g., semiconductor substrate 101 of FIG. 2) or above the substrate and below memory structure 100, as is known to a person skilled in the art. Body region 356 of the active column may be connected at terminal 331 to substrate bias voltage V.sub.bb. Substrate bias voltage V.sub.bb may be used, for example during an erase operation. The V.sub.bb supply voltage can be applied to an entire multi-gate vertical NOR string array, or be applied selectively to one or more rows of vertical NOR strings via a decoding mechanism. Lines connecting the V.sub.bb supply voltage to body region 356 run preferably along the direction of the word lines.

[0065] FIG. 3b shows a basic circuit representation in a Z-Y plane of vertical NOR string 305 formed in an active column; vertical NOR string 305 represents a three-dimensional arrangement of non-volatile storage TFTs, including (optionally) dedicated pre-charge TFT 370 for momentarily setting a voltage ("V.sub.ss") on shared local source line 355, which has a parasitic capacitance C (represented by capacitor 360), according to one embodiment of the present invention. Unlike vertical NOR string 300 of FIG. 3a, vertical NOR string 305 does not implement GSL 313, replacing it with pre-charge transistor 370 which pre-charges parasitic capacitor 360, which temporarily holds a voltage of V.sub.ss volts. Under this pre-charging scheme, global source lines (e.g., global source lines 313 of FIG. 3a) and its decoding circuitry are rendered unnecessary, thereby simplifying both the manufacturing process as well as circuit layout, and providing a very tight footprint for each vertical NOR string. FIG. 3c highlights the structure of non-volatile storage TFT 317, which can also be used, in addition to its normal storage function, to perform the pre-charge function of dedicated pre-charge transistor 370. A dynamic read operation for TFT 317 is described below in conjunction with sensing the correct one of several threshold voltages that is programmed into storage element 334 of TFT 317.

[0066] FIG. 4a is a cross section in a Z-Y plane showing side-by-side active columns 431 and 432, each of which may form a vertical NOR string that has a basic circuit representation illustrated in either FIG. 3a or FIG. 3b, according to one embodiment of the present invention. As shown in FIG. 4a, active columns 431 and 432 each include vertical N+ doped local source region 455 and vertical N+ doped local drain or bit line region 454, separated by lightly P- doped or undoped channel region 456. P- doped channel region 456, N+ doped local source region 455 and N+ doped local drain or bit line region 454 may be biased to body bias voltage V.sub.bb, source supply voltage V.sub.ss, and bit line voltage V.sub.bl, respectively. In some embodiments of the current invention, use of body bias voltage V.sub.bb is optional, such as when the active strip is sufficiently thin (e.g., 10 nanometers or less). For a sufficiently thin active strip, the active region is readily fully depleted under appropriate voltage on the control gate, such that voltage V.sub.bb may not provide a solid supply voltage to the channel regions of the TFTs along the vertical NOR string. Isolation region 436, which electrically insulates active columns 431 and 432, may be either a dielectric insulator or an air-gap. A vertical stack of word lines 423p, respectively labeled WL0-WL3i (and optionally WL.sub.CHG), provides control gates to the TFTs in the vertical NOR strings formed in active columns 431 and 432. Word line stack 423p is typically formed as long narrow metallic conductors (e.g., tungsten, a silicide or silicide) that extend along the Y-direction, electrically isolated from each other by dielectric layers 426, each typically formed out of silicon oxide (e.g., SiO.sub.2) or an air gap. A non-volatile storage element may be formed at the intersection of each word line 423p and each P- doped channel region 456 by providing a charge-trapping material (not shown) between word line 423p and P- doped channel region 456. For example, FIG. 4a indicates by dashed boxes 416 the locations where nonvolatile storage elements (or storage transistors) T.sub.0 to T.sub.31 may be formed. Dashed box 470 indicates where a dedicated pre-charge transistor may be formed, which, when momentarily switched on, allows charge to be transferred from common local bit line region 454 to common local source line region 455 when all transistors T.sub.0 to T.sub.31 are in their off state.

[0067] FIG. 4b is a cross section in the Z-X plane showing active columns 430R, 430L, 431R and 431L, charge-trapping layers 432 and 434, and word line stacks 423p-L and 423p-R, according to one embodiment of the present invention. Similar to FIG. 4a, each of vertical word line stacks 423p-L and 423p-R in FIG. 4b denotes a stack of long narrow conductors, where p is an index labeling the word lines in stack (e.g., word lines WL.sub.0 to WL.sub.31). As shown in FIG. 4b, each word line serves as control gates for the nonvolatile TFTs in the vertical NOR strings formed on adjacent active columns 430-L and 431-R on opposite sides of the word line (within region 490). For example, in FIG. 4b, word line WL.sub.31 in word line stack 423p-R serves as control gates for both transistor 416L on active column 430L and transistor 416R on active column 431R. Adjacent word line stacks (e.g., word lines stacks 423p-L and 423p-R) are separated by a distance 495, which is the width of a trench formed by etching through successive word line layers, as described below. Active columns 430R and 430L, and their respective charge-trapping layers 432 and 434, are subsequently formed inside the trench etched through the word line layers. Charge-trapping layer 434 is provided interposed between word line stack 423p-R and vertical active columns 431R and 430L. As elaborated below, during programming of transistor 416R, charge injected into charge-trapping layer 434 is trapped in the portion of charge-trapping layer 434 within dash box 480. The trapped charge alters the threshold voltage of TFT 416R, which may be detected by measuring a read current flowing between local source region 455 and local drain region 454 on active column 431R (these regions are shown, e.g., FIG. 4a in the orthogonal cross section of the active column). In some embodiments, pre-charge word line 478 (i.e., WL.sub.CHG) is provided as control gate of pre-charge TFT 470 that is used to charge parasitic capacitance C of local source line 455 (see, capacitor 360 of FIG. 3b and local source line 455 of FIG. 4a) to a ground or source supply voltage V.sub.ss. For expediency, charge-trapping layer 434 also provides a storage element in pre-charge transistor 470, which however is not itself used as a memory transistor. Pre-charging may alternatively be performed using any of memory transistors T.sub.0 to T.sub.31 formed on active column 431R. One or more of these memory transistors, in addition to their storage function, can perform the function of the pre-charge transistor. To perform the pre-charge, the voltage on the word line or control gate is temporarily raised to a few volts above its highest programmable threshold voltage, thereby allowing voltage V.sub.ss applied to local bit line 454 to be transferred to local source line 455 (FIG. 4a). Having memory transistors T.sub.0 to T.sub.31 perform the pre-charge function eliminates the need for separate dedicated pre-charge TFT 470. Care must be taken, however, to avoid unduly disturbing the threshold voltage of such memory TFT when it is performing its pre-charging function.

[0068] Although active columns 430R and 430L are shown in FIG. 4b as two separate active columns separated by an air-gap or dielectric insulation 433, the adjacent vertical N+ local source lines may be implemented by a single shared vertical local source line. Likewise, the vertical N+ local drain or bit lines may be implemented by a single shared vertical local bit line. Such a configuration provides "vertical NOR string pair". In that configuration, active columns 430L and 430R may be seen as two branches (hence the "pair") in one active column. The vertical NOR string pair provides double-density storage through charge-trapping layers 432 and 434 interposed between active columns 430R and 430L and word lines stacks 423p-L and 423p-R on opposite sides. In fact, active columns 430R and 430L may be merged into one active string by eliminating the air gap or dielectric insulation 433, yet still achieve the pair of NOR TFT strings implemented at the two opposite faces of the single active column. Such a configuration achieves the same double-density storage, as the TFTs formed in the opposite faces of the active columns are controlled by separate word line stacks and are formed out of separate charge-trapping layers 434 and 432. Maintaining separate thin active columns 430R and 430L (i.e., instead of merging them into one active column) is advantageous because TFTs on each active column are thinner than the merged column and can therefore more readily be fully depleted under appropriate control gate voltage conditions, thereby substantially reducing source-drain subthreshold leakage current between vertical source regions 455 and vertical drain regions 454 of the active columns (FIG. 4a). Having ultra-thin (and therefore highly resistive) active columns is possible for even very long vertical NOR strings (e.g., 128 TFTs or longer) because the TFTs in a vertical NOR string are connected in parallel and because only one of the many TFTs is switched on at any one time, in contrast with the high resistance of a NAND TFT string where TFTs in the string are connected in series and must therefore all be switched on to sense any one of TFTs in the string. For example, in a 32-TFT vertical NOR string, to be able to read transistor T.sub.30 (FIG. 4a), the channel length of channel region 456 may span just 20 nanometers, as compared to the corresponding channel length of a NAND string, which may be 32 times longer, or 640 nanometers.

[0069] FIG. 4c shows a basic circuit representation in the Z-X plane of vertical NOR string pairs 491 and 492, according to one embodiment of the present invention. As shown in FIG. 4c, vertical NOR strings 451b and 452a share a common word line stack 423p-R, in the manner shown for the vertical NOR strings of active strips 430L and 431R of FIG. 4b. For their respective commonly-connected local bit lines, vertical NOR string pairs 491 and 492 are served by global bit line 414-1 (GBL.sub.1) through access select transistor 411 and global bit line 414-2 (GBL.sub.2) through access select transistor 414, respectively. For their respective commonly-connected local source lines, vertical NOR string pairs 491 and 492 are served by global source line 413-1 (GSL.sub.1) and global source line 413-2 (GSL.sub.2), respectively (source line select access transistors can be similarly provided and are not shown in FIG. 4c). As shown in FIG. 4c, vertical NOR string pair 491 includes vertical NOR strings 451a and 451b that share local source line 455, local bit line 454, and optional body connection 456. Thus, vertical NOR string pair 491 represent the vertical NOR strings formed on active columns 430R and 430L of FIG. 4b. Word line stacks 423p-L and 423p-R (where, in this example, 31.gtoreq.p.gtoreq.0) provide control gates for vertical NOR string 451a and vertical NOR string 451b, respectively. The word lines to control gates in the stack are decoded by decoding circuitry formed in the substrate to ensure that appropriate voltages are applied to the addressed TFT (i.e., the activated word line) and to the unaddressed TFTs (i.e., all other non-activated word lines in the string). FIG. 4c illustrates how storage transistors 416L and 416R on active columns 430L and 431R of FIG. 4b are served by the same word line stack 423p-R. Thus, vertical NOR string 451b of vertical NOR string pair 491 and vertical NOR string 452a of vertical string pair 492 correspond to the adjacent vertical NOR strings formed on active columns 430L and 431R of FIG. 4b. Storage transistors of vertical NOR string 451a (e.g., storage transistor 415R) are served by word line stack 423p-L.

[0070] In another embodiment, the hard-wired global source lines 413-1, 413-2 of FIG. 4c are eliminated, to be substituted for by a parasitic capacitance (e.g., the parasitic capacitance represented by capacitor 460 of FIG. 4c or capacitor 360 of FIG. 3c) between shared N+ local source line 455--which is common to both vertical NOR strings 451a and 451b--and its numerous associated word lines 423p-L and 423p-R. In a vertical stack of 32 TFTs, each of the 32 word lines contribute their parasitic capacitance to provide total parasitic capacitance C, such that it is sufficiently large to temporarily hold the voltage supplied by pre-charge TFT 470 to provide a virtual source voltage V.sub.ss during the relatively short duration of read or programming operations. In this embodiment, the virtual source voltage temporarily held on the parasitic capacitor (C) is provided to local source line 455 from global bit line GBL.sub.1 through access transistor 411 and pre-charge transistor 470. Alternatively, dedicated pre-charge transistor 470 can be eliminated, if one or more of the memory TFTs in the vertical NOR sting are used, in addition to their storage function, to pre-charge local source line 455, by bringing its word line voltage momentarily higher than its highest programmed voltage. Using a storage TFT for this purpose, care must be taken, however, to avoid over-programming the storage TFT. Using the virtual V.sub.ss voltage provides the significant advantage of eliminating hard-wired global source lines (e.g., GLS.sub.1, GLS.sub.2) and their associated decoding circuitry and access transistors, thereby materially simplifying the process flow and design challenges and resulting in a significant more compact vertical NOR string.

[0071] FIG. 5a is a cross section in the Z-Y plane showing connections of vertical NOR string of active column 531 to global bit line 514-1 (GBL.sub.1), global source line 507 (GSL.sub.1), and common body bias source 506 (V.sub.bb), according to one embodiment of the present invention. As shown in FIG. 5a, bit-line access select transistor 511 connects GBL.sub.1 with local bit line 554, and buried contact 556 optionally connects a P- body region on the active strip to body bias source 506 (V.sub.bb) in the substrate. Bit-line access select transistor 511 is formed in FIG. 5a above active column 531. However, alternatively, bit-line access select transistor 511 may be formed at the bottom of active column 531 or in substrate 505 (not shown in FIG. 5a). In FIG. 5a, bit-line access select transistor 511 can for example be formed in an isolated island of an N+/P-/N+ doped polysilicon stack together with access select word line 585. When a sufficiently large voltage is applied to select word line 585, the P- channel is inverted, thereby connecting local bit line 554 to GBL.sub.1. Word line 585 runs along the same direction (i.e., the Y-direction) as the word lines 523p which serve as control gates to the TFTs of the vertical NOR string. Word line 585 may be formed separately from word lines 523p. In one embodiment, GBL.sub.1 runs horizontally along the X-direction (i.e., perpendicular to the directions of the word lines), and bit-line access select transistor 511 provides access to local bit line 554, which is the local bit line of merely one of many vertical NOR strings that are served by GBL.sub.1. To increase read and program operation efficiency, in a multi-gate NOR string array, thousands of global bit lines may be used to access in parallel the local bit lines of thousands of vertical NOR strings that are accessed by word line 585. In FIG. 5a, local source line 555 is connected through contact 557 to global source line 513-1 (GSL.sub.1), which may be decoded, for example by decoding circuitry in substrate 505. Alternatively, as described already, the global source line may be eliminated by providing a virtual source voltage V.sub.ss on local bit line 555 and temporarily pre-charging the parasitic capacitor 560 (i.e., parasitic capacitance C) of local source line 555 through TFT 570.

[0072] Support circuitry formed in substrate 505 may include address encoders, address decoders, sense amplifiers, input/output drivers, shift registers, latches, reference cells, power supply lines, bias and reference voltage generators, inverters, NAND, NOR, Exclusive-Or and other logic gates, other memory elements, sequencers and state machines, among others. The multi-gate NOR string arrays may be organized as multiple blocks of circuits, with each block having multiple multi-gate NOR string arrays.

[0073] FIG. 6a is a cross section in the X-Y plane, showing TFT 685 (T.sub.L) of vertical NOR string 451a and TFT 684 (T.sub.R) of vertical NOR string 451b in vertical NOR string pair 491, as discussed above in conjunction with FIG. 4c. As shown in FIG. 6, TFTs 684 and 685 share N+ local source region 655 and N+ local drain or bit line region 654, both regions extending in long narrow pillars along the Z-direction. (N+ local source region 655 corresponds to local source line 455 of FIG. 4a, N+ local drain region 654 corresponds to local bit line 454 of FIG. 4a). In this embodiment, P- doped channel regions 656L and 656R form a pair of active strings between local source pillar 655 and local drain pillar 654 and extend along the Z-direction, isolated from each other by isolation region 640. Charge-trapping layer 634 is formed between word lines 623p-L (WL.sub.31-0) and 623p-R (WL.sub.31-1) and the outside of channel regions 656L and 656R respectively. Charge trapping layer 634 may be a transistor gate dielectric material consisting of, for example, a thin film of tunnel dielectric (e.g., silicon dioxide), followed by a thin layer of charge trapping material such as silicon nitride or conductive nanodots embedded in a non-conducting dielectric material, or isolated floating gates, and is capped by a layer of blocking dielectric such as ONO (an oxide-nitride-oxide triple-layer) or a high dielectric constant film such as aluminum oxide or hafnium oxide or some combination of such dielectrics. Source-drain conduction is controlled by word lines 623p-L and 623p-R, respectively, forming control gates on the outside of charge-trapping layer 634. When programming or reading TFT 684 (T.sub.R), TFT 685 (T.sub.L) is turned off by maintaining an appropriate inhibit voltage at word line 623p-L. Similarly, when programming or reading TFT 685 (T.sub.L), TFT 684 (T.sub.R) is turned off by maintaining an appropriate inhibit voltage at word line 623p-R.

[0074] In the embodiment shown in FIG. 6a, word lines 623p-L and 623p-R are contoured to enhance tunneling efficiency into the TFTs 684 and 685 during programming, while reducing reverse-tunneling efficiency during erasing. Specifically, as is known to a person skilled in the art, curvature 675 of channel region 656R amplifies the electric field at the interface between the active channel polysilicon and the tunneling dielectric during programming, while reducing the electric field at the interface between the word line and the blocking dielectric during erasing. This feature is particularly helpful when storing more than one bit per TFT transistor in a multi-level cell (MLC) configuration. Using this technique, 2, 3, or 4 bits or more may be stored in each TFT. In fact, TFTs 684 and 685 may be used as analog storage TFTs with a continuum of stored states. Following a programming sequence (to be discussed below), electrons are trapped in charge-trapping layer 634, as indicated schematically by dashed lines 680. In FIG. 6a, global bit lines 614-1 and 614-2 run perpendicularly to word lines 623p-R and 623p-L and are provided either above or underneath the vertical NOR strings, corresponding to bit lines 414-1 and 414-2 respectively of FIG. 4c. As discussed above in conjunction with FIG. 2, the word lines may span the entire length of memory block 100 along the X-direction, while the global bit lines span the width of memory block 100 along the Y-direction. Of importance, in FIG. 6a, word line 623p-R is shared by TFTs 684 and 683 of two vertical NOR strings on opposite sides of word line 623p-R. Accordingly, to allow TFTs 684 and 683 to be read or programmed independently, global bit line 614-1 (GBL.sub.1) contacts local drain or bit line region 657-1 ("odd addresses"), while global bit line 614-2 (GBL.sub.2) contacts local drain or bit line region 657-2 ("even addresses"). To achieve this effect, contacts along global bit lines 614-1 and 614-2 are staggered, with each global bit line contacting every other one of the vertical NOR string pair along the X-direction row.

[0075] In like manner, global source lines (not shown in FIG. 6a), which may be located either at the bottom or above the multi-gate NOR string array, may run parallel to the global bit lines and may contact the local source lines of vertical NOR string pairs according to even or odd addresses. Alternatively, where pre-charging of the parasitic capacitor (i.e., capacitor 660) temporarily to virtual source voltage V.sub.ss is used, the global source lines need not be provided, thereby simplifying the decoding scheme as well as the process complexity.

[0076] FIG. 6a shows only one of several possible embodiments by which vertical NOR string pairs may be provided with stacked word lines. For example, curvature 675 in channel region 656R can be further accentuated. Conversely such curvature can be altogether eliminated (i.e. straightened out) as shown in the embodiment of FIG. 6b. In the embodiment of FIG. 6b isolation spacing 640 of FIG. 6a may be reduced or altogether eliminated by merging channel regions 656L and 656R into a single region 656(L+R), achieving greater area efficiency without sacrificing the dual-channel configuration: for example TFTs 685 (T.sub.L) and 684 (T.sub.R) reside on opposite faces of the same active strip. In the embodiments of FIGS. 6a, 6b, vertical NOR strings sharing a word line may be laid out in a staggered pattern relative to each other (not shown), such that they may be brought closer to each other, thereby reducing the effective footprint of each vertical NOR string. Although FIGS. 6a and 6b show direct connection via a contact between global bit line 614-1 and N+ doped local drain bit line pillar 654 (LBL-1), such connection can also be accomplished using a bit-line access selection transistor (e.g., bit line access select transistor 511 of FIG. 5a, not shown in already crowded FIGS. 6a and 6b).

[0077] In the embodiments of FIGS. 6a and 6b, dielectric isolation between N+ doped local drain region 654 and its adjacent local N+ doped source region 658 (corresponding to isolation region 436 of FIG. 4a) can be established by, for example, defining the separation 676 between word lines 623p-R and 623p-L to be less than the thicknesses of two back-to-back charge-trapping layers, so that the charge-trapping layers are merged together during their deposition. The resulting merging of the deposited charge-trapping layers creates the desired dielectric isolation. Alternatively, isolation between adjacent active strings can be achieved by using a high aspect-ratio etch of N+ polysilicon to create gap 676 (air gap or dielectric filled) isolating N+ pillar 658 of one string from N+ pillar 654 of the adjacent string (i.e., creating gap 436 shown in FIG. 4a).

[0078] Contrasting between the prior art vertical NAND strings and the vertical NOR strings of the current invention, although both types of devices employ thin-film transistors with similar word line stacks as control gates, their transistor orientations are different: in the prior art NAND string, each vertical active strip may have 32, 48 or more TFTs connected in series. In contrast, each active column forming the vertical NOR strings of the present invention the vertical column may have one or two sets of 32, 48 or more TFTs connected in parallel. In the prior art NAND strings, the word lines in some embodiments typically wrap around the active strip. In some embodiments of the vertical NOR string of the present invention separate designated left and right word lines are employed for each active strip, thereby to achieve a doubling (i.e. a pair) storage density for each global bit line, as illustrated in FIGS. 4c, 6a and 6b. The vertical NOR strings of the present invention do not suffer from program-disturb or read-disturb degradation, nor do they suffer from the slow latency of the prior art NAND strings. Thus, a much larger number of TFTs may be provided in a vertical NOR string than in a vertical NAND strings. Vertical NOR strings, however, may be more susceptible to subthreshold or other leakage between the long vertical source and drain diffusions (e.g., local source region 455 and local drain region 454, respectively, illustrated in FIG. 4a).

[0079] Two additional embodiments of the vertical NOR string of this invention are shown in FIG. 6c and FIG. 6d. In these embodiments, all word lines in each word-line stack wrap around the vertical active strip.

[0080] In FIG. 6c, a vertical NOR string is formed inside the voids that are formed by etching through a stack of metal word lines and the dielectric isolation layers between the word lines. The manufacturing process flow is similar to that of the prior art vertical NAND strings, except that the transistors in a vertical NOR string are provided parallel to each other, rather than serially in a vertical NAND string. Formation of transistors in a vertical NOR string is facilitated by the N+ doped vertical pillars extending to the entire depth of the void, providing shared local source line 655 (LSL) and shared local bit line (drain) 654 (LBL) for all the TFTs along the vertical NOR string, with undoped or lightly doped channel region 656 adjacent to both. Charge storage element 634 is positioned between channel 656 and word line stack 623p, thus forming a stack of 2, 4, 8, . . . 32, 64 or more TFTs (e.g., device 685 (T.sub.10)) along the vertical active strip. In the embodiment of FIG. 6c, the word line stacks run in the Y-direction, with individual horizontal strips 623p (WL.sub.31-0), 623p (WL.sub.31-1) being separated from each other by air gap or dielectric isolation 610. Global bit lines 614 (GBL) and global source lines 615 (GSL) run horizontally in rows along the X-direction, perpendicular to the word lines. Each global bit line 614 accesses local bit line pillars 654 (LBL) along the row of vertical strips through access select transistors (511 in FIG. 5a, not shown here) that can be positioned either below the memory array or above it. Similarly, each global source line 615 accesses the local source line pillars along the row. While the structures shown in FIGS. 6a and 6b are able to fit a pair of vertical NOR strings in roughly the same area taken up by a single vertical NOR string in the embodiment of FIG. 6c, each TFT in each vertical NOR string shown in FIG. 6c has two parallel conduction channels (i.e., channel regions 656a and 656b), and therefore may store more charge and increase or double the read current, thereby enabling storing more bits in each TFT.

[0081] FIG. 6d shows a more compact vertical NOR string with wrap-around word lines, according to one embodiment of the present invention. As shown in FIG. 6d, vertical NOR strings are staggered as to be closer together, so that word line stack 623p (WL.sub.31-0) can be shared by more vertical NOR strings. The staggered configuration is enabled by using the parasitic capacitor (i.e., parasitic capacitors 660) of local source line pillar 655 (LSL). By pre-charging capacitors 660 to temporarily hold virtual voltage V.sub.ss during read and program operations, as described below, the need for hard-wired global source lines (e.g., GSL 615 in FIG. 6c) is obviated. Although the vertical NOR strings of FIGS. 6c and 6d may not by themselves offer significant areal efficiencies, as compared to prior art vertical NAND strings (e.g., the NAND strings of FIG. 1c), such vertical NOR strings achieve much greater string lengths than vertical NAND strings. For example, while vertical NOR strings of the present invention may well support strings of length 128 to 512 or more TFTs in each stack, such string lengths are simply not practical for a vertical NAND string, given the serious limitations attendant with series-connected TFT strings.