Logic Drive With Brain-like Elasticity And Integrality Based On Standard Commodity Fpga Ic Chips Using Non-volatile Memory Cells

Lee; Jin-Yuan ; et al.

U.S. patent application number 16/125784 was filed with the patent office on 2019-08-01 for logic drive with brain-like elasticity and integrality based on standard commodity fpga ic chips using non-volatile memory cells. The applicant listed for this patent is iCometrue Company Ltd.. Invention is credited to Jin-Yuan Lee, Mou-Shiung Lin.

| Application Number | 20190238134 16/125784 |

| Document ID | / |

| Family ID | 67392943 |

| Filed Date | 2019-08-01 |

View All Diagrams

| United States Patent Application | 20190238134 |

| Kind Code | A1 |

| Lee; Jin-Yuan ; et al. | August 1, 2019 |

LOGIC DRIVE WITH BRAIN-LIKE ELASTICITY AND INTEGRALITY BASED ON STANDARD COMMODITY FPGA IC CHIPS USING NON-VOLATILE MEMORY CELLS

Abstract

A chip package comprises an interposer; an FPGA IC chip over the interposer, wherein the FPGA IC chip comprises a programmable logic block configured to perform a logic operation on its inputs, wherein the programmable logic block comprises a look-up table configured to be provided with multiple resulting values of the logic operation on multiple combinations of the inputs of the programmable logic block respectively, wherein the programmable logic block is configured to select, in accordance with one of the combinations of its inputs, one from the resulting values into its output, and multiple non-volatile memory cells configured to save the resulting values respectively; multiple first metal bumps between the interposer and the FPGA IC chip; and an underfill between the interposer and the FPGA IC chip, wherein the underfill encloses the first metal bumps.

| Inventors: | Lee; Jin-Yuan; (Hsinchu City, TW) ; Lin; Mou-Shiung; (Hsinchu City, TW) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 67392943 | ||||||||||

| Appl. No.: | 16/125784 | ||||||||||

| Filed: | September 10, 2018 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 62557727 | Sep 12, 2017 | |||

| 62630369 | Feb 14, 2018 | |||

| 62675785 | May 24, 2018 | |||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 2224/05166 20130101; H01L 2224/0558 20130101; H01L 2224/13013 20130101; H01L 2224/13147 20130101; H01L 2224/29647 20130101; H01L 29/7883 20130101; H01L 2224/13118 20130101; H01L 2224/16238 20130101; H01L 2225/1041 20130101; H01L 2224/13113 20130101; H01L 23/5386 20130101; H01L 2224/0231 20130101; H01L 2224/05008 20130101; H01L 2224/05124 20130101; H01L 2924/1432 20130101; H01L 23/5383 20130101; H01L 2224/02381 20130101; H01L 2924/18161 20130101; H01L 2224/05199 20130101; H01L 2224/2929 20130101; H03K 19/1776 20130101; H01L 25/105 20130101; H01L 29/785 20130101; H01L 2224/05186 20130101; H01L 2224/83104 20130101; H01L 2924/1431 20130101; H01L 2224/1312 20130101; H01L 2224/83862 20130101; H01L 23/5389 20130101; H01L 24/11 20130101; H01L 24/20 20130101; H01L 25/03 20130101; H01L 2224/29686 20130101; H01L 2224/92225 20130101; H01L 24/05 20130101; H01L 2224/13109 20130101; H01L 2224/13082 20130101; H01L 2224/11849 20130101; H01L 2224/13014 20130101; H01L 2924/1436 20130101; H01L 2224/292 20130101; H03K 19/20 20130101; H01L 23/3677 20130101; H01L 24/19 20130101; H03K 19/17728 20130101; H01L 2224/13023 20130101; H01L 2224/13139 20130101; H01L 2224/18 20130101; H01L 2224/73204 20130101; H01L 2224/94 20130101; H01L 24/16 20130101; H01L 2224/11462 20130101; H01L 2924/1437 20130101; H01L 2224/03912 20130101; H01L 2224/293 20130101; H01L 23/50 20130101; H01L 27/24 20130101; H01L 2224/0345 20130101; H01L 2224/05569 20130101; H01L 2225/1035 20130101; H01L 23/49816 20130101; H01L 2224/05572 20130101; H01L 2224/1147 20130101; H03K 19/1737 20130101; H01L 2224/05147 20130101; H01L 2224/05184 20130101; H01L 2224/16227 20130101; H01L 2225/1058 20130101; H01L 24/81 20130101; H01L 27/11517 20130101; H01L 27/1156 20130101; H01L 2224/05647 20130101; H01L 25/18 20130101; H01L 2224/13111 20130101; H01L 2224/81191 20130101; H01L 2224/83447 20130101; H01L 24/03 20130101; H01L 2224/0235 20130101; H01L 2224/053 20130101; H01L 2224/13022 20130101; H01L 2224/73259 20130101; H01L 2924/1443 20130101; H01L 23/49811 20130101; H01L 2224/03452 20130101; H01L 2224/29666 20130101; H01L 24/13 20130101; H01L 2224/29684 20130101; H03K 19/21 20130101; H01L 2224/0345 20130101; H01L 2924/00014 20130101; H01L 2224/03452 20130101; H01L 2924/00014 20130101; H01L 2224/11849 20130101; H01L 2924/00014 20130101; H01L 2224/94 20130101; H01L 2224/11 20130101; H01L 2224/94 20130101; H01L 2224/03 20130101; H01L 2224/13014 20130101; H01L 2924/00014 20130101; H01L 2224/13013 20130101; H01L 2924/00014 20130101; H01L 2224/18 20130101; H01L 2924/0001 20130101; H01L 2224/293 20130101; H01L 2924/00014 20130101; H01L 2224/05199 20130101; H01L 2924/00014 20130101; H01L 2224/053 20130101; H01L 2924/00014 20130101; H01L 2224/83447 20130101; H01L 2924/00014 20130101; H01L 2224/292 20130101; H01L 2924/00014 20130101; H01L 2224/29647 20130101; H01L 2924/00014 20130101; H01L 2224/05647 20130101; H01L 2924/00014 20130101 |

| International Class: | H03K 19/177 20060101 H03K019/177; H03K 19/173 20060101 H03K019/173; H01L 23/00 20060101 H01L023/00; H01L 23/538 20060101 H01L023/538; H01L 25/18 20060101 H01L025/18; H01L 27/11517 20060101 H01L027/11517; H01L 27/24 20060101 H01L027/24 |

Claims

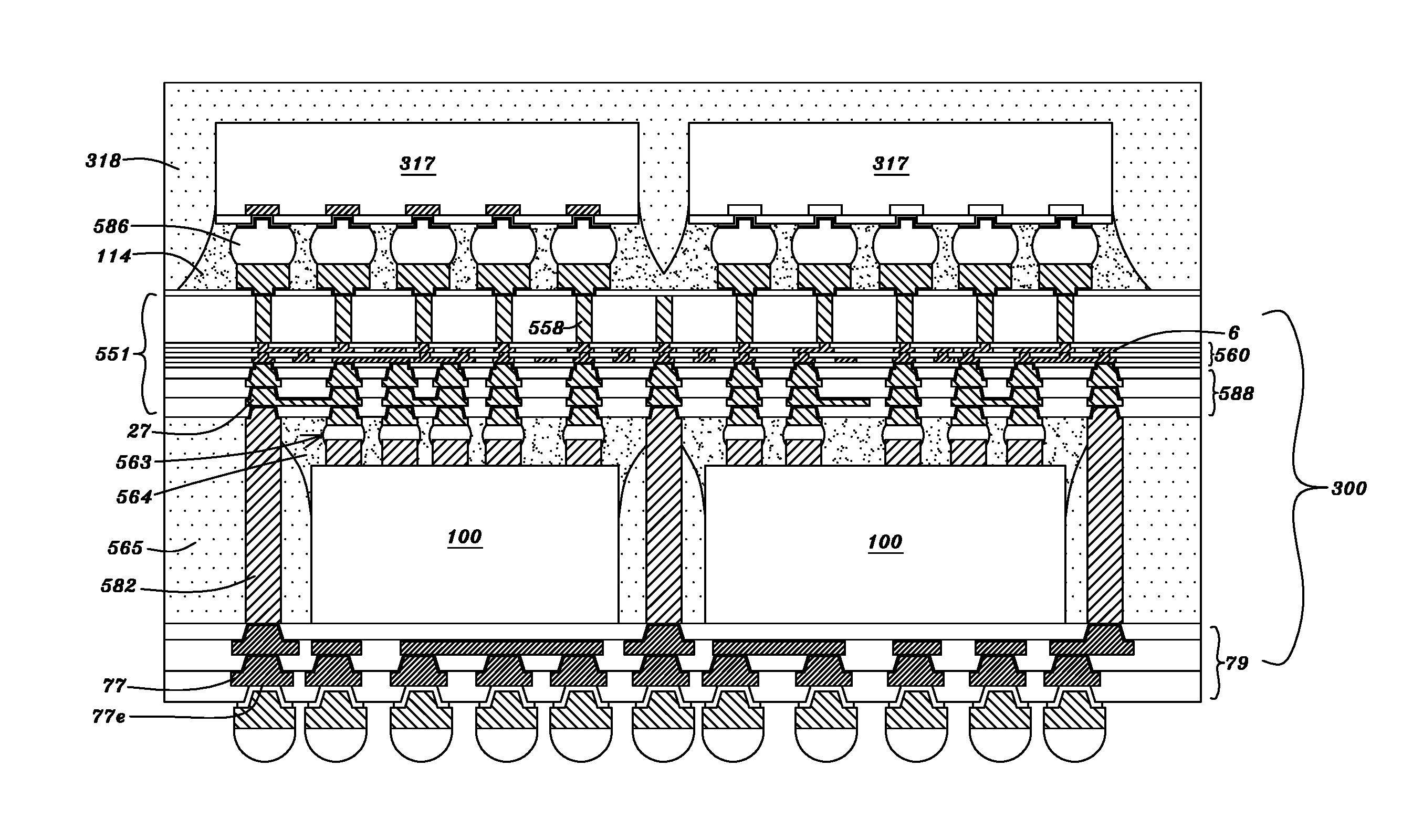

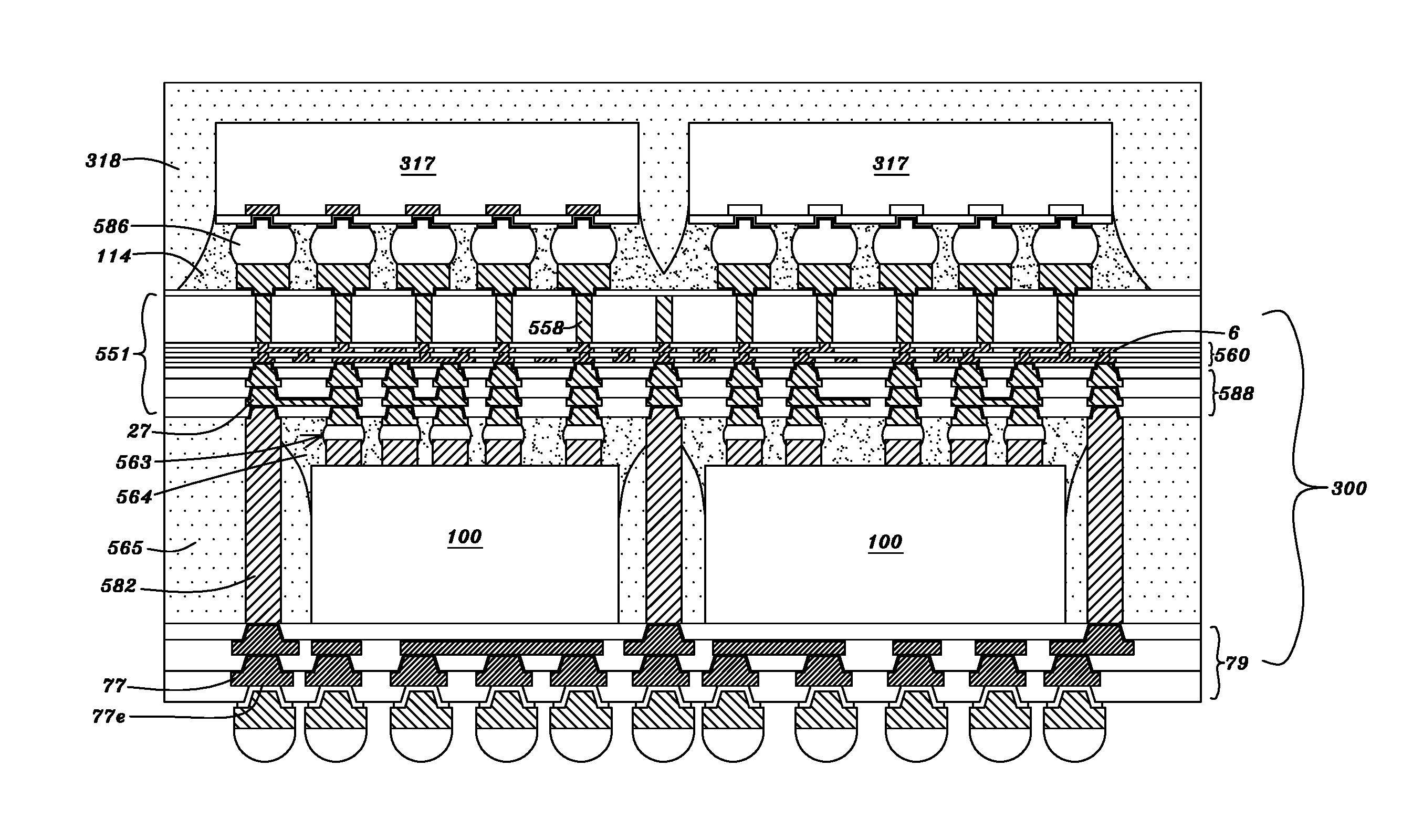

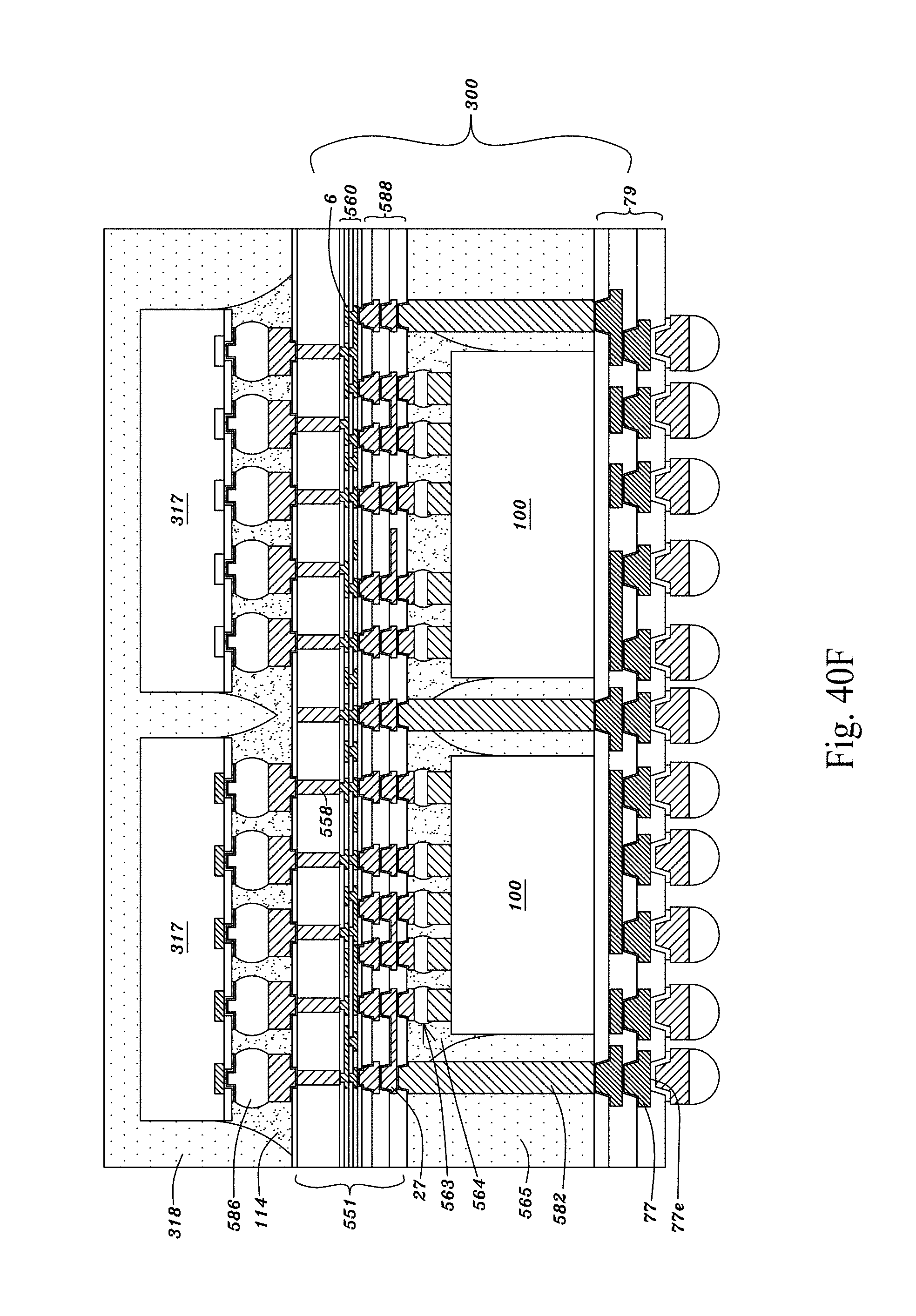

1. A chip package comprising: an interposer comprising a silicon substrate, multiple metal vias passing through the silicon substrate, a first interconnection metal layer over the silicon substrate, a second interconnection metal layer over the silicon substrate, and an insulating dielectric layer over the silicon substrate and between the first and second interconnection metal layers; a field-programmable-gate-array (FPGA) integrated-circuit (IC) chip over the interposer, wherein the FPGA IC chip comprises a programmable logic block configured to perform a logic operation on its inputs, wherein the programmable logic block comprises a look-up table (LUT) configured to be provided with multiple resulting values of the logic operation on multiple combinations of the inputs of the programmable logic block respectively, wherein the programmable logic block is configured to select, in accordance with one of the combinations of its inputs, one from the resulting values into its output, and multiple non-volatile memory cells configured to save the resulting values respectively; multiple first metal bumps between the interposer and the FPGA IC chip; and an underfill between the interposer and the FPGA IC chip, wherein the underfill encloses the first metal bumps.

2. The chip package of claim 1, wherein each of the first metal bumps comprises a copper layer, which has a thickness between 3 and 60 micrometers, between the interposer and the FPGA IC chip.

3. The chip package of claim 2, wherein said each of the first metal bumps comprises a solder layer between the copper layer of said each of the first metal bumps and the interposer.

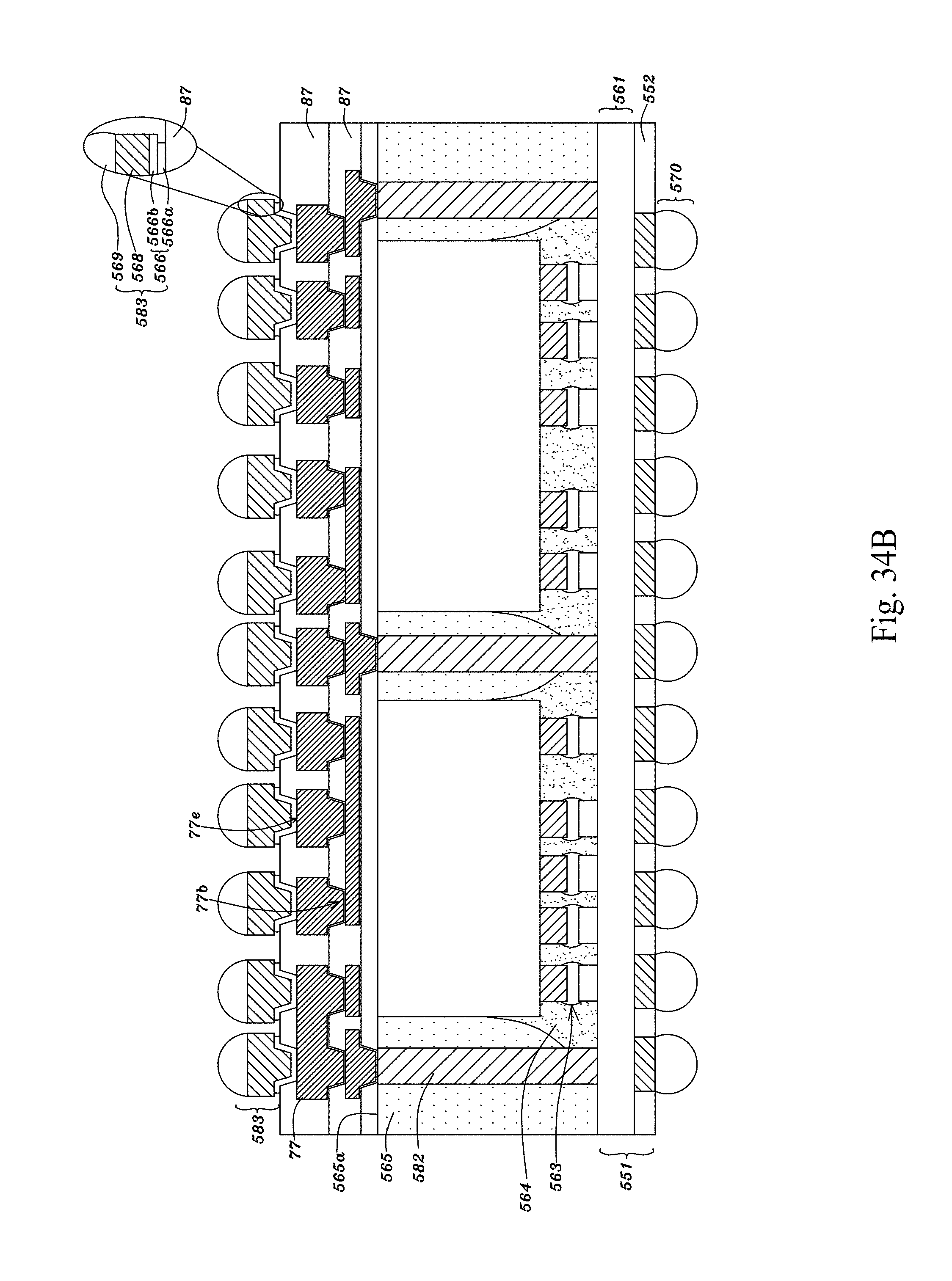

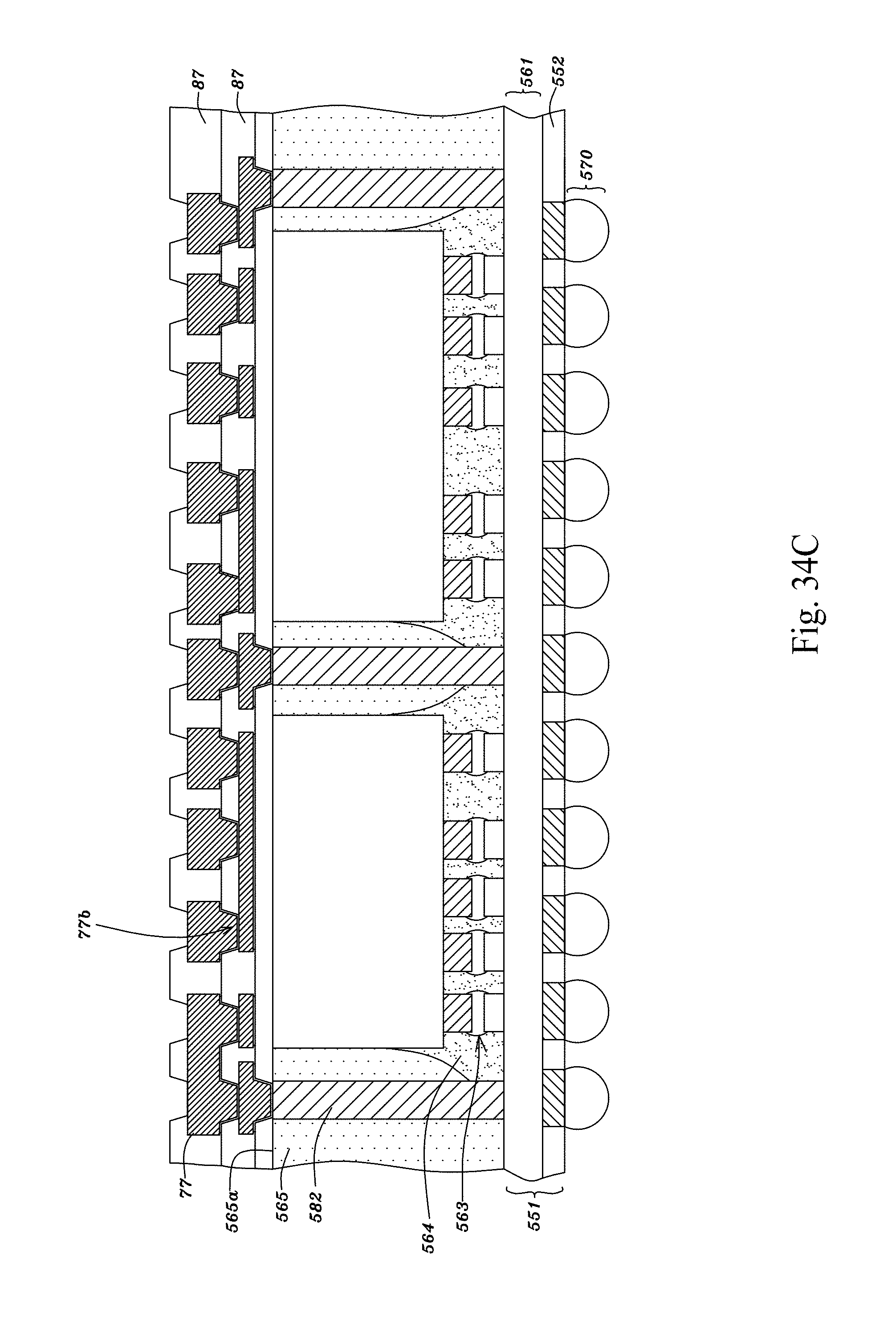

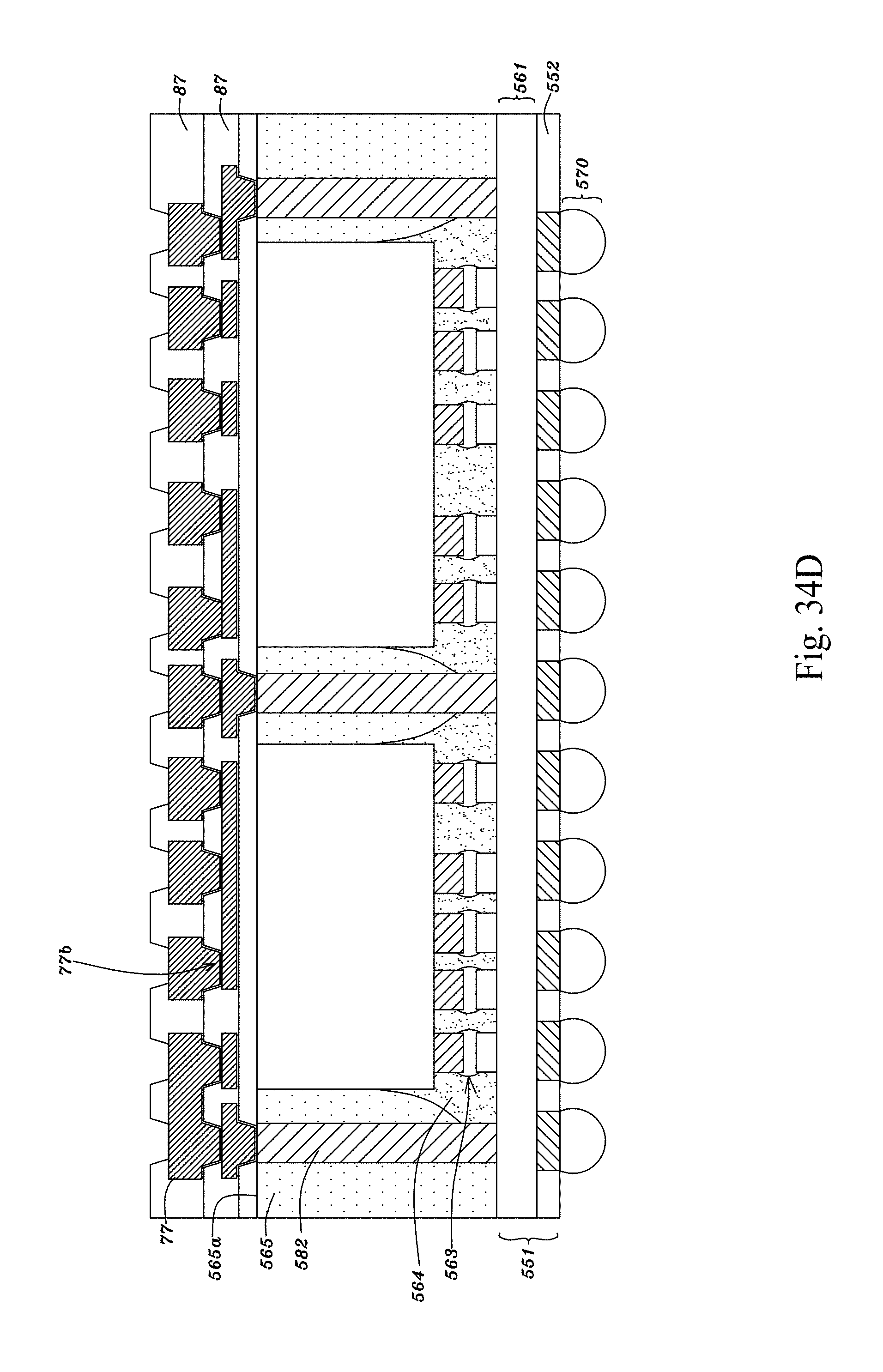

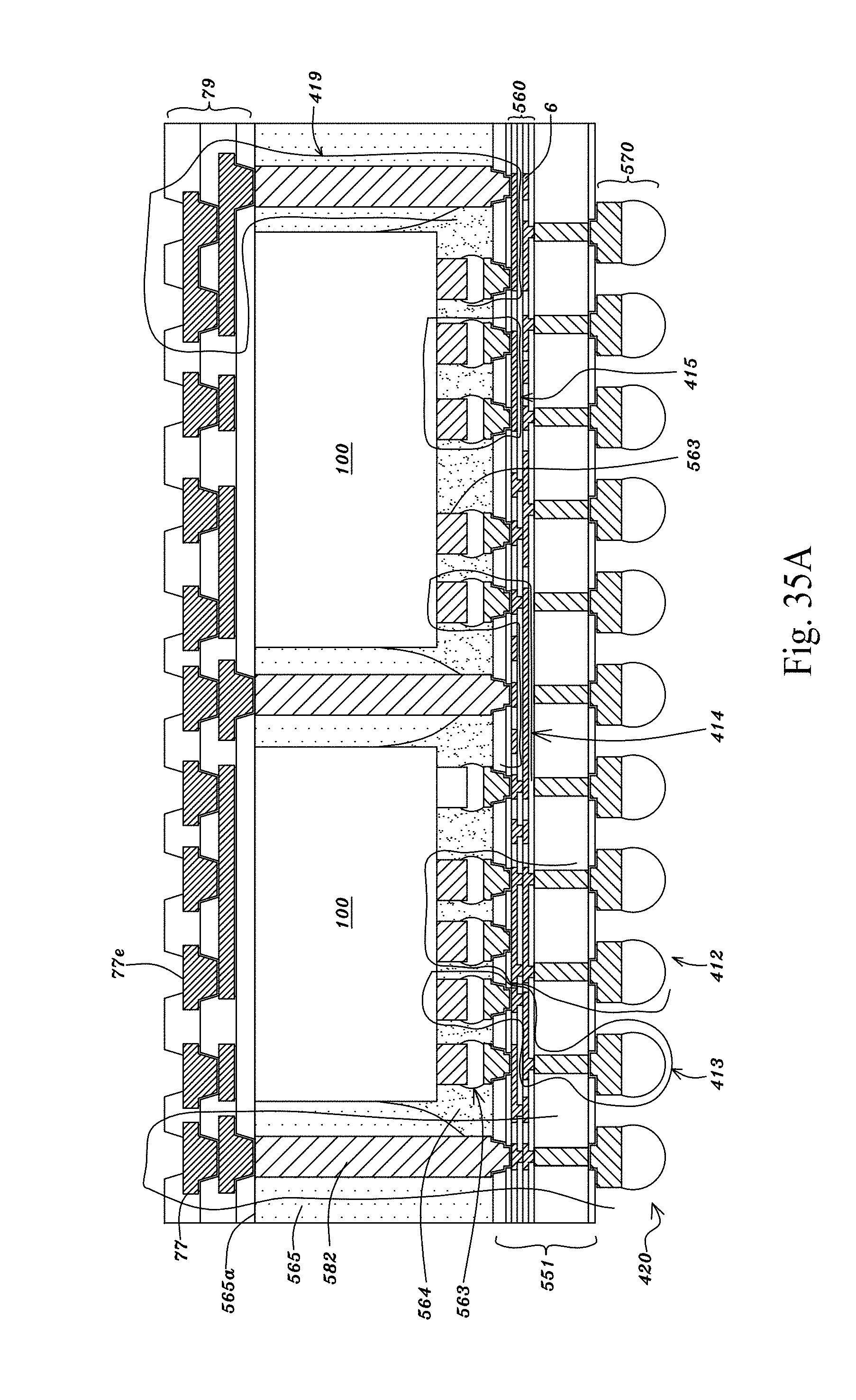

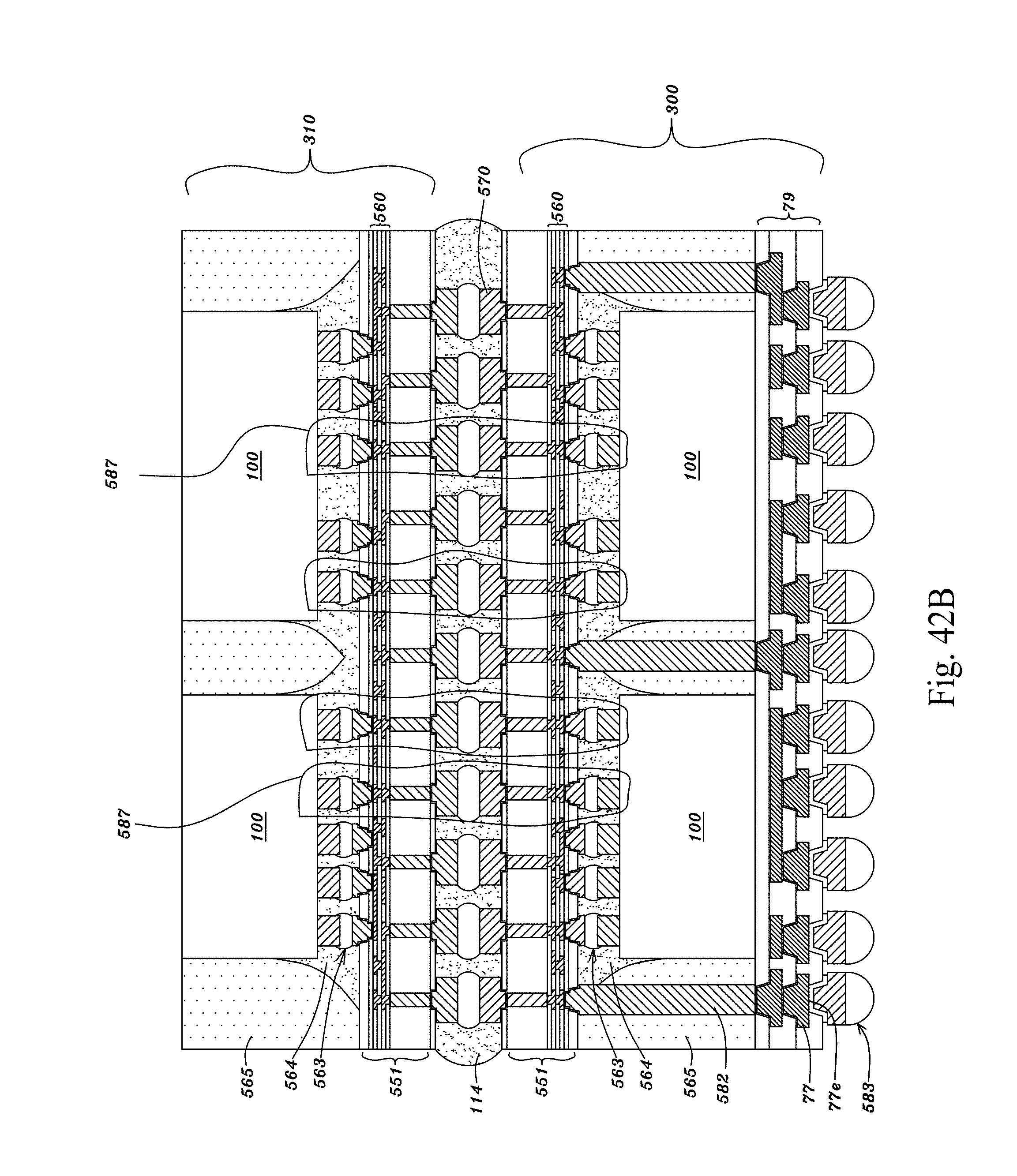

4. The chip package of claim 1 further comprising a polymer layer horizontally around the FPGA IC chip, wherein the polymer layer has a top surface coplanar with a top surface of the FPGA IC chip.

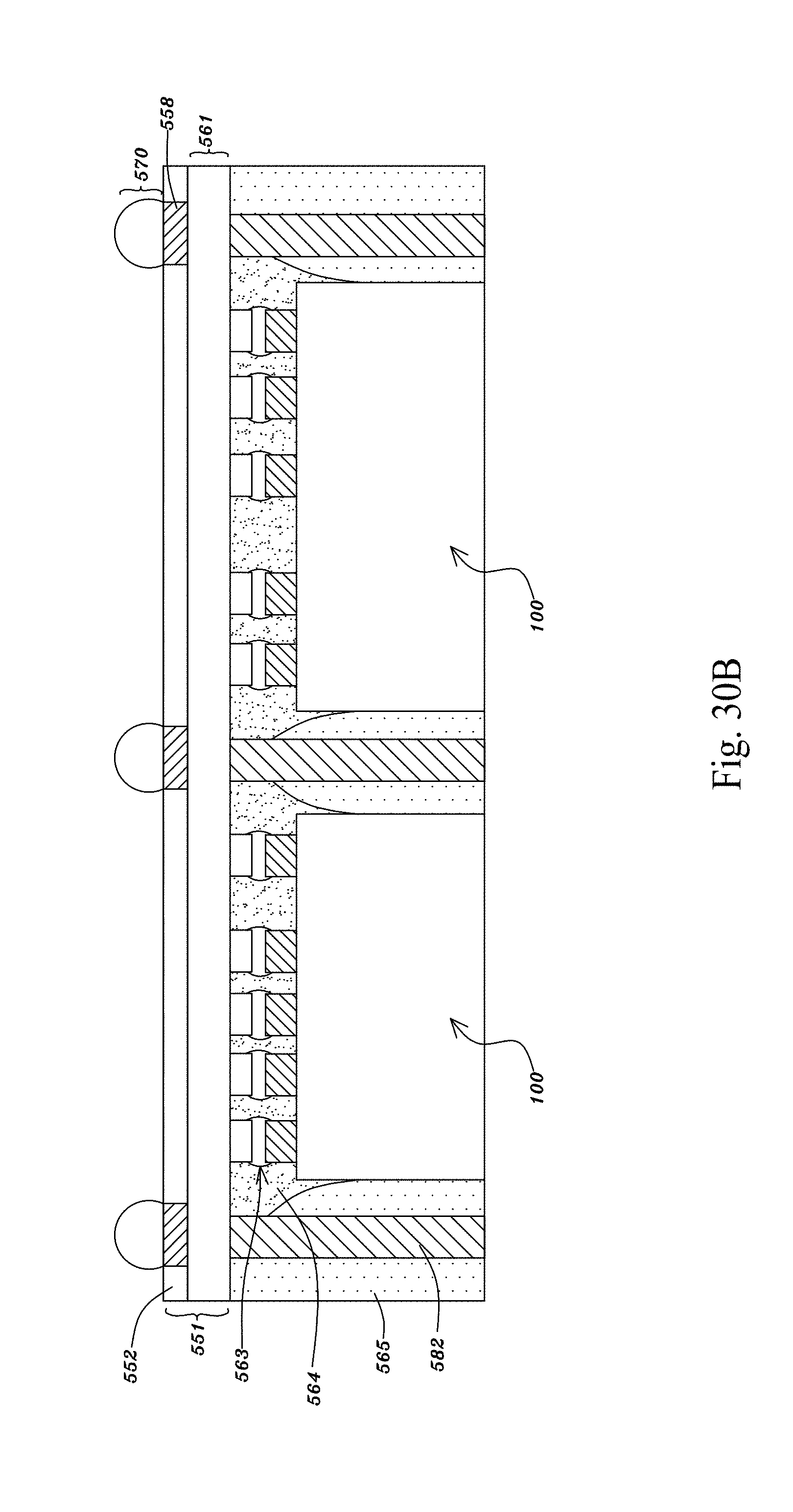

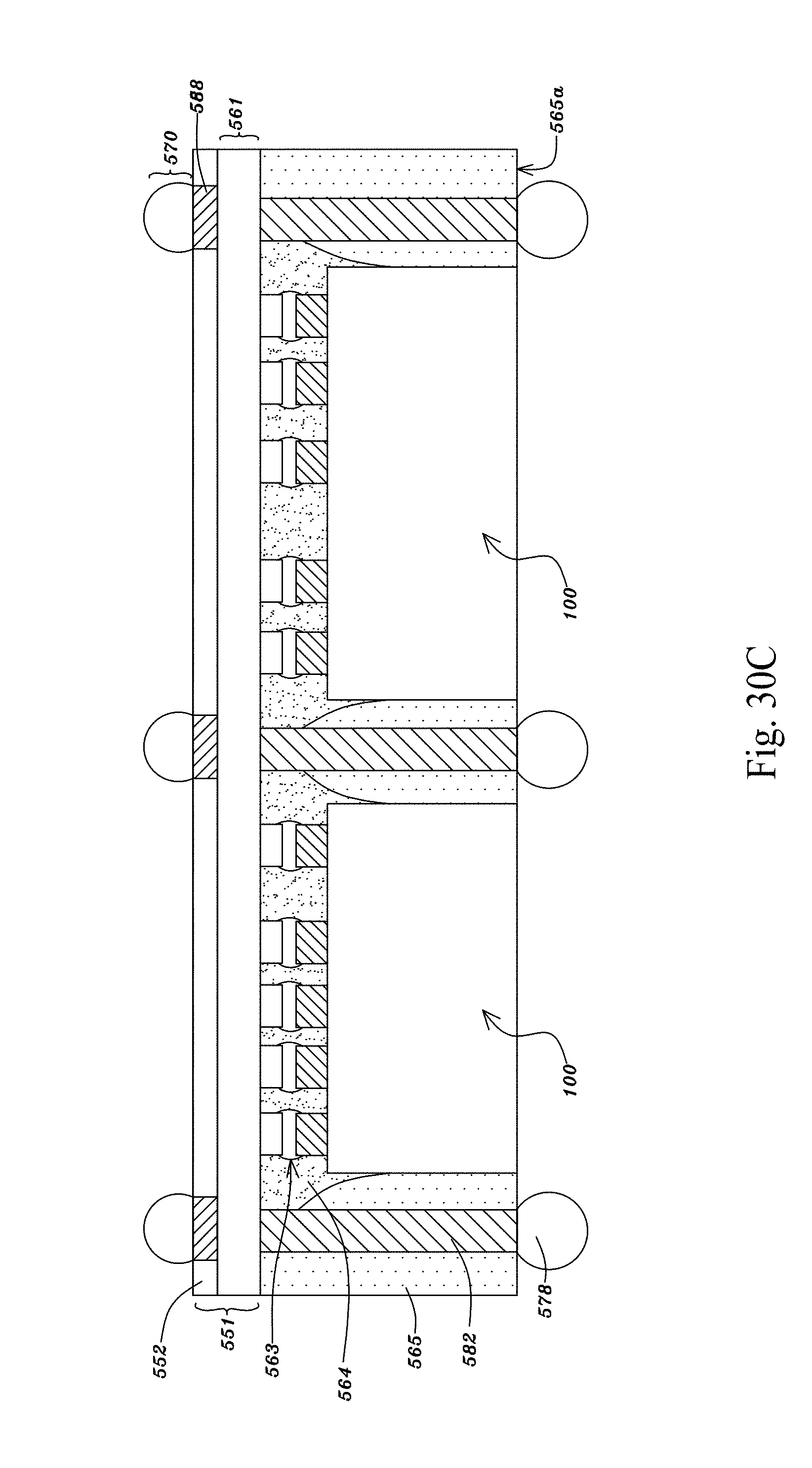

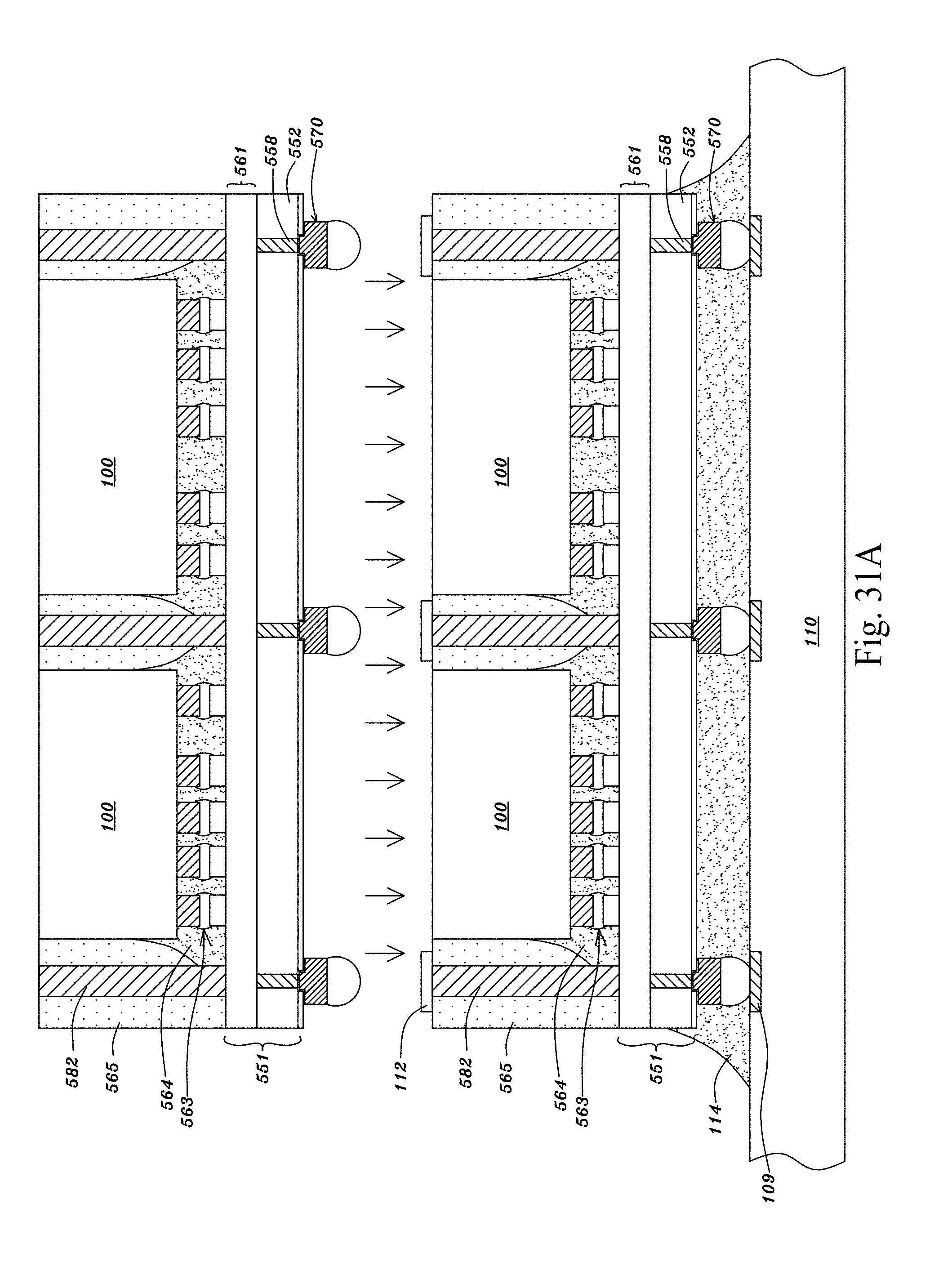

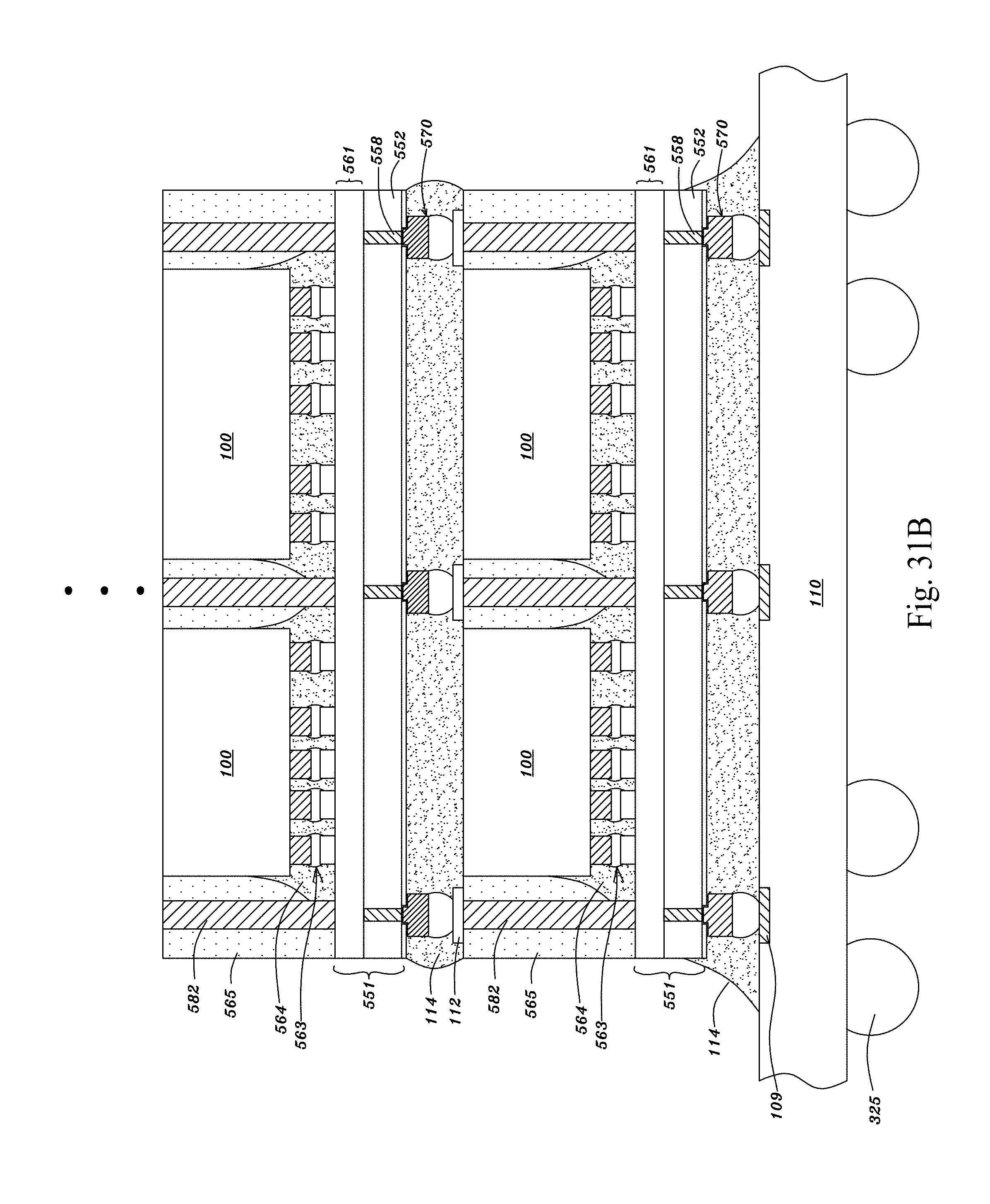

5. The chip package of claim 4 further comprising multiple through package vias in the polymer layer and on the interposer, wherein each of the through package vias has a top surface coplanar with the top surface of the polymer layer.

6. The chip package of claim 5, wherein each of the through package vias comprises a copper layer having a thickness between 5 and 300 micrometers, wherein the copper layer has a top surface coplanar with the top surface of the polymer layer.

7. The chip package of claim 1 further comprising a central-processing-unit (CPU) chip over the interposer, multiple second metal bumps between the interposer and the CPU chip, and a second underfill between the interposer and the CPU chip, wherein the second underfill encloses the second metal bumps.

8. The chip package of claim 1 further comprising a graphical-processing-unit (GPU) chip over the interposer, multiple second metal bumps between the interposer and the GPU chip, and a second underfill between the interposer and the GPU chip, wherein the second underfill encloses the second metal bumps.

9. The chip package of claim 1, wherein each of the non-volatile memory cells comprises a N-type MOS transistor having a gate terminal coupling to a gate terminal of a P-type MOS transistor of said each of the non-volatile memory cells, wherein the gate terminal of the floating-gate N-type MOS transistor and gate terminal of the floating-gate P-type MOS transistor are floating.

10. The chip package of claim 1, wherein each of the non-volatile memory cells comprises a resistive random access memory.

11. A chip package comprising: an interposer comprising a silicon substrate, multiple metal vias passing through the silicon substrate, a first interconnection metal layer over the silicon substrate, a second interconnection metal layer over the silicon substrate, and an insulating dielectric layer over the silicon substrate and between the first and second interconnection metal layers; a field-programmable-gate-array (FPGA) integrated-circuit (IC) chip over the interposer, wherein the FPGA IC chip comprises a switch configured to turn on or off two interconnects of the FPGA IC chip, and a non-volatile memory cell configured to save a programming code configured to control the switch; multiple first metal bumps between the interposer and the FPGA IC chip; and an underfill between the interposer and the FPGA IC chip, wherein the underfill encloses the first metal bumps.

12. The chip package of claim 11, wherein each of the first metal bumps comprises a copper layer, which has a thickness between 3 and 60 micrometers, between the interposer and the FPGA IC chip.

13. The chip package of claim 12, wherein said each of the first metal bumps comprises a solder layer between the copper layer of said each of the first metal bumps and the interposer.

14. The chip package of claim 11 further comprising a polymer layer horizontally around the FPGA IC chip, wherein the polymer layer has a top surface coplanar with a top surface of the FPGA IC chip.

15. The chip package of claim 14 further comprising multiple through package vias in the polymer layer and on the interposer, wherein each of the through package vias has a top surface coplanar with the top surface of the polymer layer.

16. The chip package of claim 15, wherein each of the through package vias comprises a copper layer having a thickness between 5 and 300 micrometers, wherein the copper layer has a top surface coplanar with the top surface of the polymer layer.

17. The chip package of claim 11 further comprising a central-processing-unit (CPU) chip over the interposer, multiple second metal bumps between the interposer and the CPU chip, and a second underfill between the interposer and the CPU chip, wherein the second underfill encloses the second metal bumps.

18. The chip package of claim 11 further comprising a graphical-processing-unit (GPU) chip over the interposer, multiple second metal bumps between the interposer and the GPU chip, and a second underfill between the interposer and the GPU chip, wherein the second underfill encloses the second metal bumps.

19. The chip package of claim 11, wherein each of the non-volatile memory cells comprises a N-type MOS transistor having a gate terminal coupling to a gate terminal of a P-type MOS transistor of said each of the non-volatile memory cells, wherein the gate terminal of the floating-gate N-type MOS transistor and gate terminal of the floating-gate P-type MOS transistor are floating.

20. The chip package of claim 11, wherein each of the non-volatile memory cells comprises a resistive random access memory.

Description

PRIORITY CLAIM

[0001] This application claims priority benefits from U.S. provisional application No. 62/557,727, filed on Sep. 12, 2017 and entitled "LOGIC DRIVE BASED ON STANDARD COMMODITY FPGA IC CHIPS USING NON-VOLATILE MEMORY CELLS"; U.S. provisional application No. 62/630,369, filed on Feb. 14, 2018 and entitled "LOGIC DRIVE WITH BRAIN-LIKE PLASTICITY AND INTEGRALITY"; and U.S. provisional application No. 62/675,785, filed on May 24, 2018 and entitled "LOGIC DRIVE WITH BRAIN-LIKE ELASTICITY AND INTEGRALITY". The present application incorporates the foregoing disclosures herein by reference.

BACKGROUND OF THE DISCLOSURE

Field of the Disclosure

[0002] The present invention relates to a logic package, logic package drive, logic device, logic module, logic drive, logic disk, logic disk drive, logic solid-state disk, logic solid-state drive, Field Programmable Gate Array (FPGA) logic disk, or FPGA logic drive (to be abbreviated as "logic drive" below, that is when "logic drive" is mentioned below, it means and reads as "logic package, logic package drive, logic device, logic module, logic drive, logic disk, logic disk drive, logic solid-state disk, logic solid-state drive, FPGA logic disk, or FPGA logic drive") comprising plural FPGA IC chips, and more particularly to a standardized commodity logic drive formed by using plural standardized commodity FPGA IC chips. The logic drive is to be used for different specific applications when field programmed.

Brief Description of the Related Art

[0003] The Field Programmable Gate Array (FPGA) semiconductor integrated circuit (IC) has been used for development of new or innovated applications, or for small volume applications or business demands. When an application or business demand expands to a certain volume and extend to a certain time period, the semiconductor IC suppliers may usually switch to implement the application in an Application Specific IC (ASIC) chip, or a Customer-Owned Tooling (COT) IC chip. The switch from the FPGA design to the ASIC or COT design is because the current FPGA IC chip, for a given application and compared with an ASIC or COT chip, (1) has a larger semiconductor chip size, lower fabrication yield, and higher fabrication cost, (2) consumes more power, (3) gives lower performance. When the semiconductor technology nodes or generations migrates, following the Moore's Law, to advanced nodes or generations (for example below 20 nm), the Non-Recurring Engineering (NRE) cost for designing an ASIC or COT chip increases greatly (more than US $5M or even exceeding US $10M, US $20M, US $50M or US $100M). The cost of a photo mask set for an ASIC or COT chip at the 16 nm technology node or generation may be over US $2M, US $5M, or US $10M. The high NRE cost in implementing the innovation or application using the advanced IC technology nodes or generations slows down or even stops the innovation or application using advanced and useful semiconductor technology nodes or generations. A new approach or technology is needed to inspire the continuing innovation and to lower down the barrier for implementing the innovation in the semiconductor IC chips.

SUMMARY OF THE DISCLOSURE

[0004] One aspect of the disclosure provides a standardized commodity logic drive in a multi-chip package comprising plural standardized commodity FPGA IC chips for use in different applications requiring logic, computing and/or processing functions by field programming Uses of the standardized commodity logic drive is analogues to uses of a standardized commodity data storage solid-state disk (drive), data storage hard disk (drive), data storage floppy disk, Universal Serial Bus (USB) flash drive, USB drive, USB stick, flash-disk, or USB memory, and differs in that the latter has memory functions for data storage, while the former has logic functions for processing and/or computing. Uses of the standardized commodity FPGA IC chips is analogues to uses of a standardized commodity data storage memory IC chips, for example, standard commodity DRAM chips or standard commodity NAND flash chips, and differs in that the latter has memory functions for data storage, while the former has logic functions for processing and/or computing.

[0005] Another aspect of the disclosure provides a method to reduce Non-Recurring Engineering (NRE) expenses for implementing an innovation and/or an application in semiconductor IC chips by using the standardized commodity logic drive comprising plural standardized commodity FPGA IC chips. A person, user, or developer with an innovation and/or an application concept or idea needs to purchase the standardized commodity logic drive and develops or writes software codes or programs to load into the standardized commodity logic drive to implement his/her innovation and/or application concept or idea; wherein said innovation and/or application (maybe abbreviated as innovation) comprises (i) innovative algorithms and/or architectures of computing, processing, learning and/or inferencing, and/or (ii) innovative and/or specific applications. Compared to the implementation by developing a logic ASIC or COT IC chip, the NRE cost may be reduced by a factor of larger than 2, 5, 10, 30, 50 or 100 using the disclosed standardized commodity logic drive. For advanced semiconductor technology nodes or generations (for example more advanced than or below 20 nm), the NRE cost for designing an ASIC or COT chip increases greatly, more than US $5M or even exceeding US $10M, US $20M, US $50M, or US $100M. The cost of a photo mask set for an ASIC or COT chip at the 16 nm technology node or generation may be over US $2M, US $5M, or US $10M. Implementing the same or similar innovation and/or application using the logic drive may reduce the NRE cost down to smaller than US $10M or even less than US $5M, US $3M, US $2M or US $1M. The aspect of the disclosure inspires the innovation and lowers the barrier for implementing the innovation in IC chips designed and fabricated using an advanced IC technology node or generation, for example, a technology node or generation more advanced than or below 20 nm or 10 nm.

[0006] Another aspect of the disclosure provides a "public innovation platform" for innovators to easily and cheaply implement or realize their innovation in semiconductor IC chips using advanced IC technology nodes more advanced than 20 nm, and for example, using a technology node of 16 nm, 10 nm, 7 nm, 5 nm or 3 nm, by using logic drives; wherein said innovation comprises (i) innovative algorithms or architectures of computing, processing, learning and/or inferencing, and/or (ii) innovative and/or specific applications. In years of 1990's, innovators could implement their innovation by designing IC chips and fabricating the IC chips in a semiconductor manufacturing foundry fab using technology nodes at 1 .mu.m, 0.8 .mu.m, 0.5 .mu.m, 0.35 .mu.m, 0.18 .mu.m or 0.13 .mu.m, at a cost of about several hundred thousand US dollars. The semiconductor manufacturing foundry companies are productless companies and own semiconductor manufacturing fabs. They provide manufacturing services to their customers. The customers are fabless companies, which include (i) IC chip design companies designing and owning the IC chips, (ii) system companies designing and owning the systems, (iii) IC chip designing individuals designing and owning IC chips. The IC manufacturing foundry fab then was the "public innovation platform". However, when IC technology nodes migrate to a technology node more advanced than 20 nm, and for example to the technology node of 16 nm, 10 nm, 7 nm, 5 nm or 3 nm IC technology nodes, only a few giant system or IC design companies, not the public innovators, can afford to use the semiconductor IC manufacturing foundry fab. It costs about or over 10 million US dollars to develop and implement an IC chip using these advanced technology nodes. The semiconductor IC manufacturing foundry fab is now not the "public innovation platform" anymore, they are becoming a "club innovation platform" for club innovators. The disclosed logic drives, comprising standard commodity FPGA IC chips, provides public innovators the "public innovation platform" back to semiconductor IC industry again just as in 1990's. The innovators can implement or realize their innovation (algorithms, architectures and/or applications) by using the standard commodity of logic drives and writing software programs using common programing languages, for example, C, Java, C++, C#, Scala, Swift, Matlab, Assembly Language, Pascal, Python, Visual Basic, PL/SQL or JavaScript languages, at cost of less than 500K or 300K US dollars. The innovators can use their own commodity logic drives or they can rent logic drives in data centers or clouds through networks.

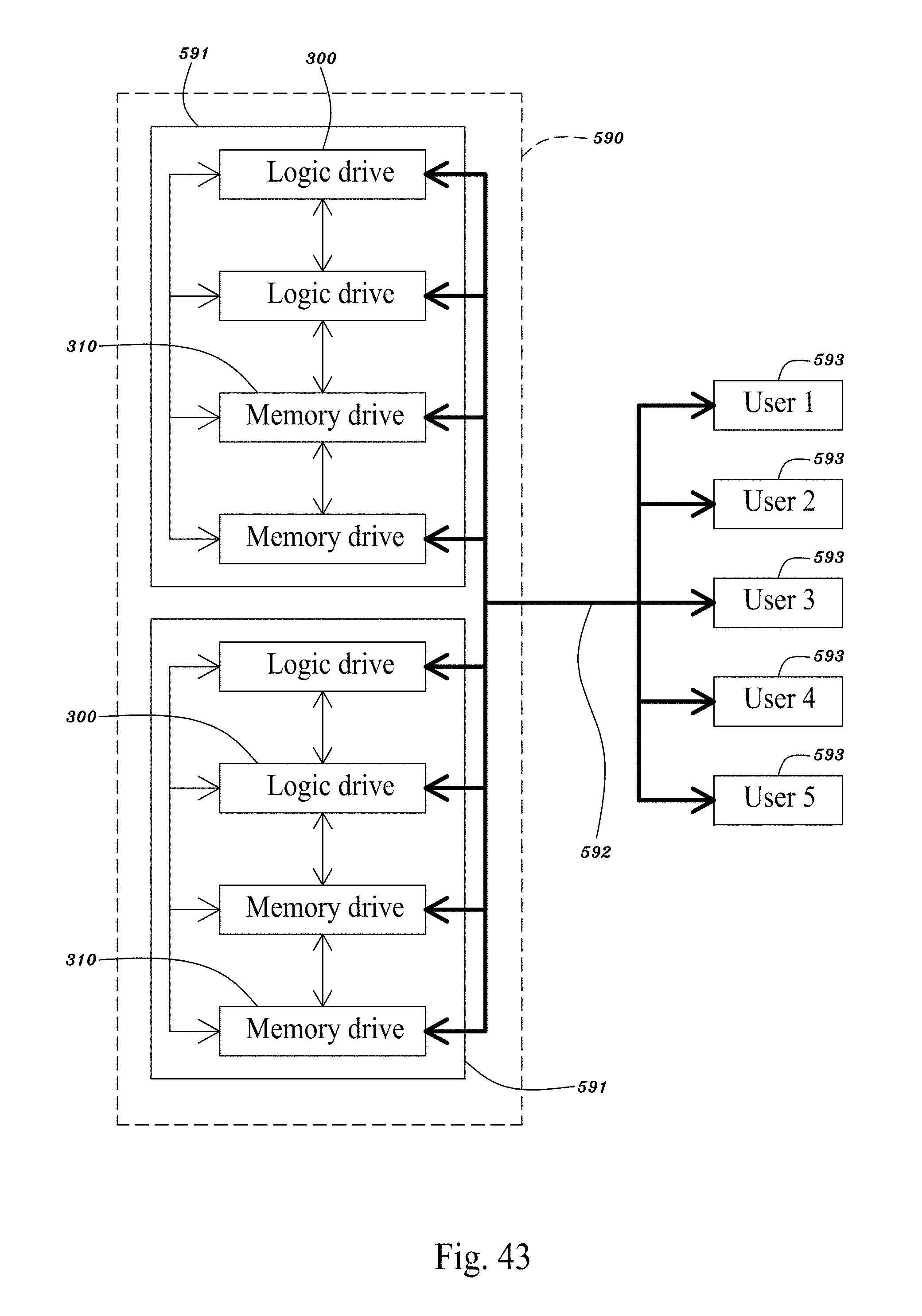

[0007] Another aspect of the disclosure provides an innovation platform for an innovator, comprising: multiple logic drives in a data center or a cloud, wherein multiple logic drives comprise multiple standard commodity FPGA IC chips fabricated using a semiconductor IC process technology node more advanced than 20 nm technology node; an innovator's device and multiple users' devices communicating with the multiple logic drives in the data center or the cloud through an internet or a network, wherein the innovator develops and writes software programs to implement his innovation (algorithms, architectures and/or applications) in a common programing language to program, through the internet or the network, the multiple logic drives in the data center or the cloud, wherein the common programing language comprises Java, C++, C#, Scala, Swift, Matlab, Assembly Language, Pascal, Python, Visual Basic, PL/SQL or JavaScript language; after programming the logic drives, the innovator or the multiple users may use the programed logic drives for his or their innovations (algorithms, architectures and/or applications) through the internet or the network; wherein said innovations comprise (i) innovative algorithms or architectures of computing, processing, learning and/or inferencing, and/or (ii) innovative and/or specific applications.

[0008] Another aspect of the disclosure provides a method to change the current logic ASIC or COT IC chip business into a commodity logic IC chip business, like the current commodity DRAM, or commodity flash memory IC chip business, by using the standardized commodity logic drive. Since the performance, power consumption, and engineering and manufacturing costs of the standardized commodity logic drive may be better or equal to that of the ASIC or COT IC chip for a same innovation (algorithms, architectures and/or applications), the standardized commodity logic drive may be used as an alternative for designing an ASIC or COT IC chip. The current logic ASIC or COT IC chip design, manufacturing and/or product companies (including fabless IC design and product companies, or IC foundry or contracted manufacturers (may be product-less), and/or vertically-integrated IC design, manufacturing and product (IDM) companies) may become companies like the current commodity DRAM, or flash memory IC chip design, manufacturing, and/or product companies; or like the current DRAM module design, manufacturing, and/or product companies; or like the current flash memory module, flash USB stick or drive, or flash solid-state drive or disk drive design, manufacturing, and/or product companies. The current logic ASIC or COT IC chip design and/or manufacturing companies (including fabless IC design and product companies, IC foundry or contracted manufacturers (may be product-less), vertically-integrated IC design, manufacturing and product companies) may become companies in the following business models: (1) designing, manufacturing, and/or selling the standard commodity FPGA IC chips; and/or (2) designing, manufacturing, and/or selling the standard commodity logic drives. The business model is similar to the current commodity DRAM or flash memory chip and module business. A person, user, customer, or software developer, or algorithm/architecture/application developer may purchase the standardized commodity logic drive and write software codes to program them for his/her desired algorithms, architectures and/or applications, for example, in algorithms, architectures and/or applications of Artificial Intelligence (AI), machine learning, deep learning, big data, Internet Of Things (IOT), industry computers, Virtual Reality (VR), Augmented Reality (AR), self-drive or driver-less car, Graphic Processing (GP), Digital Signal Processing (DSP), Micro Controlling (MC), and/or Central Processing (CP). The logic drive may be programed to perform functions like a graphic chip, or a baseband chip, or an Ethernet chip, or a wireless (for example, 802.11ac) chip, or an AI chip. The logic drive may be alternatively programmed to perform functions of all or any combinations of functions of Artificial Intelligence (AI), machine learning, deep learning, big data, Internet Of Things (IOT), industry computers, Virtual Reality (VR), Augmented Reality (AR), car electronics, Graphic Processing (GP), Digital Signal Processing (DSP), Micro Controlling (MC), and/or Central Processing (CP). The logic drive may be field programmed as an accelerator for, for example, the AI functions, in the user-end, data center or cloud, in the algorithms, architectures and/or applications of training and/or inferring of the AI functions.

[0009] Another aspect of the disclosure provides a method to change the current logic ASIC or COT IC chip hardware business into a software business by using the standardized commodity logic drive. Since the performance, power consumption, and engineering and manufacturing costs of the standardized commodity logic drive may be better or equal to that of the ASIC or COT IC chip for a same innovation (algorithms, architectures and/or applications), the standardized commodity logic drive may be used as an alternative for designing an ASIC or COT IC chip. The current ASIC or COT IC chip design companies or suppliers may become software developers or suppliers; they may adapt the following business models: (1) become software companies to develop and sell software for their innovation (algorithms, architectures and/or applications), and let their customers or users to install software in the customers' or users' own standard commodity logic drive; and/or (2) still hardware companies by selling hardware without performing ASIC or COT IC chip design and/or production. In the case (2), they may install their in-house developed software for the innovation (algorithms, architectures and/or applications) in the purchased standard commodity logic drive; and sell the program-installed logic drive to their customers or users. In both cases (1) and (2), either the customers/users or developers/companies may write software codes into the standard commodity logic drive (that is, loading the software codes in the standardized commodity logic drive) for their desired algorithms, architectures and/or applications, for example, in algorithms, architectures and/or applications of Artificial Intelligence (AI), machine learning, deep learning, big data, Internet Of Things (IOT), industry computers, car electronics, Virtual Reality (VR), Augmented Reality (AR), Graphic Processing, Digital Signal Processing, micro controlling, and/or Central Processing. The logic drive may be programed to perform functions like a graphic chip, or a baseband chip, or an Ethernet chip, or a wireless (for example, 802.11ac) chip, or an AI chip. The logic drive may be alternatively programmed to perform functions of all or any combinations of functions of Artificial Intelligence (AI), machine learning, deep learning, big data, Internet Of Things (IOT), industry computers, car electronics, Virtual Reality (VR), Augmented Reality (AR), car electronics, Graphic Processing (GP), Digital Signal Processing (DSP), Micro Controlling (MC), and/or Central Processing (CP).

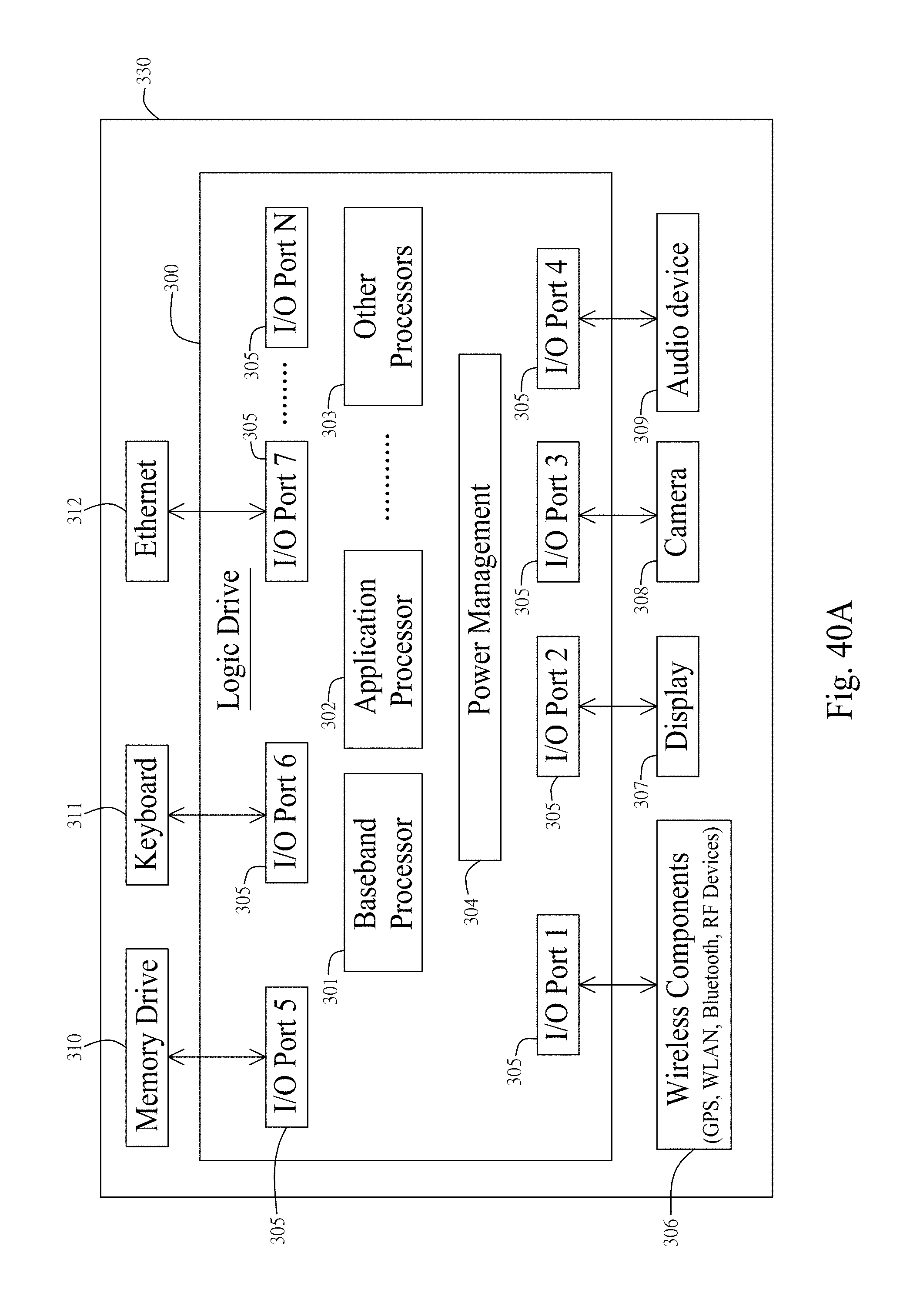

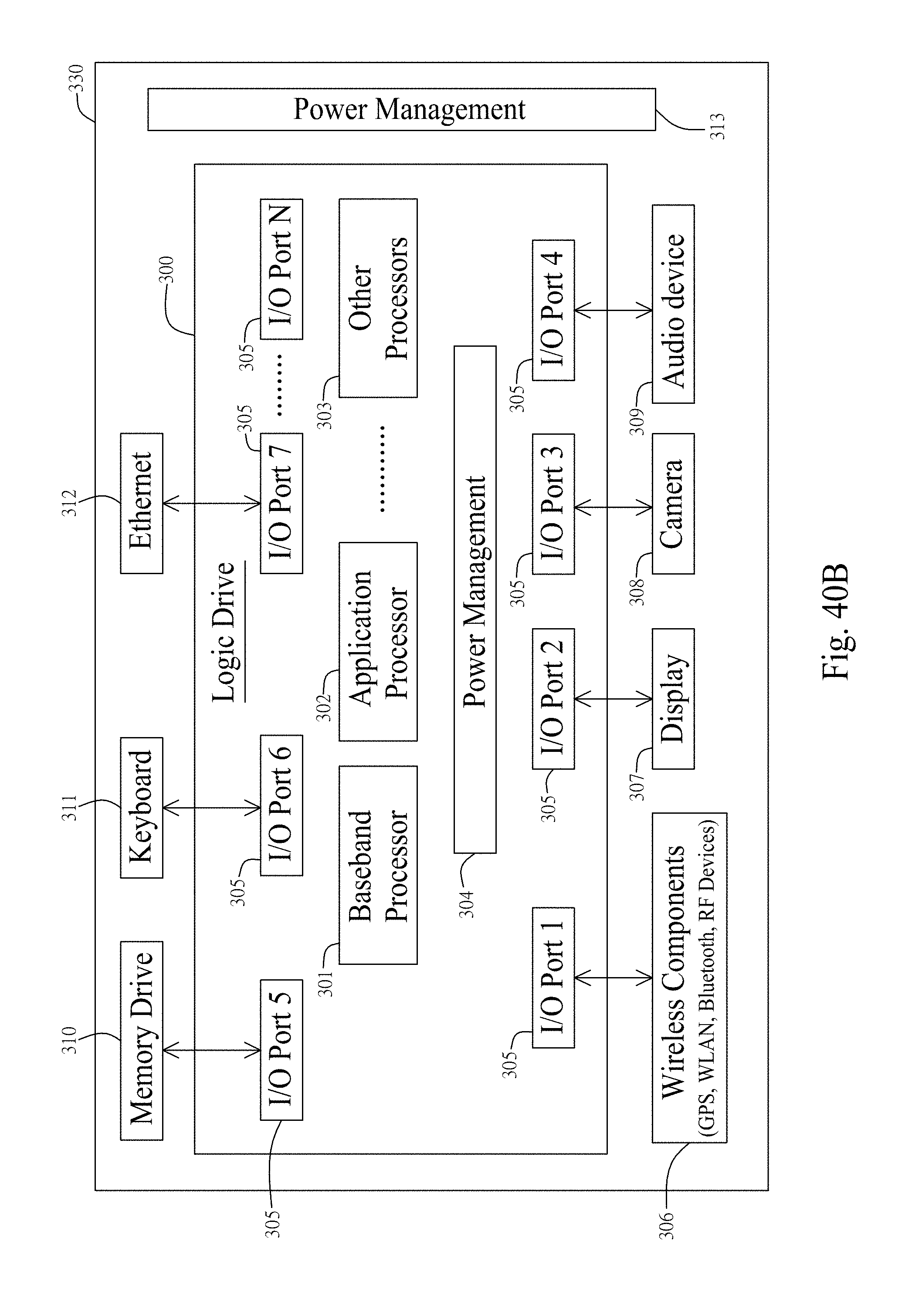

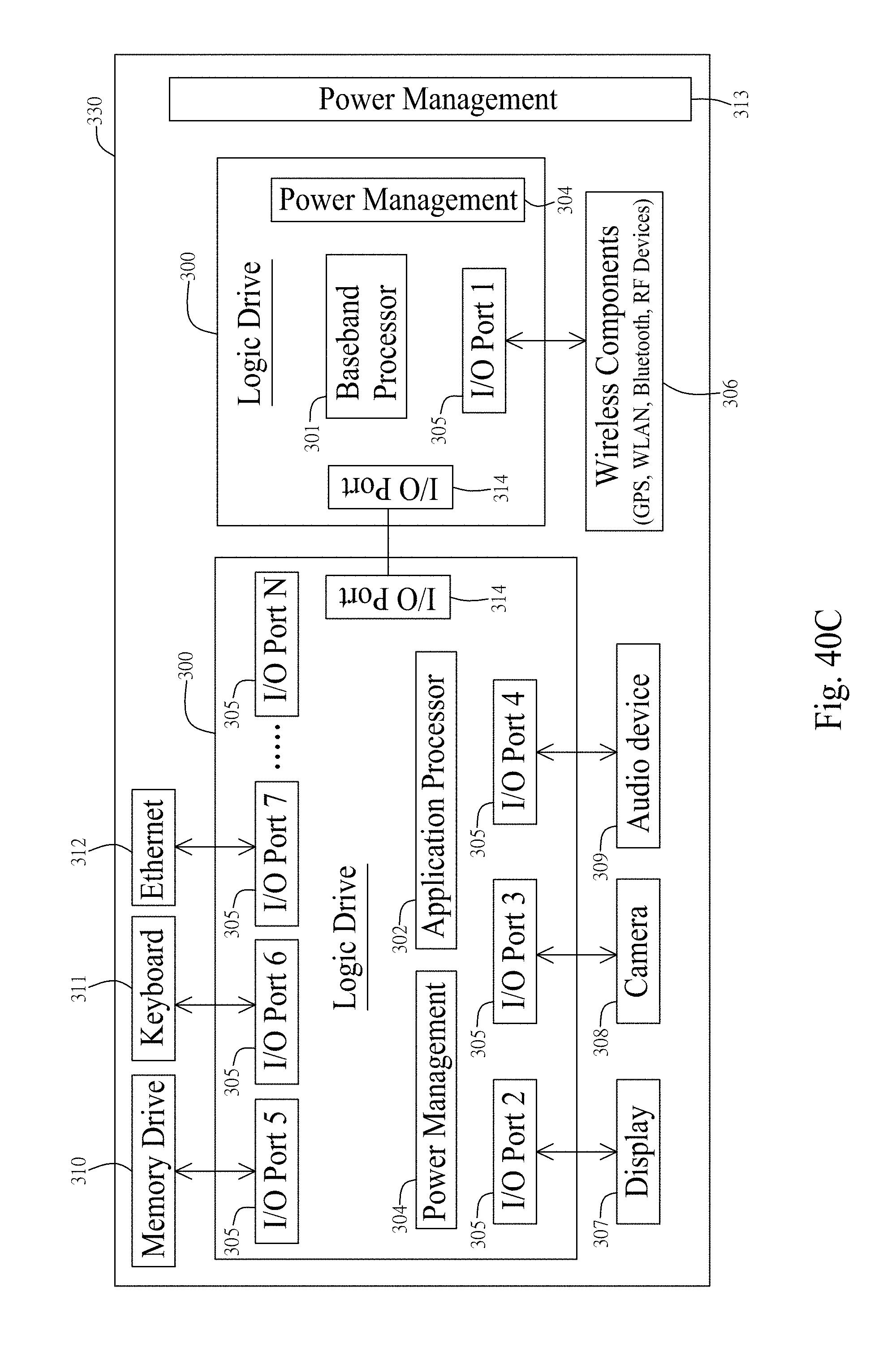

[0010] Another aspect of the disclosure provides a method to change the current system design, manufactures and/or product business into a commodity system/product business, like current commodity DRAM, or flash memory business, by using the standardized commodity logic drive. The system, computer, processor, smart-phone, or electronic equipment or device may become a standard commodity hardware comprises mainly a memory drive and a logic drive. The memory drive may be a hard disk drive, a flash drive, and/or a solid-state drive. The logic drive in the aspect of the disclosure may have big enough or adequate number of inputs/outputs (I/Os) to support I/O ports for used for programming all or most applications. The logic drive may have I/Os to support required I/O ports for programming, for example, to perform all or any combinations of functions of Artificial Intelligence (AI), machine learning, deep learning, big data, Internet Of Things (TOT), industry computers, Virtual Reality (VR), Augmented Reality (AR), car electronics, Graphic Processing (GP), Digital Signal Processing (DSP), Micro Controlling (MC), and/or Central Processing (CP), and etc. The logic drive may comprise (1) programing or configuration I/Os for software, algorithm, architecture and/or application developers to load algorithm, architecture and/or application software or program codes to program or configure the logic drive, through I/O ports or connectors connecting or coupling to the I/Os of the logic drive; and (2) operation, execution or user I/Os for the users to operate, execute and perform their instructions, through I/O ports or connectors connecting or coupling to the I/Os of the logic drive; for example, generating a Microsoft Word file, or a PowerPoint presentation file, or an Excel file. The I/O ports or connectors connecting or coupling to the corresponding I/Os of the logic drive may comprise one or multiple (2, 3, 4, or more than 4) Universal Serial Bus (USB) ports, one or more IEEE 1394 ports, one or more Ethernet ports, one or more audio ports or serial ports, for example, RS-232 or COM (communication) ports, wireless transceiver I/Os, and/or Bluetooth transceiver I/Os, and etc. The I/O ports or connectors connecting or coupling to the corresponding I/Os of the logic drive may also comprise Serial Advanced Technology Attachment (SATA) ports, or Peripheral Components Interconnect express (PCIe) ports for communicating, connecting or coupling with or to the memory drive. The I/O ports or connectors may be placed, located, assembled, or connected on or to a substrate, film or board; for example, a Printed Circuit Board (PCB), a silicon substrate with interconnection schemes, a metal substrate with interconnection schemes, a glass substrate with interconnection schemes, a ceramic substrate with interconnection schemes, a flexible film with interconnection schemes. The logic driver is assembled on the substrate, film or board using solder bumps, or copper pillars or bumps, on or of the logic drive, similar to the flip-chip assembly of the chip packaging technology, or the Chip-On-Film (COF) assembly technology used in the LCD driver packaging technology. The system, computer, processor, smart-phone, or electronic equipment or device design, manufacturing, and/or product companies may become companies to (1) design, manufacturing and/or sell the standard commodity hardware comprising a memory drive and a logic drive; in this case, the companies are still hardware companies; (2) develop system and algorithm, architecture and/or application software for users to install in the users' own standard commodity hardware; in this case, the companies become software companies; (3) install the third party's developed system and algorithm, architecture and/or application software or programs in the standard commodity hardware and sell the software-loaded hardware; and in this case, the companies are still hardware companies.

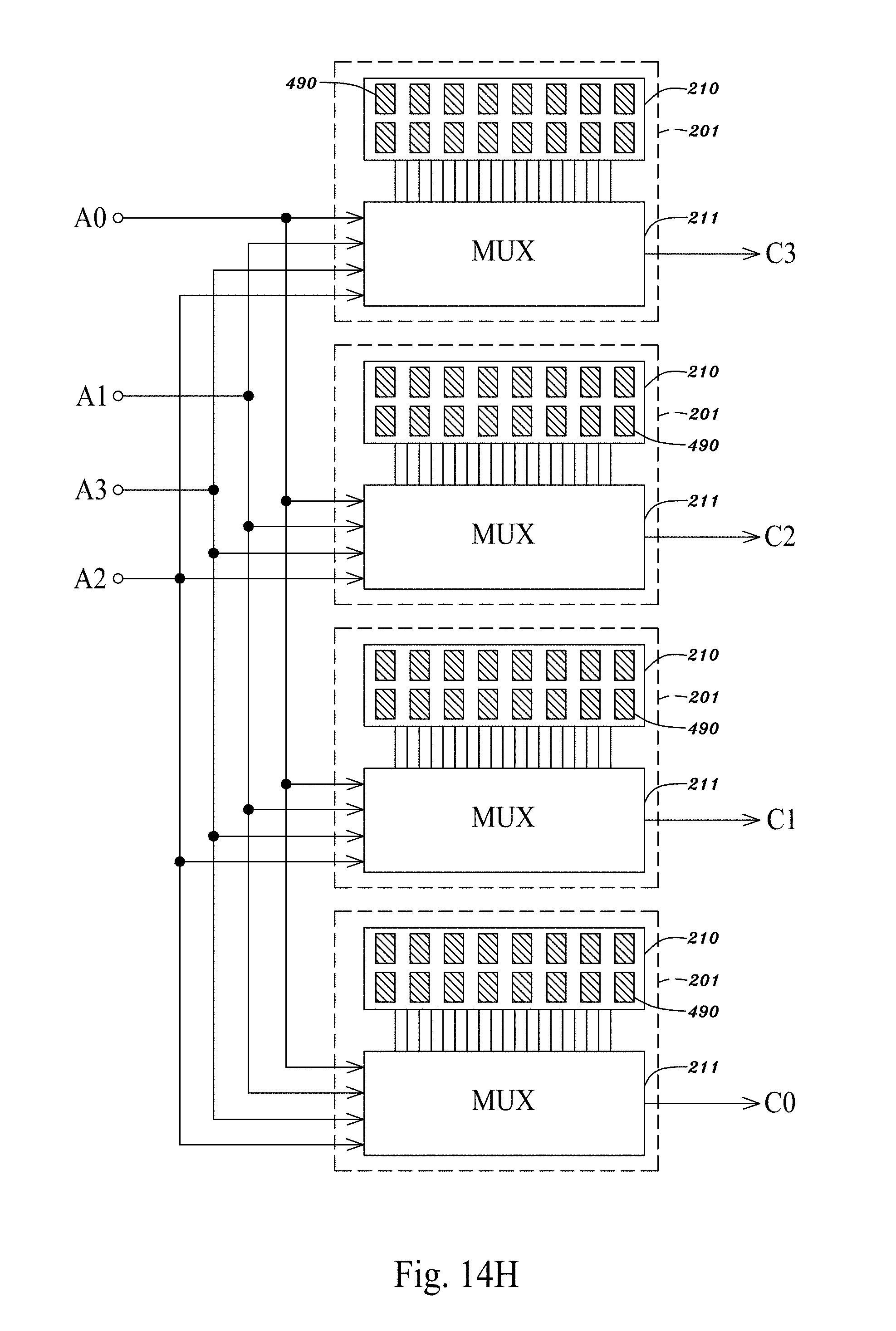

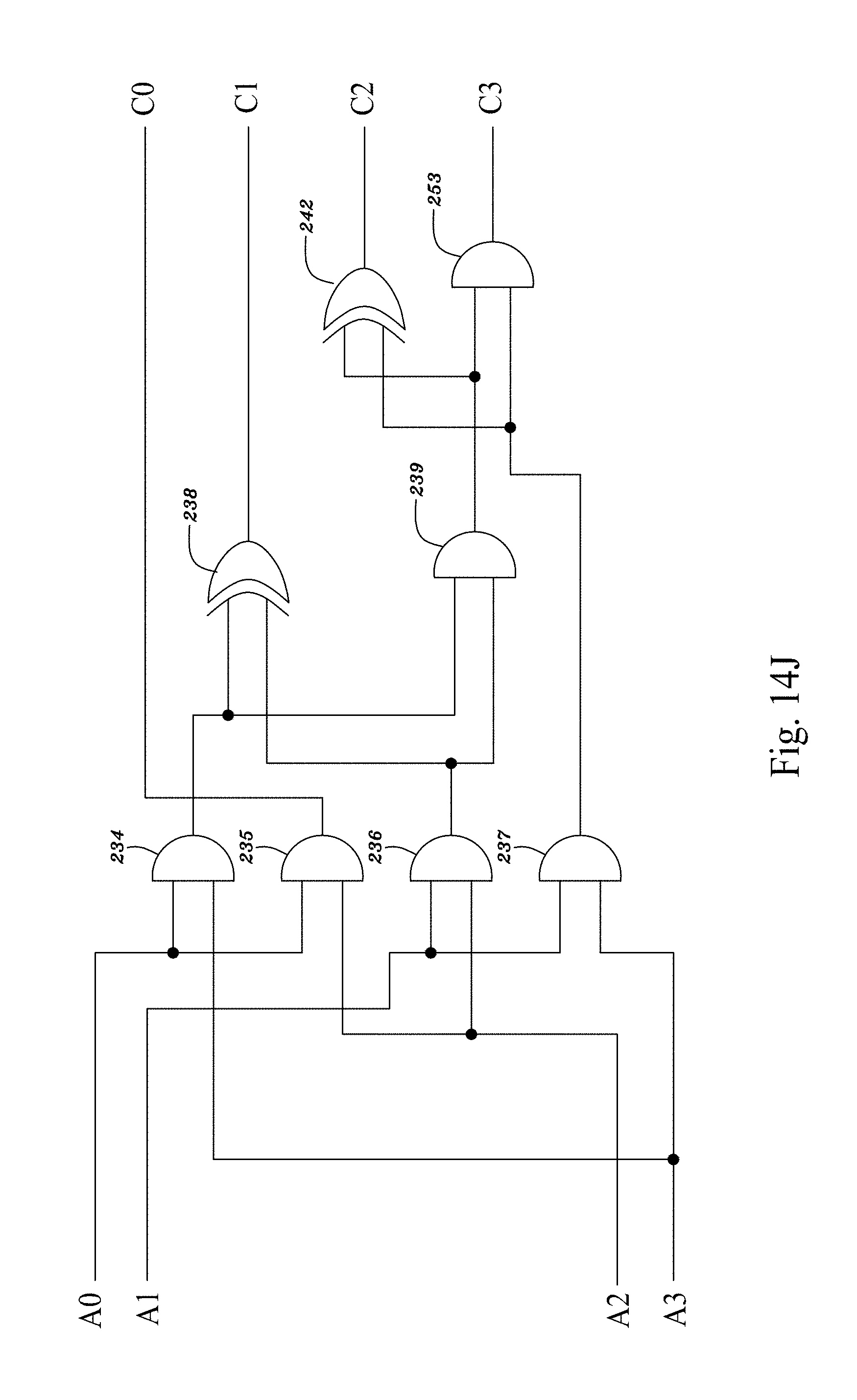

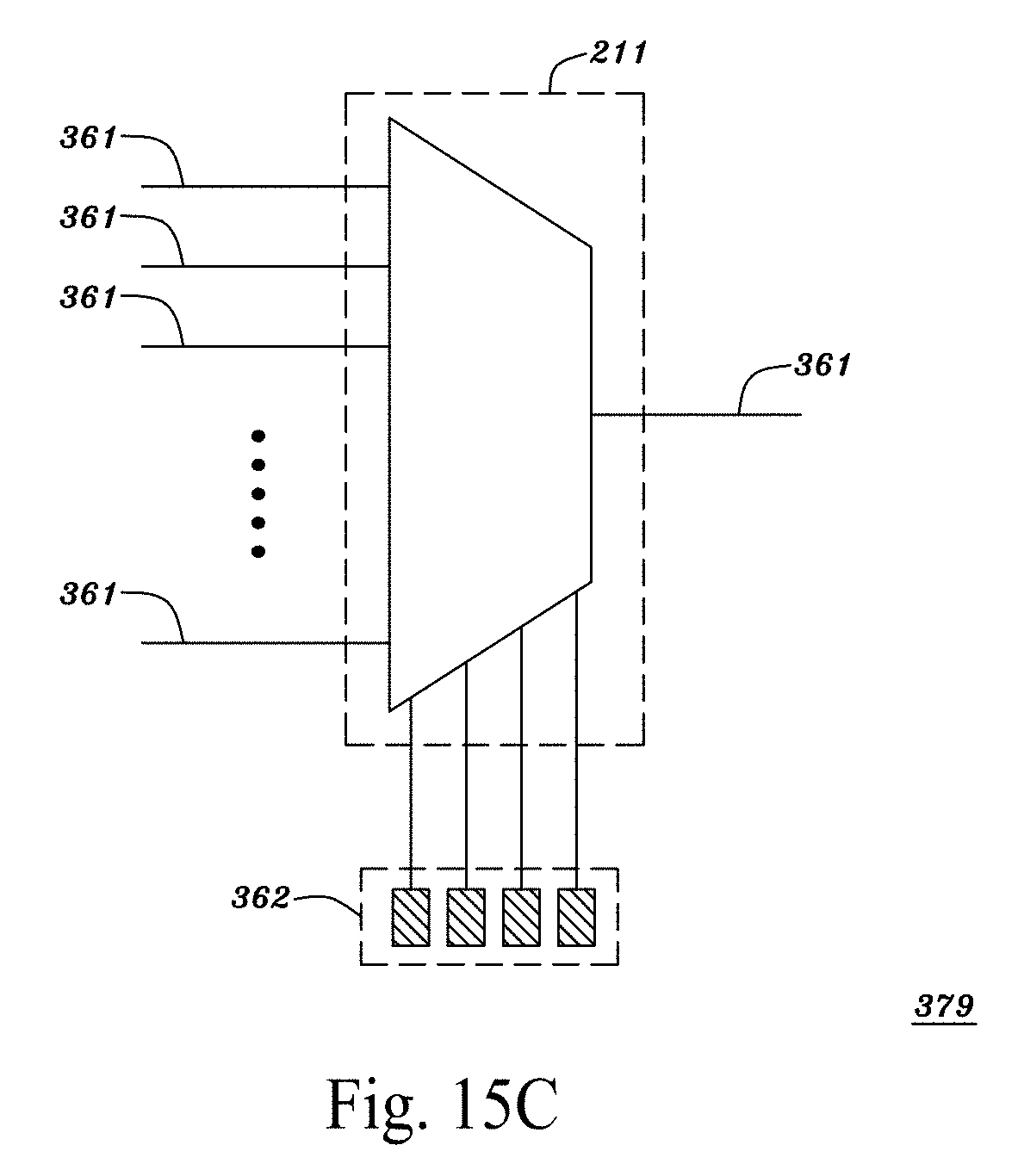

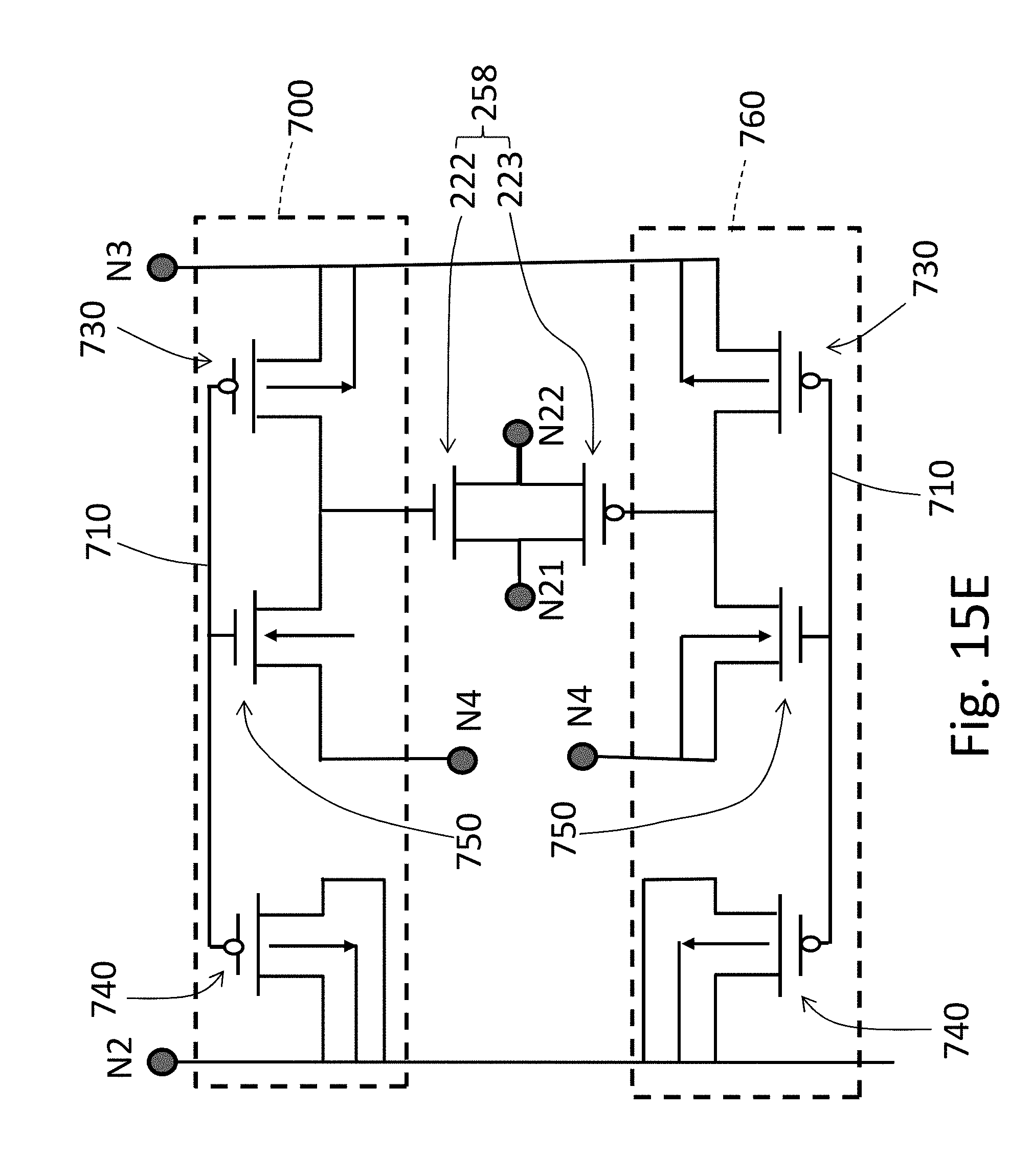

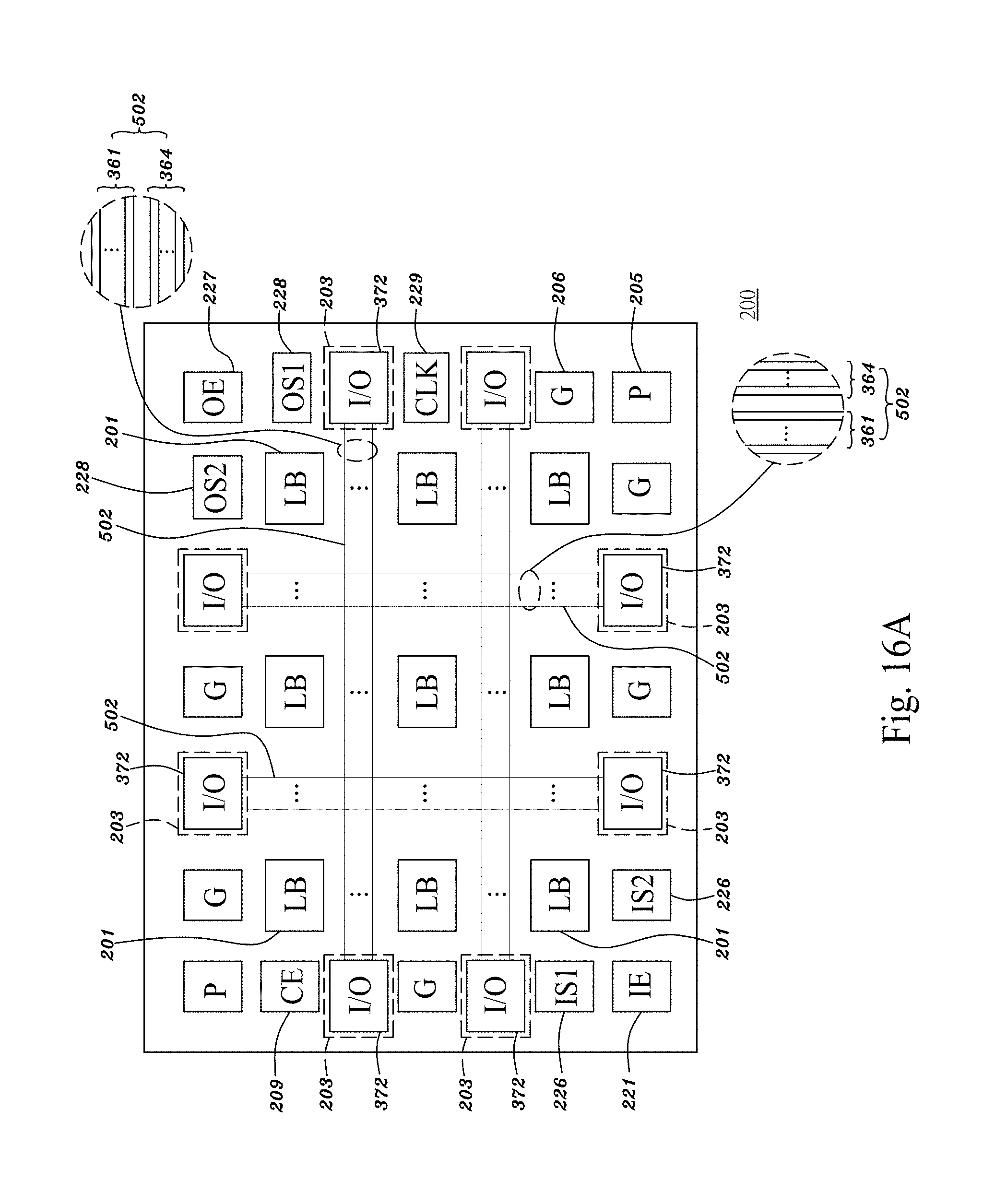

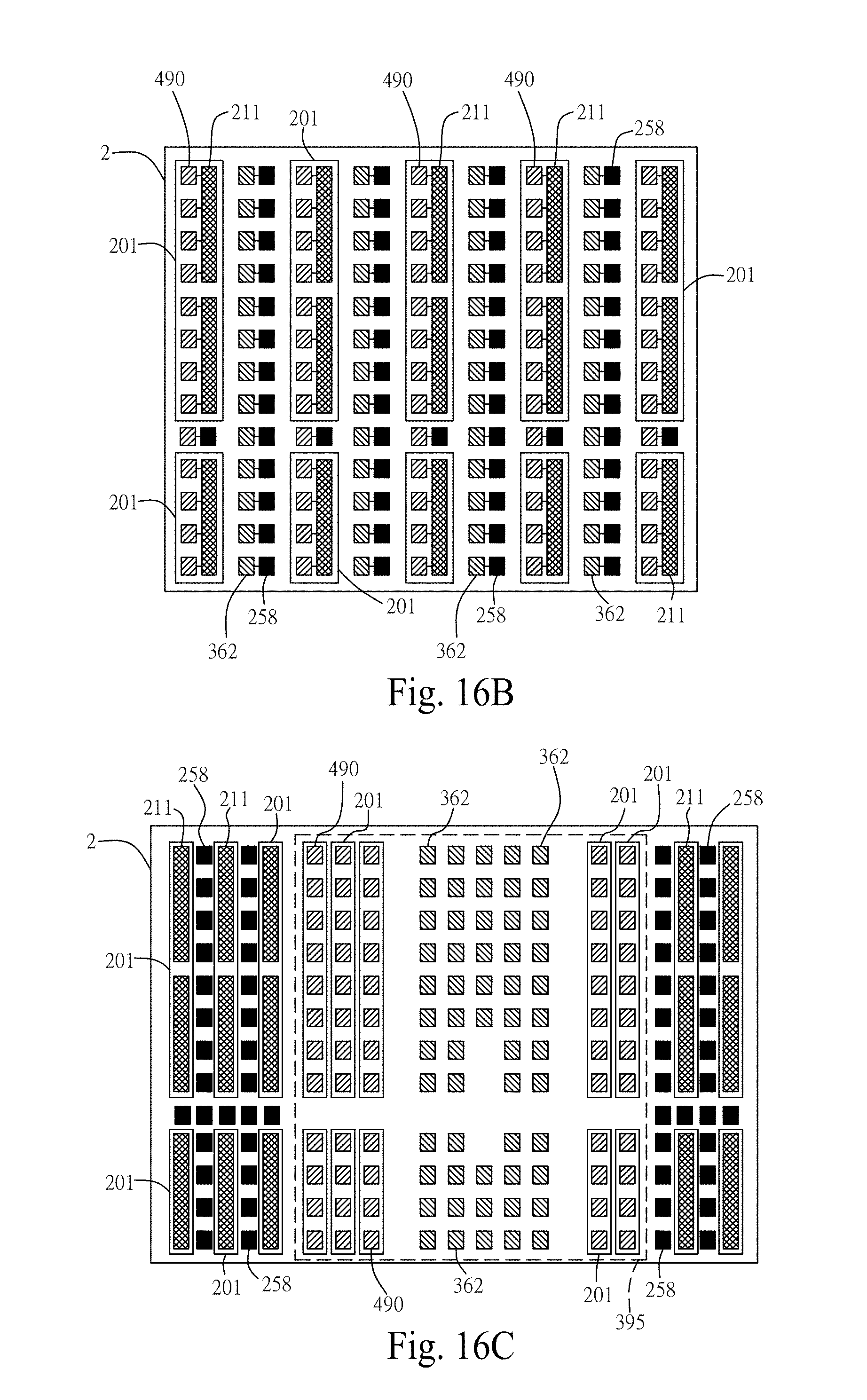

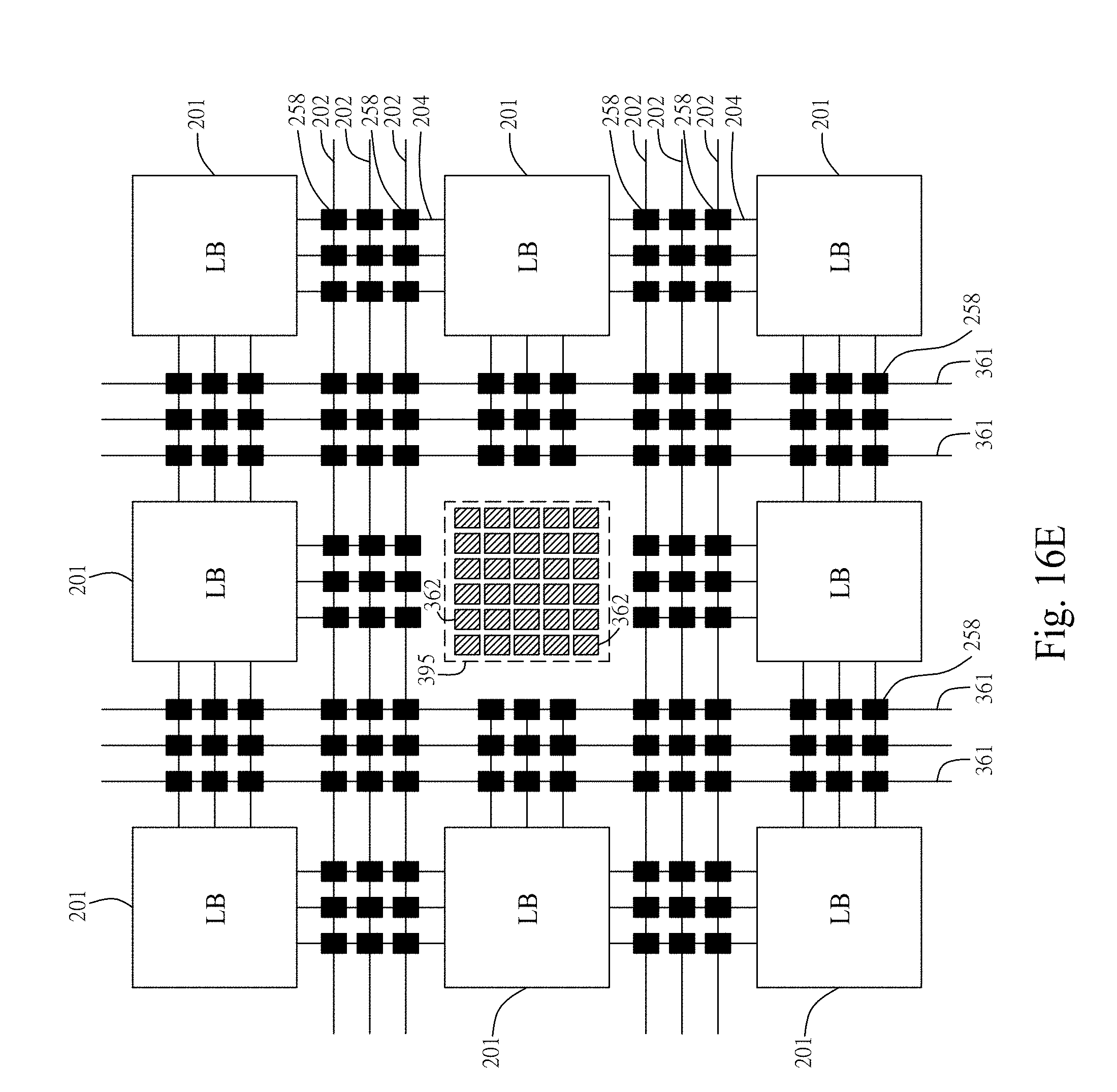

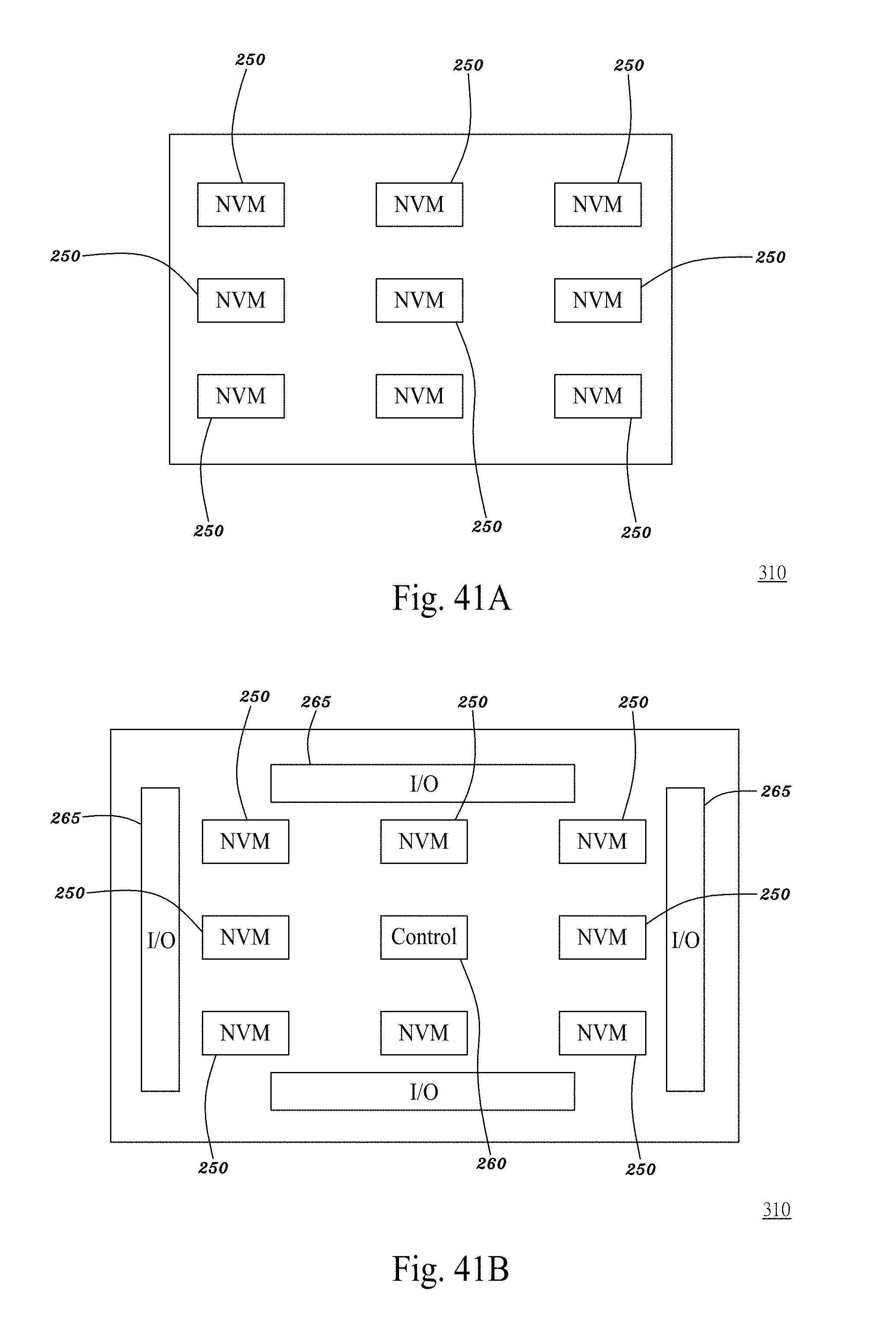

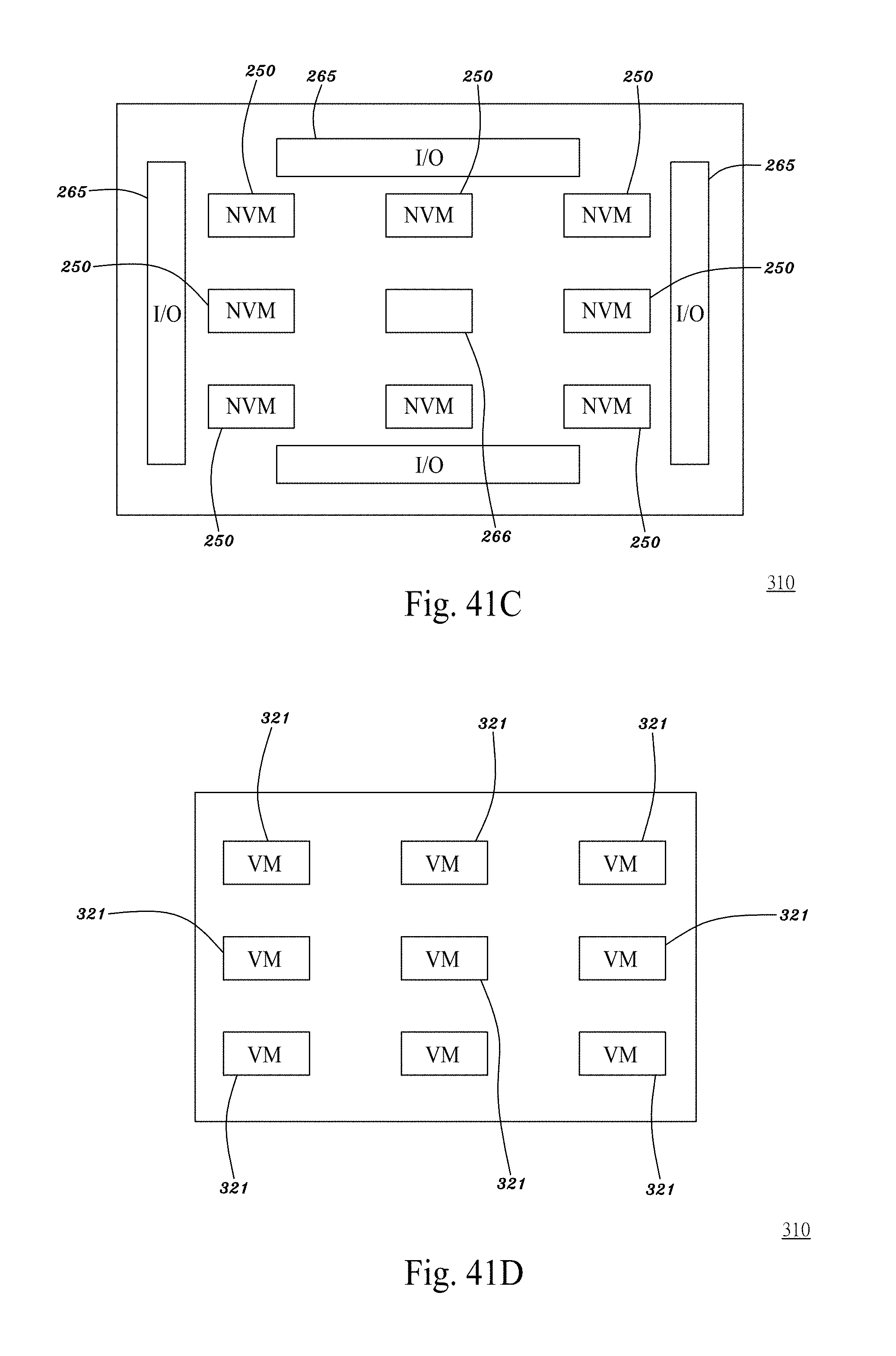

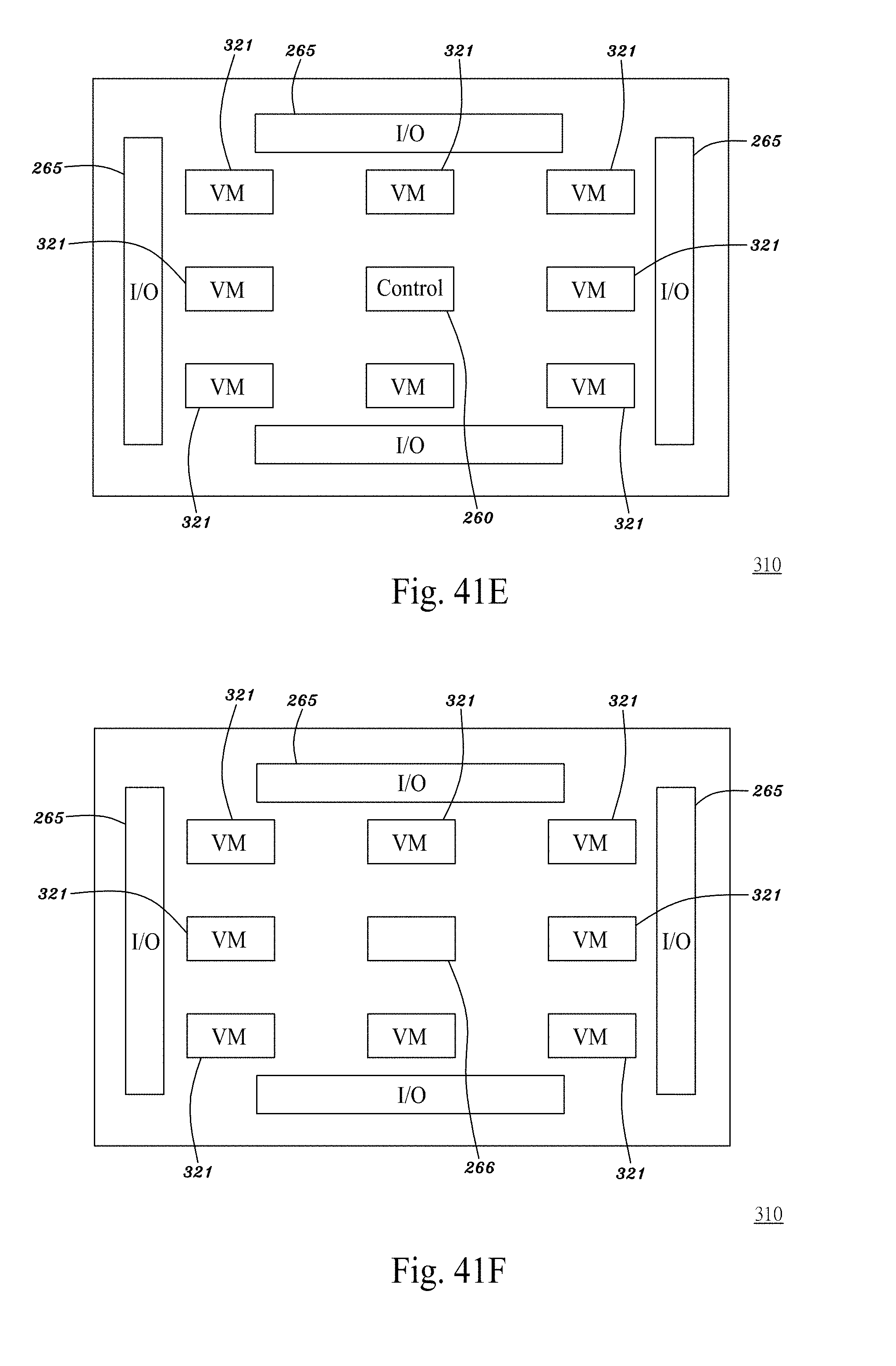

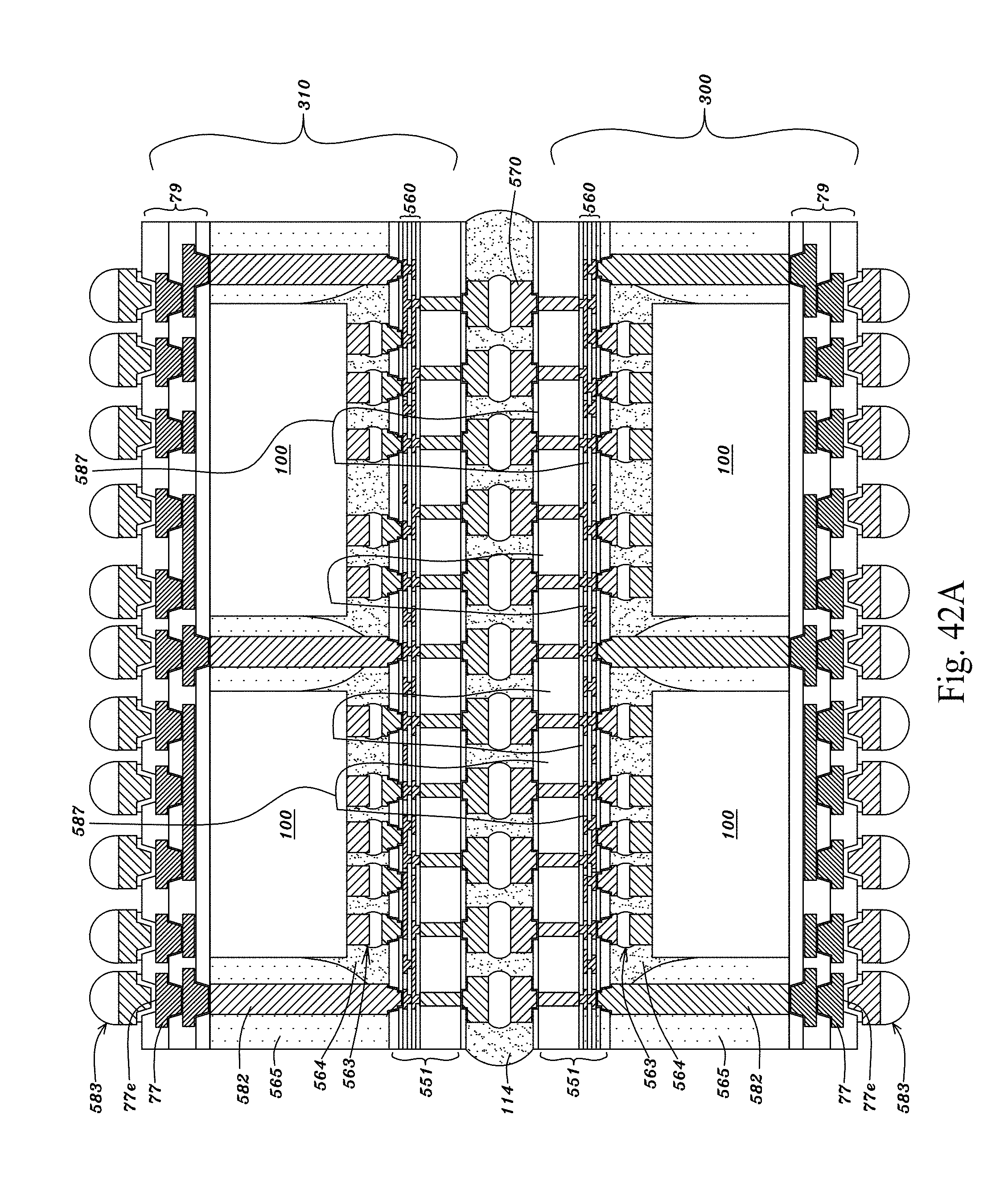

[0011] Another aspect of the disclosure provides a standard commodity FPGA IC chip for use in the standard commodity logic drive. The standard commodity FPGA IC chip is designed, implemented and fabricated using an advanced semiconductor technology node or generation, for example more advanced than or equal to, or below or equal to 20 nm or 10 nm, such as 16 nm, 14 nm, 12 nm, 10 nm, 7 nm, 5 nm or 3 nm; with a chip size and manufacturing yield optimized for the minimum manufacturing cost for the used semiconductor technology node or generation. The standard commodity FPGA IC chip may have an area between 400 mm.sup.2 and 9 mm.sup.2, 144 mm.sup.2 and 16 mm.sup.2, 75 mm.sup.2 and 16 mm.sup.2, or 50 mm.sup.2 and 16 mm.sup.2. Transistors used in the advanced semiconductor technology node or generation may be a FIN Field-Effect-Transistor (FINFET), a FINFET on Silicon-On-Insulator (FINFET SOI), a Fully Depleted Silicon-On-Insulator (FDSOI) MOSFET, a Partially Depleted Silicon-On-Insulator (PDSOI) MOSFET or a conventional MOSFET. The standard commodity FPGA IC chip may only communicate directly with other chips in or of the logic drive only; its I/O circuits may require only small I/O drivers or receivers, and small or none Electrostatic Discharge (ESD) devices. The driving capability, loading, output capacitance, or input capacitance of the small I/O drivers or receivers, or I/O circuits may be between 0.1 pF and 2 pF or 0.1 pF and 1 pF. The size of the small ESD device may be between 0.05 pF and 2 pF or 0.05 pF and 1 pF. For example, a bi-directional (or tri-state) I/O pad or circuit may comprise an ESD circuit, a receiver, and a driver, and has an input capacitance or output capacitance between 0.1 pF and 2 pF or 0.1 pF and 1 pF. All or most control and/or Input/Output (I/O) circuits or units (for example, the off-logic-drive I/O circuits, i.e., large I/O circuits, communicating with circuits or components external or outside of the logic drive) are outside of, or not included in, the standard commodity FPGA IC chip, but are included in another dedicated control chip, dedicated I/O chip, or dedicated control and I/O chip, packaged in the same logic drive. None or minimal area of the standard commodity FPGA IC chip is used for the control or I/O circuits, for example, less than 15%, 10%, 5% or 1% area is used for the control or IO circuits; or, none or minimal transistors of the standard commodity FPGA IC chip are used for the control or I/O circuits, for example, less than 15%, 10%, 5%, or 1% of the total number of transistors are used for the control or I/O circuits; or all or most area of the standard commodity FPGA IC chip is used for (i) logic blocks or functions comprising logic gate arrays, computing units or operators, and/or Look-Up-Tables (LUTs) and multiplexers, and/or (ii) programmable interconnection. For example, greater than 85%, 90%, 95% or 99% area is used for logic blocks/functions, and/or programmable interconnection; or, all or most transistors of the standard commodity FPGA IC chip are used for logic blocks/functions, and/or programmable interconnection, for example, greater than 85%, 90%, 95% or 99% of the total number of transistors are used for logic blocks/functions, and/or programmable interconnection.

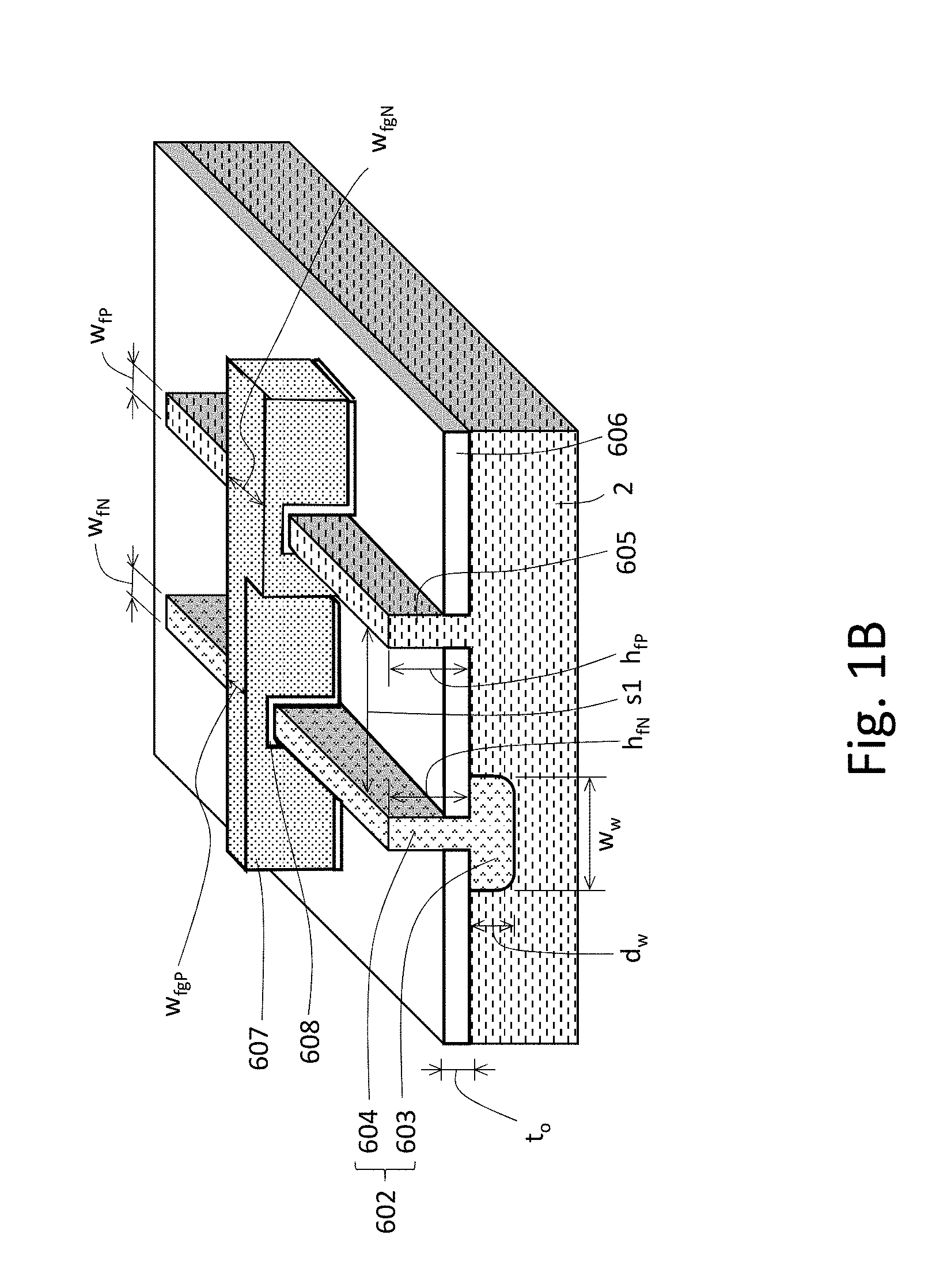

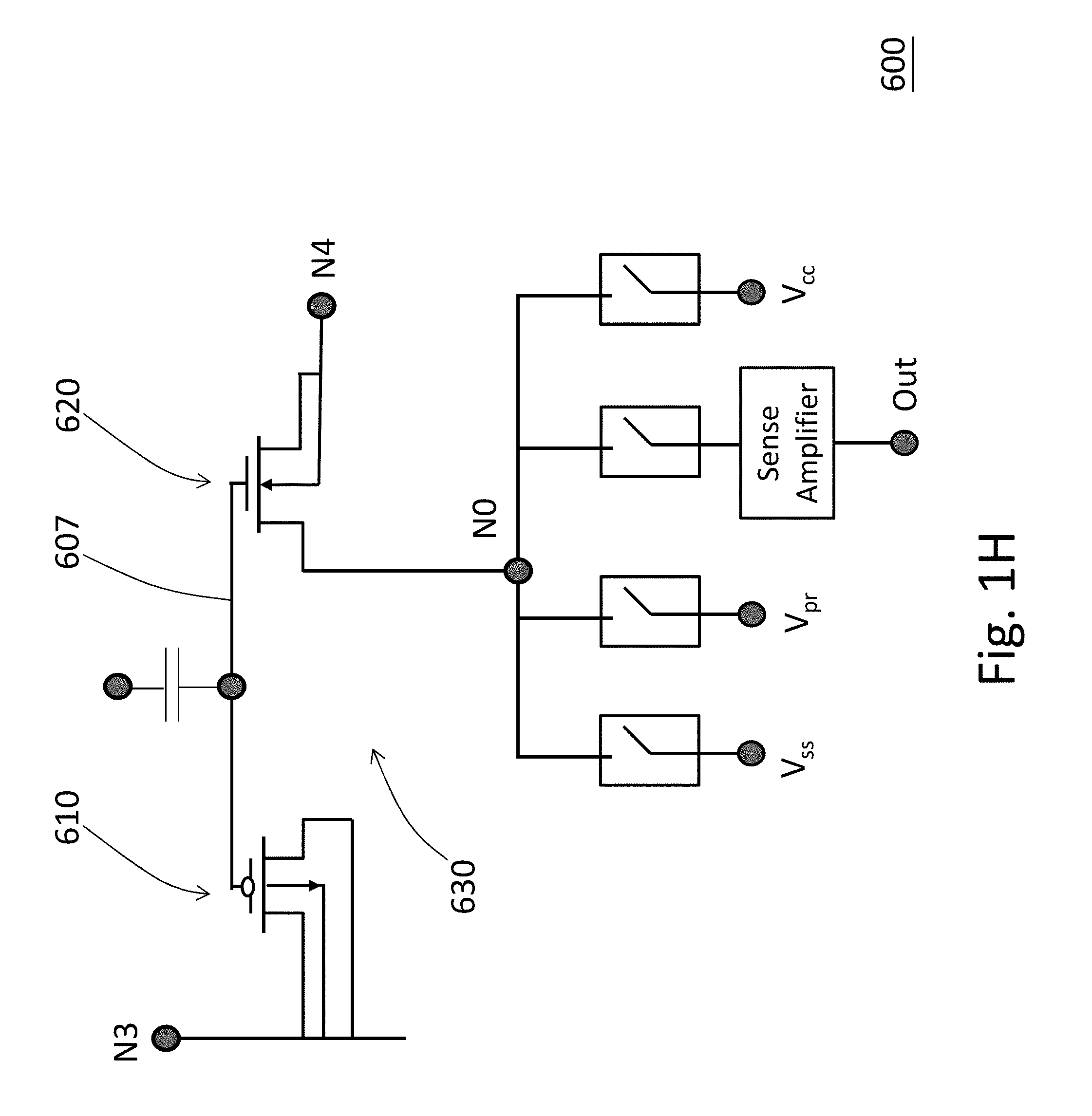

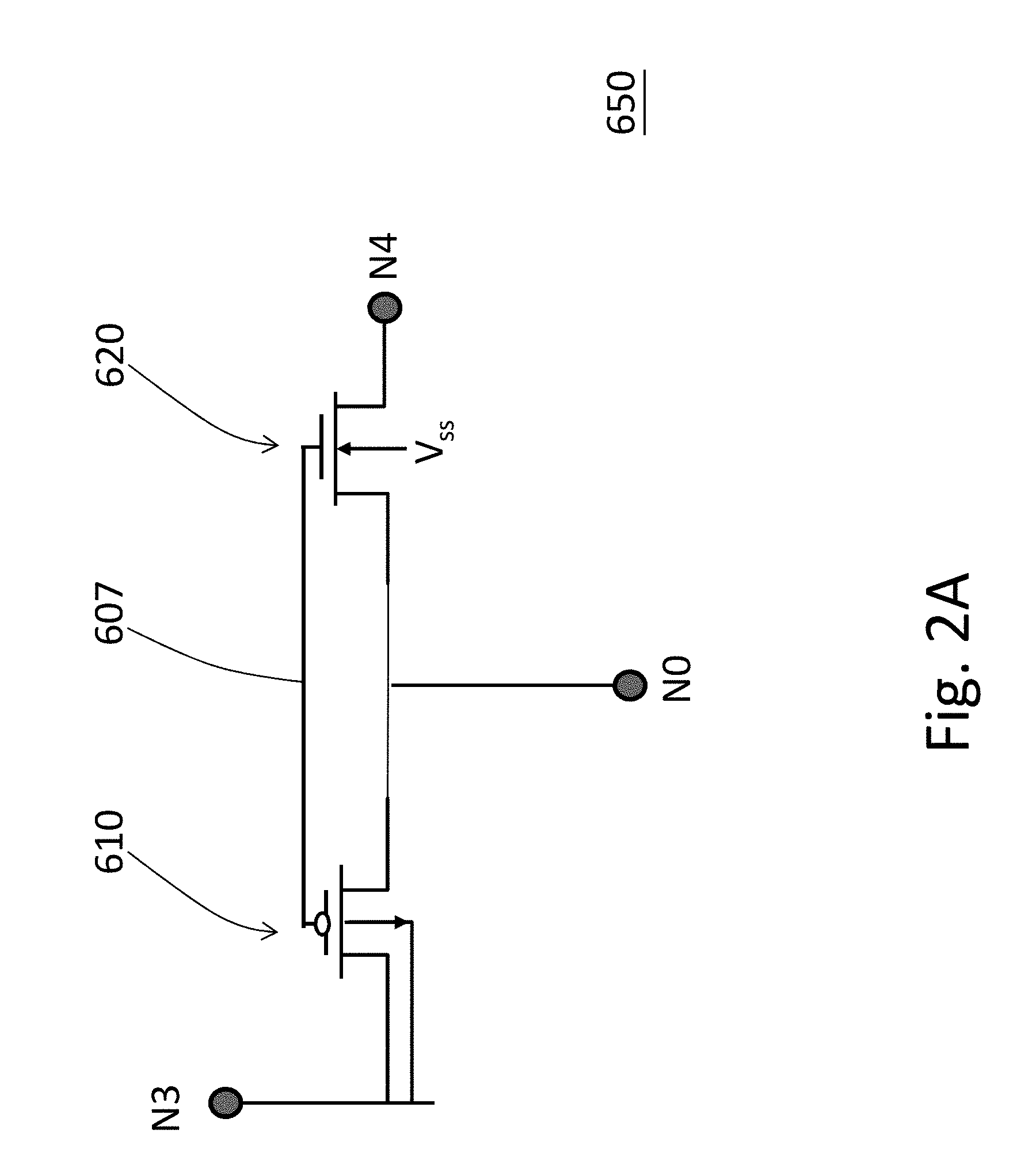

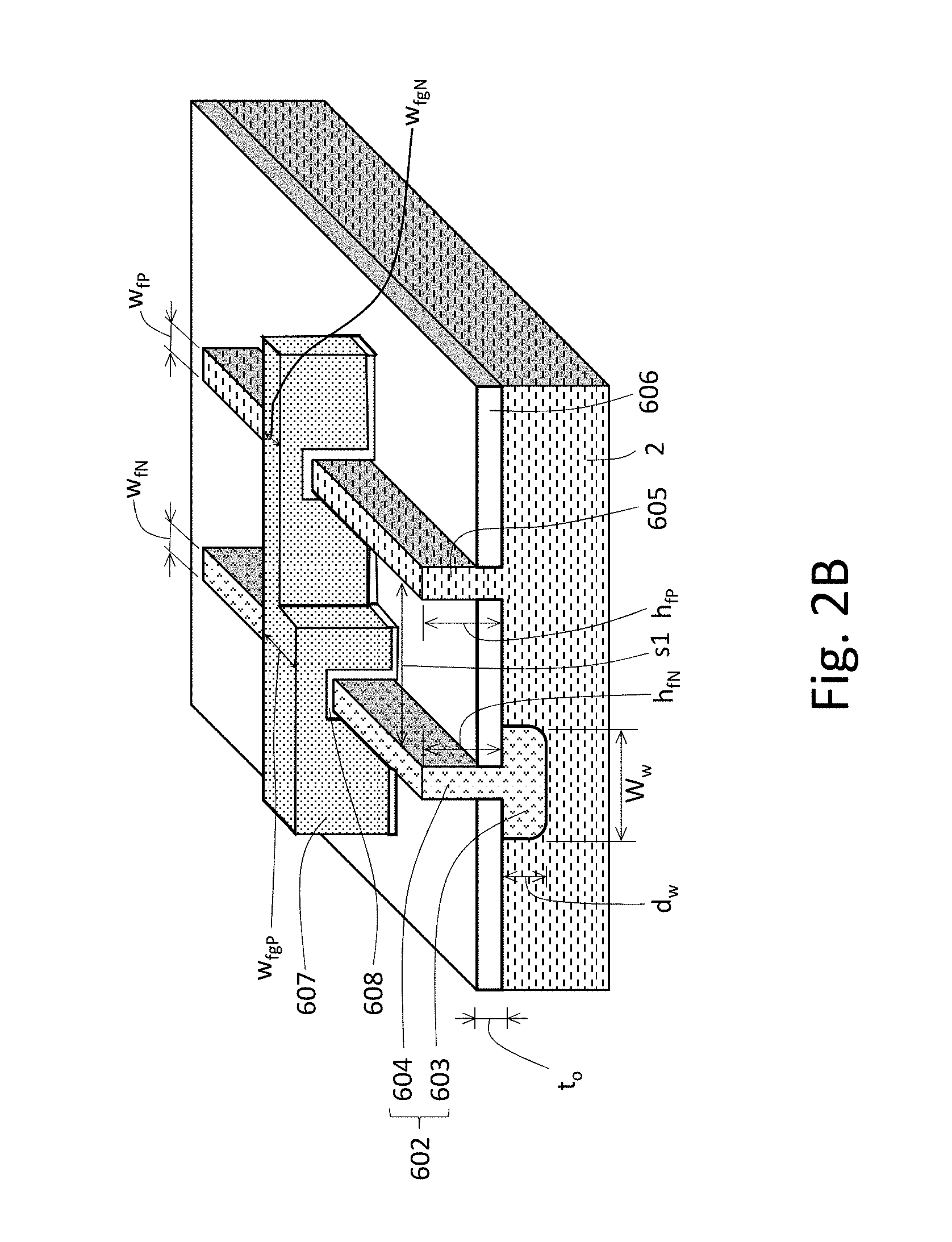

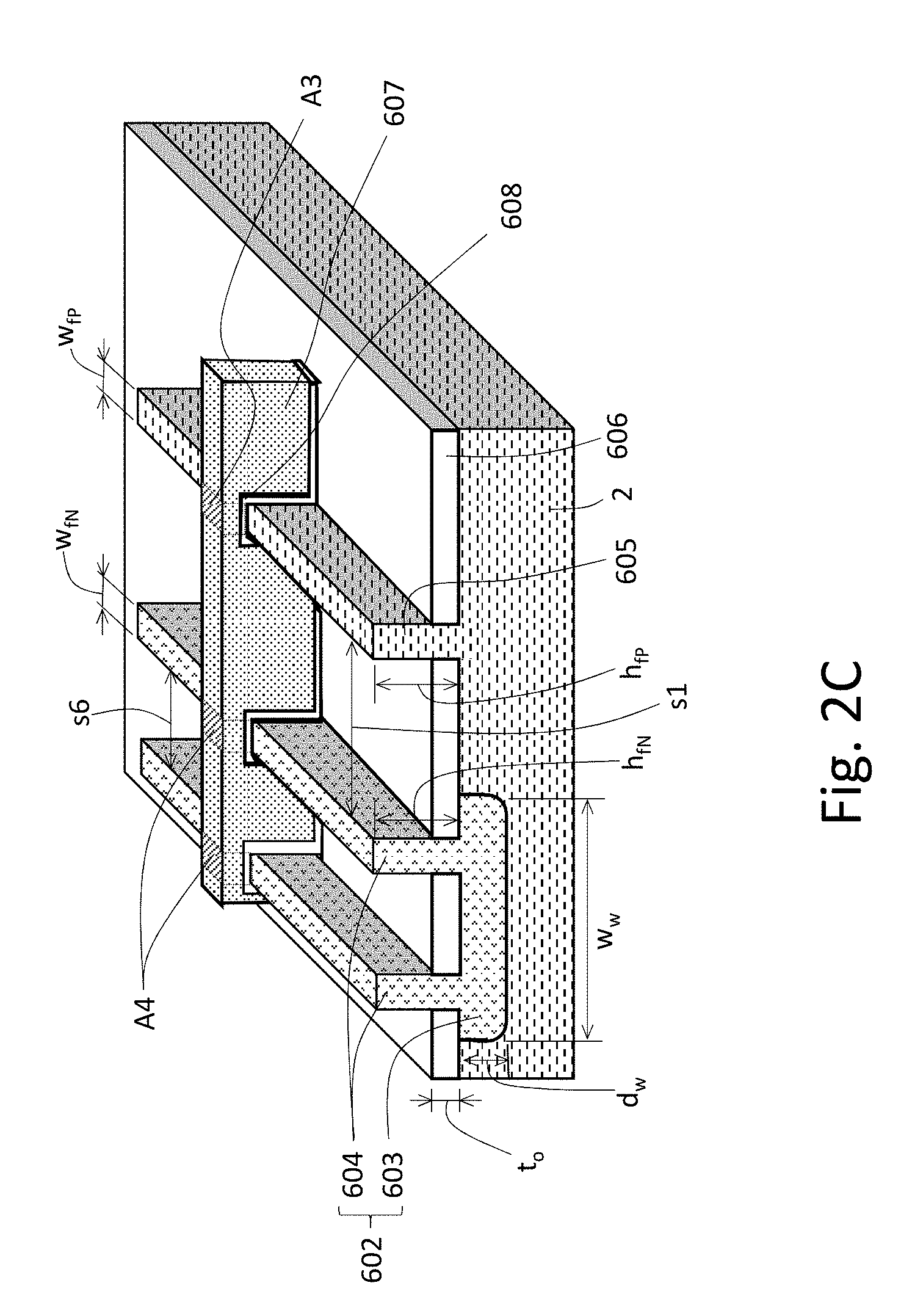

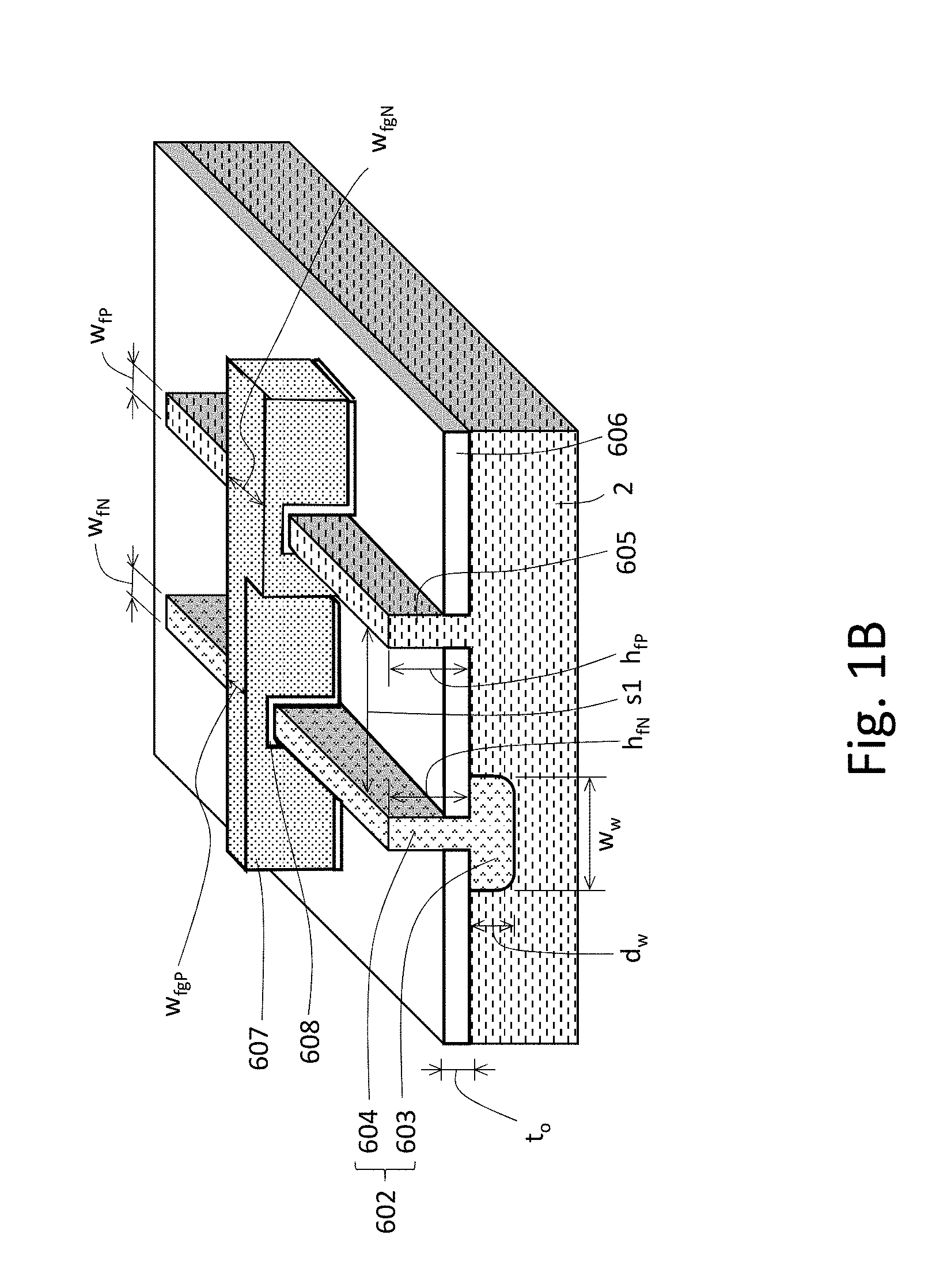

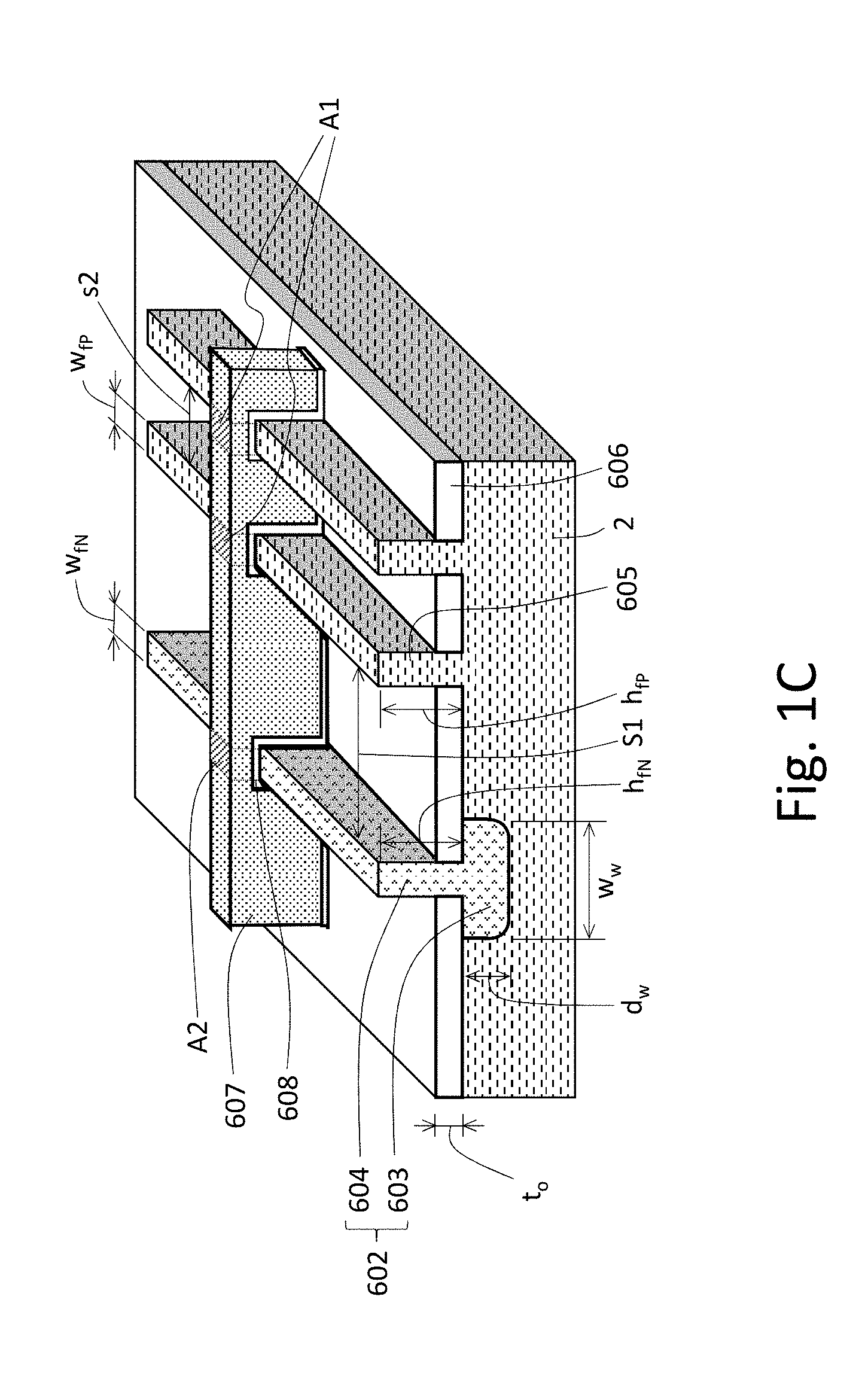

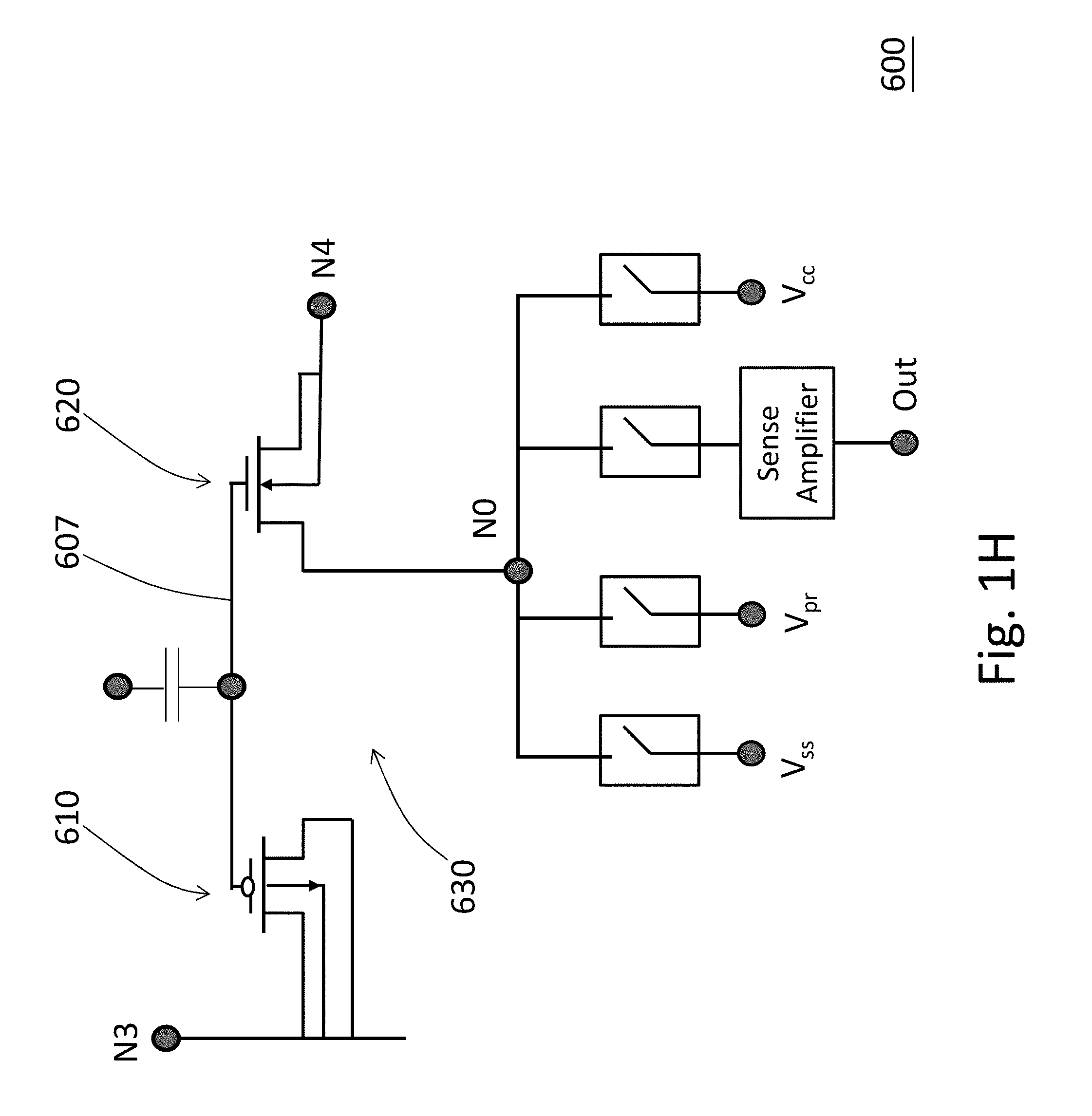

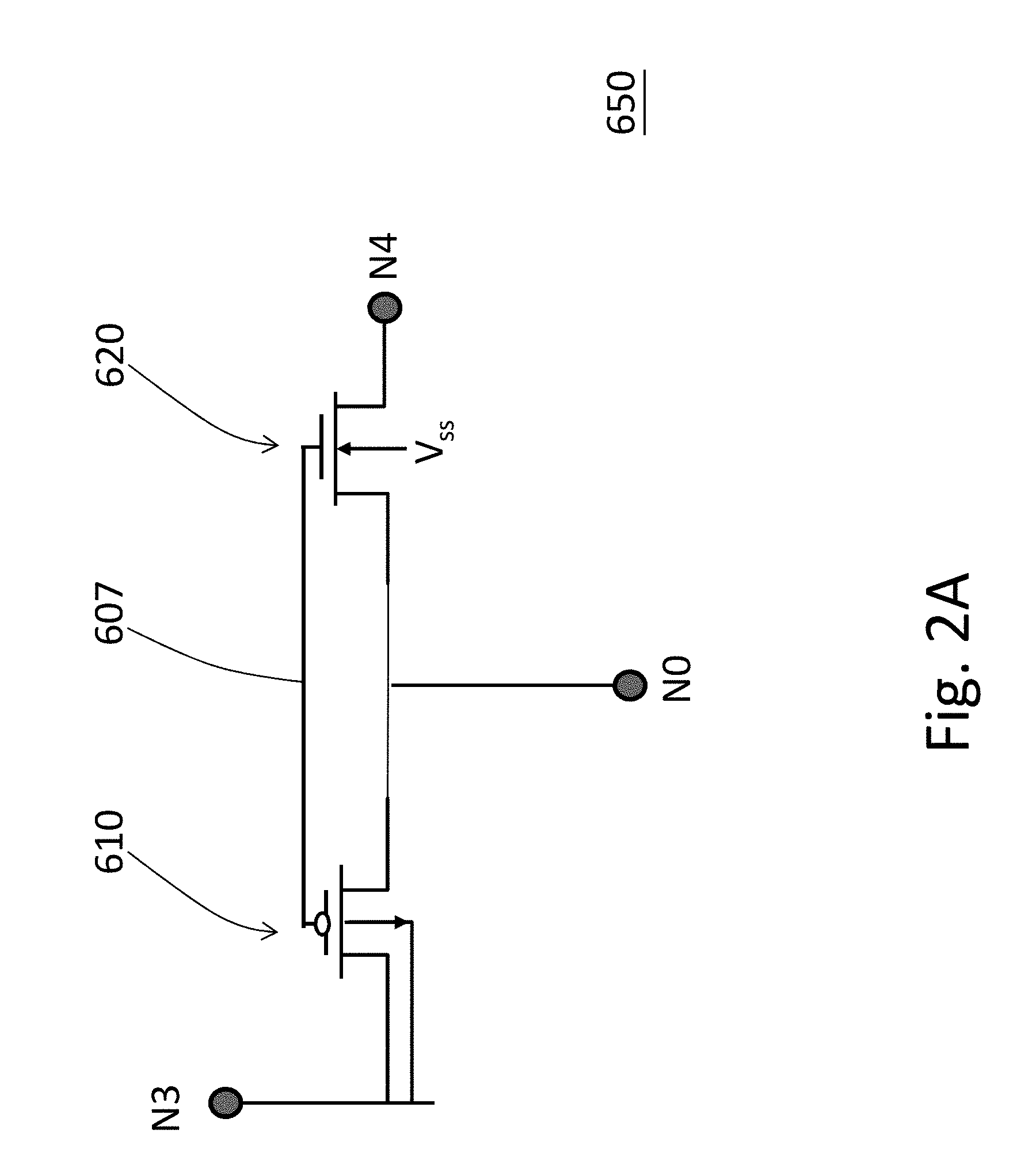

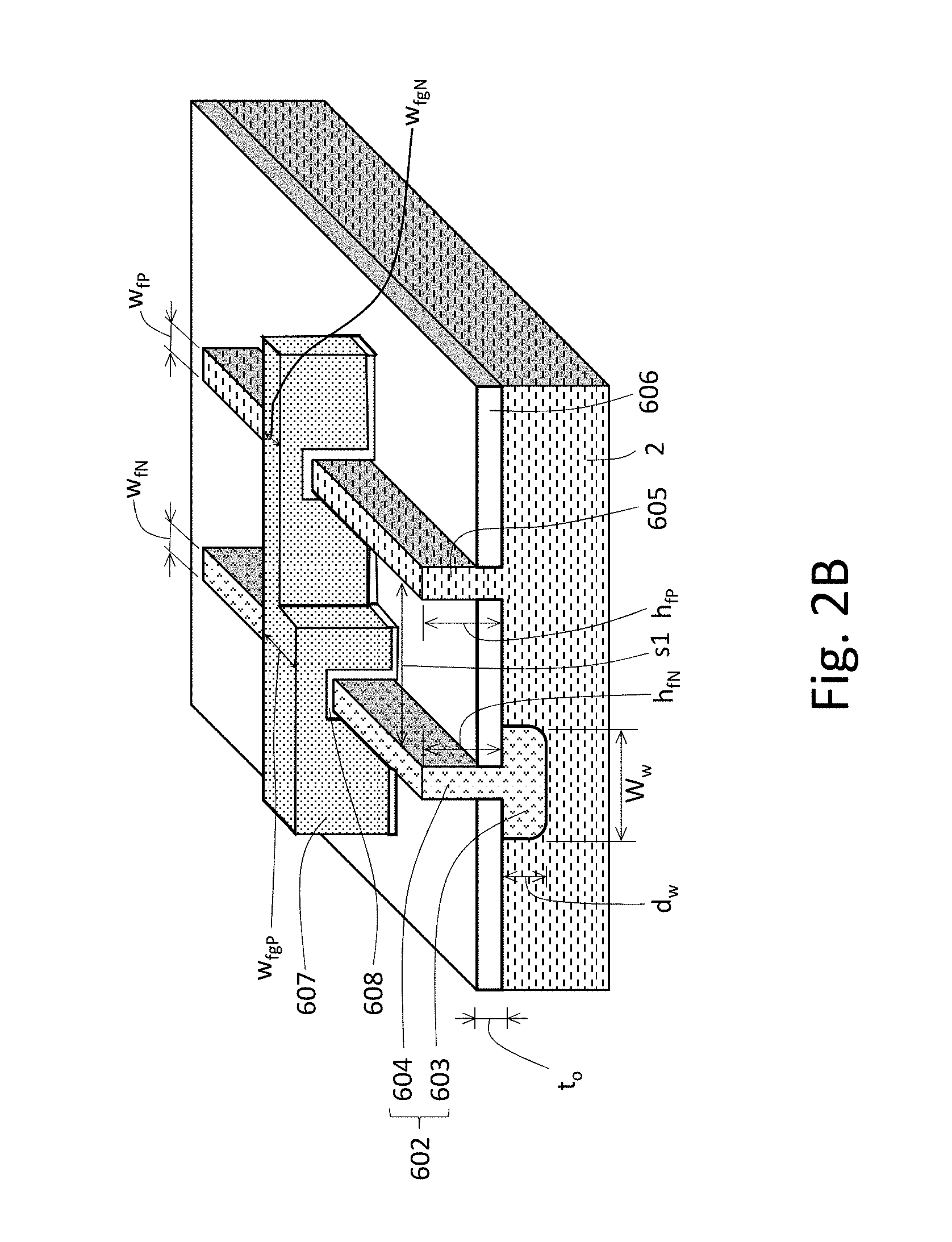

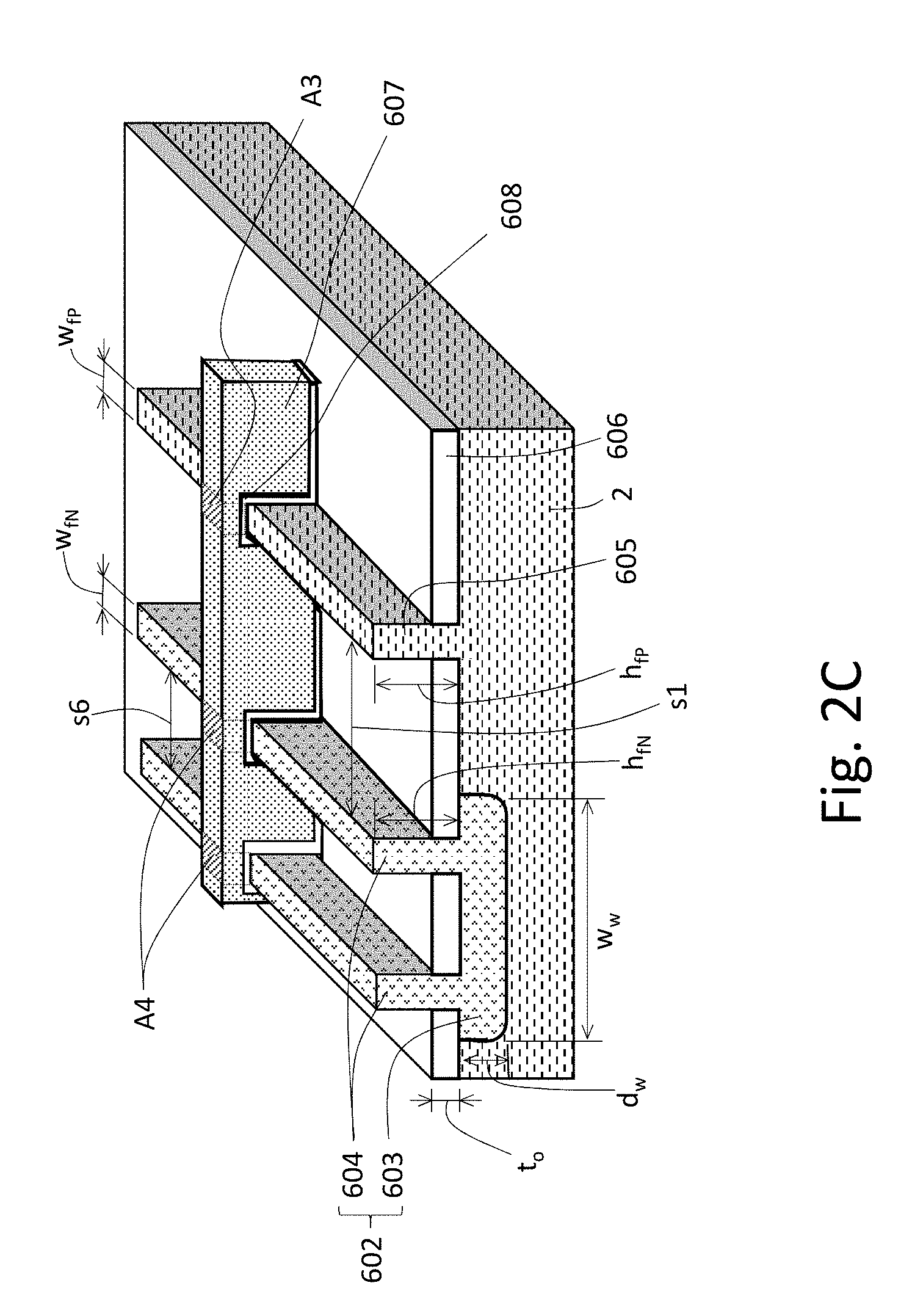

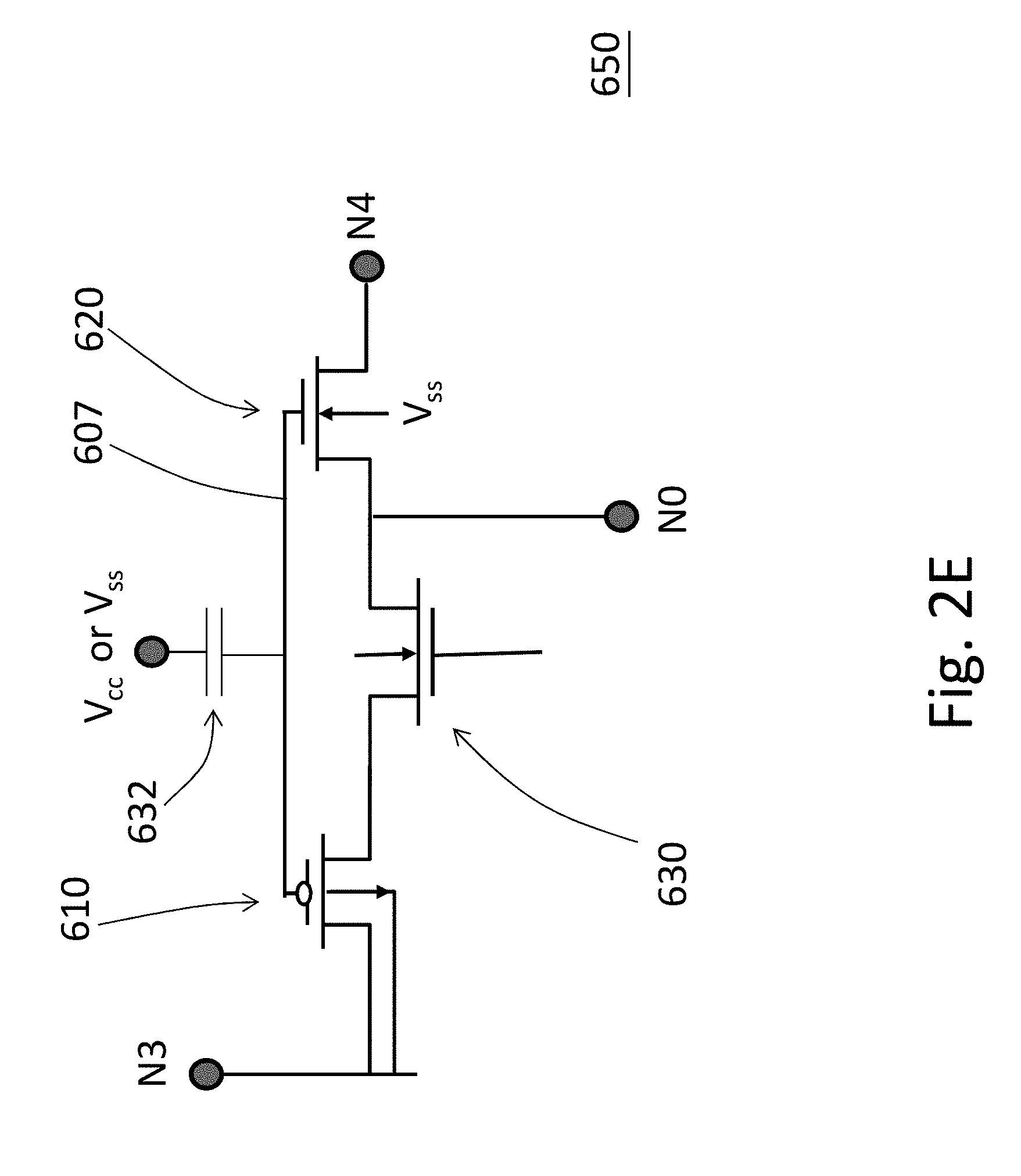

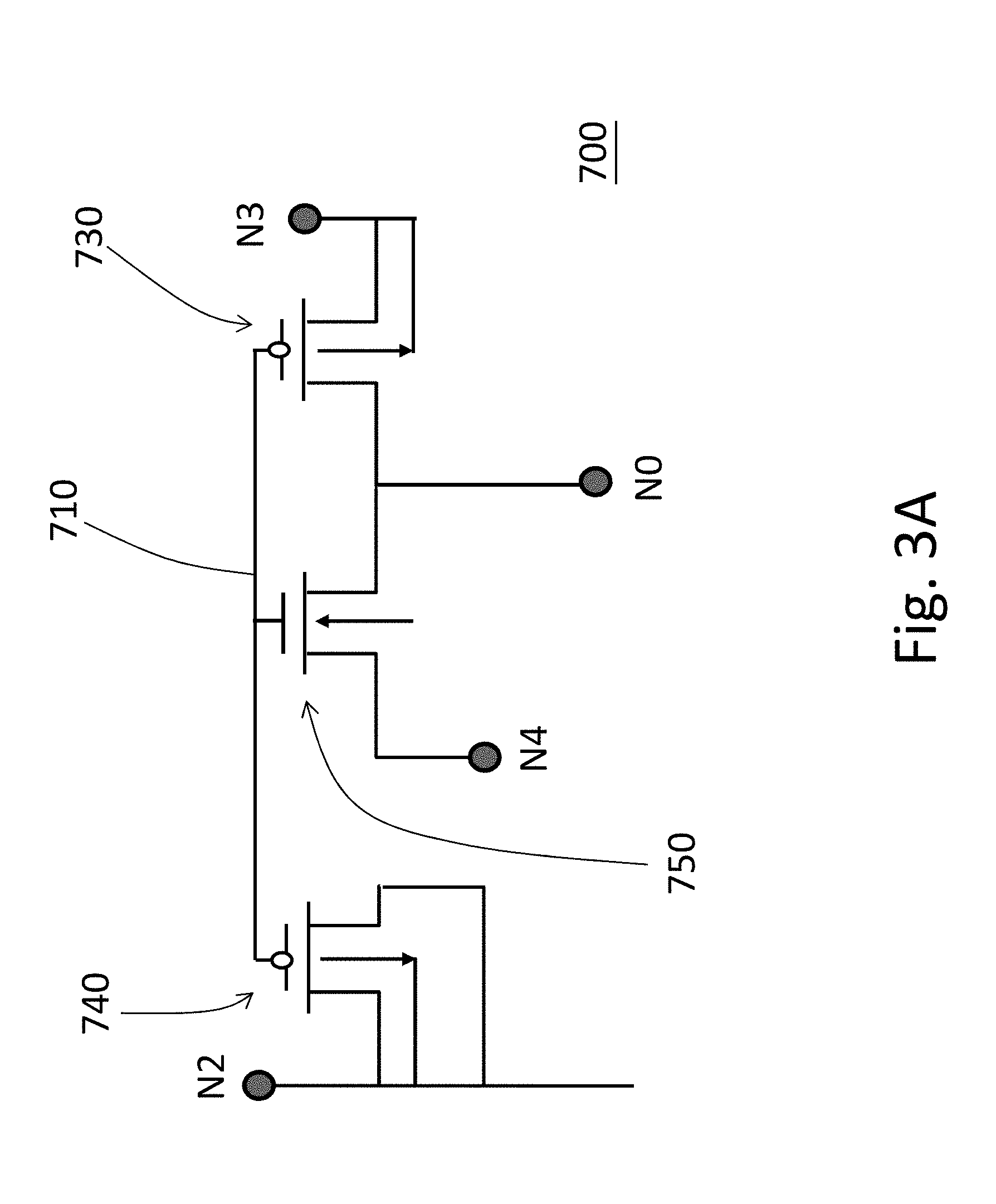

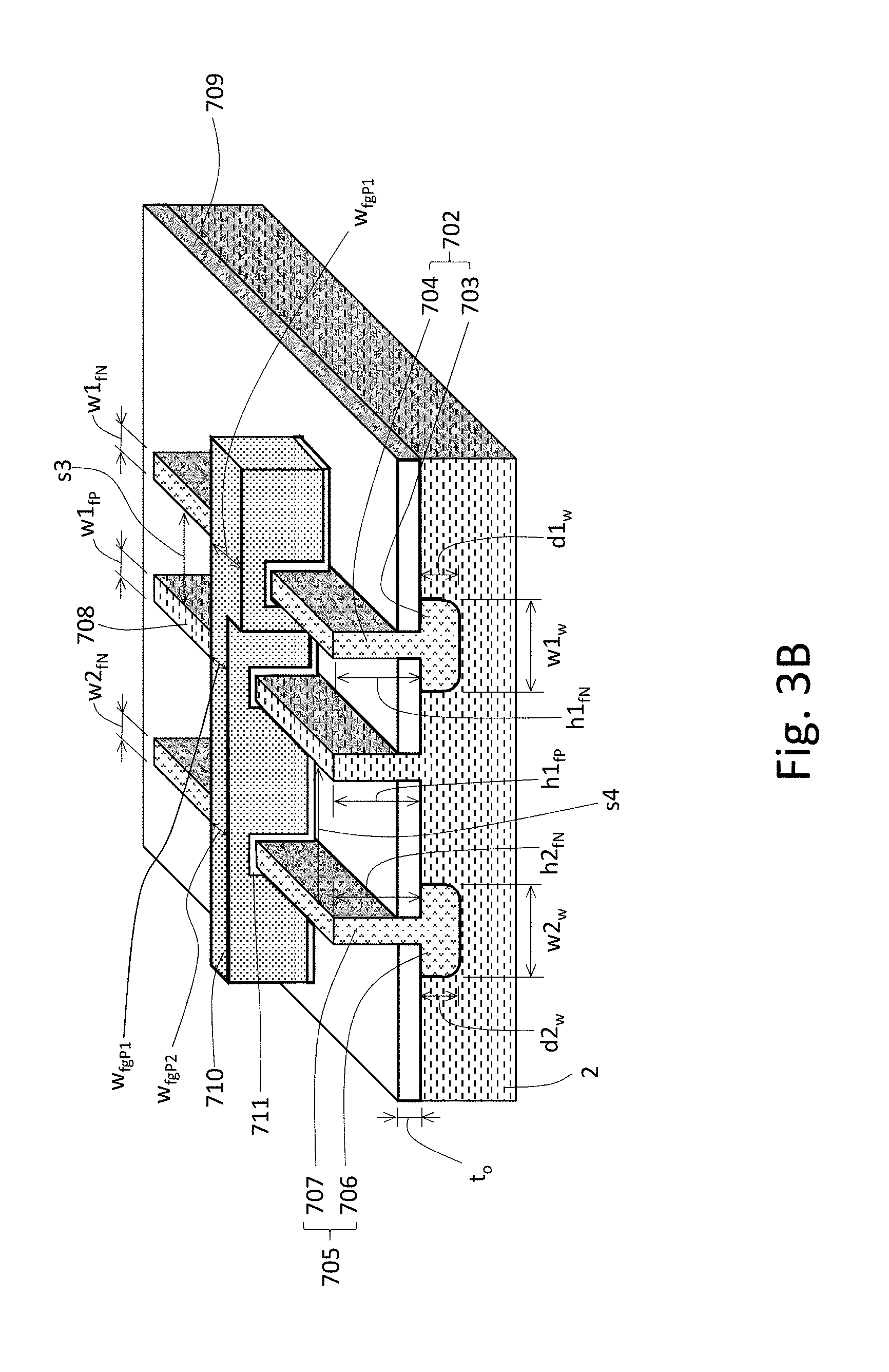

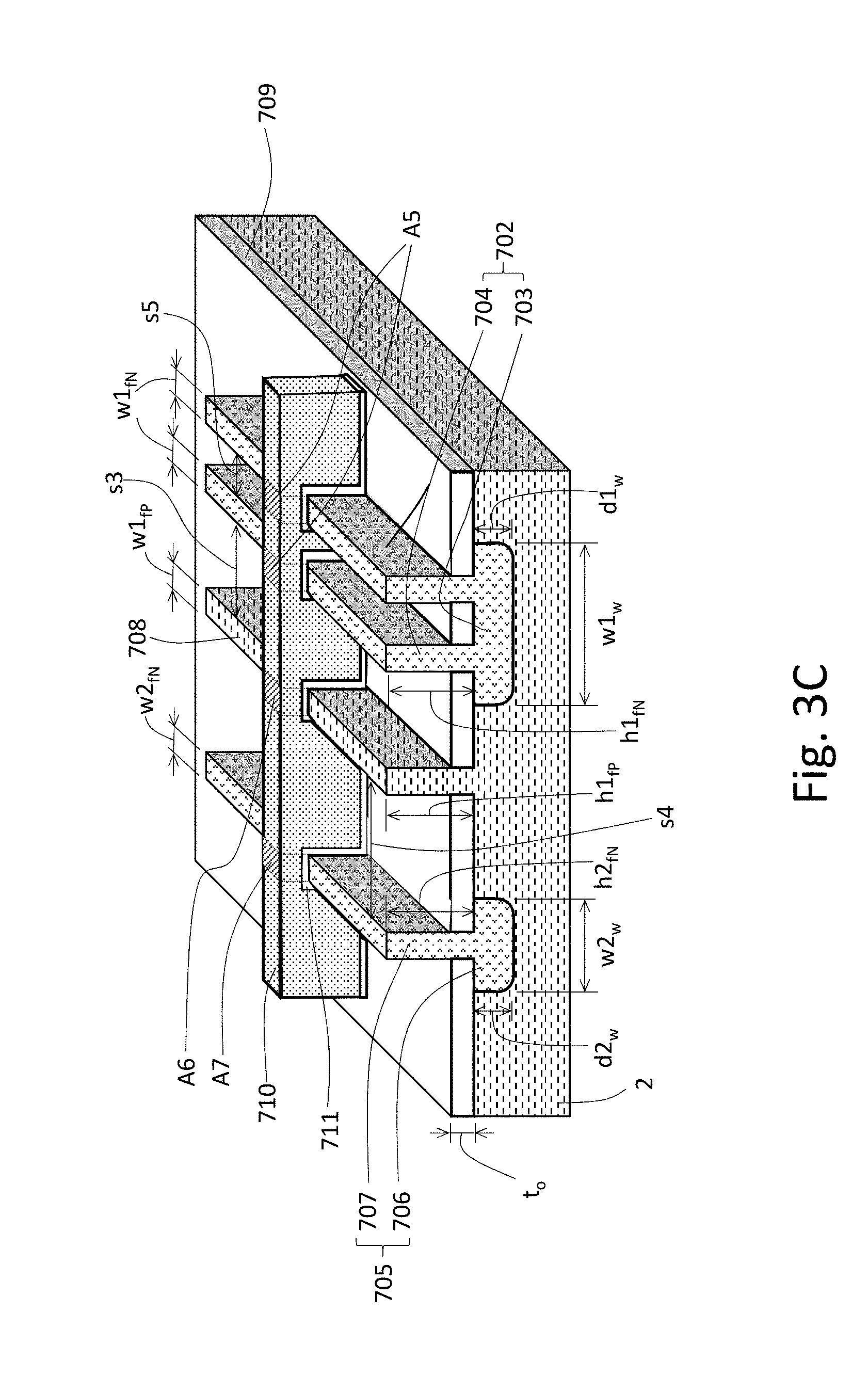

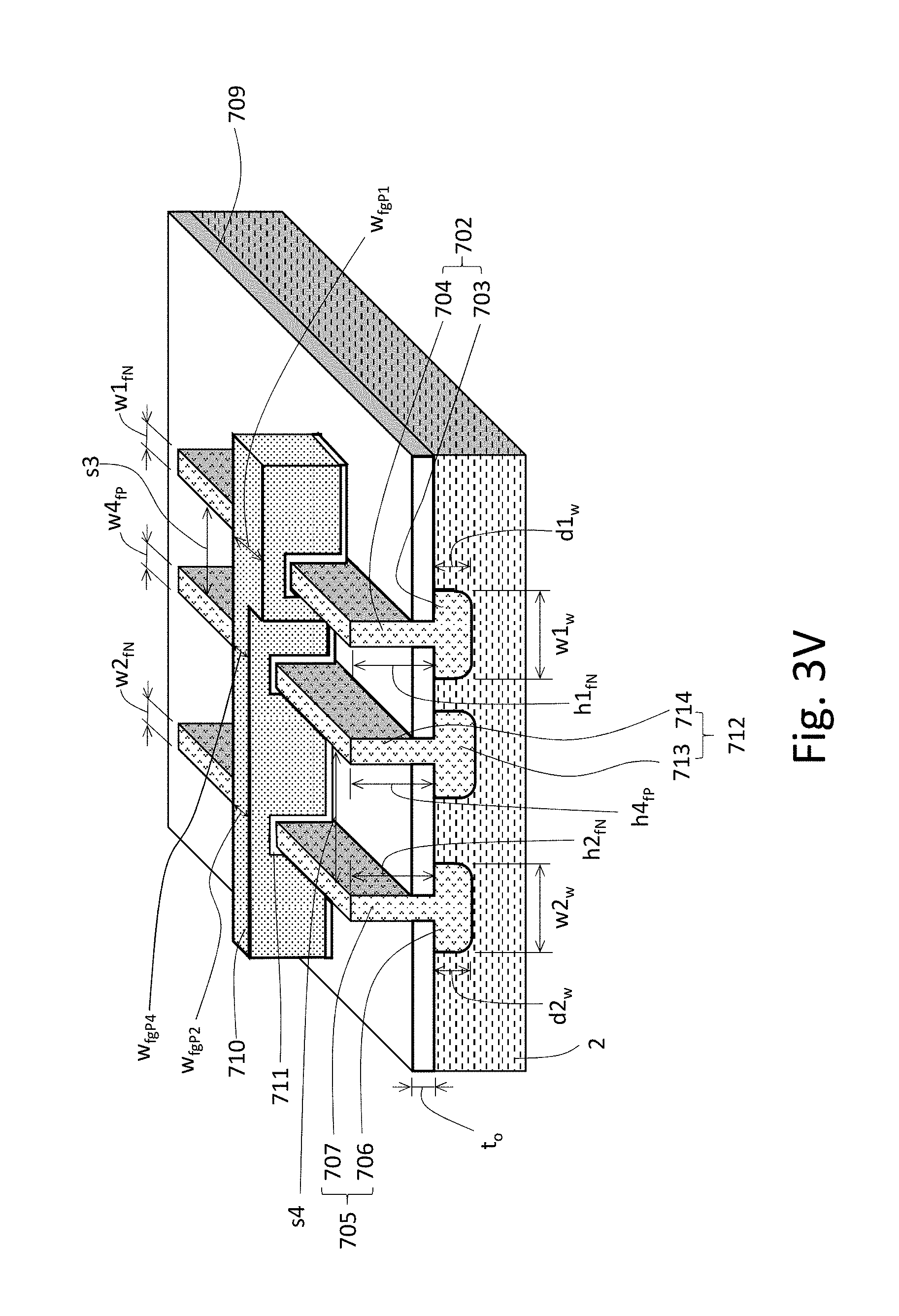

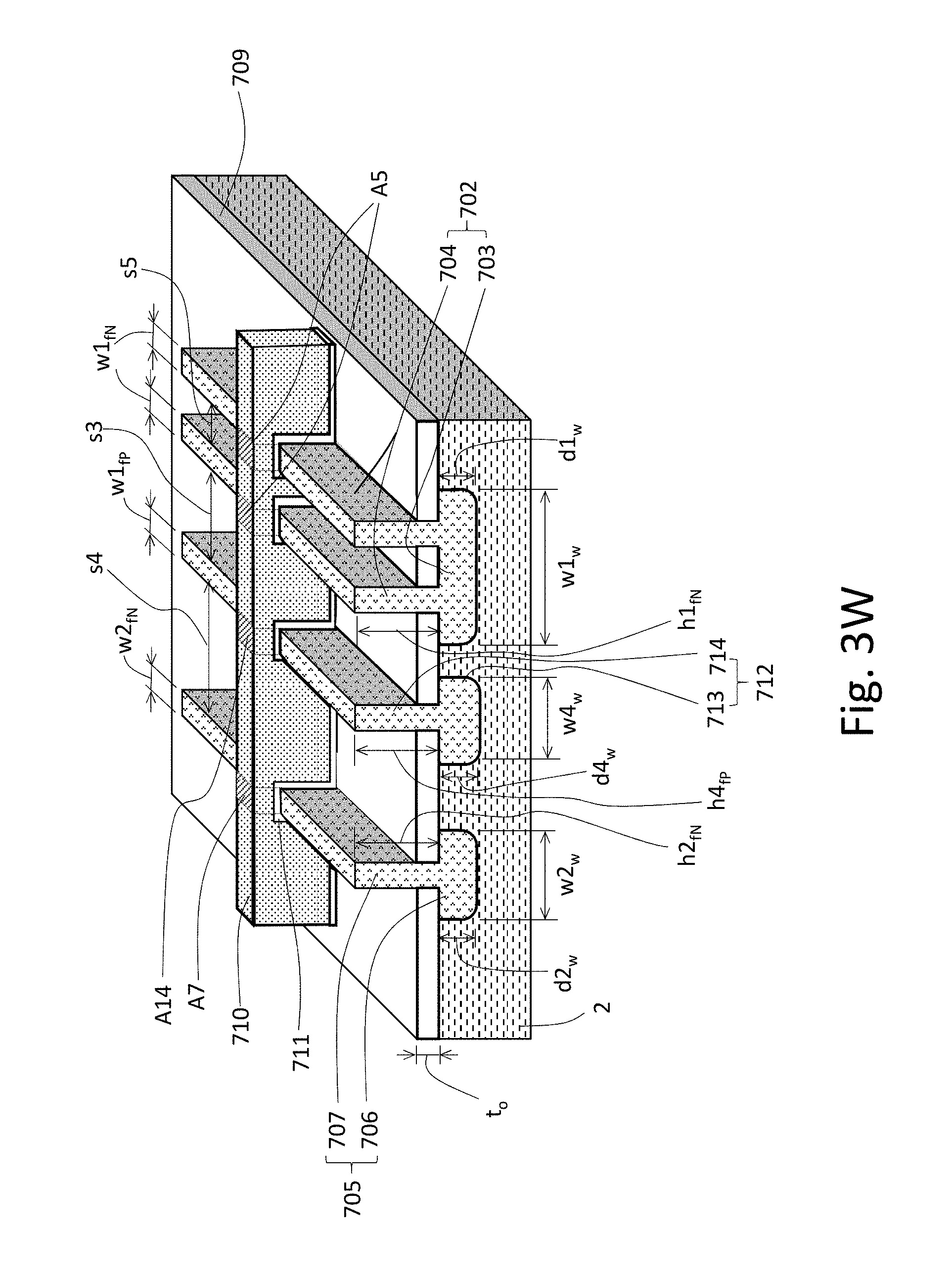

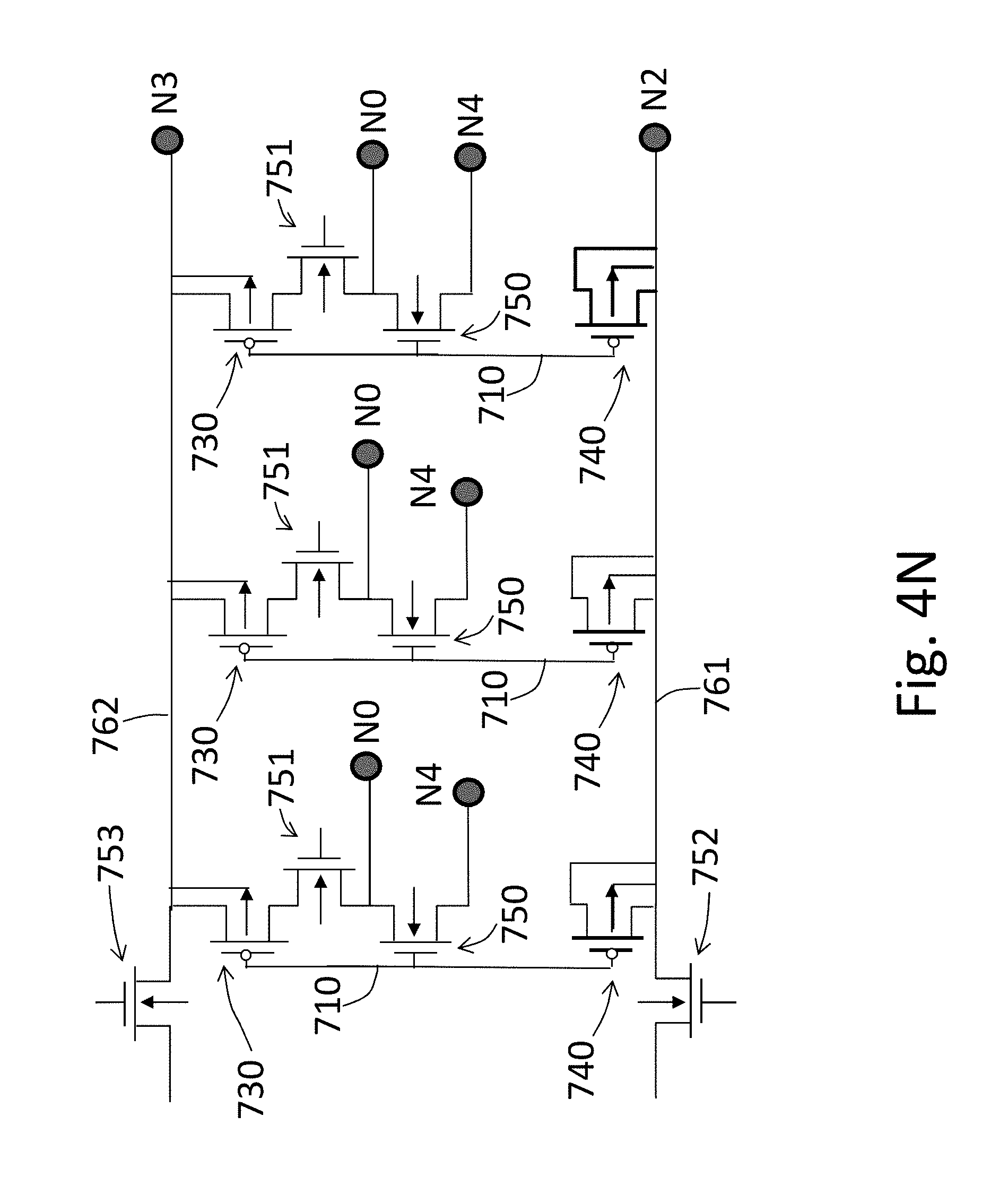

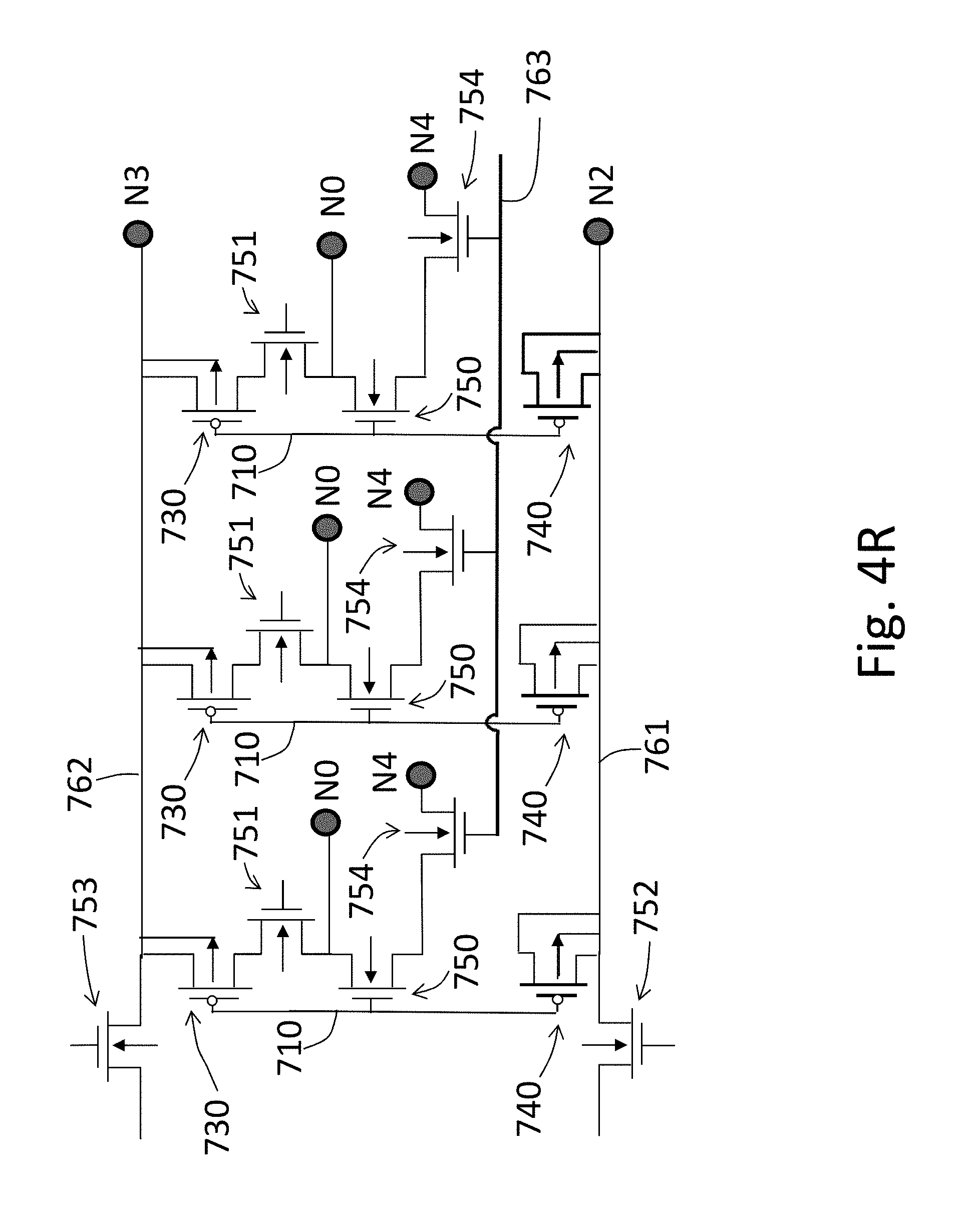

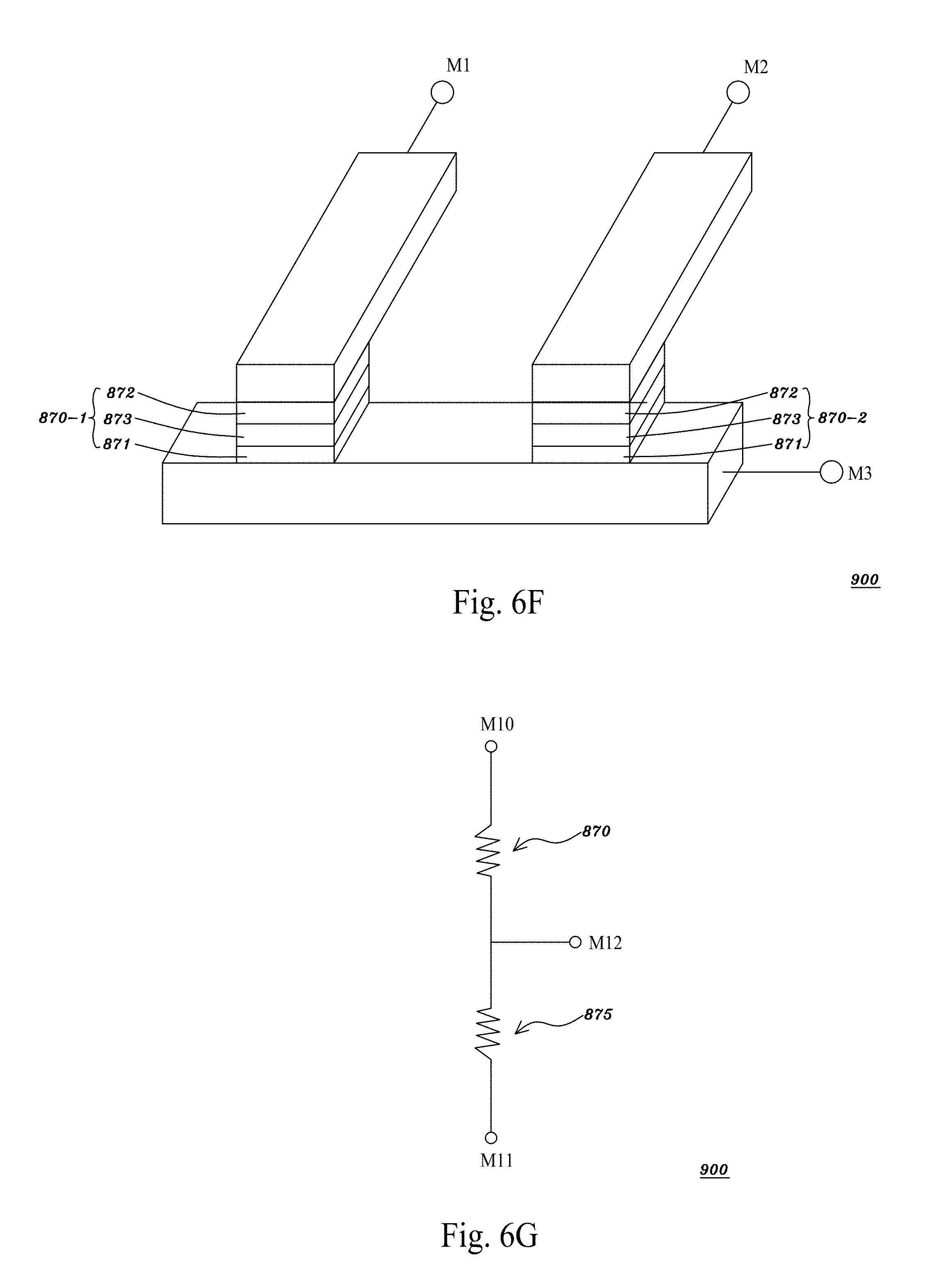

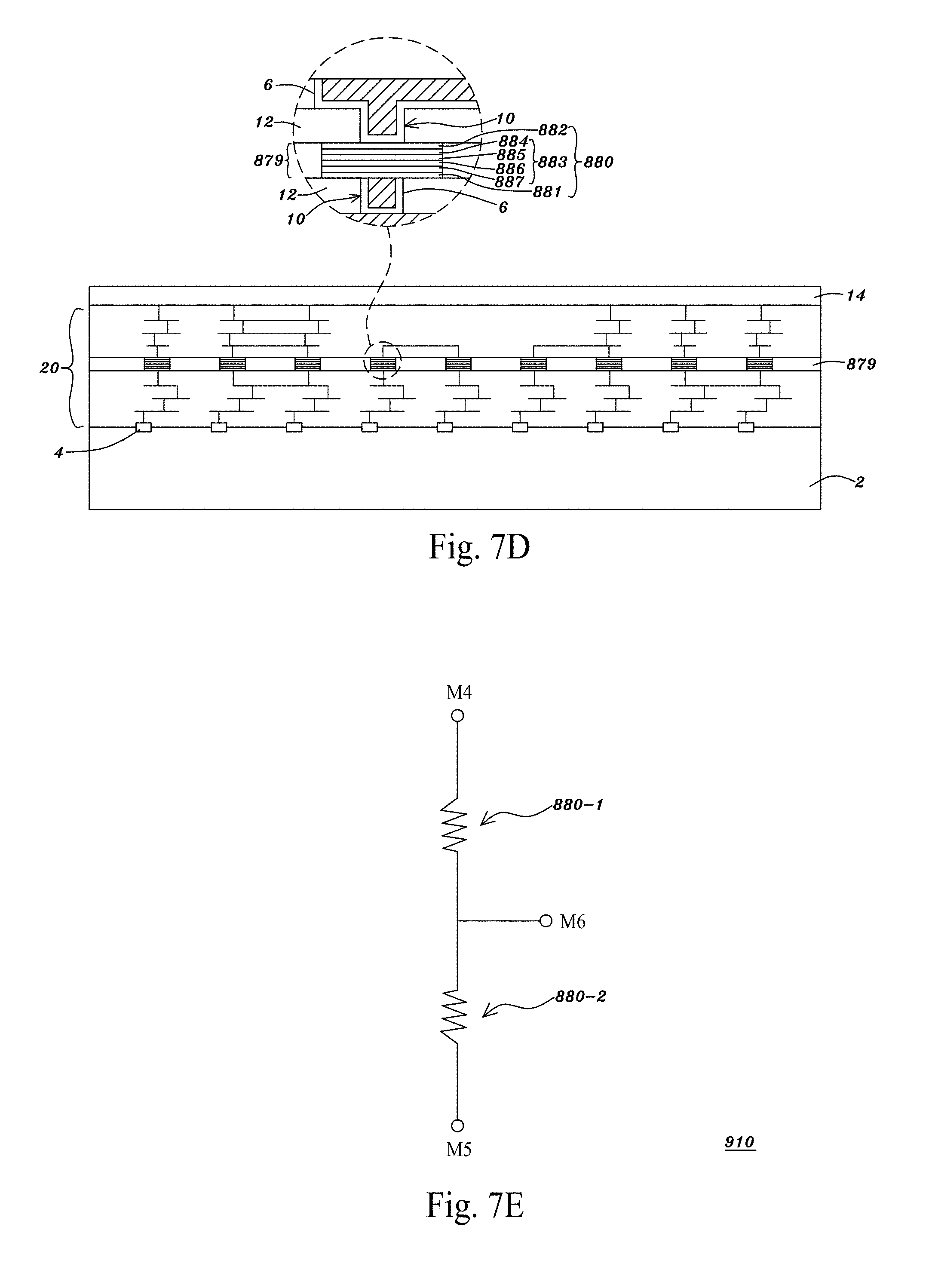

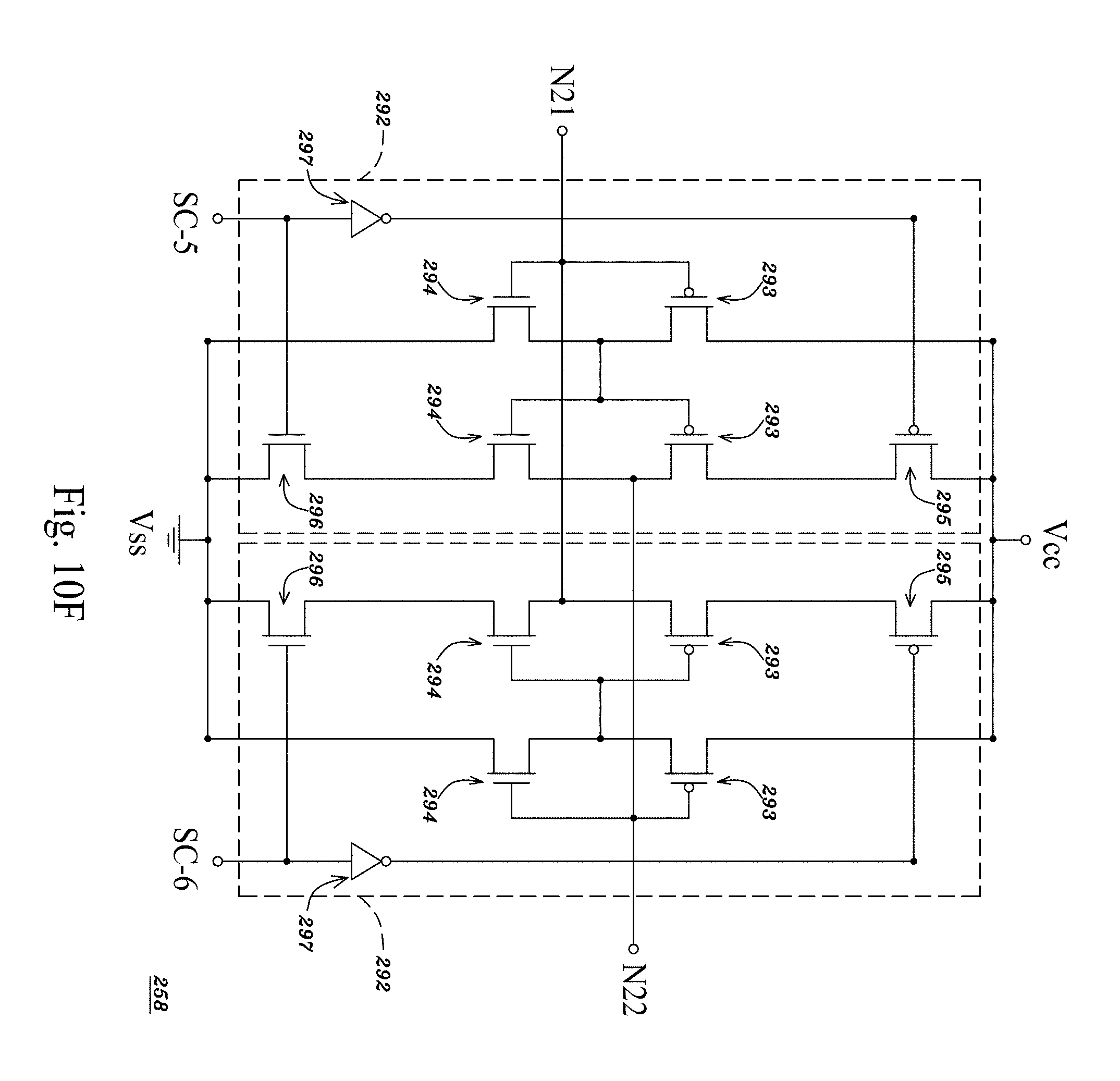

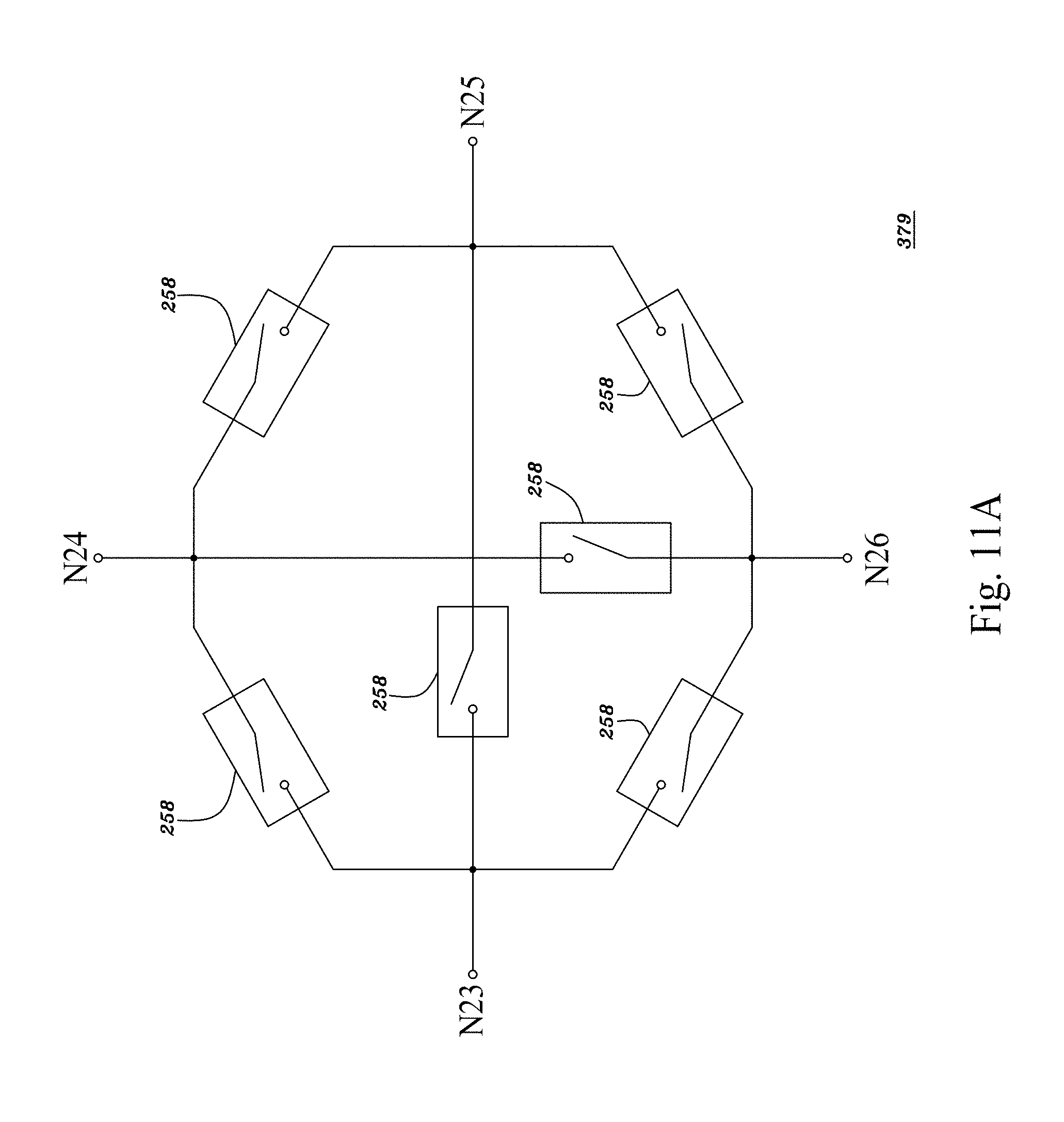

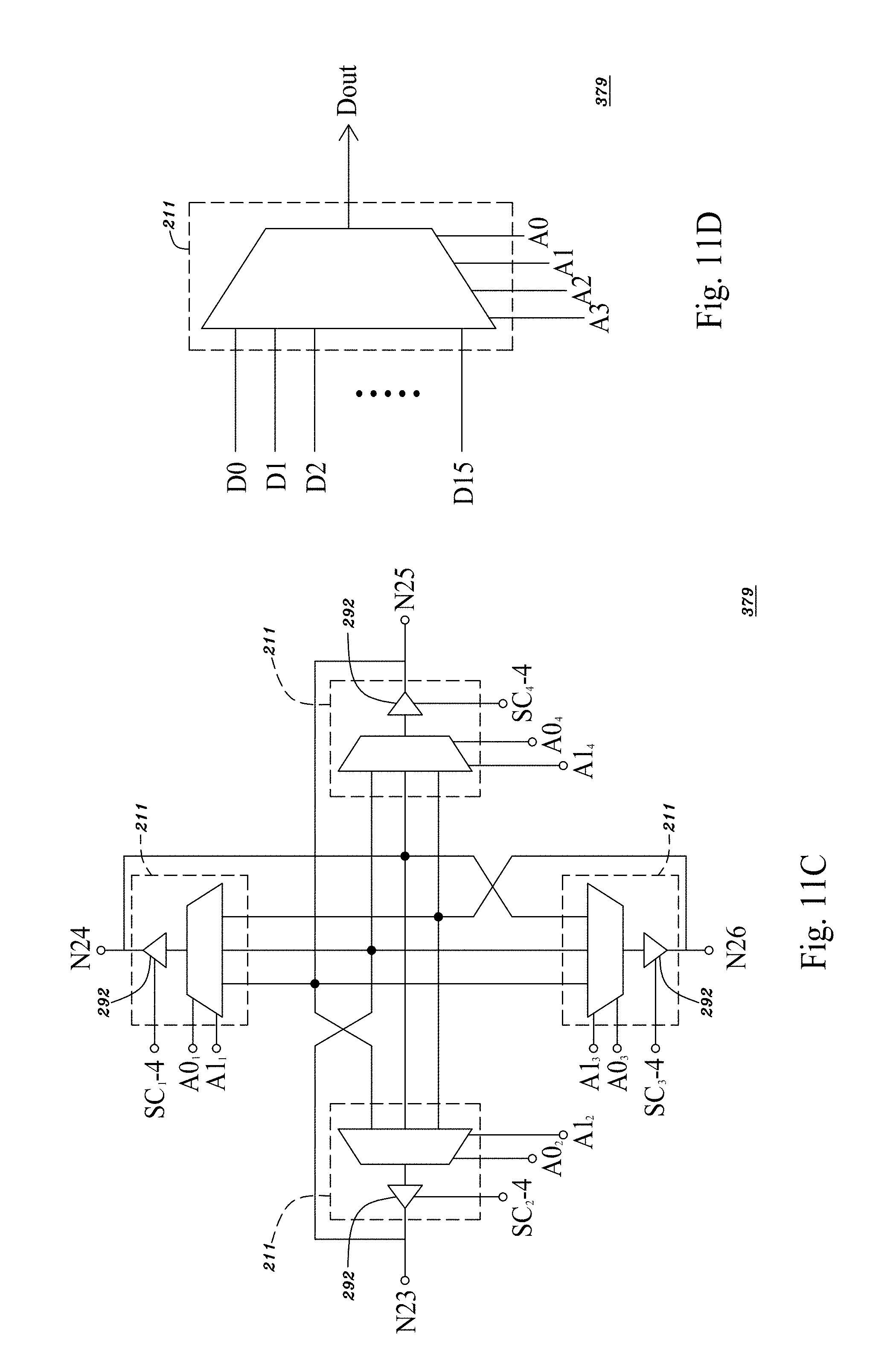

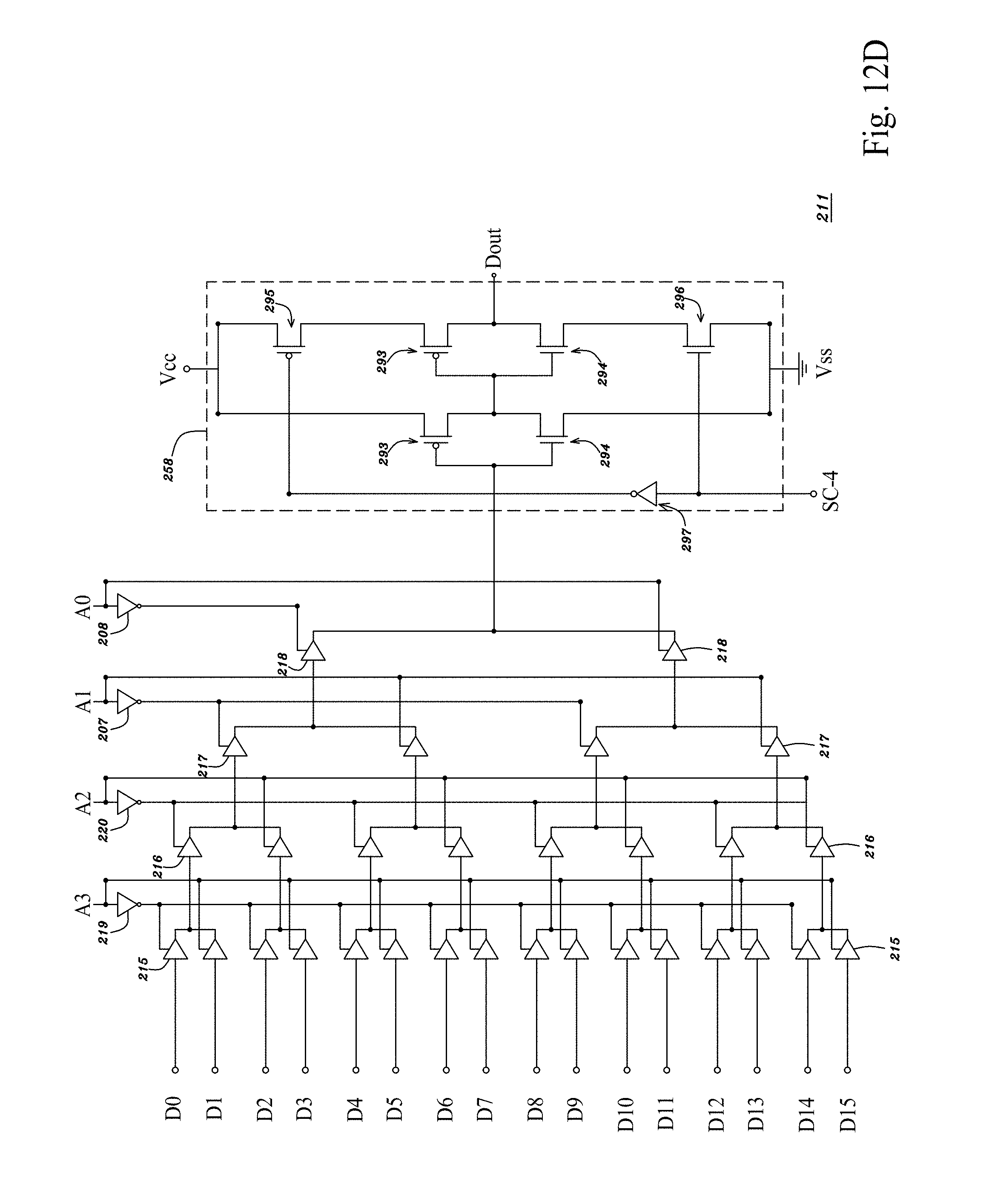

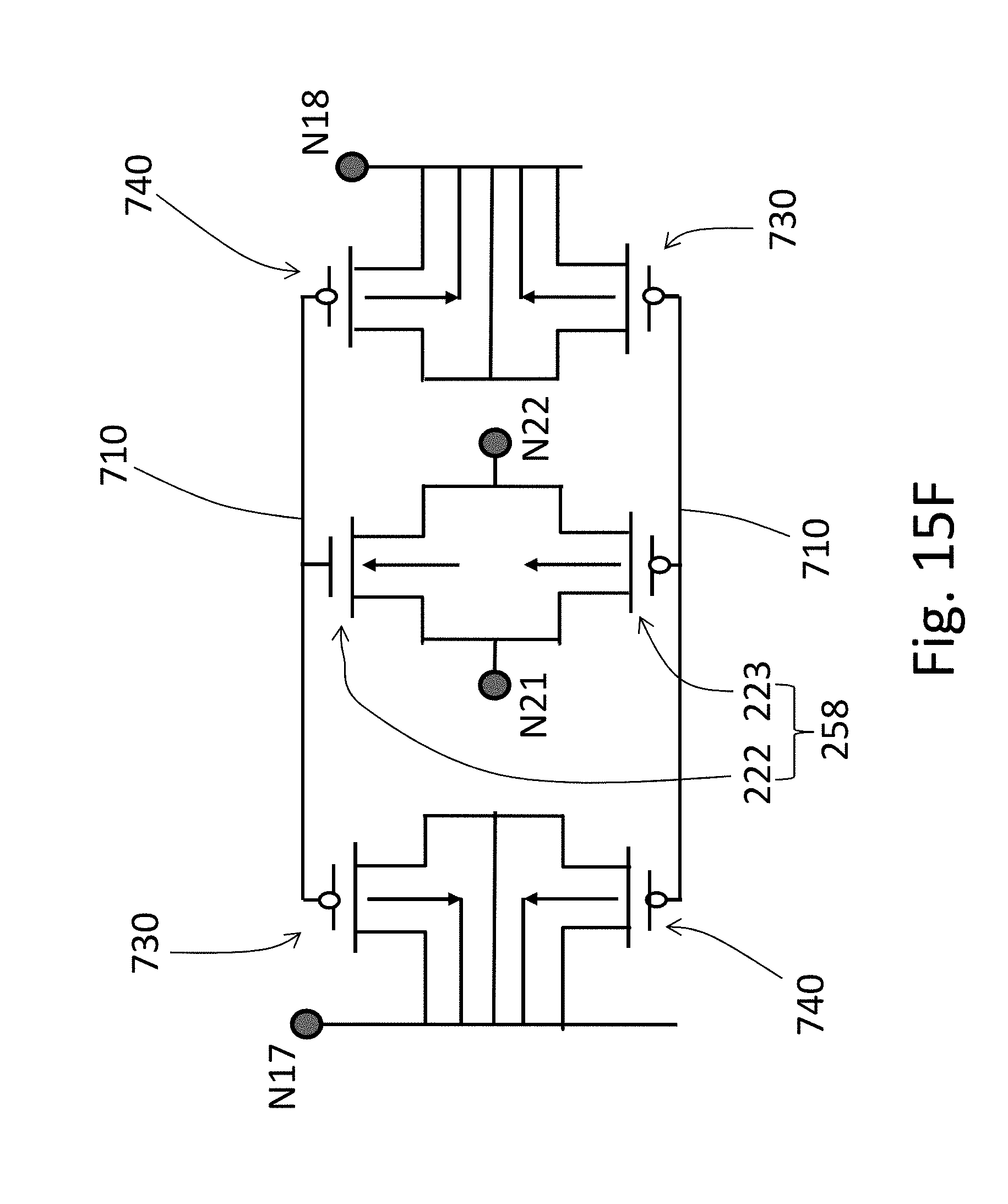

[0012] Another aspect of the disclosure provides a Floating-Gate CMOS Non-Volatile Memory cell, abbreviated as "FGCMOS Non-Volatile Memory" cell or "FGCMOS NVM" cell. The FGCMOS NVM cell may be used in the standard commodity FPGA IC chip for programmable interconnection and/or for data storage of the LUTs. As an example, a first type of a FGCMOS NVM cell comprises a floating-gate P-MOS (FG P-MOS) transistor and a floating-gate N-MOS (FG N-MOS) transistor, with the floating gates of the FG P-MOS and the FG N-MOS connected, and the drains of the FG P-MOS and the FG N-MOS connected or coupled. The FG P-MOS and FG N-MOS share a same connected floating gate. The FG P-MOS transistor is smaller than the FG N-MOS transistor, that is, for example, the gate capacitance of the FG N-MOS transistor is 2 or greater than 2 times larger than or equal to the gate capacitance of the FG P-MOS transistor. The data stored in the FGCMOS NVM cell is erased by electron tunneling through the gate oxide (or insulator) between the floating gate and source/well of the FG P-MOS by (i) biased or coupled the source/well of the FG P-MOS with an erase voltage V.sub.Er, (ii) biased or coupled the source/substrate of the FG N-MOS with a ground voltage V.sub.ss, and (iii) the connected or coupled drains are disconnected. Since the gate capacitance of the FG P-MOS transistor is smaller than that of the FG N-MOS transistor, the voltage of V.sub.Er is dropped largely across the gate oxide of the FG P-MOS transistor; that means the voltage difference between the floating gate and the source/well terminal of the FG P-MOS is large enough to cause the electron tunneling. Therefore, the electrons trapped in the floating gate are tunneling through the gate oxide of the FG P-MOS transistor. The FGCMOS NVM cell after erase is at a logic state of "1". The data is stored or programmed in the NVM cell by hot electron injection through the gate oxide (or insulator) between the floating gate and the channel/drain of the FG N-MOS by (i) biased or coupled the connected or coupled drains with a programming (write) voltage V.sub.Pr, (ii) biased or coupled the source/well of the FG P-MOS with the programming voltage V.sub.Pr, and (iii) biased or coupled the source/substrate of the FG N-MOS with a ground voltage V.sub.ss. The electrons are injected to and trapped in the floating gate by the hot carrier injection through the gate oxide of the FG N-MOS. The FGCMOS NVM cell after programming (write) is at a logic state of "0". The first type of FGCMOS NVM cell uses electron tunneling for erasing and hot electron injection for programming (write). The data stored in the FGCMOS NVM cell may be read or accessed through the connected or coupled drains with the source/well of the FG P-MOS biased at the read, access, or operation voltage V.sub.cc, and the source/substrate of the FG N-MOS biased at the ground voltage V.sub.ss. For the read, access or operation process or mode, when the floating gate is at a logic level of "1", the FG P-MOS transistor may be turned off and the FG N-MOS transistor may be turned on, and therefore, the ground voltage V at the source of the FG N-MOS is coupled to the output (the connected drain) of the FGCMOS NVM cell through a channel of the FG N-MOS transistor. Thereby, the output of the FGCMOS NVM cell may be at a logic level of "0". When the floating gate is at a logic level of "0", the FG P-MOS transistor may be turned on and the FG N-MOS transistor may be turned off, and therefore, the power supply voltage of V.sub.cc at the source of the FG P-MOS is coupled to the output (the connected drain) of the FGCMOS NVM cell through a channel of the FG P-MOS transistor. Thereby, the output of the FGCMOS NVM cell may be at a logic level of "1".

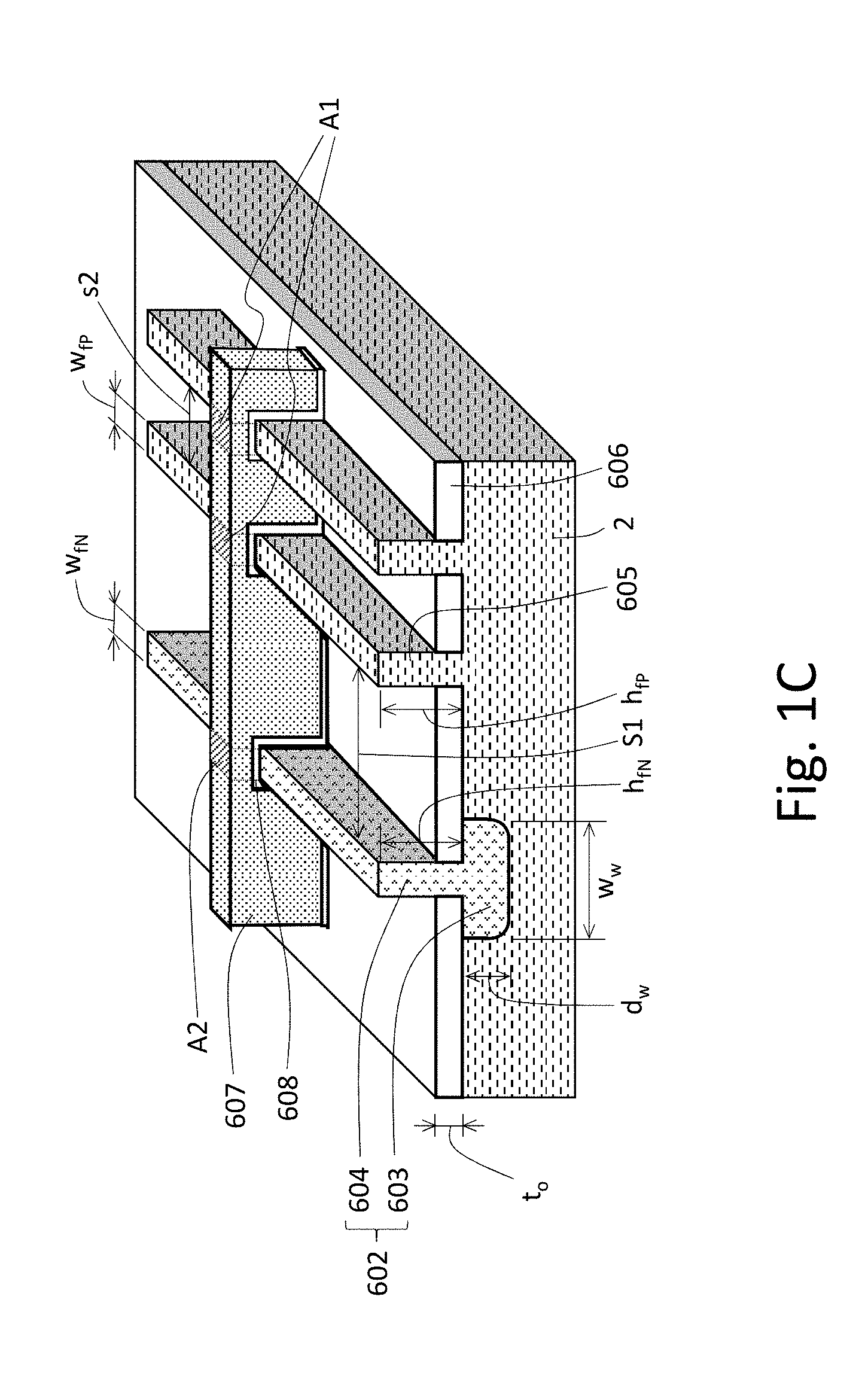

[0013] As another example, a second type of a FGCMOS NVM cell uses electron tunneling for both erasing and programming. The second type of a FGCMOS NVM cell comprises a floating-gate P-MOS (FG P-MOS) transistor and a floating-gate N-MOS (FG N-MOS) transistor, with the floating gates of the FG P-MOS and the FG N-MOS connected, and the drains of the FG P-MOS and the FG N-MOS connected or coupled. The FG P-MOS and FG N-MOS share a same connected floating gate. The FG N-MOS transistor is smaller than the FG P-MOS transistor, that is, the gate capacitance of the FG P-MOS transistor is 2 or greater than 2 times larger than or equal to the gate capacitance of the FG N-MOS transistor. The data stored in the FGCMOS NVM cell is erased by electron tunneling through the gate oxide (or insulator) between the floating gate and the source of the FGN-MOS by (i) biased or coupled the source of the FG N-MOS with an erase voltage V.sub.Er, (ii) biased the source/well of the FG P-MOS with a ground voltage V.sub.ss, and (iii) the drain of the FG N-MOS are disconnected. Since the capacitance between the floating gate and the source junction of the FG N-MOS transistor is much smaller than that of the sum of the gate capacitances of the FG P-MOS transistor and the FG N-MOS transistor, the voltage of V.sub.Er is dropped largely across the gate oxide between the floating gate and the source junction of the FG N-MOS transistor; that means the voltage difference between the floating gate and the source terminal of the FG N-MOS is large enough to cause the electron tunneling. Therefore, the electrons trapped in the floating gate are tunneling through the gate oxide between the floating gate and the source junction of the FG N-MOS transistor. The FGCMOS NVM cell after erase is at a logic state of "1". The data is stored or programmed in the FGCMOS NVM cell by electron tunneling through the gate oxide (or insulator) between the floating gate and the channel/source of the FG N-MOS by (i) biased or coupled the source/well of the FG P-MOS with a programming voltage V.sub.Pr, (ii) biased or coupled the source/substrate of the FG N-MOS with the ground voltage V.sub.ss, and (iii) the drain of the FG N-MOS is disconnected. Since the gate capacitance of the FG N-MOS transistor is smaller than that of the FG P-MOS transistor, the voltage of V.sub.Pr is dropped largely across the gate oxide of the FG N-MOS transistor; that means the voltage difference between the floating gate and the source/channel terminal of the FG N-MOS is large enough to cause the electron tunneling. Therefore, the electrons at the source/channel of the FG N-MOS transistor may tunnel through the gate oxide to the floating gate and be trapped in the floating gate. Thereby, the floating gate may be programmed to a logic level of "0". The "read", "access" or "operation" process or mode for the second type FGCMOS NVM cell is the same as that of the first type.

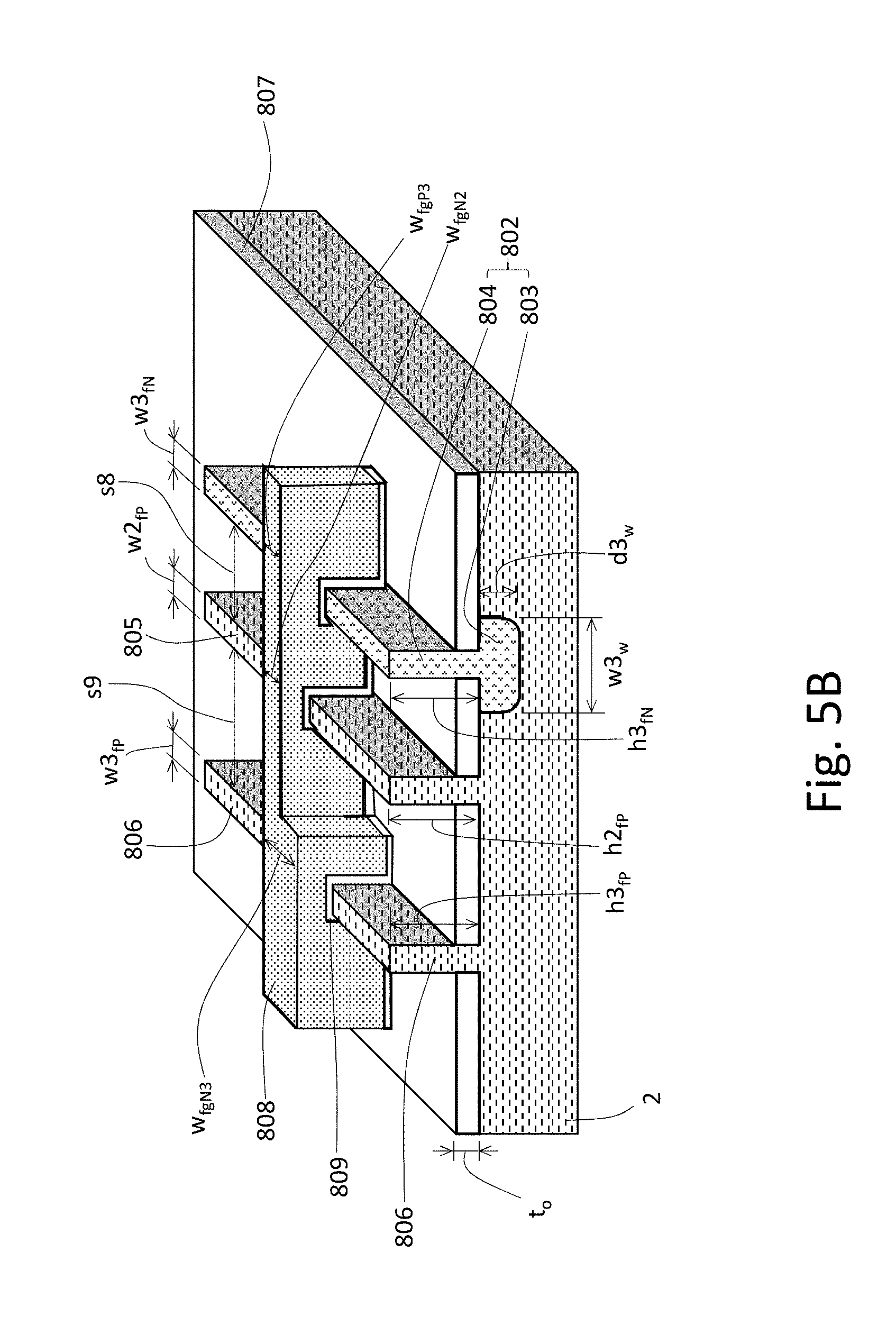

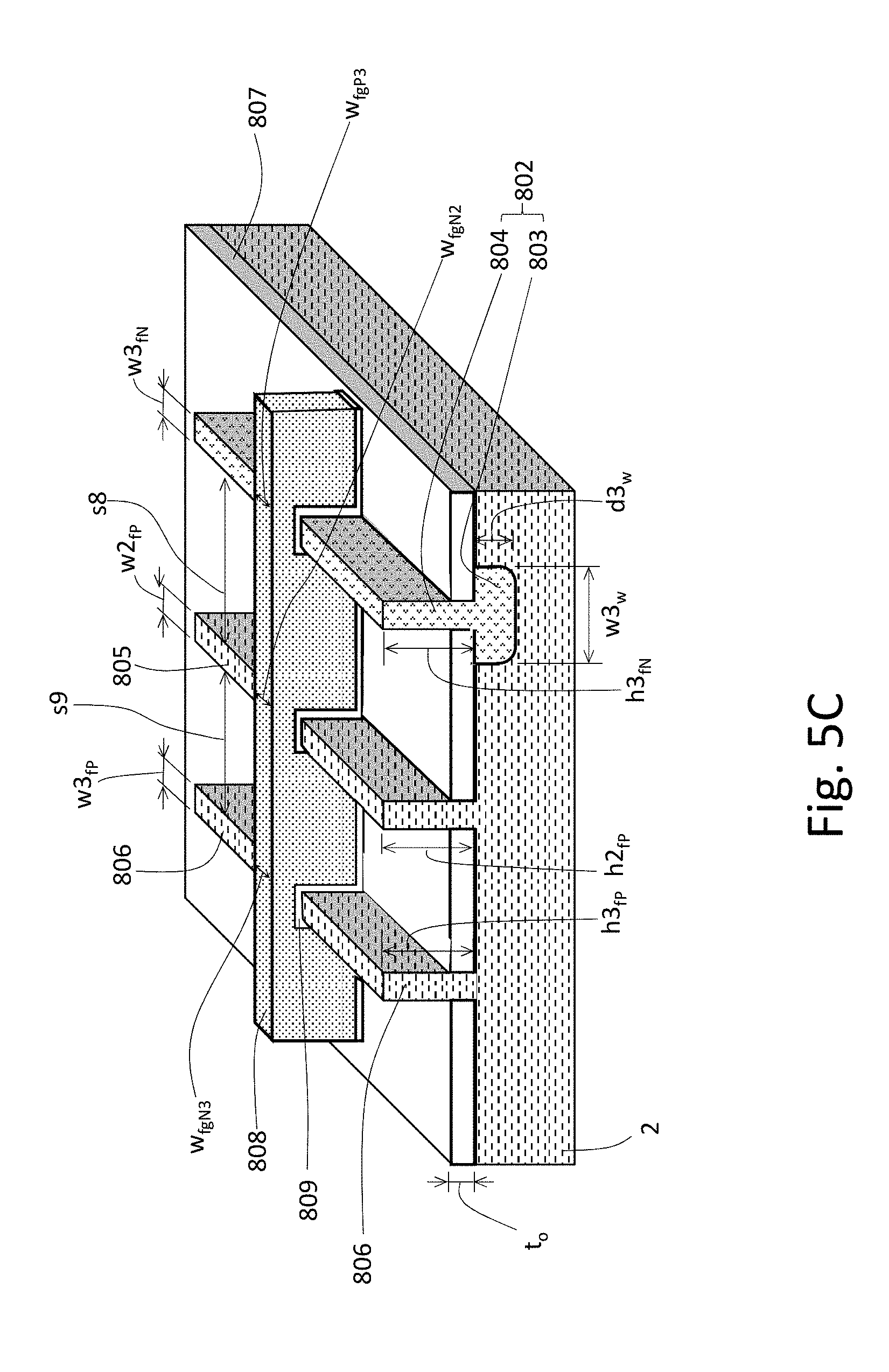

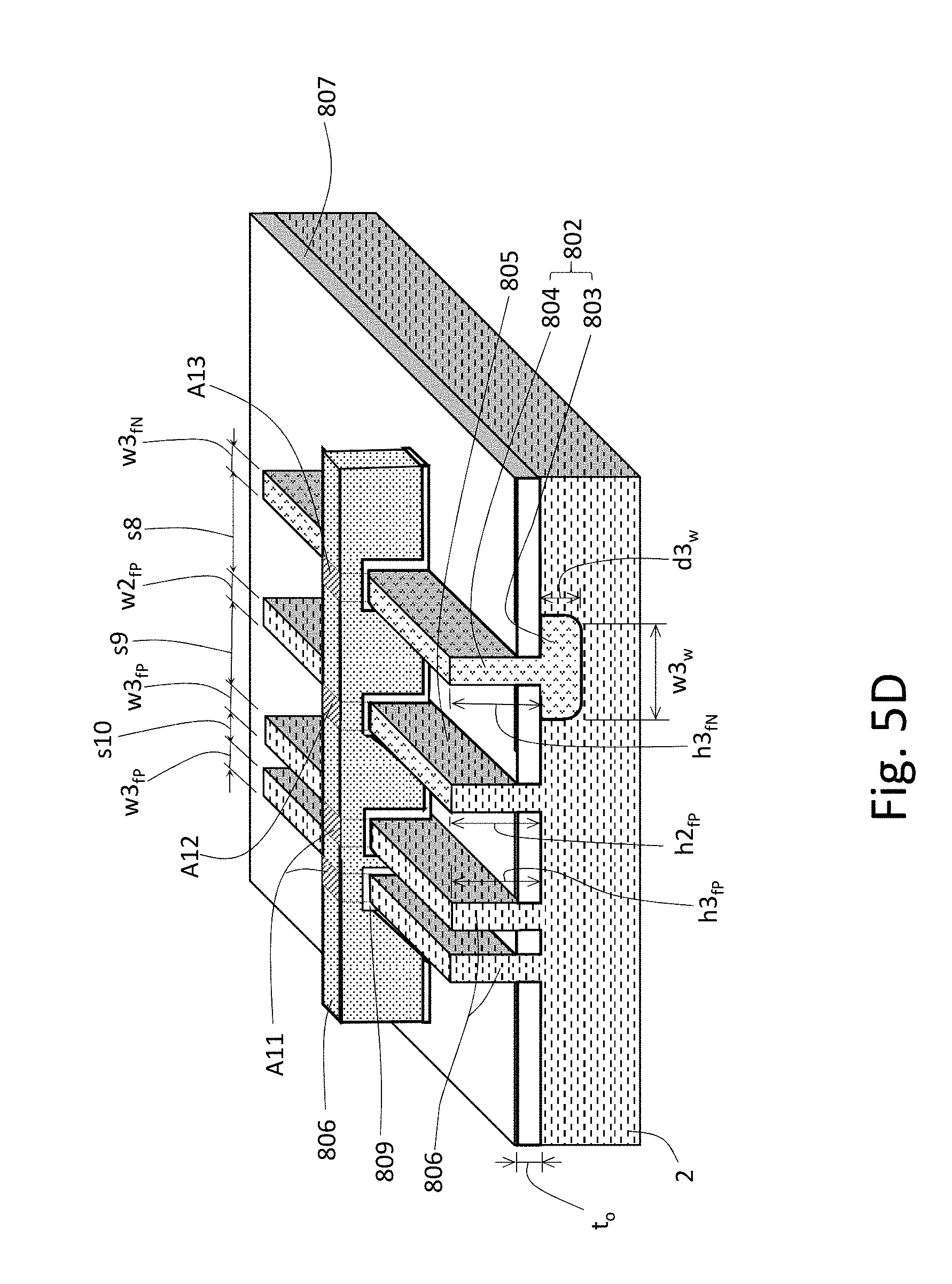

[0014] As another example, a third type of a FGCMOS NVM cell uses electron tunneling for both erasing and programming as in the above second type of the FGCMOS NVM cell. The third type of a FGCMOS NVM cell comprises an additional floating-gate P-MOS (AD FG P-MOS) transistor in addition to the floating-gate P-MOS (FG P-MOS) transistor and the floating-gate N-MOS (FG N-MOS) transistor in the above second type of the FGCMOS NVM cell. The floating gates of the FG P-MOS, the FG N-MOS and the AD FG P-MOS are connected, and the drains of the FG P-MOS and the FG N-MOS connected. The source, drain and well of the AD P-MOS are connected, so the AD FG P-MOS is functioning like a MOS capacitor. The sizes of the FG N-MOS transistor, the FG P-MOS transistor and the AD FG P-MOS may be designed such that the functions of erase, programing (write) and read of the third type of the FGCMOS NVM cell can be performed with a certain voltage biases at each of terminals. That is, the gate capacitances of the FG N-MOS transistor, the FG P-MOS transistor and the AD FG P-MOS may be designed for erase, write and read functions. In the following example, the sizes of the FG N-MOS transistor, the FG P-MOS transistor and the AD FG P-MOS are assumed the same; that is, the gate capacitances of the FG N-MOS transistor, the FG P-MOS transistor and the AD FG P-MOS are assumed the same. The data stored in the FGCMOS NVM cell is erased by electron tunneling through the gate oxide (or insulator) between the floating gate and the connected source/drain/well of the AD FG P-MOS by (i) biased or coupled the connected source/drain/well of the AD FG P-MOS with an erase voltage V.sub.Er, (ii) biased or coupled the source/well of the FG P-MOS with a ground voltage V.sub.ss, and (iii) biased or coupled the source/substrate of the FG N-MOS at a ground voltage V.sub.ss, and (iv) the connected drains of the FG P-MOS and the FG N-MOS are disconnected. Since the capacitance between the floating gate and the connected source/drain/well of the AD FG P-MOS is smaller than that of the sum of the gate capacitances of the FG P-MOS transistor and the FG N-MOS transistor, the voltage V.sub.Er is dropped largely across the gate oxide between the floating gate and the connected source/drain/well of the AD FG P-MOS; that means the voltage difference between floating gate and source/drain/well connected terminal of the AD FG P-MOS is large enough to cause the electron tunneling. Therefore, the electrons trapped in the floating gate are tunneling through the gate oxide between the floating gate and the connected source/drain/well of the AD FG P-MOS. The FGCMOS NVM cell after erase is at a logic state of "1". The data is stored or programmed in the FGCMOS NVM cell by electron tunneling through the gate oxide (or insulator) between the floating gate and the channel/source of the FG N-MOS by (i) biased or coupled the source/well of the FG P-MOS, and the connected source/drain/well of the AD FG P-MOS with a programming voltage V.sub.Pr, (ii) biased or coupled the source/substrate of the FG N-MOS with the ground voltage V.sub.ss, and (iii) the drain of the FG N-MOS is disconnected. Since the gate capacitance of the FG N-MOS transistor is smaller than the sum of the gate capacitances of the FG P-MOS transistor and the AD FG P-MOS, the voltage V.sub.Pr is dropped largely across the gate oxide of the FG N-MOS transistor; that means the voltage difference between floating gate and source/channel terminal of the FG N-MOS is large enough to cause the electron tunneling. Therefore, the electrons at the source/channel of the FG N-MOS transistor may tunnel through the gate oxide to the floating gate and be trapped in the floating gate. Thereby, the floating gate may be programmed to a logic level of "0". The "read", "access" or "operation" process or mode for the third type FGCMOS NVM cell is the same as that of the first type using the FG P-MOS transistor and the FG N-MOS transistor, except that the connected source/drain/well of the AD FG P-MOS may be biased or coupled to either V.sub.cc or V or a given voltage between V.sub.cc and V.sub.ss.

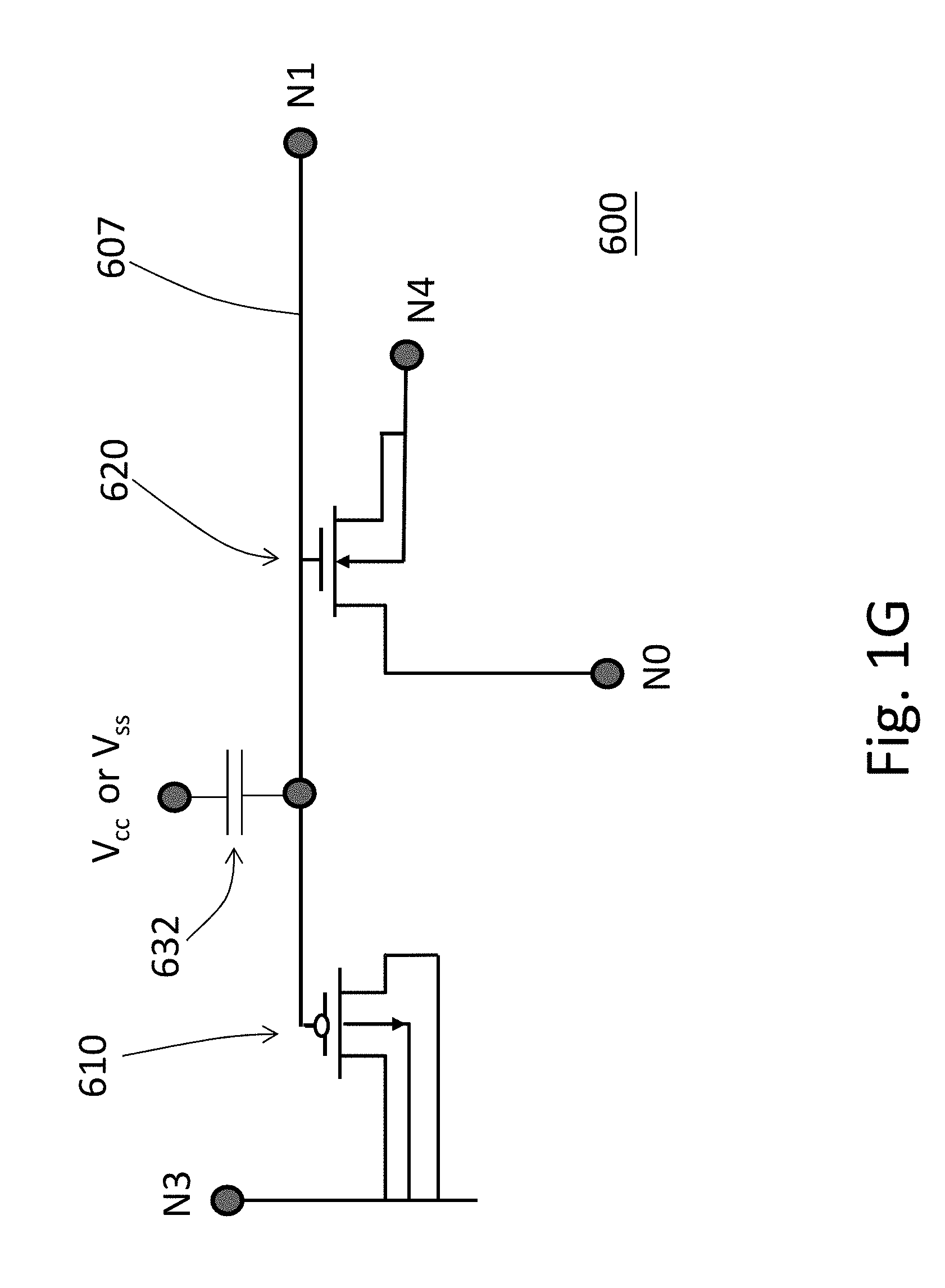

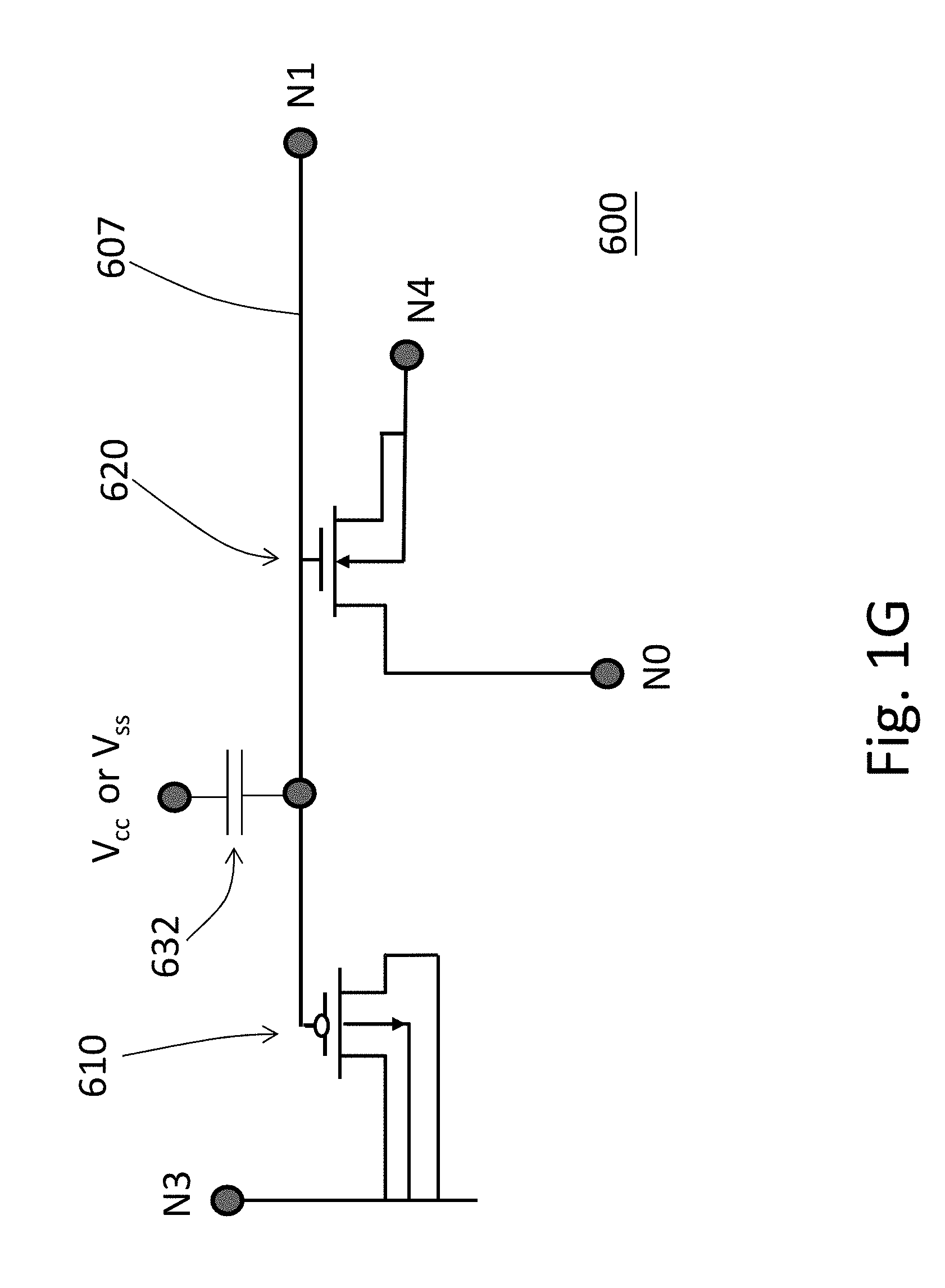

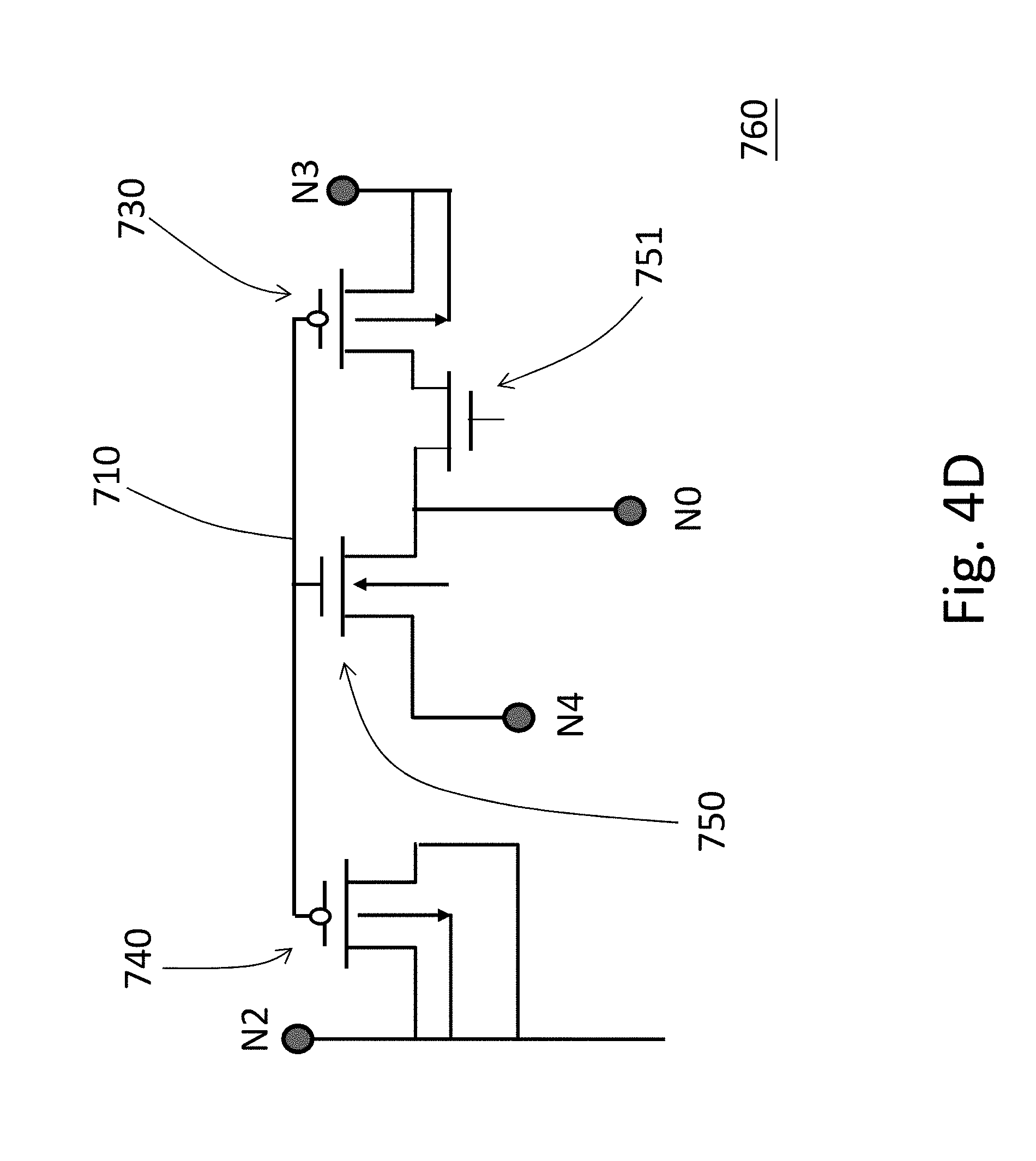

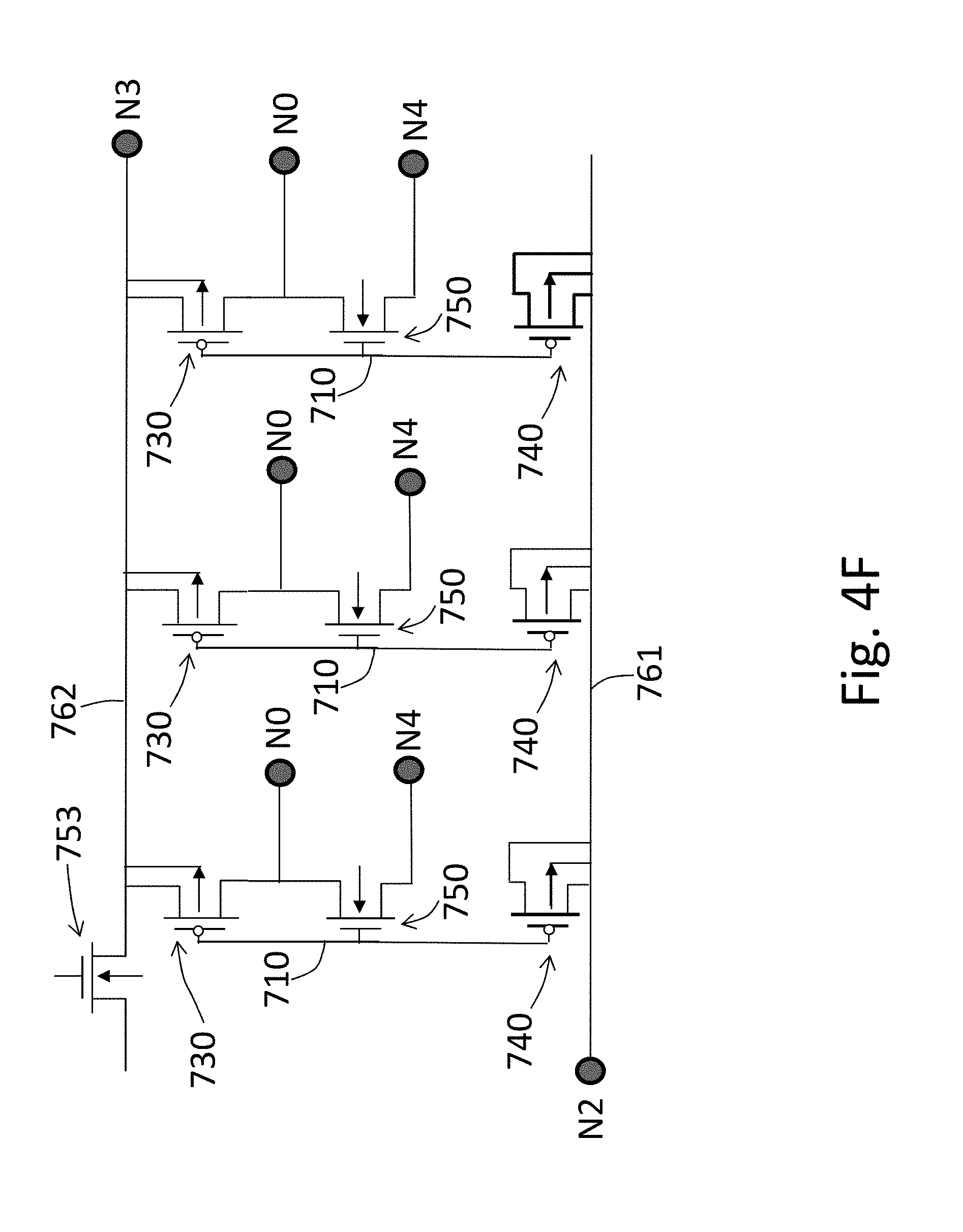

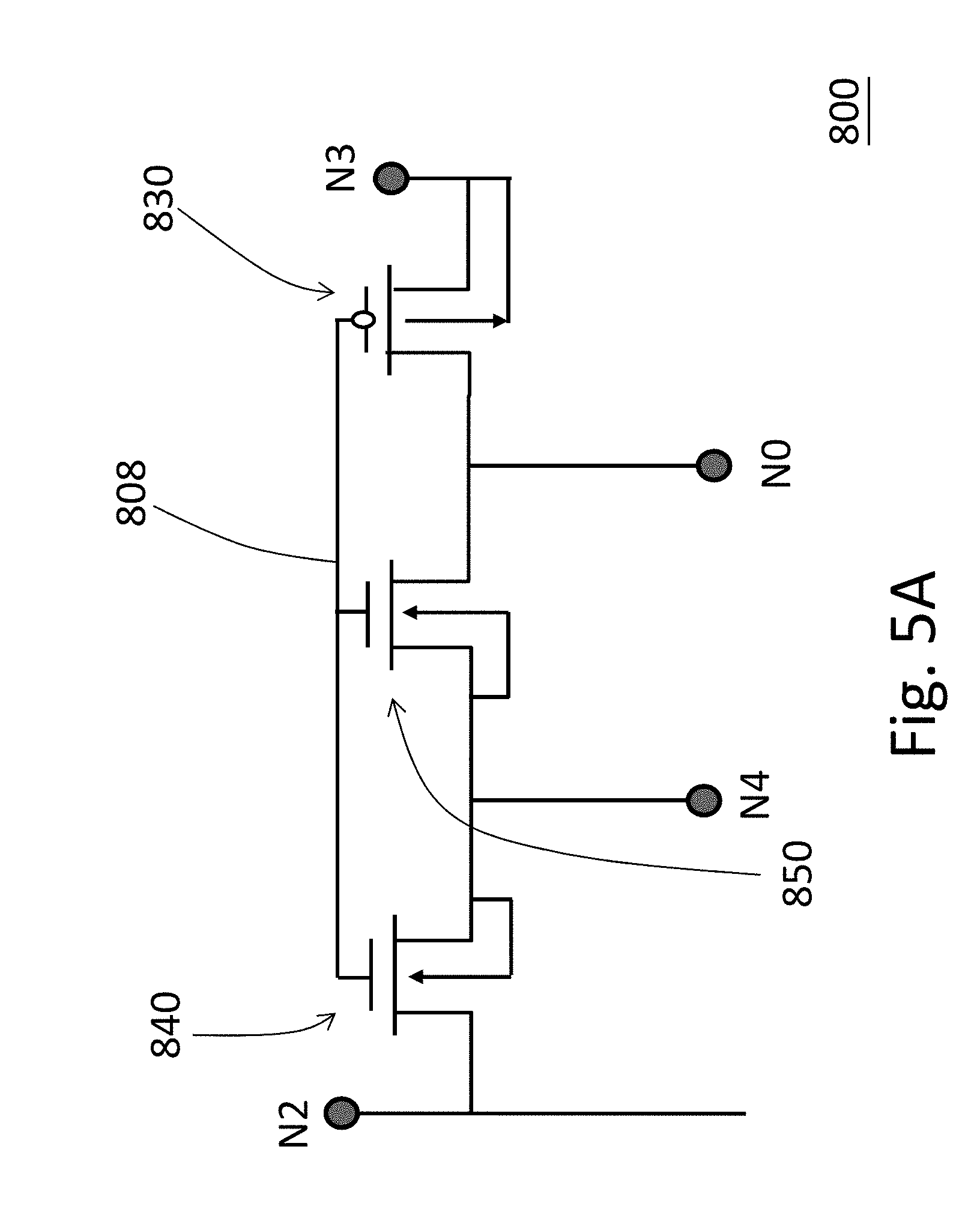

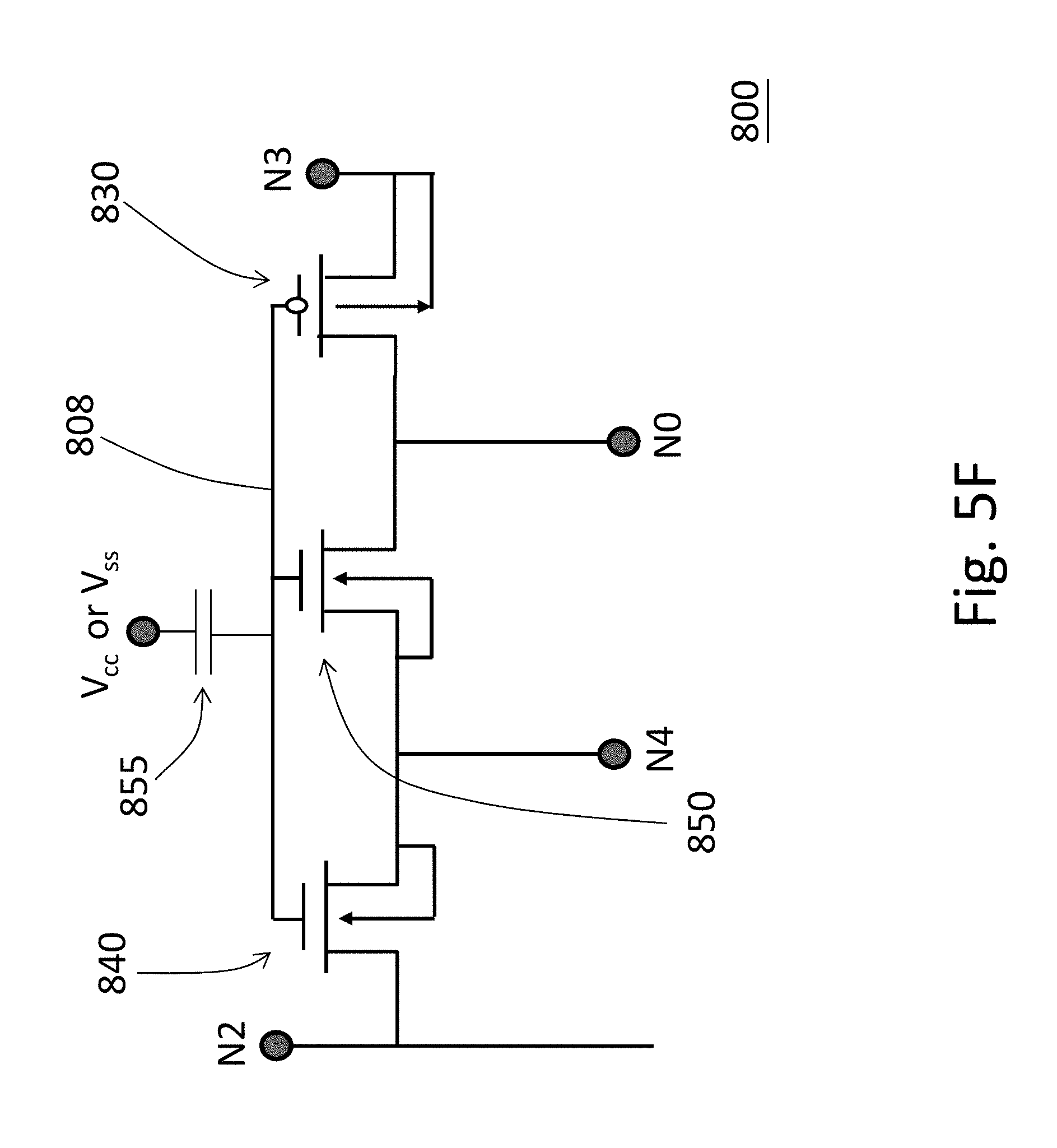

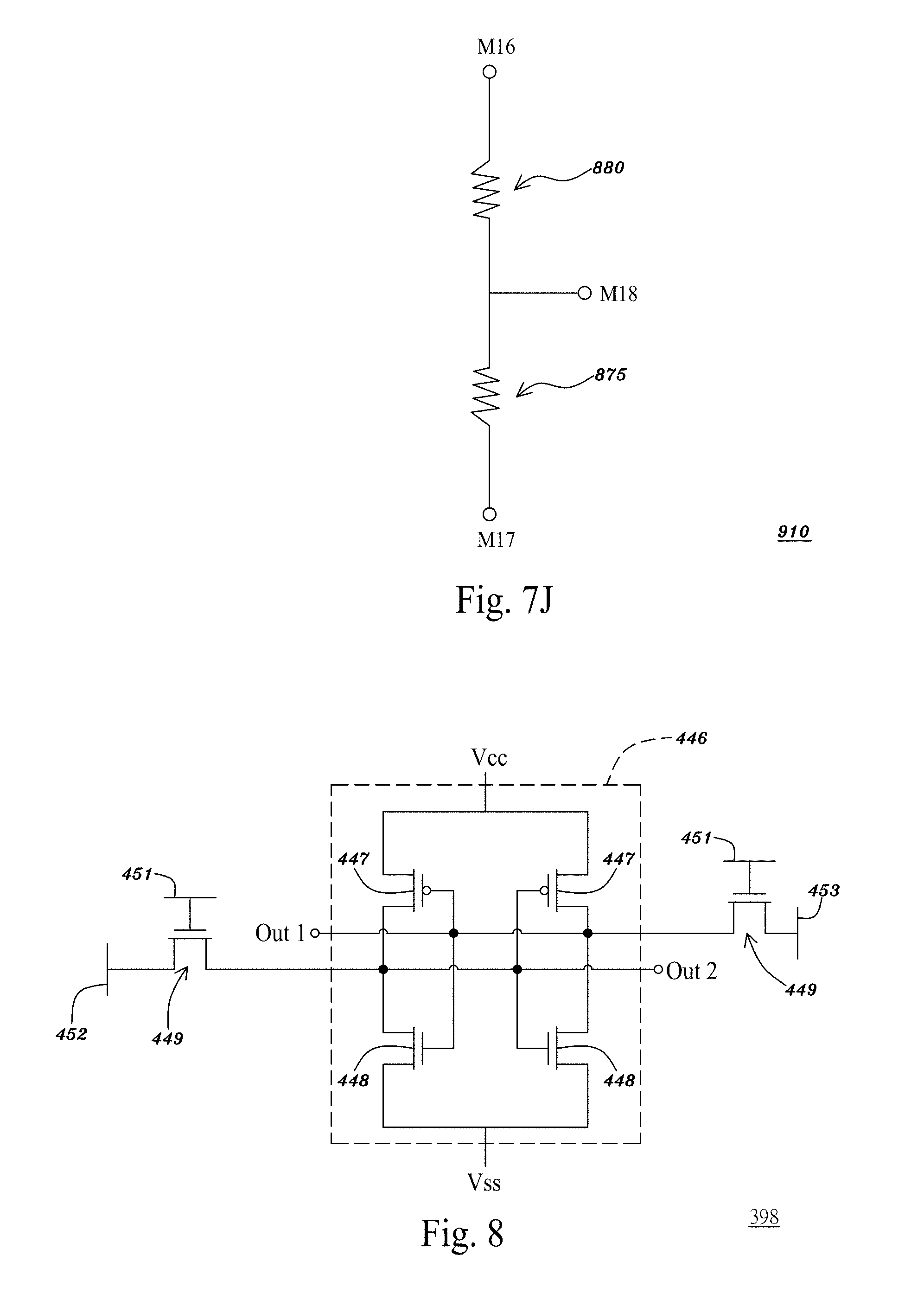

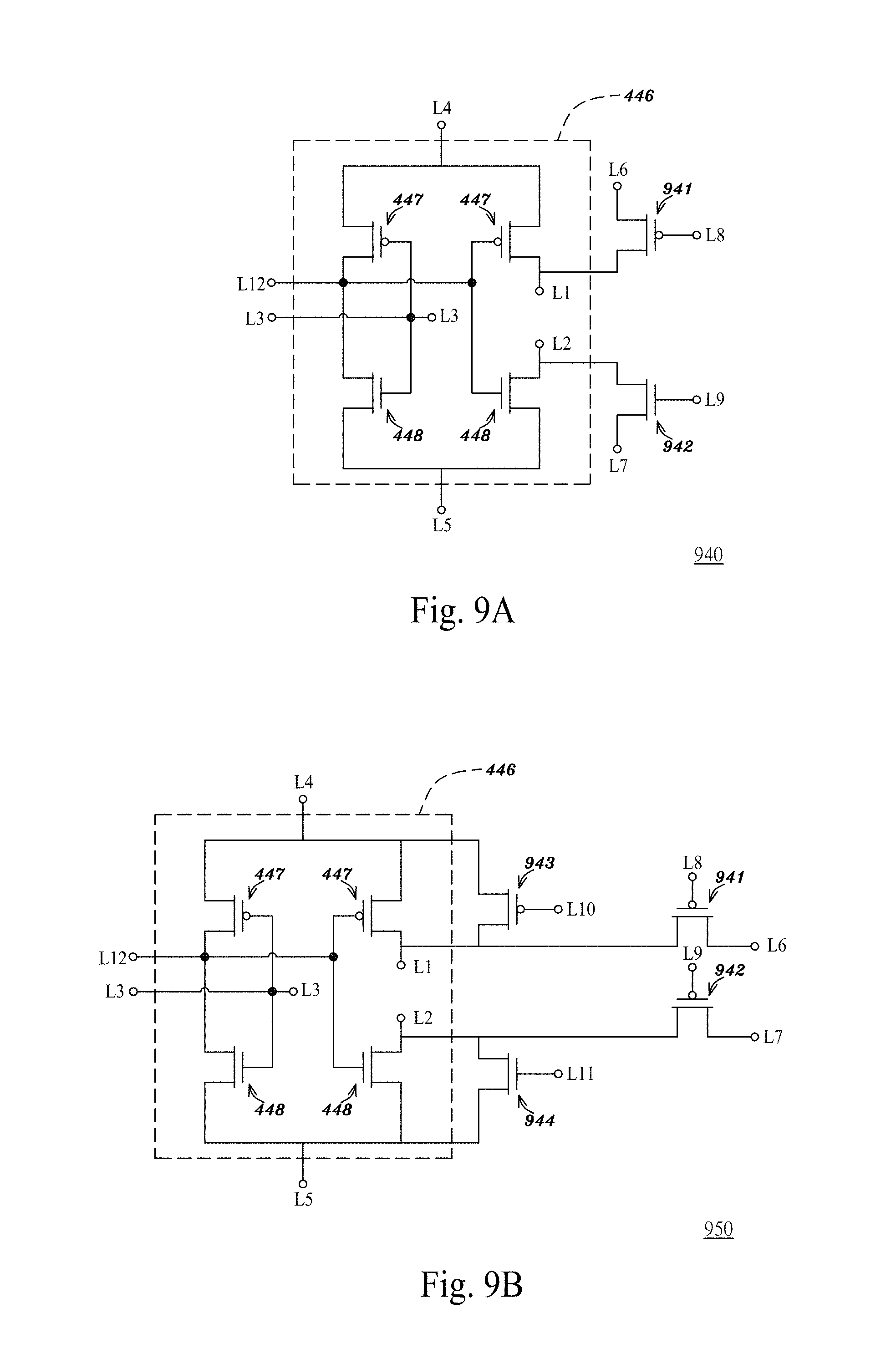

[0015] Another aspect of the disclosure provides a FGCMOS NVM cell, comprising a FGCMOS cell (the first, second or third types of the FGCMOS cells) as described and specified above, a latched circuit and a set/set-bar circuit for use in the standard commodity FPGA IC chip for programmable interconnection and/or for data storage of the LUTs. This type of FGCMOS NVM cell may be named as a Latched FGCMOS NVM cell, abbreviated as L-FGCMOS NVM. As an example, the latched circuit comprising two inverters as in the latched 4T circuit in the 6T SRAM cell. A drain of the P-MOS of a first inverter in the latched 4T circuit is connected or coupled to the source of the FG P-MOS (in the FGCMOS NVM), and a drain of the N-MOS of the first inverter in the latched 4T circuit is connected or coupled to the source of the FG N-MOS (in the FGCMOS NVM). The Bit-bar node of the latched 4T circuit is connected or coupled to (i) the connected or coupled drains of the FG P-MOS and FG N-MOS of the L-FGCMOS NVM cell, and (ii) the connected gates of the P-MOS and N-MOS of a second inverter of the latched 4T circuit. The Bit node of the latched 4T circuit is connected or coupled to (i) the connected drains of the P-MOS and N-MOS of the second inverter of the latched 4T circuit, and (ii) the connected gates of the P-MOS and N-MOS of the first inverter. A drain of Set-bar P-MOS transistor is connected to the source of the FG P-MOS, and a drain of Set N-MOS transistor is connected to the source of the FG N-MOS. In the programming or write process, the first type of FGCMOS NVM described and specified above is used here as an example: (i) to write Bit of `1", the voltage biases at nodes or terminals are: (a) the gate of the Set-bar P-MOS is connected or coupled to a low operation voltage (V.sub.ss), and the gate of the Set N-MOS is connected or coupled to a high operation voltage (V.sub.cc); (b) the source of Set-bar P-MOS and the N-well of the FG P-MOS are connected or coupled to the programming voltage (V.sub.Pr), and the source of Set N-MOS is connected or coupled to the low operation or ground voltage (V.sub.ss); (c) the connected or coupled drains (Bit-bar node) of FGCMOS are connected or coupled with a programming (write) voltage V.sub.Pr, and (d) the common sources of P-MOS's and N-MOS's in the 4T latched circuit are disconnected. The hot electrons are injected to and trapped in the floating gate by the hot carrier injection through the gate oxide of the FG N-MOS, and the FG NVM cell after programming (write) is at a logic state of `0` at the Bit-bar node and at logic state of "1" at the Bit node; (ii) to write Bit of `0", or to erase the electrons in the floating gate, (a) the gate of the Set-bar P-MOS is connected or coupled to a low operation voltage (V.sub.ss), and the gate of the Set N-MOS is connected or coupled to a high operation voltage (V.sub.cc); (b) the source of Set-bar P-MOS and the N-well of the FG P-MOS are connected or coupled to the erase voltage (V.sub.Er), and the source of Set N-MOS is connected or coupled to the low operation or ground voltage (V.sub.ss); and (c) the connected or coupled drains of the FG CMOS (Bit-bar node) are disconnected. The electrons trapped in the floating gate are tunneling through the gate oxide of the FG P-MOS transistor, and the FG NVM cell after erase is at a logic state of `0` at the Bit-bar node and at logic state of "1" at the Bit node.

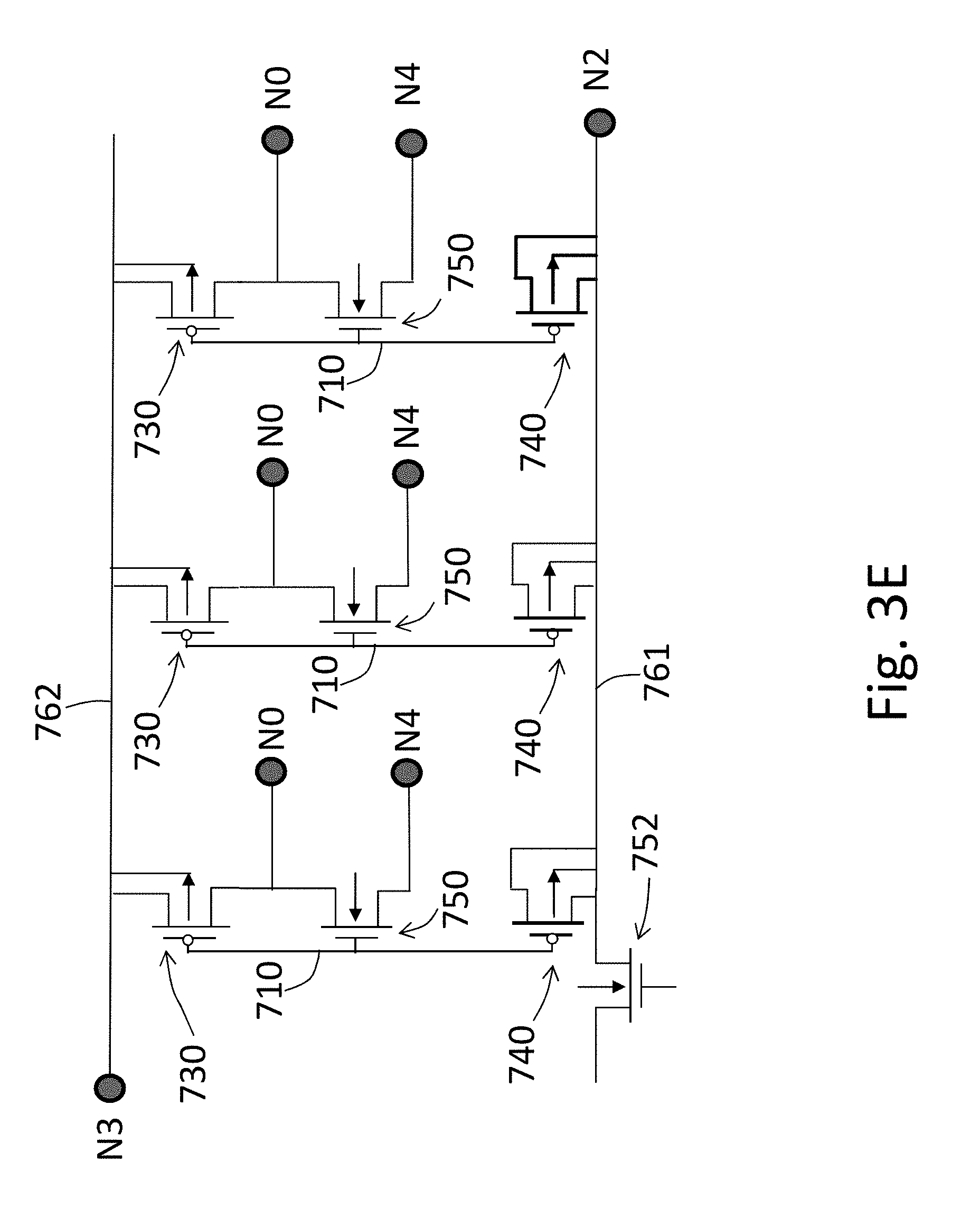

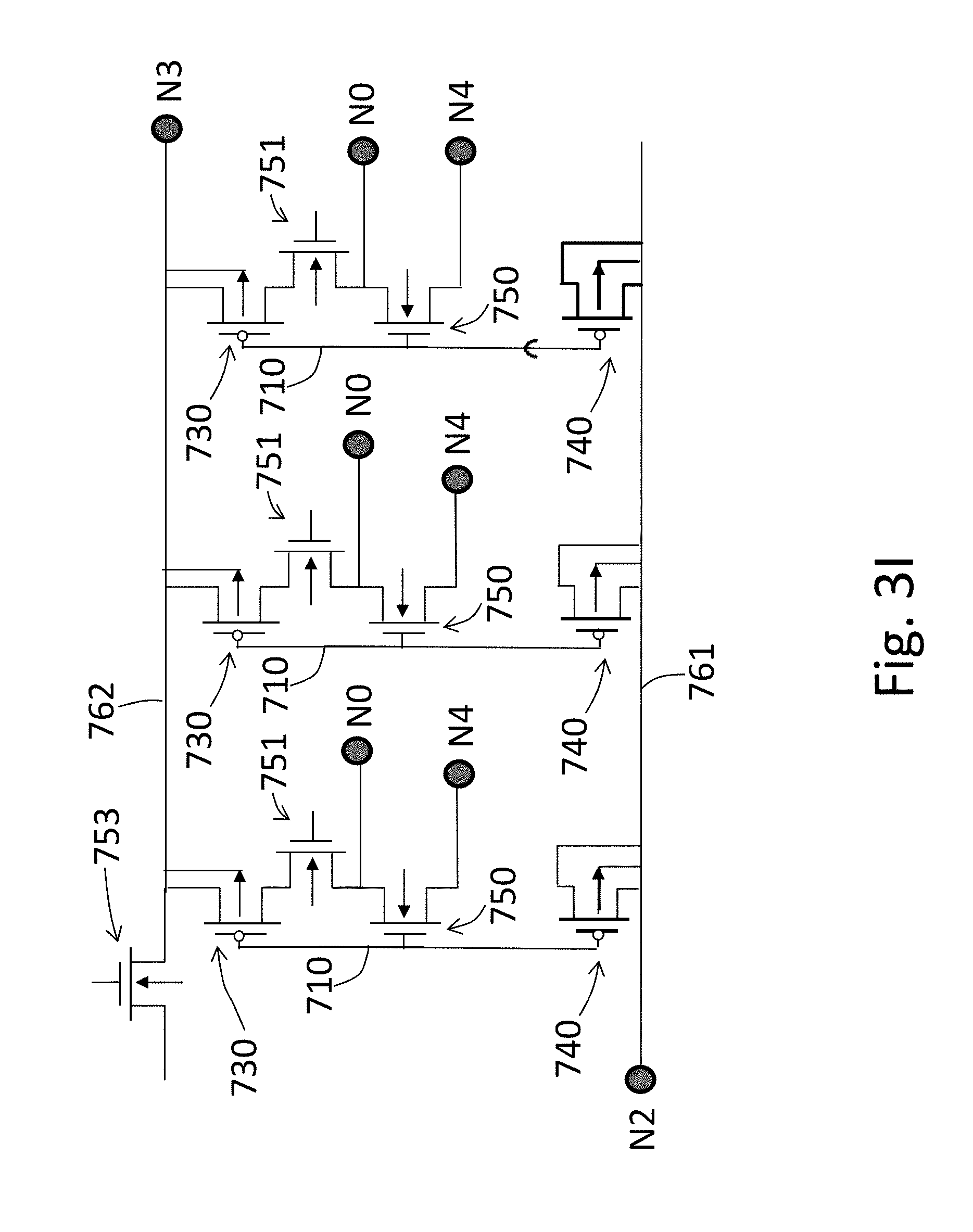

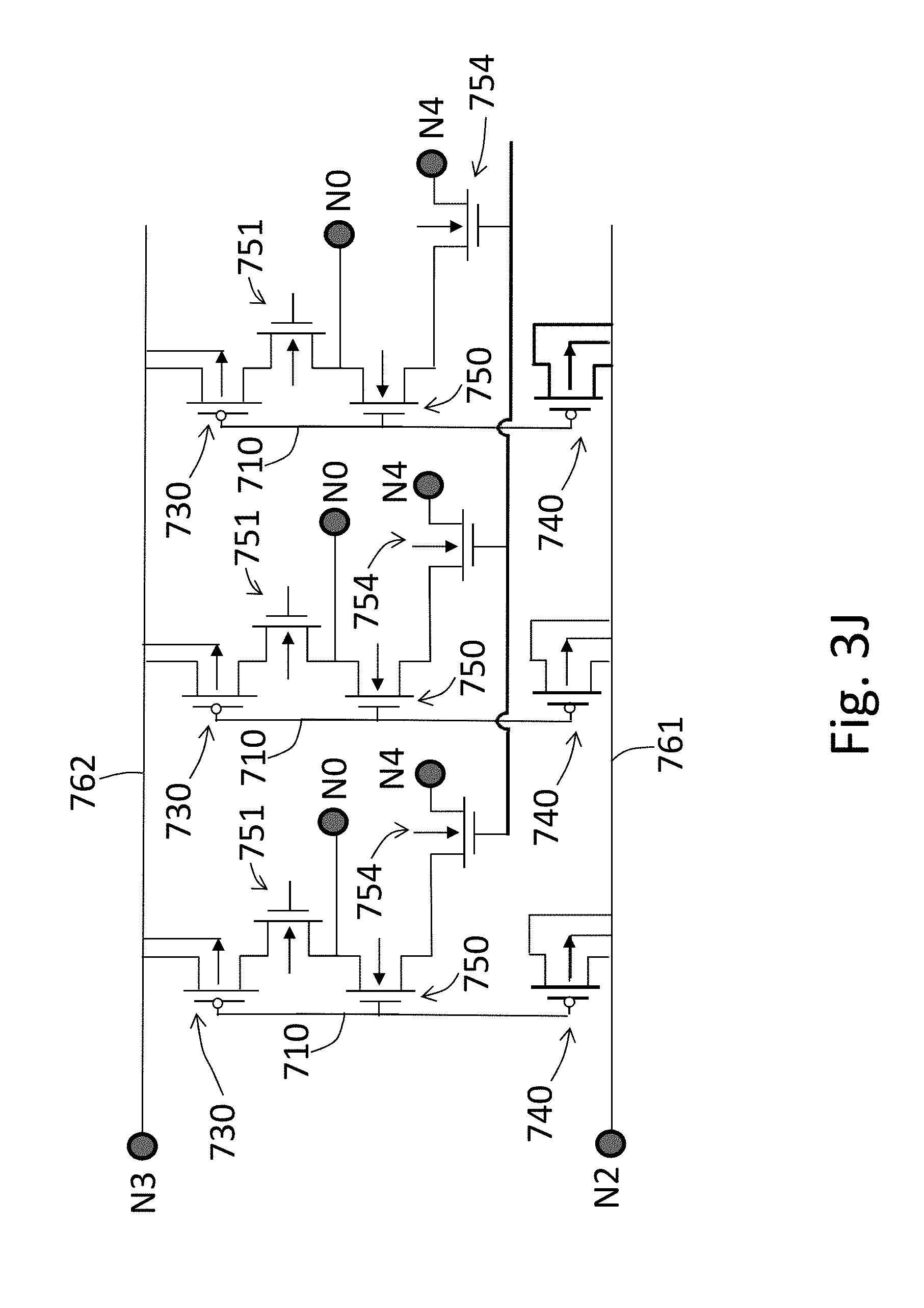

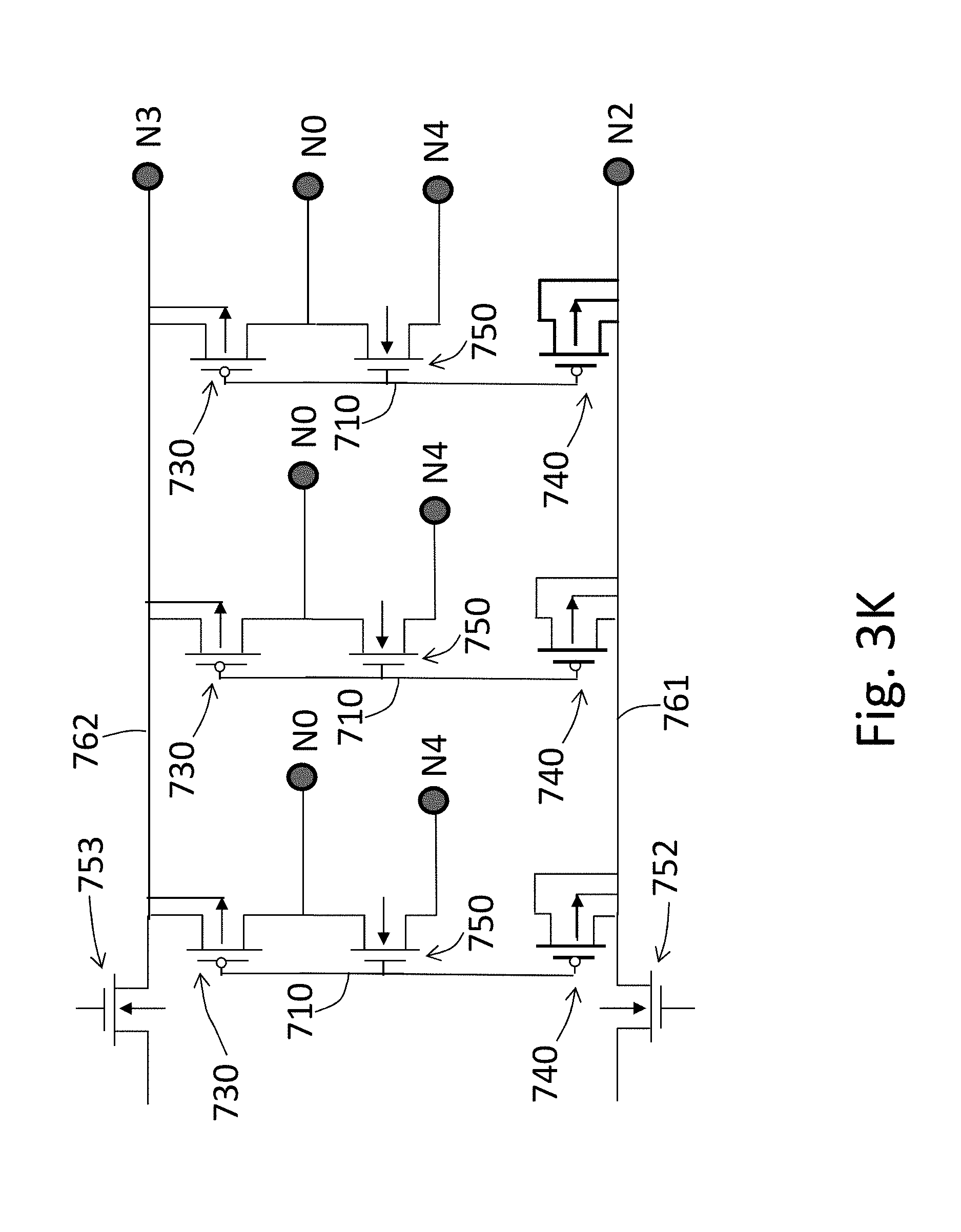

[0016] The L-FGCMOS NVM provides correction, recovery capability when the device or the FPGA IC chip is turned on, to prevent data errors caused by charge leakage during the time when the device or the FPGA chip is turn off. The data stored in the Bit-bar and Bit nodes are recovered to the correct states after the initiation process. In the initiation process after the device or the FPGA IC chip is turned on: (i) the gate of the Set-bar P-MOS is connected or coupled to a low operation or ground voltage (V.sub.ss), and the gate of the Set N-MOS is connected or coupled to a high operation voltage (V.sub.cc); the source of the Set-bar P-MOS is connected or coupled to the high operation voltage (V.sub.cc), and the source of the Set N-MOS is connected or coupled to the low operation or ground voltage (V.sub.ss); (ii) the common sources of P-MOS's in the 4T latched circuit are connected or coupled to the high operation voltage (V.sub.cc), and the common sources of N-MOS's in the 4T latched circuit are connected or coupled to the low operation or ground voltage (V.sub.ss). After the initiation process, the data stored in the Bit-bar and Bit nodes are recovered to the correct states. In the read operation process, the information stored in the FGCMOS NVM cells may be read. In the read operation process: (i) the gate of the Set-bar P-MOS is connected or coupled to a high operation voltage (V.sub.cc), and the gate of the Set N-MOS is connected or coupled to a low operation voltage (V.sub.ss); the source of the Set-bar P-MOS and the source of the Set N-MOS may be disconnected; (ii) the common sources of P-MOS's in the 4T latched circuit is connected or coupled to the high operation voltage (V.sub.cc), and the common sources of N-MOS's in the 4T latched circuit is connected or coupled to the low operation or ground voltage (V.sub.ss). The Bit and/or Bit-bar data of the L-FGCMOS NVM is used for programming the interconnection in the FPGA IC chips, or for the data storage for the LUT operation process.

[0017] Another aspect of the disclosure provides a Magnetoresistive Random Access Memory cell, abbreviated as "MRAM" cell, for use in the standard commodity FPGA IC chip for programmable interconnection and/or for data storage of the LUTs. The MRAM cell is based on the interactionbetween the electron spin and the magnetic field of the magnetic layers in a Magnetoresisitive Tunneling Junction (MTJ) of the MRAM cell. The MRAM cell uses a spin-polarized current to switch the spin of electrons, the so-called Spin Transfer Torque MRAM, STT-MRAM. The MRAM cell mainly comprises four stacked thin layers: (i) a free magnetic layer, comprising, for example, Co.sub.2Fe.sub.6B.sub.2. The free layer has a thickness between 0.5 nm and 3.5 nm, or 1 nm and 3 nm; (ii) a tunneling barrier layer, comprising for example, MgO. The tunneling barrier layer has a thickness between 0.3 nm and 2.5 nm, or 0.5 nm and 1.5 nm; (iii) a pinned or fixed magnetic layer comprising, for example, Co.sub.2Fe.sub.6B.sub.2. The pinned layer has a thickness between 0.5 nm and 3.5 nm, or 1 nm and 3 nm. The pinned layer may have a similar material as that of the free layer; and (iv) a pinning layer; comprising, for example, an anti-ferromagnetic (AF) layer. The AF layer may be a synthetic layer comprising, for example, Co/[CoPt].sub.4. The direction of the magnetization of the pinned layer is pinned or fixed by the neighboring pinning layer of the AF layer. The stacked layers of the MTJ may be formed by the Physical Vapor Deposition (PVD) method using a multi-cathode PVD chamber or sputter, followed by etching to form a mesa structure of MTJ. The direction of the magnetization of the free layer or the pinned (fixed layer) may be (i) in-plane with the free or pined (fixed) layer (iMTJ) or (ii) perpendicular to the plane of the free or pinned (fixed) layer (pMTJ). The direction of magnetization of the pinned (fixed) layer is fixed by the bi-layers structure of pinned/pinning layers. The interfacing of the ferromagnetic pinned (fixed) layer and the AF pinning layer results in that the direction of ferromagnetic pinned (fixed) layer is in a fixed direction (for example, up or down in the pMTJ), and becomes harder to change or flip in external electromagnetic force or field. While the direction of ferromagnetic free layer (for example, up or down in the pMTJ) is easier to change or flip in external electromagnetic force or field. The change or flip the direction of the ferromagnetic free layer is used for programming the MTJ MRAM cell. The state "0" is defined when the magnetization direction of the free layer is in-parallel with or in the same direction of that of the pinned (fixed) layer; and the state "1" is defined when the magnetization direction of the free layer is anti-parallel with or in the reverse direction of that of the pinned (fixed) layer. To write "0", electrons are tunneling from the pinned layer to the free layer. When electrons flow through the pinned or fixed layer, the electron spins will be aligned in-parallel with the magnetization direction of the pinned (fixed) layer. When the tunneling electrons with aligned spins flowing in the free layer, (i) the tunneling electrons may be passing through the free layer if the aligned spins of the tunneling electrons are in-parallel with that of the free layer, (ii) the tunneling electrons may flip or change the direction of the magnetization of the free layer to a direction in-parallel with the fixed layer using the spin torque of the electrons if the aligned spins of the tunneling electrons are not in-parallel with that of the free layer. After writing "0", the direction of the magnetization of the free layer is in-parallel with that of the fixed layer. To write "1" from the original "0", electrons are tunneling from the free layer to the pinned (fixed) layer. Since the directions of the magnetizations of the free layer and the pinned (fixed) layer are the same, the electrons with majority of spin polarity (in-parallel with the magnetization direction of the pinned layer) may flow and pass the pinned (fixed) layer; only electrons with minority spin polarity (not in-parallel with the magnetization direction of the pinned layer) may be reflected from pinned (fixed) layer and back to the free layer. The spin polarity of reflected electrons is in the reverse direction of the magnetization of the free layer, and may flip or change the direction of the magnetization of the free layer to a direction reverse-parallel to the fixed layer using the spin torque of the electrons. After writing "1", the direction of the magnetization of the free layer is anti-parallel to that of the fixed layer. Since write "1" is using the minority spin polarity electrons, a larger current flow through MTJ is required as compared to write "0".

[0018] Based on the magnetoresistance theory, the resistance of a MTJ is at low resistance state (LR), the "0" state, when the direction of the magnetization of the free layer is in-parallel with the direction of that of the fixed layer; while at high resistance state (HR), the "1" state, when the direction of the magnetization of the free layer is anti-parallel with the direction of that of the fixed layer. The two states of resistance may be used in read the MTJ MRAM cell.

[0019] Another aspect of the disclosure provides a MRAM cell, comprising two complementary MTJs for use in the standard commodity FPGA IC chip for programmable interconnection and/or for data storage of the LUTs. This type of MRAM cell may be named as a Complementary MRAM cell, abbreviated as CMRAM. The two MTJs are formed by stacks comprising pinning/pinned/barrier/free layers, from top to the bottom as the FPGA IC chips are facing up (with transistors and the metal interconnection structures on or over the silicon substrate). A top electrode of the First MTJ (F-MTJ) may be connected or coupled to a top electrode of the Second MTJ (S-MTJ). Alternatively, a bottom electrode of the First MTJ (F-MTJ) may be connected or coupled to a bottom electrode of the Second MTJ (S-MTJ). In other alternative, the two MTJs are formed by stacks comprising free/barrier/pinned/pinning layers, from top to the bottom as the FPGA IC chips are facing up (with transistors and the metal interconnection structures on or over the silicon substrate). A top electrode of the First MTJ (F-MTJ) may be connected or coupled to a top electrode of the Second MTJ (S-MTJ). Alternatively, a bottom electrode of the First MTJ (F-MTJ) may be connected or coupled to a bottom electrode of the Second MTJ (S-MTJ). The node or terminal connected or coupled to the electrode of the pinning layer is the node P of a MTJ, and the node or terminal connected or coupled to the electrode of the free layer is the node F of the MTJ. The CMRAM may be programmed or written for the F-MTJ and the S-MTJ as described above for a single MTJ. The F-MTJ and S-MTJ in the CMRAM cell (a type of MRAM cell) are in anti-polarity; that is, when F-MTJ is at the HR state, the S-MTJ is at LR state, and when F-MTJ is at the LR state, the S-MTJ is at the HR state. For example, in the case if the connected node is the connected or coupled electrodes of the free layers for the F-MTJ and the S-MTJ, the CMRAM cell may be written "0", by connecting the P node of the F-MTJ to a programming voltage (V.sub.P) and the P node of the S-MTJ to V.sub.ss. The S-MTJ is programmed at the LR state, and the F-MTJ is programmed at the HR state. The CMRAM is at the [1,0] state, defined as the "0" state of the CMRAM. The CMRAM cell may be written "1", by connecting the P node of the S-MTJ to a programming voltage (V.sub.P) and the P node of the F-MTJ to V.sub.ss. The S-MTJ is programmed at the HR state, and the F-MTJ is programmed at the LR state. That is, the CMRAM is at the [0,1] state, defined as the "1" state of the CMRAM. To read the data, the P node of the F-MTJ is connected to V.sub.cc, the P-node of the S-MTJ is connected to V.sub.ss, and the F nodes of the F-MTJ and the S-MTJ are electrically connected.

[0020] Another aspect of the disclosure provides a MRAM cell, comprising a CMRAM, a latched circuit and a set/set-bar circuit for use in the standard commodity FPGA IC chip for programmable interconnection and/or for data storage of the LUTs. This type of MRAM cell may be named as a Latched MRAM cell, abbreviated as LMRAM. As an example, the latched circuit comprising two inverters as in the latched 4T circuit of the 6T SRAM cell. A drain of the P-MOS of a first inverter of the latched 4T circuit is connected or coupled to the P node of the F-TWJ, and a drain of the N-MOS of the first inverter of the latched 4T circuit is connected or coupled to the P node of the S-TWJ. The Bit-bar node of the latched 4T circuit is connected or coupled to (i) the connected or coupled nodes (the F nodes of the F-TWJ and the S-TWJ) of the CMRAM cell, and (ii) the connected gates of the P-MOS and N-MOS of a second inverter of the latched 4T circuit. The Bit node of the latched 4T circuit is connected or coupled to (i) the connected drains of the P-MOS and N-MOS of the second inverter of the latched 4T circuit, and (ii) the connected gates of the P-MOS and N-MOS of the first inverter. A Set-bar P-MOS transistor of the set/set-bar circuit is connected to the P node of the F-TWJ, and a Set N-MOS transistor of the set/set-bar circuit is connected to the P node of the S-TWJ. In the programming or write process, the gate of the Set-bar P-MOS is connected or coupled to a low operation or ground voltage (V.sub.ss), and the gate of the Set N-MOS is connected or coupled to a high operation voltage (V.sub.cc), with the common sources of P-MOS's and N-MOS's in the 4T latched circuit disconnected. When the source of the Set-Bar P-MOS is connected or coupled to the programming voltage (V.sub.P), and the source of the Set N-MOS is connected or coupled to the low operation or ground voltage (V.sub.ss), F-TWJ is at the HR state, and the S-TWJ is at the LR state, the Bit-bar node is "0", and the another latched node, the Bit node, is at "1". When the source of the Set-bar P-MOS is connected or coupled to the low or ground voltage (V.sub.ss), and the source of the Set N-MOS is connected or coupled to the programming voltage (V.sub.P), F-TWJ is at the LR state, and the S-TWJ is at the HR state, the Bit-bar node is "1", and the another latched node, the Bit node, is at "0".

[0021] The LMRAM provides correction, recovery capability when the device or the FPGA IC chip is turned on, to prevent the data errors caused by the charge leakage during the time when device or the FPGA chip is turn off. The data stored in the Bit-bar and Bit are recovered to the correct state after the initiation process. In the initiation process after the device or the FPGA IC chip is turned on: (i) the gate of the Set-bar P-MOS is connected or coupled to a low operation or ground voltage (V.sub.ss), and the gate of the Set N-MOS is connected or coupled to a high operation voltage (V.sub.cc); the source of the Set P-MOS is connected or coupled to the high operation voltage (V.sub.cc), and the source of the Set N-MOS is connected or coupled to the low operation or ground voltage (V.sub.ss), (ii) the common sources of P-MOS's in the 4T latched circuit is connected or coupled to the high operation voltage (V.sub.cc), and the common sources of N-MOS's in the 4T latched circuit is connected or coupled to the low operation or ground voltage (V.sub.ss). After the initiation process, the data stored in the Bit-bar and Bit nodes are recovered to the correct states. In the read operation process, the information stored in the non-volatile MRAM cells or the TWJs may be read. In the read operation process: (i) the gate of the Set-bar P-MOS is connected or coupled to a high operation voltage (V.sub.cc), and the gate of the Set N-MOS is connected or coupled to a low operation or ground voltage (V.sub.ss); the source of the Set-bar P-MOS and the source of the Set N-MOS may be disconnected, (ii) the common sources of P-MOS's in the 4T latched circuit is connected or coupled to the high operation voltage (V.sub.cc), and the common sources of N-MOS's in the 4T latched circuit is connected or coupled to the low operation or ground voltage (V.sub.ss). The Bit and/or Bit-bar data of the LMRAM is used for programming the interconnection in the FPGA IC chips, or for the data storage of the LUTs.

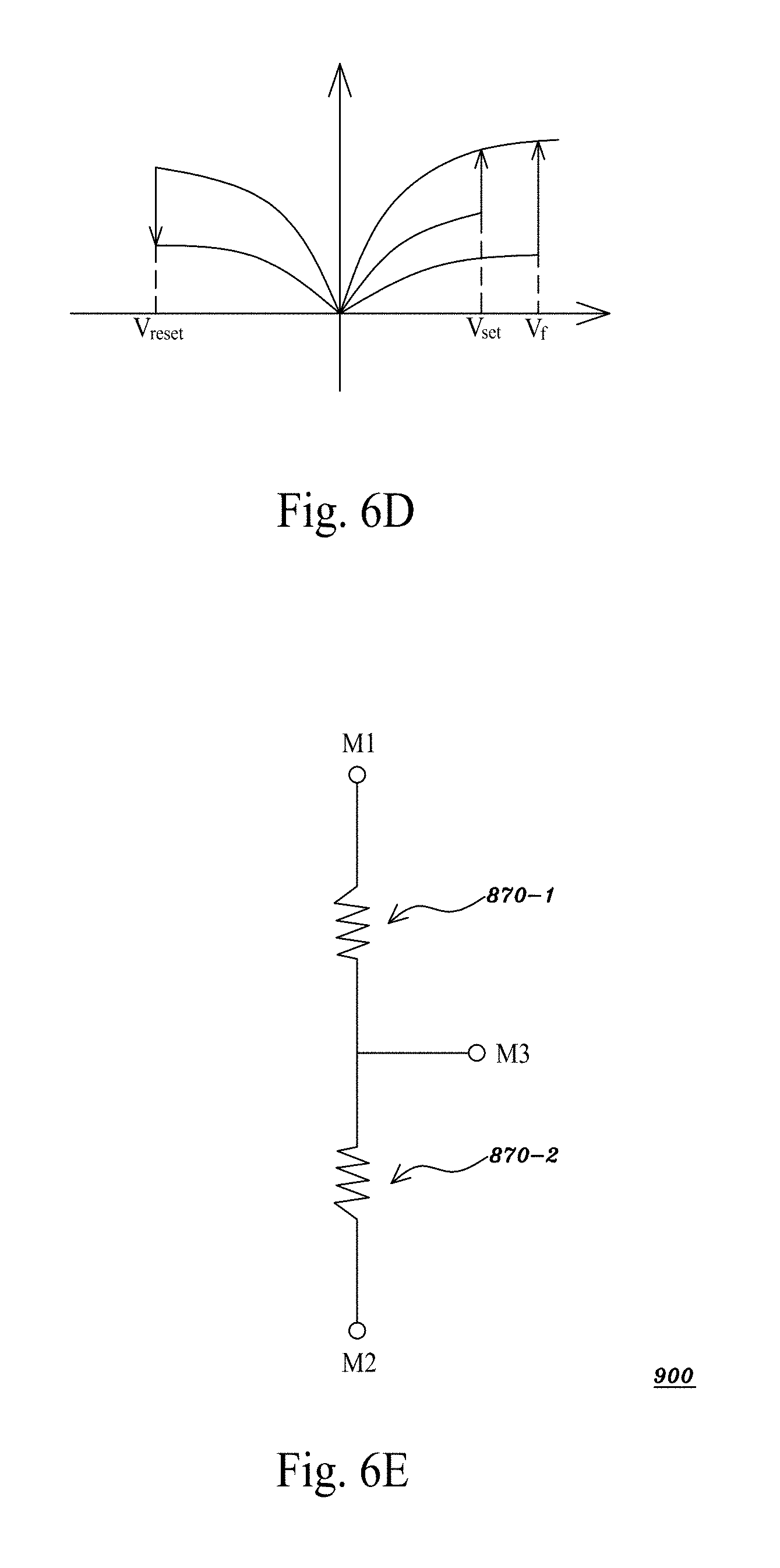

[0022] Another aspect of the disclosure provides a Resistive Random Access Memory cell, abbreviated as "RRAM" cell, for use in the standard commodity FPGA IC chip for programmable interconnection and/or for data storage of the LUTs. The RRAM cell is based on the nano-morphological modifications associated with the formation of oxygen vacancies (V.sub.o). The RRAM is based on oxidation-reduction (redox) electrochemical processes of a solid electrolyte. In the electroforming process of oxide-based RRAM devices, the oxide layer undergoes certain nano-morphological modifications associated with the formation of oxygen vacancies (V.sub.o). The RRAM cell is switched by the presence or absence of conductive filaments or paths in the oxide layer, depending on the applied electric voltages. The RRAM cell comprises a Metal/Insulator/Metal (MIM) device or structure, and mainly comprises four stacked thin layers: (i) a first metal electrode layer, for example, the metal may comprise titanium nitride (TiN) or tantalum nitride (TaN); (ii) an oxygen reservoir layer which may capture the oxygen atoms from an oxide layer. The oxygen reservoir layer may be a layer of metal comprising titanium (Ti), or tantalum (Ta). Both Ti or Ta material may capture the oxygen atoms to form TiO.sub.x or TaO.sub.x. The thickness of Ti layer may be 2 nm, 7 nm, or 12 nm; or, between 1 nm and 25 nm or 3 nm and 15 nm. The oxygen reservoir layer may be formed by Atomic Layer Deposition (ALD) methods; (iii) an oxide layer or an insulator layer, in which conductive filaments or paths may be formed depending on the applied electric voltages. The oxide layer may comprise, for example, hafnium oxide (HfO.sub.2) or Tantalum Oxide Ta.sub.2O.sub.5. The thickness of HfO.sub.2 may be 5 nm, 10 nm, or 15 nm; or, between 1 nm and 30 nm, 3 nm and 20 nm, or 5 nm and 15 nm. The oxide layer may be formed by Atomic Layer Deposition (ALD) methods; (iv) a second metal electrode layer, for example, the metal may comprise titanium nitride (TiN) or tantalum nitride (TaN). The RRAM cell is a kind of memristors (memory resistors). In the forming process stage, the first electrode of a MIM device (RRAM cell) is biased, connected or coupled to a forming voltage (V.sub.F), and the second electrode is biased, connected or coupled to a low operation or ground voltage (V.sub.ss). The forming voltage will drive or pull oxygen ions from the oxide layer (for example, HfO.sub.2) to the oxygen reservoir layer (for example, Ti), to form TiO.sub.x. Vacancies in the original oxygen sites in the oxide or insulating layer are created and forming one or more conductive filaments or paths in the oxide or insulting layer. The oxide or insulating layer becomes conductive with the presence of the one or more conductive filaments or paths, and the RRAM cell is at a low resistance state (LR). After the forming process, the RRAM cell is activated as a NVM cell for use. The state "0" is defined when the RRAM is at LR state. To reset or write the RRAM cell to a "1" state (HR), the second electrode of a MIM device (RRAM cell) is biased, connected or coupled to a reset voltage (V.sub.Rset), and the first electrode is biased, connected or coupled to a low operation or ground voltage (V.sub.ss). The reset voltage (V.sub.Rset) will drive or pull oxygen ions out from the oxygen reservoir layer (for example, Ti) and the oxygen ions are hopping or flowing to the oxide or insulating layer. The vacancies in the original oxygen sites are re-occupied by the oxygen ions and the one or more conductive filaments or paths in the oxide or insulting layer are broken or disrupted. The oxide or insulating layer is less-conductive and the RRAM cell is at a high resistance state (HR), and therefore at "1" state. To set or write the RRAM cell to a "0" state (LR), the first electrode of a MIM device (RRAM cell) is biased, connected or coupled to a set voltage (V.sub.Set), and the second electrode is biased, connected or coupled to a low operation or ground voltage (V.sub.ss). The set voltage (V.sub.Set) will drive or pull oxygen atoms or ions from the oxide or insulting layer (for example, HfO.sub.2) to the oxygen reservoir layer (for example, Ti), to form TiO.sub.x. The vacancies in the original oxygen sites in the oxide or insulating layer are created and forming one or more conductive filaments or paths in the oxide or insulting layer. The oxide or insulating layer becomes conductive and the RRAM cell is at the "0" state (LR).

[0023] Based on the conductive filament theory, the resistance of a MIM is at low resistance state (LR), the "0" state, when the set voltage is biased, connected or coupled to the first electrode; while the resistance of a MIM is at high resistance state (HR), the "1" state, when the reset voltage is biased, connected or coupled to the second electrode. The two states of resistance may be used in read the MIM RRAM cell.

[0024] Another aspect of the disclosure provides a RRAM cell in the standard commodity FPGA IC chip, comprising two complementary MIMs (Two single-RRAM cells as described and specified) for use in the FPGA IC chip for programmable interconnection and/or for data storage of the LUTs. This type of RRAM cell may be named as a Complementary RRAM cell, abbreviated as CRRAM. The two MIMs each is formed by stacks comprising first electrode/oxygen reservoir/oxide/second electrode layers, from top to the bottom as the FPGA IC chips are facing up (with transistors and the metal interconnection structures on or over the silicon substrate). A first (top) electrode of the First MIM (F-MIM) may be connected or coupled to a first (top) electrode of that of the Second MIM (S-MIM). Alternatively, a second (bottom) electrode of the First MIM (F-MIM) may be connected or coupled to a second (bottom) electrode of that of the Second MIM (S-MIM). In other alternative, the two MIMs each is formed by stacks comprising second electrode/oxide/oxygen reservoir/first electrode layers, from top to the bottom as the FPGA IC chips are facing up (with transistors and the metal interconnection structures on or over the silicon substrate). A first (bottom) electrode of the First MIM (F-MIM) may be connected or coupled to a first (bottom) electrode of that of the Second MIM (S-MIM). Alternatively, a second (top) electrode of the First MIM (F-MIM) may be connected or coupled to a second (top) electrode of that of the Second MIM (S-MIM). The node or terminal connected or coupled to the first electrode is the node F of a MIM, and the node or terminal connected or coupled to the second electrode is the node S of the MINI. The CRRAM may be programmed or written for the F-MIM and the S-MIM as described above for a single MIM. The F-MIM and S-MIM in the CRRAM (a type of RRAM cell) cell are in anti-polarity, that is when F-MIM is at the HR state, the S-MIM is at LR state, and when F-MIM is at the LR state, the S-MIM is at the HR state. For example, in a case if the connected node is the connected or coupled electrodes of the first electrodes (F nodes) for the F-MIM and the S-MIM, the CRRAM cell may be written "0", by connecting the S node of the F-MIM to a programming voltage (V.sub.P) and the S node of the S-MIM to V.sub.ss, the S-MIM is programmed at the LR state, and the F-MIM is programmed at the HR state. The CRRAM is at the [1,0] state, defined as the "0" state of the CRRAM. The CRRAM cell may be programmed or written "1", by connecting the S node of the S-MIM to the programming voltage (V.sub.P) and the S node of the F-MIM to V.sub.ss, the S-MIM is programmed at the HR state, and the F-MIM is programmed at the LR state. That is the CRRAM is at the [0,1] state, defined as the "1" state of the CRRAM.

[0025] Another aspect of the disclosure provides a RRAM cell, comprising a CRRAM, a latched circuit and a set/set-bar circuit for use in the standard commodity FPGA IC chip for programmable interconnection and/or for data storage of the LUTs. This type of RRAM cell may be named as a Latched RRAM cell, abbreviated as LRRAM. As an example, the latched circuit comprising two inverters as in the latched 4T circuit of the 6T SRAM cell. A drain of the P-MOS of a first inverter in the 4T latched circuit is connected or coupled to the S node of the F-MIM, and a drain of the N-MOS of the first inverter is connected or coupled to the S node of the S-MIM. The Bit-bar node of the 4T latched circuit is connected or coupled to (i) the connected or coupled node (the connected or coupled F nodes of the F-MIM and the S-MIM) of the CRRAM cell; (ii) the connected gates of P-MOS and N-MOS in a second inverter of the 4T latched circuit. The another latched node, the Bit node, of the 4T latched circuit is connected or coupled to (i) the connected drains of P-MOS and N-MOS in the second inverter of the 4T latched circuit; (ii) the connected gates of P-MOS and N-MOS in the first inverter of the 4T latched circuit. A Set-bar P-MOS transistor is connected to the S node of the F-MIM, and a Set N-MOS transistor is connected to the S node of the S-MIM. In the programming or write process, the gate of the Set-bar P-MOS is connected or coupled to a low operation or ground voltage (V.sub.ss), and the gate of the Set N-MOS is connected or coupled to a high operation voltage (V.sub.cc), with the common sources of P-MOS's and N-MOS's in the 4T latched circuit disconnected. When the source of the Set-Bar P-MOS is connected or coupled to the programming voltage (V.sub.P), and the source of the Set N-MOS is connected or coupled to the low operation or ground voltage (V.sub.ss), F-MIM is at the HR state, and the S-MIM is at the LR state, the Bit-bar is at "0", and the Bit node is at "1". When the source of the Set-bar P-MOS is connected or coupled to the low operation or ground voltage (V.sub.ss), and the source of the Set N-MOS is connected or coupled to the programming voltage (V.sub.P), F-MIM is at the LR state, and the S-MIM is at the HR state, the Bit-bar is at "1", and the Bit node is at "0".

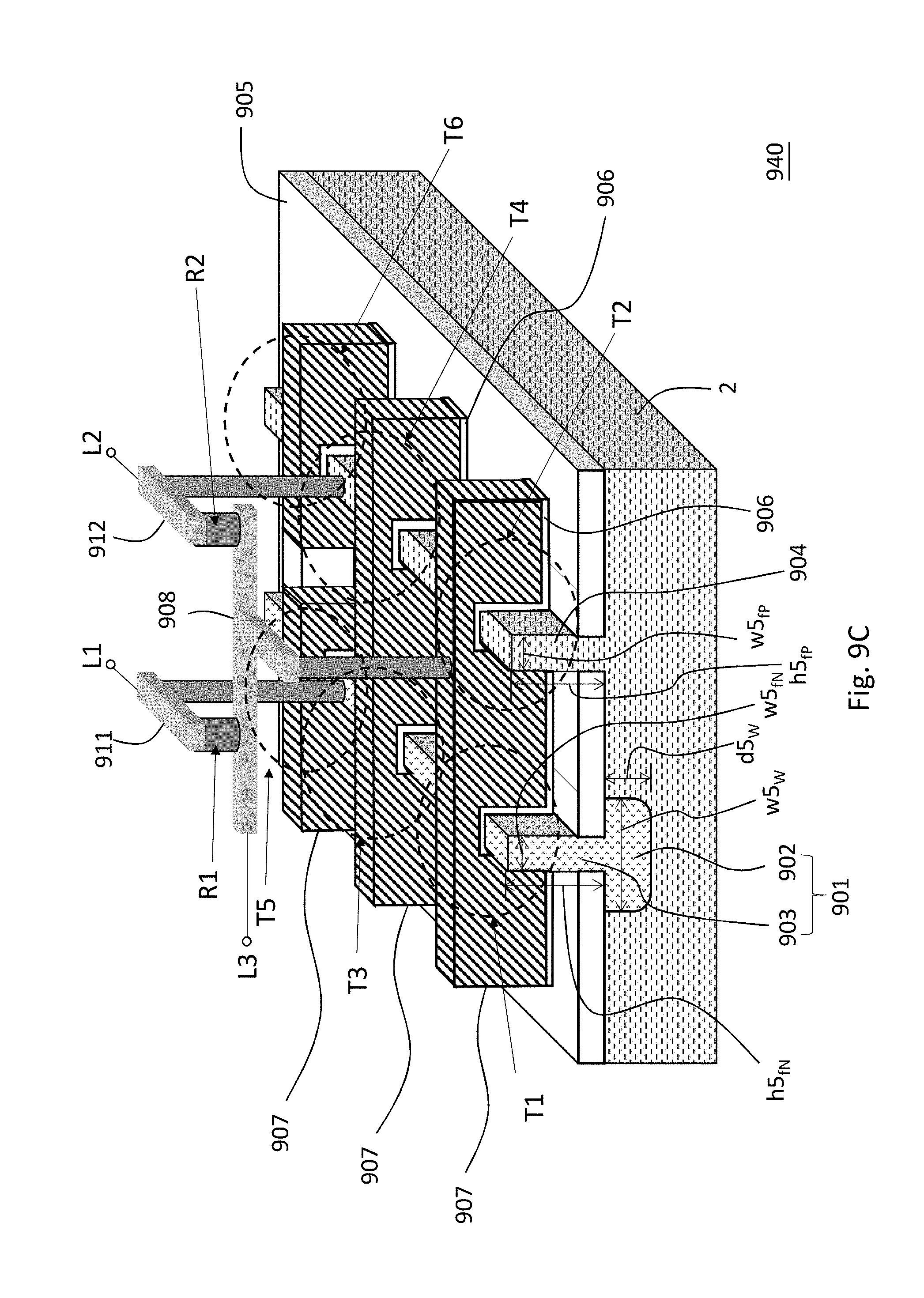

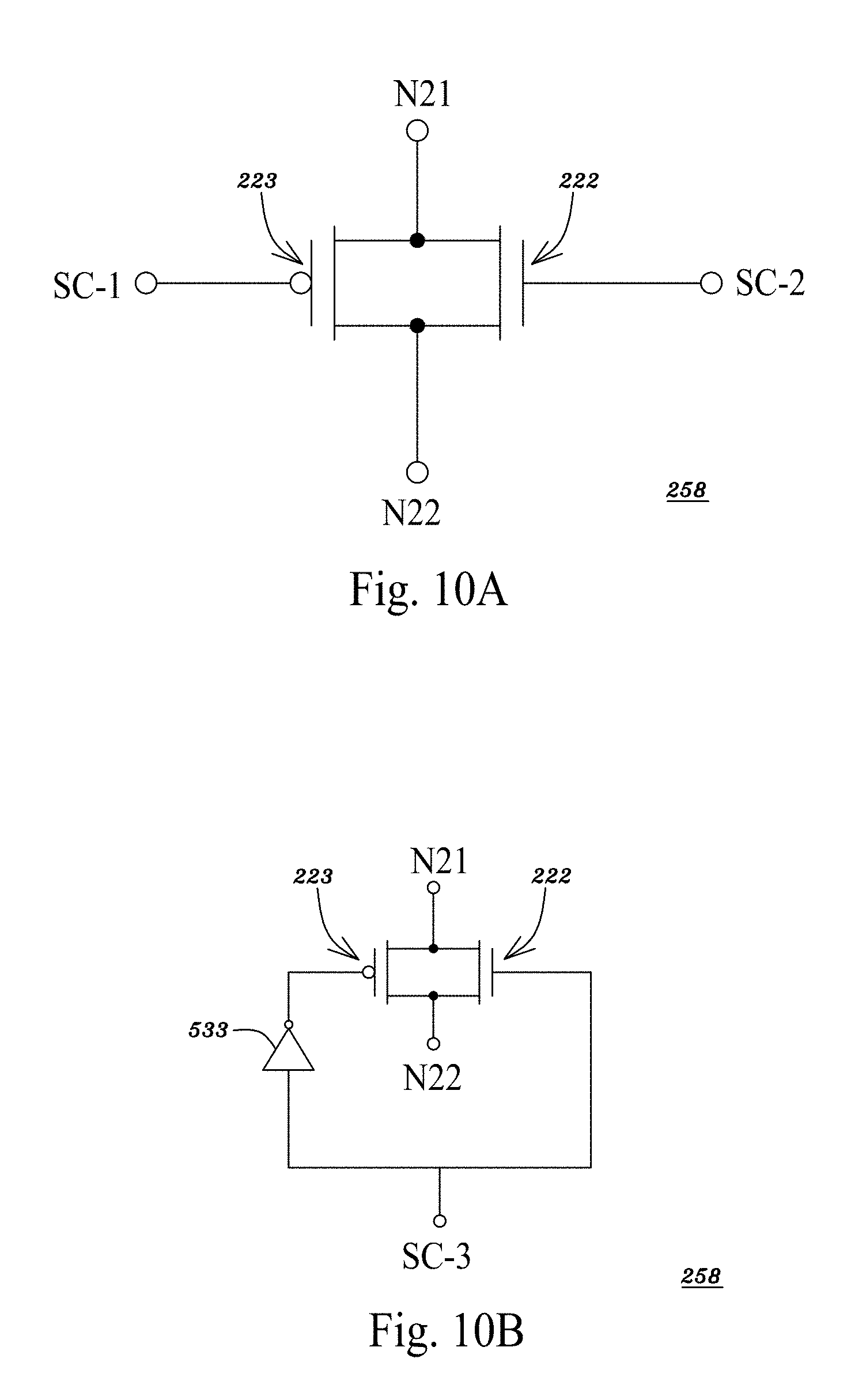

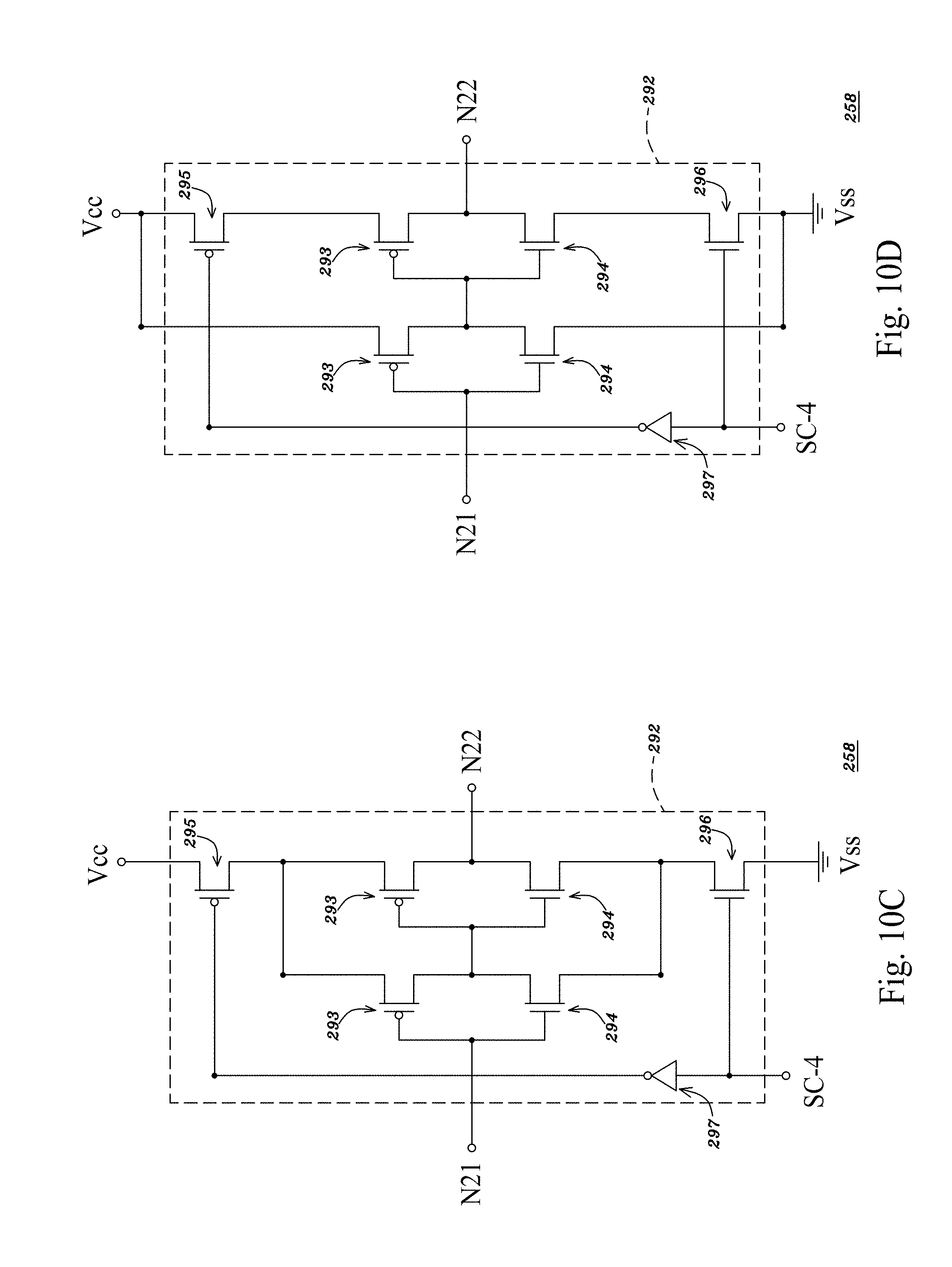

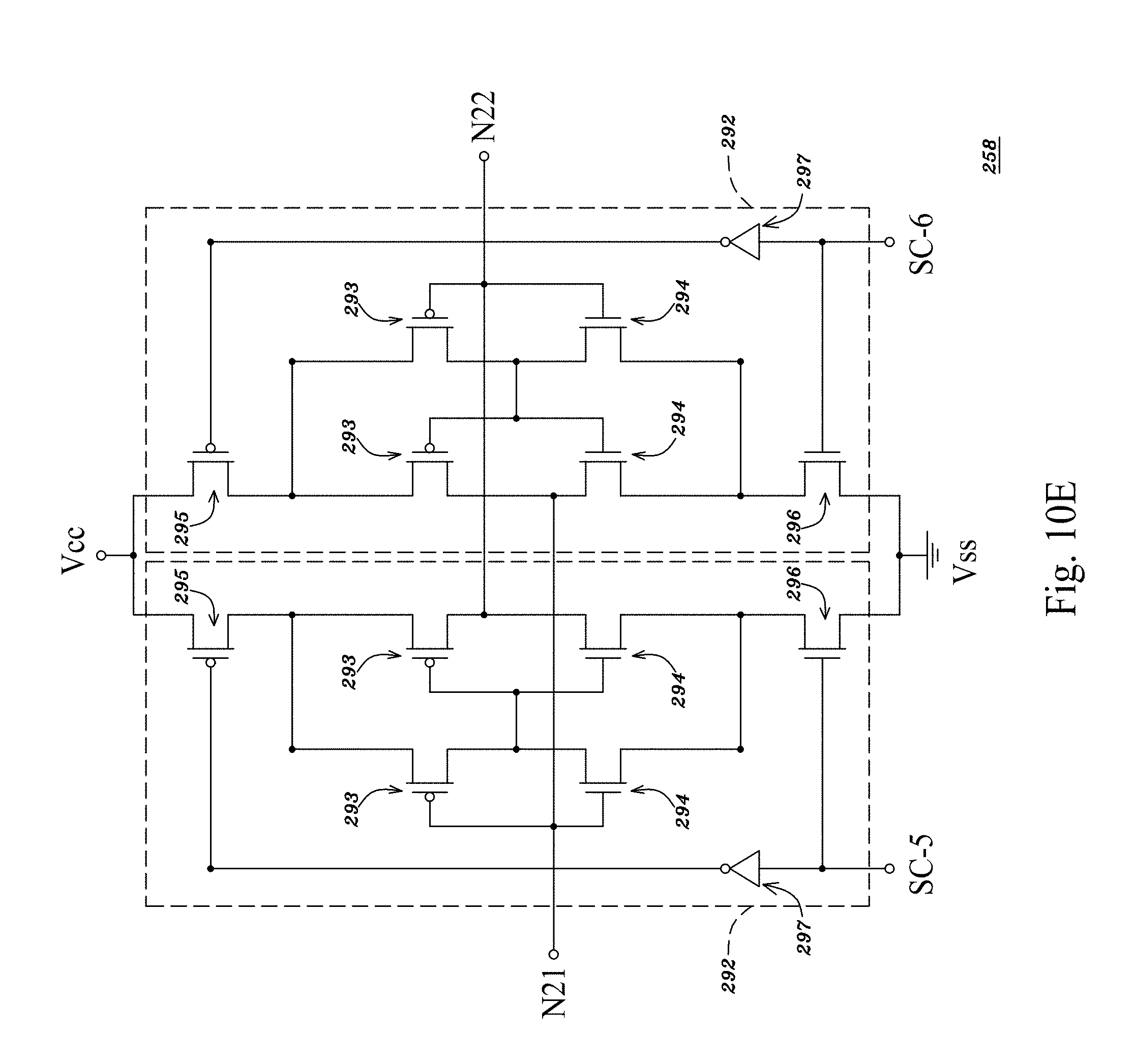

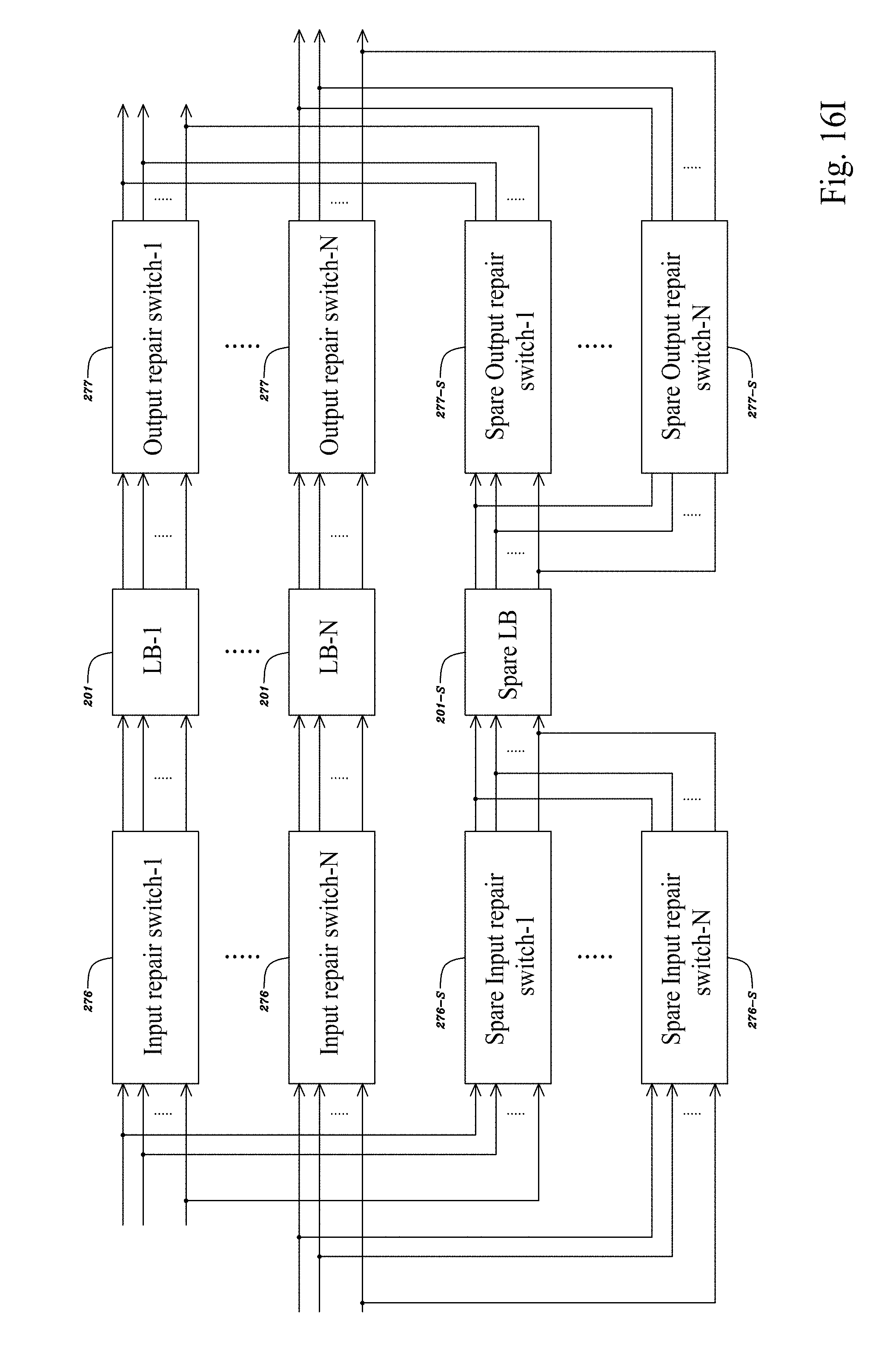

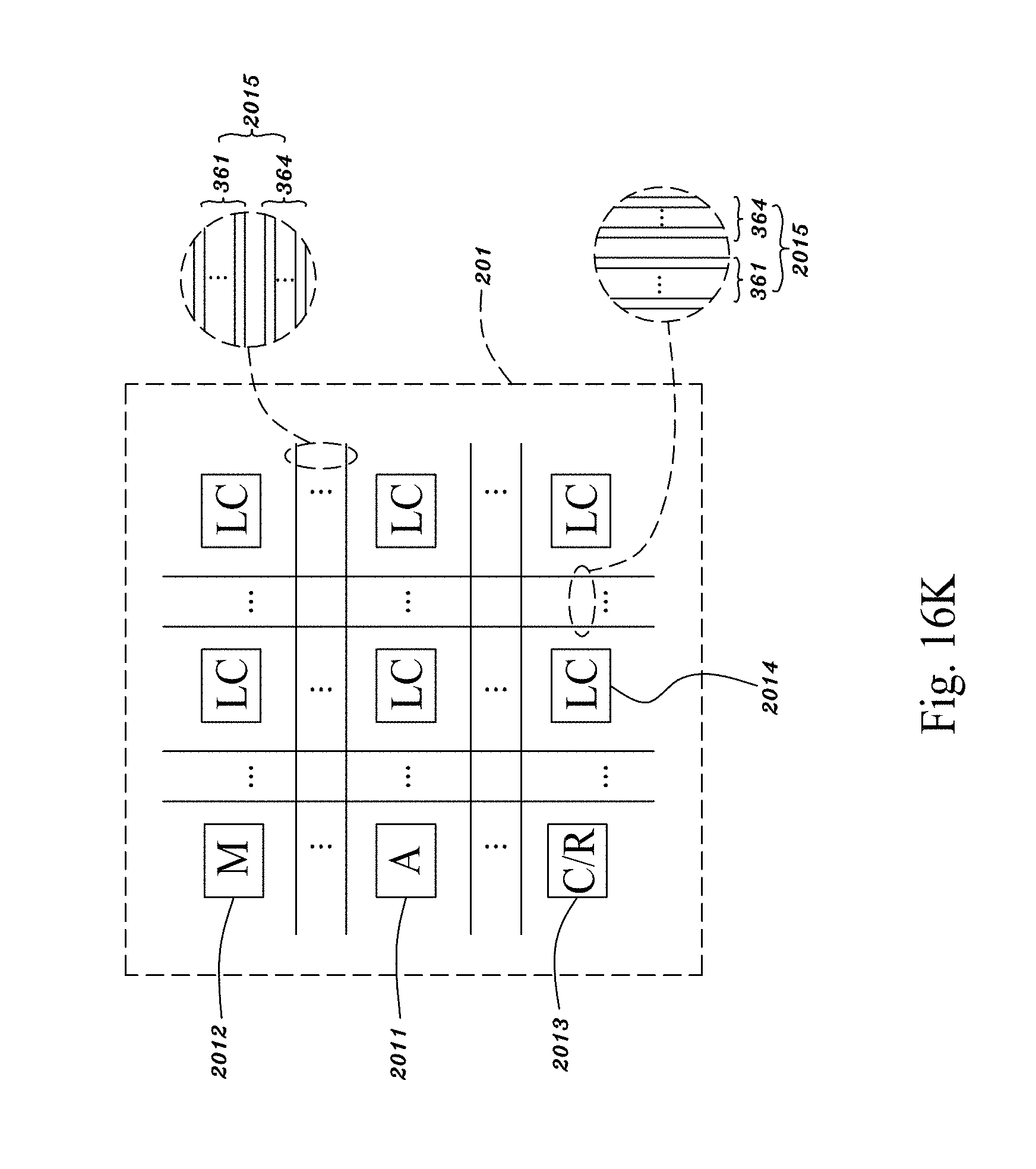

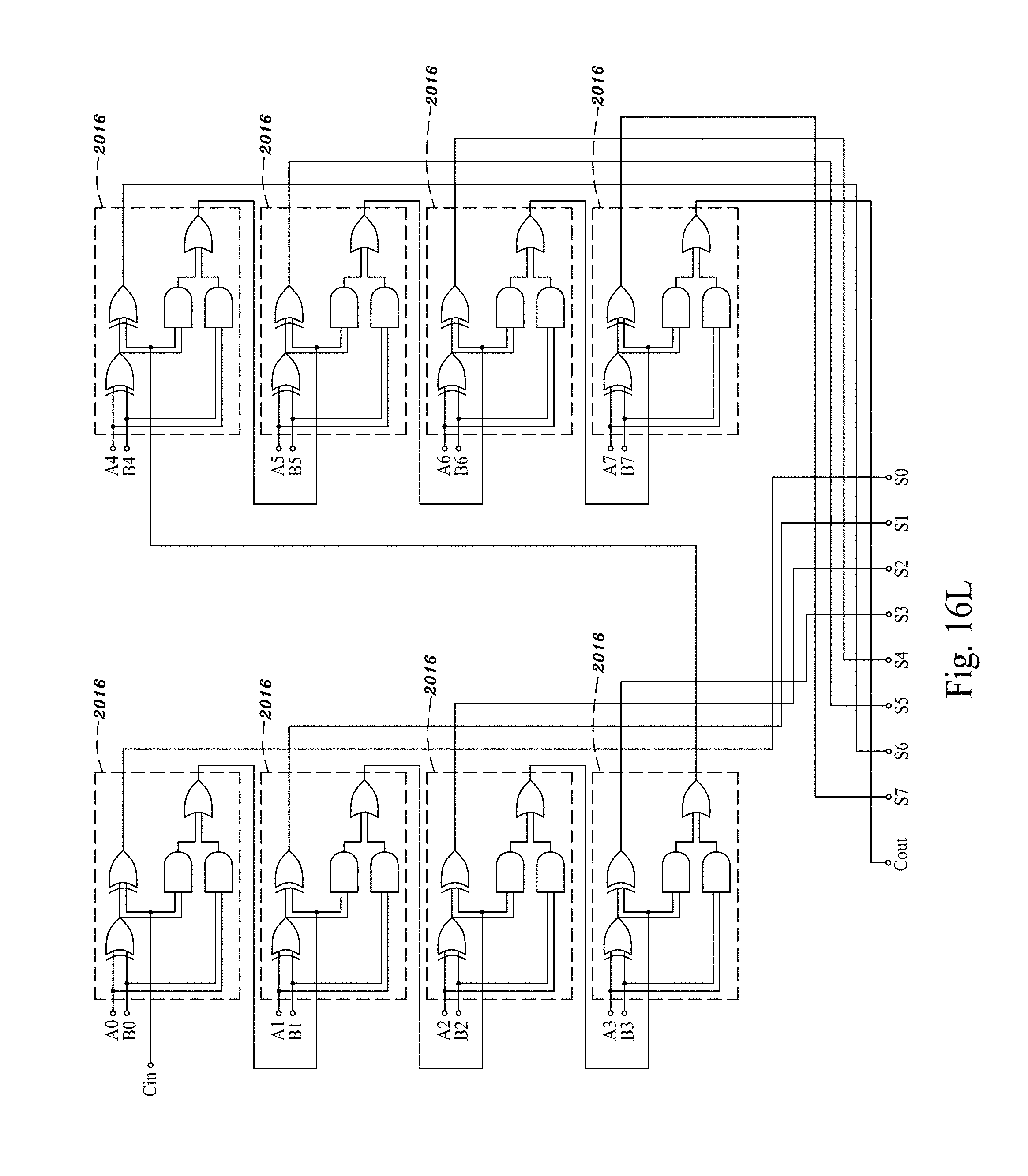

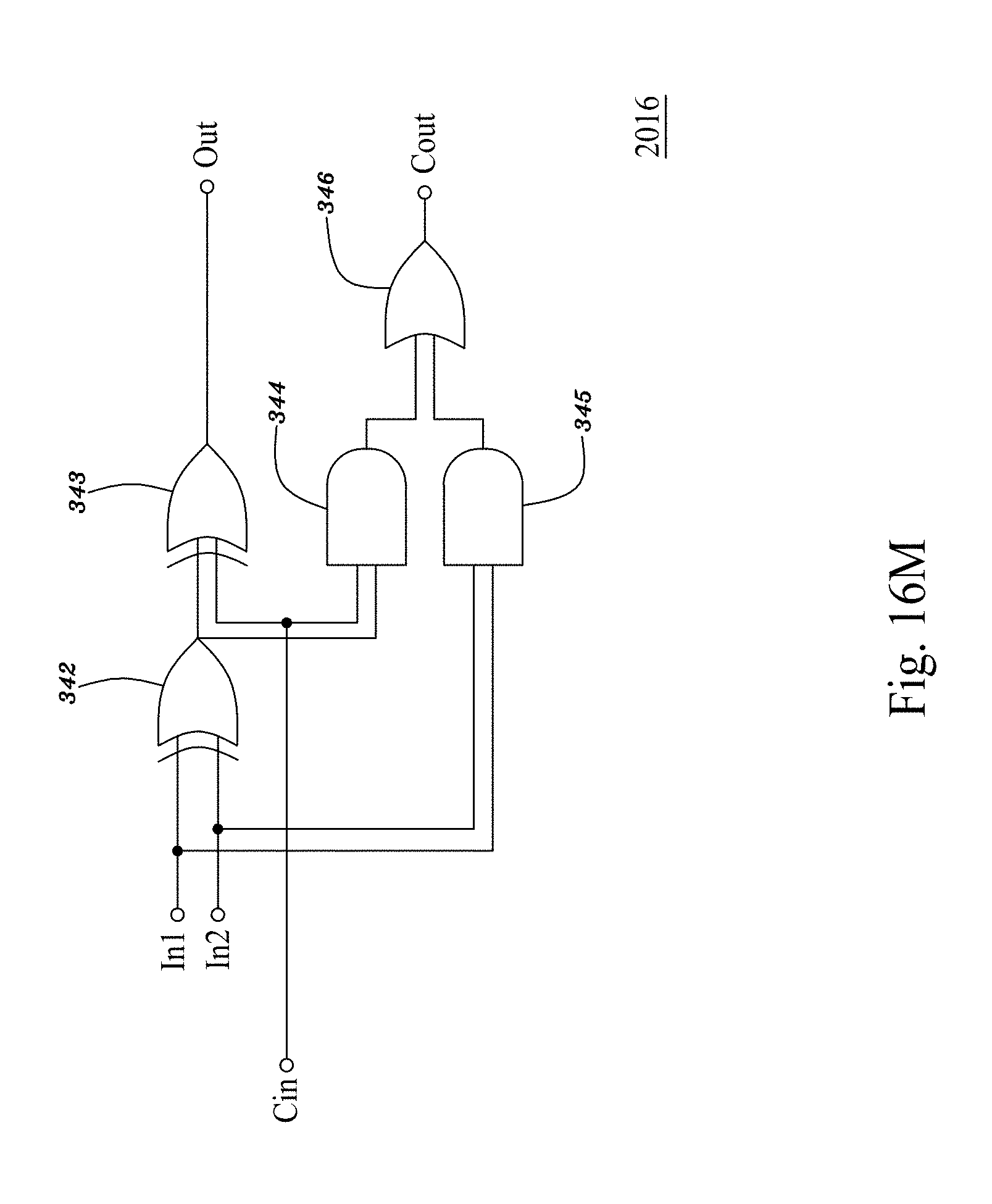

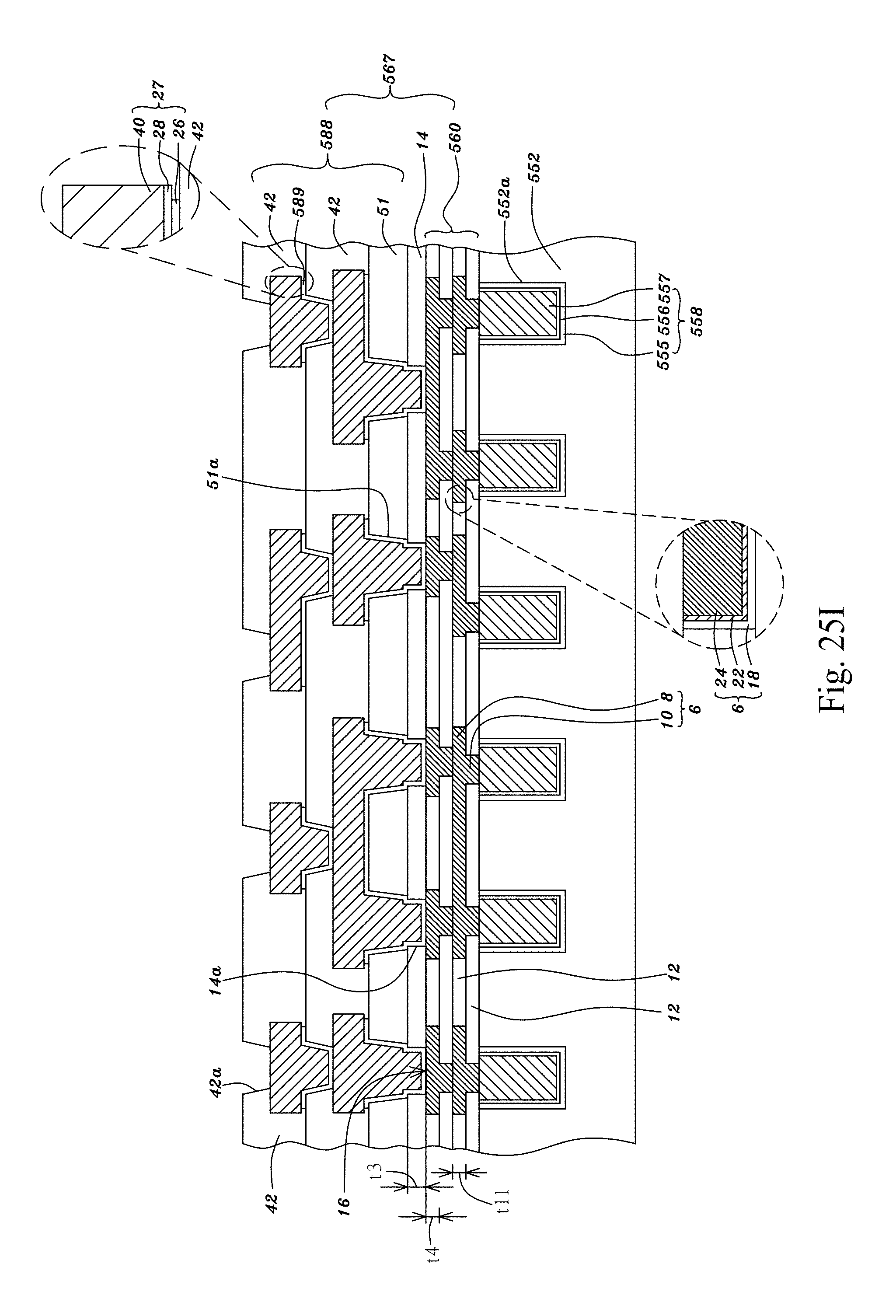

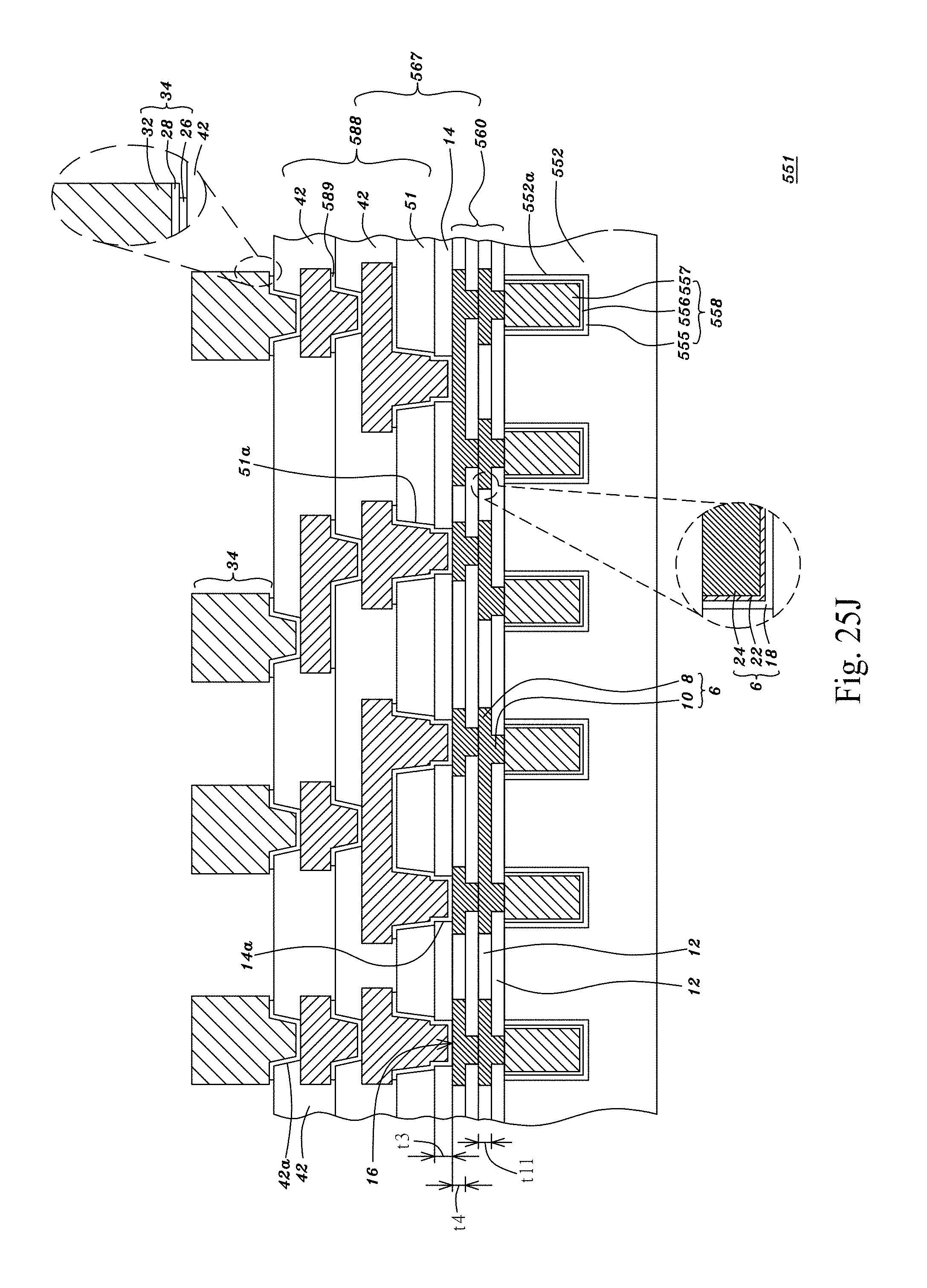

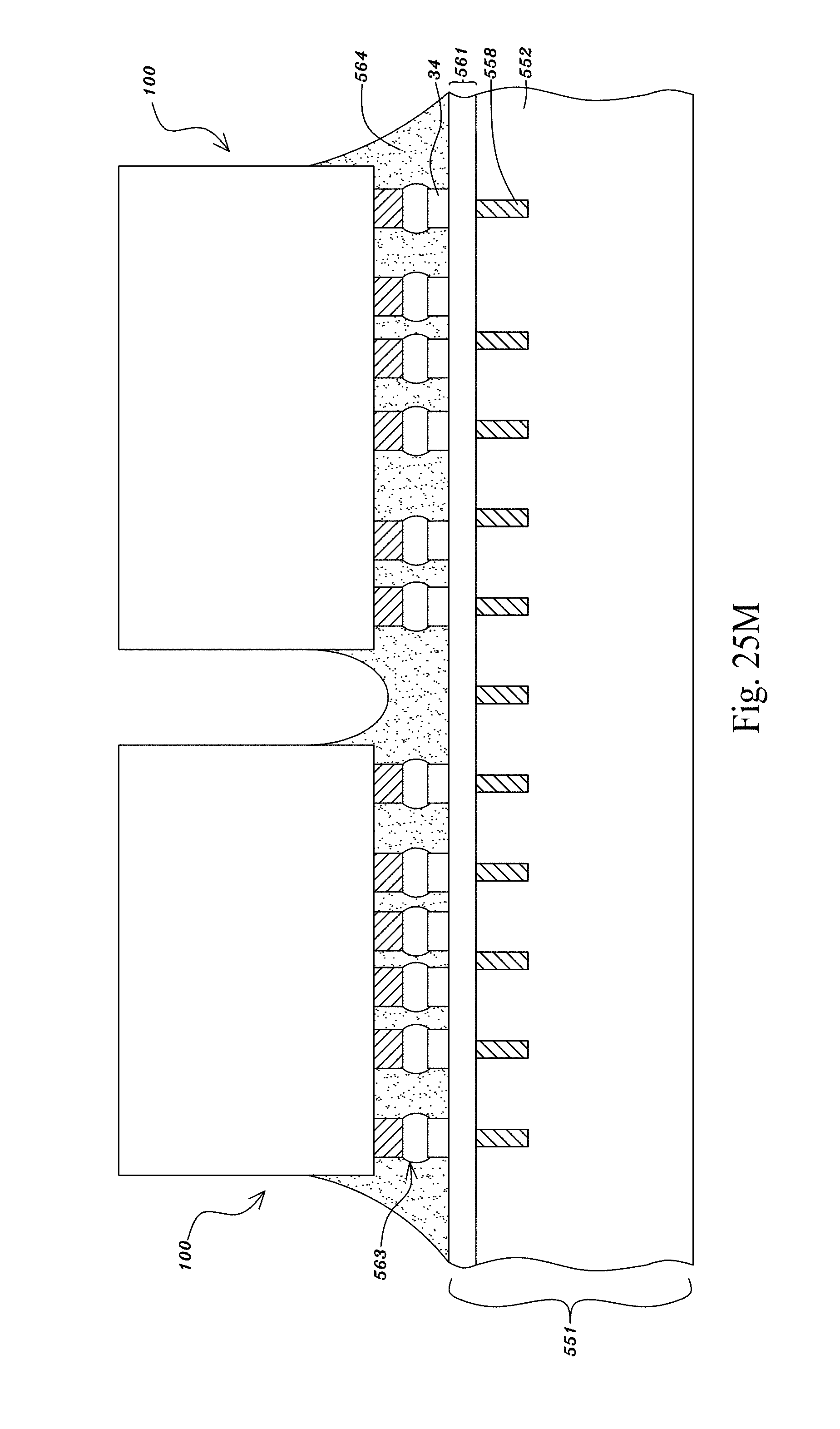

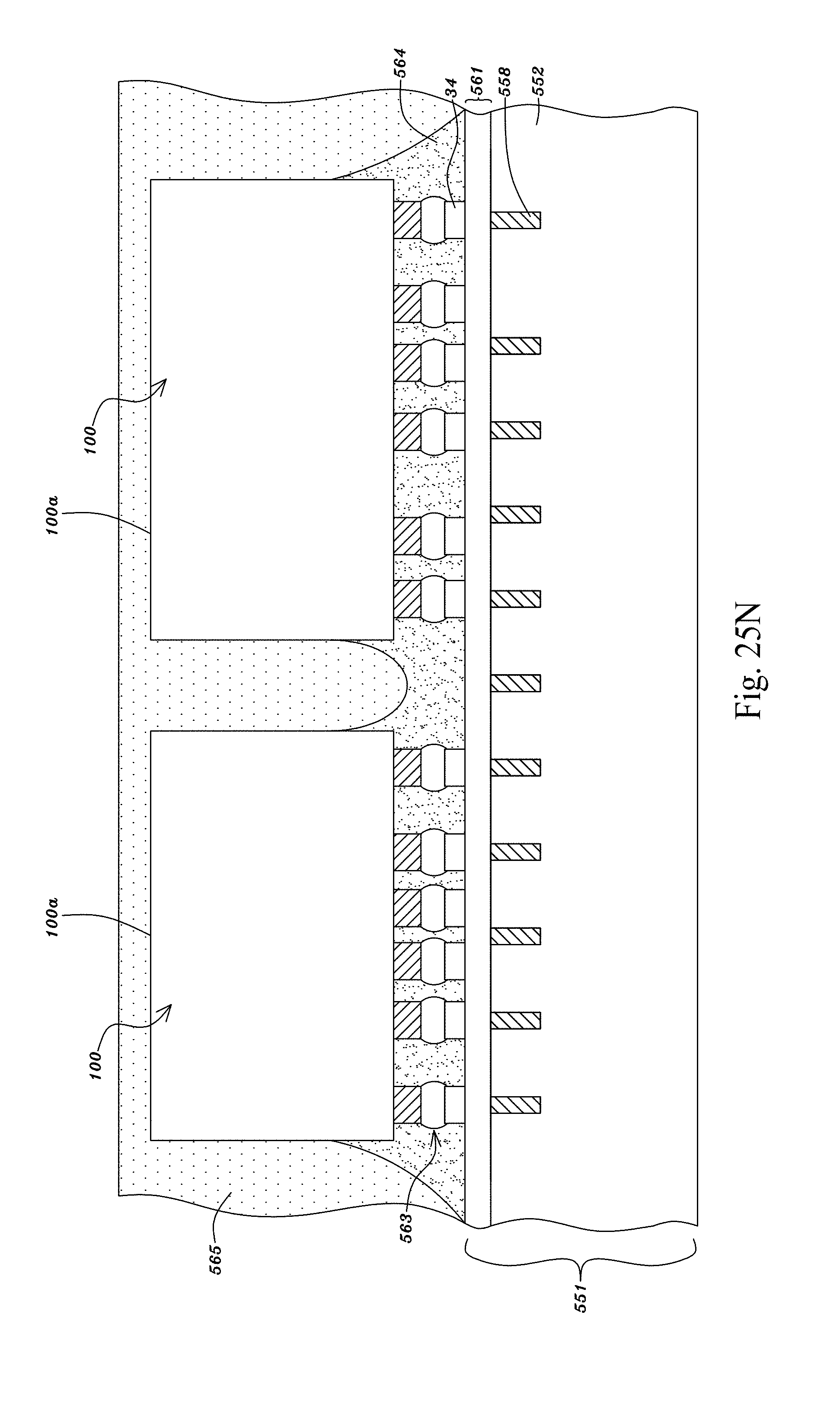

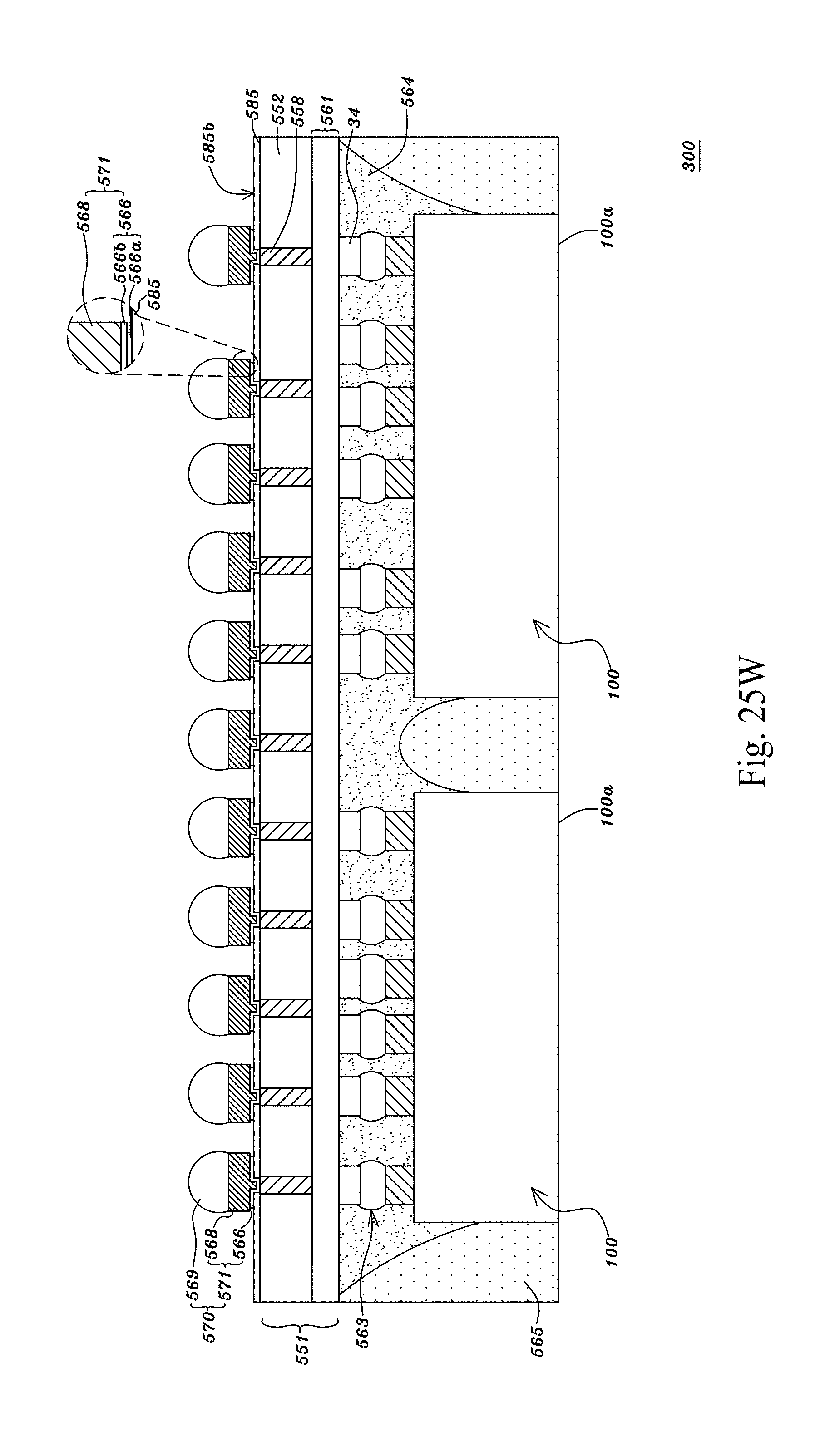

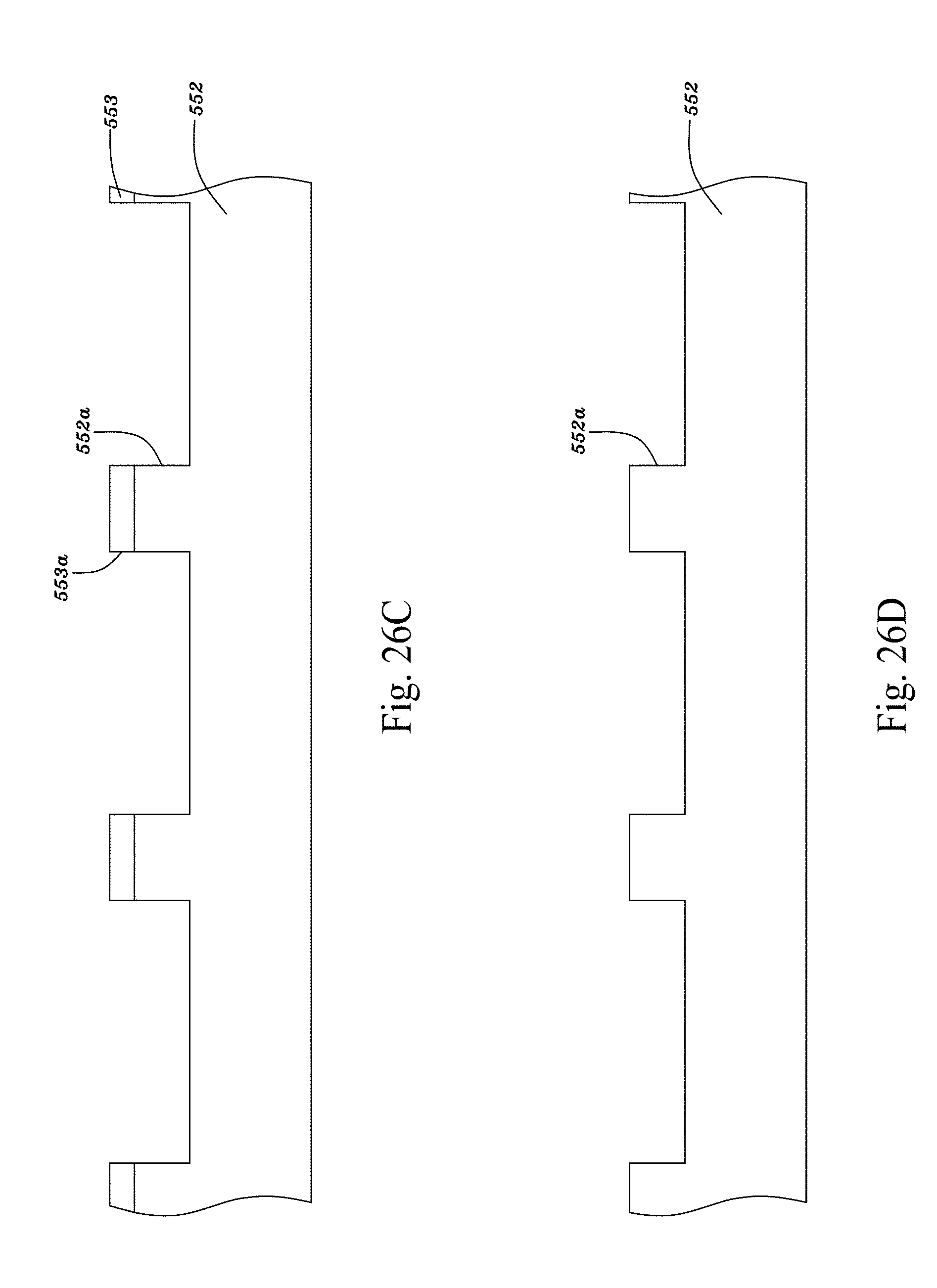

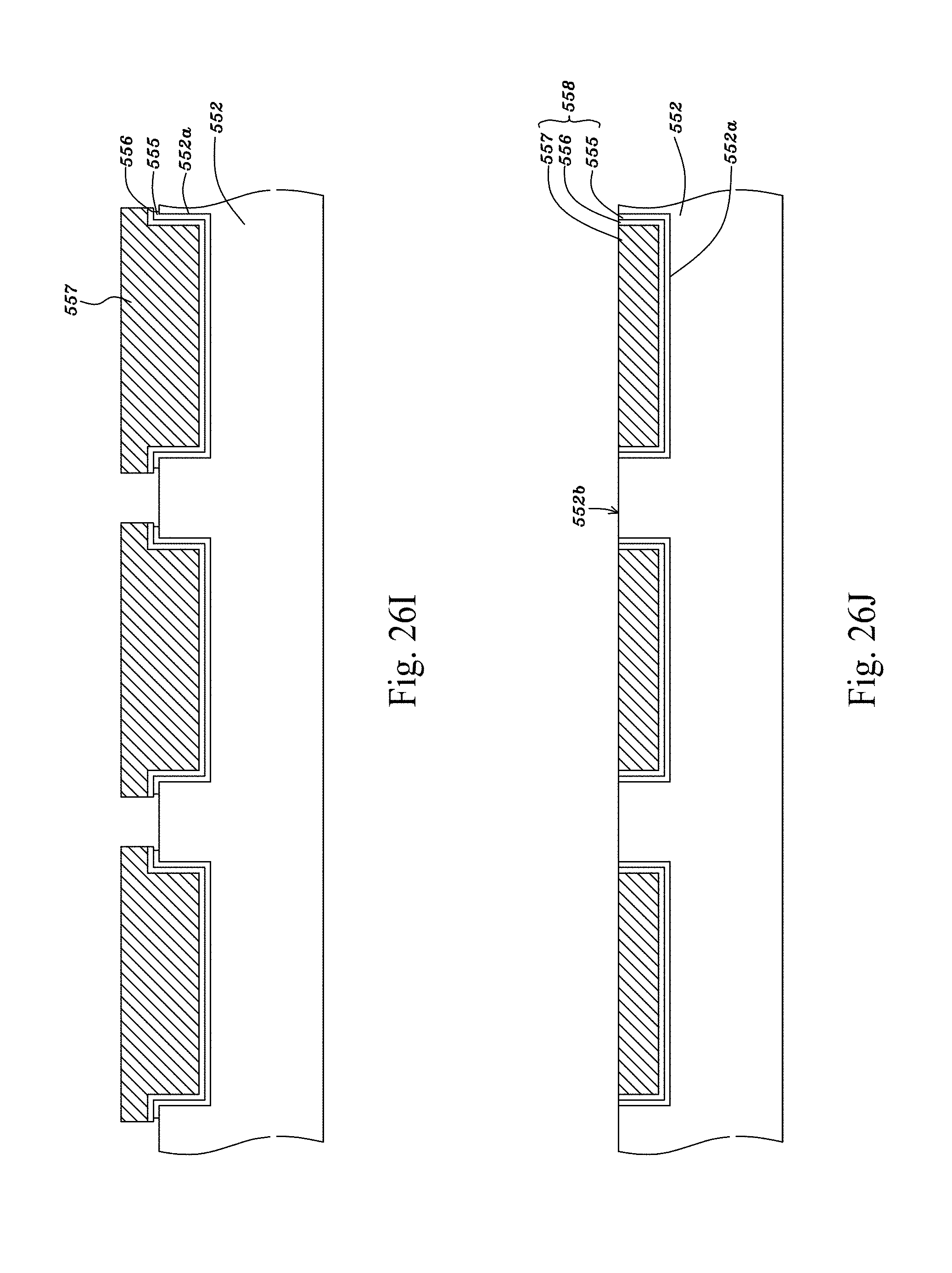

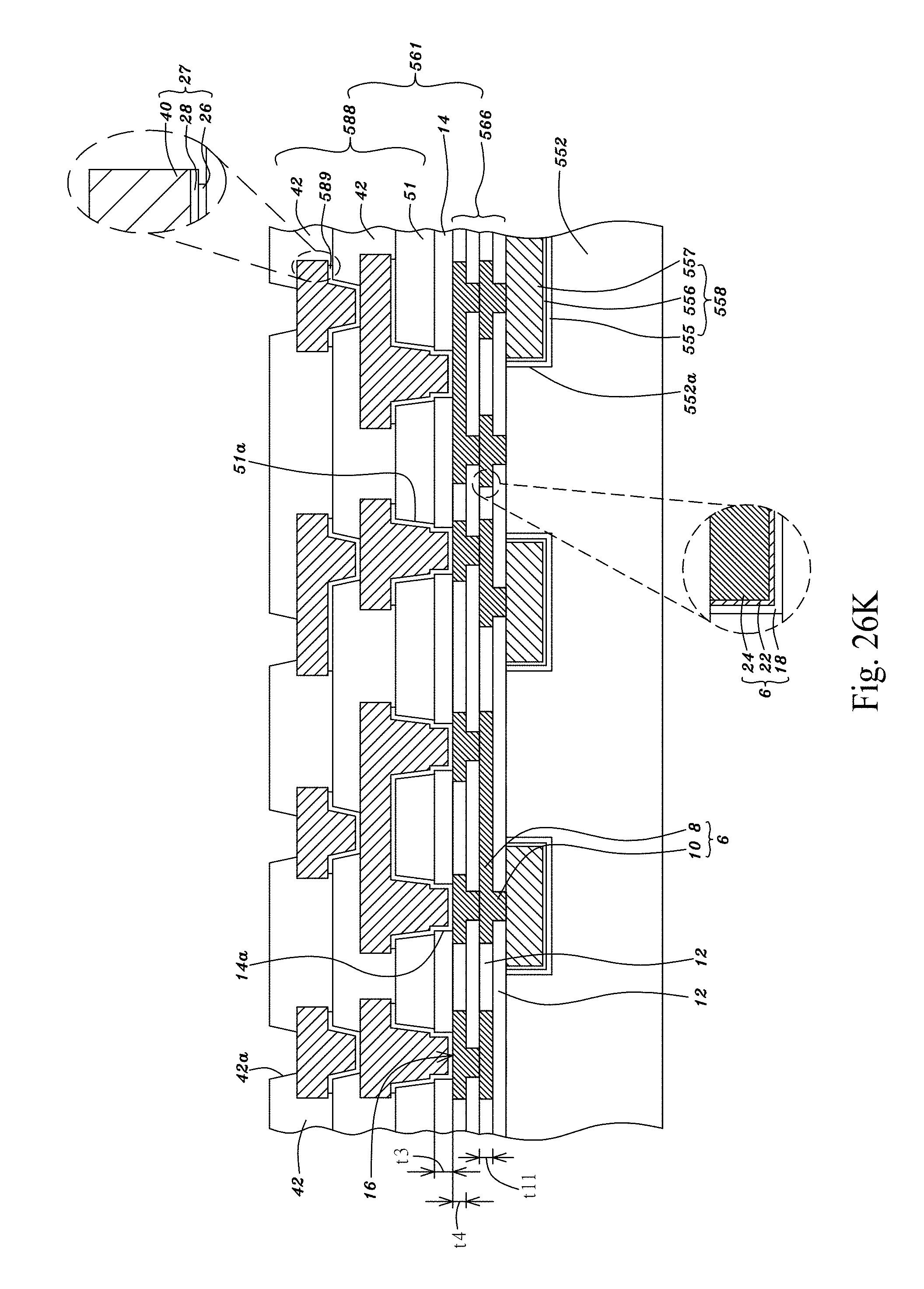

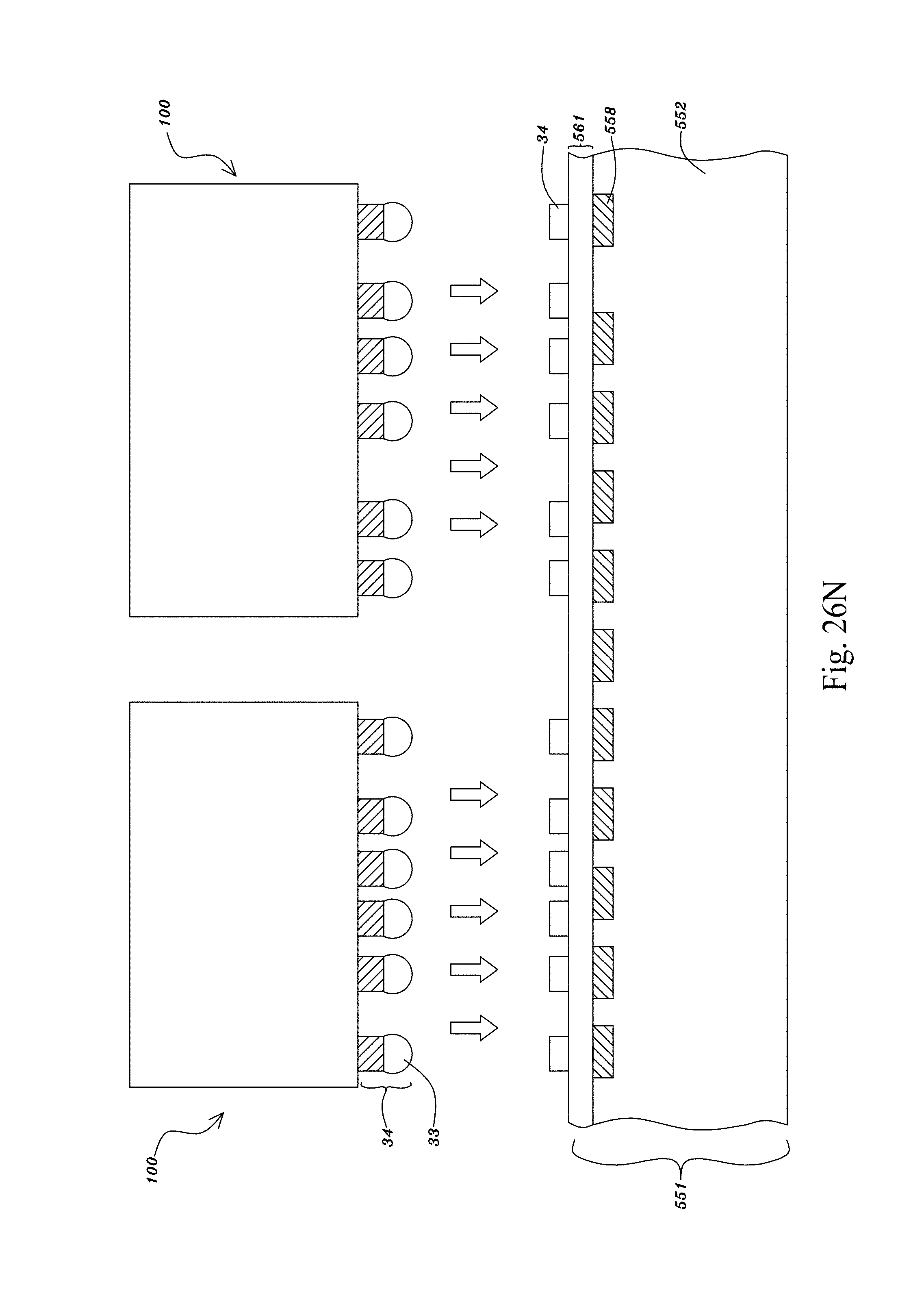

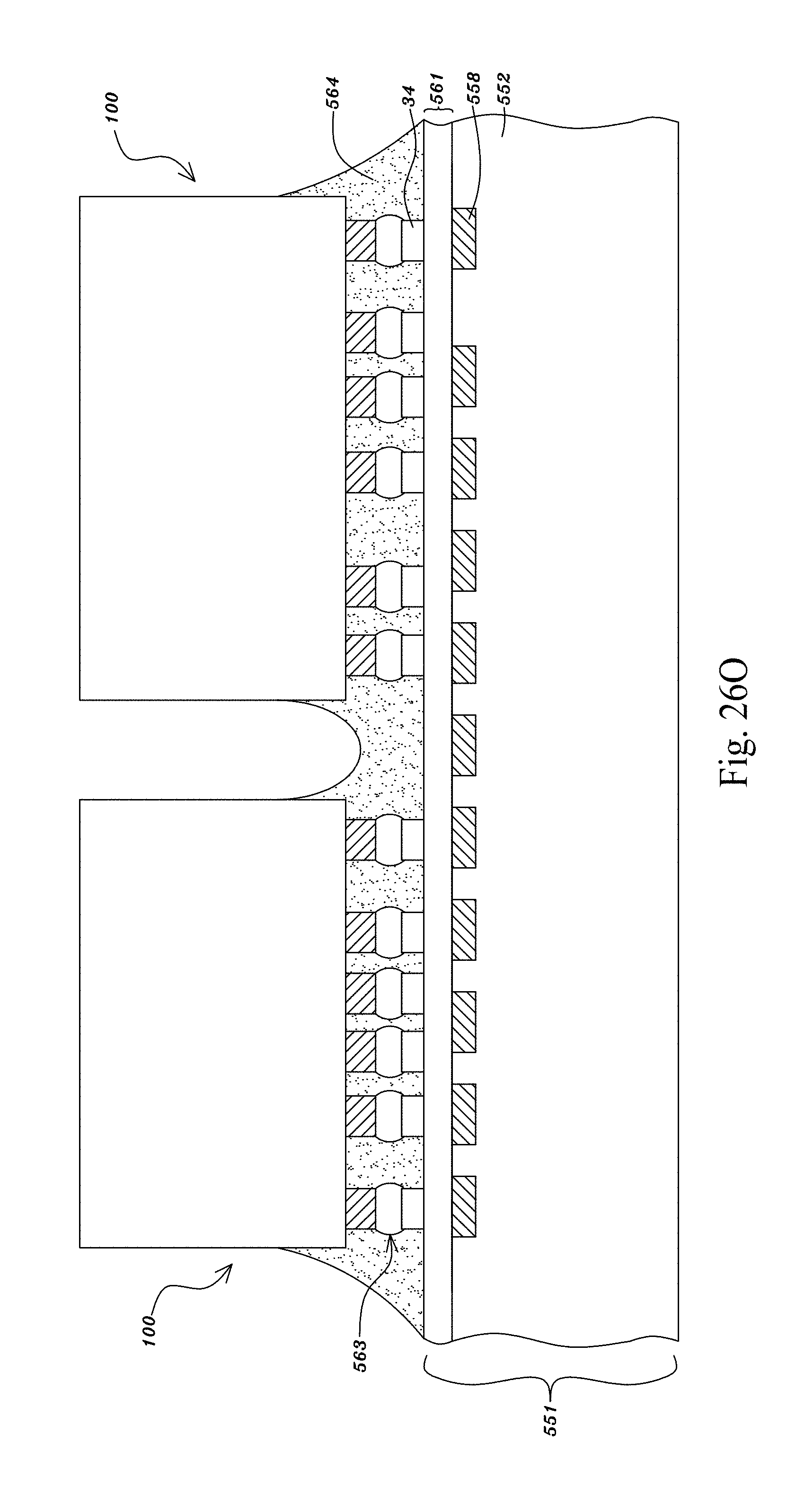

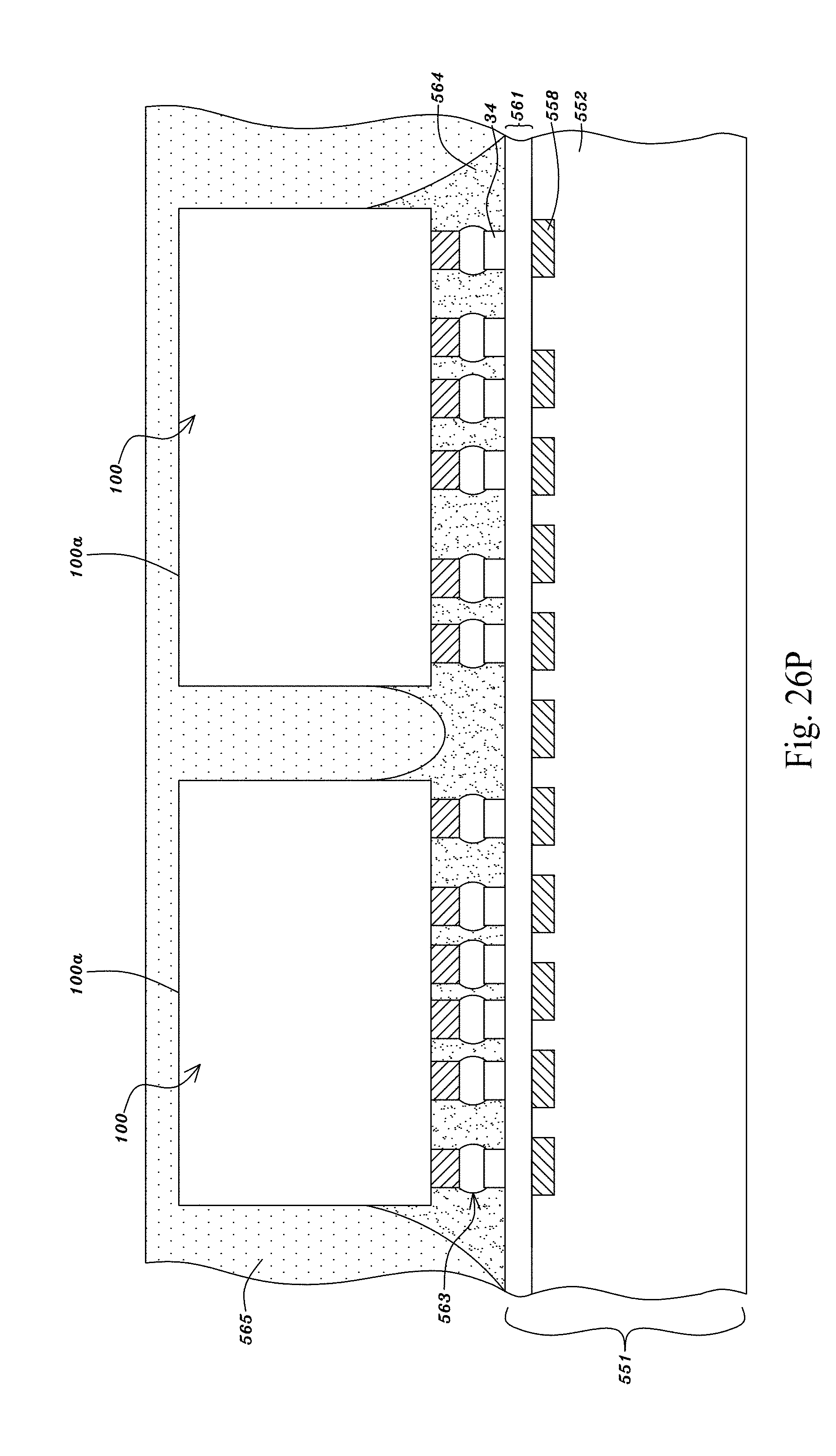

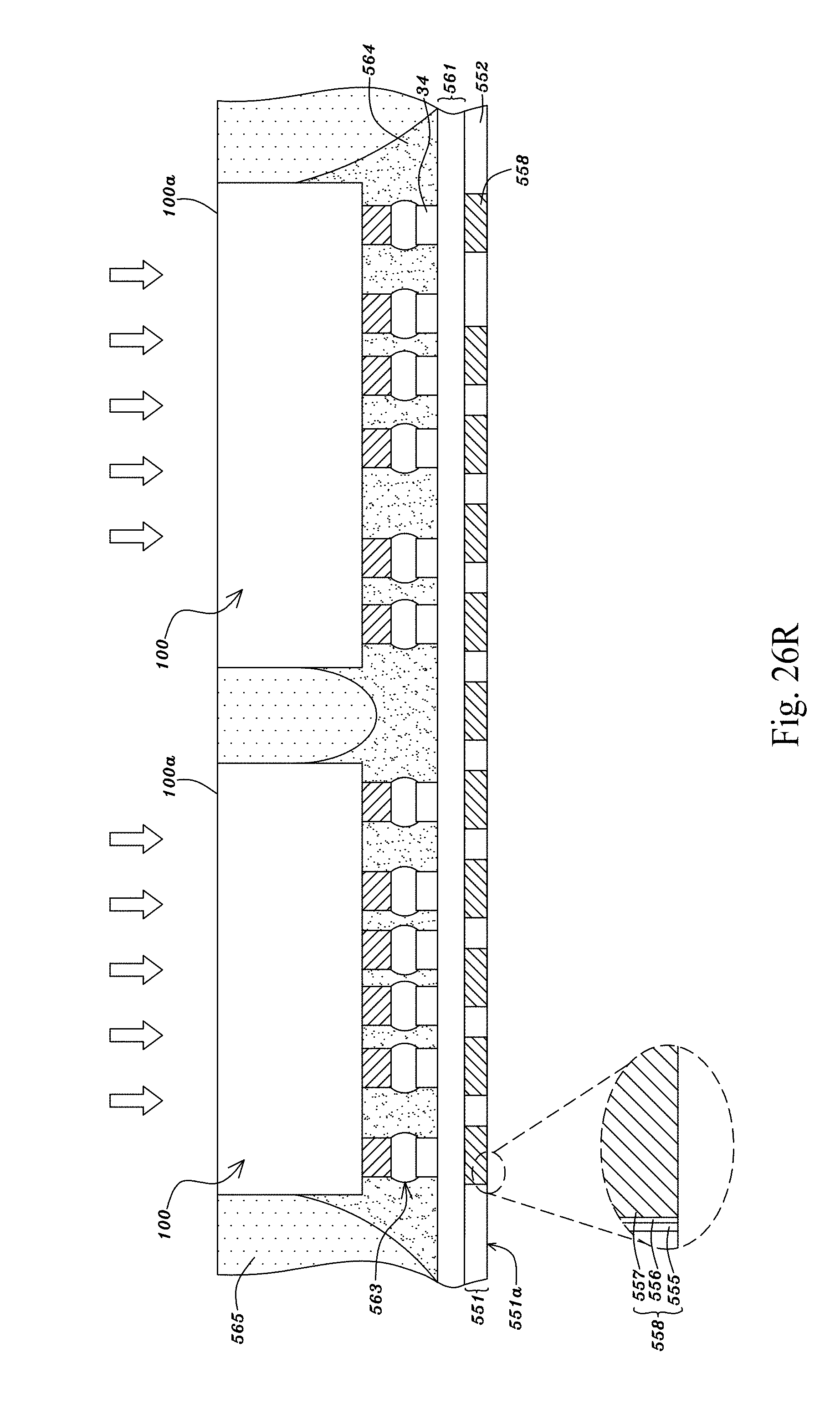

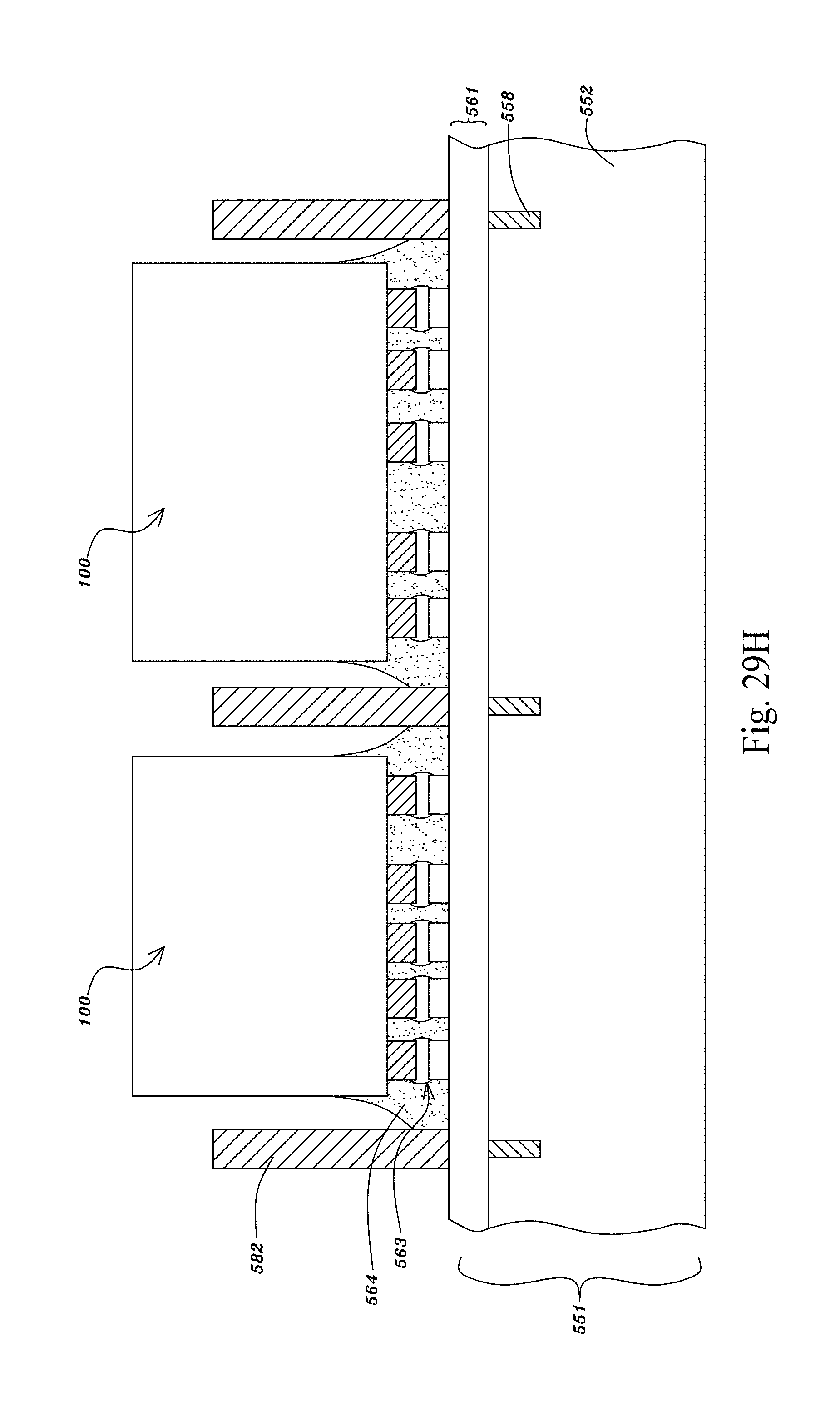

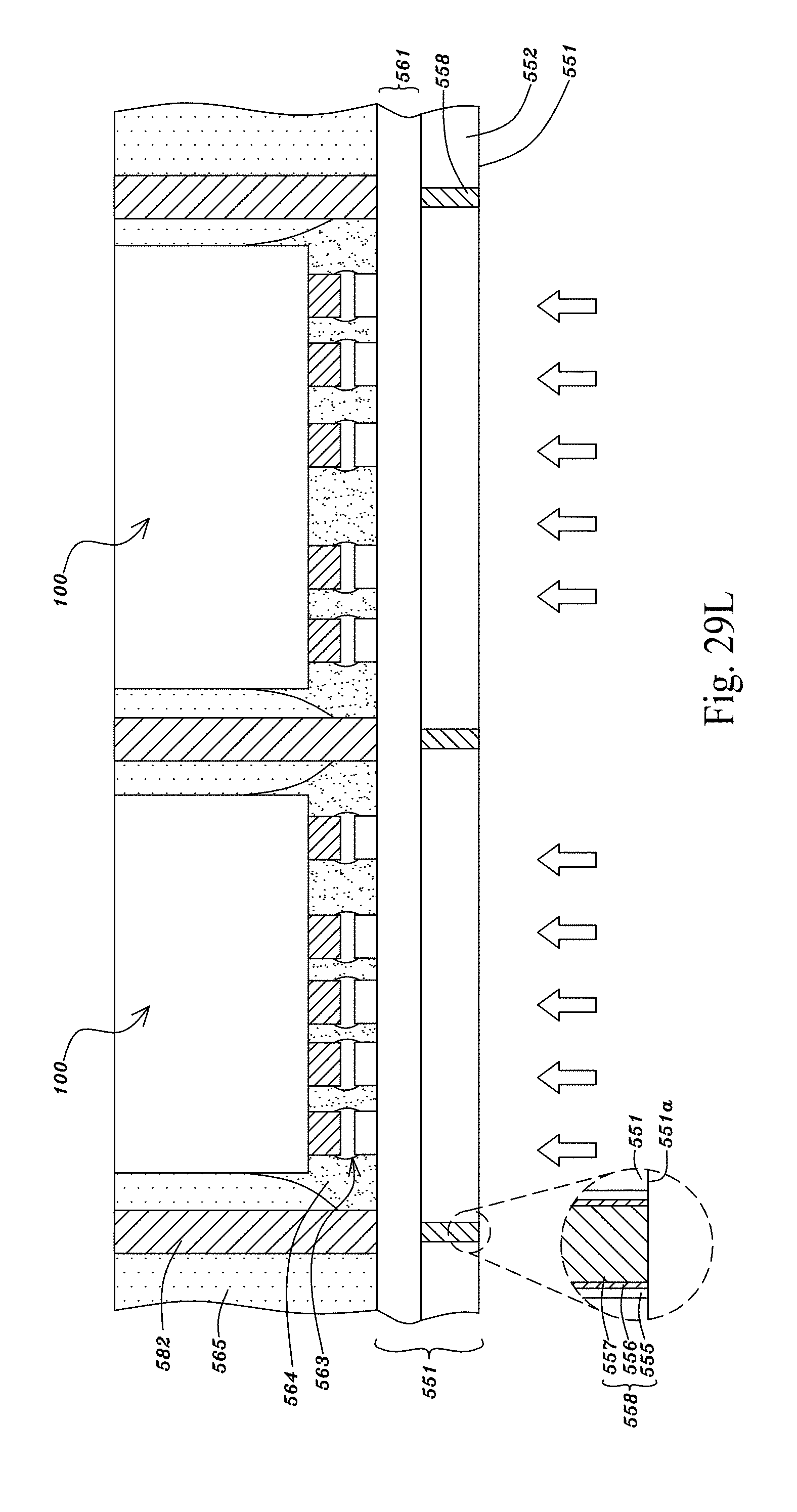

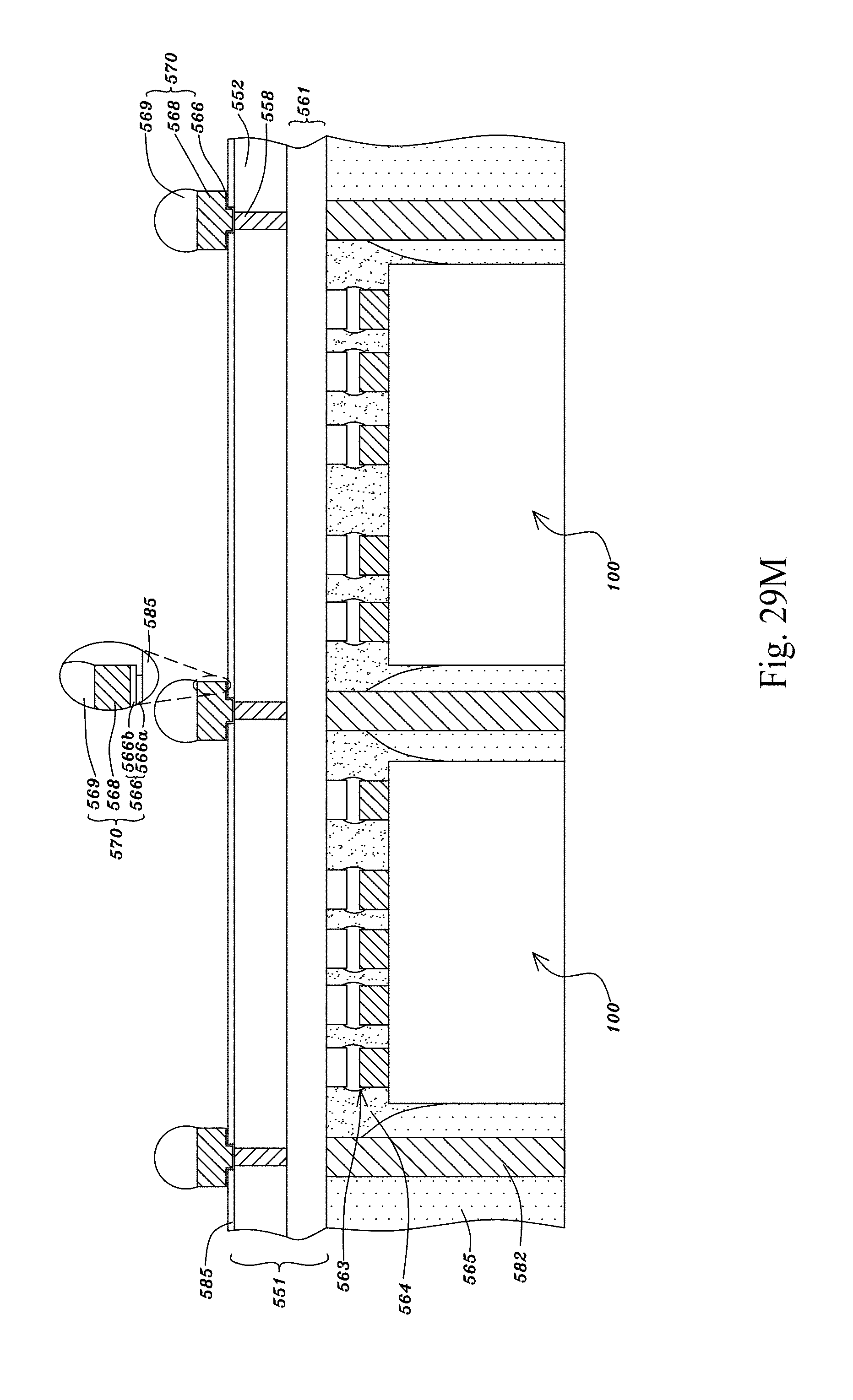

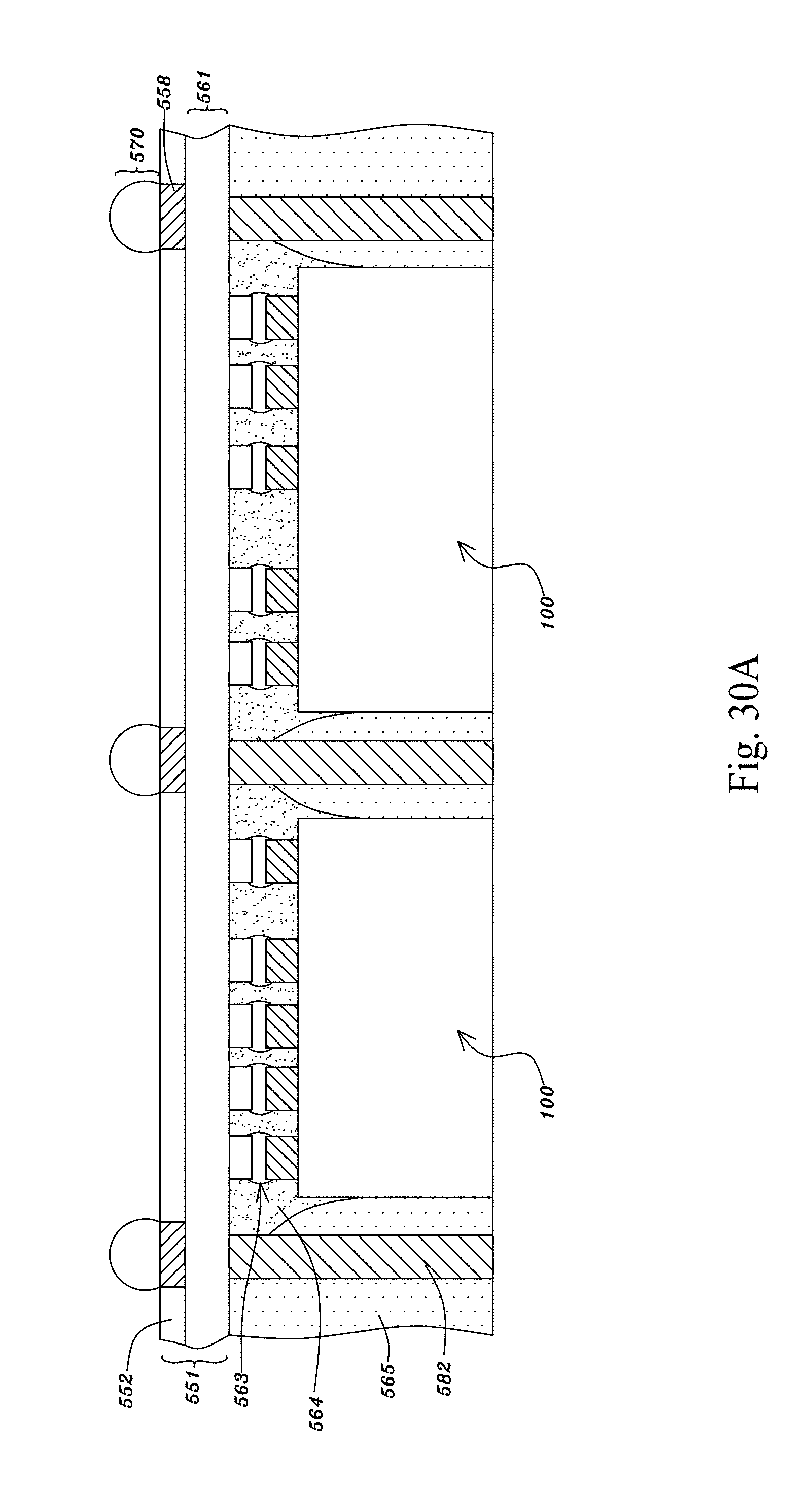

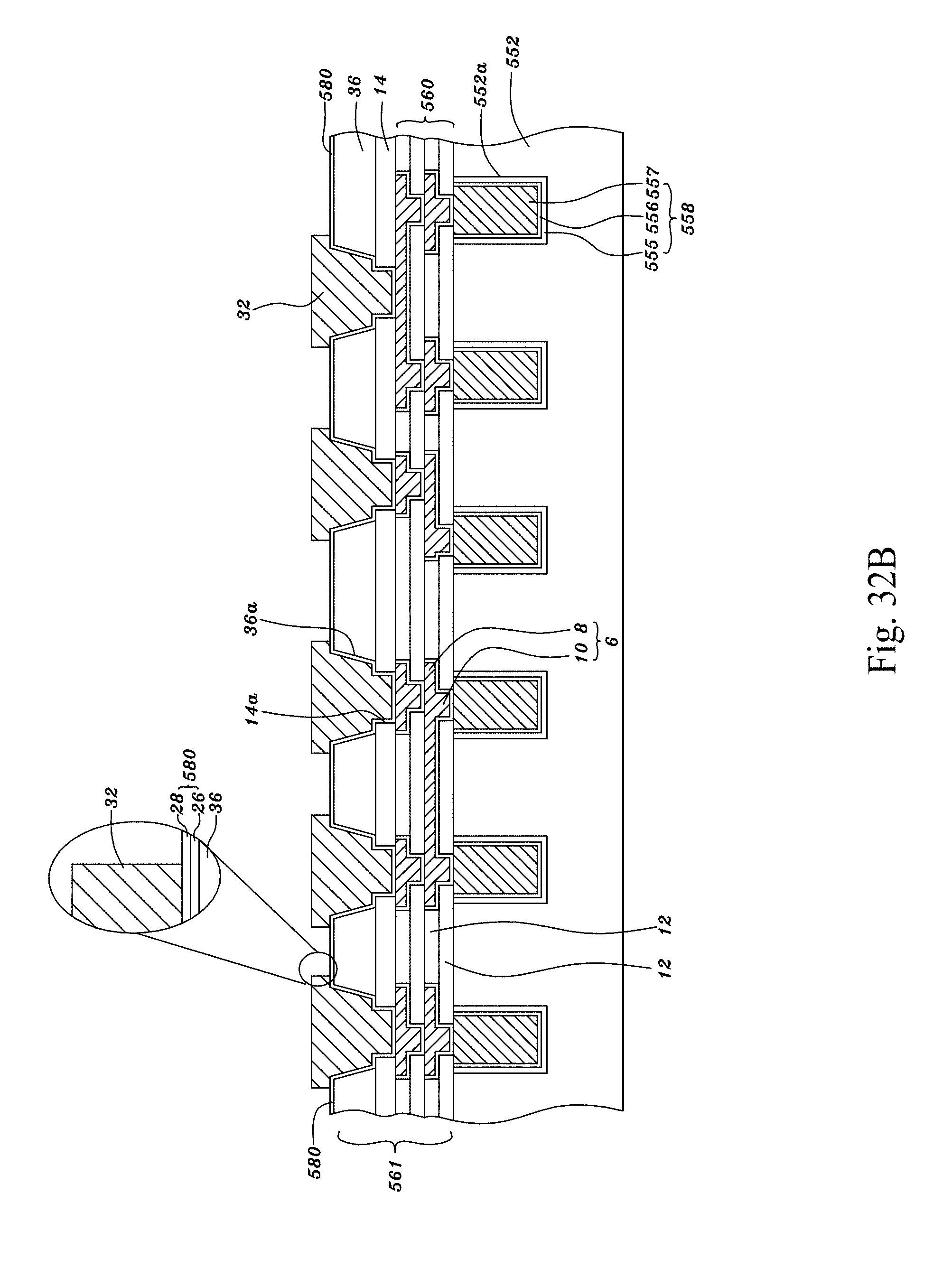

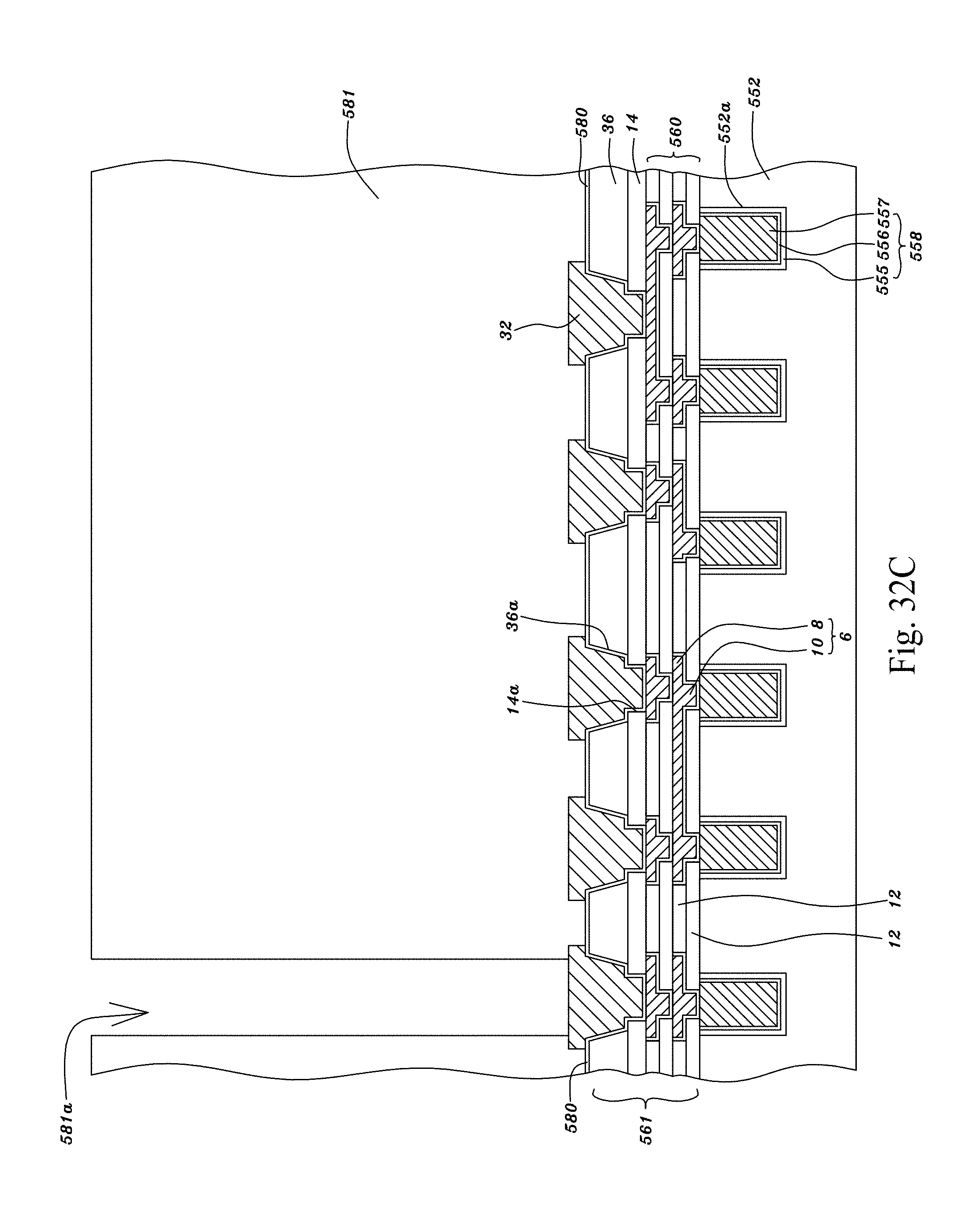

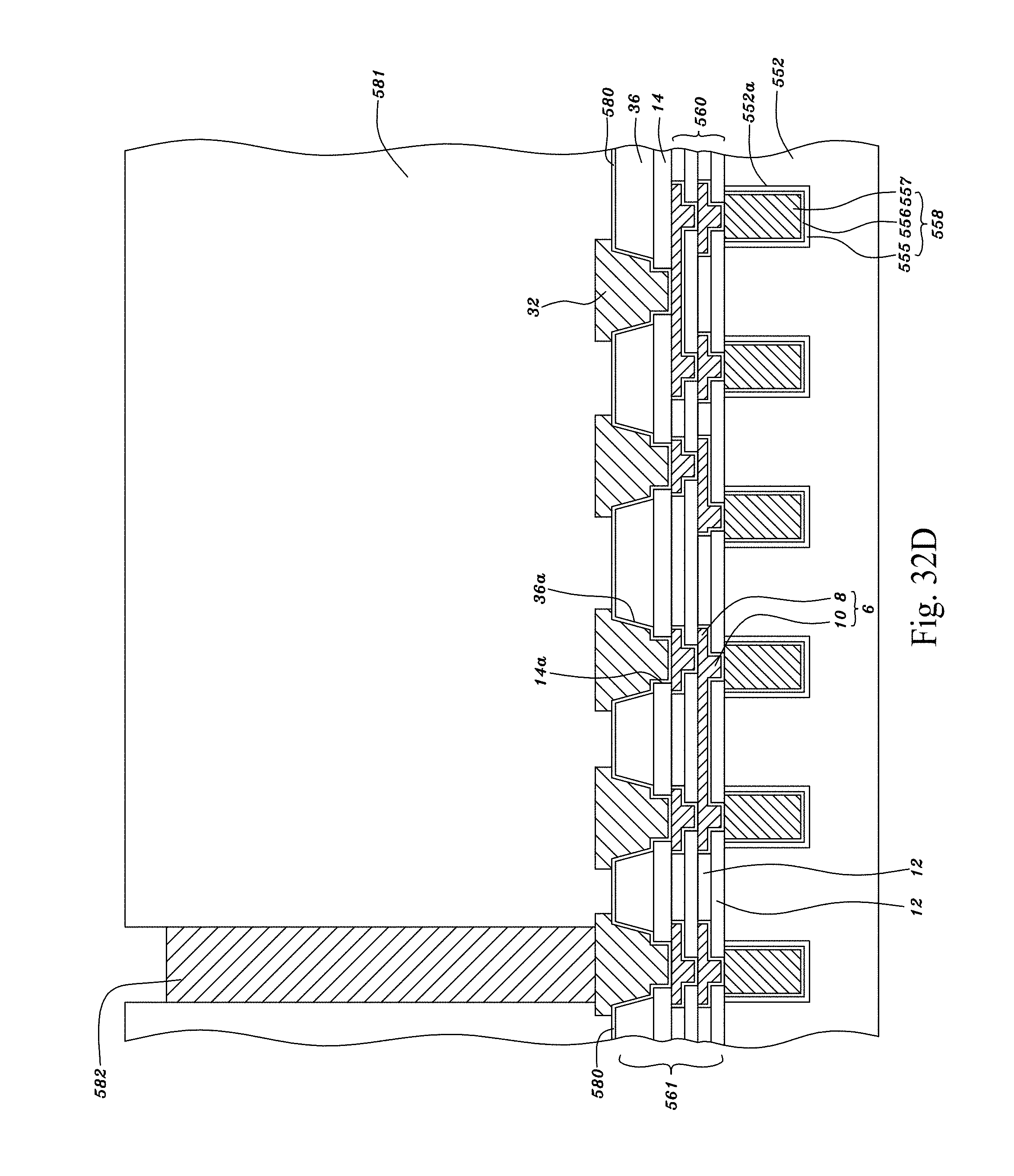

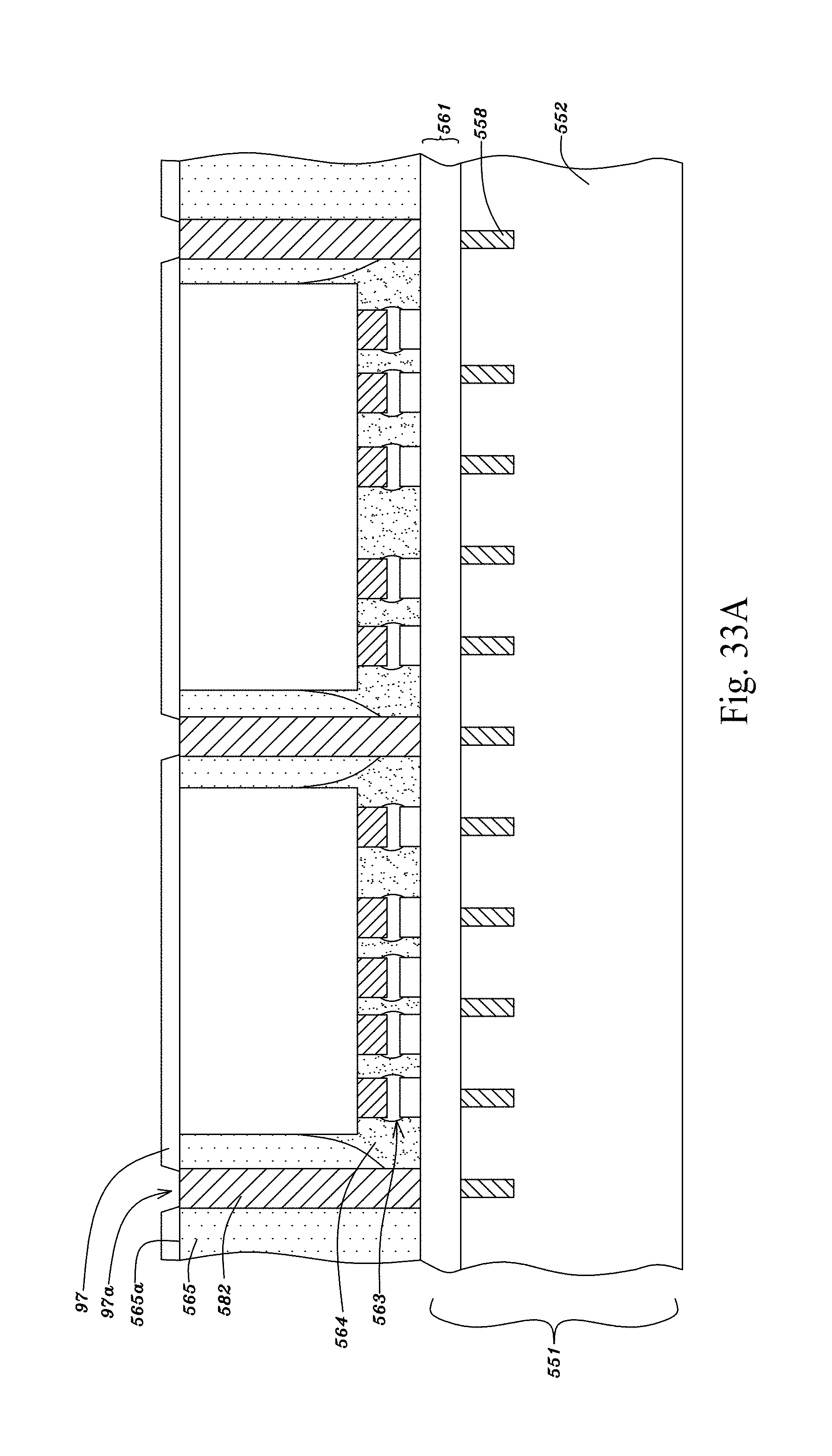

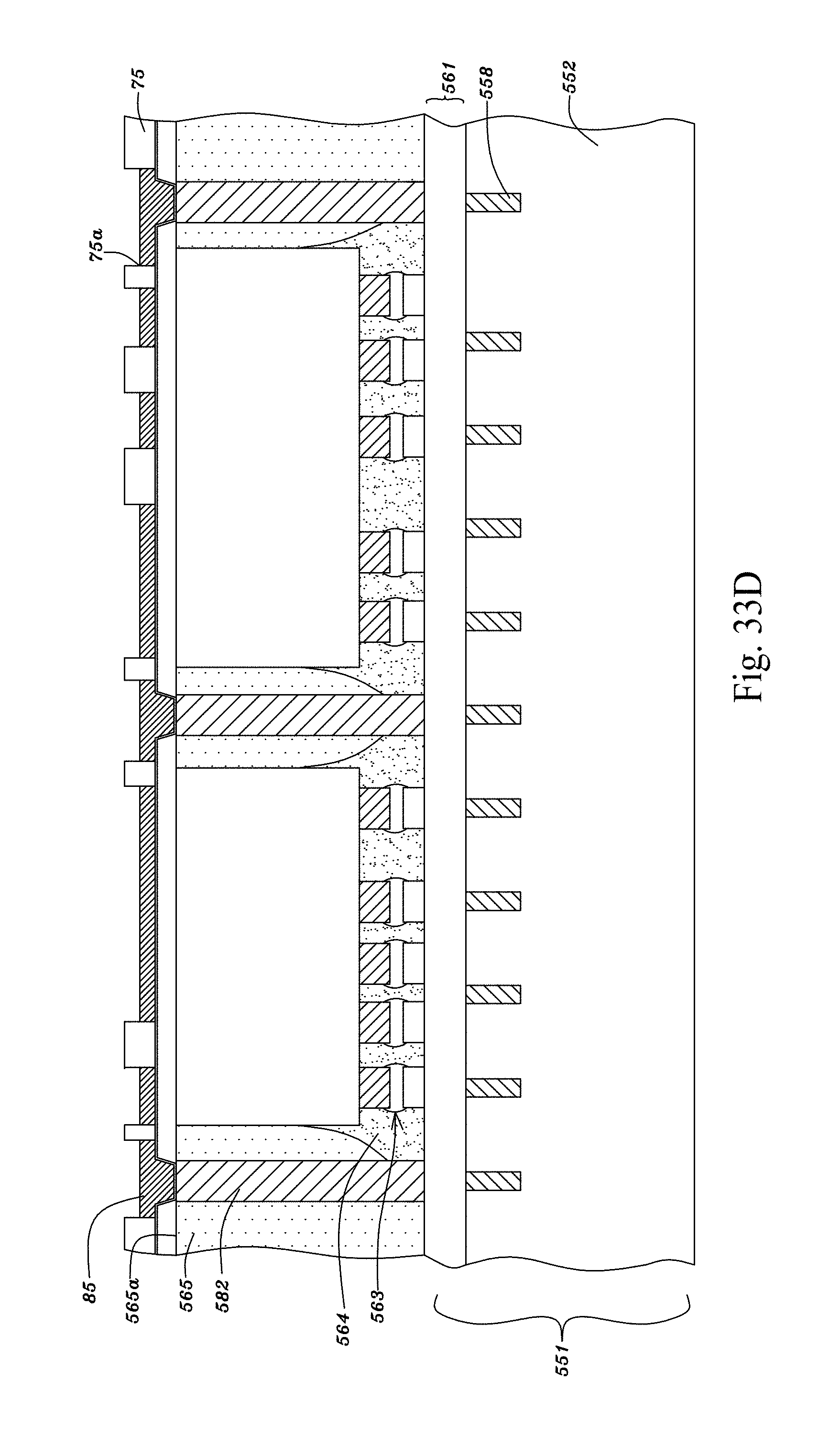

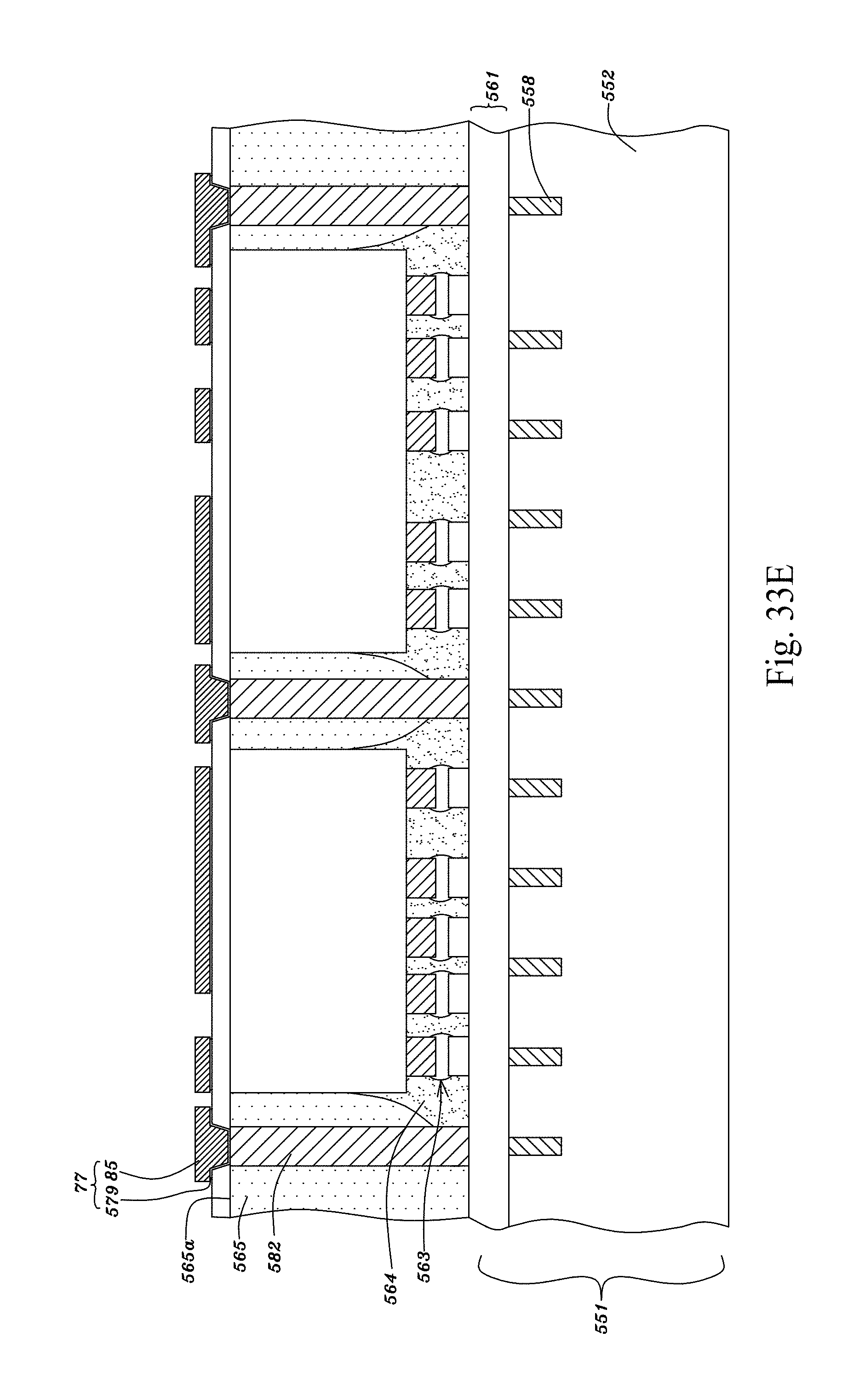

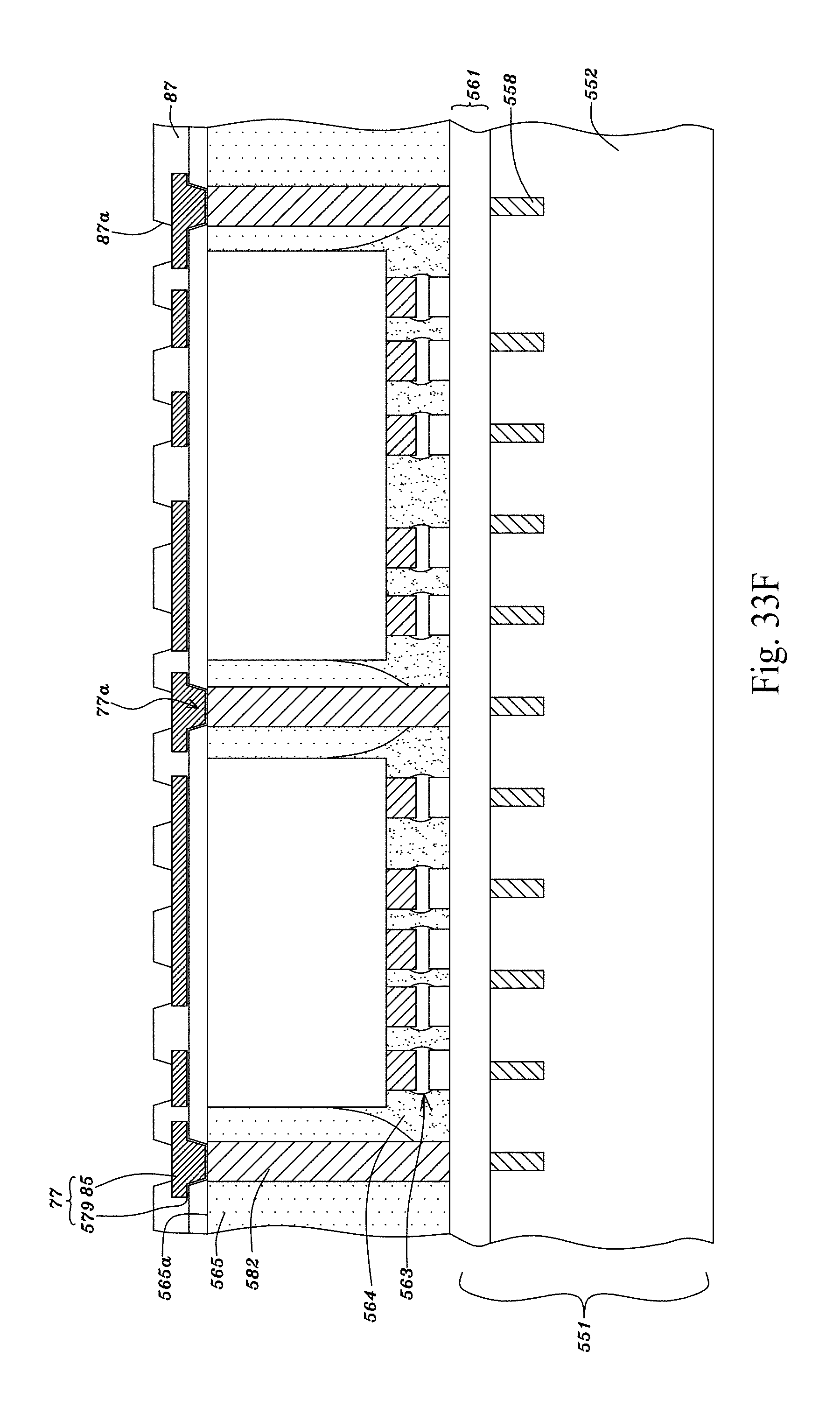

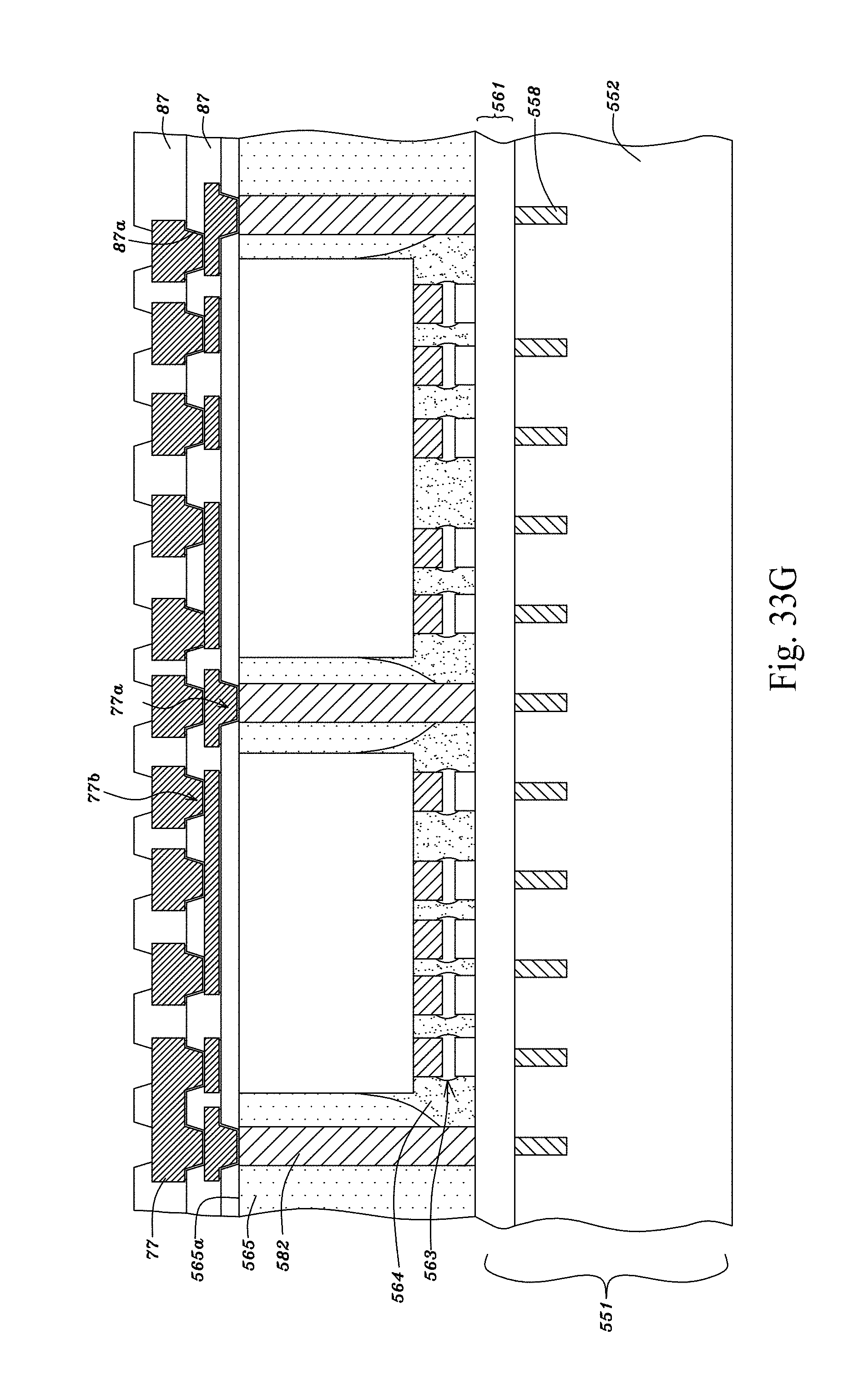

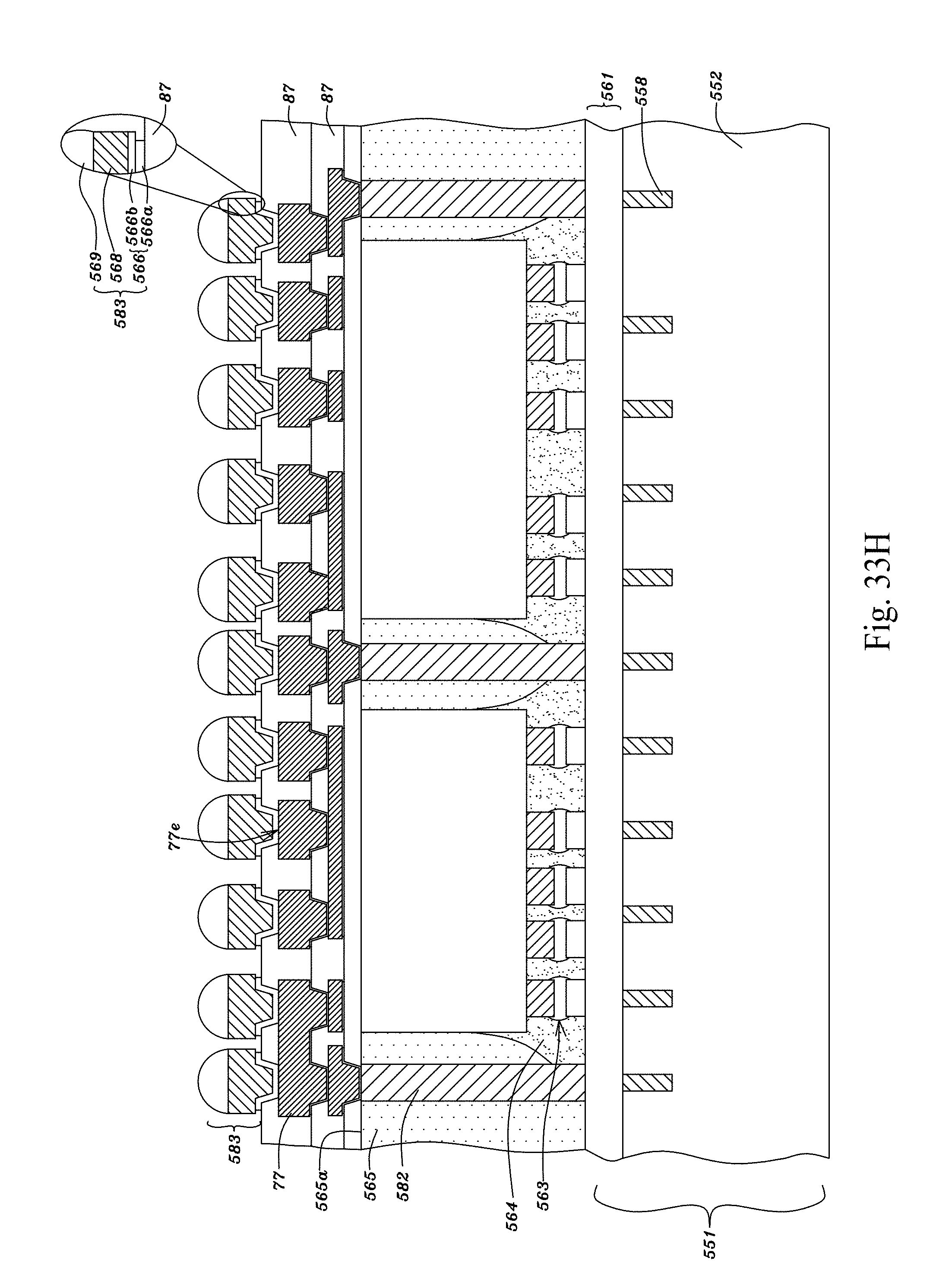

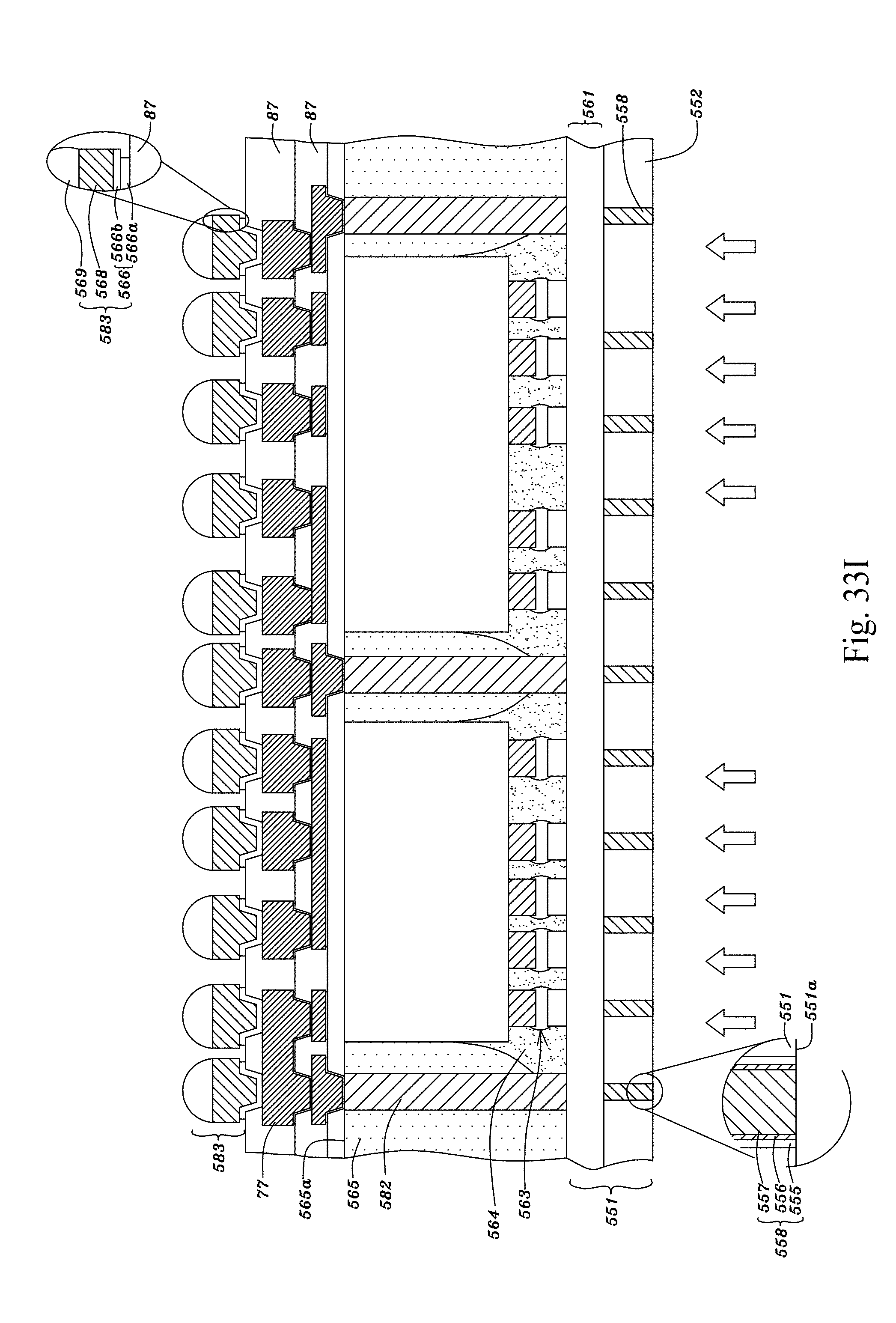

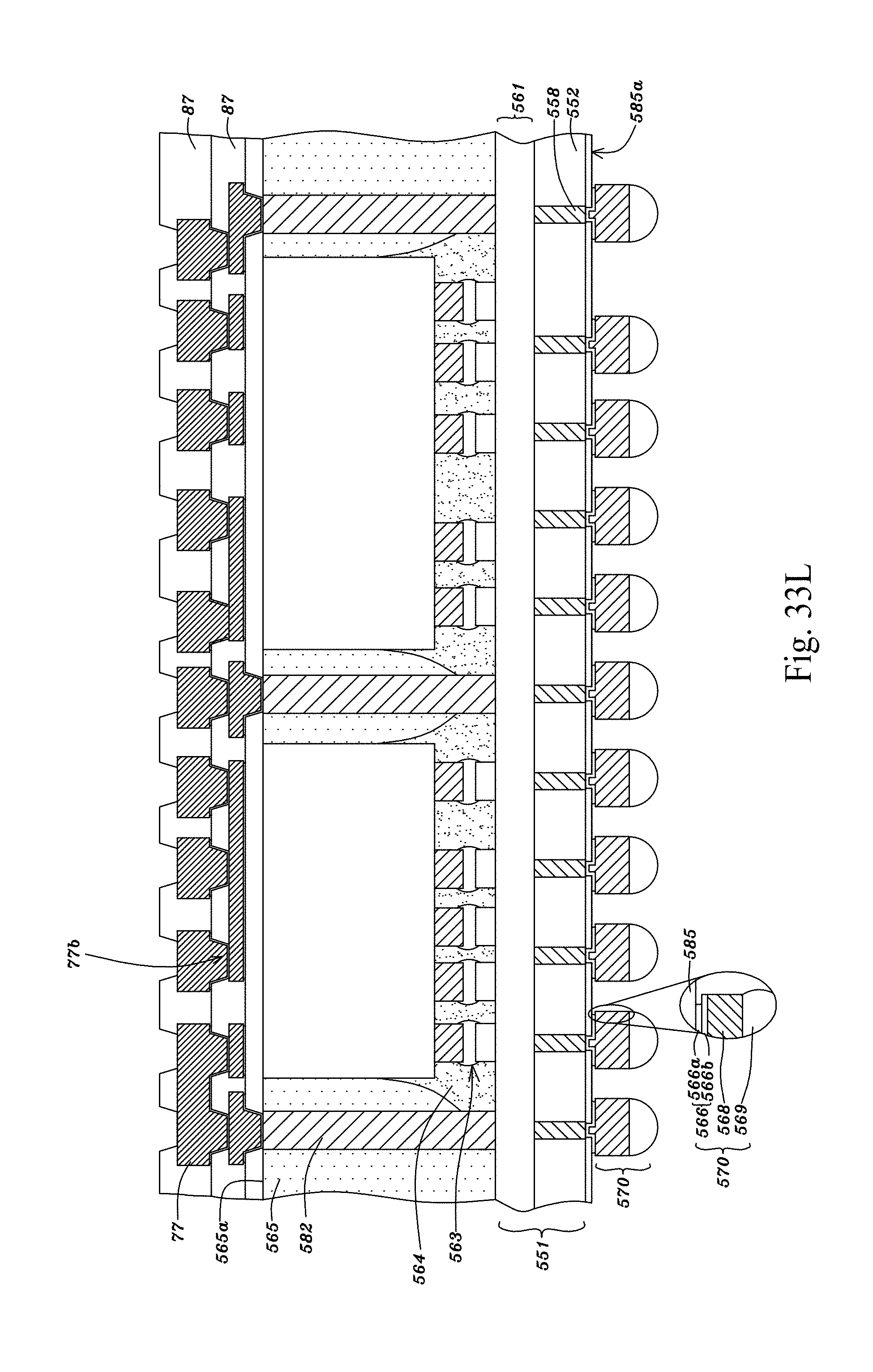

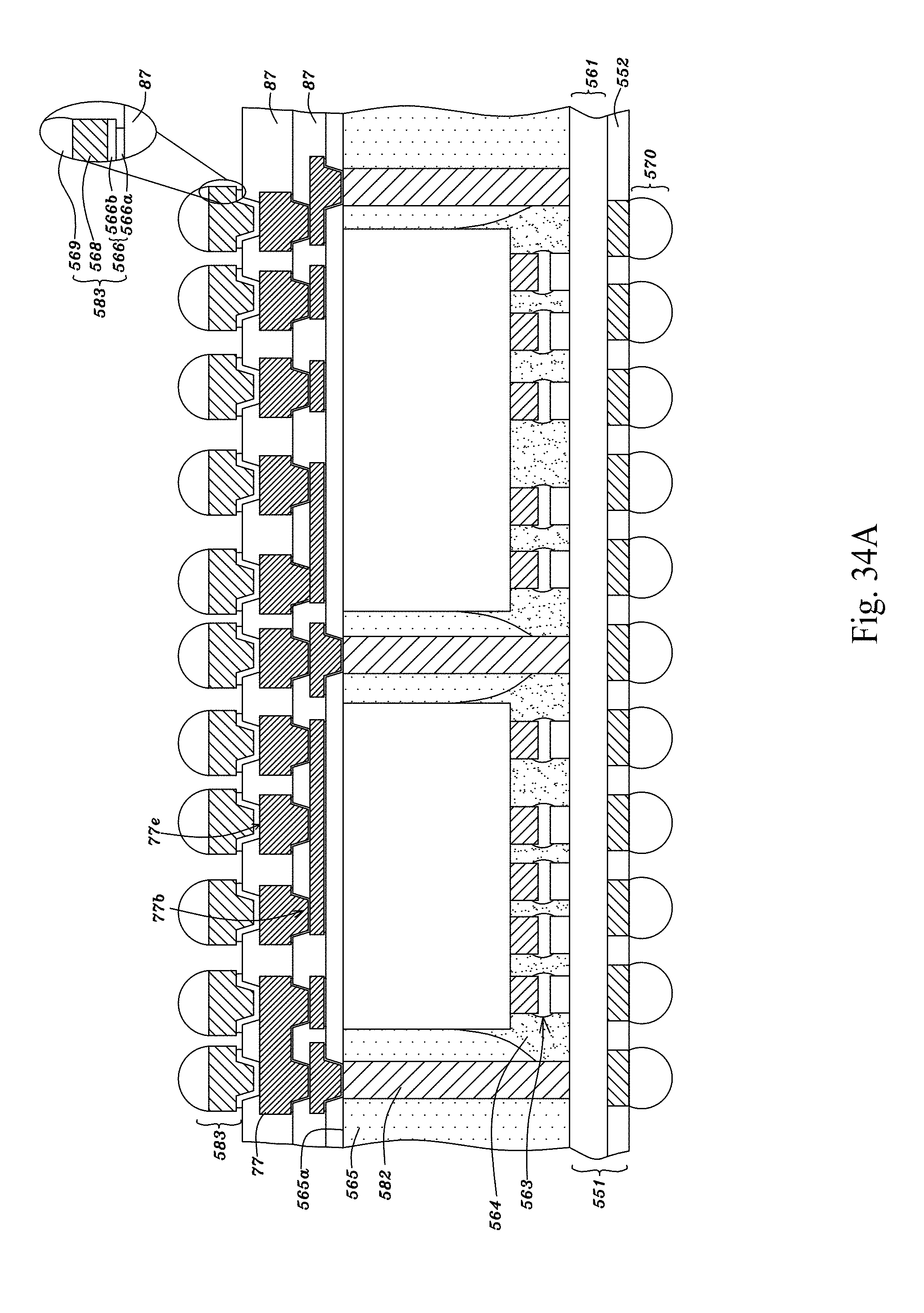

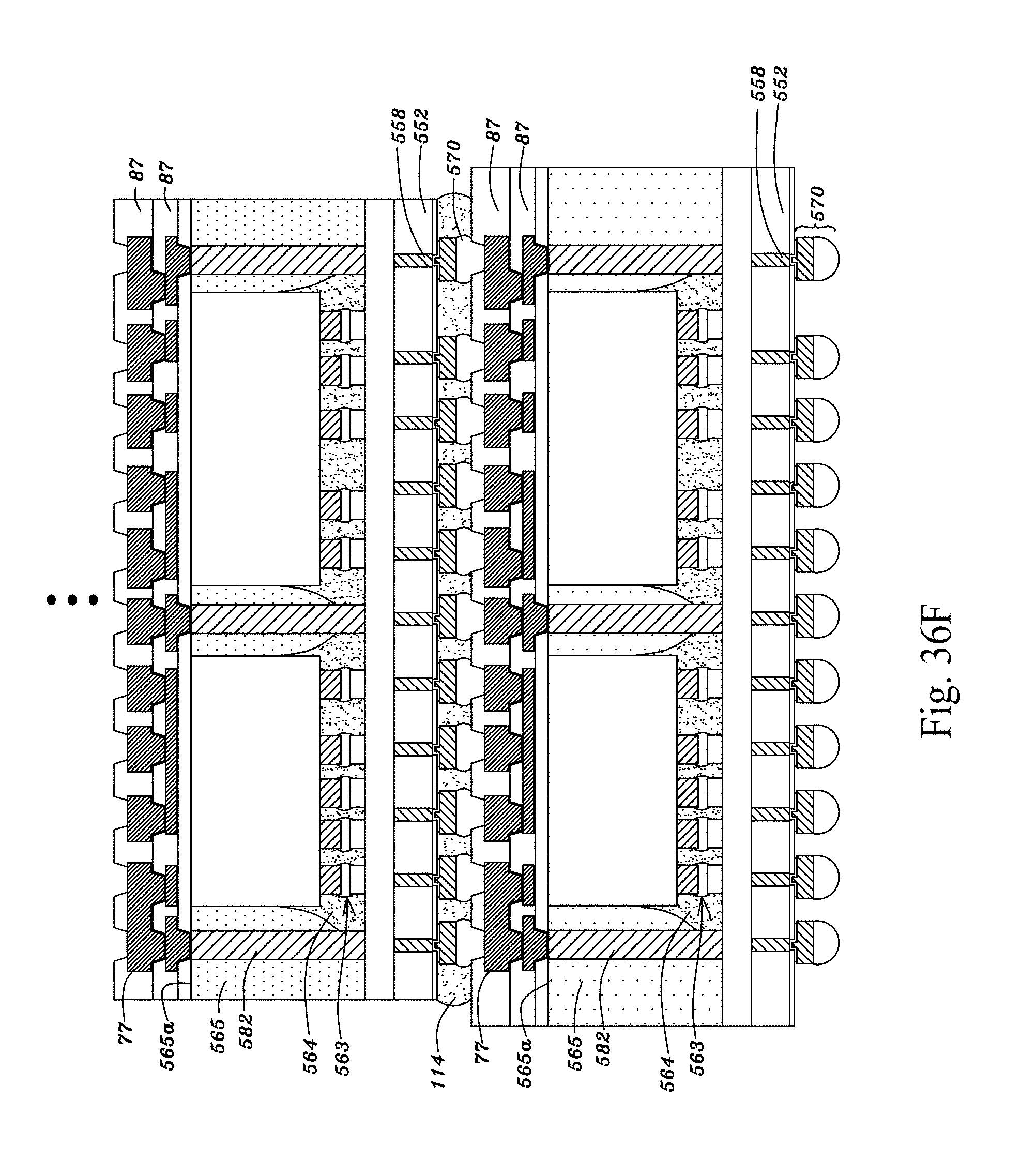

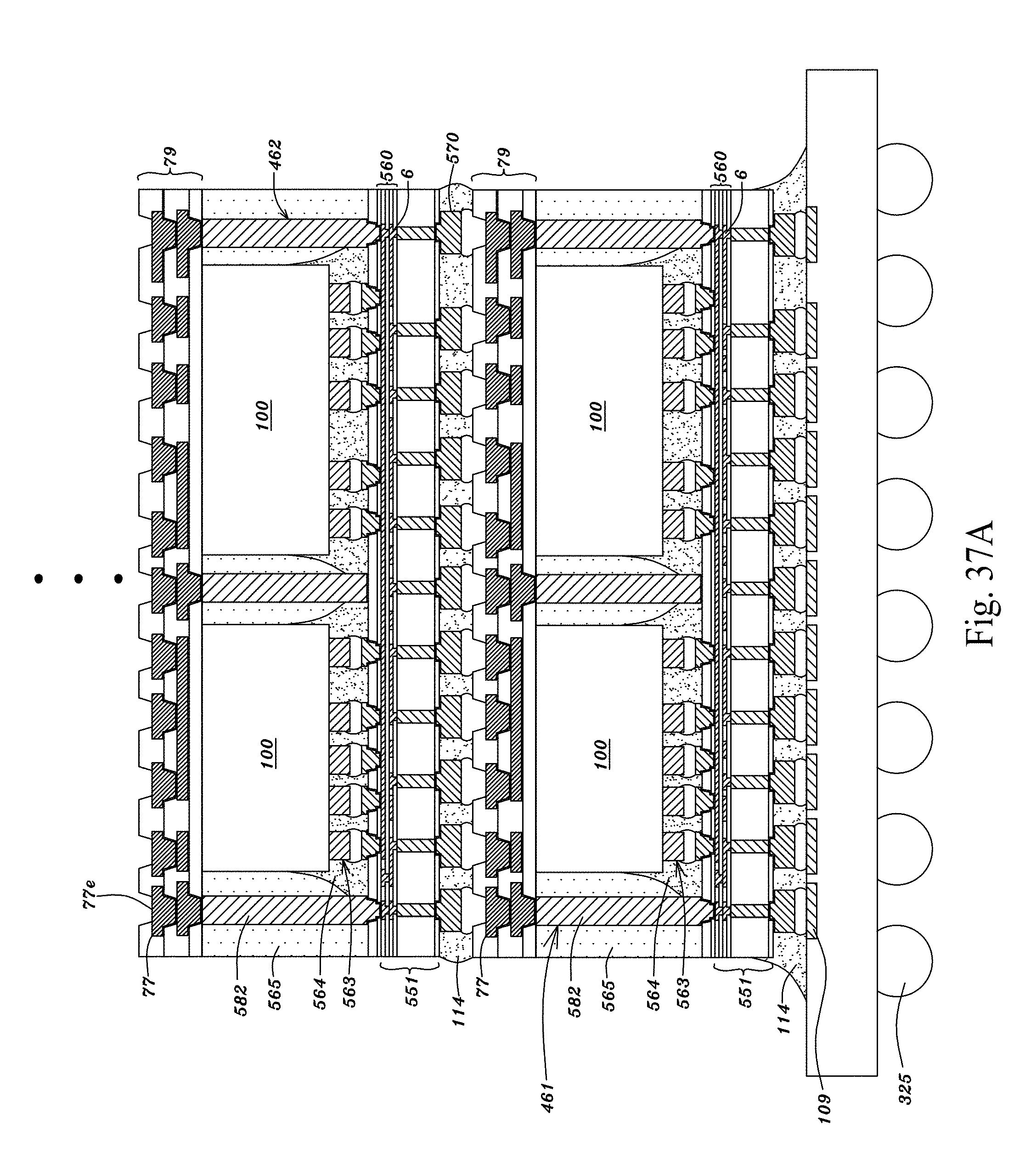

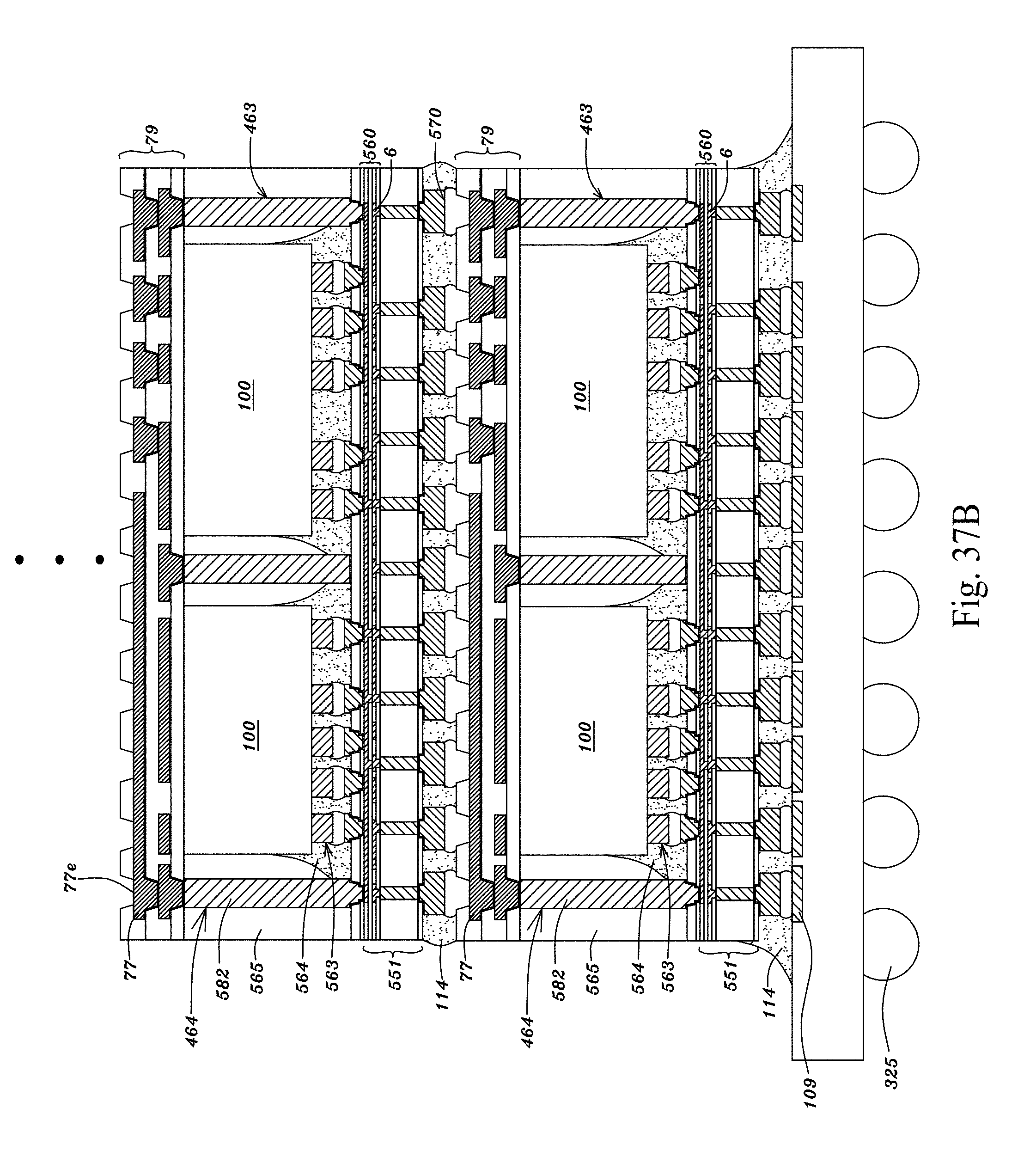

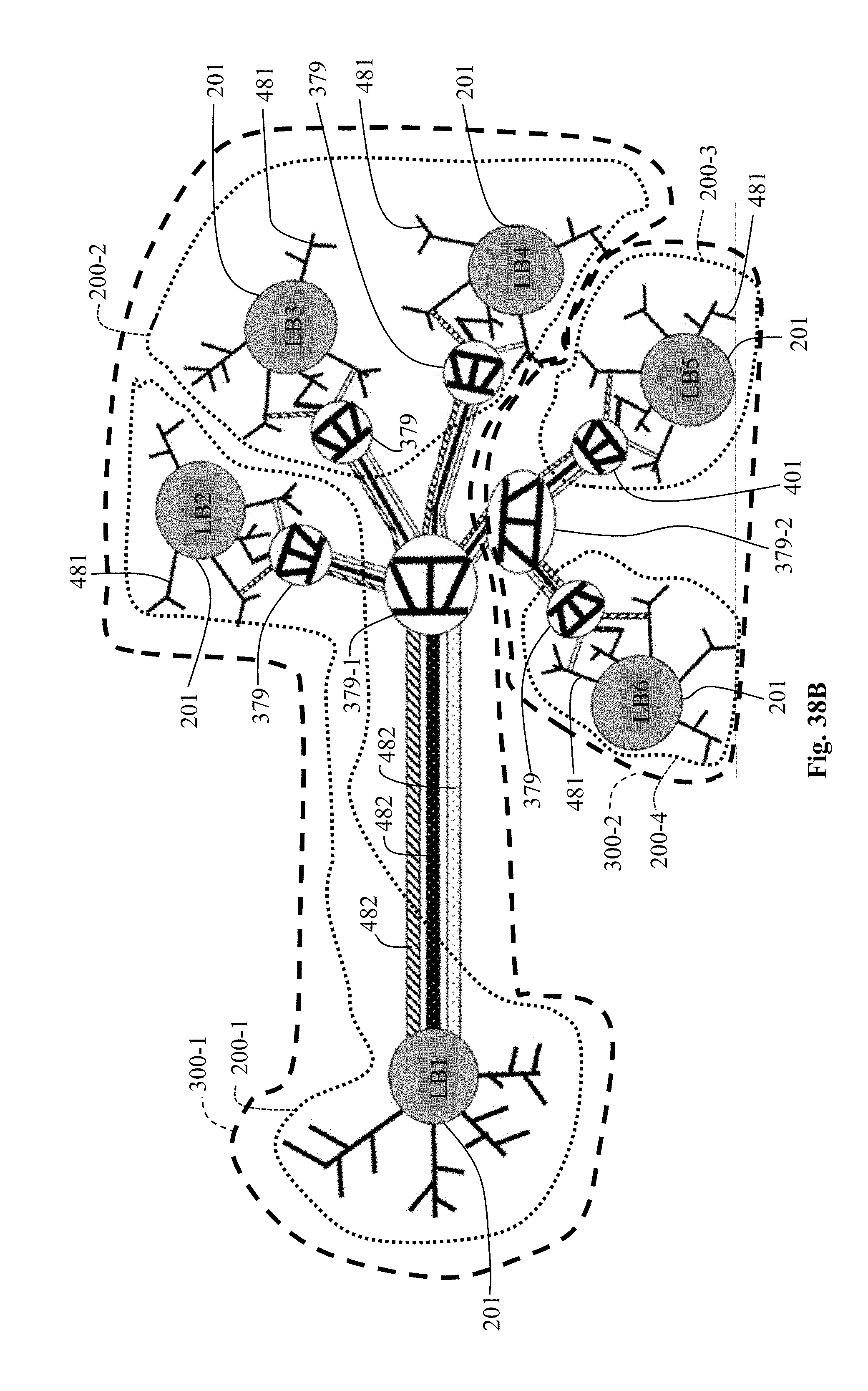

[0026] The LRRAM provides correction, recovery capability when the device or the FPGA IC chip is turned on, to prevent data errors caused by the charge leakage during the time when the device or the FPGA chip is turn off. The data stored in the Bit-bar and Bit are recovered to the correct states after the initiation process. In the initiation process after the device or the FPGA IC chip is turned on: (i) the gate of the Set-bar P-MOS is connected or coupled to a low operation or ground voltage (V.sub.ss), and the gate of the Set N-MOS is connected or coupled to a high operation voltage (V.sub.cc); the source of the Set-bar P-MOS is connected or coupled to the high operation voltage (V.sub.cc), and the source of the Set N-MOS is connected or coupled to the low operation or ground voltage (V.sub.ss), (ii) the common sources of P-MOS's in the 4T latched circuit is connected or coupled to the high operation voltage (V.sub.cc), and the common sources of N-MOS's in the 4T latched circuit is connected or coupled to the low operation or ground voltage (V.sub.ss). After the initiation process, the data stored in the Bit-bar and Bit nodes are recovered to the correct states. In the read operation process, the information stored in the non-volatile RRAM cells or the MIMs may be read. In the read operation process: (i) the gate of the Set-bar P-MOS is connected or coupled to a high operation voltage (V.sub.cc), and the gate of the Set N-MOS is connected or coupled to a low operation or ground voltage (V.sub.ss); the source of the Set-bar P-MOS and the source of the Set N-MOS may be disconnected, (ii) the common sources of P-MOS's in the 4T latched circuit is connected or coupled to the high operation voltage (V.sub.cc), and the common sources of N-MOS's in the 4T latched circuit is connected or coupled to the low operation voltage (V.sub.ss). The Bit and/or Bit-bar data of the LRRAM are used for programming the interconnection in the FPGA IC chips, or for the data storage in the LUTs.