Gate-last Semiconductor Fabrication With Negative-tone Resolution Enhancement

Leobandung; Effendi

U.S. patent application number 16/352348 was filed with the patent office on 2019-07-11 for gate-last semiconductor fabrication with negative-tone resolution enhancement. The applicant listed for this patent is International Business Machines Corporation. Invention is credited to Effendi Leobandung.

| Application Number | 20190214315 16/352348 |

| Document ID | / |

| Family ID | 64400275 |

| Filed Date | 2019-07-11 |

| United States Patent Application | 20190214315 |

| Kind Code | A1 |

| Leobandung; Effendi | July 11, 2019 |

GATE-LAST SEMICONDUCTOR FABRICATION WITH NEGATIVE-TONE RESOLUTION ENHANCEMENT

Abstract

A transistor structure includes a substrate and an active device layer formed on an upper surface of the substrate, the active device layer patterned to form multiple fins. Multiple source/drain regions are formed in the active device layer, the fins passing through the source/drain regions. The transistor structure further includes multiple source/drain contacts formed on upper surfaces of the source/drain regions, the source/drain contacts providing electrical connection to the respective source/drain regions. Multiple gate structures are formed between adjacent source/drain regions. The gate structures are electrically isolated from the active device layer by a gate dielectric layer formed between the active device layer and the respective gate structures. The gate structures are formed after formation of the source/drain regions and are self-aligned with the source/drain regions. Each of at least some of the gate structures are confined between a pair of adjacent source/drain contacts.

| Inventors: | Leobandung; Effendi; (Stormville, NY) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 64400275 | ||||||||||

| Appl. No.: | 16/352348 | ||||||||||

| Filed: | March 13, 2019 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 15606927 | May 26, 2017 | |||

| 16352348 | ||||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 29/775 20130101; H01L 21/823431 20130101; H01L 29/517 20130101; H01L 29/267 20130101; H01L 21/823437 20130101; H01L 21/823475 20130101; H01L 29/66545 20130101; H01L 21/845 20130101; H01L 21/8258 20130101; H01L 29/0673 20130101; H01L 27/0886 20130101; H01L 27/1211 20130101; H01L 29/4966 20130101 |

| International Class: | H01L 21/84 20060101 H01L021/84; H01L 27/12 20060101 H01L027/12; H01L 29/51 20060101 H01L029/51; H01L 21/8258 20060101 H01L021/8258; H01L 29/267 20060101 H01L029/267 |

Claims

1. A transistor structure, comprising: a substrate; an active device layer formed on an upper surface of the substrate, the active device layer patterned to form a plurality of fins; a plurality of source/drain regions formed in the active device layer, the plurality of fins passing through the source/drain regions; a plurality of source/drain contacts formed on upper surfaces of the plurality of source/drain regions, the source/drain contacts providing electrical connection to the respective source/drain regions; and a plurality of gate structures formed between adjacent source/drain regions, at least one of the gate structures being based on a configuration of a patterned trench, the gate structures being electrically isolated from the active device layer by a gate dielectric layer formed between the active device layer and the respective gate structures, the gate structures being formed subsequent to formation of the source/drain regions and being self-aligned with the source/drain regions, each of at least a subset of the plurality of gate structures being confined between a pair of adjacent source/drain contacts proximate a gate region where contact to the gate structure is formed.

2. The transistor structure of claim 1, wherein each of at least a subset of the gate structures comprises: a conductive material having a prescribed work function associated therewith; and a hard mask layer formed on an upper surface of the conductive material.

3. The transistor structure of claim 1, wherein the substrate is a silicon-on-insulator (SOI) substrate comprising a carrier substrate, an insulating layer formed on at least a portion of an upper surface of the carrier substrate, and the active device layer formed on at least a portion of an upper surface of the insulating layer.

4. The transistor structure of claim 1, wherein each of at least a subset of the source/drain regions comprises a Group III-V material.

5. The transistor structure of claim 4, wherein the Group III-V material comprises at least one of indium gallium arsenide (InGaAs), gallium arsenide (GaAs) and indium phosphide (InP).

6. The transistor structure of claim 1, wherein each of at least a subset of the plurality of gate structures is oriented in a direction substantially perpendicular to a major axis direction of the plurality of fins.

7. The transistor structure of claim 1, wherein a vertical height of at least a subset of the plurality of fins above an upper surface of the substrate is about 30 nanometers.

8. The transistor structure of claim 1, further comprising dielectric spacers formed on sidewalls of each of at least a subset of the plurality of source/drain contacts, each of the dielectric spacers being disposed between a corresponding one of the plurality of gate structures and an adjacent one of the source/drain contacts.

9. The transistor structure of claim 8, further comprising a high dielectric constant (high-k) dielectric layer formed on sidewalls of at least a subset of the plurality of gate structures, the high-k dielectric layer being disposed between a corresponding one of the plurality of gate structures and an adjacent one of the dielectric spacers.

10. The transistor structure of claim 9, wherein the high-k dielectric layer comprises at least one of hafnium oxide (HfO), zirconium oxide (ZrO), and aluminum oxide (Al.sub.2O.sub.3).

11. The transistor structure of claim 9, wherein the high-k dielectric layer is formed having a cross-sectional thickness of about one to three nanometers (nm).

12. The transistor structure of claim 1, wherein the source/drain regions comprise a doped epitaxial layer covering the plurality of fins.

Description

CROSS-REFERENCE TO RELATED APPLICATION(S)

[0001] The present application is a continuation of U.S. patent application Ser. No. 15/606,927, filed May 26, 2017, having the same title and inventors as the present application, the disclosure of which is hereby incorporated by reference herein in its entirety for all purposes.

BACKGROUND

[0002] The present invention relates generally to the electrical, electronic and computer arts, and, more particularly, to semiconductor devices and fabrication.

[0003] In an effort to increase the density of circuit elements within a semiconductor device, the dimensions of the elements are often scaled down. The ability to shrink certain dimensions, such as gate length, can be limited due to the particular performance requirements of the device, including operating voltage, leakage current, gate capacitance, etc. For example, polysilicon gates are adversely affected by poly depletion which can significantly reduce performance. When a metal-oxide-semiconductor field-effect transistor (MOSFET) is operated in an inversion mode, part of the applied gate voltage is dropped in the polysilicon due to poor conductivity of the polysilicon. A metal gate, which offers superior conductivity, may be used, but a metal gate is susceptible to metal migration during subsequent processing operations that are performed at elevated temperatures.

[0004] Another problem with high-density devices is precise control of gate lengths. As device dimensions continue to shrink, precise control of gate lengths becomes critical to assure performance. One method for controlling gate lengths is by using a dummy or replacement gate process. In a replacement gate process, a dummy gate is formed of silicon dioxide or a polymer such as photoresist. An oxide layer is formed over the dummy gate. The dummy gate is removed thereby creating a gate opening, and a desired gate material is deposited into the gate opening at a subsequent stage in the fabrication process. One problem with existing replacement gate processes is the limited ability to control the height of the dummy gate during removal of the overlying dielectric layer. Also, the etching process to form contact openings can cause oxidation of the source and drain regions, leading to higher source and drain resistances.

SUMMARY

[0005] Aspects according to one or more embodiments of the present invention relate to a novel transistor structure formed using a gate-last semiconductor process flow with negative-tone resolution enhancement. More particularly, a transistor structure formed in accordance with one or more embodiments of the invention includes a gate that is patterned as a trench, rather than as a freestanding line as is conventionally done. In one or more embodiments, since the gate of the transistor device is formed after formation of source/drain regions in the device, self-alignment of the gate to source drain using the source/drain regions is performed.

[0006] In one aspect, the invention relates to a method of fabricating a transistor structure. The method includes: forming an active device layer on a semiconductor substrate; patterning the active device layer to form a plurality of fins; forming a first dielectric layer on at least a portion of an upper surface and sidewalls of the plurality of fins; forming a second dielectric layer on at least a portion of an upper surface of the first dielectric layer; forming a first plurality of openings through the second dielectric layer and the first dielectric layer, exposing the underlying active device layer forming the plurality of fins; forming a plurality of source/drain regions in the active device layer exposed through the respective first plurality of openings; forming a plurality of source/drain contacts on an upper surface of each of the plurality of source/drain regions; forming a second opening through the second dielectric layer and the first dielectric layer, the second opening exposing the underlying active device layer adjacent to the plurality of source/drain regions; depositing a third dielectric layer in at least a portion of the second opening, including on sidewalls of the second opening and sidewalls and an upper surface of the plurality of fins; and forming a gate stack on the third dielectric layer, the gate stack being self-aligned with the plurality of source/drain regions.

[0007] In a further aspect, the invention relates to a gate-last transistor structure fabricated using negative-tone resolution enhancement. The transistor structure includes an active device layer formed on an upper surface of a substrate, the active device layer patterned to form a plurality of fins, a plurality of source/drain regions formed in the active device layer, the fins passing through the source/drain regions, and a plurality of source/drain contacts formed on upper surfaces of the respective source/drain regions for providing electrical connection to the source/drain regions. The transistor structure further includes a plurality of gate structures formed between adjacent source/drain regions, the gate structures being electrically isolated from the active device layer by a gate dielectric layer formed between the active device layer and the respective gate structures. The gate structures are formed subsequent to forming the source/drain regions and are self-aligned with the source/drain regions. Each of at least a subset of the gate structures are confined between a pair of adjacent source/drain contacts proximate a gate region where contact to the gate structure is formed.

[0008] Techniques as disclosed herein can provide substantial beneficial technical effects. By way of example only and without limitation, one or more embodiments may provide one or more of the following advantages: [0009] reduces detrimental standing wave effects and proximity effects caused by device scaling; [0010] reduces tilting in high aspect ratio gate freestanding line problems; [0011] less prone to extreme ultraviolet (EUV) mask defects since it is negative tone; [0012] allows lower temperature source/drain epitaxy which beneficially facilitates the use of Group III-V materials for source/drain regions;

[0013] These and other features and advantages will become apparent from the following detailed description of illustrative embodiments thereof, which is to be read in connection with the accompanying drawings.

BRIEF DESCRIPTION OF THE DRAWINGS

[0014] The following drawings are presented by way of example only and without limitation, wherein like reference numerals (when used) indicate corresponding elements throughout the several views, and wherein:

[0015] FIGS. 1A through 8D are top plan and corresponding cross-sectional views depicting intermediate processing steps in an overall semiconductor fabrication methodology for forming an active semiconductor device comprising a gate patterned as a trench, according to one or more embodiments of the invention.

[0016] It is to be appreciated that elements in the figures are illustrated for simplicity and clarity. Common but well-understood elements that may be useful or necessary in a commercially feasible embodiment may not be shown in order to facilitate a less hindered view of the illustrated embodiments.

DETAILED DESCRIPTION

[0017] Principles of the present disclosure will be described herein in the context of illustrative transistor devices having at least one gate patterned as a trench, and methods of fabricating such devices. It is to be appreciated, however, that the specific structures and/or methods illustratively shown and described herein are to be considered exemplary as opposed to limiting. Moreover, it will become apparent to those skilled in the art given the teachings herein that numerous modifications can be made to the embodiments shown that are within the scope of the appended claims. That is, no limitations with respect to the embodiments shown and described herein are intended or should be inferred.

[0018] Although the overall fabrication method and the structures for the disclosed embodiments are entirely novel, certain individual processing steps required to implement the structure and/or circuitry may utilize conventional semiconductor fabrication techniques and conventional semiconductor fabrication tooling. These techniques and tooling will already be familiar to one having ordinary skill in the relevant art given the teachings herein. Moreover, many of the processing steps and tooling used to fabricate semiconductor devices are also described in a number of readily available publications, including, for example: James D. Plummer et al., Silicon VLSI Technology, Prentice Hall; 2 edition (Nov. 11, 2008); and James D. Plummer et al., Silicon VLSI Technology: Fundamentals, Practice, and Modeling, Pearson; 1 edition (Jul. 24, 2000), both of which are hereby incorporated by reference herein in their entireties. It is emphasized that while some individual processing steps may be set forth herein, those steps are merely illustrative, and one skilled in the art may be familiar with several equally suitable alternatives that would also fall within the scope of the invention.

[0019] It is to be appreciated that the various layers, regions, structures and/or components shown in the accompanying figures may not be drawn to scale. Furthermore, one or more semiconductor layers of a type commonly used in such integrated circuit devices may not be explicitly shown in a given figure for ease of explanation. This does not imply that the semiconductor layer(s) not explicitly shown are omitted in the actual integrated circuit device.

[0020] As previously stated, as metal-oxide-semiconductor (MOS) transistor device geometries are reduced to increase density, the conventional method of patterning the MOS gate as a freestanding line produces several problems. Specifically, contact lithography offers high resolution (down to about the wavelength of the radiation), but practical problems such as mask damage and resulting low yield make this process unusable in most production environments. Proximity printing reduces mask damage by keeping the mask a set distance above the wafer (e.g., 20 .mu.m). Unfortunately, the resolution limit is increased to greater than 2 to 4 .mu.m, making proximity printing insufficient for modern technology. By far the most common method of exposure is projection printing.

[0021] In the context of semiconductor fabrication, resolution--the smallest feature that can be printed with adequate control--has two basic limits: the smallest image that can be projected onto the wafer, and the resolving capability of the photoresist to make use of that image. From a projection imaging perspective, resolution is determined by the wavelength of the imaging light (.lamda.) and the numerical aperture (NA) of the projection lens.

[0022] Another important aspect of photoresist exposure is what is often referred to as a standing wave effect. Monochromatic light, when projected onto a wafer, strikes the photoresist surface over a range of angles, approximating plane waves. This light travels down through the photoresist and, if the substrate is reflective, is reflected back up through the resist. The incoming and reflected light interfere with one another to form a standing wave pattern of high and low light intensity at different depths in the photoresist. This pattern is replicated in the photoresist, causing ridges to form in the sidewalls of the resist feature. As pattern dimensions become smaller, these ridges can significantly affect the quality of the feature. The interference that causes standing waves also results in a phenomenon called swing curves, the sinusoidal variation in linewidth with changing resist thickness.

[0023] Proximity effects are another cause of problems when device dimensions are scaled. Proximity effects are typically defined as variations in the linewidth of a feature (or the shape for a two-dimensional pattern) as a function of the proximity of other nearby features. The concept of proximity effects became prominent when it was observed that electron beam lithography can cause backscattered electrons to travel many microns, exposing photoresist at nearby features. Optical proximity effects refer to those proximity effects that occur during optical lithography (even though they may not necessarily be caused by optical phenomenon). One simple example of an optical proximity effect is the difference in printed linewidth between an isolated line and a line in a dense array of equal lines and spaces (called iso-dense print bias). Thus, as gate dimensions and spacing are reduced, optical proximity effects become more manifest.

[0024] In order to reduce disadvantageous effects caused by patterning the gate as a freestanding line, embodiments of the invention beneficially pattern the gate as a trench. Even using a conventional trench-gate fabrication process, whereby a polysilicon dummy gate is replaced with a metal gate in a later process stage, which may ultimately form a trench-like structure, the gate is still initially patterned as a freestanding line and therefore exhibits the same detrimental effects. Advantages of embodiments of the invention include, but are not limited to, reducing detrimental standing wave effects and proximity effects caused by device scaling, reducing tilting in high aspect ratio freestanding line problems, reducing the impact of extreme ultraviolet (EUV) mask defects, and allowing lower temperature source/drain epitaxy which beneficially facilitates the use of Group III-V materials for source/drain regions, as will be described in further detail below.

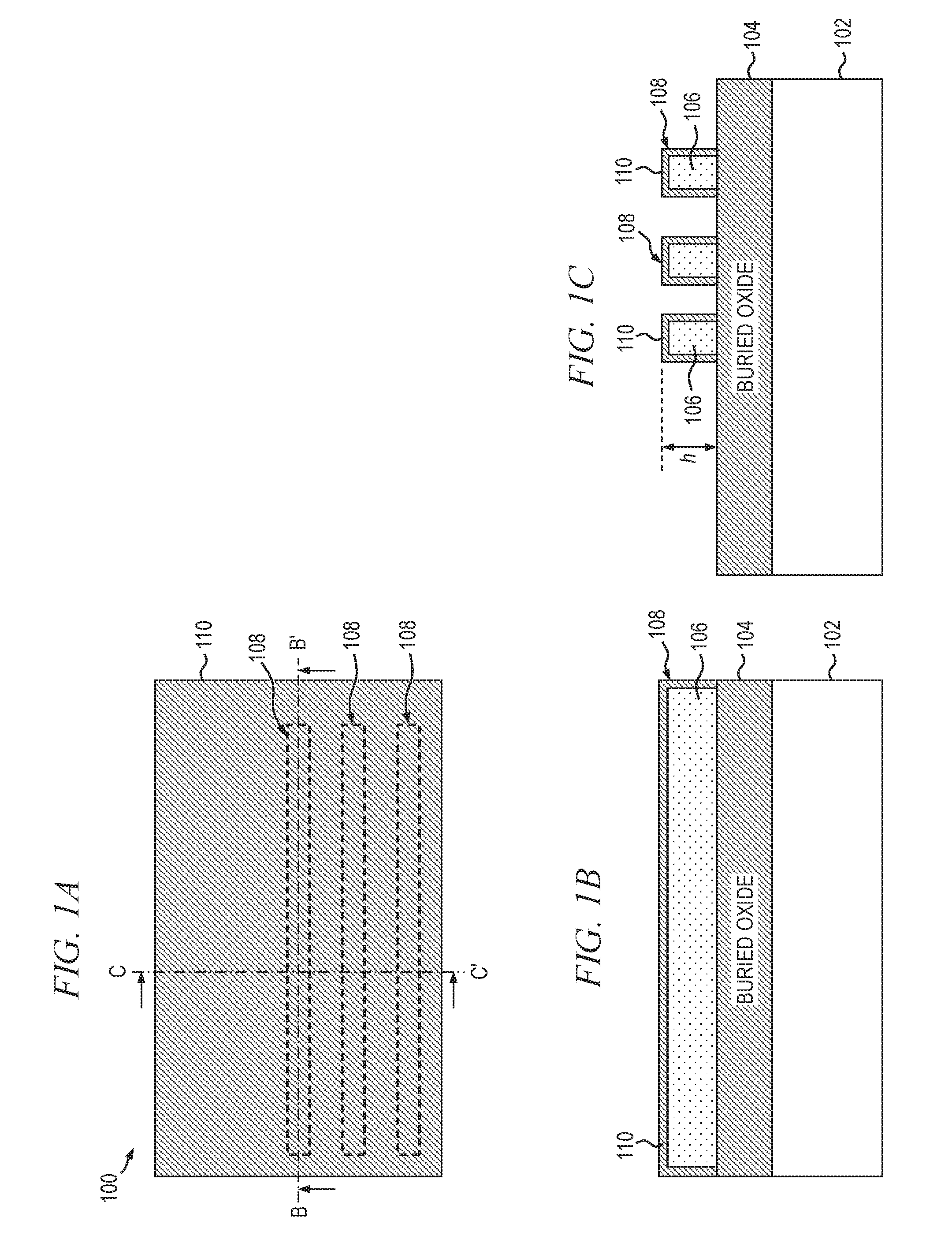

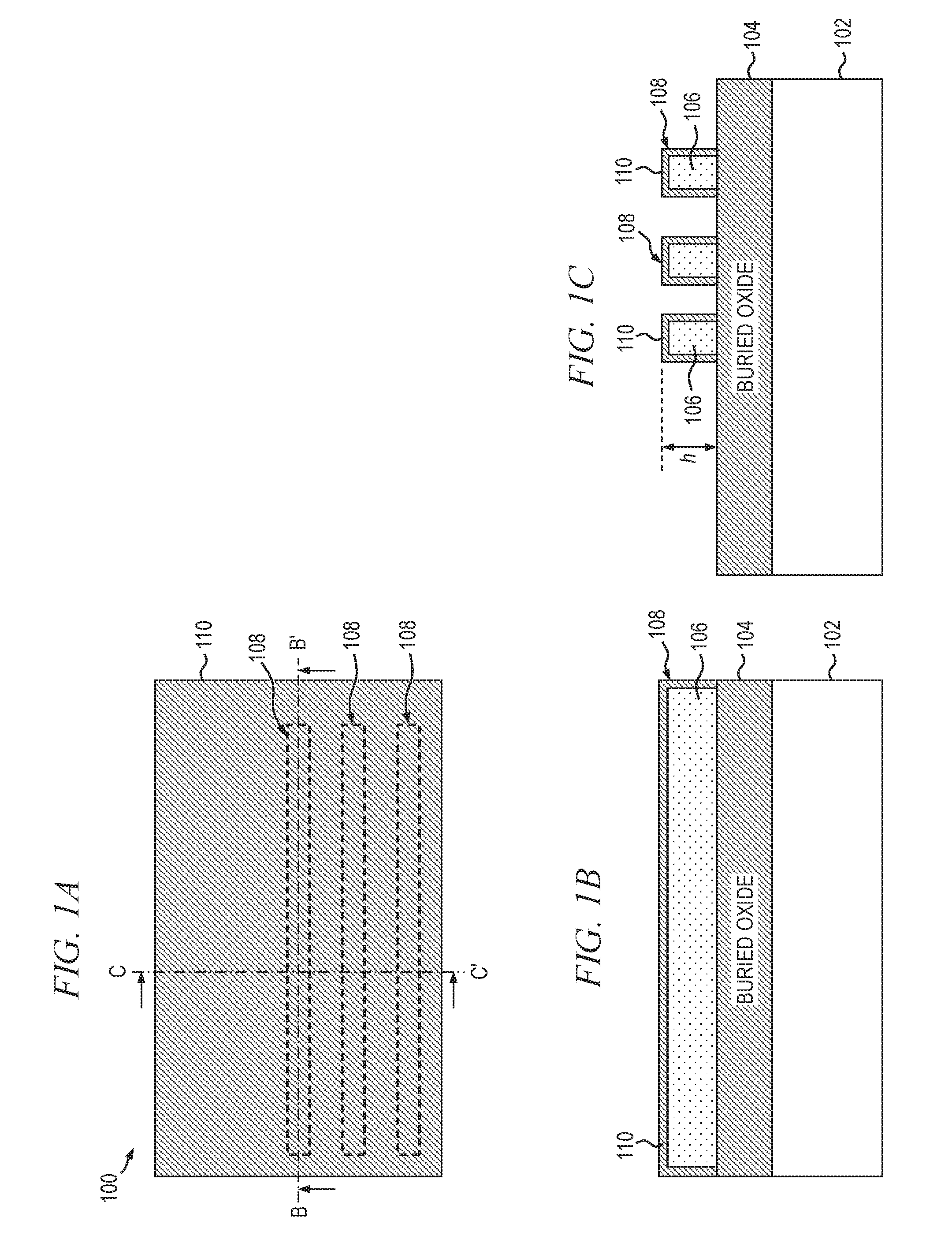

[0025] FIGS. 1A through 8D are top plan and corresponding cross-sectional views depicting various intermediate processing steps in an overall semiconductor fabrication methodology for forming an active semiconductor device (e.g., MOS transistor) comprising a gate patterned as a trench, according to one or more embodiments of the invention. With reference to FIGS. 1A-1C, FIG. 1A is a top plan view of at least a portion of an exemplary MOS transistor structure 100, FIG. 1B is a cross-sectional view of the illustrative structure 100 shown in FIG. 1A taken along line B-B', and FIG. 1C is a cross-sectional view of the illustrative structure 100 shown in FIG. 1A taken along line C-C'. The MOS transistor structure 100, in one or more embodiments, is formed on a silicon-on-insulator (SOI) substrate comprising a carrier substrate 102, which may be formed of silicon or an alternative material suitable for use as a substrate (e.g., germanium (Ge), gallium arsenide (GaAs), indium phosphide (InP), etc.), an oxide (e.g., silicon dioxide) or other insulating layer 104 formed on at least a portion of an upper surface of the substrate, and an active device layer 106 formed on at least a portion of an upper surface of the oxide layer.

[0026] The active device layer 106 may be formed of silicon having a prescribed conductivity type (e.g., n-type or p-type) associated therewith, such as by using a standard doping process. Since the oxide layer 104 is formed between the substrate 102 and active device layer 106, it is often referred to as a buried oxide (BOX) layer. The active device layer 106, buried oxide layer 104 and substrate 102 are considered elements of the SOI substrate. Although the transistor structure 100 will be described herein in the context of an SOI substrate, it is to be appreciated that the transistor structure may be similarly formed on a bulk silicon wafer in one or more embodiments of the invention, wherein layer 104 does not exist and the device is isolated with shallow trench isolation (STI) structures or other methods.

[0027] In one or more embodiments, the active device layer 106 is patterned using, for example, a standard lithographic process (e.g., photolithographic mask followed by etching) to form a plurality of fins 108. In one or more embodiments, a height, h, of the fins 108 above an upper surface of the buried oxide layer 104 is about 30 nanometers (nm), although embodiments of the invention are not restricted to any particular dimensions and/or shapes. Furthermore, embodiments of the invention are not limited to any particular number of fins 108 formed on the transistor structure 100. It is to be appreciated that although the transistor structure 100 will be described herein in the context of a fin-type field-effect transistor (FinFET) device, aspects of the invention may be similarly used in the formation of other device types, such as, for example, planar devices and/or nanowires, as will become apparent to those skilled in the art given the teachings herein.

[0028] In one or more embodiments, a thin oxide layer 110 is formed on at least a portion of an upper surface and sidewalls of the active device layer 106, covering the fins 108. The thin oxide layer 110 preferably comprises an oxide, such as, for example, silicon dioxide (SiO.sub.2), although other dielectric materials (e.g., silicon nitride (Si.sub.3N.sub.4)) may be similarly employed, despite being referred as to an oxide layer. The oxide layer 110, in one or more embodiments, may be formed by oxidizing the underlying silicon active device layer 106 to form SiO.sub.2, although other means of forming the thin oxide layer are contemplated (e.g., deposition, etc.). A thickness of the thin oxide layer 110 is preferably about 1-2 nm, although embodiments of the invention are not limited to any specific thickness of the thin oxide layer.

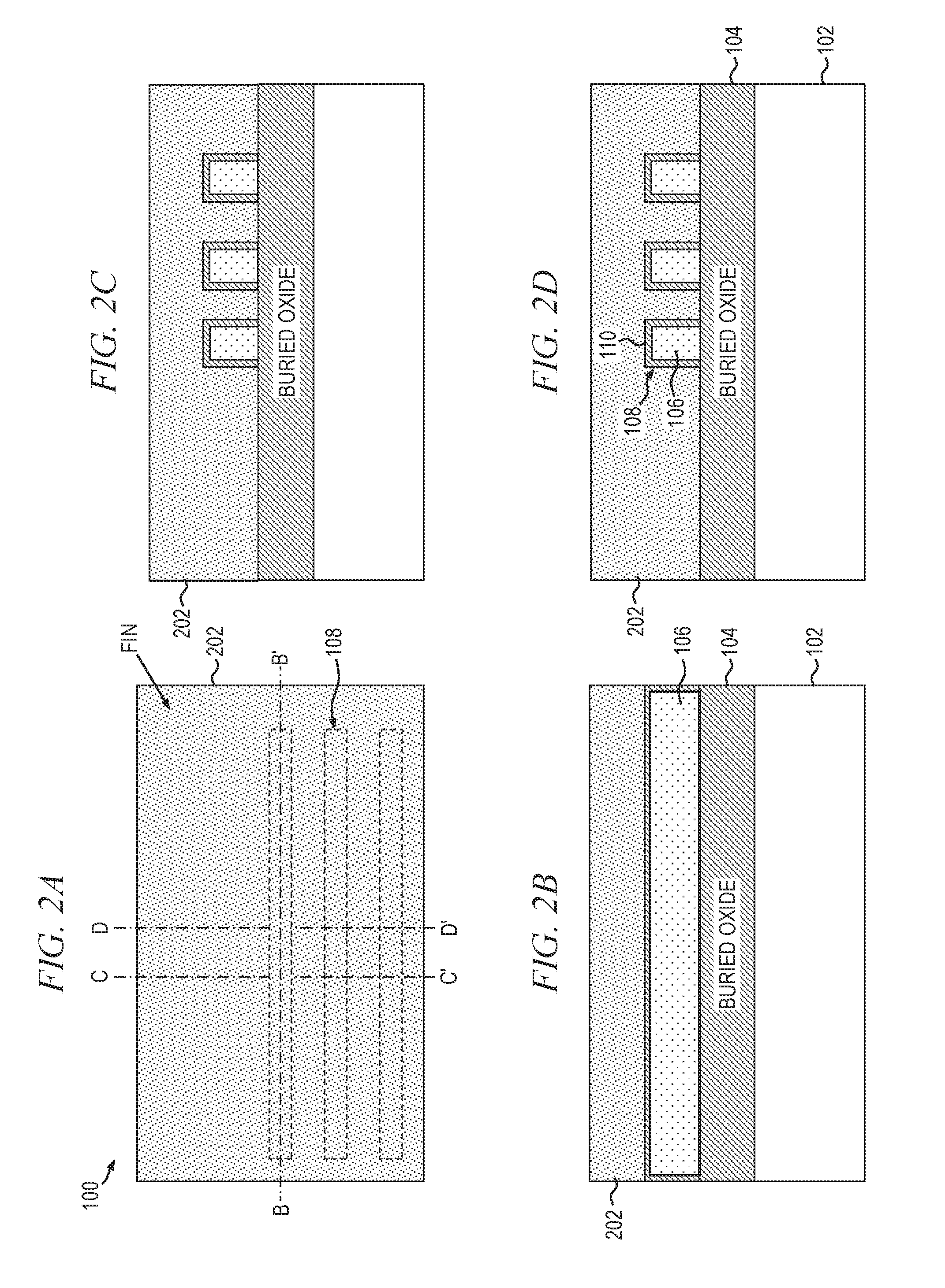

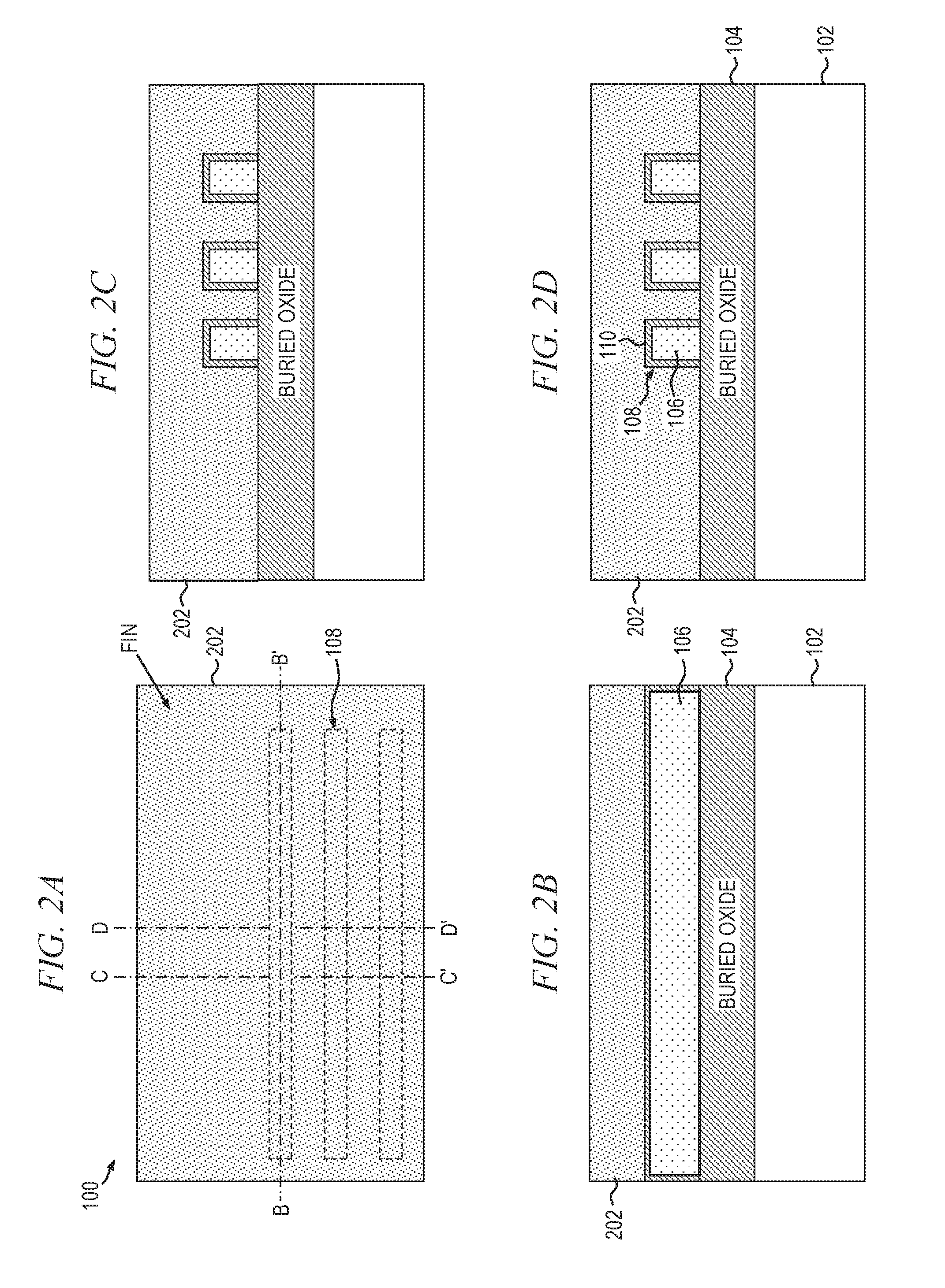

[0029] FIGS. 2A through 2D depict a subsequent stage (low-k dielectric layer deposition) in the processing of the transistor structure 100, according to an embodiment of the invention; FIG. 2A is a top plan view of at least a portion of the exemplary MOS transistor structure 100, FIG. 2B is a cross-sectional view of the illustrative structure 100 shown in FIG. 2A taken along line B-B', FIG. 2C is a cross-sectional view of the illustrative structure 100 shown in FIG. 2A taken along line C-C', and FIG. 2D is a cross-sectional view of the illustrative structure 100 shown in FIG. 2A taken along line D-D'. Specifically, FIGS. 2A through 2D illustrate the formation of a low-dielectric constant (low-k) layer 202 on at least a portion of an upper surface of the thin oxide layer 110 for middle-of-line contact formation. In this embodiment, the dielectric layer 202 is preferably formed using an oxide deposition process, followed by a planarization process, such as chemical mechanical polishing/planarization (CMP) or the like. In one or more embodiments, the dielectric layer 202 is formed of low-k carbon-doped oxide (e.g., SiCOH or porous oxide) or carbon-doped nitride (e.g., SiBCN) material, although embodiments of the invention are not limited to these materials.

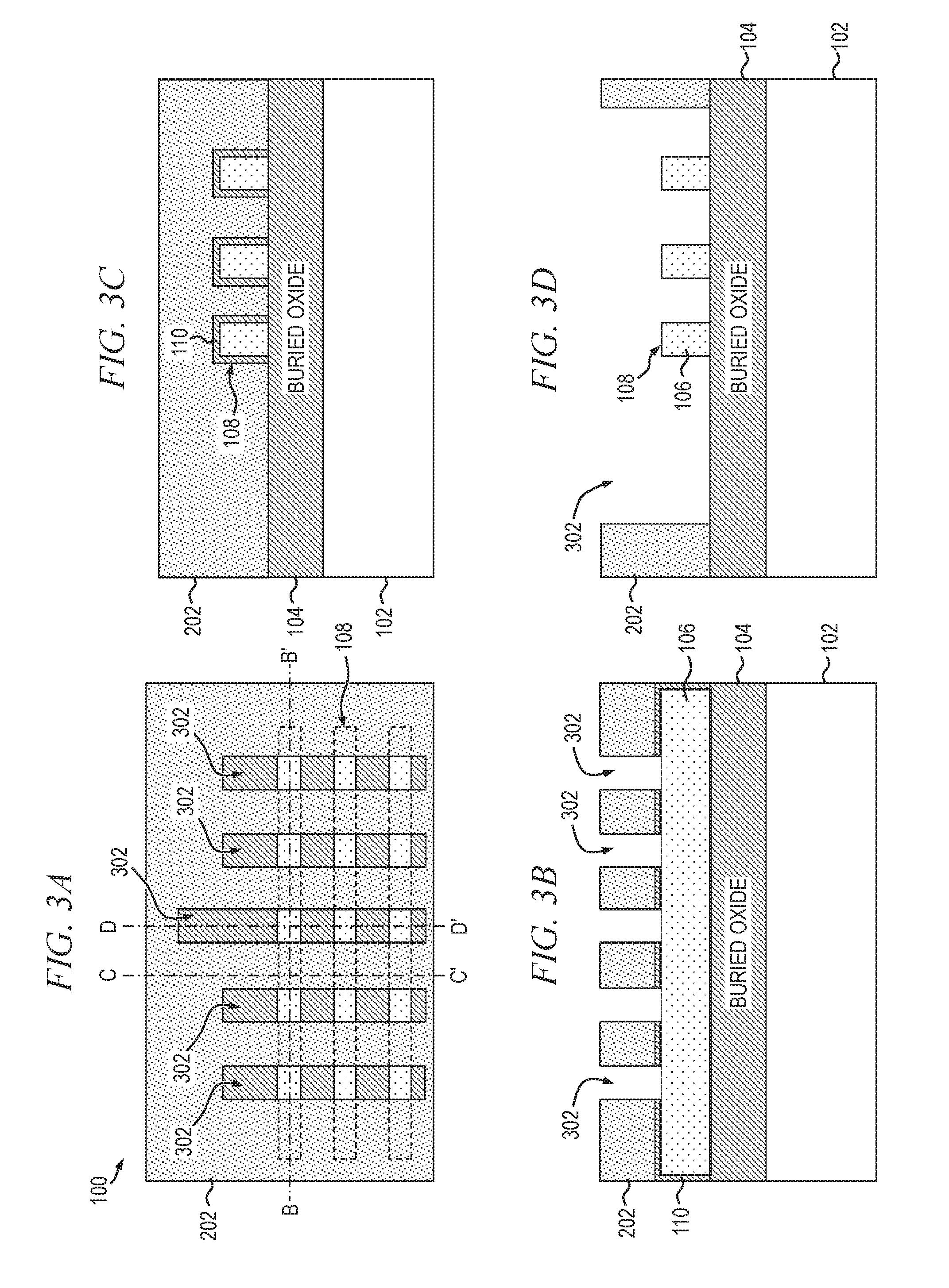

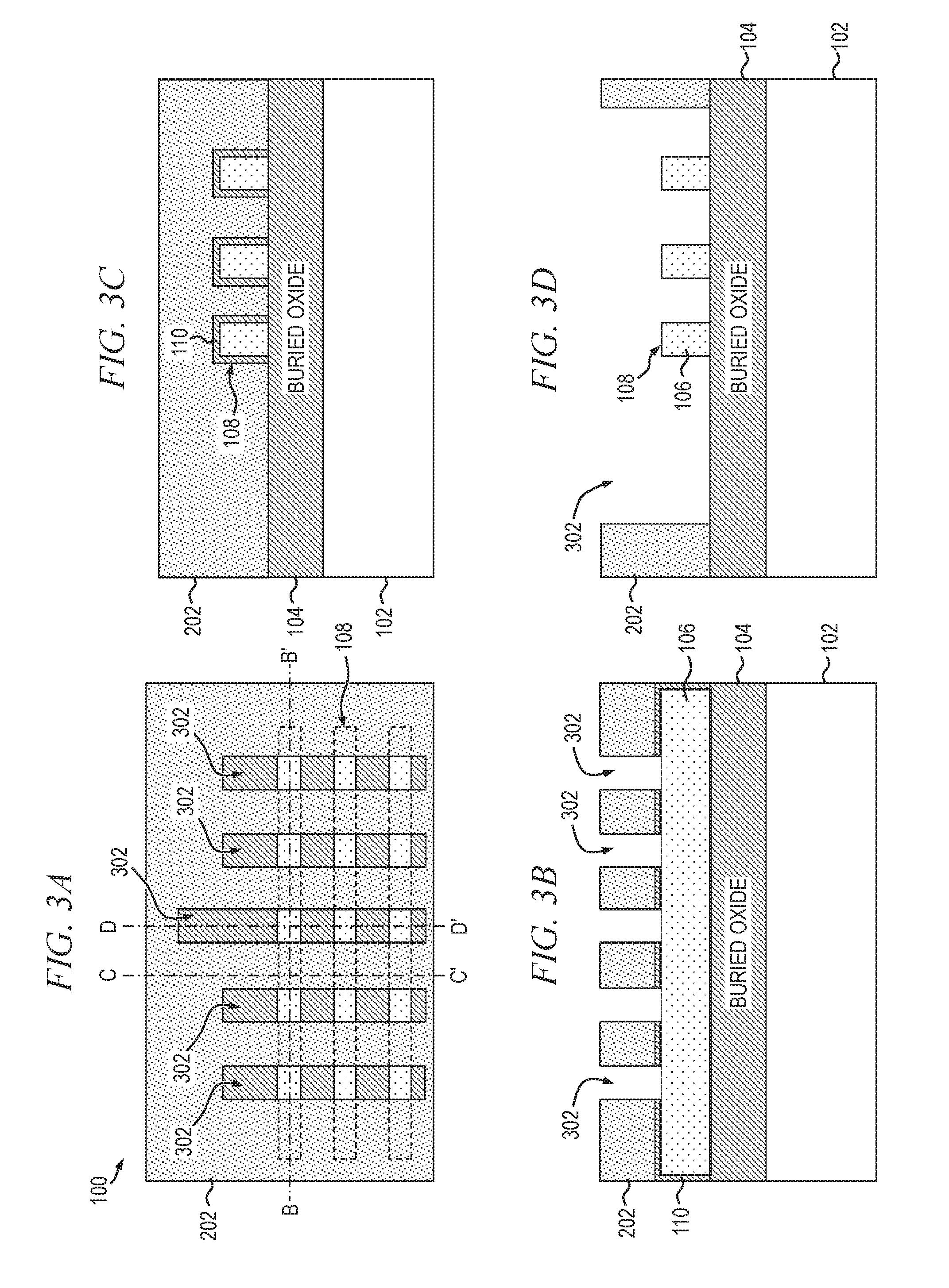

[0030] FIGS. 3A through 3D depict an exemplary pattern contact and etch processing stage in the fabrication of the transistor structure 100, according to an embodiment of the invention; FIG. 3A is a top plan view of at least a portion of the exemplary MOS transistor structure 100, FIG. 3B is a cross-sectional view of the illustrative structure 100 shown in FIG. 3A taken along line B-B', FIG. 3C is a cross-sectional view of the illustrative structure 100 shown in FIG. 3A taken along line C-C', and FIG. 3D is a cross-sectional view of the illustrative structure 100 shown in FIG. 3A taken along line D-D'. Specifically, as shown in FIGS. 3A-3D, a plurality of openings 302 are formed through the dielectric layer 202 and the thin oxide layer 110, exposing the underlying active device layer 106 and buried oxide layer 104. In one or more embodiments, the openings 302 are formed using a standard lithographic patterning and etching process. In a standard lithographic patterning process, a light sensitive polymer, called a photoresist, is exposed and developed to transfer a three-dimensional relief image, referred to as a hard mask, onto the upper surface of the wafer; in this case, the upper surface of the dielectric layer 202. The wafer is then etched so that areas/layers of the wafer not protected by the hard mask are removed; a depth of the etching will be a function of one or characteristics, such as the type etchant used, the type(s) of material(s) being etched and the length of time that the wafer is exposed to the etchant, among other factors. Etching may be achieved using reactive ion etching (RIE), although other etching methodologies are similarly contemplated (e.g., plasma etch, a wet etch (e.g., hydrofluoric (HF) acid), etc.). One or more layers of the structure may serve as an etch-stop layer, particularly when a selective etchant is employed. Although embodiments of the invention are not limited to a particular etchant, a selective etchant is preferably utilized which is not reactive with the active device layer 106.

[0031] In this illustrative embodiment, the openings 302 are oriented in a direction substantially perpendicular to a major axis direction of the fins 108. Areas in the active device layer 106 exposed through the openings 302 will form source/drain regions of the transistor structure 100 during a subsequent processing step, as will be described in conjunction with FIGS. 5A-5D.

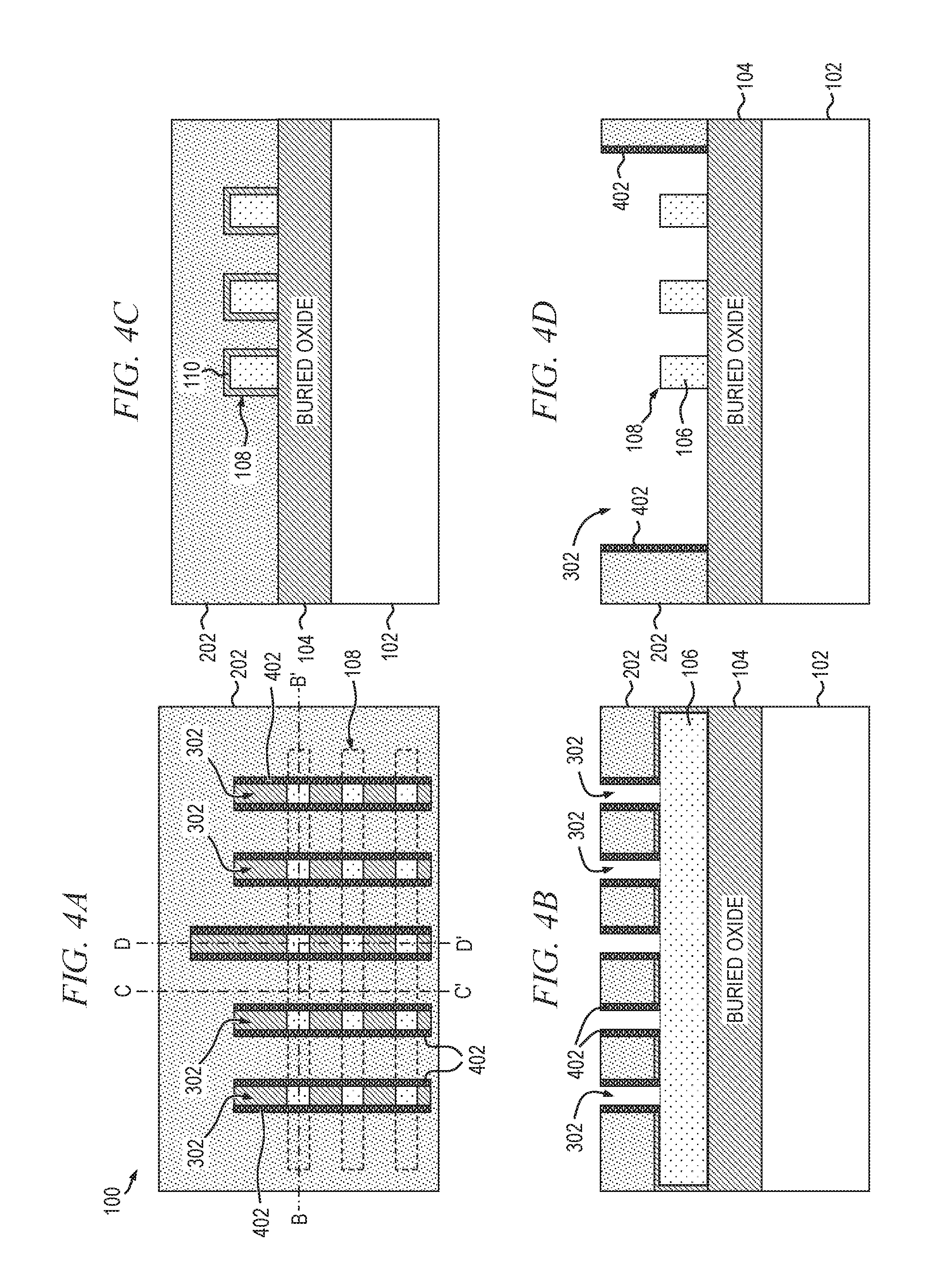

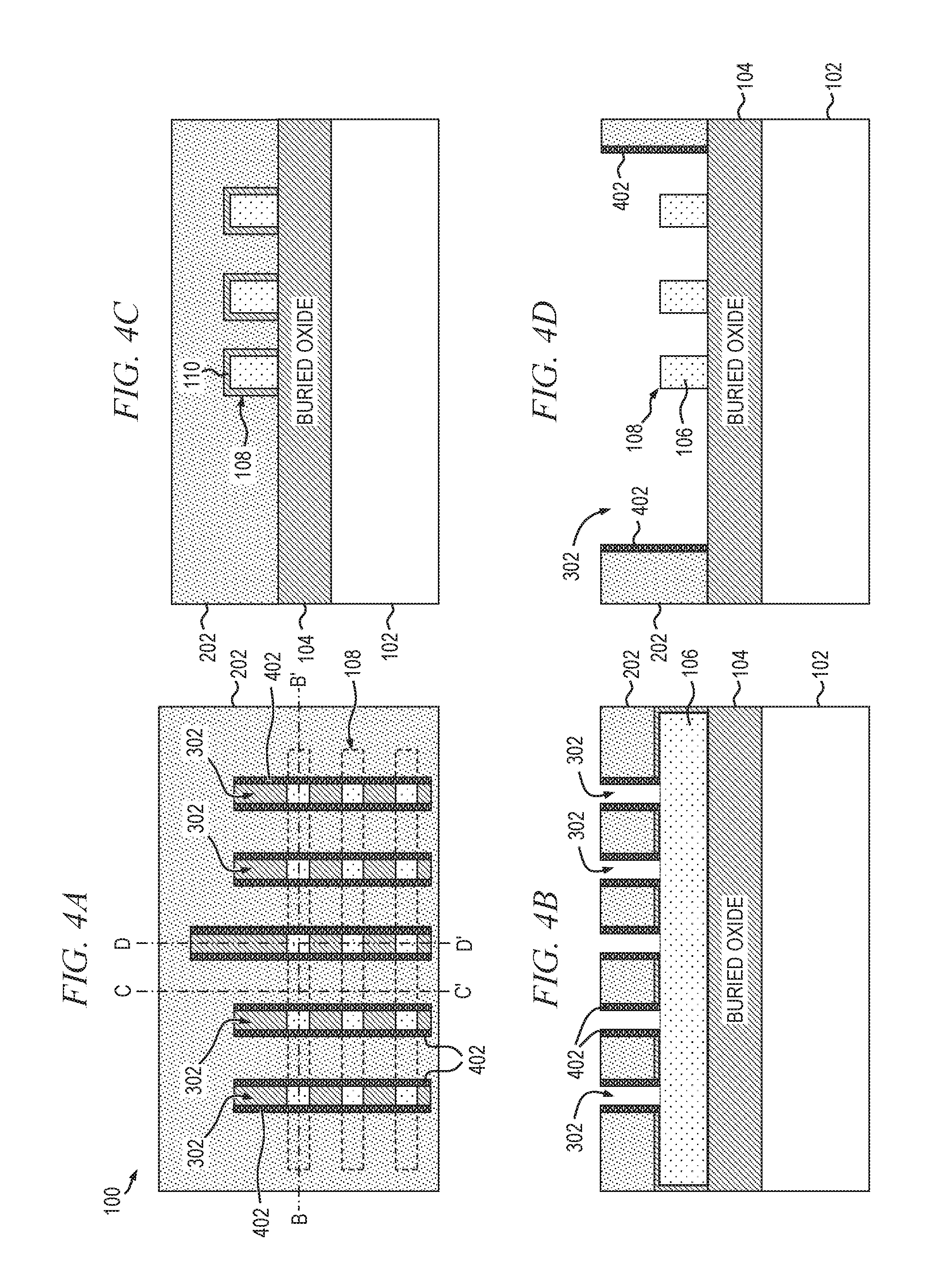

[0032] Prior to formation of heavily-doped source/drain regions in the transistor structure 100, dielectric spacers 402 are formed on sidewalls of the openings 302, as shown in FIGS. 4A through 4D; FIG. 4A is a top plan view of at least a portion of the exemplary MOS transistor structure 100, FIG. 4B is a cross-sectional view of the illustrative structure 100 shown in FIG. 4A taken along line B-B', FIG. 4C is a cross-sectional view of the illustrative structure 100 shown in FIG. 4A taken along line C-C', and FIG. 4D is a cross-sectional view of the illustrative structure 100 shown in FIG. 4A taken along line D-D'. The sidewall spacers 402, in one or more embodiments, are formed by chemical vapor deposition (CVD) of silicon dioxide from a low-density plasma source created within a reaction chamber. Other methods and materials for forming the sidewall spacers are contemplated in alternative embodiments (e.g., atomic layer deposition (ALD of titanium oxide). The sidewall spacers 402 may be optionally formed to reduce parasitic overlap capacitance (C.sub.ov).

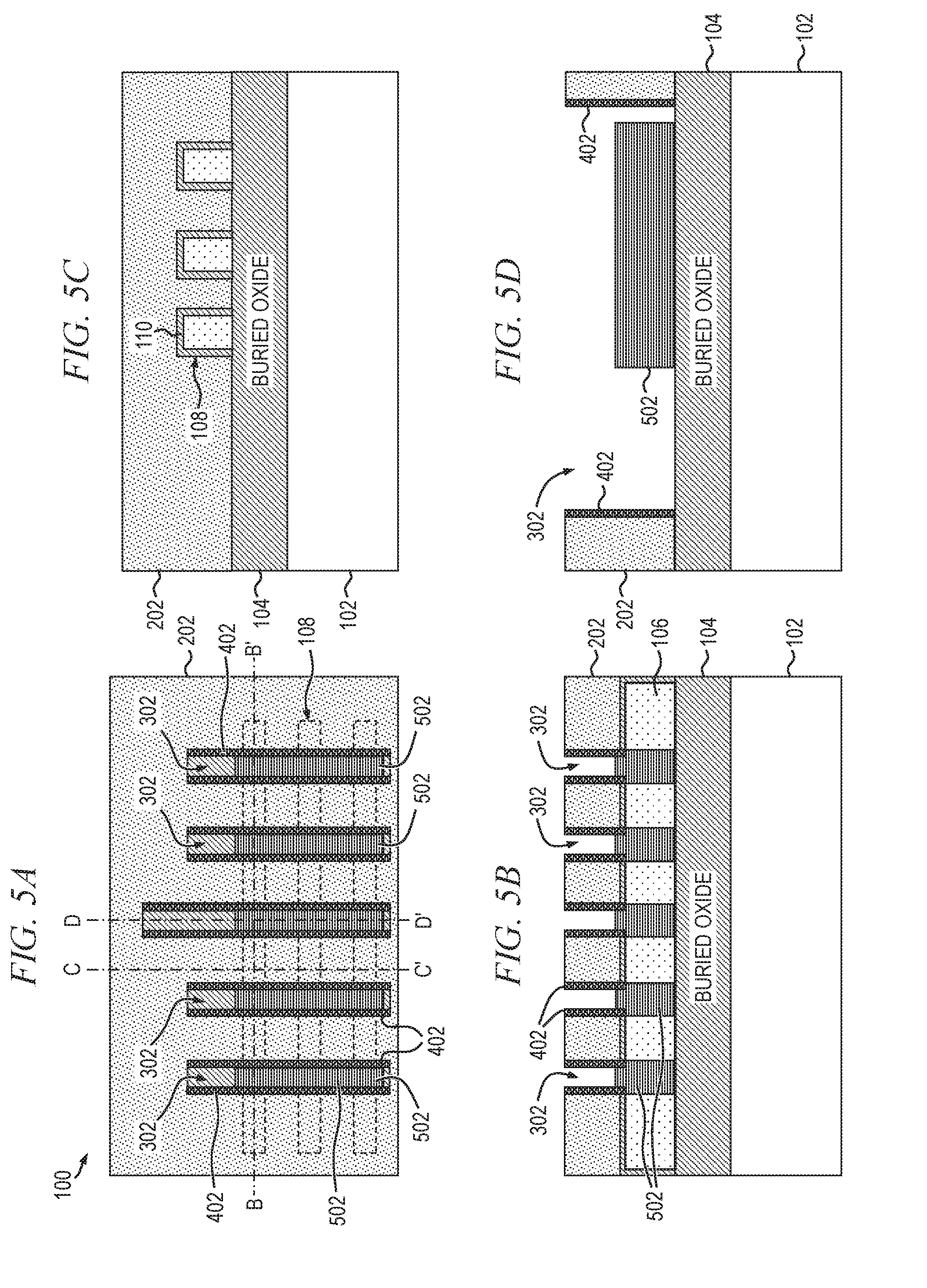

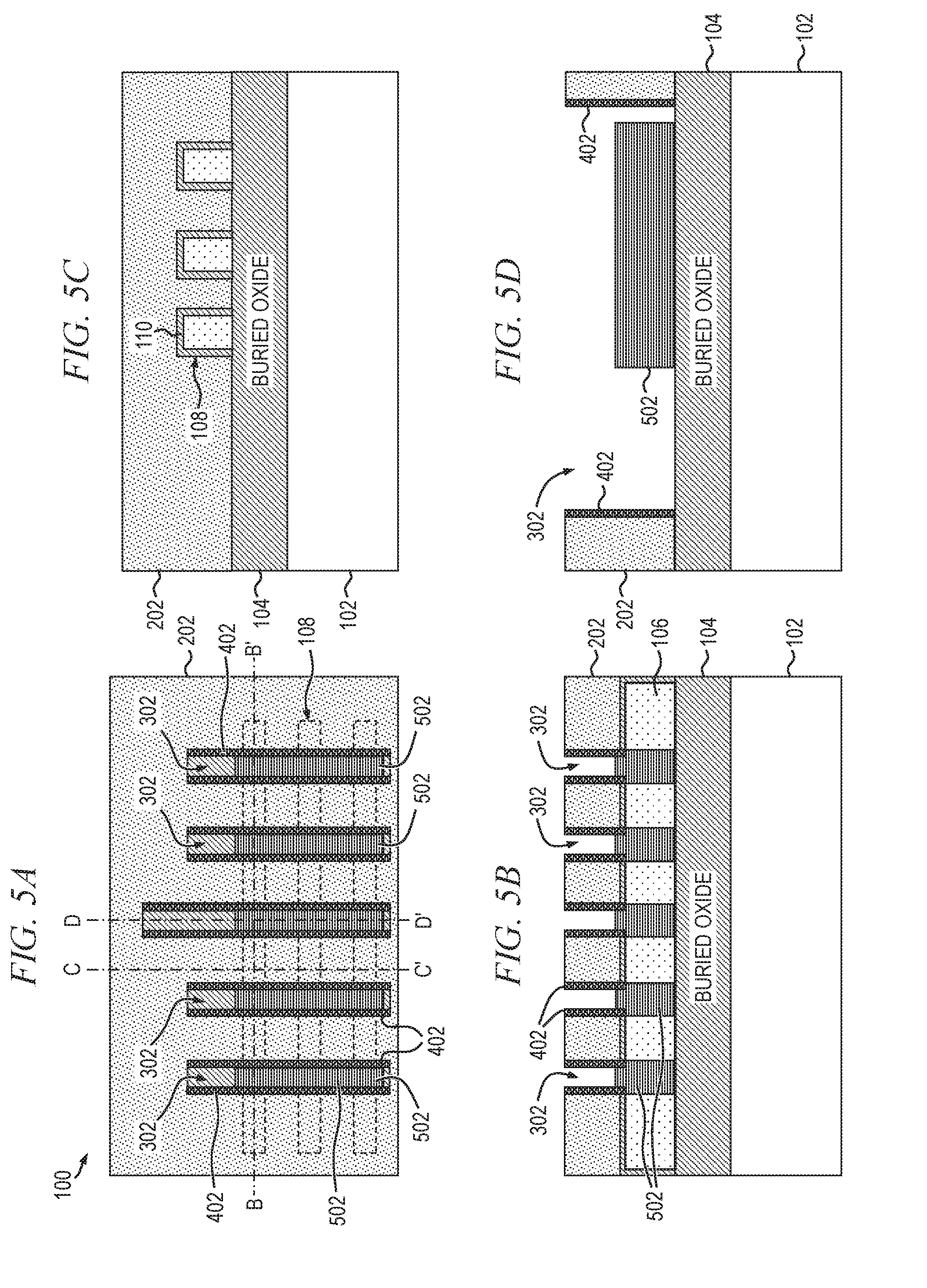

[0033] FIGS. 5A through 5D depict the formation of source/drain regions in the transistor structure 100, according to an embodiment of the invention; FIG. 5A is a top plan view of at least a portion of the exemplary MOS transistor structure 100, FIG. 5B is a cross-sectional view of the illustrative structure 100 shown in FIG. 5A taken along line B-B', FIG. 5C is a cross-sectional view of the illustrative structure 100 shown in FIG. 5A taken along line C-C', and FIG. 5D is a cross-sectional view of the illustrative structure 100 shown in FIG. 5A taken along line D-D'. With reference to FIGS. 5A-5D, source/drain regions 502 are formed in at least a portion of the openings 302 covering the fins 108 using, for example, an epitaxial growth process, such as, for example, chemical vapor deposition (CVD), molecular beam epitaxy (MBE), or metal organic chemical vapor deposition (MOCVD) epitaxy, etc., the fins 108 passing orthogonally through the source/drain regions 502 in one or more embodiments.

[0034] The source/drain regions 502, in one or more embodiments, are doped during epitaxial deposition by adding impurities to the source gas, such as arsine, phosphine or diborane, depending on the desired conductivity type of the source/drain regions. The concentration of impurity in the gas phase determines its concentration in the deposited epitaxial layer. An anneal process is used, in one or more embodiments, to drive the impurity into the source/drain regions 502, with the source/drain regions extending laterally in the active device layer 106 so as to have a width that is greater than a width of the openings 302, as shown more clearly in FIG. 5B. Forming the source/drain regions 502 in this manner, prior to formation of the gate, allows lower temperature source/drain epitaxy which beneficially facilitates the use of Group III-V materials, such as, for example, indium gallium arsenide (InGaAs), gallium arsenide (GaAs), indium phosphide (InP), etc., for the source/drain regions.

[0035] In one or more embodiments, contact metal 602, or an alternative conductive material, is then deposited in the openings 302, substantially filling the openings, as depicted in FIGS. 6A through 6D; FIG. 6A is a top plan view of at least a portion of the exemplary MOS transistor structure 100, FIG. 6B is a cross-sectional view of the illustrative structure 100 shown in FIG. 6A taken along line B-B', FIG. 6C is a cross-sectional view of the illustrative structure 100 shown in FIG. 6A taken along line C-C', and FIG. 6D is a cross-sectional view of the illustrative structure 100 shown in FIG. 6A taken along line D-D'. The contact metal 602, which may be formed using a deposition process (e.g., physical vapor deposition (PVD)), is in electrical connection with the underlying source/drain regions 502. Suitable materials for forming the contact metal 602 include, but are not limited to, titanium (Ti), titanium nitride (TiN), tungsten (W), etc.

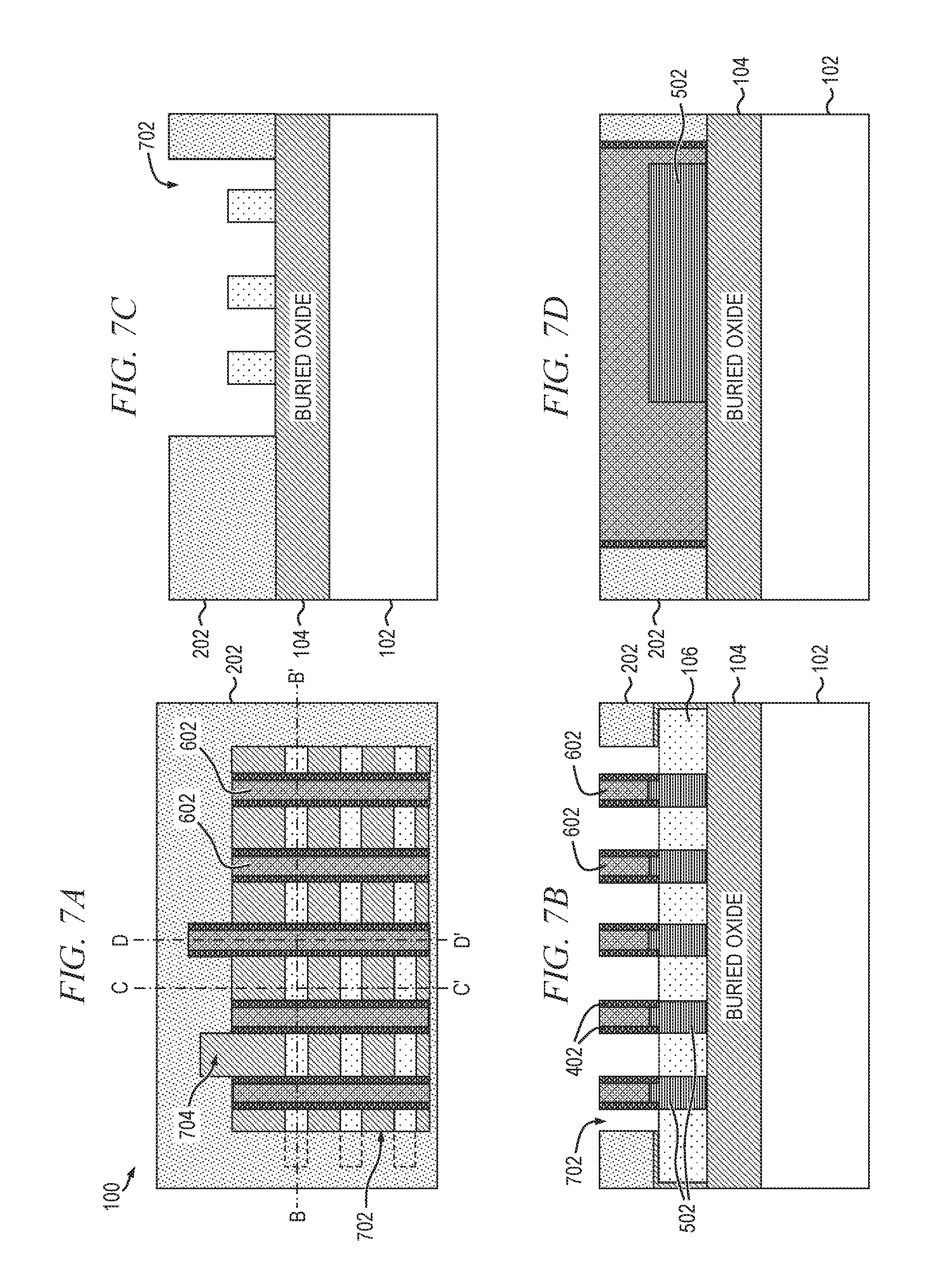

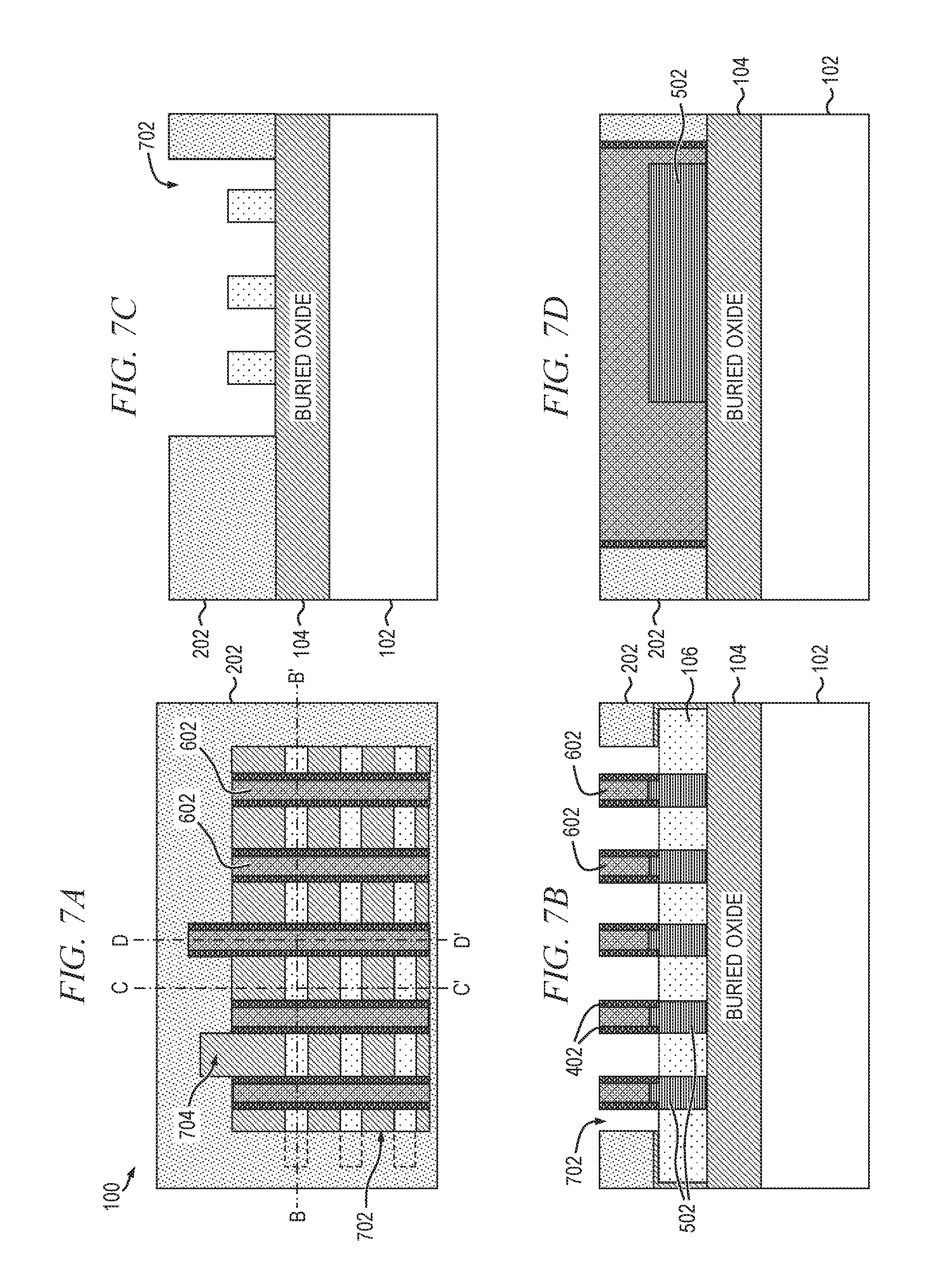

[0036] Once the source/drain regions 502 and contact metal 602 are formed, a plurality of gates are patterned and etched in the transistor 100, according to one or more embodiments of the invention, as shown in FIGS. 7A through 7D, where FIG. 7A is a top plan view of at least a portion of the exemplary MOS transistor structure 100, FIG. 7B is a cross-sectional view of the illustrative structure 100 shown in FIG. 7A taken along line B-B', FIG. 7C is a cross-sectional view of the illustrative structure 100 shown in FIG. 7A taken along line C-C', and FIG. 7D is a cross-sectional view of the illustrative structure 100 shown in FIG. 7A taken along line D-D'. With reference now to FIGS. 7A-7D, in forming the gates, an opening or trench 702 is formed through the dielectric layer 202 by patterning an area extending beyond the source/drain regions 502 and selectively etching the patterned area so as to expose the underlying active device layer 106 between adjacent source/drain regions. The etchant is selected so as to be non-reactive with the sidewall spacers 402 and contact metal 602, such that the sidewall spacers and contact metal are left intact. The gates of the transistor 100 will ultimately be formed in the areas between adjacent source/drain regions 502.

[0037] Optionally, in one or more embodiments, the patterned boundary defined by the opening or trench 702 may be extended in one or more areas, such as represented by extended area 704. This extended area 704 facilitates the formation of an enlarged gate configured to make contact to the gate outside of the device area where needed. It is to be appreciated that the dimensions and/or shape of the extended area 704 are not limited, according to embodiments of the invention. Area 704 can also be included for each gate.

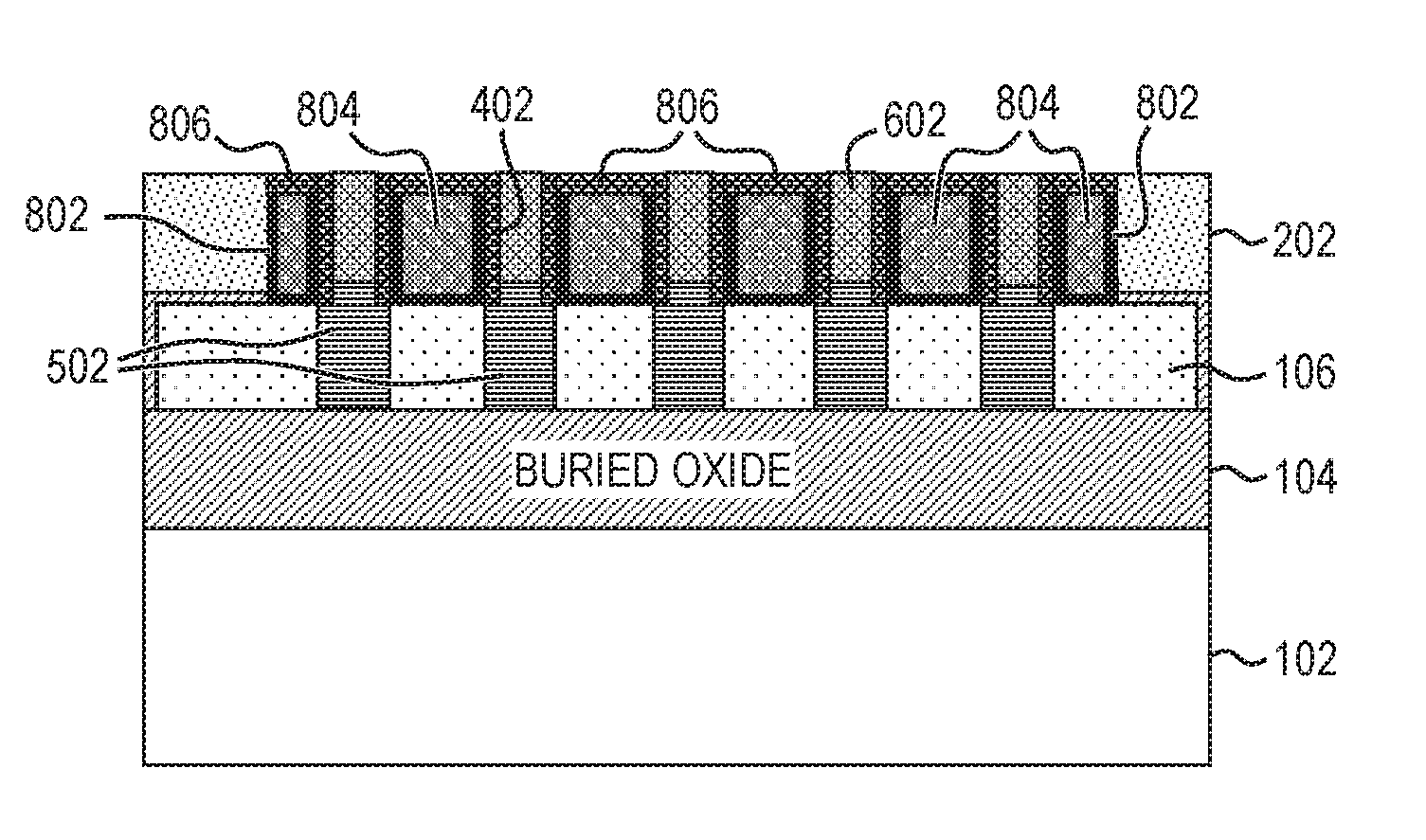

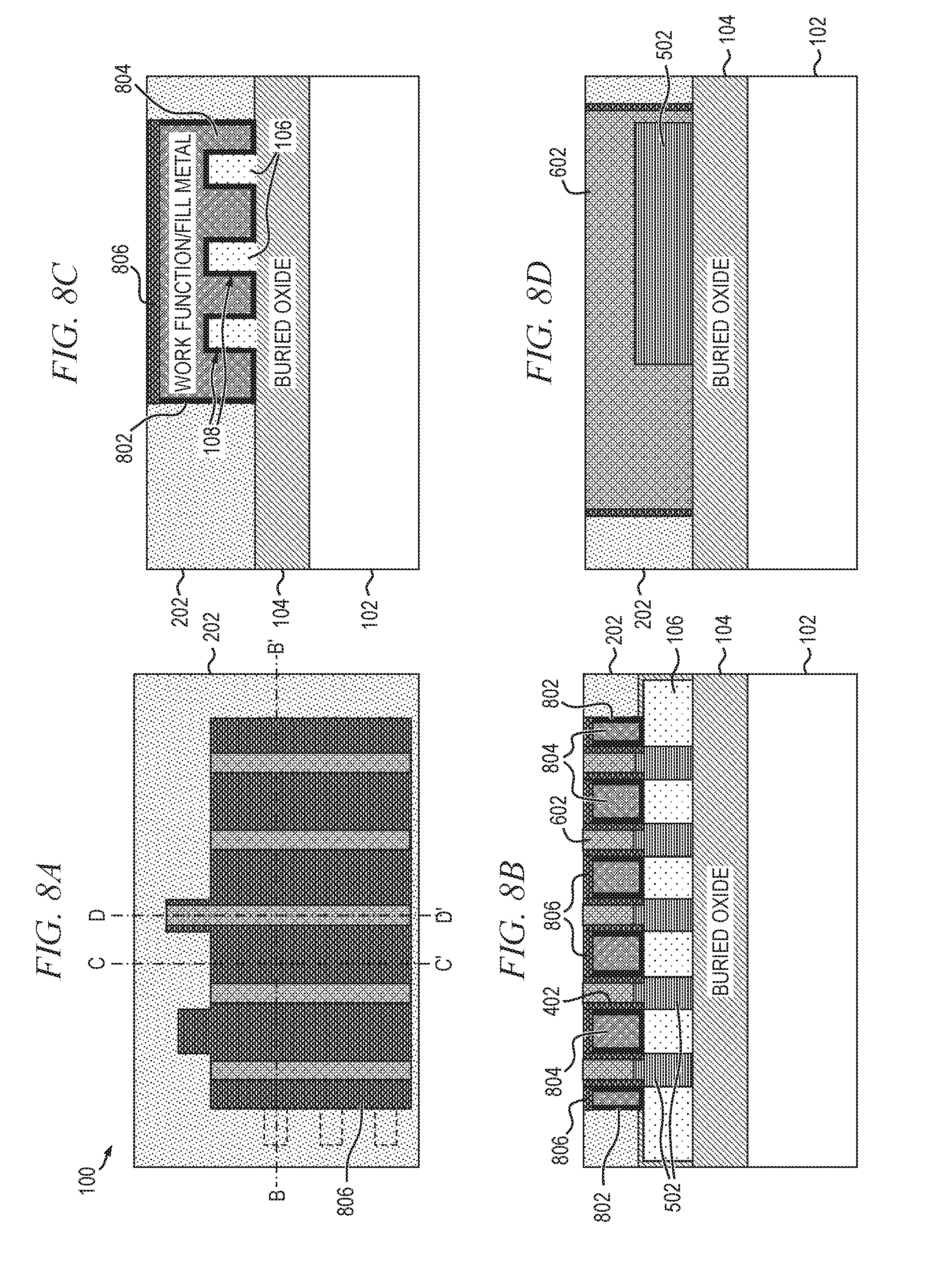

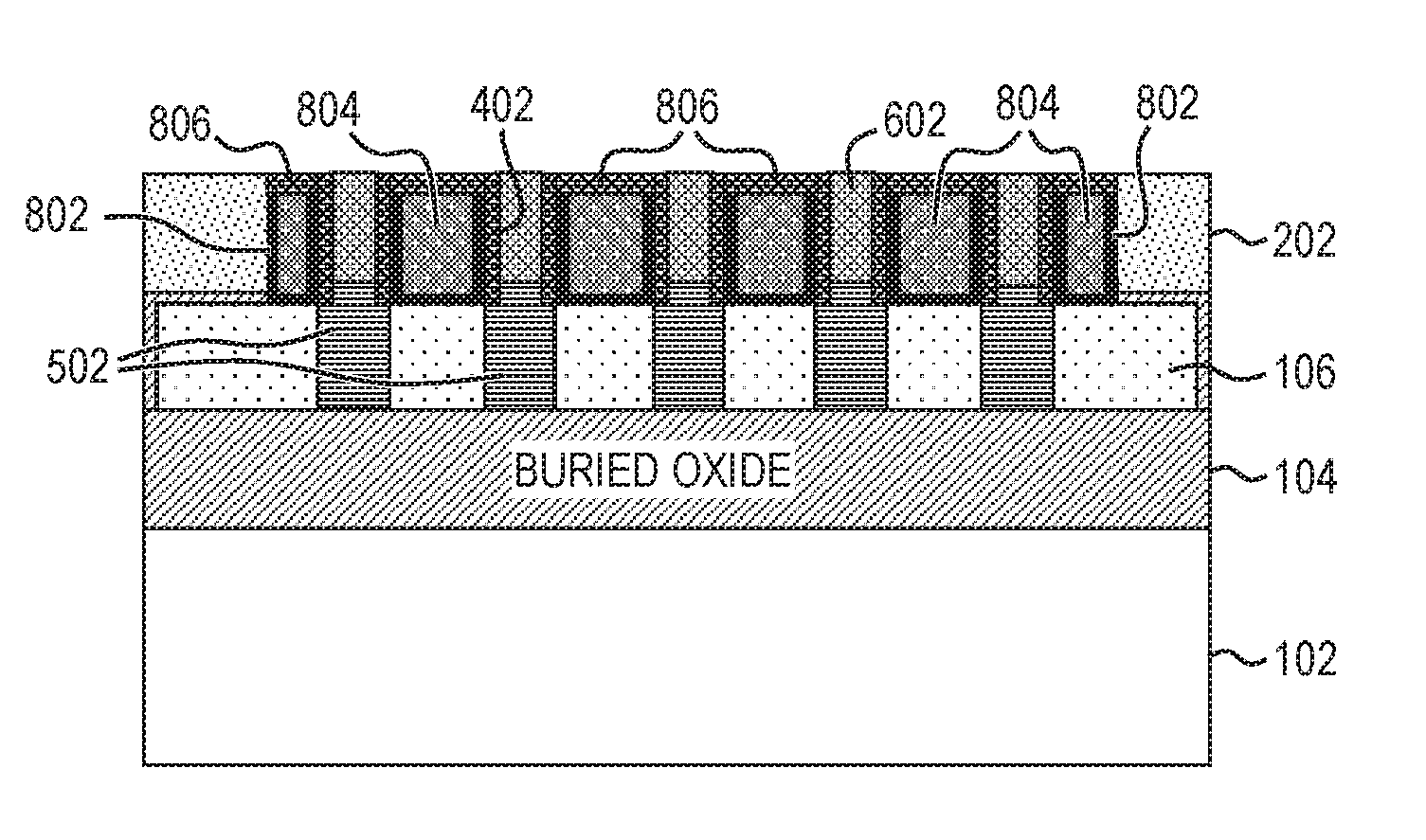

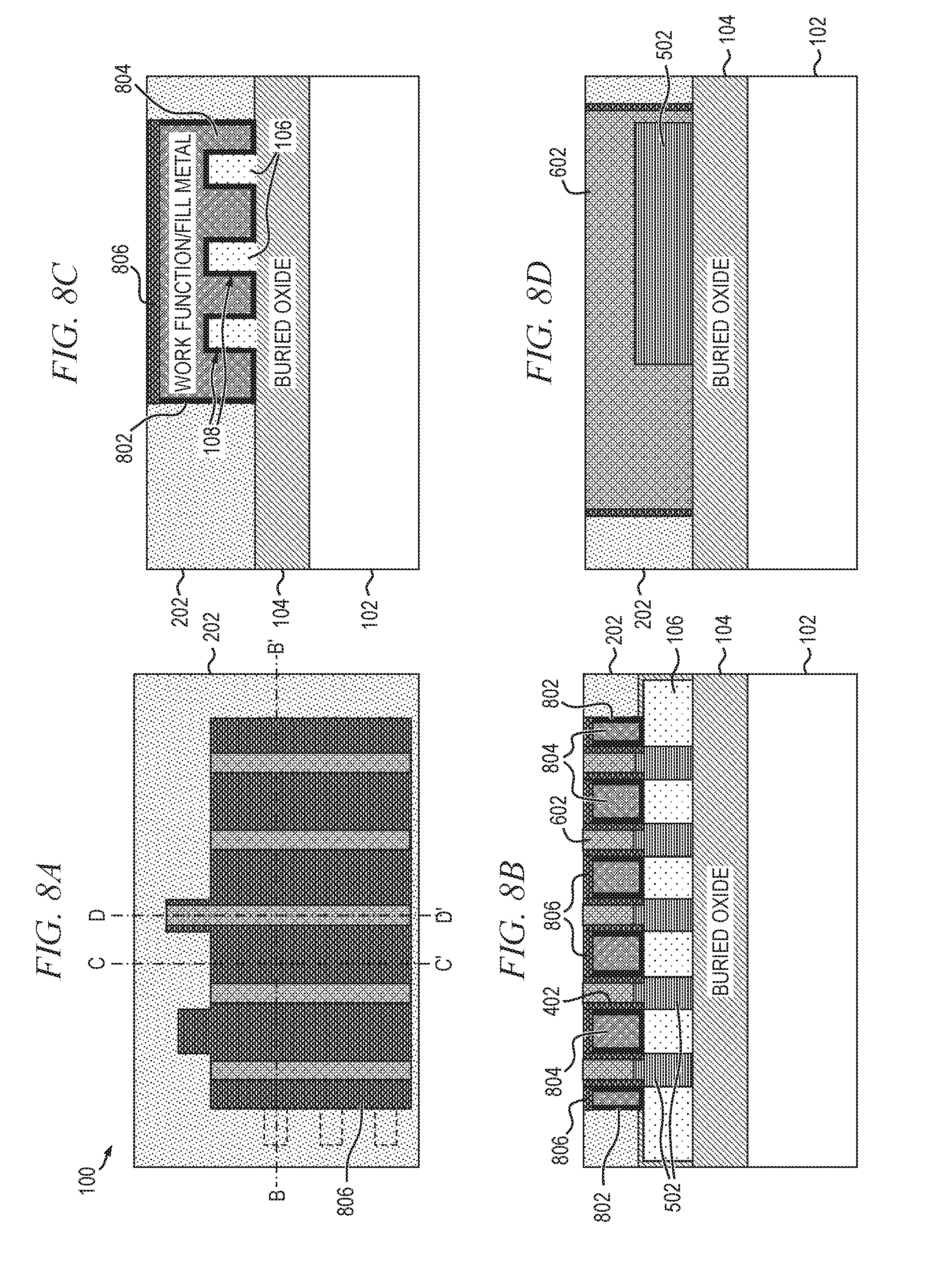

[0038] FIGS. 8A through 8D depict the formation of gate structures in the transistor 100, according to an embodiment of the invention; FIG. 8A is a top plan view of at least a portion of the exemplary MOS transistor structure 100, FIG. 8B is a cross-sectional view of the illustrative structure 100 shown in FIG. 8A taken along line B-B', FIG. 8C is a cross-sectional view of the illustrative structure 100 shown in FIG. 8A taken along line C-C', and FIG. 8D is a cross-sectional view of the illustrative structure 100 shown in FIG. 8A taken along line D-D'. Specifically, in one or more embodiments a high-k dielectric layer 802 is deposited in at least a portion of the opening 702, including on sidewalls of the opening, sidewalls of the spacers 402, an upper surface of the active device layer 106 which is exposed through the opening 702, an upper surface of the buried oxide layer 104 exposed through the opening 702, and sidewalls and a top surface of the fin structures 108 exposed through the opening. The high-k dielectric layer 802 thus forms an insulating barrier lining the openings between adjacent source/drain contact metal structures 602. This dielectric layer 802 will form a gate oxide layer electrically isolating the gate from the underlying active device layer 106.

[0039] The dielectric layer 802, in one or more embodiments, is formed using a deposition process, such as, for example, atomic layer deposition (ALD), although other means for forming the dielectric layer 802 are similarly contemplated, including, but not limited to, oxide growth, plasma deposition, etc. In one or more embodiments, a cross-sectional thickness of the dielectric layer 802 is about 1-3 nm, although embodiments of the invention are not limited to any particular thickness of the dielectric layer.

[0040] Once the dielectric layer 802 has been formed, the opening 702 is filled with a conductive material to form a gate stack 804. The gate stack 804, in one or more embodiments, comprises a metallic compound, such as, for example, atomic layer deposition (ALD) of a metallic compound (e.g., titanium nitride (TiN), tantalum nitride (TaN), titanium aluminum nitride (TiAlN), tantalum aluminum nitride (TaAlN), titanium silicon nitride (TiSiN), tungsten aluminum nitride (WAlN), etc.) configured to provide a prescribed work function. In other words, the composition of the material(s) used to form the gate stack 804 are "tuned," in one or more embodiments, to provide a desired work function.

[0041] The gate stack 804 is formed, in one or more embodiments, using a deposition process, such as, for example, atomic layer deposition (ALD), plasma deposition, CVD, or the like. Gate stack 804, in one or more embodiments, may comprise multiple metal layers. A hard mask 806 may be formed over the gate stack 804 which serves as a protection layer for the gate if contact to source drain are needed. The hard mask 806 may, in one or more embodiments, be formed of the same material as the sidewall spacers 402, although the invention is not limited to any particular material. It is to be appreciated that since the gate stack 804 of the transistor structure 100 is formed after formation of source/drain regions 502 in the device, self-alignment of the gate using the source/drain regions is performed.

[0042] Given the discussion thus far, it will be appreciated that, in general terms, an exemplary method for fabricating a transistor structure includes: forming an active device layer on a semiconductor substrate, the active device layer having a prescribed conductivity type associated therewith; patterning the active device layer to form a plurality of fins; forming a first dielectric layer on at least a portion of an upper surface and sidewalls of the plurality of fins; forming a second dielectric layer on at least a portion of an upper surface of the first dielectric layer; forming a first plurality of openings through the second dielectric layer and the first dielectric layer, exposing the underlying active device layer forming the plurality of fins; forming a plurality of source/drain regions in the active device layer exposed through the respective first plurality of openings; forming a plurality of source/drain contacts on an upper surface of each of the plurality of source/drain regions; forming a second opening through the second dielectric layer and the first dielectric layer, the second opening exposing the underlying active device layer adjacent to the plurality of source/drain regions; depositing a third dielectric layer in at least a portion of the second opening, including on sidewalls of the second opening and sidewalls and an upper surface of the plurality of fins; and forming a gate stack on the third dielectric layer, the gate stack being self-aligned with the plurality of source/drain regions.

[0043] Given the discussion thus far, it will be appreciated that, in general terms, an exemplary gate-last transistor structure fabricated using negative-tone resolution enhancement techniques includes an active device layer formed on an upper surface of a substrate, the active device layer patterned to form a plurality of fins, a plurality of source/drain regions formed in the active device layer, the fins passing through the source/drain regions, and a plurality of source/drain contacts formed on upper surfaces of the plurality of source/drain regions for providing electrical connection to the respective source/drain regions. The transistor structure further includes a plurality of gate structures formed between adjacent source/drain regions, the gate structures being electrically isolated from the active device layer by a gate dielectric layer formed between the active device layer and the respective gate structures. The gate structures being formed subsequent to forming the source/drain regions and are self-aligned with the source/drain regions. Each of at least a subset of the gate structures are confined between a pair of adjacent source/drain contacts proximate a gate region where contact to the gate structure is formed.

[0044] At least a portion of the methods and apparatus described above may be implemented in an integrated circuit. In forming integrated circuits, identical dies are typically fabricated in a repeated pattern on a surface of a semiconductor wafer. Each die includes a device described herein, and may include other structures and/or circuits. The individual dies are cut or diced from the wafer, then packaged as an integrated circuit. One skilled in the art would know how to dice wafers and package die to produce integrated circuits.

[0045] Those skilled in the art will appreciate that the exemplary structures discussed above can be distributed in raw form (i.e., a single wafer having multiple unpackaged chips), as bare dies, in packaged form, or incorporated as parts of intermediate products or end products that benefit from having transistor or other active semiconductor devices formed in accordance with one or more of the exemplary embodiments.

[0046] The illustrations of embodiments described herein are intended to provide a general understanding of the various embodiments, and they are not intended to serve as a complete description of all the elements and/or features of methods and apparatus that might make use of the structures and techniques described herein. Many other embodiments will become apparent to those skilled in the art given the teachings herein; other embodiments are utilized and derived therefrom, such that structural and logical substitutions and changes can be made without departing from the scope of this disclosure. It should also be noted that, in some alternative implementations, some of the steps of exemplary methods described herein may occur out of the order described or noted in the figures (where shown). For example, two steps described or shown in succession may, in fact, be executed substantially concurrently, or certain steps may sometimes be executed in the reverse order, depending upon the functionality involved. The drawings are also merely representational and are not drawn to scale. Accordingly, the specification and drawings are to be regarded in an illustrative rather than a restrictive sense.

[0047] Embodiments are referred to herein, individually and/or collectively, by the term "embodiment" merely for convenience and without intending to limit the scope of this application to any single embodiment or inventive concept if more than one is, in fact, shown. Thus, although specific embodiments have been illustrated and described herein, it should be understood that an arrangement achieving the same purpose can be substituted for the specific embodiment(s) shown; that is, this disclosure is intended to cover any and all adaptations or variations of various embodiments. Combinations of the above embodiments, and other embodiments not specifically described herein, will become apparent to those of skill in the art given the teachings herein.

[0048] The terminology used herein is for the purpose of describing particular embodiments only and is not intended to be limiting. As used herein, the singular forms "a," "an" and "the" are intended to include the plural forms as well, unless the context clearly indicates otherwise. It will be further understood that the terms "comprises" and/or "comprising," when used in this specification, specify the presence of stated features, steps, operations, elements, and/or components, but do not preclude the presence or addition of one or more other features, steps, operations, elements, components, and/or groups thereof. Terms such as "above" and "below," where used, are intended to indicate positioning of elements or structures relative to each other as opposed to absolute elevation.

[0049] The corresponding structures, materials, acts, and equivalents of any means or step-plus-function elements in the claims below are intended to include any structure, material, or act for performing the function in combination with other claimed elements as specifically claimed. The description of the various embodiments has been presented for purposes of illustration and description, but is not intended to be exhaustive or limited to the forms disclosed. Many modifications and variations will be apparent to those of ordinary skill in the art without departing from the scope and spirit thereof. The embodiments were chosen and described in order to best explain principles and practical applications, and to enable others of ordinary skill in the art to understand the various embodiments with various modifications as are suited to the particular use contemplated.

[0050] The abstract is provided to comply with 37 C.F.R. .sctn. 1.72(b), which requires an abstract that will allow the reader to quickly ascertain the nature of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or meaning of the claims. In addition, in the foregoing Detailed Description, it can be seen that various features are grouped together in a single embodiment for the purpose of streamlining the disclosure. This method of disclosure is not to be interpreted as reflecting an intention that the claimed embodiments require more features than are expressly recited in each claim. Rather, as the appended claims reflect, the claimed subject matter may lie in less than all features of a single embodiment. Thus the following claims are hereby incorporated into the Detailed Description, with each claim standing on its own as separately claimed subject matter.

[0051] Given the teachings provided herein, one of ordinary skill in the art will be able to contemplate other implementations and applications of the techniques and disclosed embodiments. Although illustrative embodiments have been described herein with reference to the accompanying drawings, it is to be understood that illustrative embodiments are not limited to those precise embodiments, and that various other changes and modifications are made therein by one skilled in the art without departing from the scope of the appended claims.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.