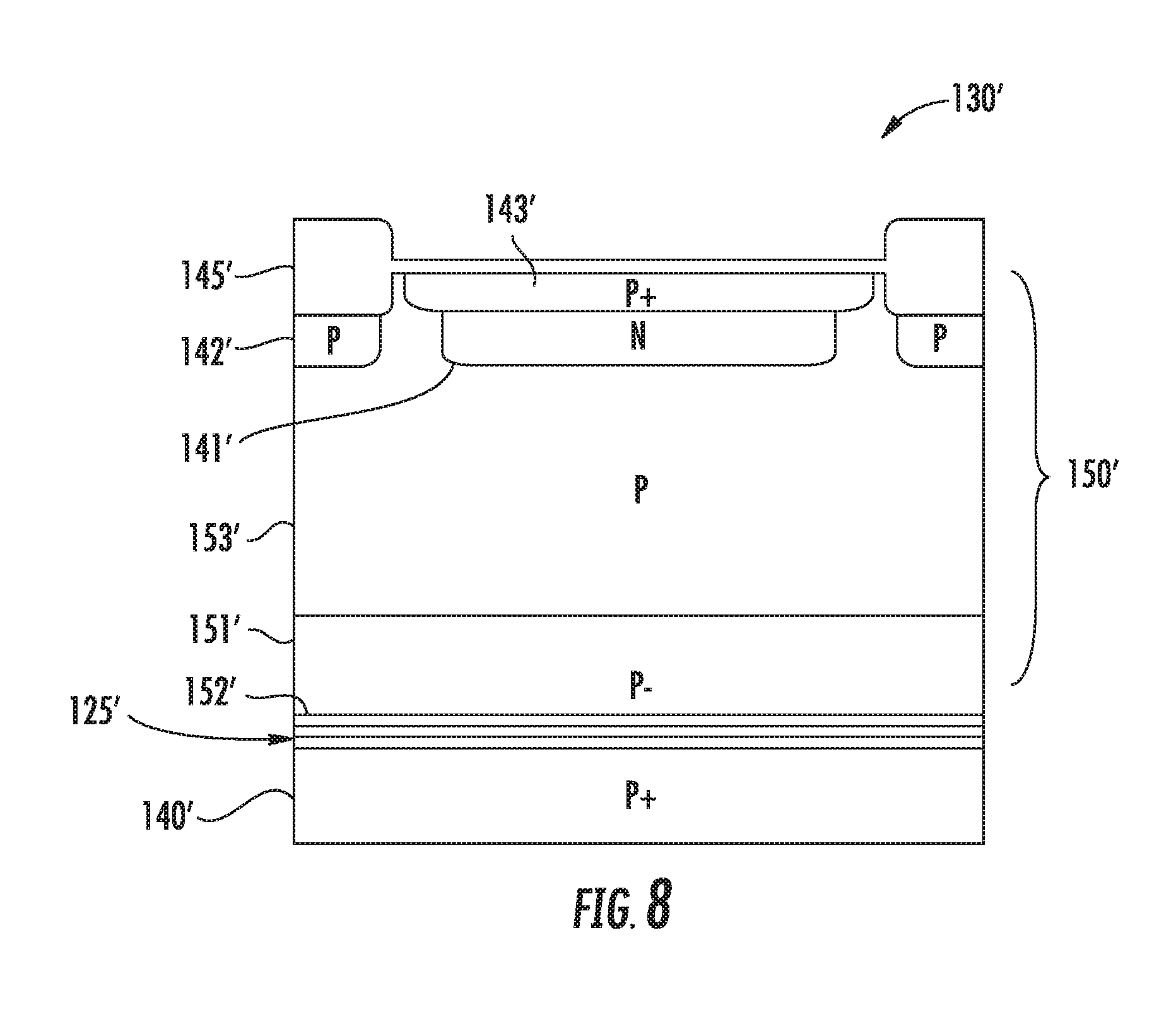

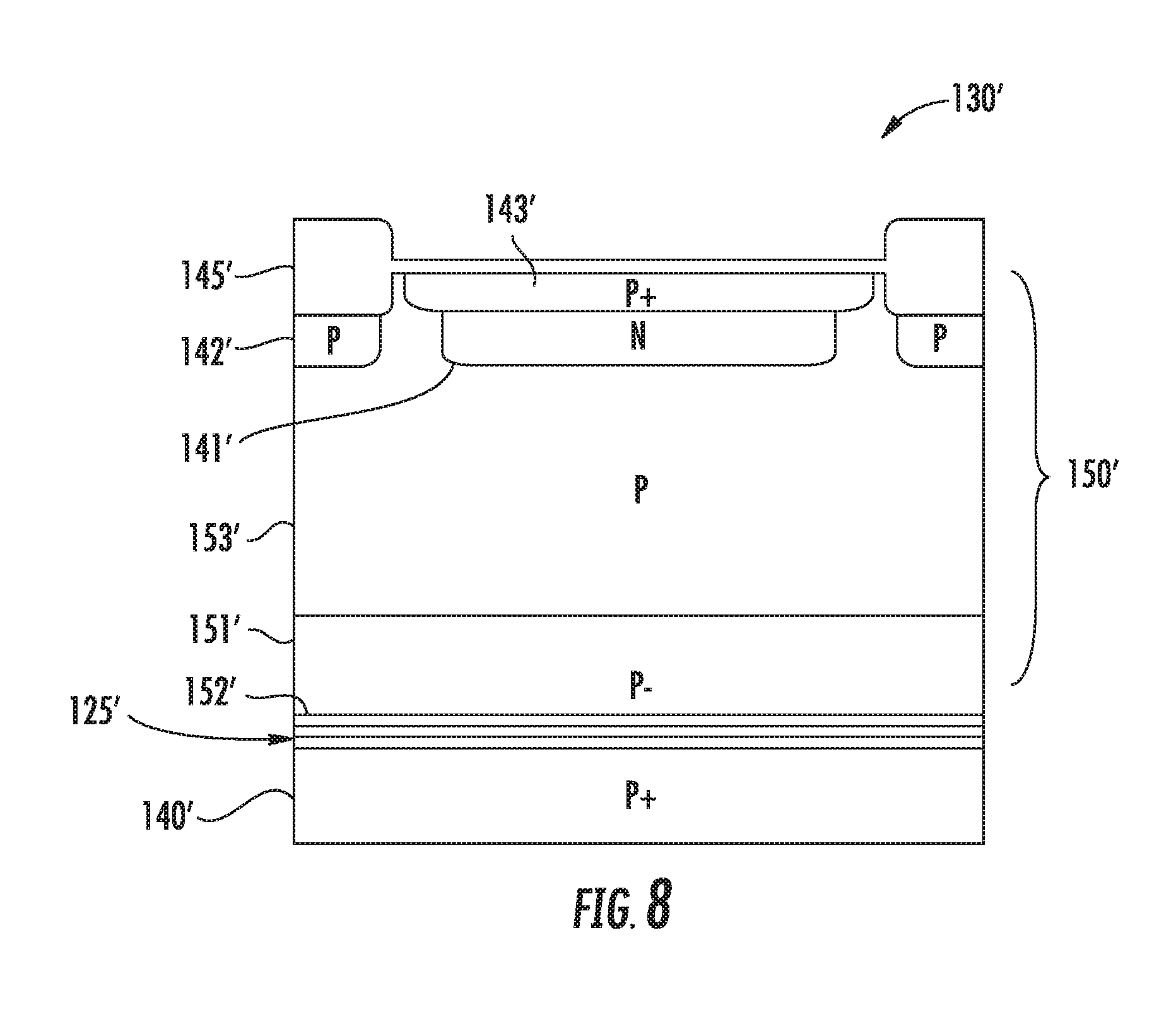

Cmos Image Sensor With Buried Superlattice Layer To Reduce Crosstalk

CHEN; YI-ANN ; et al.

U.S. patent application number 15/843106 was filed with the patent office on 2019-06-20 for cmos image sensor with buried superlattice layer to reduce crosstalk. The applicant listed for this patent is Atomera Incorporated. Invention is credited to YI-ANN CHEN, Abid Husain, Hideki Takeuchi.

| Application Number | 20190189652 15/843106 |

| Document ID | / |

| Family ID | 66636429 |

| Filed Date | 2019-06-20 |

View All Diagrams

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

D00009

D00010

D00011

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.