Qubit-detector Die Assemblies

Roberts; Jeanette M. ; et al.

U.S. patent application number 16/328670 was filed with the patent office on 2019-06-13 for qubit-detector die assemblies. This patent application is currently assigned to Intel Corporation. The applicant listed for this patent is Intel Corporation. Invention is credited to James S. Clarke, Hubert C. George, Ravi Pillarisetty, Jeanette M. Roberts, Nicole K. Thomas.

| Application Number | 20190181256 16/328670 |

| Document ID | / |

| Family ID | 61690606 |

| Filed Date | 2019-06-13 |

View All Diagrams

| United States Patent Application | 20190181256 |

| Kind Code | A1 |

| Roberts; Jeanette M. ; et al. | June 13, 2019 |

QUBIT-DETECTOR DIE ASSEMBLIES

Abstract

Disclosed herein are qubit-detector die assemblies, as well as related computing devices and methods. In some embodiments, a die assembly may include: a first die having a first face and an opposing second face, wherein a plurality of active qubit devices are disposed at the first face of the first die; and a second die, mechanically coupled to the first die, having a first face and an opposing second face, wherein a plurality of quantum state detector devices are disposed at the first face of the second die; wherein the first faces of the first and second dies face each other.

| Inventors: | Roberts; Jeanette M.; (North Plains, OR) ; Pillarisetty; Ravi; (Portland, OR) ; Thomas; Nicole K.; (Portland, OR) ; George; Hubert C.; (Portland, OR) ; Clarke; James S.; (Portland, OR) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Assignee: | Intel Corporation Santa Clara CA |

||||||||||

| Family ID: | 61690606 | ||||||||||

| Appl. No.: | 16/328670 | ||||||||||

| Filed: | September 24, 2016 | ||||||||||

| PCT Filed: | September 24, 2016 | ||||||||||

| PCT NO: | PCT/US2016/053607 | ||||||||||

| 371 Date: | February 26, 2019 |

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 29/165 20130101; H01L 29/775 20130101; H01L 2224/05567 20130101; H01L 2224/0401 20130101; H01L 2224/16145 20130101; H01L 2224/16225 20130101; H01L 29/7613 20130101; H01L 2224/06155 20130101; B82Y 10/00 20130101; H01L 24/19 20130101; H01L 29/127 20130101; H01L 25/117 20130101; H01L 24/18 20130101; H01L 2224/131 20130101; H01L 29/0673 20130101; H01L 25/18 20130101; H01L 2224/16237 20130101; H01L 23/3107 20130101; H01L 2224/16147 20130101; H01L 24/05 20130101; H01L 29/66 20130101; H01L 29/66977 20130101; H01L 29/42376 20130101; H01L 2224/06154 20130101; H01L 29/423 20130101; H01L 24/16 20130101; H01L 25/16 20130101; H01L 24/20 20130101; H01L 29/12 20130101; H01L 24/17 20130101; H01L 2224/18 20130101; H01L 21/568 20130101; H01L 24/06 20130101; H01L 25/50 20130101; H01L 2224/18 20130101; H01L 2924/0001 20130101; H01L 2224/131 20130101; H01L 2924/014 20130101; H01L 2924/00014 20130101 |

| International Class: | H01L 29/76 20060101 H01L029/76; H01L 29/12 20060101 H01L029/12; H01L 25/11 20060101 H01L025/11; H01L 25/00 20060101 H01L025/00; H01L 29/423 20060101 H01L029/423; H01L 29/775 20060101 H01L029/775; H01L 29/06 20060101 H01L029/06 |

Claims

1. A die assembly, comprising: a first die having a first face and an opposing second face, wherein a plurality of active qubit devices are disposed at the first face of the first die; and a second die, mechanically coupled to the first die, having a first face and an opposing second face, wherein a plurality of quantum state detector devices are disposed at the first face of the second die; wherein the first face of the first die is disposed between the second face of the first die and the first face of the second die, and the first face of the second die is disposed between the second face of the second die and the first face of the first die.

2. The die assembly of claim 1, wherein a distance between the first face of the first die and the first face of the second die is between 50 and 250 nanometers.

3. The die assembly of claim 1, wherein the first and second dies are mechanically coupled with an adhesive disposed between the first face of the first die and the first face of the second die.

4. The die assembly of claim 1, wherein the first and second dies are mechanically coupled with solder disposed between the first face of the first die and the first face of the second die.

5. The die assembly of claim 1, wherein the second die is electrically coupled to the first die.

6. The die assembly of claim 1, wherein the active qubit devices or the quantum state detector devices include: a quantum well stack including a quantum well layer, a doped layer, and a barrier layer disposed between the doped layer and the quantum well layer; a plurality of first gates disposed above the quantum well stack, wherein at least two of the first gates are spaced apart in a first dimension above the quantum well stack, at least two of the first gates are spaced apart in a second dimension above the quantum well stack, and the first and second dimensions are perpendicular; and a material disposed above the quantum well stack, wherein the material extends between at least two of the first gates spaced apart in the first dimension, and the material extends between at least two of the first gates spaced apart in the second dimension.

7. The die assembly of claim 6, wherein the material is a gate metal for a second gate.

8. The die assembly of claim 6, wherein the material is an insulating material.

9. The die assembly of claim 6, wherein the plurality of first gates are arranged in an n.times.m array, n is greater than 1, and m is greater than 1.

10. The die assembly of claim 1, wherein the active qubit devices or the quantum state detector devices include a single electron transistor (SET).

11. The die assembly of claim 10, wherein the SET includes: first and second insulating supports; first and second source/drain (S/D) electrodes, wherein the first S/D electrode is disposed on a side face of the first insulating support and the second S/D electrode is disposed on a side face of the second insulating support; an island, disposed between the first and second S/D electrodes and extending into an area between the first and second insulating supports; and first and second portions of a dielectric, wherein the first portion of the dielectric is disposed between the first S/D electrode and the island, and the second portion of the dielectric is disposed between the second S/D electrode and the island.

12. The die assembly of claim 11, wherein the first and second S/D electrodes are disposed on a substrate, and another portion of the dielectric is disposed between the substrate and the island.

13. The die assembly of claim 12, wherein the SET further includes: a third insulating support; and a gate electrode of the SET disposed on a side face of the third insulating support.

14. The die assembly of claim 11, wherein the SET is a first SET, the island is a first island, the side face of the first insulating support is a first side face of the first insulating support, the side face of the second insulating support is a first side face of the second insulating support, and the die assembly further includes: third and fourth S/D electrodes of a second SET, wherein the third S/D electrode is disposed on a second side face of the first insulating support and the fourth S/D electrode is disposed on a second side face of the second insulating support; a second island of the second SET, disposed between the third and fourth S/D electrodes and extending into the area between the first and second insulating supports; and third and fourth portions of the dielectric; wherein the third portion of the dielectric is disposed between the third S/D electrode and the second island, and the fourth portion of the dielectric is disposed between the fourth S/D electrode and the second island.

15. The die assembly of claim 10, wherein the SET includes: first and second source/drain (S/D) electrodes disposed on a substrate; an island disposed in an area between the first and second S/D electrodes; first and second portions of dielectric disposed between the first S/D electrode and the island and between the second S/D electrode and the island, respectively; and a third portion of dielectric disposed between the substrate and the island.

16. The die assembly of claim 1, wherein the active qubit devices and the quantum state detector devices are each drawn from a group consisting of single electron transistors (SETS) and gates disposed on quantum well stacks.

17. A method of manufacturing a quantum computing device, comprising: coupling a first die to a second die, wherein the first die includes a plurality of first devices at a first face of the first die, the second die includes a plurality of second devices at a first face of the second die, and the first faces of the first and second die face each other; and electrically coupling the second die to a support; wherein the first devices are active qubit devices and the second devices are quantum state detector devices, or the second devices are active qubit devices and the first devices are quantum state detector devices.

18. The method of claim 17, wherein the active qubit devices and the quantum state detector devices are each drawn from a group consisting of single electron transistors (SETS) and gates disposed on quantum well stacks.

19-23. (canceled)

24. A quantum computing device, comprising: a quantum processing device, wherein the quantum processing device includes a first die coupled to a second die, wherein the first die includes a plurality of active qubit devices disposed at a first face of the first die, the second die includes a plurality of quantum state detector devices disposed at a first face of the second die, and the first faces of the first and second dies face each other; a non-quantum processing device, coupled to the quantum processing device, to control electrical signals applied to the first die; and a memory device to store data generated by the second die during operation of the quantum processing device.

25. The quantum computing device of claim 24, further comprising: a communication chip communicatively coupled to the non-quantum processing device.

Description

CROSS-REFERENCE TO RELATED APPLICATION

[0001] This application is a national stage application under 35 U.S.C. .sctn. 371 of PCT International Application Serial No. PCT/US2016/053607, filed on Sep. 24, 2016 and entitled "QUBIT-DETECTOR DIE ASSEMBLIES," which is hereby incorporated by reference herein in its entirety.

BACKGROUND

[0002] Quantum computing refers to the field of research related to computation systems that use quantum mechanical phenomena to manipulate data. These quantum mechanical phenomena, such as superposition (in which a quantum variable can simultaneously exist in multiple different states) and entanglement (in which multiple quantum variables have related states irrespective of the distance between them in space or time), do not have analogs in the world of classical computing, and thus cannot be implemented with classical computing devices.

BRIEF DESCRIPTION OF THE DRAWINGS

[0003] Embodiments will be readily understood by the following detailed description in conjunction with the accompanying drawings. To facilitate this description, like reference numerals designate like structural elements. Embodiments are illustrated by way of example, and not by way of limitation, in the figures of the accompanying drawings.

[0004] FIGS. 1A, 1B, and 1C are cross-sectional views of an embodiment of a qubit-detector die assembly, in accordance with various embodiments.

[0005] FIGS. 2A, 2B, and 2C are cross-sectional views of an embodiment of a gate-stack device, in accordance with various embodiments.

[0006] FIGS. 3-5, 6A, 6B, 6C, 7-8, 9A, 9B, and 10-19 illustrate various example stages in the manufacture of the gate-stack device of FIGS. 2A, 2B, and 2C, in accordance with various embodiments.

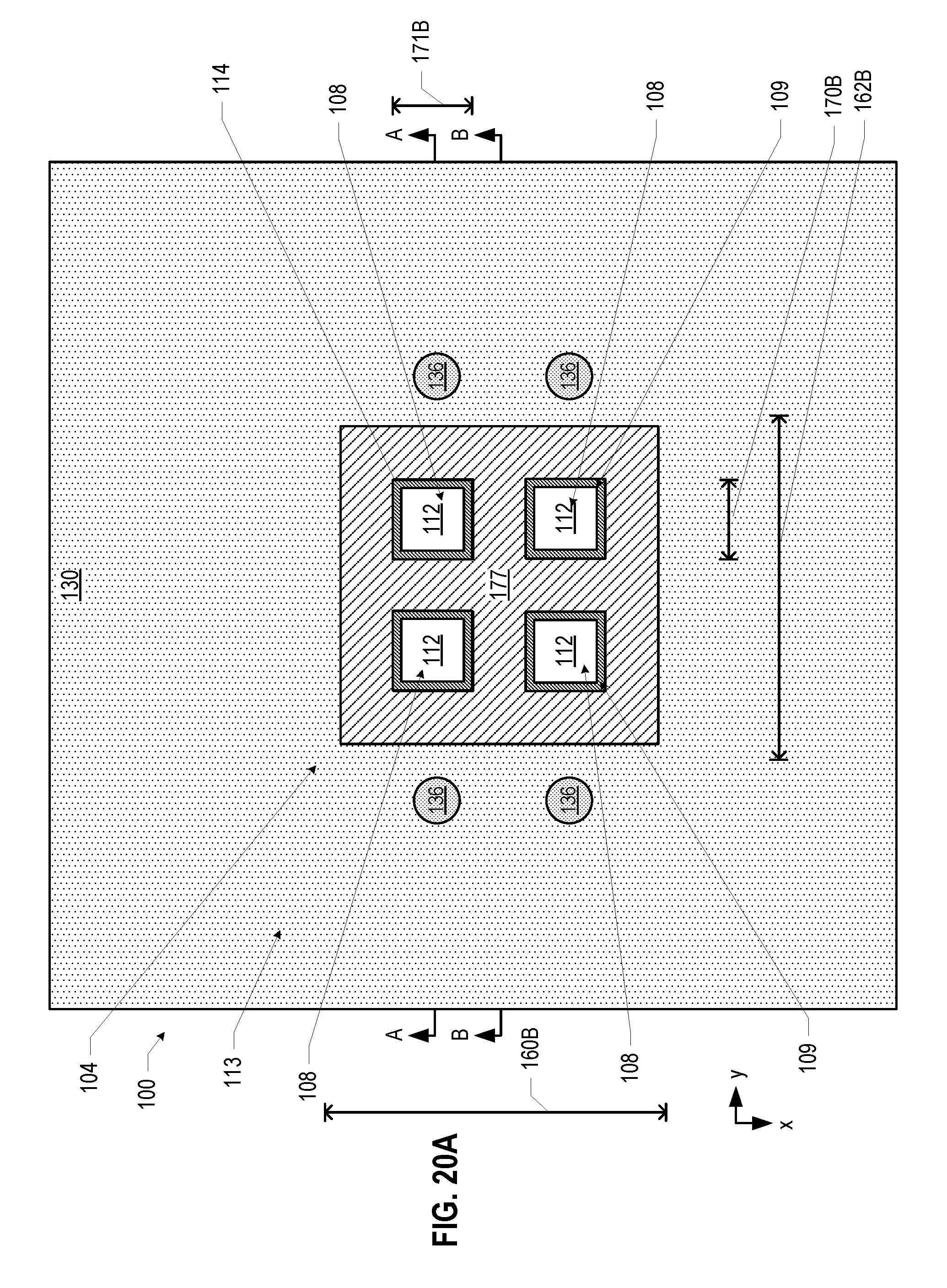

[0007] FIGS. 20A, 20B, and 20C are cross-sectional views of another embodiment of a gate-stack device, in accordance with various embodiments.

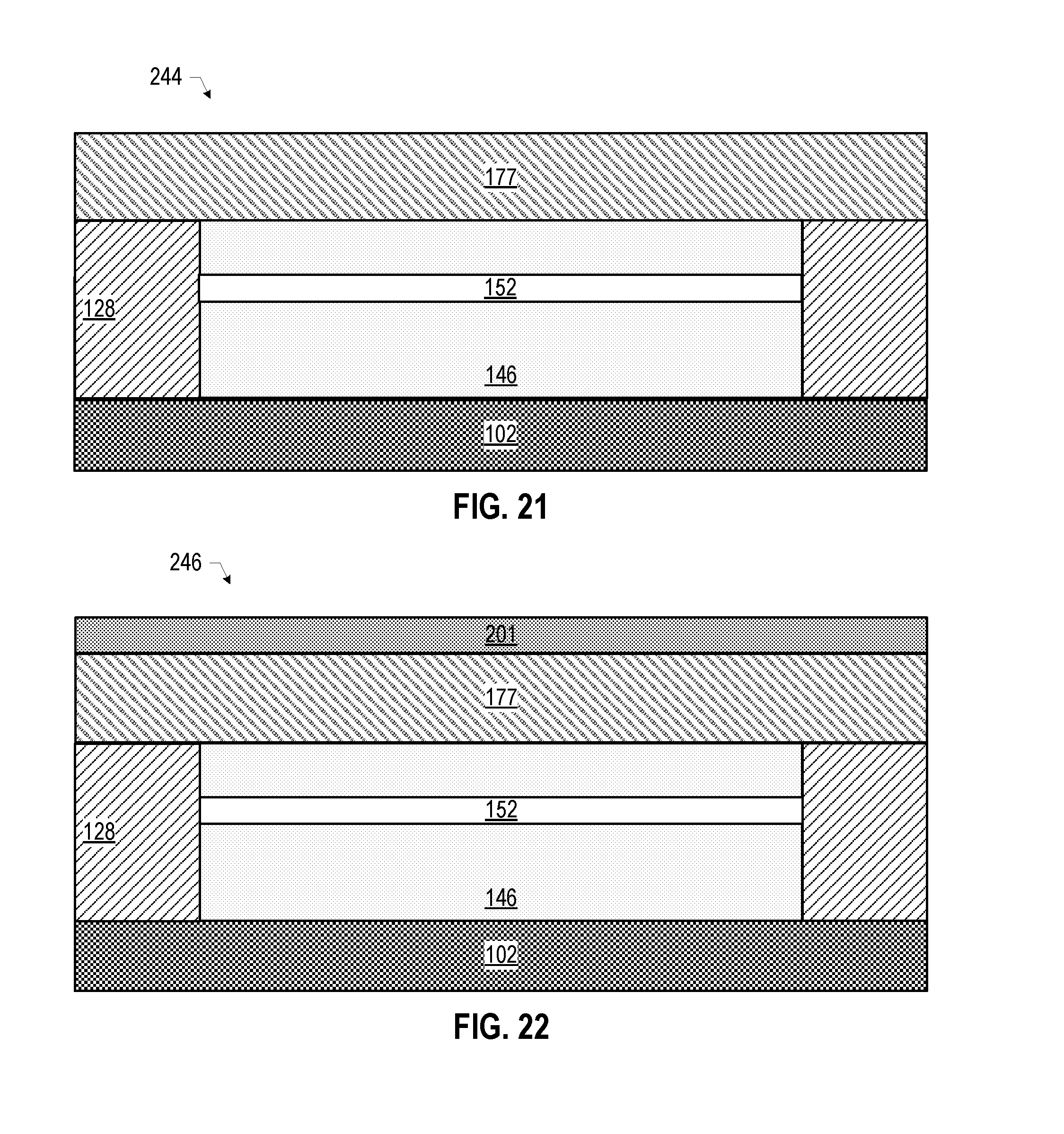

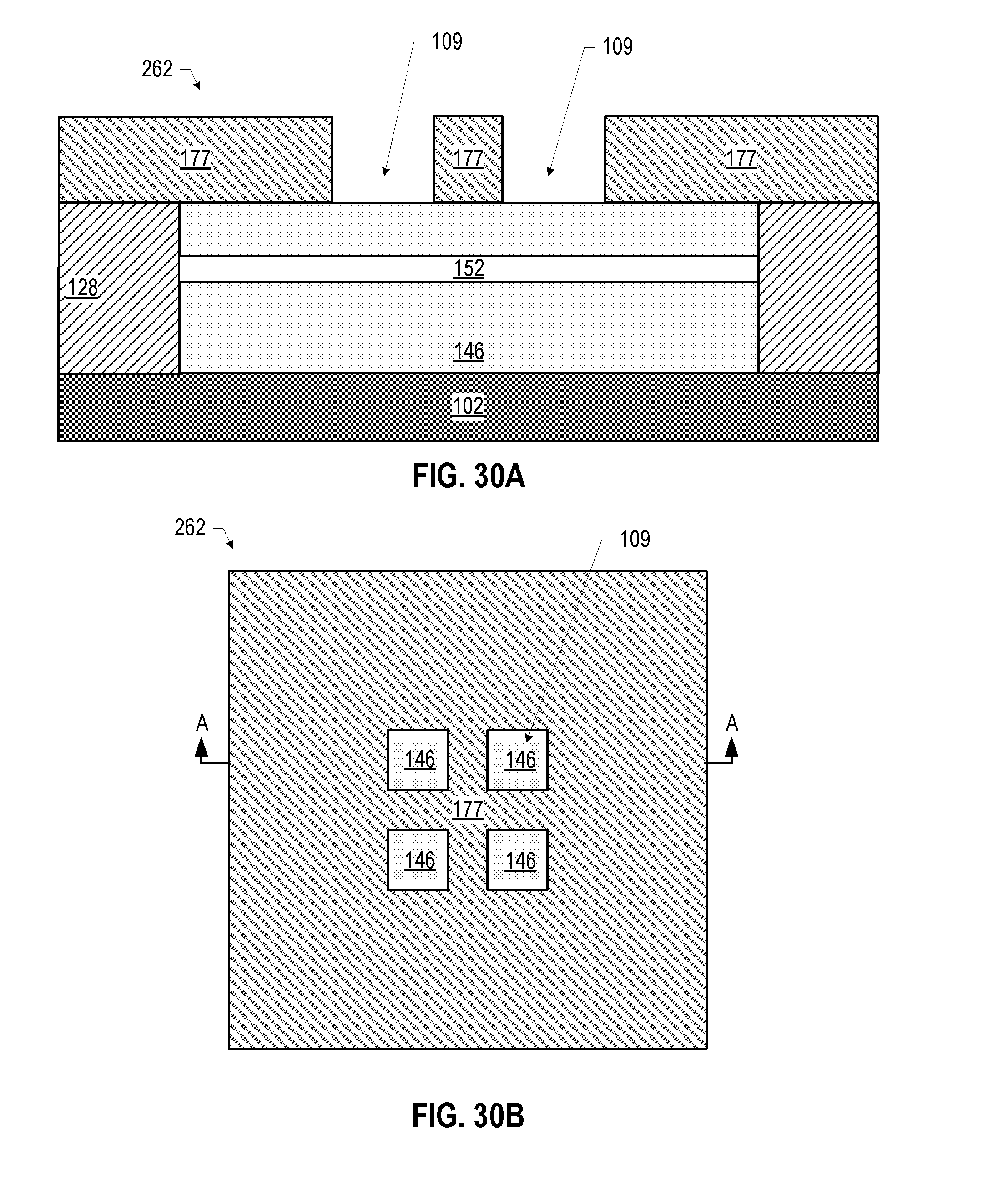

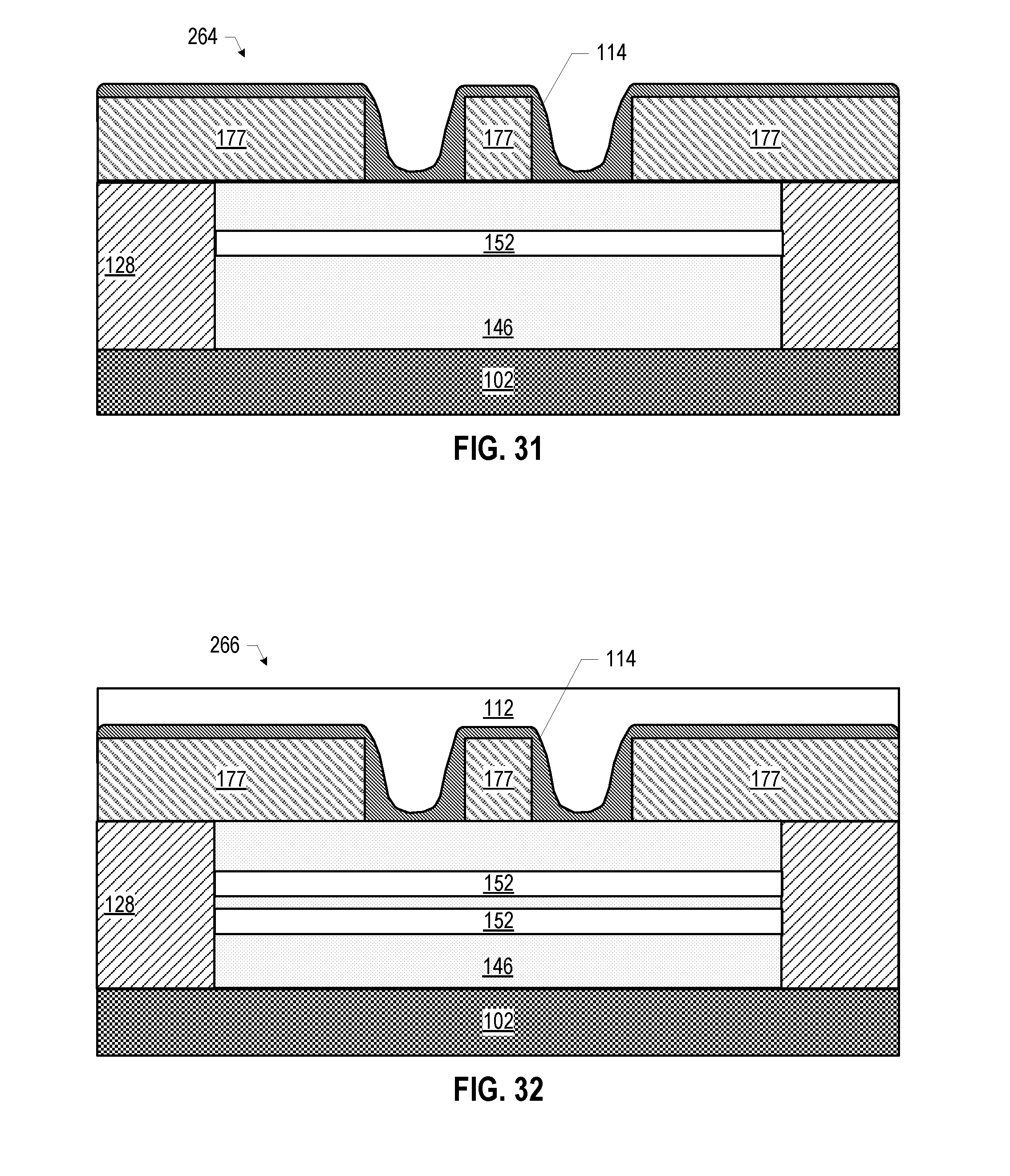

[0008] FIGS. 21, 22, 23A, 23B, 24A, 24B, 25A, 25B, 26A, 26B, 27A, 27B, 28A, 28B, 29A, 29B, 30A, 30B, and 31-36 illustrate various example stages in the manufacture of the gate-stack device of FIGS. 20A, 20B, and 20C, in accordance with various embodiments.

[0009] FIGS. 37-39 are cross-sectional views of various examples of quantum well stacks that may be used in a gate-stack device, in accordance with various embodiments.

[0010] FIG. 40 illustrates an embodiment of a gate-stack device having multiple quantum dot formation regions, in accordance with various embodiments.

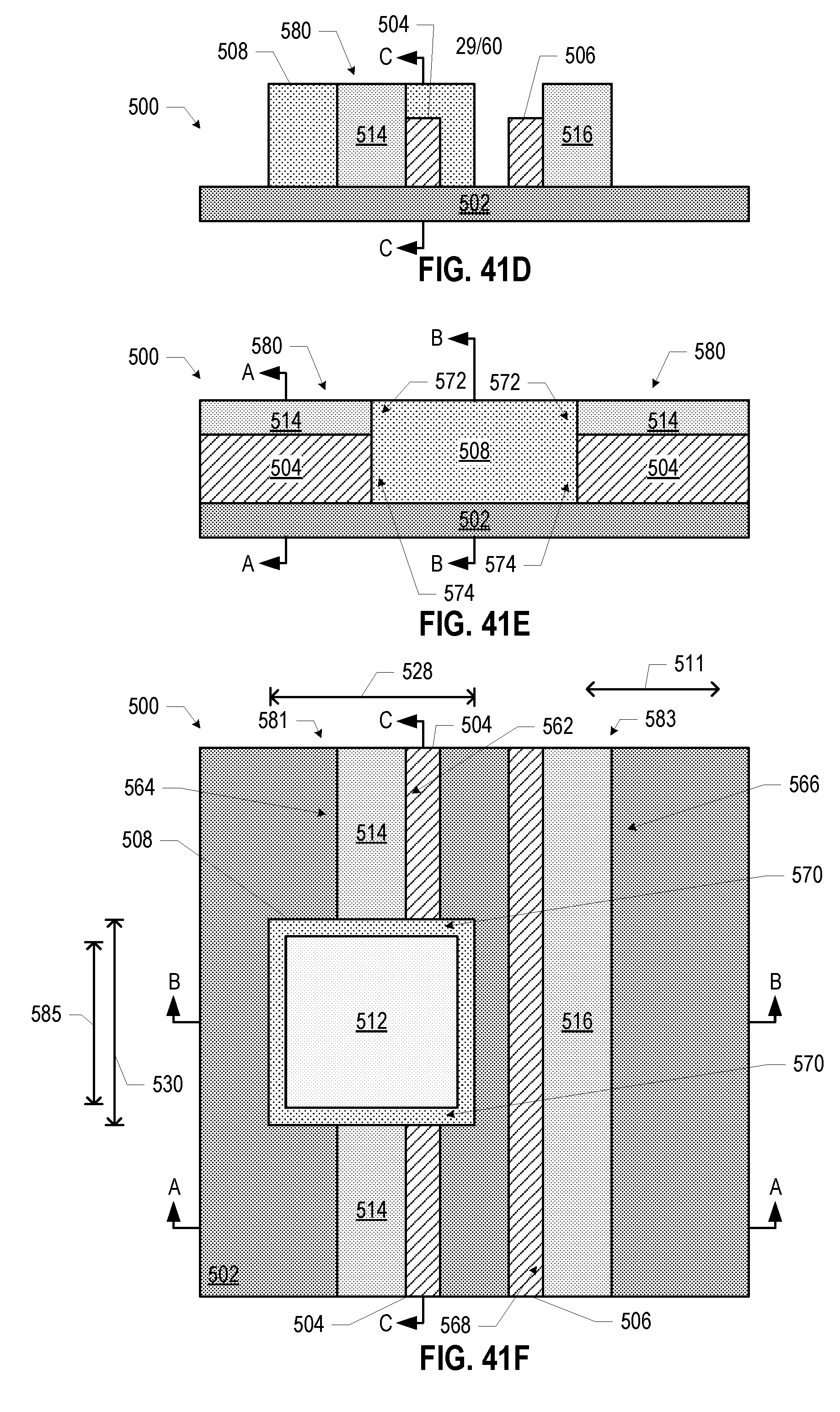

[0011] FIGS. 41A-41F are various views of a single electron transistor (SET) device, in accordance with various embodiments.

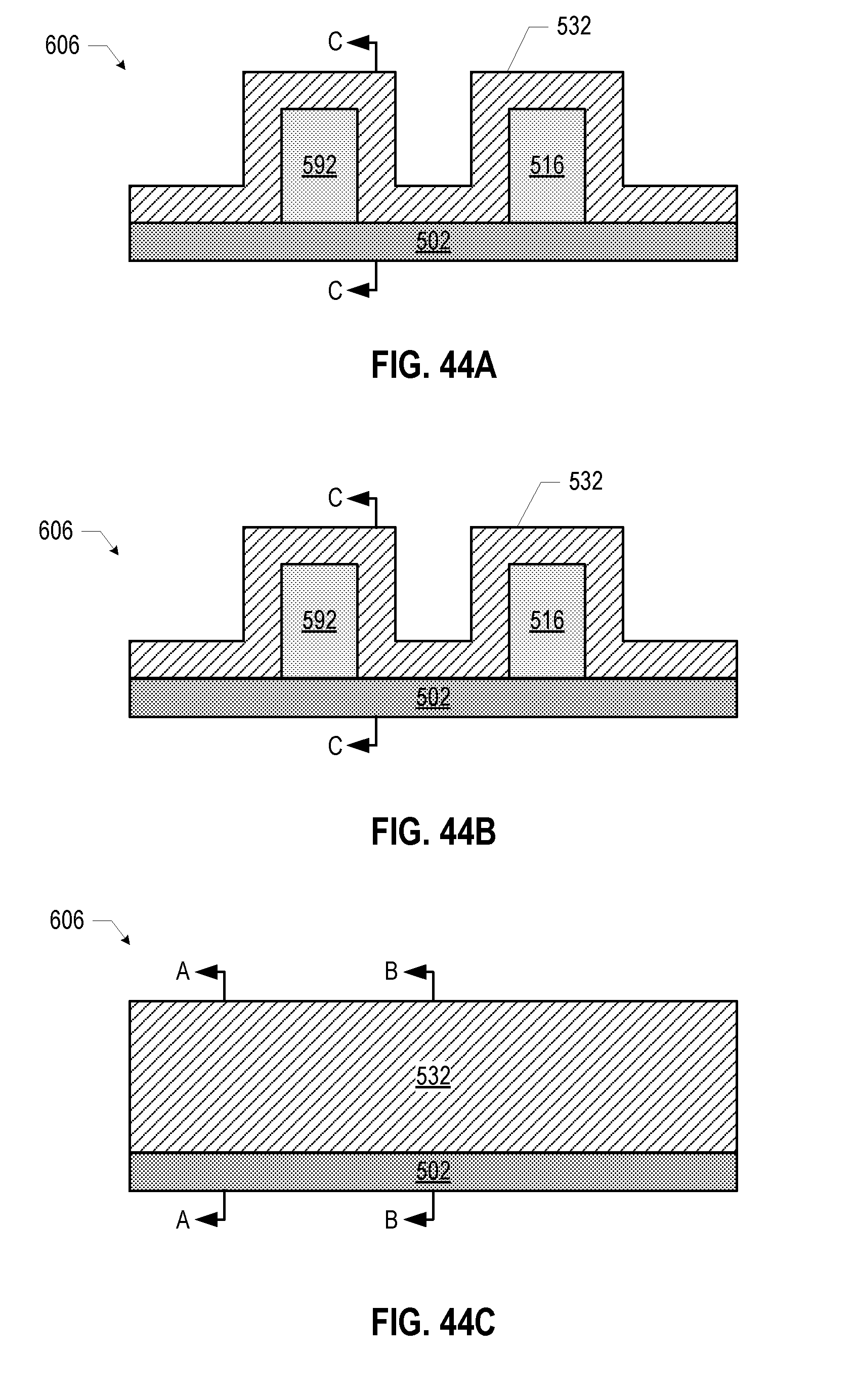

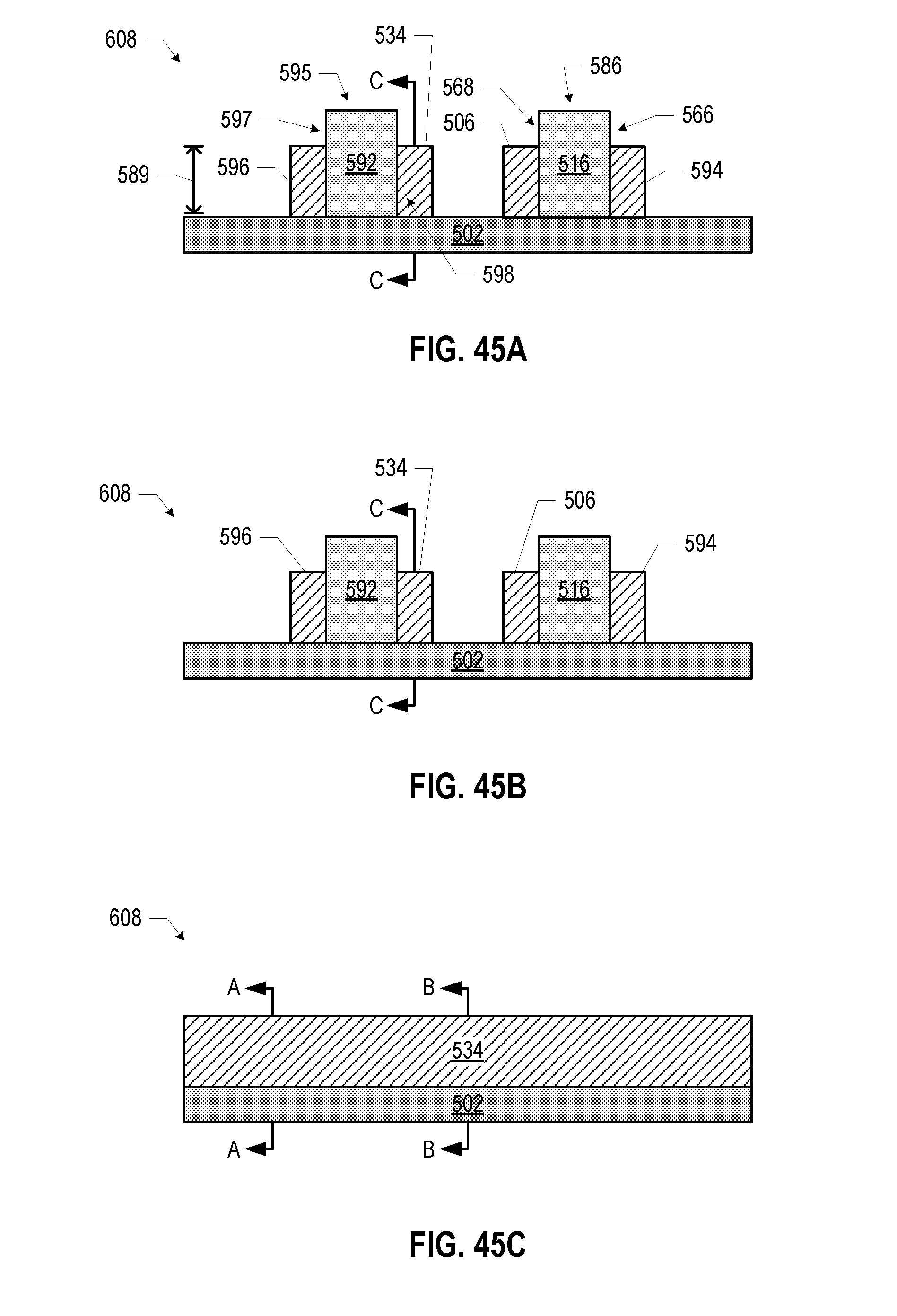

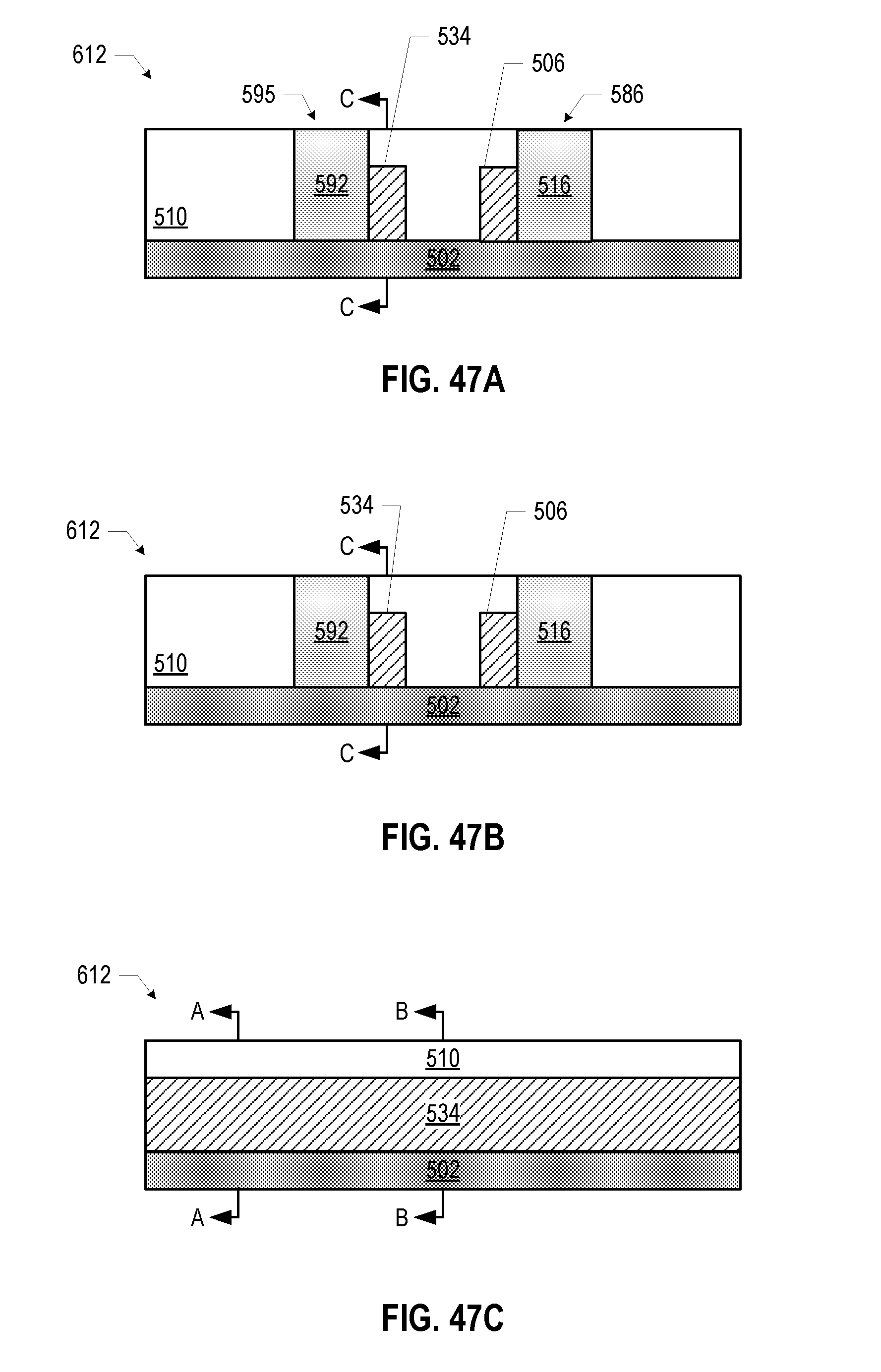

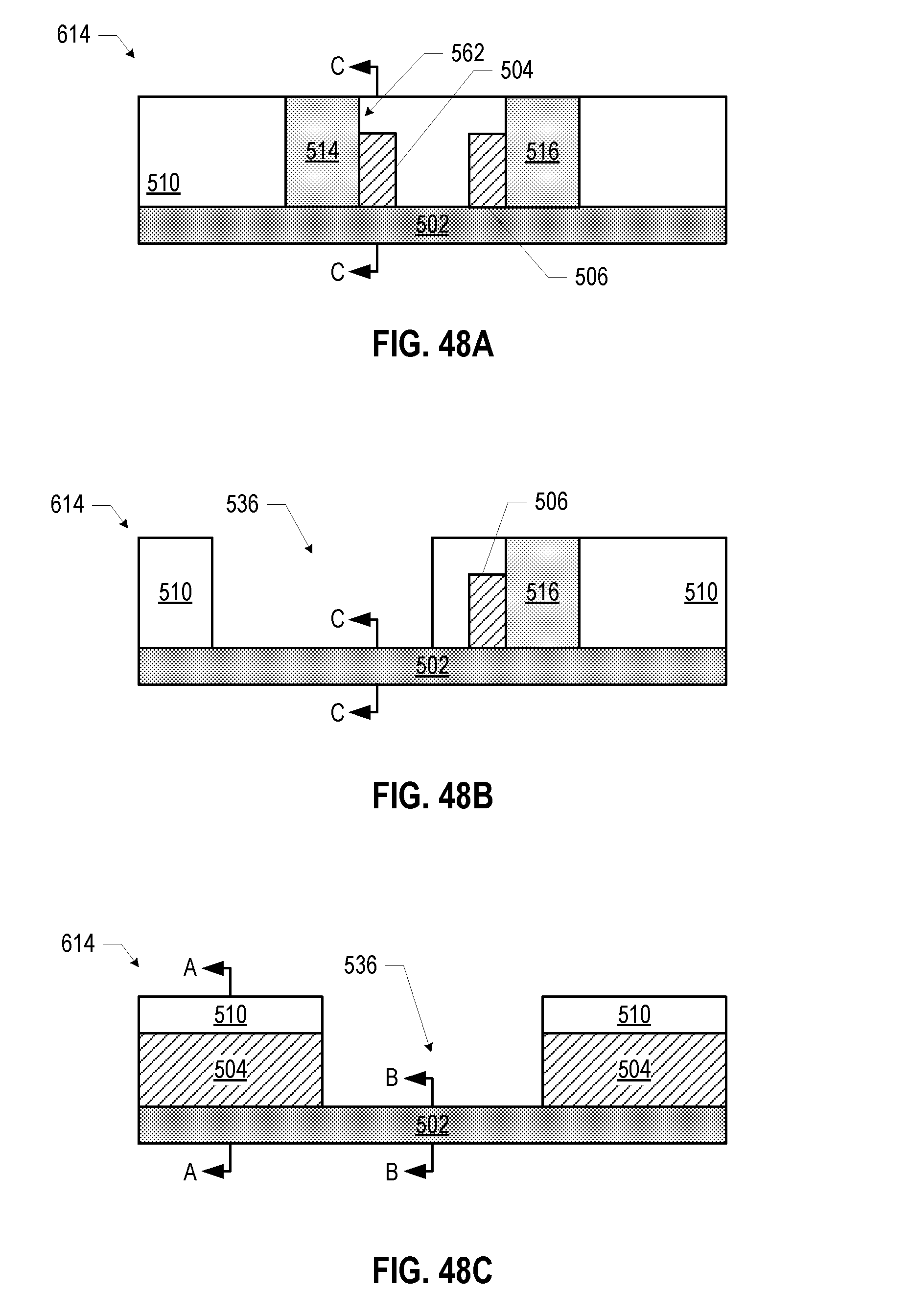

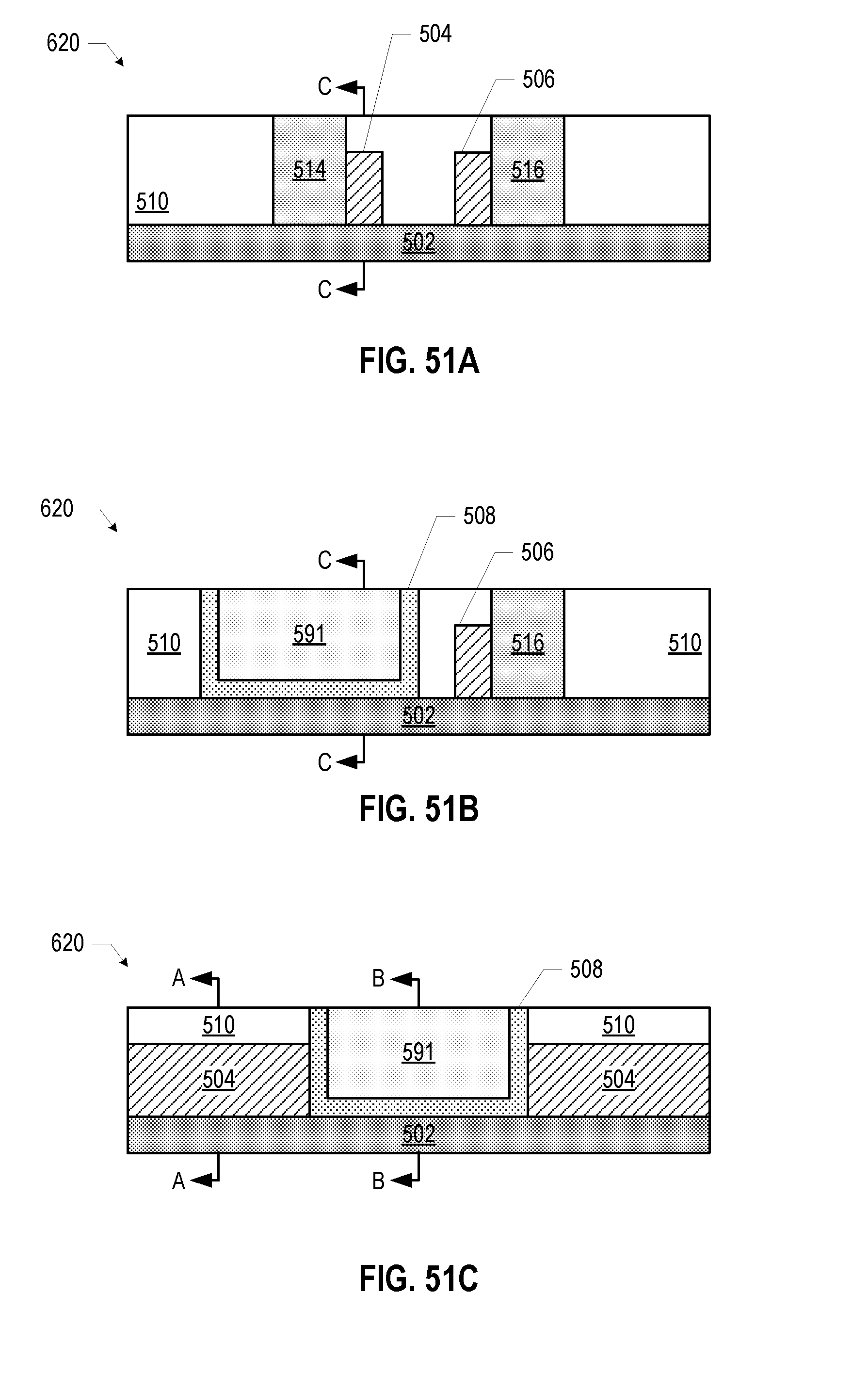

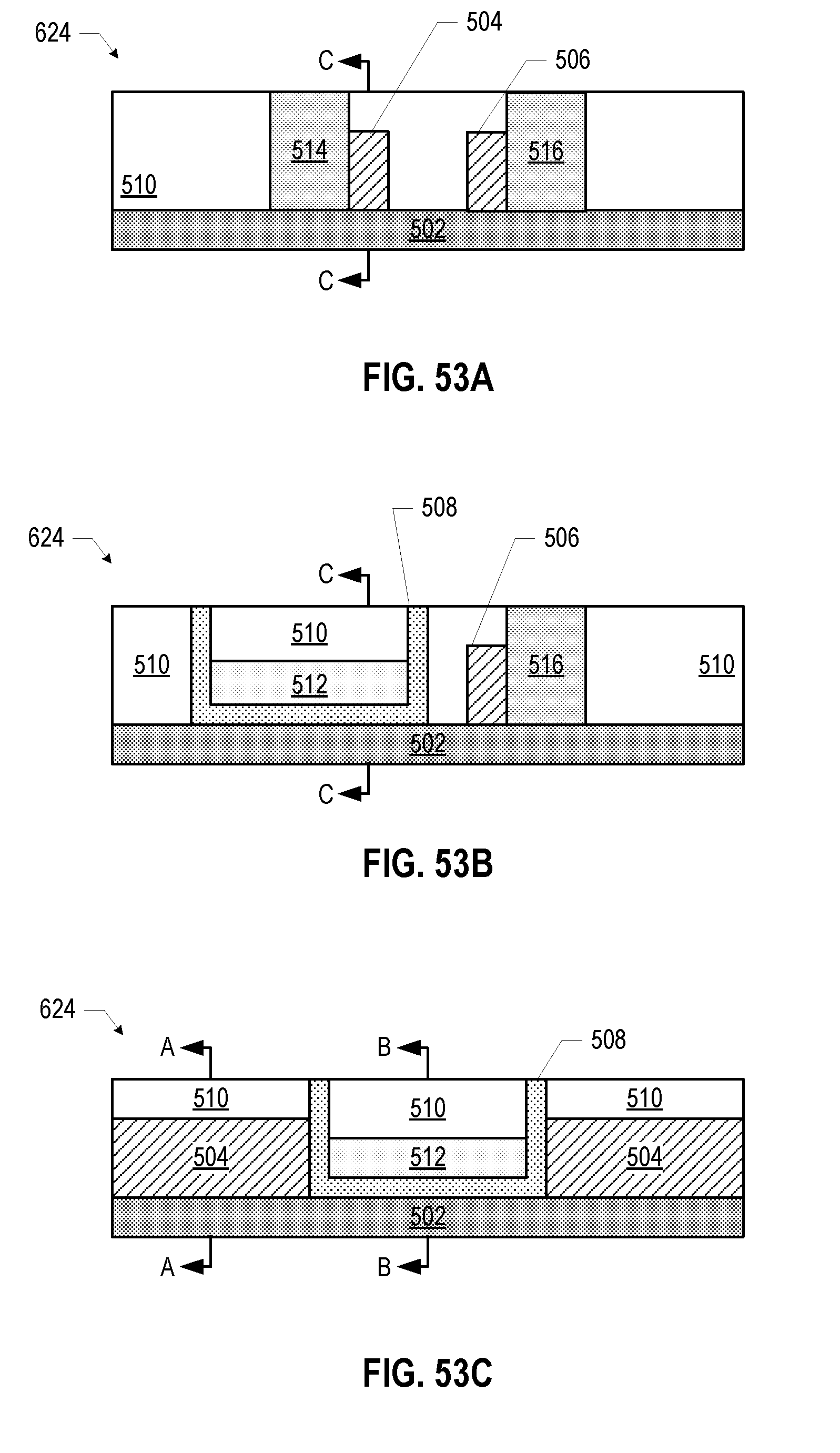

[0012] FIGS. 42A-42C, 43A-43C, 44A-44C, 45A-45C, 46A-46C, 47A-47C, 48A-48C, 49A-49C, 50A-50C, 51A-51C, 52A-52C, and 53A-53C illustrate various example stages in the manufacture of the SET device of FIGS. 41A-41F, in accordance with various embodiments.

[0013] FIGS. 54A-54F are various views of another SET device, in accordance with various embodiments.

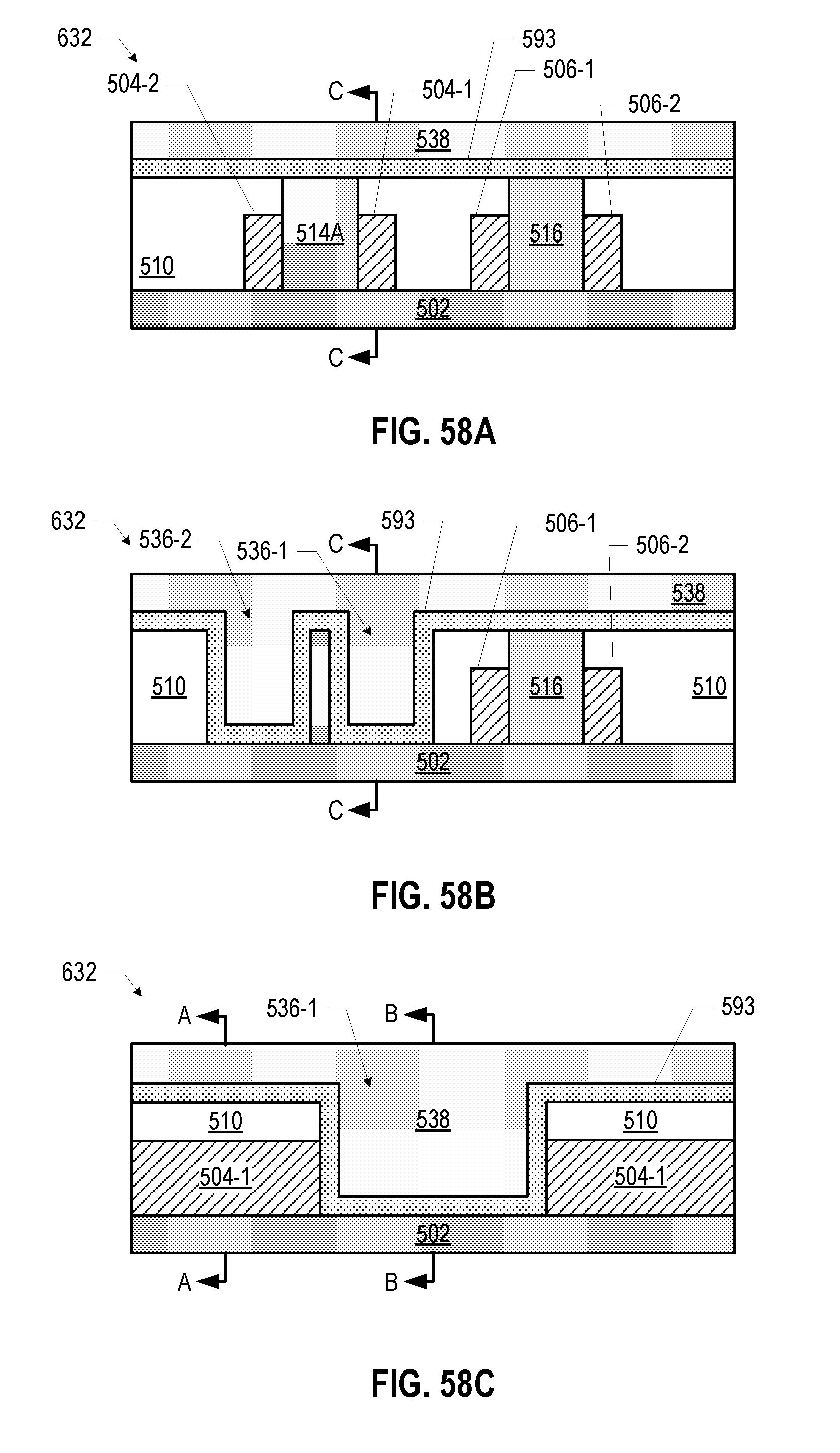

[0014] FIGS. 55A-55C, 56A-56C, 57A-57C, and 58A-58C illustrate various example stages in the manufacture of the SET device of FIGS. 54A-54F, in accordance with various embodiments.

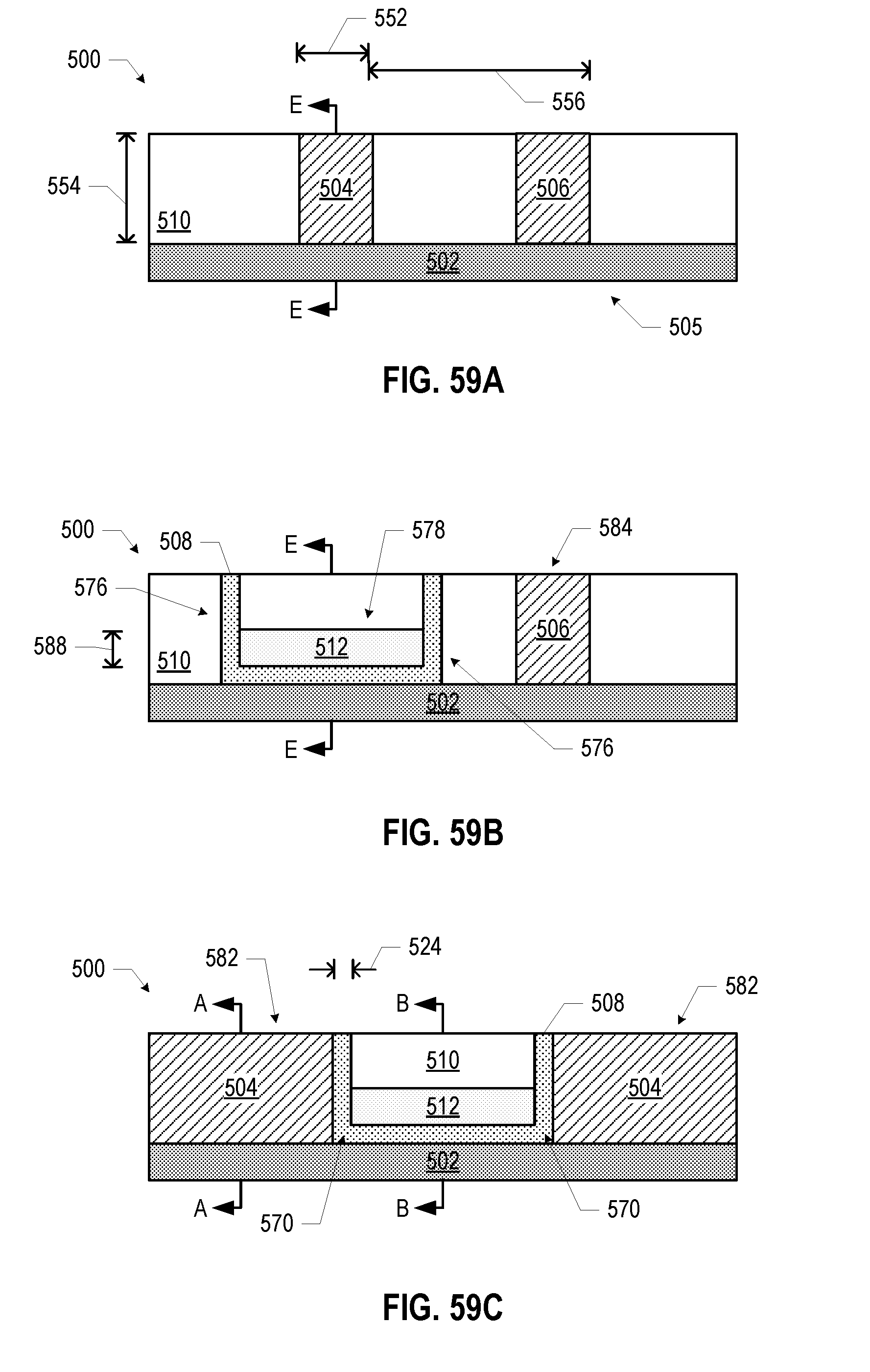

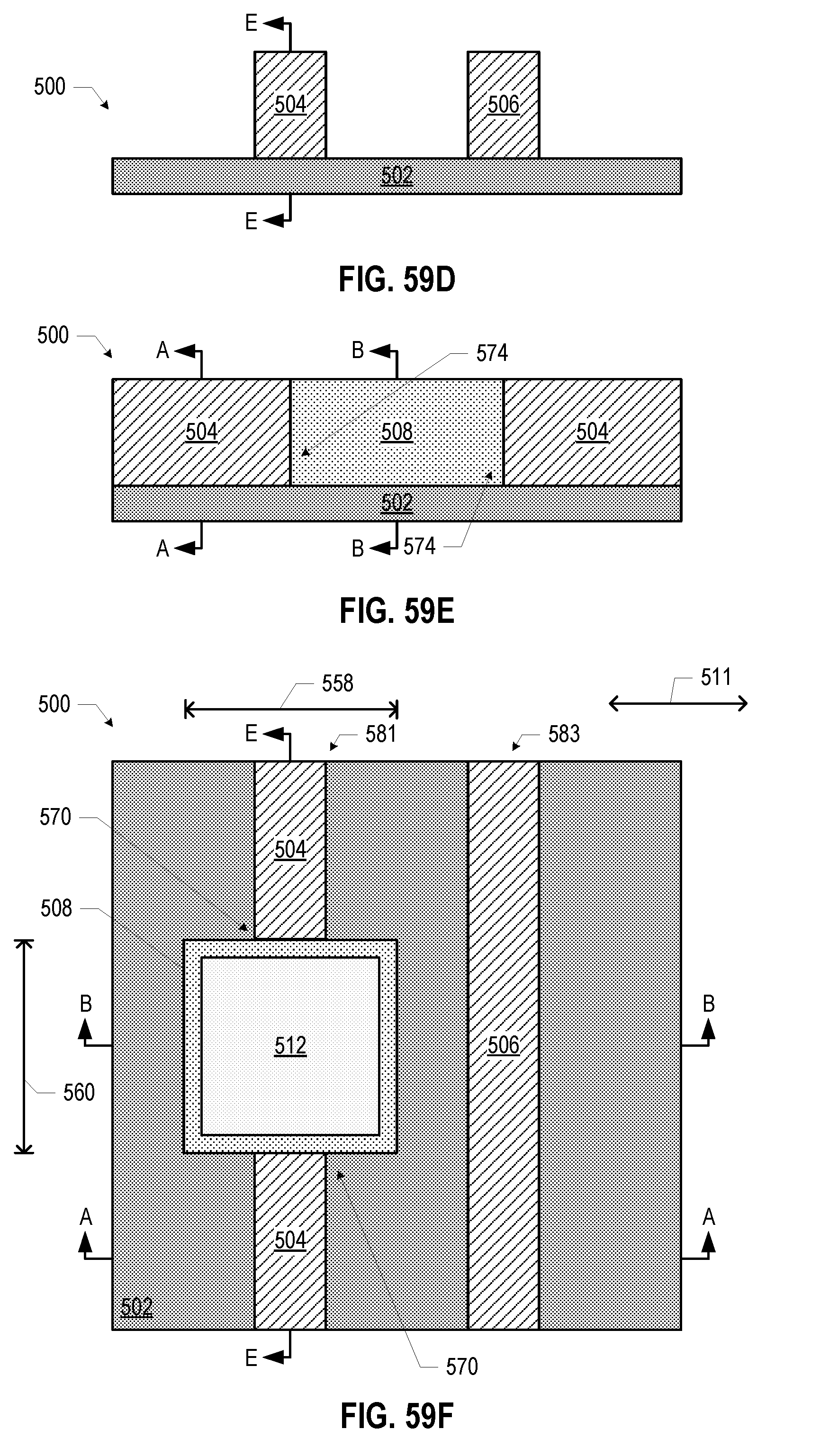

[0015] FIGS. 59A-59F are various views of another SET device, in accordance with various embodiments.

[0016] FIGS. 60A-60C, 61A-61C, and 62A-62C illustrate various example stages in the manufacture of the SET device of FIGS. 59A-59F, in accordance with various embodiments.

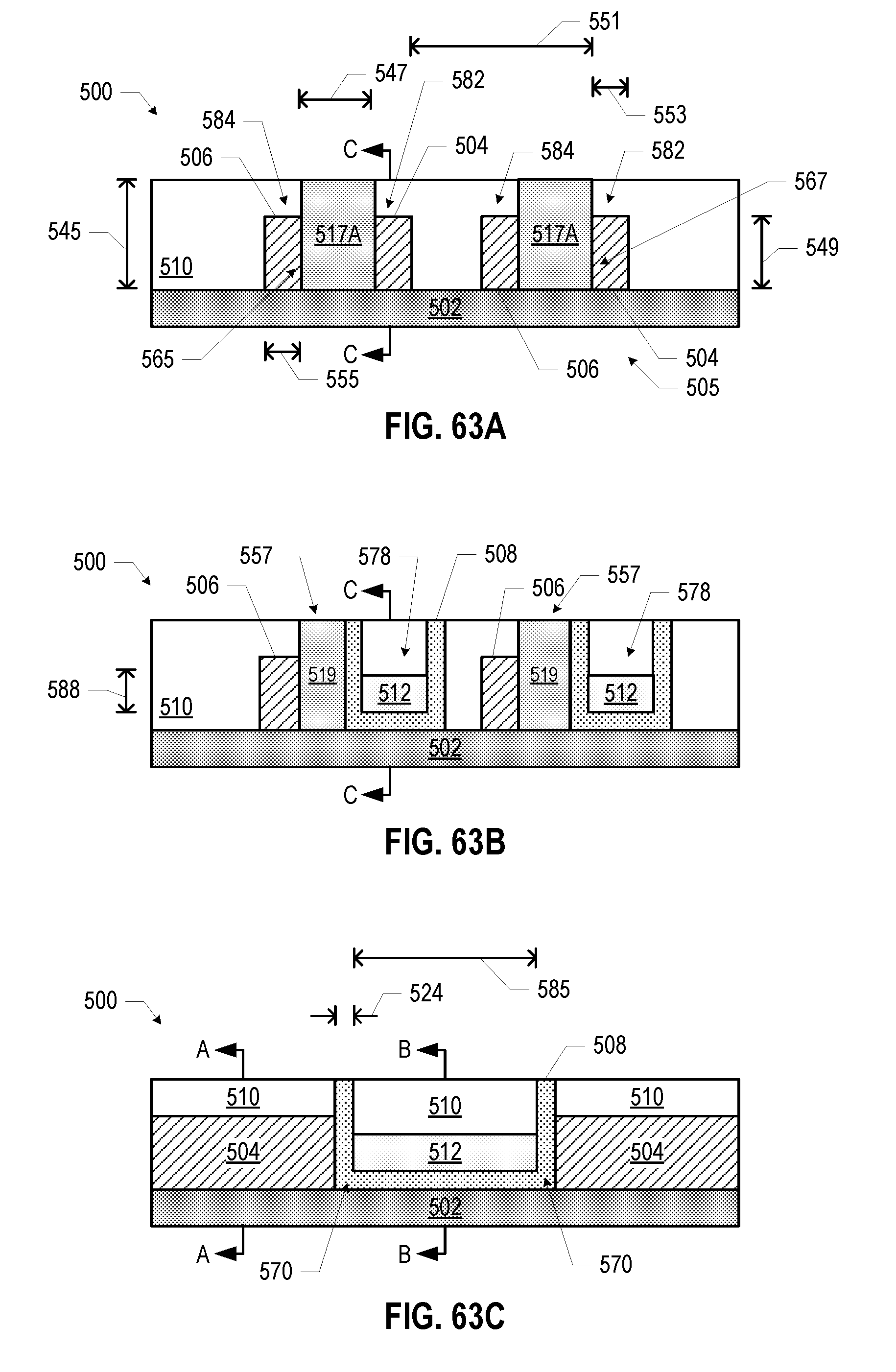

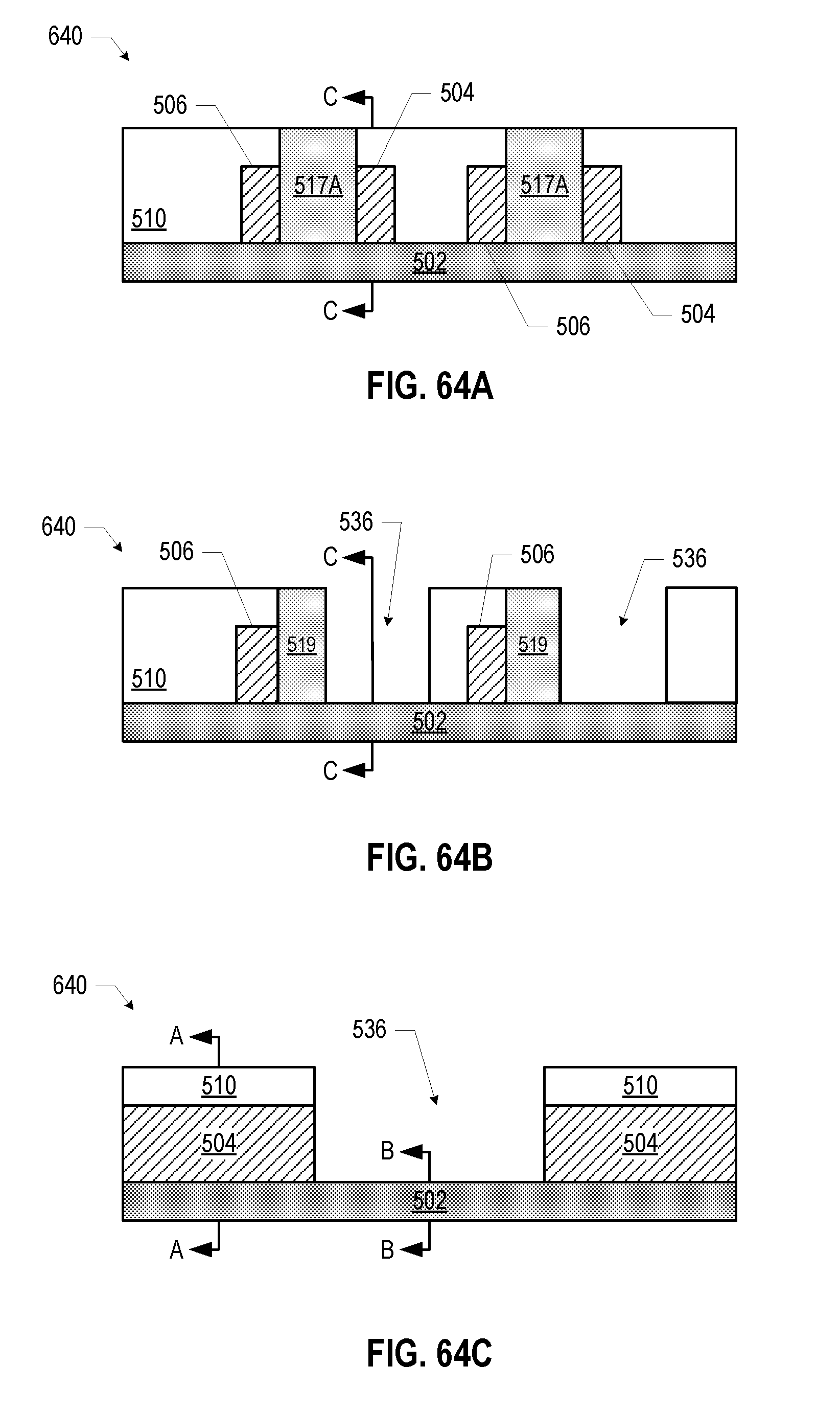

[0017] FIGS. 63A-63F are various views of another SET device, in accordance with various embodiments.

[0018] FIGS. 64A-64C illustrate an example stage in the manufacture of the SET device of FIGS. 63A-63F, in accordance with various embodiments.

[0019] FIG. 65 is a cross-sectional view of a die including a SET device, in accordance with various embodiments.

[0020] FIG. 66 is a cross-sectional view of a die including a gate-stack device, in accordance with various embodiments.

[0021] FIGS. 67A and 67B are top views of a wafer and dies that may include any of the active qubit devices or detector devices disclosed herein.

[0022] FIG. 68 is a cross-sectional side view of a device assembly that may include any of the qubit-detector die assemblies disclosed herein.

[0023] FIG. 69 is a flow diagram of an illustrative method of manufacturing a quantum computing device, in accordance with various embodiments.

[0024] FIG. 70 is a flow diagram of an illustrative method of operating a qubit-detector die assembly, in accordance with various embodiments.

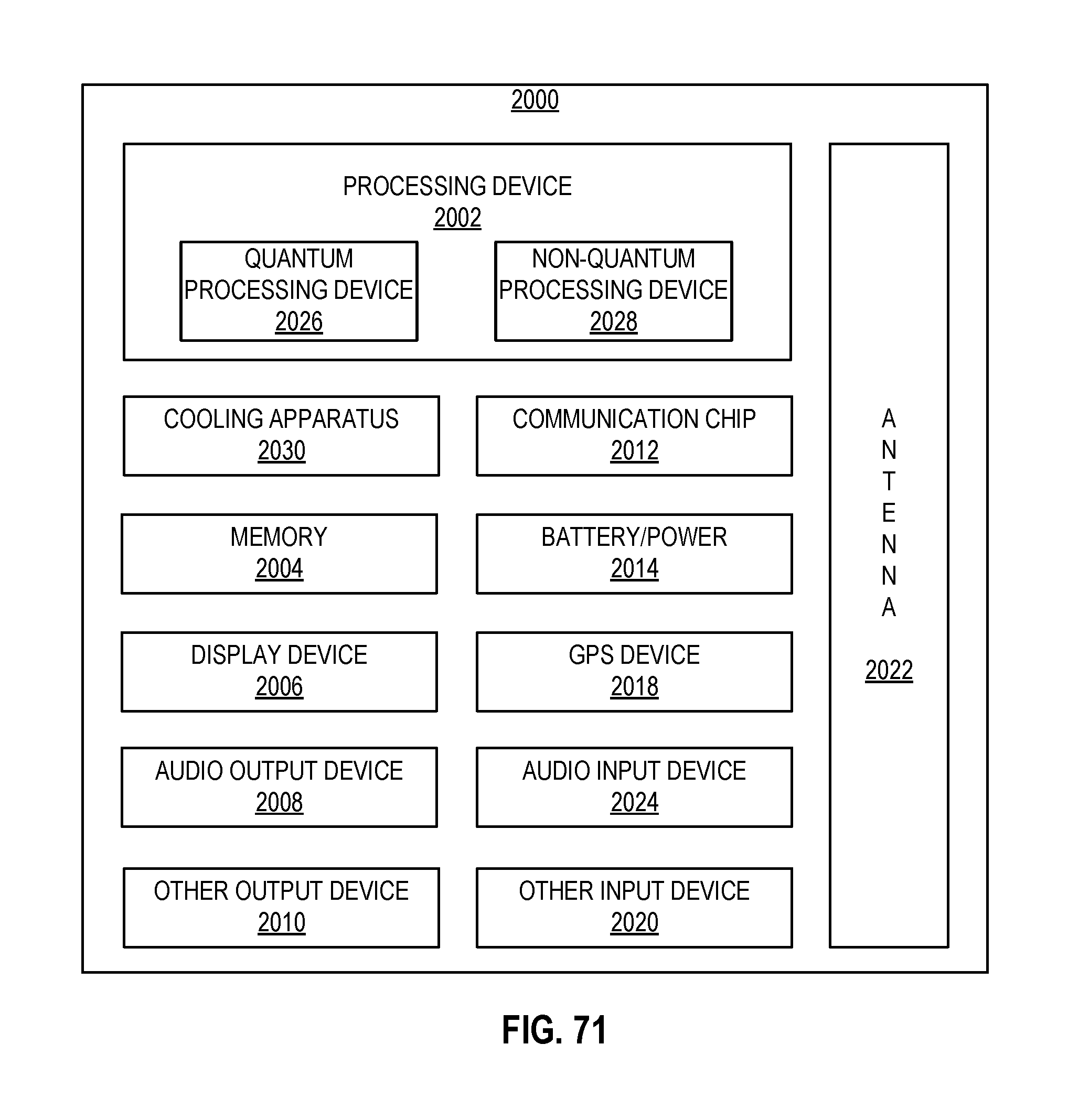

[0025] FIG. 71 is a block diagram of an example quantum computing device that may include any of the qubit-detector die assemblies disclosed herein, in accordance with various embodiments.

DETAILED DESCRIPTION

[0026] Disclosed herein are qubit-detector die assemblies, as well as related computing devices and methods. For example, in some embodiments, a die assembly may include: a first die having a first face and an opposing second face, wherein a plurality of active qubit devices are disposed at the first face of the first die; and a second die, mechanically coupled to the first die, having a first face and an opposing second face, wherein a plurality of quantum state detector devices are disposed at the first face of the second die; wherein the first faces of the first and second dies face each other.

[0027] The devices disclosed herein may enable the formation of quantum dots to serve as quantum bits ("qubits") in a quantum computing device, as well as the control of these quantum dots to perform quantum logic operations. Unlike previous approaches to quantum dot formation and manipulation, various embodiments of the devices disclosed herein provide strong spatial localization of the quantum dots (and therefore good control over quantum dot interactions and manipulation), good scalability in the number of quantum dots included in the device, and/or design flexibility in making electrical connections to the devices to integrate the devices in larger computing devices.

[0028] In the following detailed description, reference is made to the accompanying drawings that form a part hereof, and in which is shown, by way of illustration, embodiments that may be practiced. It is to be understood that other embodiments may be utilized and structural or logical changes may be made without departing from the scope of the present disclosure. Therefore, the following detailed description is not to be taken in a limiting sense.

[0029] Various operations may be described as multiple discrete actions or operations in turn in a manner that is most helpful in understanding the claimed subject matter. However, the order of description should not be construed as to imply that these operations are necessarily order dependent. In particular, these operations may not be performed in the order of presentation. Operations described may be performed in a different order from the described embodiment. Various additional operations may be performed, and/or described operations may be omitted in additional embodiments.

[0030] For the purposes of the present disclosure, the phrase "A and/or B" means (A), (B), or (A and B). For the purposes of the present disclosure, the phrase "A, B, and/or C" means (A), (B), (C), (A and B), (A and C), (B and C), or (A, B, and C). The term "between," when used with reference to measurement ranges, is inclusive of the ends of the measurement ranges. As used herein, the notation "A/B/C" means (A), (B), and/or (C). For ease of discussion, all of the lettered sub-figures associated with a particular numbered figure may be referred to by the number of that figure; for example, FIGS. 1A-1C may be referred to as "FIG. 1," FIGS. 2A-2C may be referred to as "FIG. 2," etc.

[0031] The description uses the phrases "in an embodiment" or "in embodiments," which may each refer to one or more of the same or different embodiments. Furthermore, the terms "comprising," "including," "having," and the like, as used with respect to embodiments of the present disclosure, are synonymous. The disclosure may use perspective-based descriptions such as "above," "below," "top," "bottom," and "side"; such descriptions are used to facilitate the discussion and are not intended to restrict the application of disclosed embodiments. The accompanying drawings are not necessarily drawn to scale. As used herein, a "high-k dielectric" refers to a material having a higher dielectric constant than silicon oxide.

[0032] FIGS. 1A, 1B, and 1C are cross-sectional views of an embodiment of a qubit-detector die assembly 800, in accordance with various embodiments. In particular, FIG. 1B is a cross-sectional view of the active qubit die 802 through the section B-B of FIG. 1A, and FIG. 1C is a cross-sectional view of the quantum state detector die 804 through the section A-A of FIG. 1A.

[0033] The qubit-detector die assembly 800 may include an active qubit die 802 mechanically coupled to a quantum state detector die 804. The active qubit die 802 may have a first face 806 and an opposing second face 808. Multiple active qubit devices 836 may be disposed proximate to the first face 806 of the active qubit die 802. The quantum state detector die 804 may have a first face 810 and an opposing second face 812. The quantum state detector die 804 may include multiple detector devices 838 disposed proximate to the first face 810. The active qubit die 802 and the quantum state detector die 804 may be coupled together so that the first face 806 of the active qubit die 802 faces the first face 810 of the quantum state detector die 804, and thus the active qubit devices 836 are proximate to the detector devices 838. In some embodiments, the distance 834 between the first face 810 and the first face 806 may be between 50 and 250 nanometers (e.g., between 50 and 150 nanometers, or between 100 and 200 nanometers). During operation of the die assembly 800, the quantum states of quantum dots generated by the active qubit devices 836 in the active qubit die 802 may be detected by the detector devices 838 in the quantum state detector die 804; the distance 834 may be small enough so that quantum state detection may take place "across" the space between the active qubit die 802 and the quantum state detector die 804. As discussed below, a number of different devices may provide the active qubit devices 836, and a number of different devices may provide the detector devices 838.

[0034] In some embodiments, the active qubit devices 836 and the detector devices 838 may have a same or similar structure, while in other embodiments, the active qubit devices 836 and the detector devices 838 may have different structures. For example, in some embodiments, the active qubit devices 836 and the detector devices 838 may both include any of the gate-stack devices 100 disclosed herein. In some embodiments, the active qubit devices 836 and the detector devices 838 may both include any of the SET devices 500 disclosed herein. In some embodiments, the active qubit devices 836 may include any of the gate-stack devices 100 disclosed herein, and the detector devices 838 may include any of the SET devices 500 disclosed herein. In some embodiments, the active qubit devices 836 may include any of the SET devices 500 disclosed herein, and the detector devices 838 may include any of the gate-stack devices 100 disclosed herein. In some embodiments, the active qubit die 802 and the quantum state detector die 804 may be "mirror images" of each other in the die assembly 800.

[0035] The active qubit die 802 and the quantum state detector die 804 may be mechanically coupled in any of a number of ways. In some embodiments, the active qubit die 802 and the quantum state detector die 804 may be coupled together with an adhesive disposed between the first face 806 and the first face 810. In some embodiments, the active qubit die 802 and the quantum state detector die 804 may be coupled together with conductive material. For example, the active qubit die 802 may include one or more conductive contacts 816 disposed at the first face 806, and these conductive contacts 816 may be coupled to corresponding conductive contacts 820 disposed at the first face 810 of the quantum state detector die 804 via die-to-die interconnects 828. As used herein, a "conductive contact" may include a bond pad, a post, or any other suitable contact structure. In some embodiments, the die-to-die interconnects 828 may include solder bumps, paste, or balls (as illustrated in FIG. 1A); for example, the die-to-die interconnects 828 may be flip chip (or controlled collapse chip connection, "C4") bumps disposed initially on the active qubit die 802 or on the quantum state detector die 804. Any other die-to-die coupling technology may be used to provide the die-to-die interconnects 828.

[0036] In some embodiments in which the active qubit die 802 and the quantum state detector die 804 are coupled via solder, one or more of the conductive contacts 816 disposed at the first face 806 of the active qubit die 802 that mechanically couple the active qubit die 802 to the quantum state detector die 804 may not be connected to any significant conductive pathways within the active qubit die 802 (e.g., no power or electrical signals may flow through those conductive contacts 816). Similarly, one or more of the conductive contacts 820 disposed at the first face 810 of the quantum state detector die 804 that mechanically couple the active qubit die 802 to the quantum state detector die 804 may not be connected to any significant conductive pathways within the quantum state detector die 804. For example, FIG. 1A depicts a coupling structure 852 that includes a conductive contact 816, a conductive contact 820, and die-to-die interconnects 828 coupling the conductive contacts 816 and 820. The conductive contact 816 of the coupling structure 852 may not be connected to any conductive pathways within the active qubit die 802, and the conductive contact 820 of the coupling structure 852 may not be connected to any significant conductive pathways within the quantum state detector die 804. In such embodiments, the die-to-die interconnects 828 coupling the conductive contact 816 and the conductive contact 820 of the coupling structure 852 may simply provide a mechanical coupling.

[0037] In some embodiments in which the active qubit die 802 and the quantum state detector die 804 are coupled via solder, the solder may provide an electrical pathway between the active qubit die 802 and the quantum state detector die 804 through which electrical signals and/or power or reference signals may flow (e.g., as discussed below with reference to the conductive pathways 843). The "conductive pathways" discussed with reference to FIG. 1 may generally include conductive vias, conductive lines, and/or any combination of conductive vias and lines, among other structures, arranged as appropriate. In some embodiments, conductive lines of a die (or a package substrate, as discussed below) may extend into and out of the plane of the drawing, providing conductive pathways to route electrical signals to and/or from various elements in the die. Conductive vias and/or lines that provide the conductive pathways in a die or package substrate may be formed using any suitable techniques. Examples of such techniques may include subtractive fabrication techniques, additive or semi-additive fabrication techniques, single Damascene fabrication techniques, dual Damascene fabrication techniques, or any other suitable technique.

[0038] The active qubit die 802 may include one or more conductive contacts 818 disposed at the second face 808 of the active qubit die 802. In some embodiments, the active qubit die 802 may include one or more conductive pathways 846 between the active qubit devices 836 (or other components of the active qubit die 802) and one or more conductive contacts 818; these conductive contacts 818 may be coupled to other devices (not shown) via solder, wire bonding, or any other suitable technique. In some embodiments, the active qubit die 802 may include one or more conductive pathways 854 between one or more conductive contacts 818 and one or more conductive contacts 816; the conductive contacts 816 of the conductive pathways 854 may be coupled to conductive contacts 820 of the quantum state detector die 804 via solder, for example, and the conductive contacts 818 of the conductive pathways 854 may be coupled to other devices (not shown) via solder, wire bonding, or any other suitable technique. In some embodiments, the active qubit die 802 may include one or more conductive pathways 843 between the active qubit devices 836 (or other components of the active qubit die 802) and one or more conductive contacts 816; the conductive contacts 816 of the conductive pathways 843 may be coupled to conductive contacts 820 of the quantum state detector die 804, as shown. Generally, the active qubit die 802 may include any desired conductive pathways between various components included in the active qubit die 802 (e.g., the active qubit devices 836) and the conductive contacts 816 and/or 818. During operation of the active qubit die 802, electrical signals (such as power and/or input/output (I/O) signals) may be routed to and/or from the active qubit devices 836 (and/or other components) of the active qubit die 802 through the conductive pathways 846 and/or 842.

[0039] The quantum state detector die 804 may also include any desired conductive pathways between various components included in the quantum state detector die 804 (e.g., the detector devices 838) and the conductive contacts 820 and/or the conductive contacts 822 disposed at the second face 812 of the quantum state detector die 804. In some embodiments, the quantum state detector die 804 may include one or more conductive pathways 848 between the detector devices 838 (or other components of the quantum state detector die 804) and one or more conductive contacts 822; these conductive contacts 822 may be coupled to a package substrate 814, for example, via first level interconnects 830 (and thus the die assembly 800 may be regarded as an electronics package). In some embodiments, the quantum state detector die 804 may include one or more conductive pathways 856 between one or more conductive contacts 820 and one or more conductive contacts 822. In some embodiments, the quantum state detector die 804 may include one or more conductive pathways 841 between the detector devices 838 (or other components of the quantum state detector die 804) and one or more conductive contacts 820; the conductive contacts 820 of the conductive pathways 841 may be coupled to conductive contacts 816 of the active qubit die 802, as shown. During operation of the quantum state detector die 804, electrical signals (such as power and/or input/output (I/O) signals) may be routed to and/or from the detector devices 838 (and/or other components) of the quantum state detector die 804 through the conductive pathways 848 (or any other suitable conductive pathways).

[0040] In some embodiments, a single detector device 838 may be used to sense the quantum state of a single quantum dot formed by an active qubit device 836. In other embodiments, a single detector device 838 may be used to sense the quantum state of more than one quantum dot formed by one or more active qubit devices 836; for example, a single detector device 838 may be used to sense the quantum state of two quantum dots, or three quantum dots.

[0041] An active qubit die 802 may include any desired number and arrangement of active qubit devices 836; similarly, a quantum state detector die 804 may include any desired number and arrangement of detector devices 838. In some embodiments, as illustrated in FIG. 1, the active qubit devices 836 and the detector devices 838 may be arranged in regular rectangular spacing. In other embodiments, the active qubit devices 836 and the detector devices 838 may be arranged in any desired pattern.

[0042] In the die assembly 800 illustrated in FIG. 1A, the quantum state detector die 804 is disposed between the active qubit die 802 and a package substrate 814. In other embodiments, the active qubit die 802 may be disposed between the quantum state detector die 804 and the package substrate 814; in such embodiments, the detector devices 838 of the quantum state detector die 804 may still "face" the active qubit devices 836 of the active qubit die 802.

[0043] The package substrate 814 may include a first face 858 and an opposing second face 860. Conductive contacts 824 may be disposed at the first face 858, and conductive contacts 826 may be disposed at the second face 860. Conductive pathways 850 may extend between the conductive contacts 824 at the first face 858 and the conductive contacts 826 at the second face 860 of the package substrate 814, electrically coupling various ones of the conductive contacts 824 to various ones of the conductive contacts 826, in any desired manner. The conductive pathways 850 may include one or more conductive vias and/or one or more conductive lines, for example.

[0044] In some embodiments, the package substrate 814 may be built on a carrier material (not shown) that remains in the package substrate 814. In such embodiments, the carrier material may be a dielectric material; laser vias or other through-holes may be made through the carrier material to allow conductive pathways 850 to extend between the first face 858 and the second face 860. In some embodiments, the package substrate 814 may be or may otherwise include a silicon interposer, and the conductive pathways 850 may be through-silicon vias. Silicon may have a desirably low coefficient of thermal expansion compared with other dielectric materials that may be used in the package substrate 814, and thus may limit the degree to which the package substrate 814 expands and contracts during temperature changes relative to such other materials (e.g., polymers having higher coefficients of thermal expansion). A silicon interposer may also help the package substrate 814 achieve a desirably small line width and maintain high connection density to the quantum state detector die 804.

[0045] Limiting differential expansion and contraction may help preserve the mechanical and electrical integrity of the die assembly 800 as the die assembly 800 is fabricated (and exposed to higher temperatures) and used in a cooled environment (and exposed to lower temperatures). In some embodiments, thermal expansion and contraction in the package substrate 814 may be managed by maintaining an approximately uniform density of the conductive material in the package substrate 814 (so that different portions of the package substrate 814 expand and contract uniformly), using reinforced dielectric materials as the insulating material in the package substrate 814 (e.g., dielectric materials with silicon dioxide fillers), or utilizing stiffer materials as the insulating material in the package substrate 814 (e.g., a prepreg material including glass cloth fibers).

[0046] The conductive contacts 822 of the quantum state detector die 804 may be electrically coupled to the conductive contacts 824 of the package substrate 814 via the first level interconnects 830. In some embodiments, the first level interconnects 830 may include solder bumps or balls (as illustrated in FIG. 1A); for example, the first level interconnects 830 may be flip chip bumps disposed initially on the quantum state detector die 804 or on the package substrate 814. Second level interconnects 832 (e.g., solder balls or other types of interconnects) may couple the conductive contacts 826 on the second face 860 of the package substrate 814 to another component, such as a circuit board (not shown). Examples of arrangements of electronics packages that may include an embodiment of the die assembly 800 are discussed below with reference to FIG. 68.

[0047] During manufacturing of the die assembly 800, the active qubit die 802 may be brought into contact with the quantum state detector die 804 using a pick-and-place apparatus, for example, and a reflow or thermal compression bonding operation may be used to couple the active qubit die 802 to the quantum state detector die 804 via the die-to-die interconnects 828. Similarly, the quantum state detector die 804 may be brought in contact with the package substrate 814 using a pick-and-place apparatus, for example, and a reflow or thermal compression bonding operation may be used to couple the quantum state detector die 804 to the package substrate 814 via the first level interconnects 830. In some embodiments, a different structure may take the place of the package substrate 814; for example, the die assembly 800 may include a circuit board, interposer, or other die in the place of the package substrate 814.

[0048] The conductive contacts of the die assembly 800 may include multiple layers of material that may be selected to serve different purposes. In some embodiments, some or all of the conductive contacts may be formed of aluminum, and may include a layer of gold (e.g., with a thickness of less than 1 micron) between the aluminum and the adjacent interconnect to limit the oxidation of the surface of the contacts and improve the adhesion with adjacent solder. In some embodiments, some or all of the conductive contacts may be formed of aluminum, and may include a layer of a barrier metal such as nickel, as well as a layer of gold, wherein the layer of barrier metal is disposed between the aluminum and the layer of gold, and the layer of gold is disposed between the barrier metal and the adjacent interconnect. In such embodiments, the gold may protect the barrier metal surface from oxidation before assembly, and the barrier metal may limit the diffusion of solder from the adjacent interconnects into the aluminum.

[0049] In some embodiments, the conductive pathways included in the die assembly 800 may include superconducting materials. Example superconducting materials that may be used for the structures in these conductive pathways (and/or conductive contacts) may include aluminum, niobium, tin, titanium, osmium, zinc, molybdenum, tantalum, vanadium, or composites of such materials (e.g., niobium-titanium, niobium-aluminum, or niobium-tin). In some embodiments, the conductive contacts may include aluminum, and the solder may include an indium-based solder.

[0050] In some embodiments, the structures and materials in the active qubit die 802 and/or the quantum state detector die 804 may be damaged if exposed to the high temperatures that are common in conventional integrated circuit processing (e.g., greater than 100 degrees Celsius, or greater than 200 degrees Celsius). In particular, in embodiments in which the die-to-die interconnects 828 or the first level interconnects 830 include solder, the solder may be a low-temperature solder (e.g., a solder having a melting point below 100 degrees Celsius) so that it can be melted to couple the associated conductive contacts without having to expose the components in the die assembly 800 to higher temperatures and risk of damage. Examples of solders that may be suitable include indium-based solders (e.g., solders including indium alloys). When low-temperature solders are used, however, these solders may not be fully solid during handling of the die assembly 800 (e.g., at room temperature or temperatures between room temperature and 100 degrees Celsius), and thus the solder of the die-to-die interconnects 828 or the first level interconnects 830 alone may not reliably mechanically couple the associated components. In some such embodiments, the die assembly 800 may further include a mechanical stabilizer to maintain mechanical coupling between the components of the die assembly 800, even when the low-temperature solder is not solid. Examples of mechanical stabilizers may include an underfill material disposed between adjacent components, a corner glue disposed between adjacent components, an overmold material disposed around adjacent components, and/or a mechanical frame to secure the adjacent components.

[0051] As noted above, different types of active qubit devices 836 may be used to generate the "active" quantum dots in the device assembly 800, and different types of detector devices 838 may be used to detect the quantum state of these active quantum dots. Discussed below are a number of embodiments of gate-stack devices 100 and SET devices 500. Any of the gate-stack devices 100 disclosed herein may be included in the active qubit devices 836 and/or the detector devices 838; similarly, any of the SET devices 500 disclosed herein may be included in the active qubit devices 836 and/or the detector devices 838. Additionally, any desired combination of the gate-stack devices 100 and/or the SET devices 500 may be used in the active qubit devices 836 and/or the detector devices 838. Other quantum dot formation/detection devices may be included in the die assembly 800 as active qubit devices 836 and/or detector devices 838. For example, in some embodiments, the detector devices 838 may include one or more quantum point contacts (QPCs).

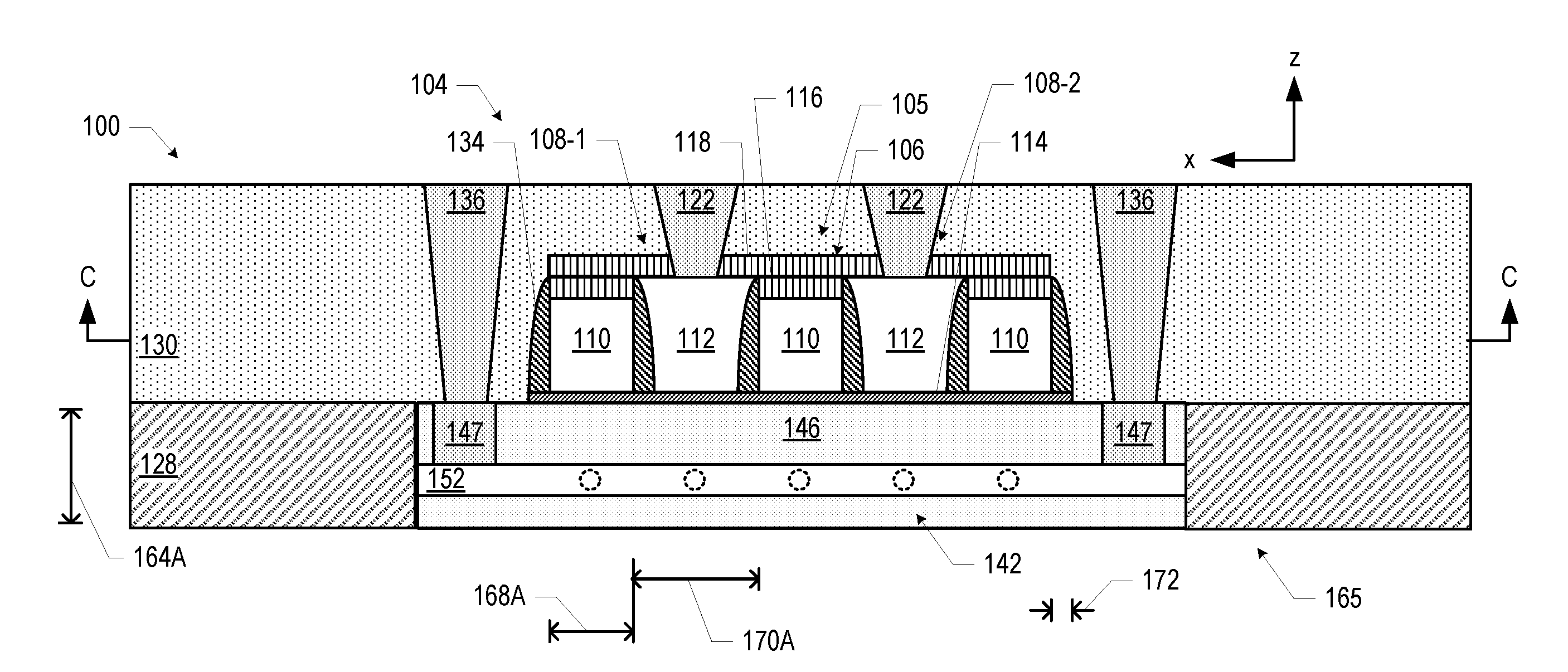

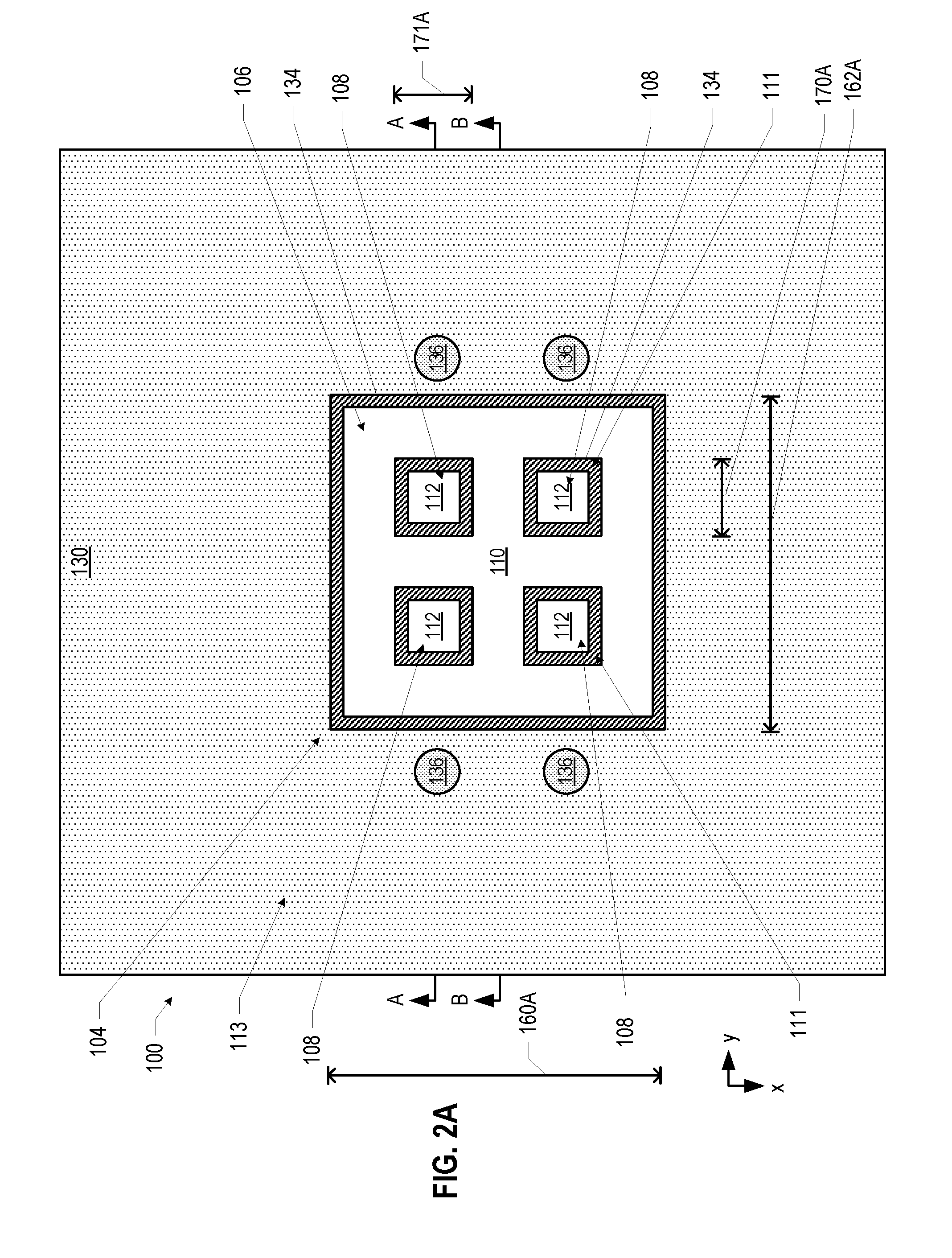

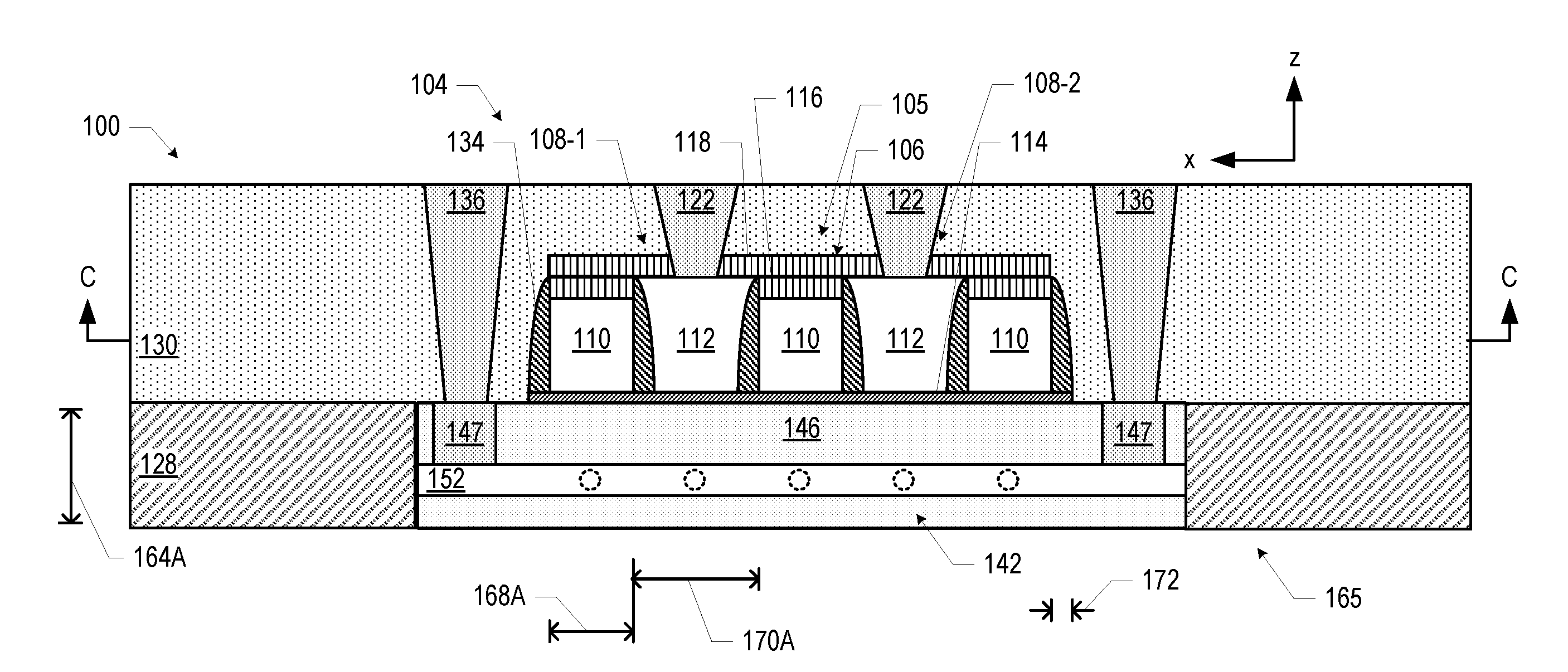

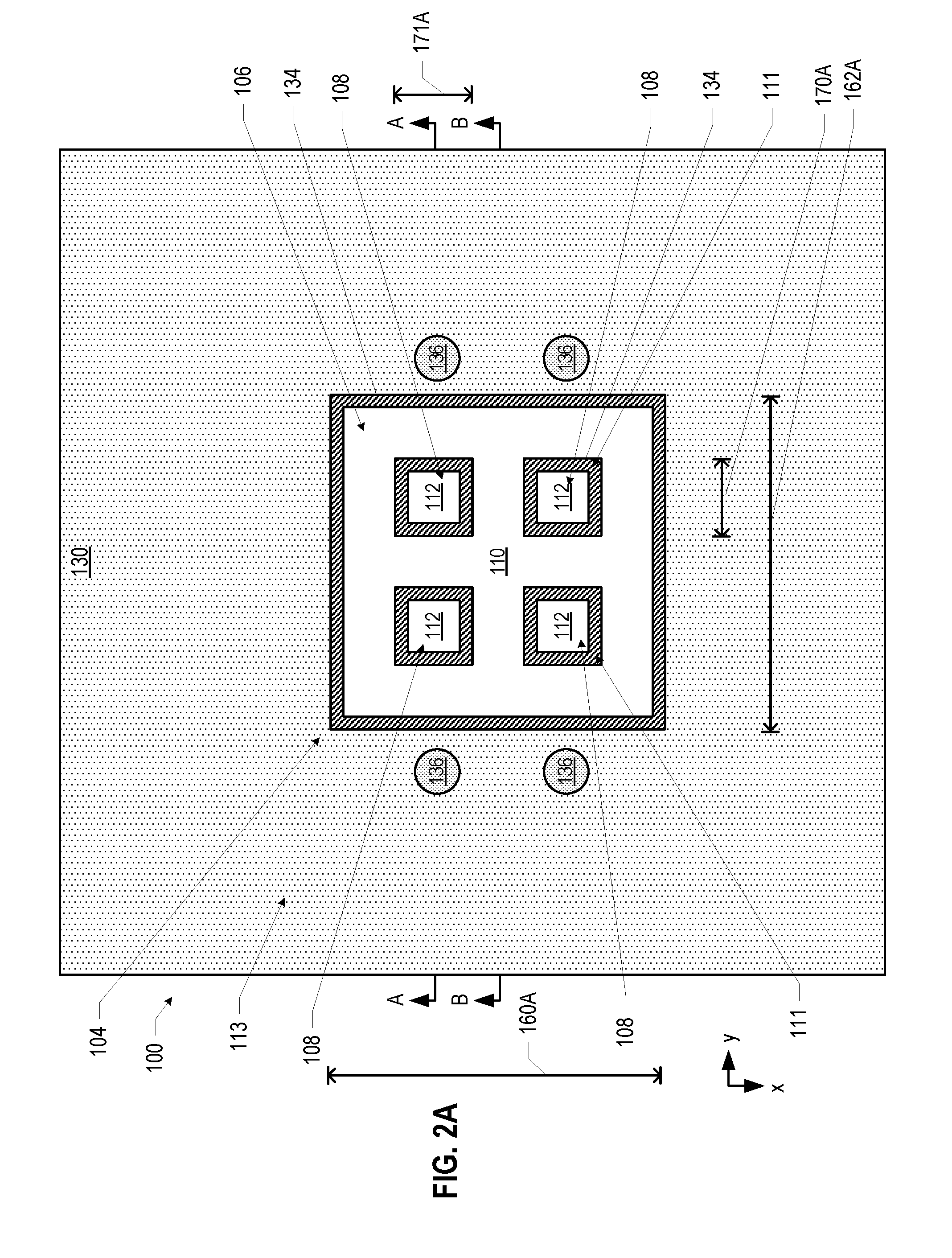

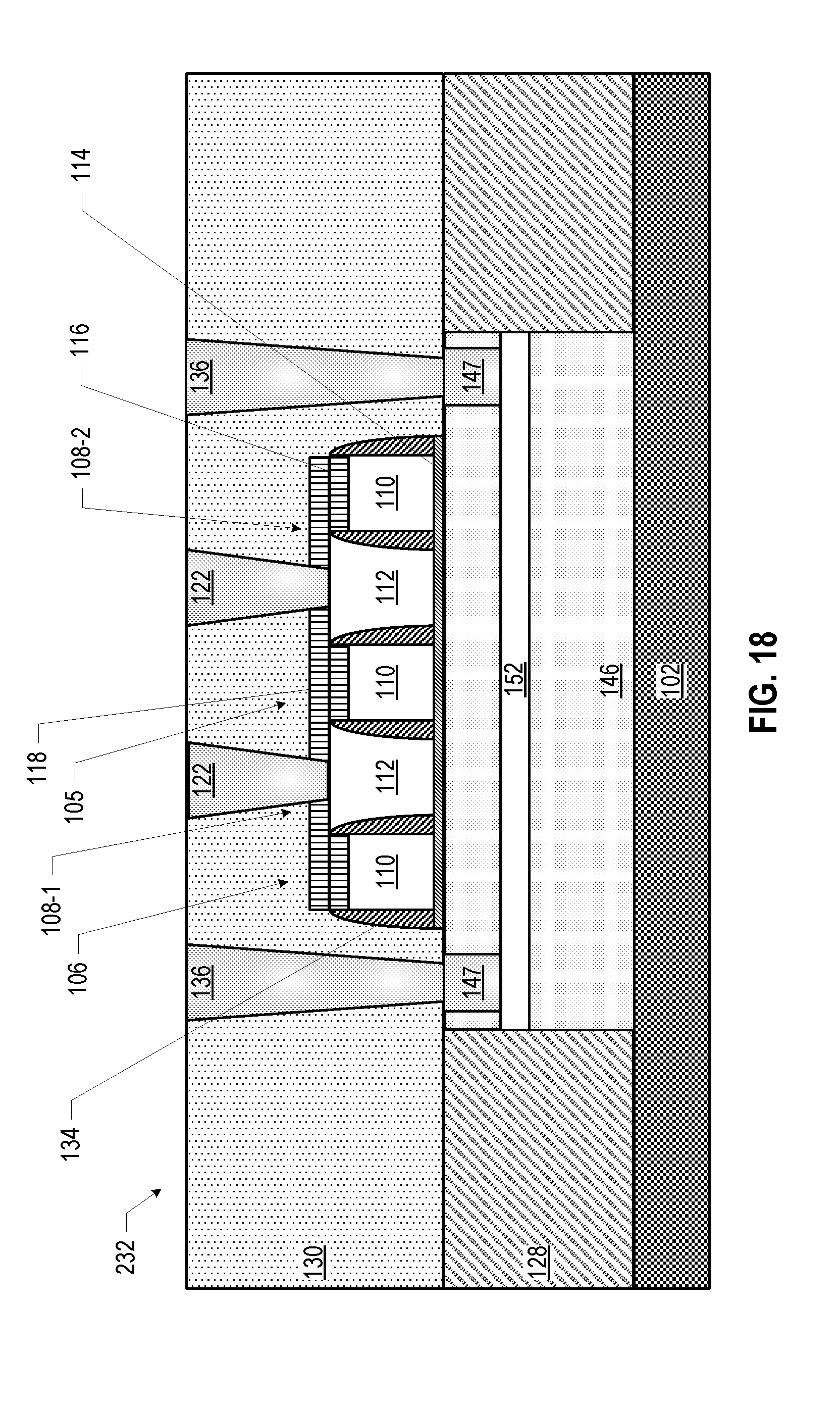

[0052] FIGS. 2A, 2B, and 2C are cross-sectional views of a gate-stack device 100, in accordance with various embodiments. In particular, FIG. 2B illustrates the gate-stack device 100 taken along the section A-A of FIG. 2A, and FIG. 2C illustrates the gate-stack device 100 taken along the section B-B of FIG. 2A (while FIG. 2A illustrates the gate-stack device 100 taken along the section C-C of FIGS. 2B and 2C. FIG. 2A may be considered a "top" cross-sectional view, and FIGS. 2B and 2C may be considered "side" cross-sectional views, although as noted above, such descriptions are used to facilitate the discussion and are not intended to restrict the application of disclosed embodiments. As noted above, the gate-stack device 100 illustrated in FIG. 2 may be included in the active qubit devices 836, the detector devices 838, or both, as desired. When the gate-stack device 100 of FIG. 2 is included in the active qubit devices 836, the face 165 of the gate-stack device 100 may provide (or be oriented towards) the first face 806 of the active qubit die 802 of the die assembly 800. When the gate-stack device 100 of FIG. 2 is included in the detector devices 838, the face 165 of the gate-stack device 100 may provide (or be oriented towards) the first face 810 of the quantum state detector die 804 of the die assembly 800.

[0053] The gate-stack device 100 may include one or more quantum dot formation regions 104 spaced apart by insulating material 128 (e.g., silicon oxide). Although only a single quantum dot formation region 104 is shown in FIG. 2, this is simply for ease of illustration, and more than one quantum dot formation region 104 may be included in the gate-stack device 100 (e.g., as discussed below with reference to FIG. 39). The quantum dot formation regions 104 may include a quantum well stack 146, which may be a quantum well stack including one or more quantum well layers 152. In some embodiments, as discussed below, the quantum well stack 146 may be a modulation doped stack, including one or more doped layers 137 (not illustrated in FIG. 2), and one or more barrier layers 154 (not illustrated in FIG. 2) disposed between the quantum well layer(s) 152 and the doped layer(s) 137. The relative position of the quantum well layer 152 in FIG. 2B (and in others of the accompanying drawings) is intended to represent the inclusion of the quantum well layer 152 in the quantum well stack 146, and particular arrangements of various components of the quantum well stack 146 are discussed in detail below with reference to FIGS. 37-39.

[0054] As noted above, each of the quantum dot formation regions 104 may include one or more quantum well layers 152. A quantum well layer 152 included in the quantum dot formation regions 104 may be arranged normal to the z-direction, and may provide a layer in which a two-dimensional electron gas (2DEG) may form to enable the generation of a quantum dot during operation of the gate-stack device 100, as discussed in further detail below. A quantum well layer 152 itself may provide a geometric constraint on the z-location of quantum dots in the quantum dot formation regions 104. To control the x-location and the y-location of quantum dots in the quantum dot formation regions 104, voltages may be applied to gates disposed on the quantum dot formation regions 104 to adjust the energy profile along the quantum dot formation regions 104 in the x-direction and the y-direction and thereby constrain the x-location and y-location of quantum dots within quantum wells (discussed in detail below with reference to the gates 106/108). The dimensions of the quantum dot formation regions 104 may take any suitable values. The x-length 160A and the y-length 162A, for example, may depend on the number and arrangement of gates included in the quantum dot formation region 104. In some embodiments, the z-length 164A of the quantum well stack 146 included in a quantum dot formation region 104 may be between 200 and 400 nanometers (e.g., between 250 and 350 nanometers, or equal to 300 nanometers). Insulating material and conductive pathways may be present in the peripheral region 113 around a quantum dot formation region 104, as discussed in detail below.

[0055] Multiple gates may be disposed in each of the quantum dot formation regions 104. In particular, a set of gates 105 may be disposed at the "top" of each quantum dot formation region 104. In the embodiment illustrated in FIG. 2, the set of gates 105 includes a gate 106 and four gates 108. This particular number of gates is simply illustrative, and any suitable number and arrangement of gates may be used. For example, a set of gates 105 may include three or more gates 108, arranged in any desired arrangement (e.g., as vertices of triangles or other polygons, in a rectangular or other array, in an irregular arrangement on the quantum well stack 146, etc.). Additionally, as discussed below with reference to FIG. 39, multiple quantum dot formation regions 104 may be included in a gate-stack device 100, as desired.

[0056] As shown in FIG. 2, the gate 108-1 may be disposed in an opening 111 in the gate 106, and the gate 108-2 may be disposed in a different opening 111 in the gate 106. Reference to a "gate 108" herein may refer to any of the gates 108.

[0057] A set of gates 105 may include multiple gates 108 that include at least one pair of gates spaced apart from each other in a first dimension (e.g., spaced apart from each other in the x-dimension), and at least one pair of gates spaced apart from each other in a second dimension perpendicular to the first dimension (e.g., spaced apart from each other in the y-dimension). A two-dimensional regular array of spaced-apart gates 108 is one example of such an arrangement (e.g., as illustrated in FIG. 2), but many others exist (e.g., an irregular array or other distribution). These pairs may share a gate; for example, three gates may satisfy this description if arranged accordingly. In the embodiment illustrated in FIG. 2, the gates 108 in a set 105 are spaced apart by intervening portions of the gate 106 in the set 105; in other embodiments, other materials or structures may be disposed between pairs of gates 108 in a set 105.

[0058] In the embodiment illustrated in FIG. 2A, from a top view, the gate metal 110 of the gates 106 may be shaped substantially as a "grid" having openings 111 in which the gate metal 112 of the gates 108 are at least partially disposed. Such a grid may have one or more cross-shaped portions (between a set of four adjacent openings 111) and a perimeter portion (extending around the collection of openings 111). As noted elsewhere herein, the gate metal 110 of the gates 106 may be patterned in any suitable way to define the location and shape of the gates 106 and the locations and shapes of the gates 108.

[0059] Each of the gates 106/108 may include a gate dielectric 114. In the embodiment illustrated in FIG. 2, the gate dielectric 114 for all of the gates 106/108 in a particular set of gates 105 is provided by a common layer of gate dielectric material. In other embodiments, the gate dielectric 114 for each of the gates 106/108 in a particular set of gates 105 may be provided by separate portions of gate dielectric 114 (e.g., as discussed below with reference to FIGS. 31-33). In some embodiments, the gate dielectric 114 may be a multilayer gate dielectric (e.g., with multiple materials used to improve the interface between the quantum well stack 146 and the corresponding gate metal). The gate dielectric 114 may be, for example, silicon oxide, aluminum oxide, or a high-k dielectric, such as hafnium oxide. More generally, the gate dielectric 114 may include elements such as hafnium, silicon, oxygen, titanium, tantalum, lanthanum, aluminum, zirconium, barium, strontium, yttrium, lead, scandium, niobium, and zinc. Examples of materials that may be used in the gate dielectric 114 may include, but are not limited to, hafnium oxide, hafnium silicon oxide, lanthanum oxide, lanthanum aluminum oxide, zirconium oxide, zirconium silicon oxide, tantalum oxide, titanium oxide, barium strontium titanium oxide, barium titanium oxide, strontium titanium oxide, yttrium oxide, aluminum oxide, tantalum oxide, tantalum silicon oxide, lead scandium tantalum oxide, and lead zinc niobate. In some embodiments, an annealing process may be carried out on the gate dielectric 114 to improve the quality of the gate dielectric 114.

[0060] The gate 106 may include a gate metal 110 and a hardmask 116. The hardmask 116 may be formed of silicon nitride, silicon carbide, or another suitable material. The gate metal 110 may be disposed between the hardmask 116 and the gate dielectric 114, and the gate dielectric 114 may be disposed between the gate metal 110 and the quantum well stack 146. Only one portion of the hardmask 116 is labeled in FIGS. 2B and 2C for ease of illustration. In some embodiments, the hardmask 116 may not be present in the gate-stack device 100 (e.g., a hardmask like the hardmask 116 may be removed during processing, as discussed below). In some embodiments, the gate metal 110 may be a superconductor, such as aluminum, titanium nitride (e.g., deposited via atomic layer deposition), or niobium titanium nitride. The sides of the gate metal 110 may be substantially parallel, as shown in FIGS. 2B and 2C, and insulating spacers 134 may be disposed on the sides of the gate metal 110. As illustrated in FIGS. 2B and 2C, the spacers 134 may be thinner farther from the quantum well stack 146 and thicker closer to the quantum well stack 146. In some embodiments, the spacers 134 may have a convex shape. The spacers 134 may be formed of any suitable material, such as a carbon-doped oxide, silicon nitride, silicon oxide, or other carbides or nitrides (e.g., silicon carbide, silicon nitride doped with carbon, and silicon oxynitride).

[0061] Each of the gates 108 may include a gate metal 112 and a hardmask 118. The hardmask 118 may be formed of any of the materials discussed above with reference to the hardmask 116. The gate metal 112 may be disposed between the hardmask 118 and the gate dielectric 114, and the gate dielectric 114 may be disposed between the gate metal 112 and the quantum well stack 146. In the embodiment illustrated in FIGS. 2B and 2C, the hardmask 118 may extend over the hardmask 116 (and over the gate metal 110 of the gate 106), while in other embodiments, the hardmask 118 may not extend over the gate metal 110. The gate dielectric 114 may be disposed between the gate metal 112 and the quantum well stack 146. In some embodiments, the gate metal 112 may be a different metal from the gate metal 110; in other embodiments, the gate metal 112 and the gate metal 110 may have the same material composition. In some embodiments, the gate metal 112 may be a superconductor, such as aluminum, titanium nitride (e.g., deposited via atomic layer deposition), or niobium titanium nitride. In some embodiments, the hardmask 118 may not be present in the gate-stack device 100 (e.g., a hardmask like the hardmask 118 may be removed during processing, as discussed below).

[0062] The gate 108-1 may extend between the proximate spacers 134 on the sides of the corresponding opening 111 in the gate 106, as shown. In some embodiments, the gate metal 112 of the gate 108-1 may extend between the spacers 134 on the sides of the corresponding opening 111. Thus, the gate metal 112 of the gate 108-1 may have a shape that is substantially complementary to the shape of the spacers 134, as shown. Similarly, the gate 108-2 may extend between the proximate spacers 134 on the sides of the corresponding opening 111. In some embodiments in which the gate dielectric 114 is not a layer shared commonly between the associated gates 106 and 108, but instead is separately deposited on the quantum well stack 146 between the associated spacers 134, the gate dielectric 114 may extend at least partially up the sides of the associated spacers 134, and the gate metal 112 may extend between the portions of the associated gate dielectric 114 on the associated spacers 134.

[0063] The dimensions of the gates 106/108 may take any suitable values. For example, in some embodiments, the z-height 166A of the gate metal 110 may be between 40 and 75 nanometers (e.g., approximately 50 nanometers); the z-height of the gate metal 112 may be in the same range. In some embodiments (e.g., the embodiment illustrated in FIG. 2B), the z-height of the gate metal 112 may be greater than the z-height of the gate metal 110. In some embodiments, the x-length 168A of the gate metal 110 in the cross section of FIG. 2B may be between 20 and 40 nanometers (e.g., 30 nanometers). In some embodiments, the x-length 170A of the openings 111 in the gates 106 may be between 40 and 60 nanometers (e.g., 50 nanometers); the y-length 171A of the openings 111 may take any of the values described herein for the x-length 170A, for example. In some embodiments, the thickness 172 of the spacers 134 may be between 1 and 10 nanometers (e.g., between 3 and 5 nanometers, between 4 and 6 nanometers, or between 4 and 7 nanometers). The x-length of the gate metal 112 may depend on the dimensions of the gates 106 and the spacers 134, as illustrated in FIG. 2B.

[0064] During operation of the gate-stack device 100, voltages may be applied to the gates 106/108 to adjust the potential energy in the quantum well layer 152 in the quantum dot formation region 104 to create quantum wells of varying depths in which quantum dots 142 may form. Only one quantum dot 142 is labeled with a reference numeral in FIG. 2B for ease of illustration, but five are indicated as dotted circles in the quantum well layer 152 of the quantum well stack 146. In some embodiments, the quantum well stack 146 and the quantum well layer 152 may be sized and spaced so that the distance between the quantum well layer 152 and the face 165 is less than 100 nanometers; when the gate-stack device 100 is included in the die 802 or 804 in the die assembly 800, the distance between the quantum well layer 152 and the die 804 or 802, respectively, may be less than 200 nanometers.

[0065] The spacers 134 may themselves provide "passive" barriers between quantum wells under the gates 106/108 in the quantum well layer 152, and the voltages applied to different ones of the gates 106/108 may adjust the potential energy under the gates 106/108 in the quantum well layer; decreasing the potential energy may form quantum wells, while increasing the potential energy may form quantum barriers.

[0066] In some embodiments, the gate-stack device 100 may include a reservoir of charge carriers. These charge carriers may flow through the quantum well layer 152, and may be "trapped" to form quantum dots 142, as discussed above. In some embodiments, one or more reservoirs of charge carriers may be disposed in the peripheral region 113 of the gate-stack device 100, and the quantum well layer 152 may extend into the reservoirs. Such reservoirs may be formed by, e.g., heavily doping appropriate regions of the gate-stack device 100 (e.g., by ion implantation). As noted above, in some embodiments, the quantum well stack 146 may include one or more doped layers 137 (not shown in FIG. 2) that may serve as a reservoir of charge carriers for the gate-stack device 100 (and thus the quantum well stack 146 may be a "modulation doped stack"). For example, an n-type doped layer may supply electrons for electron-type quantum dots 142, and a p-type doped layer may supply holes for hole-type quantum dots 142. A doped layer 137 may be spaced apart from the quantum well layer 152 in the quantum well stack 146 (e.g., by a barrier layer 154, also not shown in FIG. 2) to allow charge carriers to flow into the quantum well layer 152 without "contaminating" the quantum well layer 152 with the ionized impurities that would be present in the quantum well layer 152 if it were directly doped. Examples of doped layers 137, barrier layers 154, and quantum well layers 152 are discussed in detail below (e.g., with reference to FIGS. 37-39).

[0067] The gate-stack devices 100 disclosed herein may be used to form electron-type or hole-type quantum dots 142. Note that the polarity of the voltages applied to the gates 106/108 to form quantum wells/barriers depend on the charge carriers used in the gate-stack device 100. In embodiments in which the charge carriers are electrons (and thus the quantum dots 142 are electron-type quantum dots), amply negative voltages applied to a gate 106/108 may increase the potential barrier under the gate 106/108, and amply positive voltages applied to a gate 106/108 may decrease the potential barrier under the gate 106/108 (thereby forming a potential well in the associated quantum well layer 152 in which an electron-type quantum dot 142 may form). In embodiments in which the charge carriers are holes (and thus the quantum dots 142 are hole-type quantum dots), amply positive voltages applied to a gate 106/108 may increase the potential barrier under the gate 106/108, and amply negative voltages applied to a gate 106/108 may decrease the potential barrier under the gate 106/108 (thereby forming a potential well in the associated quantum well layer 152 in which a hole-type quantum dot 142 may form). The gate-stack devices 100 disclosed herein may be used to form electron-type or hole-type quantum dots.

[0068] Voltages may be applied to each of the gates 106 and 108 separately to adjust the potential energy in the quantum well layer under the gates 106 and 108, and thereby control the formation of quantum dots 142 under each of the gates 106 and 108. Additionally, the relative potential energy profiles under different ones of the gates 106 and 108 allow the gate-stack device 100 to tune the potential interaction between quantum dots 142 under adjacent gates. For example, if two adjacent quantum dots 142 (e.g., one quantum dot 142 under a gate 108 and another quantum dot 142 under an adjacent gate 108) are separated by only a short potential barrier, the two quantum dots 142 may interact more strongly than if they were separated by a taller potential barrier. Since the depth of the potential wells/height of the potential barriers under each gate 106/108 may be adjusted by adjusting the voltages on the respective gates 106/108 and neighboring gates, the differences in potential between various gates 106/108 may be adjusted, and thus the interaction tuned. In some applications, the gates 108 may be used as plunger gates to enable the formation of quantum dots 142 under the gates 108, while the gates 106 may be used as barrier gates to adjust the potential barrier between quantum dots 142 formed under adjacent gates 108.

[0069] Conductive vias and lines may make contact with the gates 106/108, and with the quantum well stack 146, to enable electrical connection to the gates 106/108 and the quantum well stack 146 to be made in desired locations. As shown in FIG. 2, the gate 106 may extend away from the quantum well stack 146, and conductive vias 120 may contact the gate 106. The conductive vias 120 may extend through the hardmask 116 and the hardmask 118 to contact the gate metal 110 of the gate 106. The gates 108 may extend away from the quantum well stack 146, and conductive vias 122 may contact the gates 108. The conductive vias 122 may extend through the hardmask 118 to contact the gate metal 112 of the gates 108.

[0070] In some embodiments, the gate-stack device 100 may include conductive pathways (including, e.g., vias and lines) to the quantum well layer 152 of the quantum well stack 146. In other embodiments, the gate-stack device 100 may not include such conductive pathways to the quantum well layer 152 of the quantum well stack 146. Embodiments of the gate-stack device 100 that do include conductive pathways to the quantum well layer 152 may use the conductive pathways to couple the quantum well layer 152 to additional sources/drains of carriers (not shown), which may be provided by implant doping or outer accumulation gates, for example. Such conductive pathways may not be needed (and may thus be beneficially omitted for manufacturing simplicity) when doped layer 137 of a modulation doped stack are able to provide an adequate volume of carriers to the quantum well layer 152.

[0071] In some embodiments in which the quantum well stack 146 is a modulation doped stack, the gate-stack device 100 may include conductive pathways (including, e.g., vias and lines) to the doped layer 137 of the quantum well stack 146. In other embodiments, the gate-stack device 100 may not include such conductive pathways to the doped layer 137 of the quantum well stack 146. Embodiments of the gate-stack device 100 that do include conductive pathways to the doped layer 137 may use the conductive pathways to provide further carriers to the doped layer 137; for example, after parent donor atoms have donated their electrons, more electrons may be provided to the doped layer 137 by an appropriate voltage provided to the doped layer 137 through conductive pathways. Providing conductive pathways to the doped layer 137, therefore, may allow the carrier density in the doped layer 137 to be dynamically adjusted. Such conductive pathways may be omitted, in some embodiments, for manufacturing simplicity.

[0072] Various ones of the accompanying drawings depict conductive pathways to the quantum well stack 146 for illustrative purposes. These conductive pathways, discussed below, may make electrical contact with the quantum well layer 152 and/or the doped layer 137, and additional conductive pathways like those illustrated may be included to make any desired combination of contacts. As noted above, in some embodiments, no conductive pathways may extend to the quantum well layer 152 or the doped layer 137, and thus the pathways to the quantum well stack 146 illustrated in various ones of the accompanying drawings may be omitted.

[0073] In the embodiment illustrated in FIG. 2, a conductive pathway to the quantum well layer 152 and/or a doped layer 137 (not shown) may include conductive vias 136 (extending through the insulating material 130) and conductive bridges 147-1 (extending into the quantum well stack 146). In the embodiment illustrated in FIG. 2, the conductive bridges 147 may be formed by ion implantation of dopants (e.g., n-type or p-type dopants, as appropriate) into the quantum well stack 146 so as to form a conductive region between the conductive vias 136 and the quantum well layer 152 and/or a doped layer 137 (not shown) (e.g., as discussed below). The conductive bridges 147 may take any of the forms discussed herein. In other embodiments, conductive pathways to one or more components in the quantum well stack 146 may take other forms (e.g., as discussed below).

[0074] The gate-stack device 100 may include further conductive vias and/or lines (not shown) to make electrical contact to the gates 106/108 and/or the quantum well stack 146, as desired. The conductive vias and lines included in a gate-stack device 100 may include any suitable materials, such as copper, tungsten (deposited, e.g., by CVD), or a superconductor (e.g., aluminum, tin, titanium nitride, niobium titanium nitride, tantalum, niobium, or other niobium compounds such as niobium tin and niobium germanium).

[0075] In some embodiments in which the quantum well stack 146 is a modulation doped stack, during operation, a bias voltage may be applied to the quantum well layers 152 (e.g., through the appropriate conductive pathways) to cause current to flow through the quantum well layers 152. When the doped layers 137 are doped with an n-type material, this voltage may be positive; when the doped layers 137 are doped with a p-type material, this voltage may be negative. The magnitude of this bias voltage may take any suitable value (e.g., between 0.25 volts and 2 volts). Layers other than the quantum well layer 152 in the quantum well stack 146 (e.g., the doped layer 137 of the quantum well stack 146) may have higher threshold voltages for conduction than the quantum well layer 152 so that when the quantum well layer 152 is biased at its threshold voltages, the quantum well layer 152 conducts and the other layers of the quantum well stack 146 do not. This may avoid parallel conduction in both the quantum well layer 152 and the other layers, and thus avoid compromising the strong mobility of the quantum well layer 152 with conduction in layers having inferior mobility.

[0076] The conductive vias 120, 122, and 136 may be electrically isolated from each other by various insulating materials, including the insulating material 130, as shown. The insulating material 130 may be any suitable material, such as an interlayer dielectric (ILD). Examples of the insulating material 130 may include silicon oxide, silicon nitride, aluminum oxide, carbon-doped oxide, and/or silicon oxynitride. As known in the art of integrated circuit manufacturing, conductive vias and lines may be formed in an iterative process in which layers of structures are formed on top of each other. In some embodiments, the conductive vias 120/122/136 may have a width that is 20 nanometers or greater at their widest point (e.g., 30 nanometers), and a pitch of 80 nanometers or greater (e.g., 100 nanometers). In some embodiments, conductive lines (not shown in FIG. 2) included in the gate-stack device 100 may have a width that is 100 nanometers or greater, and a pitch of 100 nanometers or greater. The particular arrangement of conductive vias and lines shown in FIG. 2 is simply illustrative, and any electrical routing arrangement may be implemented.

[0077] In embodiments in which the gate-stack device 100 is an active qubit device 836 in the active qubit die 802, the quantum dots 142 in the quantum well layer 152 may be used as "active" quantum dots in the sense that these quantum dots 142 act as qubits and are controlled (e.g., by voltages applied to the gates 106/108) to perform quantum computations. In embodiments in which the gate-stack device 100 is a detector device 838 in the quantum state detector die 804, the quantum dots 142 in the quantum well layer 152 may be used as "read" quantum dots in the sense that these quantum dots 142 may sense the quantum state of the "active" quantum dots formed by the active qubit devices 836 in the active qubit die 802 by detecting the electric field generated by the charge in the active quantum dots, and may convert the quantum state of the active quantum dots into electrical signals that may be detected by the gates 106/108.

[0078] The gate-stack devices 100 disclosed herein may be manufactured using any suitable techniques. FIGS. 3-19 illustrate various example stages in the manufacture of the gate-stack device 100 of FIG. 2, in accordance with various embodiments. Although the particular manufacturing operations discussed below with reference to FIGS. 3-19 are illustrated as manufacturing a particular embodiment of the gate-stack device 100, these operations may be applied to manufacture many different embodiments of the gate-stack device 100, as discussed herein. Any of the elements discussed below with reference to FIGS. 3-19 may take the form of any of the embodiments of those elements discussed above (or otherwise disclosed herein). For ease of illustration, not all elements in each of FIGS. 3-19 are expressly labeled with reference numerals, but reference numerals for each element are included among the drawings of FIGS. 3-19.

[0079] FIG. 3 illustrates a cross-sectional view of an assembly 202 including a base 102. The base 102 may include any suitable semiconductor material or materials, or any other suitable structure on which to perform the subsequent operations. In some embodiments, the base 102 may include a semiconductor material. For example, the base 102 may include silicon (e.g., may be formed from a silicon wafer).

[0080] FIG. 4 illustrates a cross-sectional view of an assembly 204 subsequent to providing a quantum well stack 146 on the base 102 of the assembly 202 (FIG. 3). The quantum well stack 146 may include at least one quantum well layer 152. When the quantum well stack 146 is a modulation doped stack, the quantum well stack 146 may also include at least one doped layer 137 (not shown), and at least one barrier layer 154 (not shown). As discussed above, a 2DEG may form in the quantum well layer 152 during operation of the gate-stack device 100. Various embodiments of the quantum well stack 146 are discussed below with reference to FIGS. 37-39.

[0081] FIG. 5 illustrates a cross-sectional view of an assembly 206 subsequent to etching the quantum well stack 146 of the assembly 204 (FIG. 4) into a desired shape, then providing an insulating material 128 around the etched quantum well stack 146. The size and shape of the quantum well stack 146 after etching may take any suitable form (e.g., the substantially rectangular solid form illustrated in FIG. 2 and FIGS. 5-6). The quantum well stack 146 may be patterned and etched using any suitable technique known in the art. For example, a combination of dry and wet etch chemistry may be used to shape the quantum well stack 146, and the appropriate chemistry may depend on the materials included in the assembly 204, as known in the art. Any suitable material may be used as the insulating material 128 to electrically insulate the quantum well stack 146. As noted above, in some embodiments, the insulating material 128 may be a dielectric material, such as silicon oxide. Although the etched quantum well stacks 146 are illustrated in FIG. 5 as substantially rectangular with parallel sidewalls, this is simply for ease of illustration, and the etched quantum well stacks 146 may have any suitable shape (e.g., a shape appropriate to the manufacturing processes used to shape the quantum well stacks 146). For example, in some embodiments, the etched quantum well stacks 146 may be tapered, narrowing as they extend away from the base 102 (FIG. 5). In some embodiments, the quantum well stacks 146 may taper by 3-10 nanometers in x-width for every 100 nanometers in z-height (e.g., 5 nanometers in x-width for every 100 nanometers in z-height).

[0082] FIG. 6A illustrates a cross-sectional view of an assembly 208 subsequent to planarizing the assembly 206 (FIG. 5) to remove the insulating material 128 above the quantum well stack 146. In some embodiments, the assembly 206 may be planarized into the assembly 208 using a chemical mechanical polishing (CMP) technique.

[0083] FIG. 6B is a perspective view of at least a portion of the assembly 208, showing the quantum well stack 146 extending from the base 102 and laterally insulated by the insulating material 128. FIG. 6C is another cross-sectional view of the assembly 208.

[0084] FIG. 7 is a cross-sectional view of an assembly 210 subsequent to forming a gate stack 174 on the quantum well stack 146 of the assembly 208 (FIG. 6). The gate stack 174 may include the gate dielectric 114, the gate metal 110, and a hardmask 116. The hardmask 116 may be formed of an electrically insulating material, such as silicon nitride or carbon-doped nitride.

[0085] FIG. 8 is a cross-sectional view of an assembly 212 subsequent to patterning the hardmask 116 of the assembly 210 (FIG. 7). The pattern applied to the hardmask 116 may correspond to the locations for the gate 106, as discussed below. The hardmask 116 may be patterned by applying a resist, patterning the resist using lithography, and then etching the hardmask (using dry etching or any appropriate technique).

[0086] FIG. 9A is a cross-sectional view of an assembly 214 subsequent to etching the assembly 212 (FIG. 8) to remove the gate metal 110 that is not protected by the patterned hardmask 116 to form the gate 106. In some embodiments, as illustrated in FIG. 9A, the gate dielectric 114 may remain after the etched gate metal 110 is etched away; in other embodiments, the gate dielectric 114 may also be etched during the etching of the gate metal 110. Etching the gate metal 110 may form openings 111 in the gate metal 110 (and the hardmask 116) that extend down to the gate dielectric 114. FIG. 9B is a top view of the assembly 214, depicting the openings 111 as substantially rectangular in footprint. Although a particular number of particular shapes of the openings 111 are illustrated in FIG. 9 in a particular arrangement, this is simply an illustrative embodiment and the openings 111 may have any desired and appropriate shape (e.g., a footprint that is circular, square, an oval, a polygon, etc.), number, or arrangement (e.g., in a rectangular array, a non-rectangular array, a regular or irregular arrangement, etc.).

[0087] FIG. 10 is a cross-sectional view of an assembly 216 subsequent to providing spacer material 132 on the assembly 214 (FIG. 9). The spacer material 132 may include any of the materials discussed above with reference to the spacers 134, for example, and may be deposited using any suitable technique. For example, the spacer material 132 may be a nitride material (e.g., silicon nitride) deposited by sputtering. The spacer material 132 may at least partially fill the openings 111.

[0088] FIG. 11 is a cross-sectional view of an assembly 218 subsequent to etching the spacer material 132 of the assembly 216 (FIG. 10), leaving spacers 134 formed of the spacer material 132 on the side faces of the gate 106 (e.g., on the sides of the hardmask 116 and the gate metal 110). The etching of the spacer material 132 may be an anisotropic etch, etching the spacer material 132 "downward" to remove the spacer material 132 on top of the gate 106 and in some of the area between the gate metal 110 of the gate 106 (e.g., at the "bottoms" of the openings 111), while leaving the spacers 134 on the sides of the gate 106. In some embodiments, the anisotropic etch may be a dry etch.

[0089] FIG. 12 is a cross-sectional view of an assembly 220 subsequent to providing the gate metal 112 on the assembly 218 (FIG. 11). The gate metal 112 may fill the openings 111 between adjacent portions of the gate 106, and may extend over the tops of the gate 106 and beyond the outer side faces of the gate 106.

[0090] FIG. 13 is a cross-sectional view of an assembly 222 subsequent to planarizing the assembly 220 (FIG. 12) to remove the gate metal 112 above the gate 106. In some embodiments, the assembly 220 may be planarized to form the assembly 222 using a CMP technique. Some of the remaining gate metal 112 may fill the openings 111 between adjacent portions of the gate 106, while other portions 150 of the remaining gate metal 112 may be located "outside" of the gate 106.

[0091] FIG. 14 is a cross-sectional view of an assembly 224 subsequent to providing a hardmask 118 on the planarized surface of the assembly 222 (FIG. 13). The hardmask 118 may be formed of any of the materials discussed above with reference to the hardmask 116, for example.

[0092] FIG. 15 is a cross-sectional view of an assembly 226 subsequent to patterning the hardmask 118 of the assembly 224 (FIG. 14). The pattern applied to the hardmask 118 may extend over the hardmask 116 (and over the gate metal 110 of the gate 106, as well as over the locations for the gates 108 (as illustrated in FIG. 2B). The hardmask 118 may be non-coplanar with the hardmask 116, as illustrated in FIG. 15. The hardmask 118 illustrated in FIG. 15 may thus be a common, continuous portion of hardmask 118 that extends over all of the hardmask 116; in other embodiments, the hardmask 118 may not be disposed over the entirety of the hardmask 116. The hardmask 118 may be patterned using any of the techniques discussed above with reference to the patterning of the hardmask 116, for example.

[0093] FIG. 16 is a cross-sectional view of an assembly 228 subsequent to etching the assembly 226 (FIG. 15) to remove the portions 150 that are not protected by the patterned hardmask 118 to form the gates 108. Portions of the hardmask 118 may remain on top of the hardmask 116, as shown. The operations performed on the assembly 226 may include removing any gate dielectric 114 that is "exposed" on the quantum well stack 146, as shown. The excess gate dielectric 114 may be removed using any suitable technique, such as chemical etching or silicon bombardment.

[0094] FIG. 17 is a cross-sectional view of an assembly 230 subsequent to providing an insulating material 130 on the assembly 228 (FIG. 16). The insulating material 130 may take any of the forms discussed above. For example, the insulating material 130 may be a dielectric material, such as silicon oxide. The insulating material 130 may be provided on the assembly 228 using any suitable technique, such as spin coating, chemical vapor deposition (CVD), or plasma-enhanced CVD (PECVD). In some embodiments, the insulating material 130 may be polished back after deposition, and before further processing. In some embodiments, the assembly 230 may be planarized to remove the hardmasks 116 and 118, then additional insulating material 130 may optionally be provided on the planarized surface; in such an embodiment, the hardmasks 116 and 118 would not be present in the gate-stack device 100.

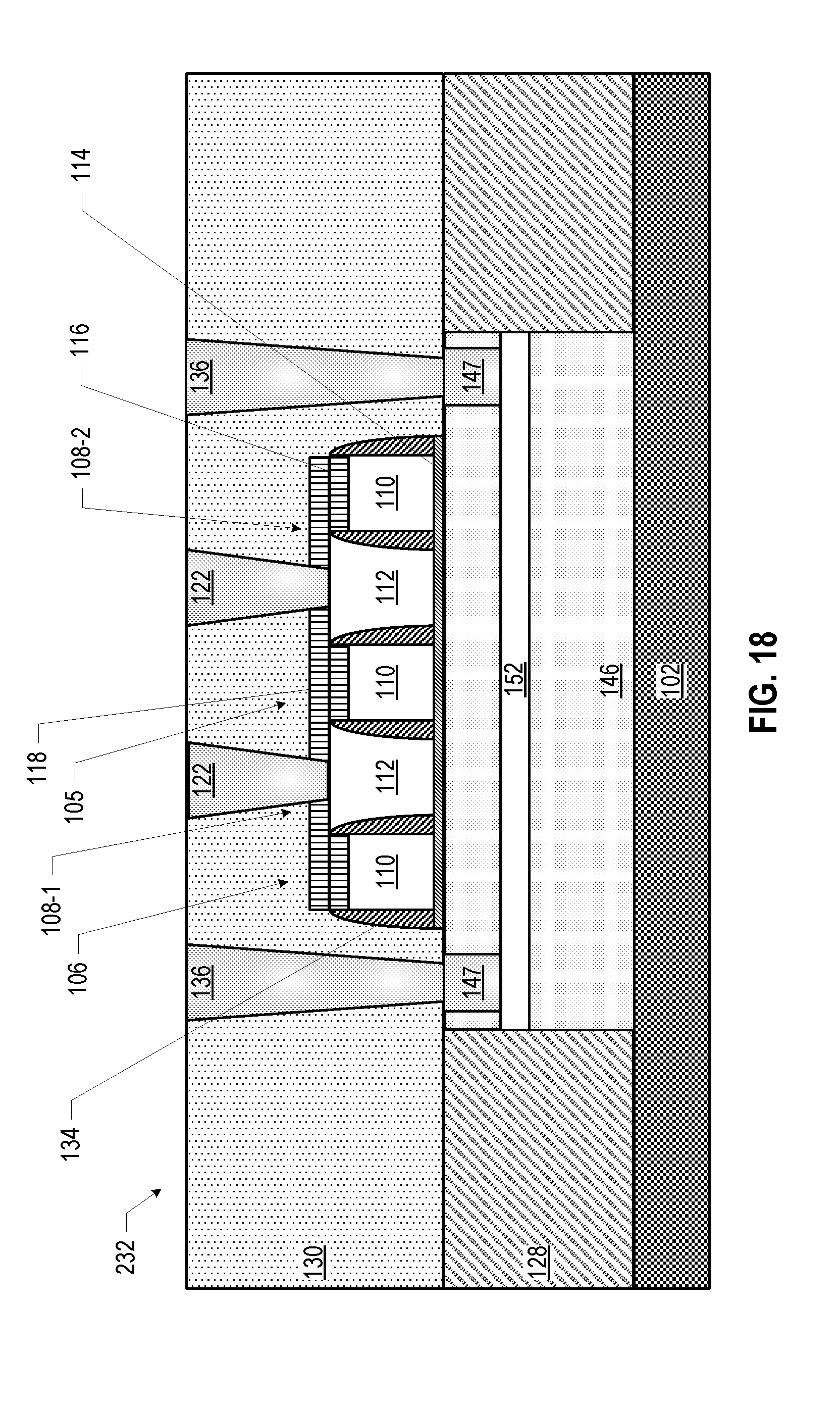

[0095] FIG. 18 is a cross-sectional view of an assembly 232 subsequent to forming conductive vias 122 in electrical contact with the gate metal 112 of the gates 108 of the assembly 230 (FIG. 17), as well as forming conductive vias 120 in electrical contact with the gate metal 110 of the gate 106 (not shown in FIG. 18, but illustrated in FIG. 2C). FIG. 18 also illustrates conductive bridges 147 and conductive vias 136 in electrical contact with the quantum well layer 152 and/or a doped layer 137 (not shown) of the quantum well stack 146. The conductive vias and any desired lines may be formed using any conventional interconnect technique (e.g., forming cavities for the vias, filling the cavities with conductive material for the vias, depositing additional insulating material 130, forming trenches for the lines, filling the trenches with conductive material for the lines, etc.). Generally, conductive vias and lines included in the gate-stack devices 100 disclosed herein may be formed using any suitable additive, subtractive, semi-additive/subtractive, or other known interconnect formation technique. The conductive material included in the assembly 232 may include any suitable ones of the materials disclosed herein (e.g., a superconducting material), and the conductive material may be provided to form the vias and lines using any suitable deposition or growth technique (e.g., sputtering, electroless plating, CVD, ALD, or electroplating).