Display Panel And Manufacturing Method Thereof, Display Device

Wang; Zhen ; et al.

U.S. patent application number 16/118357 was filed with the patent office on 2019-05-30 for display panel and manufacturing method thereof, display device. The applicant listed for this patent is BOE TECHNOLOGY GROUP CO., LTD., Ordos Yuansheng Optoelectronics Co., Ltd.. Invention is credited to Jian Sun, Zhen Wang, Han Zhang.

| Application Number | 20190164996 16/118357 |

| Document ID | / |

| Family ID | 61645773 |

| Filed Date | 2019-05-30 |

| United States Patent Application | 20190164996 |

| Kind Code | A1 |

| Wang; Zhen ; et al. | May 30, 2019 |

DISPLAY PANEL AND MANUFACTURING METHOD THEREOF, DISPLAY DEVICE

Abstract

The present disclosure provides a display panel, a manufacturing method of a display panel, and a display device including the display panel. The display panel includes: an array substrate, including a display region, a non-display region around the display region, and data lines extending into the non-display region; a planarization layer, covering the data lines; and a metal wiring layer, disposed on the planarization layer in the non-display region, and including a plurality of metal wirings spaced apart from each other and corresponding to the data lines.

| Inventors: | Wang; Zhen; (Beijing, CN) ; Sun; Jian; (Beijing, CN) ; Zhang; Han; (Beijing, CN) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 61645773 | ||||||||||

| Appl. No.: | 16/118357 | ||||||||||

| Filed: | August 30, 2018 |

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 27/1222 20130101; H01L 27/124 20130101; H01L 27/1259 20130101; H01L 29/78675 20130101; H01L 27/1248 20130101; H01L 29/78633 20130101 |

| International Class: | H01L 27/12 20060101 H01L027/12; H01L 29/786 20060101 H01L029/786 |

Foreign Application Data

| Date | Code | Application Number |

|---|---|---|

| Nov 27, 2017 | CN | 201711205655.2 |

Claims

1. A display panel, comprising: an array substrate, comprising a display region, a non-display region around the display region, and data lines extending into the non-display region; a planarization layer, covering the data lines; and a metal wiring layer, disposed on the planarization layer in the non-display region, and comprising a plurality of metal wirings spaced apart from each other and corresponding to the data lines.

2. The display panel according to claim 1, further comprising: a first insulating layer, covering the metal wiring layer; a first electrode layer, disposed on the first insulating layer and comprising a plurality of first electrodes corresponding to the metal wirings.

3. The display panel according to claim 2, wherein the first electrode layer and a pixel electrode in the display region are disposed in a same layer.

4. The display panel according to claim 3, wherein a second insulating layer is disposed between the planarization layer and the metal wiring layer.

5. The display panel according to claim 4, wherein one of the plurality of first electrodes is coupled to the metal wiring through a first through-hole, and the first through-hole is disposed in the first insulating layer.

6. The display panel according to claim 5, wherein one of the plurality of first electrodes is coupled to the data line through a second through-hole, and the second through-hole is disposed in the first insulating layer, the second insulating layer and the planarization layer.

7. A manufacturing method of a display panel, comprising: providing an array substrate comprising a display region, a non-display region around the display region, and data lines extending into the non-display region; forming a planarization layer on the data lines; forming a metal wiring layer on the planarization layer, the metal wiring layer comprising a plurality of metal wirings spaced apart from each other and corresponding to the data lines; forming a first insulating layer on the metal wirings and a portion of the planarization layer not covered by the metal wirings; and forming a first electrode layer on the first insulating layer, the first electrode layer comprising a plurality of first electrodes coupled to the metal wirings and the data lines.

8. The manufacturing method of a display panel according to claim 7, further comprising: forming a second insulating layer between the planarization layer and the metal wiring layer.

9. The manufacturing method of a display panel according to claim 8, wherein the forming a first electrode layer on the first insulating layer comprises: providing a mask layer on the first insulating layer; etching the first insulating layer to form a first through-hole and the first insulating layer, the second insulating layer and the planarization layer to form a second through-hole by the mask layer; and filling the first through-hole and the second through-hole with a conductive material, and forming the first electrode layer on the first through-hole and the second through-hole to couple the first electrode to the metal wiring and the data line.

10. A display device comprising a display panel, wherein the display panel comprises: an array substrate, comprising a display region, a non-display region around the display region, and data lines extending into the non-display region; a planarization layer, covering the data lines; and a metal wiring layer, disposed on the planarization layer in the non-display region, and comprising a plurality of metal wirings spaced apart from each other and corresponding to the data lines.

11. The display device according to claim 10, wherein the display panel further comprises: a first insulating layer, covering the metal wiring layer; a first electrode layer, disposed on the first insulating layer and comprising a plurality of first electrodes corresponding to the metal wirings.

12. The display device according to claim 11, wherein the first electrode layer and a pixel electrode in the display region are disposed in a same layer.

13. The display device according to claim 11, wherein a second insulating layer is disposed between the planarization layer and the metal wiring layer.

14. The display device according to claim 13, wherein the first electrode is coupled to the metal wiring through a first through-hole, and the first through-hole is disposed in the first insulating layer.

15. The display device according to claim 14, wherein the first electrode is coupled to the data line through a second through-hole, and the second through-hole is disposed in the first insulating layer, the second insulating layer and the planarization layer.

Description

CROSS-REFERENCE

[0001] The present application is based upon and claims priority to Chinese Patent Application No. 201711205655.2, filed on Nov. 27, 2017, and the entire contents thereof are incorporated herein by reference.

TECHNICAL FIELD

[0002] The present disclosure relates to the field of display technology, in particular, to a display panel, a manufacturing method of a display panel, and a display device including the display panel.

BACKGROUND

[0003] In recent years, with the development of science and technology, the display screen has gradually developed toward a thin structure with a high screen-to-body ratio and a narrow border. In order to improve the visual effect of a display screen, the four corners of the display screen are also beveled or rounded to perform a design with an abnormal shape such as C-angle, R-angle, L-shape or U-shape.

[0004] The display screen includes a display region in the middle and a border at the sides. Generally, wirings are arranged in the border. Due to the design with an abnormal shape and increasingly complicated wiring, the wiring will occupy more space, resulting in that the border at a location in an abnormal shape has a width that is 1.2 to 1.5 times that of a conventional border, which goes against the development of a narrow border display.

[0005] In view of this, there is an urgent need in the art to develop a technique capable of reducing a border at a location in an abnormal shape to increase the screen-to-body ratio.

[0006] It should be noted that the information disclosed in the foregoing background section is only for enhancement of understanding of the background of the present disclosure and therefore may include information that does not constitute the prior art that is already known to those of ordinary skill in the art.

SUMMARY

[0007] The present disclosure provides a display panel, a manufacturing method of a display panel, and a display device including the display panel.

[0008] Other features and advantages of the present disclosure will be apparent from the following detailed description, or learned in part by the practice of the present disclosure.

[0009] According to a first aspect of the present disclosure, there is provided a display panel, including: an array substrate, including a display region, a non-display region around the display region, and data lines extending into the non-display region; a planarization layer, covering the data lines; and a metal wiring layer, disposed on the planarization layer in the non-display region, and including a plurality of metal wirings spaced apart from each other and corresponding to the data lines.

[0010] In an exemplary arrangement of the present disclosure, the display panel further includes: a first insulating layer, covering the metal wiring layer; a first electrode layer, disposed on the first insulating layer and including a plurality of first electrodes corresponding to the metal wirings.

[0011] In an exemplary arrangement of the present disclosure, the first electrode layer is disposed in a same layer as that of a pixel electrode in the display region.

[0012] In an exemplary arrangement of the present disclosure, a second insulating layer is disposed between the planarization layer and the metal wiring layer.

[0013] In an exemplary arrangement of the present disclosure, the first electrode is coupled to the metal wiring through a first through-hole, and the first through-hole is disposed in the first insulating layer.

[0014] In an exemplary arrangement of the present disclosure, the first electrode is coupled to the data line through a second through-hole, and the second through-hole is disposed in the first insulating layer, the second insulating layer and the planarization layer.

[0015] According to a second aspect of the present disclosure, there is provided a manufacturing method of a display panel, including: providing an array substrate including a display region, a non-display region around the display region, and data lines extending into the non-display region; forming a planarization layer on the data lines; forming a metal wiring layer on the planarization layer, the metal wiring layer including a plurality of metal wirings spaced apart from each other and corresponding to the data lines; forming a first insulating layer on the metal wirings and a portion of the planarization layer not covered by the metal wirings; and forming a first electrode layer on the first insulating layer, the first electrode layer including a plurality of first electrodes coupled to the metal wirings and the data lines.

[0016] In an exemplary arrangement of the present disclosure, the method further includes: forming a second insulating layer between the planarization layer and the metal wiring layer.

[0017] In an exemplary arrangement of the present disclosure, the forming a first electrode layer on the first insulating layer includes: providing a mask layer on the first insulating layer; etching the first insulating layer to form a first through-hole and the first insulating layer, the second insulating layer and the planarization layer to form a second through-hole by the mask layer; filling the first through-hole and the second through-hole with a conductive material, and forming the first electrode layer on the first through-hole and the second through-hole to couple the first electrode to the metal wiring and the data line.

[0018] According to a third aspect of the present disclosure, there is provided a display device including the above display panel.

[0019] It is to be understood that both the foregoing general description and the following detailed description are exemplary and explanatory only and are not restrictive of the present disclosure.

BRIEF DESCRIPTION OF THE DRAWINGS

[0020] The accompanying drawings herein, which are incorporated in and constitute a part of this description, illustrate arrangements consistent with the present disclosure, and together with the description serve to explain the principles of the present disclosure. Obviously, the drawings in the following description are merely some arrangements of the present disclosure, and those skilled in the art can also obtain other drawings based on these drawings without any creative work. In the drawing:

[0021] FIG. 1 is a schematic cross-sectional view showing a wiring at a location in an abnormal shape in the related art;

[0022] FIG. 2 is a plan view showing a wiring at a location in an abnormal shape in the related art;

[0023] FIG. 3 is a schematic cross-sectional view showing a wiring at a location in an abnormal shape in an exemplary arrangement of the present disclosure;

[0024] FIG. 4 is a plan view showing a wiring at a location in an abnormal shape in an exemplary arrangement of the present disclosure;

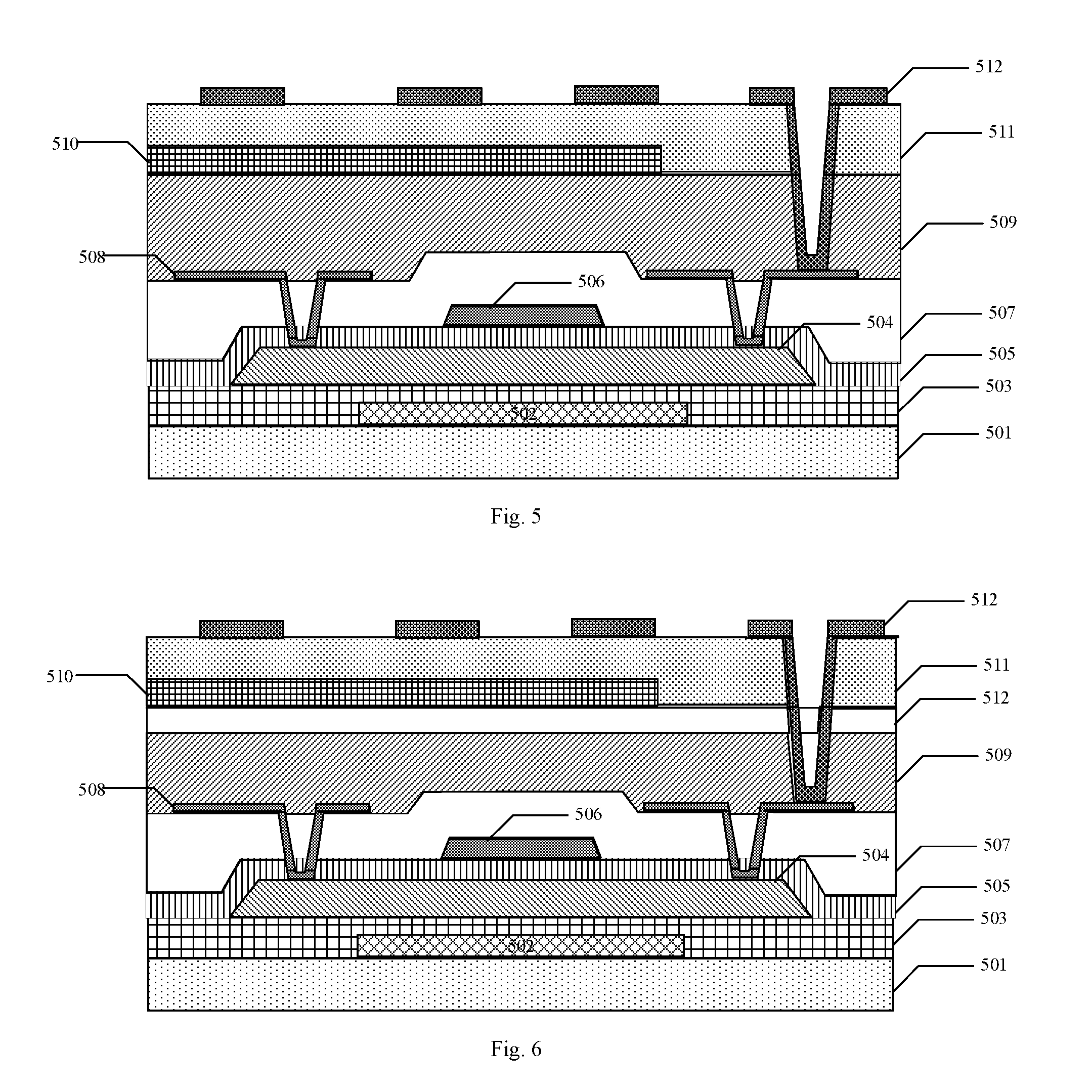

[0025] FIG. 5 is a cross-sectional view showing a display region in the related art;

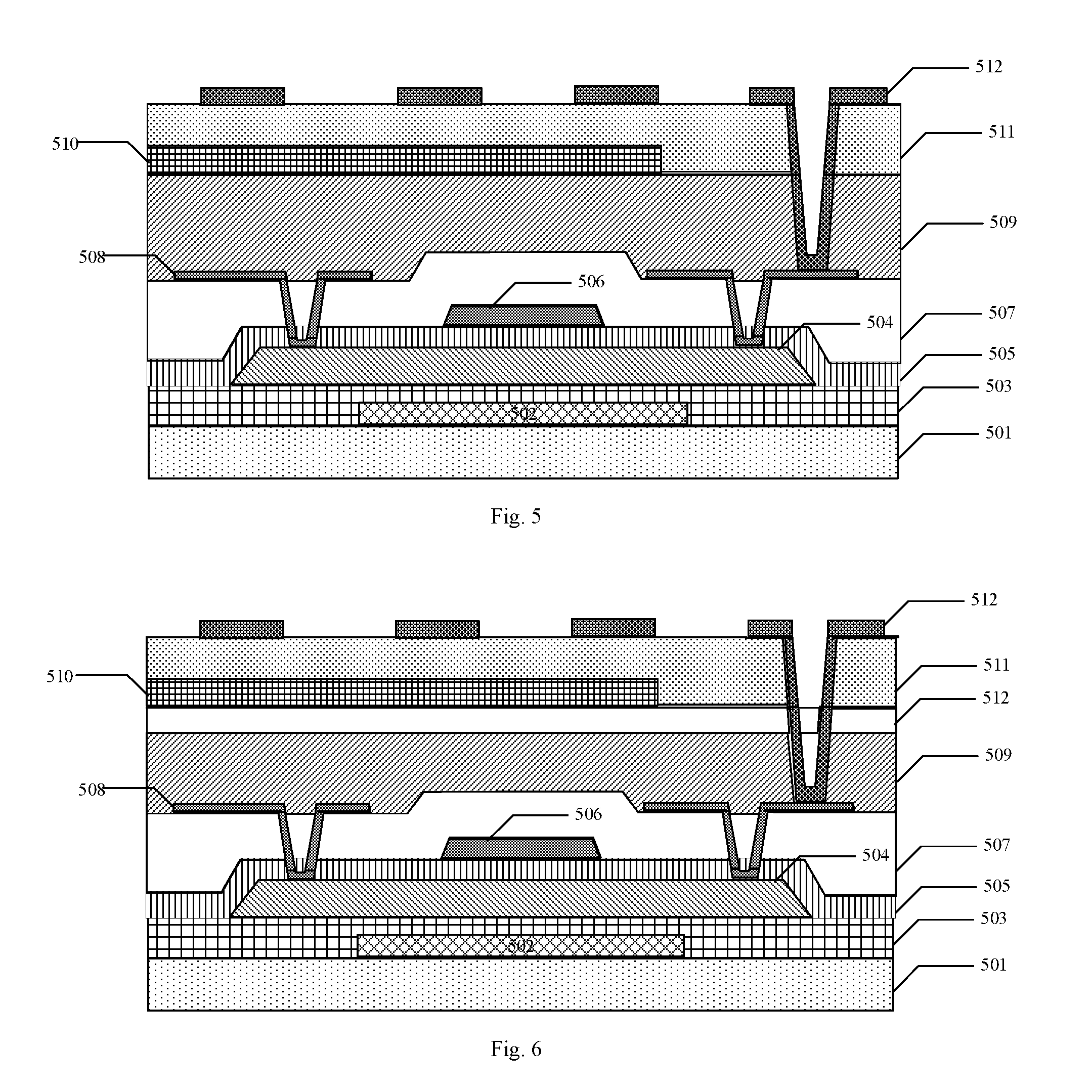

[0026] FIG. 6 is a schematic cross-sectional view showing a display region in an exemplary arrangement of the present disclosure;

[0027] FIG. 7 is a schematic cross-sectional view showing a wiring at a location in an abnormal shape in an exemplary arrangement of the present disclosure;

[0028] FIG. 8 is a flow chart showing a manufacturing method of a display panel in an exemplary arrangement of the present disclosure; and

[0029] FIG. 9 is a schematic view showing a structure of a display device in an exemplary arrangement of the present disclosure.

DETAILED DESCRIPTION

[0030] Exemplary arrangements will now be described more fully with reference to the accompanying drawings. However, the exemplary arrangements can be implemented in various forms and should not be construed as limited to the examples set forth herein; rather, these arrangements are provided so that this disclosure will be more complete and thorough, and will fully convey the concept of the exemplary arrangements to those skilled in the ar. The features, structures, or characteristics described may be combined in any suitable manner in one or more arrangements. In the following description, numerous specific details are provided to provide a thorough understanding of the arrangements of the present disclosure. However, those skilled in the art will recognize that the technical solutions of the present disclosure may be practiced without one or more of the specific details, or that other methods, components, devices, steps, etc. may be employed. In other instances, well-known technical solutions have not been shown or described in detail to avoid obscuring aspects of the present disclosure.

[0031] The terms "a", "an", "the", and "said" are used in the description to indicate that one or more elements/components/etc. are present, the terms "comprising", "including" and "having" should be understood in an open-ended meaning and are used to mean that there may be additional elements/components/etc. in addition to listed elements/components/etc. The terms "first" and "second" are used only as labels, not to limit the number of objects thereof.

[0032] Moreover, the drawings are merely schematic illustrations of the present disclosure and are not necessarily drawn to scale. The same reference numerals in the drawings denote the same or similar parts, and their repeated description will be omitted. Some of the blocks shown in the figures are functional entities and do not necessarily have to correspond to physically or logically independent entities.

[0033] FIG. 1 is a schematic cross-sectional view showing a wiring at a location in an abnormal shape in the related art. Referring to FIG. 1, the display panel may include a glass substrate 101, a buffer layer 102, a gate insulating layer 103, a gate electrode 104, an interlayer dielectric layer 105, a source/drain layer 106, a planarization layer 107, an insulating layer 108 and the like at a location in an abnormal shape. FIG. 2 is a plan view showing a wiring at a location in an abnormal shape in the related art, which shows a pixel region 201, a functional unit 202 disposed adjacent to the pixel region 201, a gate driving circuit unit 203 disposed adjacent to the functional unit 202, and a wiring 204 disposed at another side of the gate driving circuit unit 203. The functional unit 202 may include an anti-electrostatic breakdown unit, a test terminal unit, a fast discharge unit, and the like. Each functional unit 202 corresponds to a column of pixels and each gate driving circuit unit 203 corresponds to a row of pixels. As can be seen from FIG. 2, the width of the border is "a," which is a distance from the pixel region to the outermost wiring.

[0034] In the related art, the border shall cover the functional unit 202, the gate driving circuit unit 203, and the wiring 204, so that the border is relatively wide, and thus it is difficult to realize a high screen-to-body ratio and a narrow border of a display screen, thus reducing the user experience.

[0035] Firstly, an exemplary arrangement provides a display panel. As shown in FIG. 3, the display panel includes an array substrate and a metal wiring layer 302. The array substrate includes a display region and a non-display region around the display region. The non-display region of the array substrate includes a glass substrate 303, a buffer layer 304, a gate insulating layer 305, a gate electrode 306, an interlayer dielectric layer 307, a data line layer 308, and a planarization layer 309. A metal wiring layer 302 and a first insulating layer 311 are disposed on the planarization layer 309. The metal wiring layer 302 includes a plurality of metal wirings 310 spaced apart from each other, and the metal wirings 310 are disposed over the data line layer 308 to correspond to the data line in a vertical direction. The first insulating layer 311 covers the metal wirings 310 and a portion of the planarization layer 309 not covered by the metal wirings 310. The first insulating layer 311 may include an insulating material commonly used in the art such as SiOx, SiNx, etc., which will not be described in detail herein.

[0036] In the display panel of the present disclosure, the metal wiring layer is correspondingly disposed on the gate layer and the data line layer in the non-display region, and thus no longer occupies an additional wiring space, thus reducing the border at a location in an abnormal shape. Through measurement, it is found that when disposing the metal wiring layer 302, the border at a location in an abnormal shape is reduced by 10%-30%, which realizes a high screen-to-body ratio and narrow border.

[0037] FIG. 4 shows a plan view in which the metal wiring layer 302 is disposed on the planarization layer in the non-display region. In comparison to the wiring at a location in an abnormal shape in the related art as shown in FIG. 1, in the present arrangement, the metal wirings are disposed on the functional unit 202 and the gate driving circuit unit 203, and the functional unit 202 and the gate driving circuit unit 203 may be formed into metal wirings with jumper wire which extend on the device. Therefore, the border may only cover the functional unit 202 and the gate driving circuit unit 203, and the width of the border is "b". In comparison to the related art, the wiring space in the border is greatly reduced, and thus the width of the border is reduced.

[0038] As shown in FIG. 7, in an exemplary arrangement of the present disclosure, a first electrode layer 312 is disposed on the first insulating layer 311, and a first electrode of the first electrode layer 312 is disposed in a same layer as a pixel electrode in the display region. The first electrode may be also formed at the same time as that of the pixel electrode. The material of the first electrode layer 312 may be the same as or different from the material of the pixel electrode. In an exemplary arrangement, the first electrode layer 312 and the pixel electrode may be formed of the same electrode material.

[0039] As shown in FIG. 7, in an exemplary arrangement of the present disclosure, in order to prevent the planarization layer 309 from releasing gas due to heat and thus contaminating the sputtering chamber when the metal wiring layer 302 is formed by sputtering, a second insulating layer 313 may be formed between the planarization layer 309 and the metal wiring layer 302, and the second insulating layer 313 may cover the exposed planarization layer 309. The material used for the second insulating layer 313 and the material used for the first insulating layer 311 may be the same or different. The second insulating layer 313 is not essential. When the material used for the planarization layer 309 does not release gas when being heated, the second insulating layer 313 may not be provided.

[0040] Further, in the present arrangement, the first electrode layer 312 is coupled to the metal wiring layer 302 and the data line layer 308 through the first through-hole V1 and the second through-hole V2 respectively. The first through-hole V1 is disposed in the first insulating layer 311, and the second through-hole V2 is disposed in the first insulating layer 311 and the planarization layer 309 or disposed in the first insulating layer 311, the second insulating layer 313, and the planarization layer 309. A mask layer is disposed on the first insulating layer 311. The mask layer may be formed by a method commonly used in the art, for example, by spin coating, spraying, sputtering, etc., which is not specifically limited in the present disclosure. With the mask layer, the first insulating layer 311 is etched to form the first through-hole V1 in the first insulating layer 311, and at the same time, the first insulating layer 311, the second insulating layer 313 and the planarization layer 309 are etched to form the second through-hole V2.

[0041] FIG. 5 is a schematic structural view of a display region in the related art. As shown in FIG. 5, the display region includes a glass substrate 501, a light shielding layer 502, a buffer layer 503, a polycrystalline layer 504, and a gate insulating layer 505, a gate layer 506, an interlayer dielectric layer 507, a source/drain layer 508, a planarization layer 509, a common electrode layer 510, a first insulating layer 511, and a pixel electrode layer 512. Source and drain electrodes shown pass through the interlayer electric layer 507 and the gate insulating layer 505 to be electrically coupled to the polycrystalline layer 504. The pixel electrode layer 512 shown is electrically coupled to the source/drain layer 508 through the first insulating layer 511 and the planarization layer 509.

[0042] In the art, the display region and the non-display region are usually formed on the same array substrate. In order to improve the manufacturing efficiency, the planarization layer 509 and the second insulating layer 512 may be simultaneously formed on the source/drain layer in the display region and the data line layer in the non-display region of the array substrate. Then, a common electrode layer 510 (shown in FIG. 6) is formed on the second insulating layer in the display region, and a metal wiring layer 302 is formed on the second insulating layer 313 in the non-display region (as shown in FIG. 7).

[0043] FIG. 8 is a flow chart showing a manufacturing method of a display panel in an exemplary arrangement of the present disclosure. The manufacturing method includes S1-S5.

[0044] In S1, an array substrate including a display region, a non-display region around the display region, and data lines extending into the non-display region is provided.

[0045] The data line is formed simultaneously with the source and drain electrodes in the display region, and may be formed of the same material as or different material from that of the source and drain electrodes. To improve manufacturing efficiency, in an exemplary arrangement, the same material is used to form the data line, source electrode and drain electrode, and the material may a metal or a metal alloy commonly used in the art, such as Au, Ag, Cu, etc., which is not specifically limited in the present disclosure.

[0046] In S2, a planarization layer is formed on the data lines.

[0047] The planarization layer is formed by forming a dielectric layer on the data lines and a portion of the interlayer dielectric layer not covered by the data lines through a process such as sputtering, coating and the like, and processing the dielectric layer through a chemical mechanical planarization process. The planarization layer may include dielectric material commonly used in the art, which is not described in detail herein.

[0048] In S3, a metal wiring layer is formed on the planarization layer. The metal wiring layer includes a plurality of metal wirings spaced apart from each other and corresponding to the data lines.

[0049] The metal wirings may be formed of metal or metal alloys commonly used in the art, which is not described herein. The metal wirings are formed above the data line layer to correspond to the data lines in the vertical direction to reduce the wiring space, thus reducing the width of the border at a location in an abnormal shape.

[0050] In S4, a first insulating layer is formed on the metal wirings and a portion of the planarization layer not covered by the metal wirings.

[0051] The first insulating layer may be formed of a material such as SiNx, SiOx and the like. Of course, other insulating materials commonly used in the art may be also used, which is not specifically limited in the present disclosure. The first insulating layer may prevent the metal wiring from being contacted with a first electrode to be formed subsequently to affect the performance of the device.

[0052] In S5, a first electrode layer is formed on the first insulating layer. The first electrode layer includes a plurality of first electrodes coupled to the metal wirings and the data lines.

[0053] The wiring space is reduced by disposing metal wirings above the data line layer, thus reducing the width of the border at a location in an abnormal shape.

[0054] In an exemplary arrangement of the present disclosure, before the S2, a second insulating layer may be formed on the planarization layer, then the metal wiring layer is formed on the second insulating layer in the non-display area, and a common electrode layer is formed on the second insulating layer in the display area. The second insulating layer is formed to cover the planarization layer, so that the planarization layer may be prevented from releasing gas due to heat and thus contaminating the sputtering chamber when the metal wiring is formed by sputtering.

[0055] Further, the above S4 may include the following: P1, providing a mask layer on the first insulating layer; P2, etching the first insulating layer to form a first through-hole and the first insulating layer, the second insulating layer and the planarization layer to form a second through-hole by the mask layer; and P3, filling the first through-hole and the second through-hole with a conductive material, and forming the first electrode layer on the first through-hole and the second through-hole to couple the first electrode to the metal wiring and the data line.

[0056] The conductive material and the material of the first electrode layer may be the same or different, and may be a metal material or a metal alloy material commonly used in the art. The conductive material and the material of the first electrode layer are not specifically limited in the present disclosure.

[0057] Filling the conductive material and forming the first electrode layer may be performed simultaneously, or may be performed differently. In an arrangement, the through-holes are filed and the first electrode layer is formed with the same conductive material at the same time. Specifically, after forming the first through-hole and the second through-hole, the mask layer is removed, and the through-holes are filed with electrode material, and the first electrode layer covering the first and second through-holes is formed on the first insulating layer.

[0058] Further, an exemplary arrangement provides a display device. As shown in FIG. 9, the display device 900 includes a display panel 901. The display panel 901 is the display panel according to the above arrangement of the present disclosure, and the display device 900 may be a product or a component having a display function, such as an electronic paper, an OLED display, a mobile phone, a tablet computer, a television, a notebook computer, a digital photo frame, a navigator, and the like.

[0059] Those skilled in the art will readily recognize other arrangements of the present disclosure upon consideration of the specification and practice of the present disclosure disclosed herein. This application is intended to cover any variations, uses, or adaptations of the present disclosure which follow the general principles of the present disclosure and include any common knowledge or conventional techniques in this technical field not disclosed by the present disclosure. The description and examples are to be considered exemplary only, with the true scope and spirit of the present disclosure being indicated by the following claims.

[0060] It should be understood that the present disclosure is not limited to the precise structure that has been described above and shown in the drawings, and various modifications and changes can be made without departing from the scope thereof. The scope of the present disclosure is limited only by the attached claims.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.