Manufacture Method Of Polysilicon Thin Film And Polysilicon Tft Structure

Zhang; Liangfen ; et al.

U.S. patent application number 16/233027 was filed with the patent office on 2019-05-02 for manufacture method of polysilicon thin film and polysilicon tft structure. The applicant listed for this patent is Shenzhen China Star Optoelectronics Technology Co., Ltd.. Invention is credited to Rongsheng Chen, Yuanjun Hsu, Hoising Kwok, Shuichih Lien, Changcheng Lo, Man Wong, Yuanchun Wu, Liangfen Zhang, Meng Zhang, Wei Zhou.

| Application Number | 20190131132 16/233027 |

| Document ID | / |

| Family ID | 54304692 |

| Filed Date | 2019-05-02 |

| United States Patent Application | 20190131132 |

| Kind Code | A1 |

| Zhang; Liangfen ; et al. | May 2, 2019 |

MANUFACTURE METHOD OF POLYSILICON THIN FILM AND POLYSILICON TFT STRUCTURE

Abstract

A polysilicon thin film transistor (TFT) structure includes a substrate, a buffer layer covering the substrate, an island shaped semiconductor layer positioned on the buffer layer, a gate isolation layer covering the island shaped semiconductor layer, a gate positioned on the gate isolation layer, a passivation layer positioned on the gate and the gate isolation layer, and a source and a drain positioned on the passivation layer. The island shaped semiconductor layer is formed with a process that includes forming a polysilicon thin film on the substrate and implementing silicon self-ion implantation to the polysilicon thin film with a dosage and an energy level that prevent the polysilicon thin film from being decrystallized. The silicon self-ion implanted polysilicon thin film is further subjected to photolithography and ion doping to form the island shaped semiconductor layer with ion doping areas.

| Inventors: | Zhang; Liangfen; (Shenzhen City, CN) ; Lien; Shuichih; (Shenzhen City, CN) ; Lo; Changcheng; (Shenzhen City, CN) ; Wu; Yuanchun; (Shenzhen City, CN) ; Hsu; Yuanjun; (Shenzhen City, CN) ; Kwok; Hoising; (Shenzhen City, CN) ; Wong; Man; (Shenzhen City, CN) ; Chen; Rongsheng; (Shenzhen City, CN) ; Zhou; Wei; (Shenzhen City, CN) ; Zhang; Meng; (Shenzhen City, CN) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Family ID: | 54304692 | ||||||||||

| Appl. No.: | 16/233027 | ||||||||||

| Filed: | December 26, 2018 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 14892199 | Nov 19, 2015 | 10204787 | ||

| 16233027 | ||||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 21/02488 20130101; H01L 21/02667 20130101; H01L 21/02422 20130101; H01L 29/66757 20130101; H01L 27/1285 20130101; H01L 29/78675 20130101; H01L 21/26513 20130101; H01L 21/02532 20130101 |

| International Class: | H01L 21/265 20060101 H01L021/265; H01L 27/12 20060101 H01L027/12; H01L 21/02 20060101 H01L021/02; H01L 29/66 20060101 H01L029/66; H01L 29/786 20060101 H01L029/786 |

Foreign Application Data

| Date | Code | Application Number |

|---|---|---|

| Jun 9, 2015 | CN | 201510314265.3 |

Claims

1. A polysilicon thin film transistor (TFT) structure, comprising a substrate, a buffer layer covering the substrate, an island shaped semiconductor layer positioned on the buffer layer, a gate isolation layer covering the island shaped semiconductor layer, a gate positioned on the gate isolation layer, a passivation layer positioned on the gate and the gate isolation layer, and a source and a drain positioned on the passivation layer; wherein the island shaped semiconductor layer comprises a channel area and a source contact area and a drain contact area respectively positioned at two sides of the channel area, the source being in contact with the source contact area, the drain being in contact with the drain contact area; wherein the island shaped semiconductor layer is formed with a process that comprises first providing a substrate, forming a polysilicon thin film of a predetermined thickness on a surface of the substrate, and implementing silicon self-ion implantation to the polysilicon thin film, wherein implantation of silicon ions is conducted with a dosage and an energy level that prevent the polysilicon thin film from being decrystallized, the energy level being 15 keV, the silicon self-ion implanted polysilicon thin film being further subjected to photolithography and ion doping to form the island shaped semiconductor layer with ion doping areas, the source contact area and the drain contact area corresponding to the ion doping areas of the silicon self-ion implanted polysilicon thin film, respectively; wherein the polysilicon TFT structure belongs to a P-type TFT element or a N-type TFT element.

2. The polysilicon TFT structure according to claim 1, wherein a material of each of the gate isolation layer and the passivation layer is silicon oxide, silicon nitride or a combination of the two, and a material of each of the gate, the source and the drain is aluminum.

3. The polysilicon TFT structure according to claim 1, wherein the process further comprises implementing post annealing to the silicon self-ion implanted polysilicon thin film.

4. The polysilicon TFT structure according to claim 1, wherein the substrate comprises a base plate covered with a buffer layer.

5. The polysilicon TFT structure according to claim 4, wherein the base plate comprises one of a silicon plate, a glass plate, and a flexible plate.

6. The polysilicon TFT structure according to claim 4, wherein the buffer layer is made of a material comprising silicon oxide, silicon nitride, or a combination thereof.

7. The polysilicon TFT structure according to claim 1, wherein the polysilicon thin film is formed with direct vapor deposition of a material of polysilicon.

8. The polysilicon TFT structure according to claim 1, wherein the polysilicon thin film is formed with crystallization of amorphous silicon.

9. The polysilicon TFT structure according to claim 8, wherein the crystallization of amorphous silicon is conducted with solid phase crystallization.

10. The polysilicon TFT structure according to claim 8, wherein the crystallization of amorphous silicon is conducted with metal induced crystallization.

11. The polysilicon TFT structure according to claim 8, wherein the crystallization of amorphous silicon is conducted with applying heat to crystallize amorphous silicon through liquid phase crystallization.

12. The polysilicon TFT structure according to claim 11, wherein the heat applied to crystallize amorphous silicon through liquid phase crystallization comprises a light-emitting diode (LED) or a laser device.

13. The polysilicon TFT substrate according to claim 3, wherein the post annealing is carried out with a furnace or a rapid thermal annealing apparatus.

14. The polysilicon TFT substrate according to claim 1, wherein the process comprises depositing a protective layer on the polysilicon thin film before silicon self-ion implantation.

15. The polysilicon TFT substrate according to claim 14, wherein the protective layer is made of a material comprising silicon oxide, silicon nitride, or a combination thereof.

Description

CROSS REFERENCE TO RELATED APPLICATIONS

[0001] This is a divisional application of co-ending patent application Ser. No. 14/892,199, filed on Nov. 19, 2015, which is a national stage of PCT Application No. PCT/CN2015/082265, filed on Jun. 25, 2015, claiming foreign priority of Chinese Patent Application No. 201510314265.3, filed on Jun. 9, 2015.

FIELD OF THE INVENTION

[0002] The present invention relates to a display technology field, and more particularly to a manufacturing method of a polysilicon thin film and a polysilicon TFT structure.

BACKGROUND OF THE INVENTION

[0003] In the display skill field, liquid crystal display (LCD), organic light emitting diode (OLED) and other panel displays have been gradually replaced the CRT displays.

[0004] With the development of panel displays, the high resolution and low power consumption panels has constantly been demanded. The low temperature poly-silicon (LTPS) thin film transistor (TFT) draws the attentions of the industry related to the high resolution active matrix liquid crystal display (AMLCD) and active matrix organic light emitting display (AMOLED) to be considered with great application value and potential. Compared with amorphous silicon (a-Si), the LTPS TFT has higher carrier mobility, which can reach up from dozens to hundreds cm.sup.2/VS. The response speed of the element is fast, and the stability is good, which can satisfy the demands of the high resolution AMLCD and AMOLED. The LTPS TFT cannot only be the pixel switch but also can be employed to construct the peripheral driving circuit to realize circuit integration.

[0005] The LTPS is a branch of the poly-Si technology. The reason why the polysilicon material possesses higher electron mobility is due to the polysilicon structure of the polysilicon itself. Compared with the amorphous silicon of having high defect concentration and being highly disordered, the polysilicon is constructed by a plurality of ordered crystalline grains.

[0006] In prior arts, the polysilicon thin film can be obtained by chemical vapor deposition (CVD); also can be obtained by implementing annealing process to the amorphous silicon to be decrystallized, and the common methods are: solid phase crystallization (SPC), metal-induced crystallization (MIC), excimer laser annealing (ELA) and etc.

[0007] At present, the main factor of restricting the polysilicon TFT element property is the grain boundary among the polysilicon crystalline grains. A large amount of defects exist at the grain boundary. The grain sizes and distributions of the polysilicon thin film manufactured by the aforesaid various methods are different, and the numbers of the grain boundary defects are quite different, too.

[0008] Lots of methods have been proposed to focus how to improve the quality of the polysilicon thin film in the research literatures. Some researches have pointed out that the silicon self-ion implantation can be used to make the polysilicon thin film be decrystallized, and then the recrystallization is performed to reduce the crystal nucleus density and thus, enlarge the grain size after the recrystallization.

[0009] R. Reif and J. E. Knott (Electronics Letters, Vol.17 No. 17, 1981) has already proved that with the silicon ion of high dosage (such as 3.times.10.sup.15/cm.sup.2) to be implanted in the polysilicon thin film, most crystal structures of the polysilicon thin film can be decrystallized. Due to the tunnel effect of the ion implantation, only few crystal nucleuses are left. These crystal nucleuses grow to be large size grains in the following SPC recrystallization.

[0010] N. Yamauchi, etc (IEEE Electron Device Letters, Vol. 11, No. 1, 1990 and Journal of Applied Physics, vol. 75, pp. 3235-3257, 1994) utilizes the polysilicon obtained by the aforesaid method to manufacture TFTs. With the enlarged grain size, the mobility of the element increases, and the subthreshold swing is cliffy. However, in the meantime, the literature also reveals that the uniformity of the small size elements seriously descends because of the random distribution of the large grain sizes.

[0011] The above literatures indicate that the silicon self-ion implantation of a high dosage can decrystallize most of the polysilicon. The decrystallization makes the crystal nucleus density decreased and the large size grains are obtained after recrystallization. The enlarged grains makes the grain boundary defects decreased, and the element property be improved. Nevertheless, this method needs silicon ion implantation of a large dosage on one hand, and one more crystallization annealing process is required on the other hand. Moreover, the element uniformity issue exists.

[0012] To this day, an effect of silicon ion implantation of a lower dosage that will not cause decrystallization has not been researched and applied to polysilicon.

SUMMARY OF THE INVENTION

[0013] An objective of the present invention is to provide a manufacturing method of a polysilicon thin film, which can reduce the defect concentration of the polysilicon grain boundary and improve the quality of the polysilicon thin film.

[0014] Another objective of the present invention is to provide a polysilicon TFT structure, which can reduce the grain boundary potential barrier in the activation stage, and enlarge the carrier mobility, and increase the on state current, and decrease the threshold voltage, and improve the TFT property.

[0015] The present invention further provides a manufacturing method of a polysilicon thin film, comprising steps of:

[0016] step 1, providing a substrate, and forming the polysilicon thin film on the substrate, and a thickness of the polysilicon thin film accords with a required thickness of manufacturing a semiconductor element;

[0017] step 2, implementing silicon slef-ion implantation to the polysilicon thin film, and an implantation dosage of silicon ion is lower than a measurement limit for making polysilicon be decrystallized.

[0018] The manufacturing method of the polysilicon thin film further comprises: step 3, implementing post annealing process to the polysilicon thin film, of which the silicon self-ion implantation is accomplished.

[0019] The substrate in the step 1 is a silicon substrate covered with a buffer layer, a glass substrate covered with a buffer layer or a flexible substrate covered with a buffer layer, and material of the buffer layer is silicon oxide, silicon nitride or a combination of the two.

[0020] the step 1 forms the polysilicon thin film by direct vapor deposition of the polysilicon;

[0021] or, the step 1 makes amorphous silicon be crystallized to form the polysilicon thin film by solid phase crystallization or metal induced crystallization;

[0022] or, the step 1 employs laser or LED as a heat source to make amorphous silicon generate liquid phase crystallization to form the polysilicon thin film.

[0023] The step 2 employs an ion implanter, or ion sprayer for implementing silicon self-ion implantation to the polysilicon thin film.

[0024] The step 3 employs a furnace or a rapid thermal annealing apparatus for implementing post annealing process.

[0025] Before implementing silicon self-ion implantation to the polysilicon thin film, a protective layer is further required to be deposed on the polysilicon thin film, and material of the protective layer is silicon oxide, silicon nitride or a combination of the two.

[0026] The present invention further provides a manufacturing method of a polysilicon thin film, comprising steps of:

[0027] step 1, providing a substrate, and forming the polysilicon thin film on the substrate, and a thickness of the polysilicon thin film accords with a required thickness of manufacturing a semiconductor element;

[0028] step 2, implementing silicon self-ion implantation to the polysilicon thin film, and an implantation dosage of silicon ion is lower than a measurement limit for making polysilicon be decrystallized;

[0029] step 3, implementing post annealing process to the polysilicon thin film, of which the silicon self-ion implantation is accomplished;

[0030] wherein the substrate in the step 1 is a silicon substrate covered with a buffer layer, a glass substrate covered with a buffer layer or a flexible substrate covered with a buffer layer, and material of the buffer layer is silicon oxide, silicon nitride or a combination of the two;

[0031] wherein the step 2 employs an ion implanter, or ion sprayer for implementing silicon self-ion implantation to the polysilicon thin film.

[0032] The present invention further provides a polysilicon TFT structure, comprising: a substrate, a buffer layer covering the substrate, an island shaped semiconductor layer positioned on the buffer layer, a gate isolation layer covering the island shaped semiconductor layer, a gate positioned on the gate isolation layer, a passivation layer positioned on the gate and the gate isolation layer, and a source and a drain positioned on the passivation layer;

[0033] the island shaped semiconductor layer comprises a channel area and a source contact area and a drain contact area respectively positioned at two sides of the channel area, and the source contacts the source contact area, and the drain contacts the drain contact area;

[0034] the island shaped semiconductor layer is formed by the polysilicon thin film manufactured by the aforesaid manufacturing method of the polysilicon thin film after photolithography and ion doping, and the source contact area and the drain contact area correspond to an area of ion doping;

[0035] the polysilicon TFT structure belongs to a P-type TFT element or a N-type TFT element.

[0036] Material of the gate isolation layer and the passivation layer is silicon oxide, silicon nitride or a combination of the two, and material of the gate, the source and the drain is aluminum.

[0037] The benefits of the present invention are: the present invention provides a manufacturing method of a polysilicon thin film. With implementing silicon self-ion implantation to the polysilicon thin film, and an implantation dosage of silicon ion is lower than a measurement limit for making polysilicon be decrystallized for making the implanted silicon ion to form interstitial silicon to move to the polysilicon grain boundary, the defect concentration of the polysilicon grain boundary can be reduced and the quality of the polysilicon thin film can be improved. The present invention provides a polysilicon TFT structure, of which the island shaped semiconductor layer is manufactured by the polysilicon thin film after low dosage silicon self-ion implantation, which can reduce the grain boundary potential barrier in the activation stage, and enlarge the carrier mobility, and increase the on state current, and decrease the threshold voltage, and improve the TFT property.

BRIEF DESCRIPTION OF THE DRAWINGS

[0038] In order to better understand the characteristics and technical aspect of the invention, please refer to the following detailed description of the present invention is concerned with the diagrams, however, provide reference to the accompanying drawings and description only and is not intended to be limiting of the invention.

[0039] In drawings,

[0040] FIG. 1 is a flowchart of a manufacturing method of a polysilicon thin film according to the present invention;

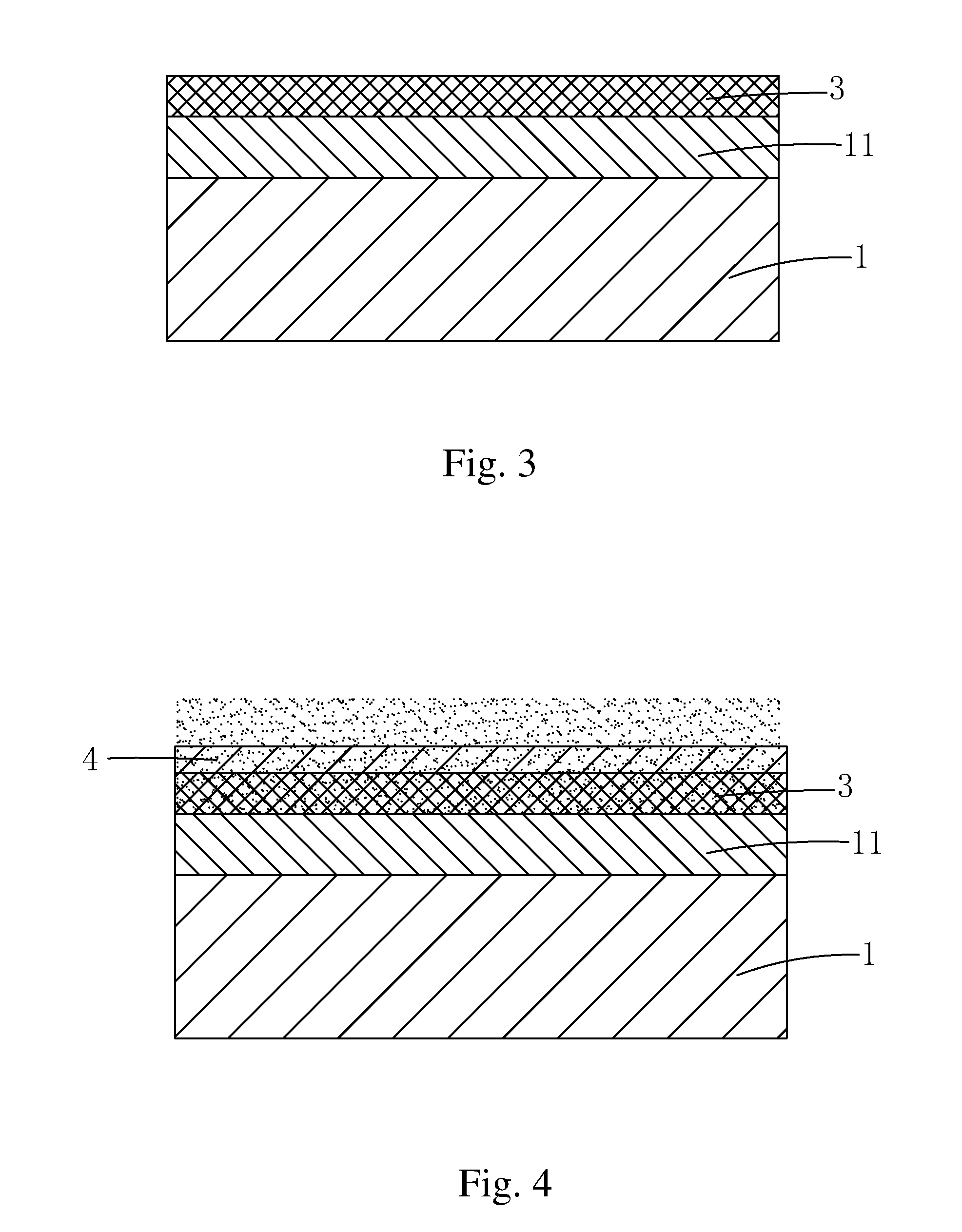

[0041] FIGS. 2 and 3 are diagrams of the step 1 of the manufacturing method of the polysilicon thin film according to the present invention;

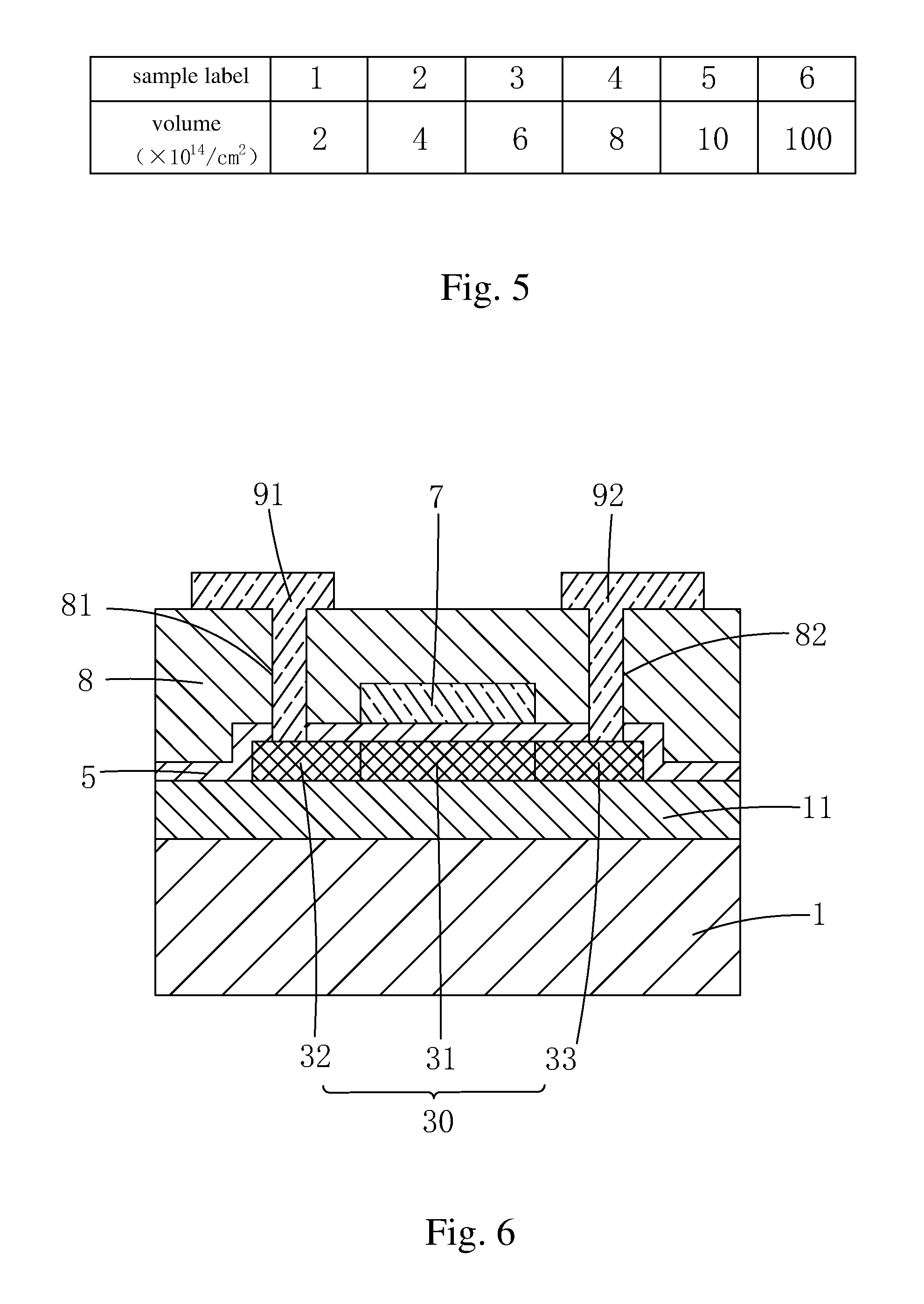

[0042] FIG. 4 is a diagram of the step 2 of the manufacturing method of the polysilicon thin film according to the present invention;

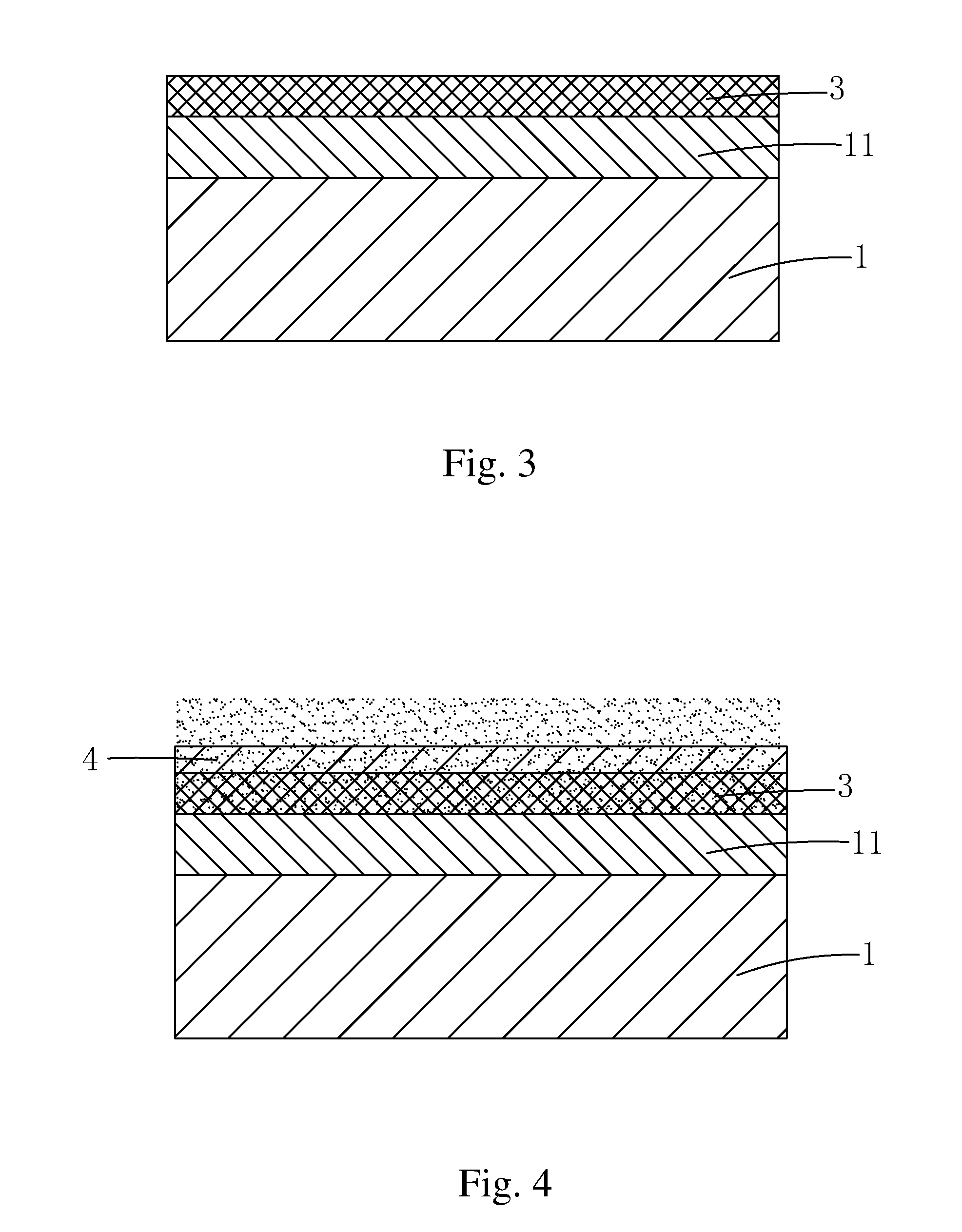

[0043] FIG. 5 shows various silicon ion implantation dosages and the corresponding sample label list in the step 2 of the manufacturing method of the polysilicon thin film according to the present invention;

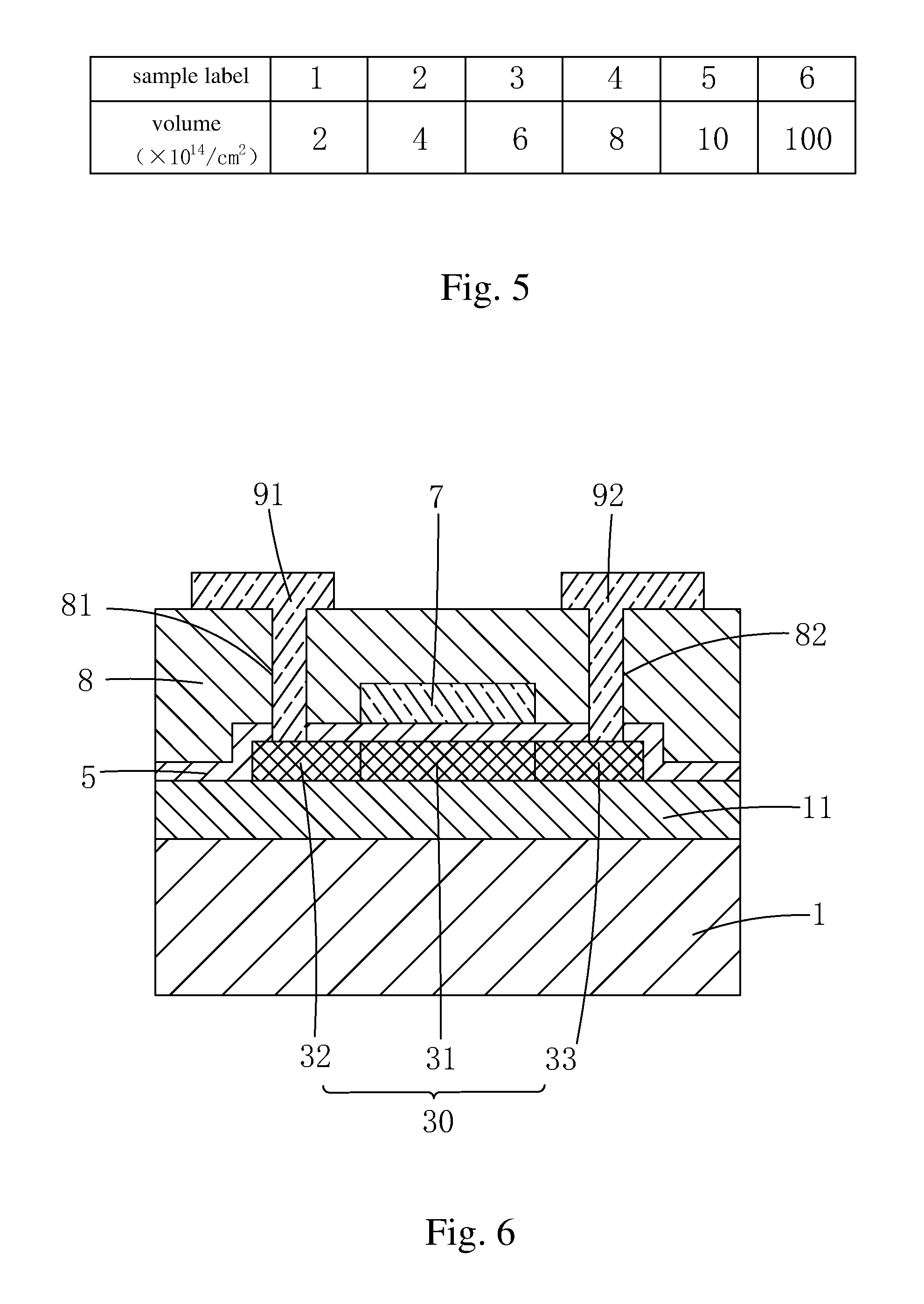

[0044] FIG. 6 is a sectional diagram of a polysilicon TFT structure according to the present invention;

[0045] FIG. 7 is a test result diagram of implementing carrier mobility test to the polysilicon TFTs employing various samples;

[0046] FIG. 8 is a data sheet in accordance with FIG. 7.

DETAILED DESCRIPTION OF PREFERRED EMBODIMENTS

[0047] For better explaining the technical solution and the effect of the present invention, the present invention will be further described in detail with the accompanying drawings and the specific embodiments.

[0048] Please refer to FIG. 1. The present invention first provides a manufacturing method of a polysilicon thin film, comprising steps of:

[0049] step 1, referring to FIGS. 2 and 3, providing a substrate 1, and forming the polysilicon thin film 3 on the substrate 1, and a thickness of the polysilicon thin film 3 accords with a required thickness of manufacturing a semiconductor element.

[0050] Specifically, the substrate 1 in the step 1 is a silicon substrate covered with a buffer layer 11, a glass substrate covered with a buffer layer 11 or a flexible substrate covered with a buffer layer 11, and a material of the buffer layer 11 is silicon oxide, silicon nitride or a combination of the two, and preferably, the material of the buffer layer 11 is silicon oxide (SiO.sub.2).

[0051] The step 1 can form the polysilicon thin film 3 by direct vapor deposition of the polysilicon.

[0052] Or, the step 1 can make amorphous silicon be crystallized to form the polysilicon thin film 3 by solid phase crystallization or metal induced crystallization.

[0053] Or, the step 1 can employ laser or LED as a heat source to make amorphous silicon generate liquid phase crystallization to form the polysilicon thin film 3.

[0054] Furthermore, as shown in FIG. 2 and FIG. 3, employing metal induced crystallization to make amorphous silicon be crystallized to form the polysilicon thin film 3 is illustrated. The detail procedure of the step 1 is: first, employing low pressure chemical vapor deposition (LPCVD) to depose an amorphous silicon thin film 3', of which the thickness is 50 nm; then, deposing a thin layer (the thickness<5 nm) of metal nickel 4'; and then, implementing nitrogen annealing to crystallize amorphous silicon, and the annealing temperature is 600.degree. C., and the annealing period is 10 hours; after the crystallization of amorphous silicon is accomplished to form the polysilicon thin film 3, the warmed sulfuric acid and Hydrogen peroxide mixture is employed to clean the substrate 1 to remove the residual metal nickel 4'.

[0055] step 2, implementing silicon self-ion implantation to the polysilicon thin film 3, and an implantation dosage of silicon ion is lower than a measurement limit for making polysilicon be decrystallized. Preferably, the implantation dosage of silicon ion is 4.times.10.sup.14/cm.sup.2-8.times.10.sup.14/cm.sup.2.

[0056] Specifically, as shown in FIG. 4, employing metal induced crystallization to make amorphous silicon be crystallized to form the polysilicon thin film 3 is still illustrated. A protective layer 4 can be deposed on the polysilicon thin film 3 on practical demands before the silicon self-ion implantation is implemented to the polysilicon thin film 3. The thickness of the protective layer 4 can be selected according to the energy of subsequent silicon ion implantation. Certainly, the protective layer 4 can be omitted. In this embodiment, the protective layer 4 with thickness 25 nm is deposed, and material of the protective layer 4 is silicon oxide, silicon nitride or a combination of the two. Preferably, material of the protective layer 4 is SiO.sub.2; then, an ion implanter, or ion sprayer is employed for implementing silicon ion implantation to the polysilicon thin film 3. The implantation energy is 15 keV.

[0057] For verifying the influence of the silicon ion implantation dosage to the polysilicon thin film and the performance of the final product, polysilicon TFT, the present invention implements experiments with multiple samples with various silicon ion implantation dosages: as shown in FIG. 5, the samples of which the silicon ion implantation dosages respectively are 2.times.10.sup.14/cm.sup.2, 4.times.10.sup.14/cm.sup.2, 6.times.10.sup.14/cm.sup.28.times.10.sup.14/cm.sup.2, 10.times.10.sup.14/cm.sup.2, 100.times.10.sup.14/cm.sup.2 are labeled with 1, 2, 3, 4, 5, 6, and twenty samples of every labels are respectively selected for implementing the following performance test for the polysilicon TFT.

[0058] After the step 2 is accomplished, the step 3 is further required to be implemented. The nitrogen post annealing process is implemented to the polysilicon thin film 3 after the silicon self-ion implantation is accomplished, and the temperature of the nitrogen post annealing process is 600.degree. C., and the annealing time is 4 hours.

[0059] The manufacturing method of the polysilicon thin film according to the present invention makes the implanted silicon ion to form interstitial silicon to move to the polysilicon grain boundary, which can reduce the defect concentration of the polysilicon grain boundary and improve the quality of the polysilicon thin film.

[0060] Please refer to FIG. 6. On the basis of the aforesaid manufacturing method of the polysilicon thin film, the present invention further provides a polysilicon TFT structure, comprising a substrate 1, a buffer layer 11 covering the substrate 1, an island shaped semiconductor layer 30 positioned on the buffer layer 11, a gate isolation layer 5 covering the island shaped semiconductor layer 30, a gate 7 positioned on the gate isolation layer 5, a passivation layer 8 positioned on the gate 7 and the gate isolation layer 5, and a source 91 and a drain 92 positioned on the passivation layer 8.

[0061] The procedure of manufacturing the polysilicon TFT structure is: after manufacturing the polysilicon thin film 3 according to the aforesaid method, the photolithography is first implemented to the polysilicon thin film 3 to be an island shape, and then, LPCVD is employed to depose the gate isolation layer 5 of the thickness 50 nm, and material of the gate isolation layer 5 is silicon oxide, silicon nitride or a combination of the two, of which SiO.sub.2 is preferred; then, aluminum of the thickness 300 nm is deposed and the photolithography is implemented to form the gate 7; and then, the gate 7 is employed to be shield to implement ion implantation doping of self-alignment to the island shape polysilicon thin film after photolithography, and the dosage of the ion implantation is 4.times.10.sup.15/cm.sup.2, and the implantation energy is 20 keV to make the island shape polysilicon thin film become the island shape oxide semiconductor layer 30, wherein the source contact area 32 and the drain contact area 33 are formed corresponding to the area of ion doping, and the area shielded by the gate 7 which is not implemented with ion doping becomes the channel area 30; next, LPCVD is employed to depose the passivation layer 8 of the thickness 500 nm, and a first via hole 81 and a second via hole 82 are opened to the passivation layer 8 and the gate isolation layer 5 correspondingly above the source contact area 32 and the drain contact area 33, and material of the passivation layer 8 is silicon oxide, silicon nitride or a combination of the two, of which SiO.sub.2 is preferred; aluminum (containing 1% silicon) of the thickness 700 nm is sputtered and the photolithography is implemented to be the source 91 and the drain 92, and the source 91 contacts the source contact area 32 through the first via hole 81, and the drain 92 contacts the drain contact area 33 through the second via hole 82; At last, 30 minutes hydrogen treatment is implemented.

[0062] In the aforesaid procedure of manufacturing the polysilicon TFT structure, according to the various ion implanted to the island shape polysilicon thin film, a P-type TFT element or a N-type TFT element can be manufactured. For example, implanting boron ion can manufacture the P-type TFT element, and implanting phosphorous ion can manufacture the N-type TFT element.

[0063] After manufacturing multiple polysilicon TFTs in accordance with samples of various labels, in room temperature, the HP4156B semiconductor parameter analyzer is employed to implement performance test to the polysilicon TFTs and calculates the average carrier mobility of the multiple polysilicon TFTs in accordance with the samples of the same label.

[0064] As shown in FIG. 7, FIG. 8, both the length L and the width W of the channel area of the polysilicon TFT are 10 .mu.m, and the source-drain voltage V.sub.ds is -0.1V. In the range of 4.times.10.sup.14/cm.sup.2-8.times.10.sup.14/cm.sup.2, the carrier mobility is improved. With the increase of the dosage of the silicon ion implantation, the carrier mobility also increases. This is because the implantation dosage of silicon ion is lower than a measurement limit for making polysilicon be decrystallized. The implanted silicon ion forms interstitial silicon to move to the polysilicon grain boundary, which can reduce the defect concentration of the polysilicon grain boundary. When the dosage of the silicon ion implantation is larger than or equal to 1.times.10.sup.15/cm.sup.2, the carrier mobility obviously descends. This is because a large amount of silicon ions are implanted in the polysilicon thin film, and the polysilicon is decrystallized in different levels. The manufacturing method of the present invention does not implement high temperature annealing recrystallization treatment to the polysilicon thin film implanted with silicon ion. The lattice structure of the polysilicon has been damaged to cause the performance degradation of the polysilicon TFT. The test result verifies: it is correct that the manufacturing method of polysilicon thin film 3 according to the present invention sets the dosage of silicon self-ion implantation to be lower than a measurement limit for making polysilicon be decrystallized.

[0065] In conclusion, the manufacturing method of the polysilicon thin film according to the present invention, with implementing silicon self-ion implantation to the polysilicon thin film, and an implantation dosage of silicon ion is lower than a measurement limit for making polysilicon be decrystallized for making the implanted silicon ion to form interstitial silicon to move to the polysilicon grain boundary, can reduce the defect concentration of the polysilicon grain boundary and improve the quality of the polysilicon thin film. In the polysilicon TFT structure according to the present invention, the island shaped semiconductor layer is manufactured by the polysilicon thin film after low dosage silicon self-ion implantation, which can reduce the grain boundary potential barrier in the activation stage, and enlarge the carrier mobility, and increase the on state current, and decrease the threshold voltage, and improve the TFT property.

[0066] Above are only specific embodiments of the present invention, the scope of the present invention is not limited to this, and to any persons who are skilled in the art, change or replacement which is easily derived should be covered by the protected scope of the invention. Thus, the protected scope of the invention should go by the subject claims.

* * * * *

D00000

D00001

D00002

D00003

D00004

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.