Stun Device Testing Apparatus And Methods

Stethem; Kenneth J. ; et al.

U.S. patent application number 15/984786 was filed with the patent office on 2019-05-02 for stun device testing apparatus and methods. This patent application is currently assigned to Aegis Industries, Inc.. The applicant listed for this patent is Aegis Industries, Inc.. Invention is credited to Tor Alden, Seymour Friedel, Kenneth J. Stethem.

| Application Number | 20190128649 15/984786 |

| Document ID | / |

| Family ID | 51297072 |

| Filed Date | 2019-05-02 |

View All Diagrams

| United States Patent Application | 20190128649 |

| Kind Code | A1 |

| Stethem; Kenneth J. ; et al. | May 2, 2019 |

STUN DEVICE TESTING APPARATUS AND METHODS

Abstract

A testing apparatus includes a housing having a port for receiving a discharge end of an electrical discharge device. A discharge-receiving circuit is operatively connected to the port, and is configured to receive a discharge from the electrical discharge device. The discharge-receiving circuit includes a default resistor and at least one supplemental resistor. When in a first setting, the discharge-receiving circuit is configured so as to pass the discharge automatically through at least the default resistor. When in a second setting, the discharge-receiving circuit is configurable so as to selectively pass the discharge through at least one of the plurality of resistors.

| Inventors: | Stethem; Kenneth J.; (Hailey, ID) ; Friedel; Seymour; (Mena, AR) ; Alden; Tor; (Basking Ridge, NJ) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Assignee: | Aegis Industries, Inc. Rockville MD |

||||||||||

| Family ID: | 51297072 | ||||||||||

| Appl. No.: | 15/984786 | ||||||||||

| Filed: | May 21, 2018 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 14042010 | Sep 30, 2013 | |||

| 15984786 | ||||

| 61707101 | Sep 28, 2012 | |||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | F41H 13/0018 20130101 |

| International Class: | F41H 13/00 20060101 F41H013/00 |

Claims

1. An apparatus comprising: a housing comprising a port for receiving a discharge end of an electrical discharge device; and an discharge-receiving circuit operatively connected to the port, the discharge-receiving circuit configured to receive a discharge from the electrical discharge device, wherein the discharge-receiving circuit comprises: a plurality of resistors comprising a default resistor and at least one supplemental resistor, wherein when in a first setting, the discharge-receiving circuit is configured so as to pass the discharge automatically through at least the default resistor, and wherein when in a second setting, the discharge-receiving circuit is configurable so as to selectively pass the discharge through at least one of the plurality of resistors.

2. The apparatus of claim 1, wherein the at least one supplemental resistor comprises a first supplemental resistor and a second supplemental resistor.

3. The apparatus of claim 2, wherein a resistance of the default resistor is higher than a resistance of at least one of the first supplemental resistor and the second supplemental resistor.

4. The apparatus of claim 1, further comprising a switch for selectively setting the discharge-receiving circuit to either of the first setting and the second setting.

5. The apparatus of claim 1, wherein the discharge-receiving circuit is set to the first setting when the discharge-receiving circuit is unpowered.

6. The apparatus of claim 1, further comprising an environmental module for detecting at least one of an ambient temperature, an ambient humidity, and a barometric pressure.

7. The apparatus of claim 1, further comprising an air intake fan for drawing ambient air into the housing, and wherein the environmental module detects at least one of the ambient temperature and the ambient humidity, and wherein the environmental module is disposed downstream of the air intake fan.

8. The apparatus of claim 1, wherein the discharge-receiving circuit further comprises an analysis module.

9. A method of configuring a circuit, the method comprising: detecting a condition indicative of a loss of power to the circuit; configuring the circuit such that an electrical discharge through the circuit is routed through at least one of a plurality of resistors, wherein the electrical discharge is received from a device located external to the circuit.

10. The method of claim 9, further comprising receiving the electrical discharge from the external device.

11. The method of claim 9, further comprising: detecting a condition indicative of a receipt of power to the circuit; and selectively configuring the circuit so as to route the discharge through at least one of the plurality of resistors.

12. The method of claim 11, further comprising: selecting a protocol; and selectively configuring the circuit based at least in part on the selected protocol.

13. The method of claim 9, wherein the condition is based at least in part on the position of a switch in the circuit.

14. The method of claim 9, wherein the condition is based at least in part on an absence of supply power to the circuit.

15. The method of claim 9, wherein configuring the circuit comprises at least one of opening or closing a solenoid.

16. The method of claim 9, wherein the circuit is disposed within a testing device.

Description

CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application claims priority to and the benefit of U.S. Provisional Patent Application Ser. No. 61/707,101, entitled "Stun Device Testing Apparatus and Methods," filed Sep. 28, 2012, the disclosure of which is hereby incorporated by reference herein in its entirety.

INTRODUCTION

[0002] The use of neuromuscular incapacitation (NMI) devices (and other stun devices that emit electrical discharges against a target mammal) has increased over the last decade to encompass over 200,000 units in operation worldwide with over 800,000 actual firing deployments involving training personnel and law enforcement incidents. The output of stun devices is electrical in nature and thus may not leave an identifying mark or clear trace of historical events, unlike a bullet, that normally leaves such a mark. Furthermore, stun devices are designed to incapacitate effectively and temporarily an individual based on a unique and specific electrical output, as stated by a manufacturer.

[0003] Currently, there are many stun devices available around the world, featuring a variety of outputs with respect to voltage, current, waveform, and timing intervals. While many are available, however, only a limited number of manufacturers sell stun devices in a gun form-factor. U.S. Pat. Nos. 7,234,262 and 6,636,412 by Taser International and U.S. Pat. No. 6,575,073 by Stinger Systems all describe currently available commercial stun devices. The disclosures of these patents are hereby incorporated by reference herein in their entireties. The electrical output of each company's device differs significantly from the others and within each specified output for a given load, but each manufacturer makes their own claims of effectiveness and safety, as discussed below. The differences and characteristics of electrical output of stun devices are known from detailed and sophisticated measurements with a variety of specialized oscilloscopes and related measuring tools.

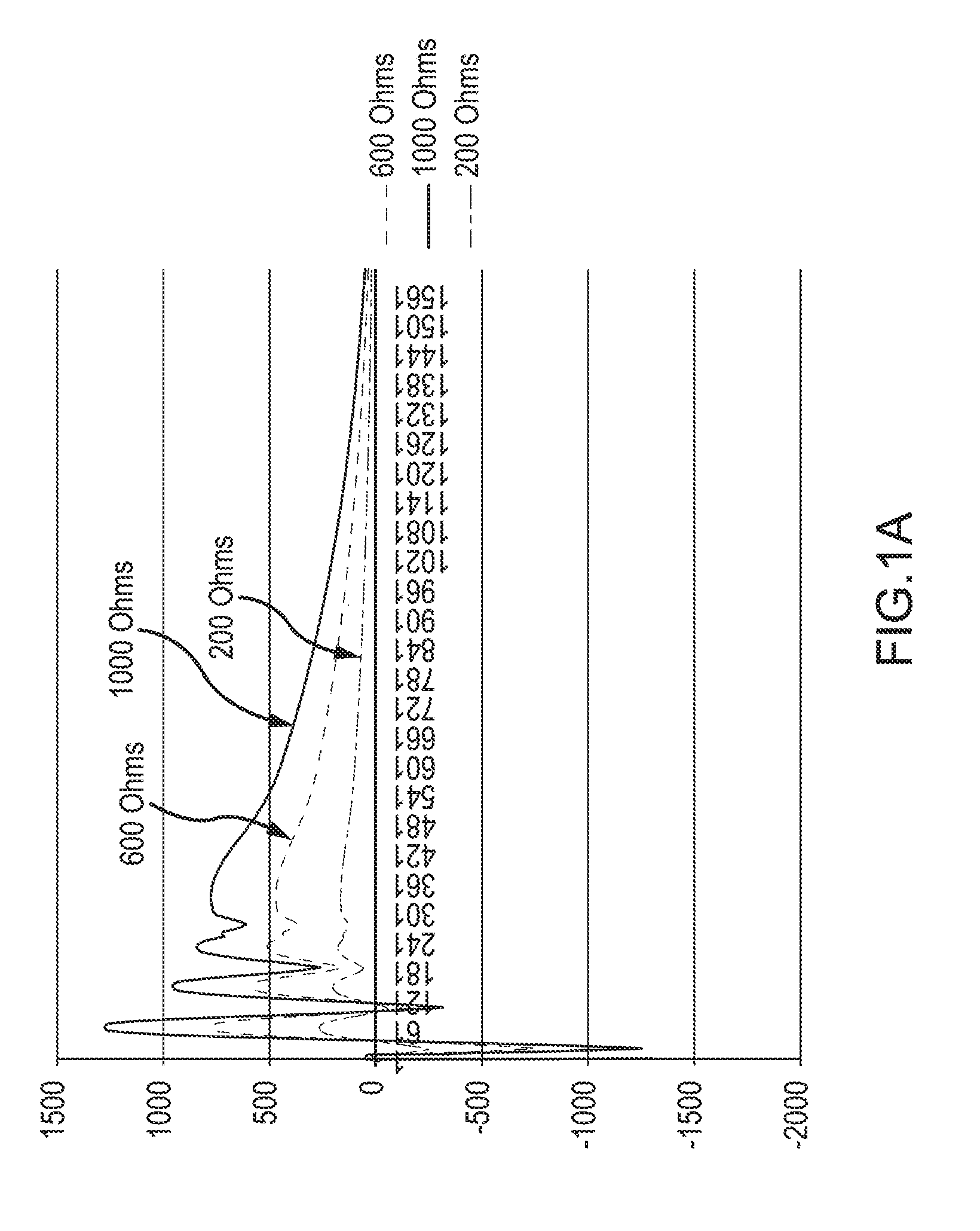

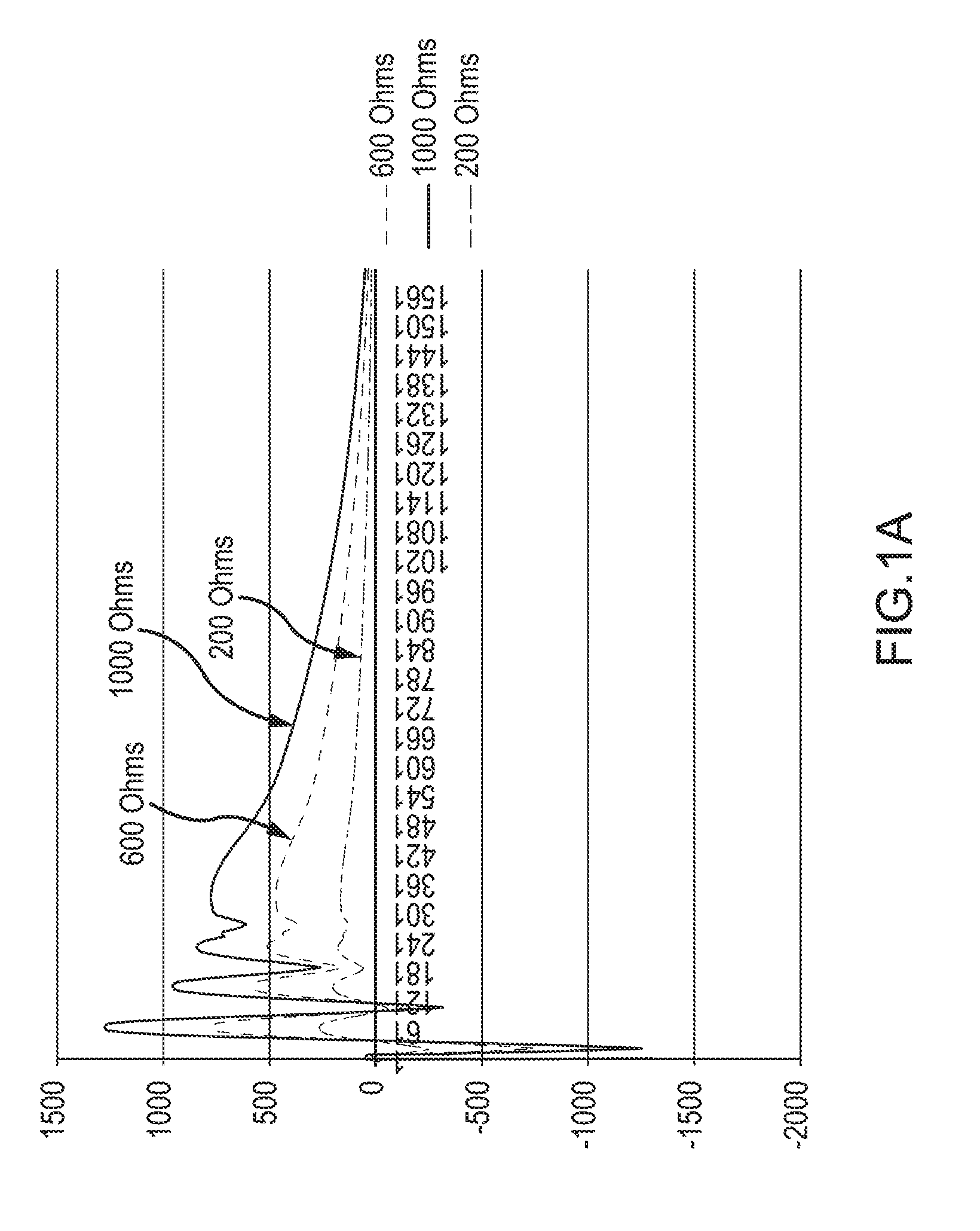

[0004] FIGS. 1, 1A and 2 and TABLE 1 show detailed traces of waveforms under specific conditions using sophisticated oscilloscopes as well as a summary of typical electrical output for a variety of related, electrically-focused technologies used in the medical profession and other fields. FIG. 1 shows waveforms from a commercially available stun device of a hand-held type, illustrating several important features of the waveform, including pulse height and charge, repetition rate, slope of the peak, duration of the waveform, changing shape of the waveform and total energy delivered. FIG. 1 depicts the waveforms at four resistances, while FIG. 1A depicts the waveforms of another stun device, at three resistances. FIG. 2 shows additional details of an "idealized" waveform discharged by a device presently in commercial use, indicating a variety of characteristics. The characteristics shown in FIGS. 1, 1A, and 2 define the waveform of choice for a given device and manufacturer. TABLE 1 provides a comparison of stun devices, and includes similar information for biomedical devices employing electrical current, such as Electroconvulsive (ECT) therapy, cauterizing devices (electro-surgery), and defibrillators.

TABLE-US-00001 TABLE 1 Electrical Discharge Comparison of Various Device Types Voltage Current Pulse Duration Pulse Frequency Power Electric Fencing 5-10 kV 10-20 mA 0.1-1 sec 0.5-1 Hz 0.1-18 J/pulse Early Stun Devices 40-100 kV 3-4 mA ~20 .mu.sec 5-20 Hz 0.8 J/pulse 7 watt Taser Current Stun Devices 18-50 kV 2-4 mA average 11 .mu.sec 10-25 Hz 0.1-1.8 J/pulse 26 watt Taser 18 A peak ECS, ECT 70-450 V 20-900 mA 1.5 msec 70 Hz 0.6 J/pulse Defibrillators ~750-1500 V 20-65 A 5-7 msec 1-6 total 100-360 J/pulse Electrosurgery 1000-9000 V variable variable <200,000 Hz 80-300 Watts

[0005] It is helpful to note that a manufacturer's claim of effectiveness and safety must be linked directly to a consistent electrical output. Manufacturers have conducted various safety studies involving humans and animals to allay public fears and to use as a defense in litigation, where the actual output of the device is considered to have been a cause of injury or death of the target. Thus, lacking regulatory approval of a universal waveform, each company documents its waveform's safety by performing safety studies for its own devices. While safety factors of each waveform have been disclosed in publications, the device use data and associated instances of injury and death to date also reveals significant questions regarding safety. Thus, the identity and integrity of a specific waveform is of high value to a number of stakeholders including manufacturers, end-users (e.g., law enforcement) and the public on whom the devices are deployed for non-lethal purposes. Examples of studies resulting in claims of both safety and potential injury can be found, for example, in the following publications: Jeffrey D. Ho, MD, James R. Miner, MD, Dhanunjaya R. Lakireddy, MD, Laura L. Bultman, MD, William G. Heegaard, MD, MPH, "Cardiovascular and Physiologic Effects of Conducted Electrical Weapon Discharge in Resting Adults," ACADEMIC EMERGENCY MEDICINE, 13:589-595 (2006); Valentino, D. J., Walter, R. J., Dennis, A. J., Nagy, K., Loor, M. M., & Winners, J. et al., "Neuromuscular effects of stun device discharges," JOURNAL OF SURGICAL RESEARCH, 143(1), 78-87 (2007); Valentino, D. J., Walter, R. J., Nagy, K., Dennis, A. J., Winners, J., & Bokhari, F. et al., "Repeated thoracic discharges from a stun device," JOURNAL OF TRAUMA--INJURY, INFECTION AND CRITICAL CARE, 62(5), 1134-1142 (2007); A. Esquivel, E. Dawe, J. Sala-Mercado, R. Hammond, C. Bir, "The Physiologic Effects of a Conducted Electrical Weapon in Swine," ANNALS OF EMERGENCY MEDICINE, Vol. 50, Issue 5, Pages 576-583 (2007); Lakkireddy, D., Khasnis, A., Antenacci, J., Ryshcon, K Chung, M. K., & Wallick, D. et al., "Do electrical stun guns (TASER-X26.RTM.) affect the functional integrity of implantable pacemakers and defibrillators?," EUROPACE, 9(7), 551-556 (2007); and Lakkireddy, D., Wallick, D., Ryschon, K Chung, M. K Butany, J., & Martin, D. et al., "Effects of cocaine intoxication on the threshold for stun gun induction of ventricular fibrillation," JOURNAL OF THE AMERICAN COLLEGE OF CARDIOLOGY, 48(4), 805-811 (2006). The disclosures of these references are hereby incorporated by reference herein in their entireties.

[0006] Notwithstanding a manufacturer's claim of safety, electric stun device safety can only be assured if the stated waveform is both proven safe and is consistently produced and delivered by the device. Given the importance of this link between device output, safety, and effectiveness, we have determined it to be desirable that the output be verifiable for a given device during its cycle of normal duty and on a schedule of appropriate timing to ensure that only devices having outputs that are studied and verified safe are used on targets. However, there is no easy, simple way to verify device output on a regular basis within the typical law enforcement context. Thus, we have determined that verification of device output is needed in the law enforcement setting, in a testing apparatus that is simple to operate and inexpensive to purchase.

[0007] It also is reasonable to assume that as stun devices of different manufacturers and types become even more widely deployed and better studied, there will be a need to examine in detail the output of a specific device or class of devices. This output may be in relation to a specific incident or a class of incidents in which one or more devices are involved, including devices by different manufacturers. In such a case, currently, it is necessary to use sophisticated oscilloscopes operated by an expert or someone very familiar with the measurement equipment and the particular features of stun devices to capture, study and analyze the device's electrical output. Further, the waveform must be interpreted to assess whether it is, in fact, safe. While this approach may be helpful in determining the safety of a device right off the assembly line, stun devices are rarely, if ever, tested after being in the field for a period of time. Moreover, any tests performed on a particular device are often performed only after a discharge against a target has occurred, usually, and unfortunately, after there exists a reason for testing (e.g., an unintentional death of a target during deployment). There is essentially no focus on the actual routine verification of output prior to routine use. In addition, because electrical currents are transient and may not leave tangible traces that are currently recognized by the medical profession, the commonly recognized characteristics of an electrical discharge (voltage, amplitude, etc.) are often the only measure of output that was received by the target. These commonly recognized characteristics may not be sufficient, in all circumstances, to determine adequately or reliably the reason for an adverse result (i.e., a death of a target).

[0008] Moreover, if one follows the analogy of forensic study of ballistic evidence, it is clear that the capability to collect and analyze electric stun discharge evidence is lacking. Thus, we have determined that it is highly advantageous to have a device or series of measurement devices that are easy to operate and understand and are linked to the known waveform output of stun devices available. While some attempts are being made to develop systems to test particular stun devices from a specific manufacturer, these attempts do not appear to contemplate a device that test both existing and not-yet-developed stun devices, or to test and compile information on both existing and not-yet-developed stun devices to enable research into the safety and efficacy of electric waveforms and stun devices, generally. See, e.g., Nelson Bennett, "lasers' test results sparks technology," Richmond News (Sep. 9, 2009) (available at http://www2.canada.com/richmondnews/news/story.html?id=0fa3b787-b632-4543- -a991-354de3f9cd74), the disclosure of which is hereby incorporated by reference herein in its entirety.

[0009] Additionally, having these devices readily available (both economically and physically) would allow law enforcement departments and forensic investigators and coroners the capability of in-depth analysis of stun device discharges, as needed.

[0010] Stun device output is a function, in part, of the internal electronic circuitry designed to produce a given waveform of a given magnitude and duration. We have determined that it would be desirable for the discharge output to be verified during the life cycle of a device. Changes in output can occur due to a number of factors, including, but not limited to, defective manufacture, component failure due to use, current leakage to operator, change in manufacturing components, deliberate alteration of components and power supply, etc. Additionally, manufacturers develop and sell successor models of stun devices (e.g., Taser models M18, M26, X26, wireless systems, sentry systems; see www.taser.com) and may alter the original waveform and output as models change over time. Moreover, nearly all projectile-based gun-platform stun devices may also deliver a subcutaneous electrical discharge significantly different than a discharge directly against the skin. Thus, manufacturers' stated claims of output should not be relied upon as accurate over the lifetime of use of the device, nor across successor models. It would be desirable to verify such output on a routine basis.

[0011] Currently, stun device output is not regulated at the state or federal level with respect to waveform or magnitude, nor are manufacturing standards tied to any stated degree of device performance or acceptable deviation from stated specifications. Without verification, there is little, if any, accountability for holding manufacturers responsible for quality performance features. The lack of verification is problematic for law enforcement officials who use the devices routinely and who may be involved in litigation due to a specific, often fatal, incident. Such details become important in complex deployment situations where drugs, alcohol and extreme agitation, as well as a victim's pre-existing conditions (such as use of pacemakers, etc.) are present. Medical experience has shown that risks from electrical stimulation include abnormal heart rhythms, epileptic seizures, cell injury and death. While there is an extensive history of the use of stun-devices with no apparent long term effects, the possibility exists. Variations from the normal stimuli are of particular concern. For example very fast, high-amplitude transients can produce injury inside of cells. Ventricular fibrillation can be induced more easily at some rates, as well. Thus, a convenient and cost effective program by law enforcement to track and record the features of the devices deployed over time may be desirable.

[0012] Currently, a number of oscilloscopes and other measuring devices are employed for the detailed analysis of waveforms and output of stun devices. Many of these measuring devices and oscilloscopes are sophisticated with respect to data capture rate, range and magnitude of signal, signal sampling parameters, and ability to analyze, record and handle large amounts of stored data. The technology involved in typical electrical output analysis includes a multimeter as described in U.S. Pat. No. 7,342,393, issued Mar. 11, 2008, to Newcombe; combination test instruments and voltage detectors as described in U.S. Pat. No. 7,242,173, issued Jul. 10, 2007, to Cavoretto; devices generating electronic test signals as described in U.S. Pat. No. 6,944,569, issued Sep. 13, 2005, to Harbord; digital oscilloscopes with waveform pattern recognition as described in U.S. Pat. No. 6,621,913, issued Sep. 16, 2003, to de Vries; specialized circuits for measuring in-circuit resistance and current as described in U.S. Pat. No. 5,804,979, issued Sep. 8, 1998, to Lund; and devices designed to detect minimum pulse widths of waveforms as described in U.S. Pat. No. 5,708,375, issued Jan. 13, 1998, to Lemmens. U.S. Pat. No. 6,469,492, issued Oct. 22, 2002, to Britz and U.S. Pat. No. 5,930,745, issued Jul. 27, 1999, to Swift disclose additional testing equipment. The disclosures of each of the above-identified references are incorporated by reference herein in their entireties.

[0013] Additionally, there are a number of devices that are used to measure and verify electrical signals from a variety of biomedical devices including defibrillators, as described in U.S. Published Patent Application No. 2007/0226574, published Sep. 27, 2007, by Ryan; pacemakers, as described in U.S. Pat. No. 5,209,228, issued May 11, 1993, to Cano; electro-surgery devices; and others. Many electrical testing devices provide comparisons with known electrical standards such as the International Electrotechnical Commission (IEC) and the Association for the Advancement of Medical Instrumentation (AAMI). The disclosures of each of the above-identified references are incorporated by reference herein in their entireties.

[0014] However, no universal test devices currently exist that can consistently meet the needs described above for known and to-be-developed stun devices. Additionally, there presently exists no method for imposing accountability on users or manufacturers of stun devices by proving how a particular stun device was operating prior to discharge during routine use against a target. Moreover, there exists no system for collecting information and storing it reliably for "large data" analysis about stun device discharge characteristics to study the effects of stun devices on an industry-wide basis.

SUMMARY

[0015] The technology disclosed herein consists of one or more testing devices or apparatus that are capable of a spectrum of measurements and data-handling features. The testing devices according to the technology include an adapter for effective, consistent, and safe coupling to an instrument capable of accepting, recording and analyzing the outputs of a stun device. Some of the contemplated testing devices include interchangeable adapters specific to testing particular stun devices. The testing device, in a basic form, may record only total electrical output, maximum voltage and current, or other simple numerical data. A more complex embodiment can also allow capture of waveform characteristics such as frequency, repetition rate, pulse train duration, anomalies, etc., at several different load options, each simulating contact with the human body. Other embodiments can provide options of waveform analysis, as compared to a "standard" waveform supplied by a manufacturer or other source. Embodiments of other devices can be equipped with data storage and analytical features, libraries of waveforms of various devices, statistical programs, and a variety of resistance factors simulating electrical pathways through human tissue. Other testing devices according to the technology can also be used to record total output and waveform features for repeated applications of stun devices. Furthermore, certain of these testing devices can report output relative to existing or new standards, regulations, and protocols, for the stun device industry as they are developed, relative to a variety of electrical safety standards in the U.S. or other jurisdictions, or relative to a set of specific standards for stun devices. These standards, regulations, or protocols may be developed by stun device manufacturers, governments, industry organizations, non-governmental organizations, medical organizations, standards-setting organizations, etc.

[0016] One difference between the technical features of many of the testing devices described in the Background and one embodiment of the stun device safety tester as described below, is the basic unit of electrical sampling. Available stun devices produce pulses with durations ranging from less than 1 microsecond to tens of milliseconds. In addition, transients associated with spark-gap type stun devices have durations that are fractions of a microsecond, as shown in FIG. 3 (note, e.g., leading spike on negative lobe). Thus, in contrast to defibrillator testers that measure single and very large pulses and pacemaker analyzers that measure relatively wide (slow) pulses over a very short period, the stun device tester in one embodiment will record the detailed behavior of waveforms with features ranging from very fast, high magnitude transients to normal pulse durations of tens of milliseconds. This suggests sampling rates of at least 20 mega samples/second for 10 milliseconds, demanding 200,000 words of storage to recreate waveforms or 20,000 words of storage to identify the presence of fast transients. Sampling rates of 10 mega samples/second may also be utilized. In one embodiment, normal waveforms from a spectrum of devices can be captured and analyzed as well as chaotic and very fast anomalies that, to date, have not been characterized for stun devices. While the medical and safety significance of such transients and anomalies are not entirely understood, such aberrations can be identified and measured to assess their relevance and to help ensure claimed output parameters and safety.

[0017] In one aspect, the technology relates to an apparatus including: a housing including a port for receiving a discharge end of an electrical discharge device; and an discharge-receiving circuit operatively connected to the port, the discharge-receiving circuit configured to receive a discharge from the electrical discharge device, wherein the discharge-receiving circuit has: a plurality of resistors including a default resistor and at least one supplemental resistor, wherein when in a first setting, the discharge-receiving circuit is configured so as to pass the discharge automatically through at least the default resistor, and wherein when in a second setting, the discharge-receiving circuit is configurable so as to selectively pass the discharge through at least one of the plurality of resistors. In an embodiment, the at least one supplemental resistor includes a first supplemental resistor and a second supplemental resistor. In another embodiment, a resistance of the default resistor is higher than a resistance of at least one of the first supplemental resistor and the second supplemental resistor. In yet another embodiment, the apparatus includes a switch for selectively setting the discharge-receiving circuit to either of the first setting and the second setting. In still another embodiment, the discharge-receiving circuit is set to the first setting when the discharge-receiving circuit is unpowered.

[0018] In another embodiment of the above aspect, the apparatus includes an environmental module for detecting at least one of an ambient temperature, an ambient humidity, and a barometric pressure. In another embodiment, the apparatus includes an air intake fan for drawing ambient air into the housing, and wherein the environmental module detects at least one of the ambient temperature and the ambient humidity, and wherein the environmental module is disposed downstream of the air intake fan. In another embodiment, the discharge-receiving circuit further includes an analysis module.

[0019] In another aspect, the technology relates to a method of configuring a circuit, the method including: detecting a condition indicative of a loss of power to the circuit; configuring the circuit such that an electrical discharge through the circuit is routed through at least one of a plurality of resistors, wherein the electrical discharge is received from a device located external to the circuit. In an embodiment, the method includes receiving the electrical discharge from the external device. In another embodiment, the method includes detecting a condition indicative of a receipt of power to the circuit; and selectively configuring the circuit so as to route the discharge through at least one of the plurality of resistors. In yet another embodiment, the method includes selecting a protocol; and selectively configuring the circuit based at least in part on the selected protocol. In still another embodiment, the condition is based at least in part on the position of a switch in the circuit.

[0020] In another embodiment of the above aspect, the condition is based at least in part on an absence of supply power to the circuit. In another embodiment, configuring the circuit has at least one of opening or closing a solenoid. In another embodiment, the circuit is disposed within a testing device.

[0021] In another aspect, the invention includes an article of manufacture having a computer-readable medium with computer-readable instructions embodied thereon for performing the methods described in the preceding paragraphs. In particular, the functionality of a method of the present invention may be embedded on a computer-readable medium, such as, but not limited to, a floppy disk, a hard disk, an optical disk, a magnetic tape, a PROM, an EPROM, CD-ROM, DVD-ROM or downloaded from a server. The functionality of the techniques may be embedded on the computer-readable medium in any number of computer-readable instructions, or languages such as, for example, FORTRAN, PASCAL, C, C++, Java, PERL, LISP, JavaScript, C#, Tel, BASIC and assembly language. Further, the computer-readable instructions may, for example, be written in a script, macro, or functionally embedded in commercially available software (such as EXCEL or VISUAL BASIC).

BRIEF DESCRIPTION OF THE DRAWINGS

[0022] Other features and advantages of the present technology, as well as the technology itself, can be more fully understood from the following description of the various embodiments, when read together with the accompanying drawings, in which:

[0023] FIG. 1 depicts a graph of waveforms from a commercially-available stun device, under four different resistor loads.

[0024] FIG. 1A depicts a graph of waveforms from another commercially-available stun device, under three different resistor loads

[0025] FIG. 2 depicts waveform detail and characteristics of a commercially available stun device.

[0026] FIG. 3 depicts waveform detail of a particular waveform produced by the stun device of FIG. 2.

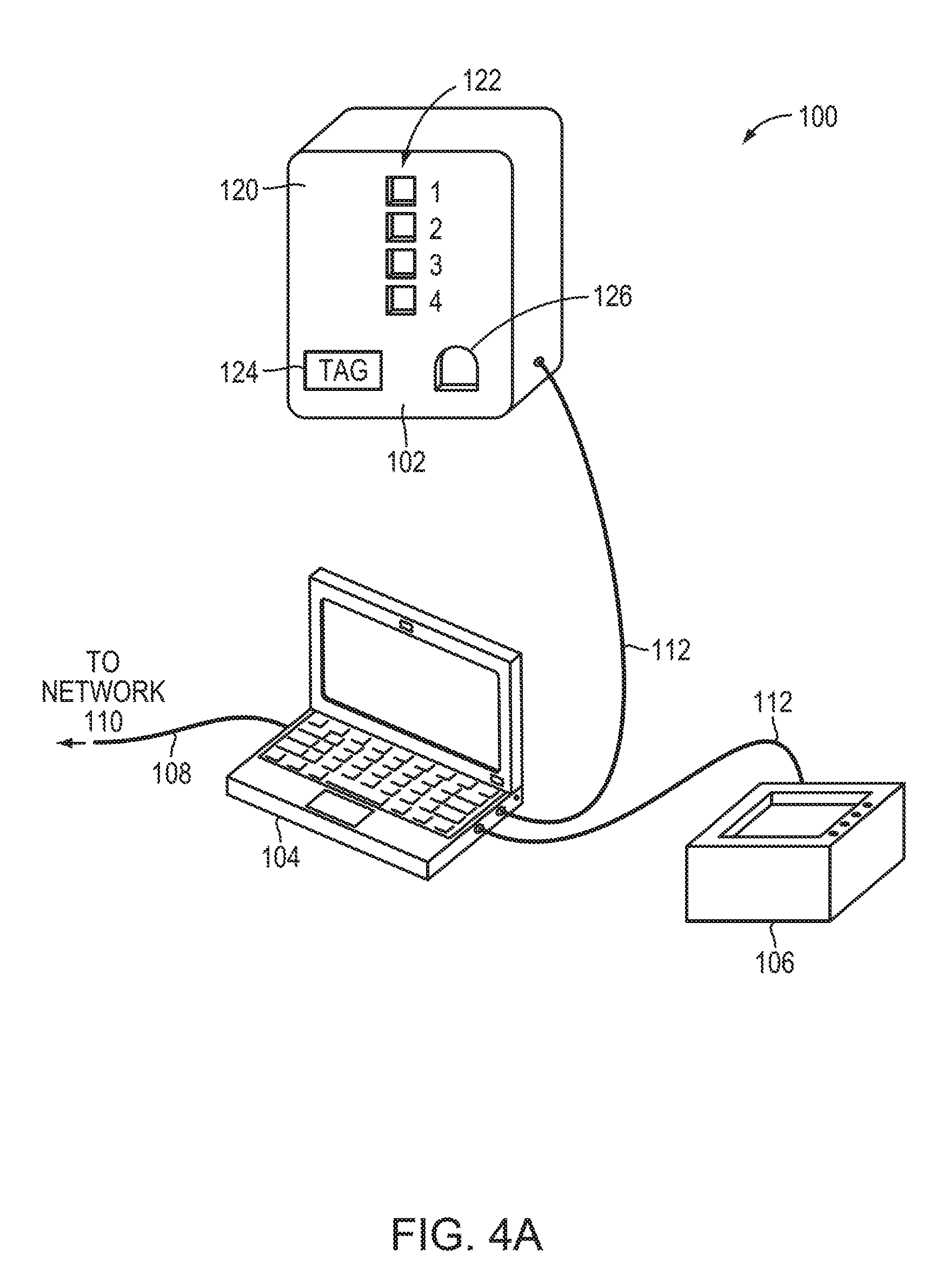

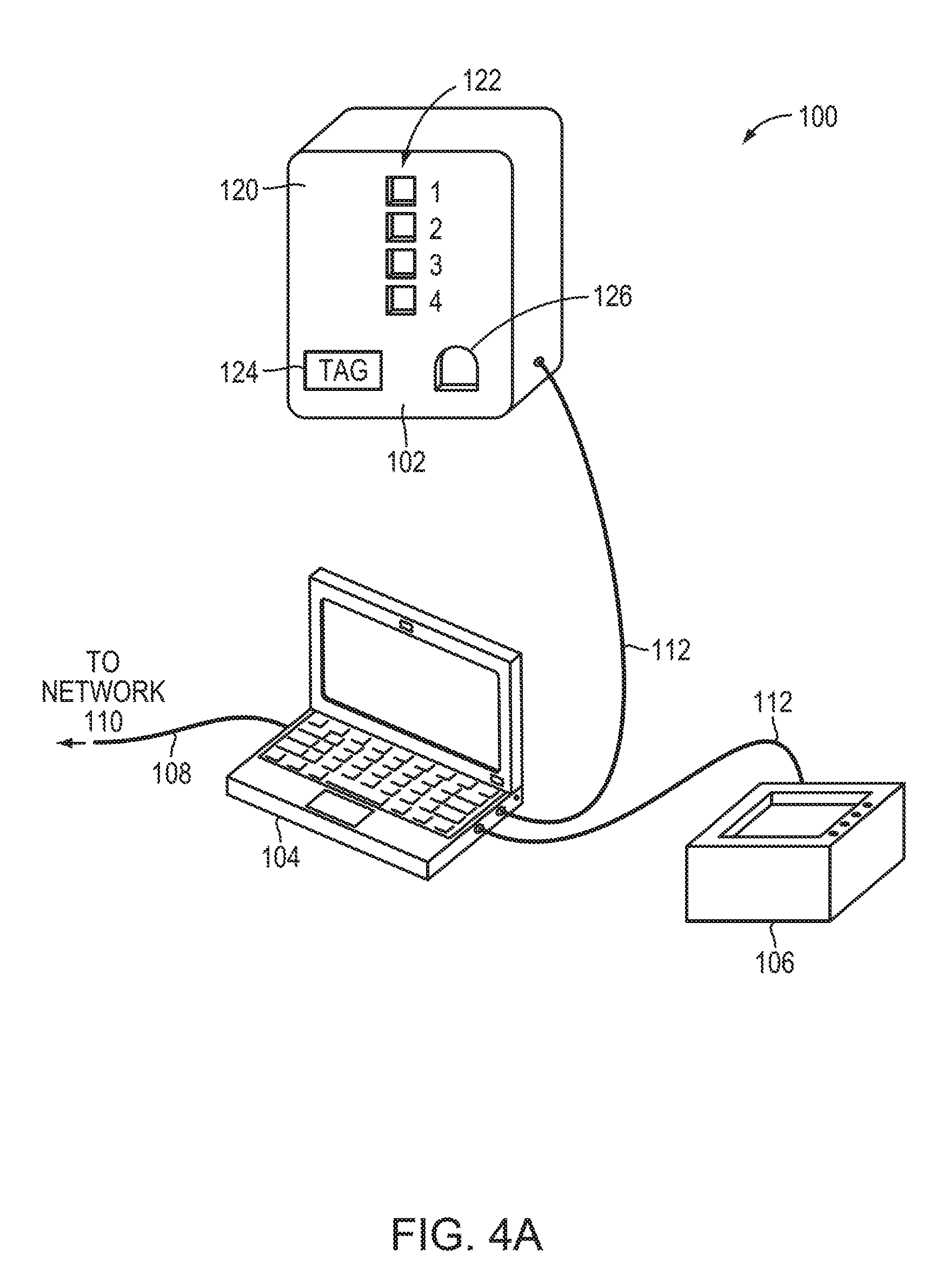

[0027] FIG. 4A depicts a schematic perspective view of a stun device testing system in accordance with an embodiment of the technology.

[0028] FIG. 4B depicts a schematic perspective view of a stun device testing system in accordance with another embodiment of the technology.

[0029] FIG. 5A depicts a schematic block diagram of a stun device testing system in accordance with another embodiment of the technology.

[0030] FIG. 5B depicts a schematic block diagram of a stun device testing system in accordance with another embodiment of the technology.

[0031] FIG. 6A depicts a schematic diagram of a stun device testing system in accordance with another embodiment of the technology.

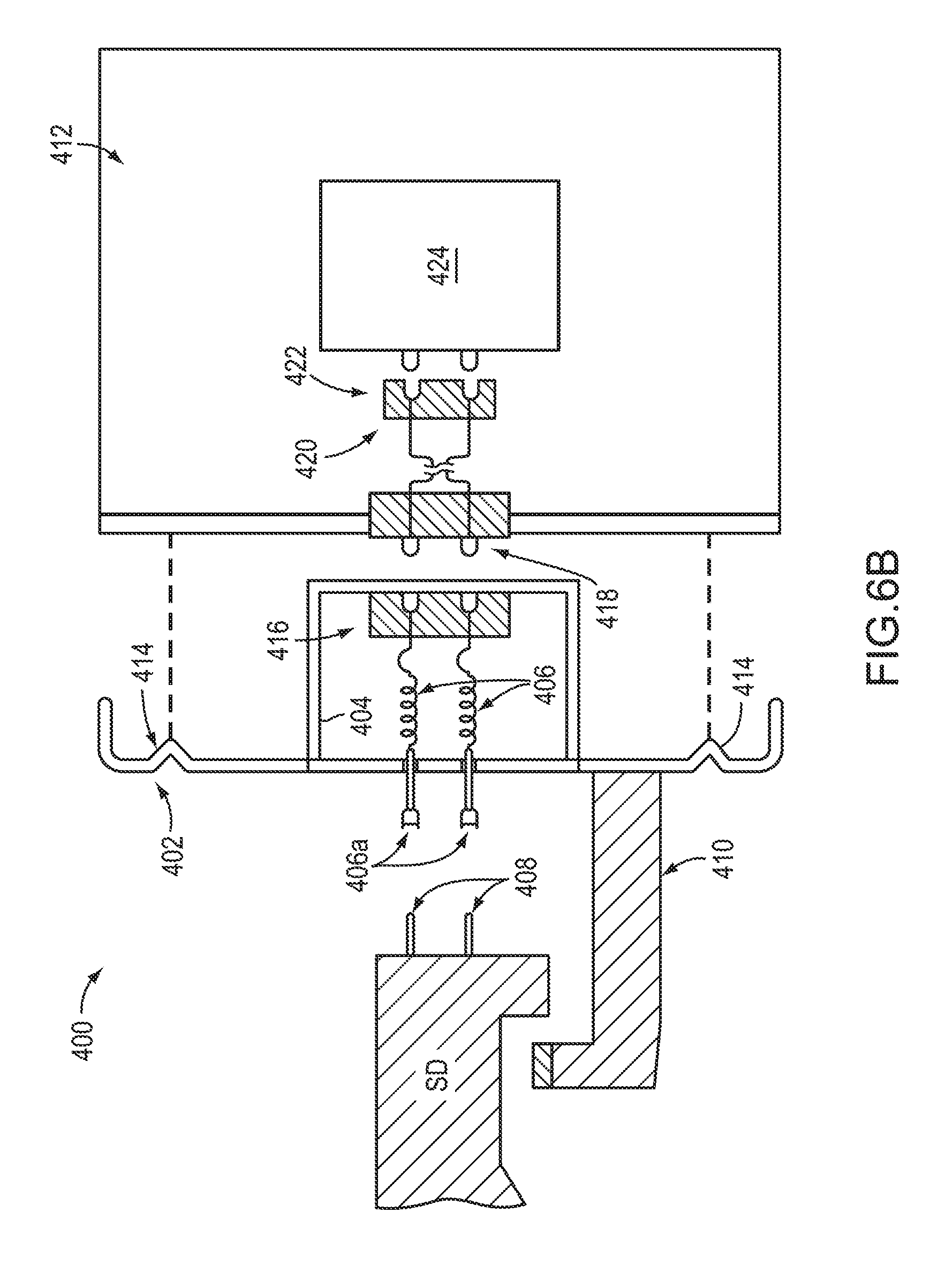

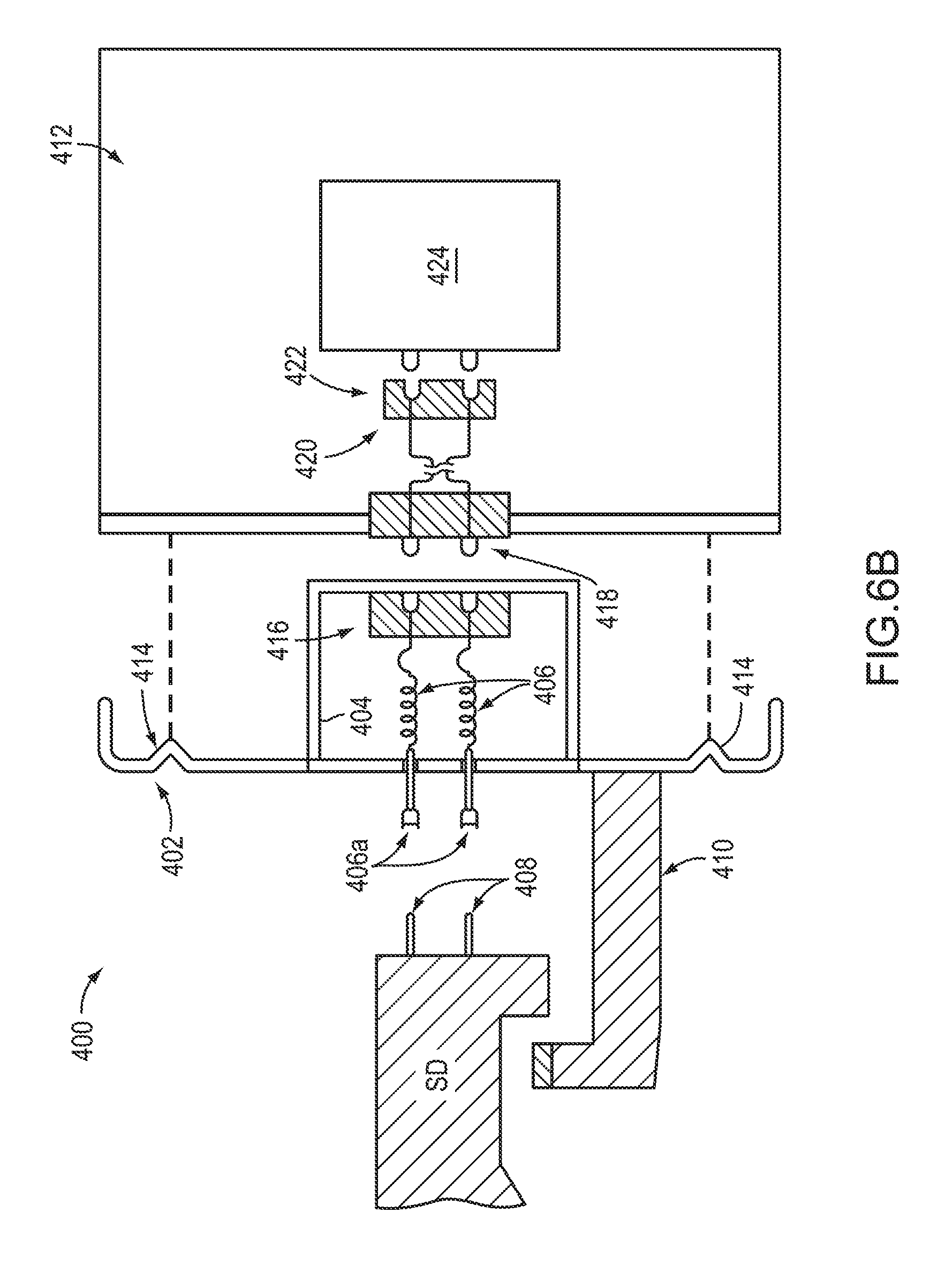

[0032] FIG. 6B depicts a schematic cross-sectional side view of an interface for a stun device testing system in accordance with one embodiment of the technology.

[0033] FIG. 6C depicts a partial perspective view of an interior portion of a housing for a stun device testing system in accordance with one embodiment of the technology.

[0034] FIG. 7A is a schematic block diagram of a hardware configuration of a stun device testing system in accordance with an embodiment of the technology.

[0035] FIG. 7B is a schematic block diagram of a field programmable gate array configuration for a stun device testing apparatus in accordance with an embodiment of the technology.

[0036] FIG. 8A is a schematic block diagram of a hardware configuration of a stun device testing apparatus in accordance with another embodiment of the technology.

[0037] FIG. 8B is a schematic block diagram of function performed by the hardware configuration of FIG. 8A.

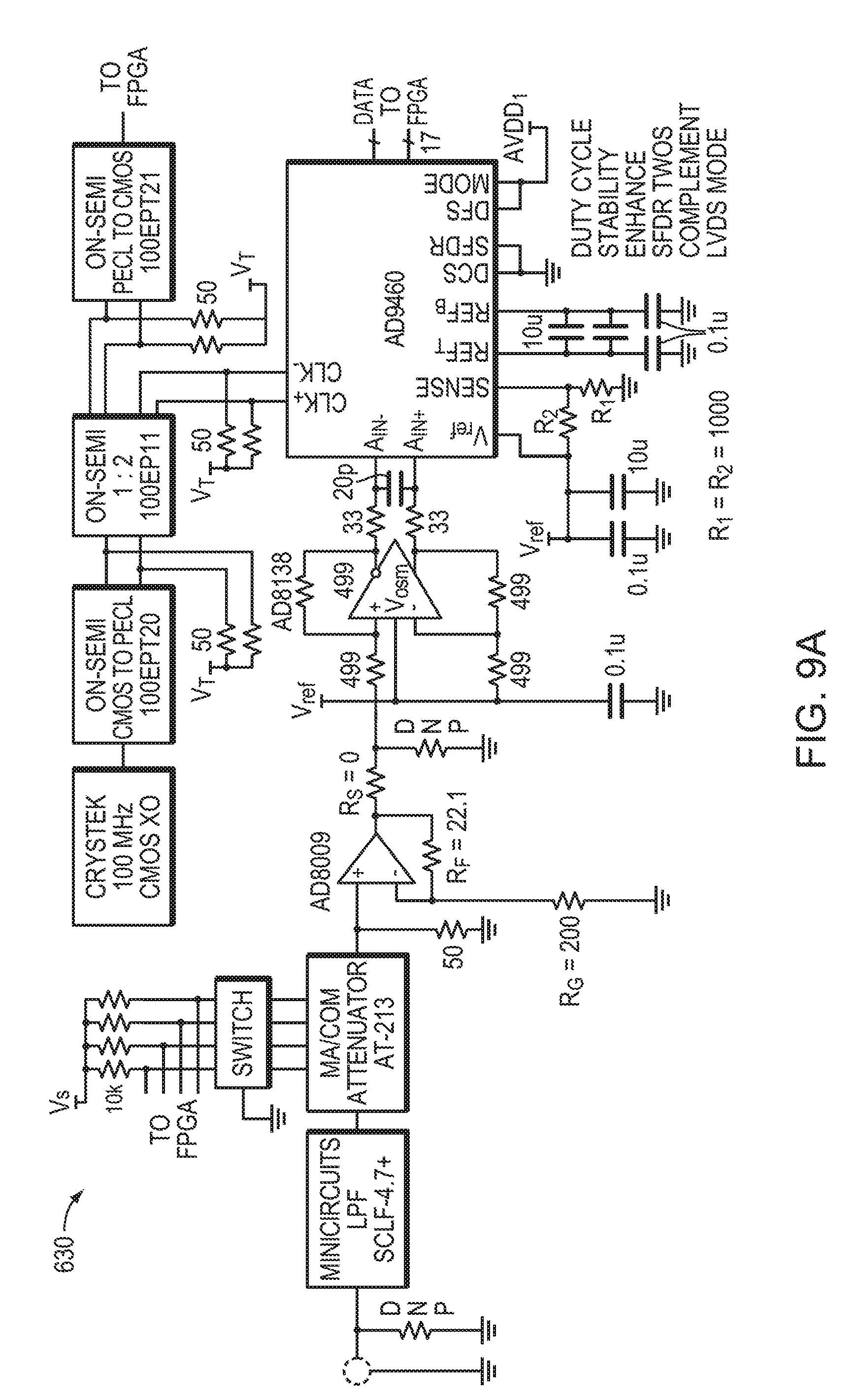

[0038] FIG. 9A is a schematic diagram of a circuit utilized in the hardware configuration of FIG. 7A.

[0039] FIG. 9B is a schematic diagram of a circuit utilized in a stun device testing system in accordance with another embodiment of the technology.

[0040] FIGS. 10A-10C depict a block diagram of a hardware configuration of a stun device testing apparatus in accordance with another embodiment of the technology.

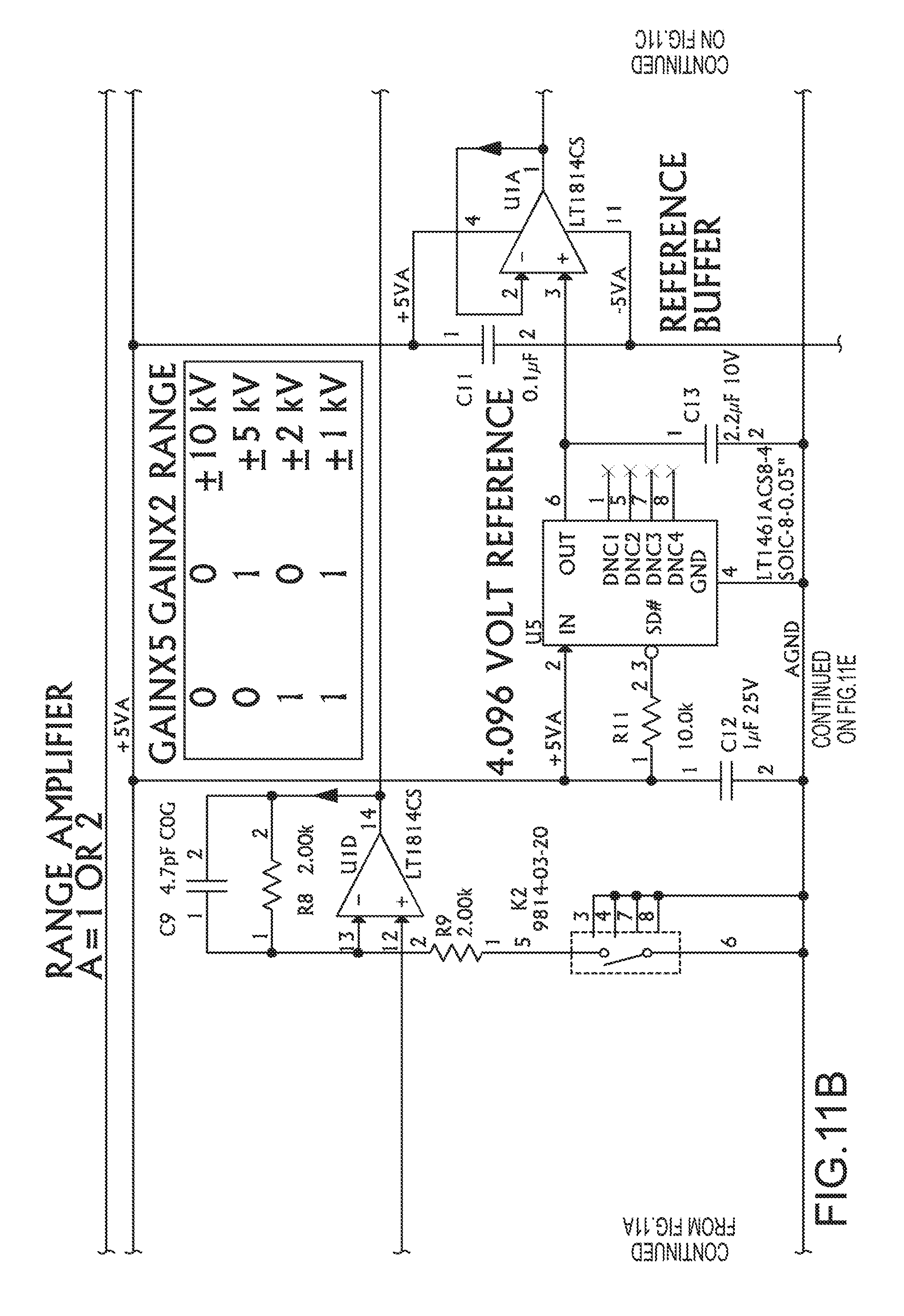

[0041] FIGS. 11-11F depict a schematic diagram of a front end circuit utilized in the hardware configuration of FIGS. 10A-10C.

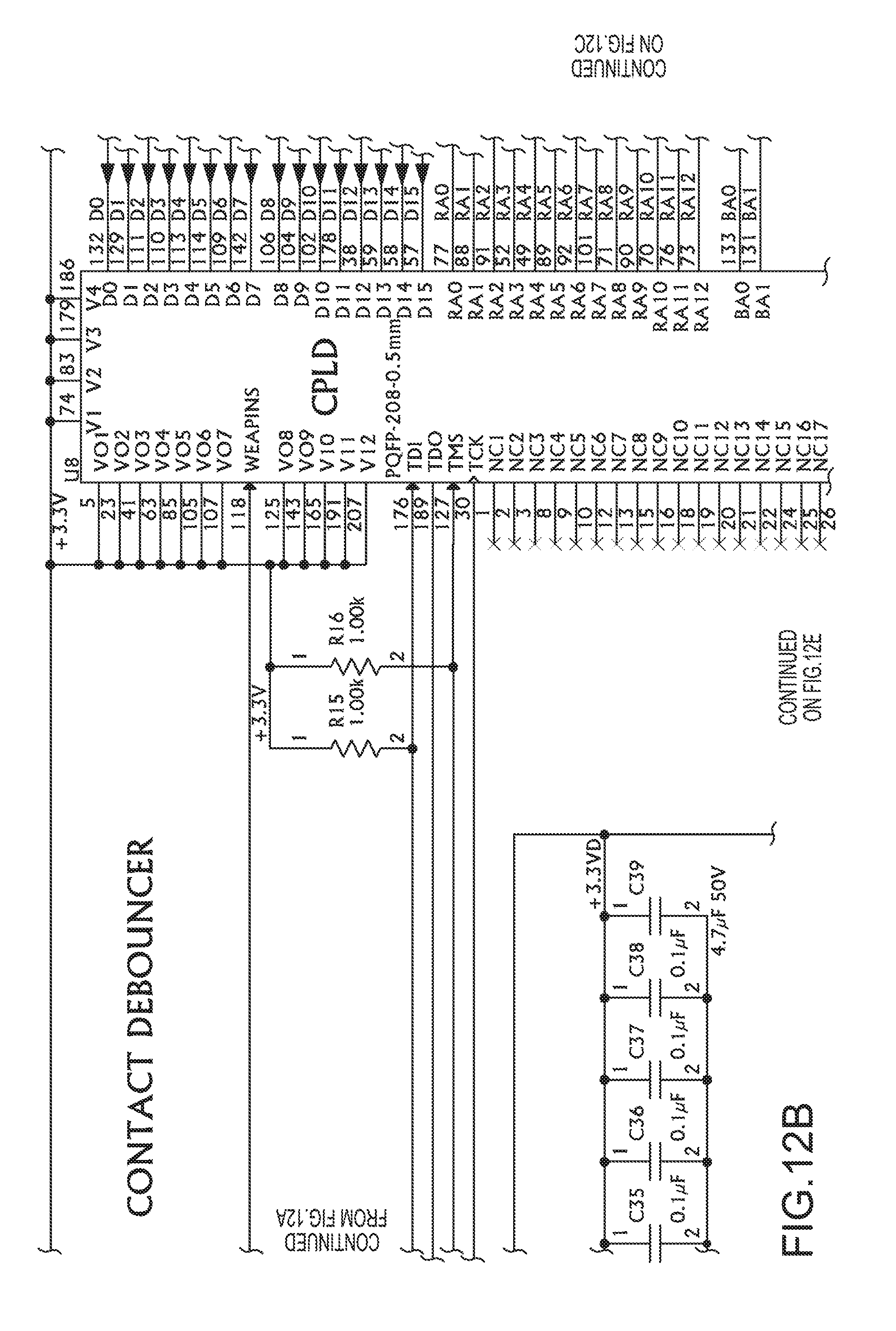

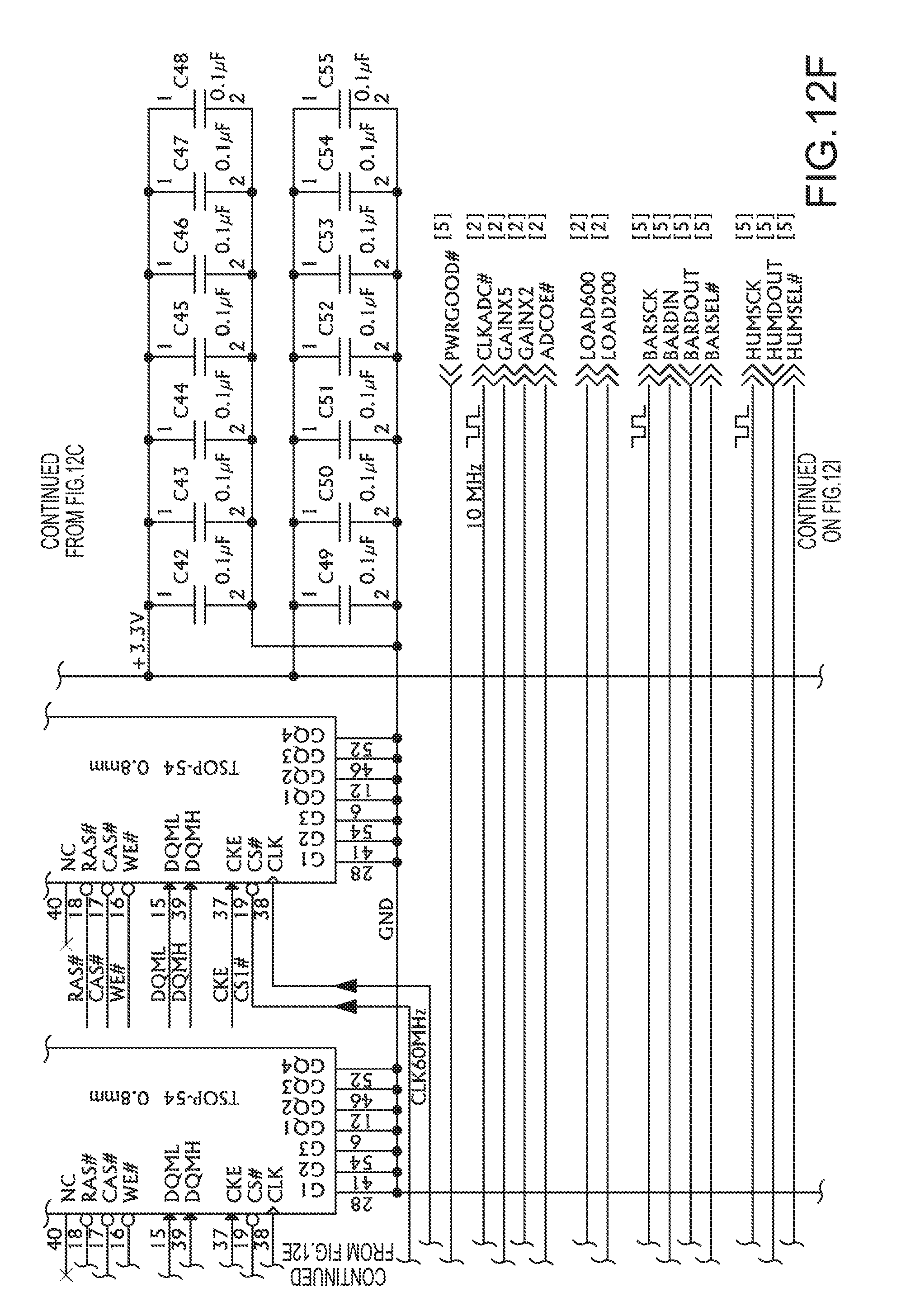

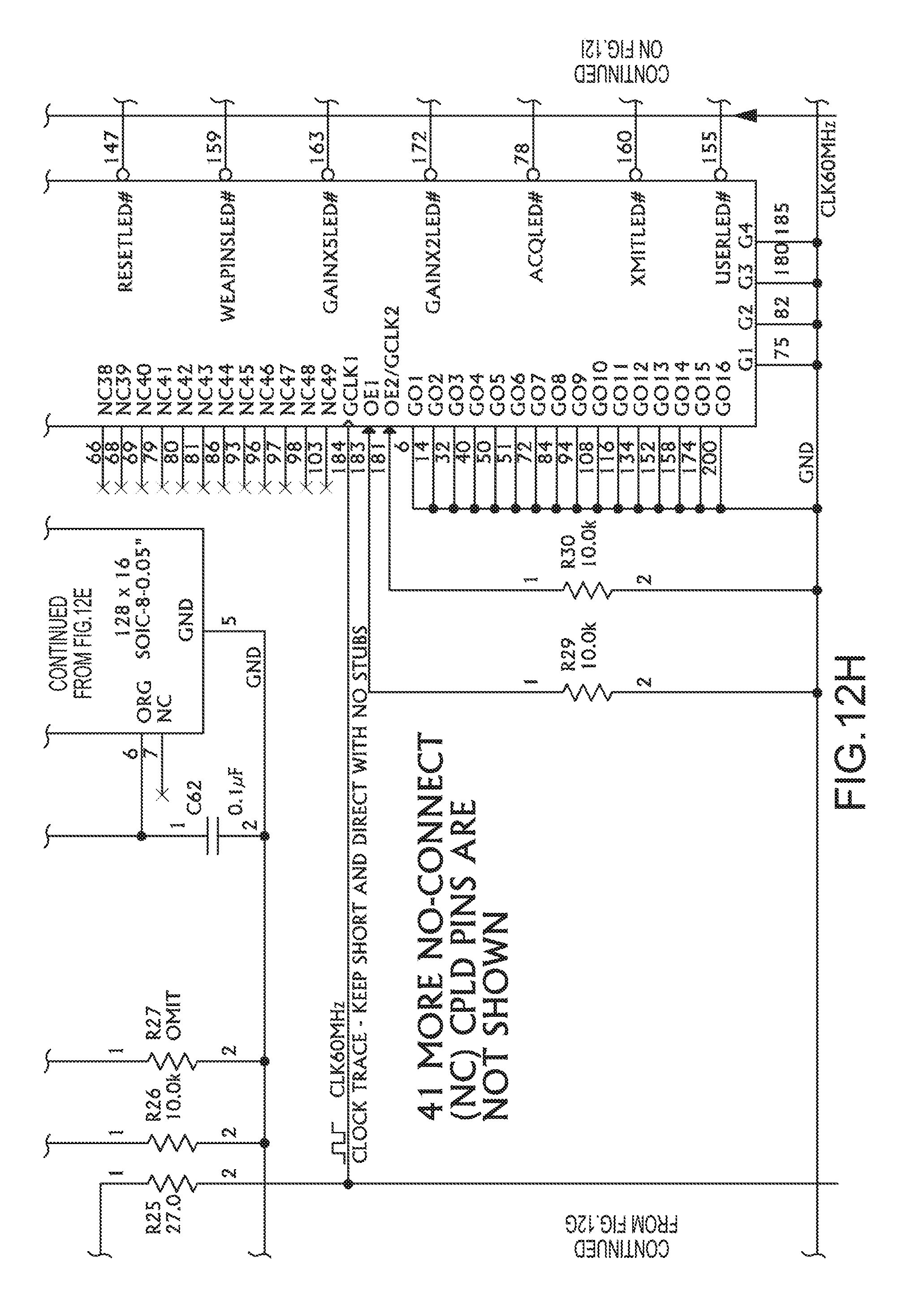

[0042] FIGS. 12-121 depict a schematic diagram of control circuit utilized in the hardware configuration of FIGS. 10A-10C.

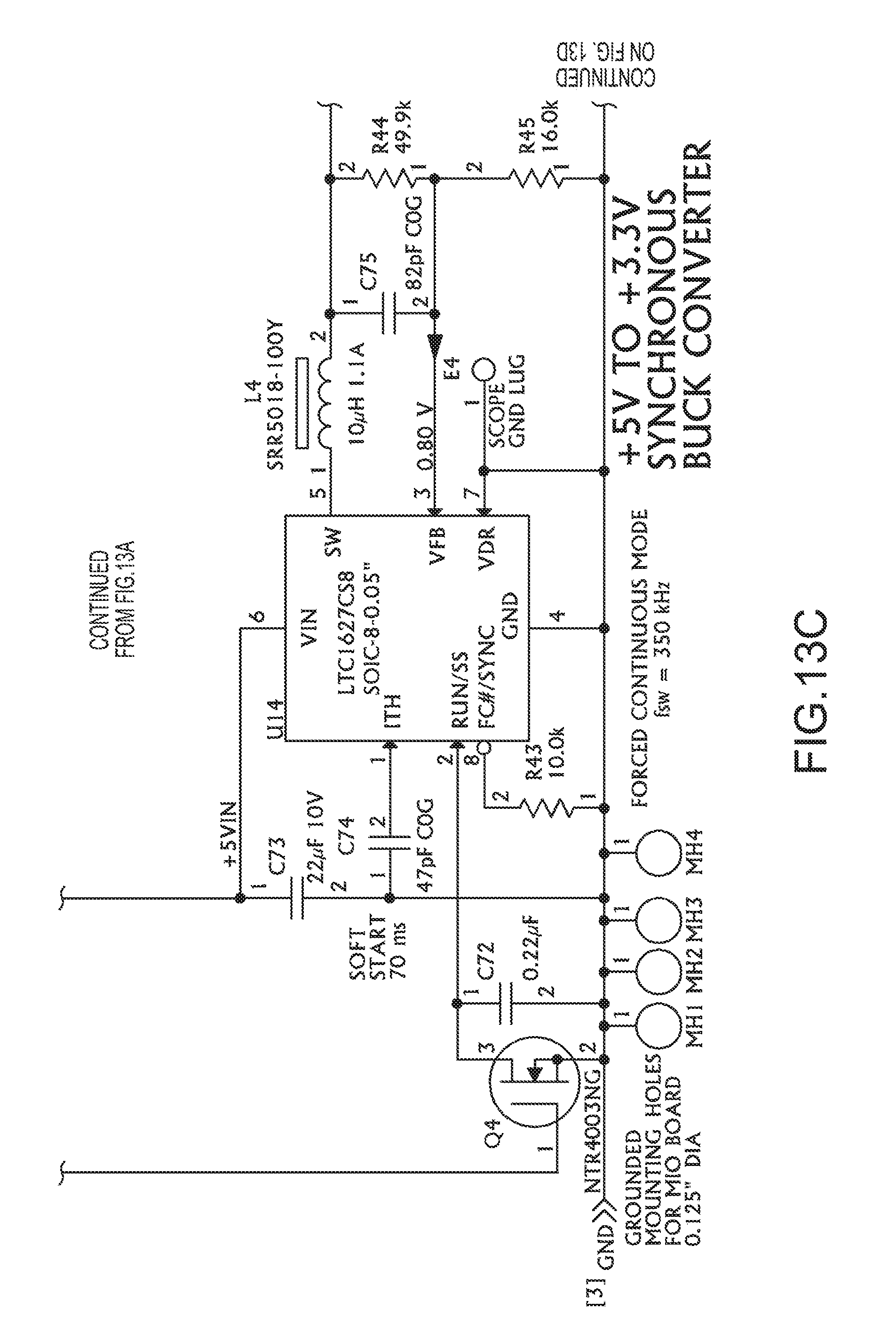

[0043] FIGS. 13-13D depict a schematic diagram of a power circuit utilized in the hardware configuration of FIGS. 10A-10C.

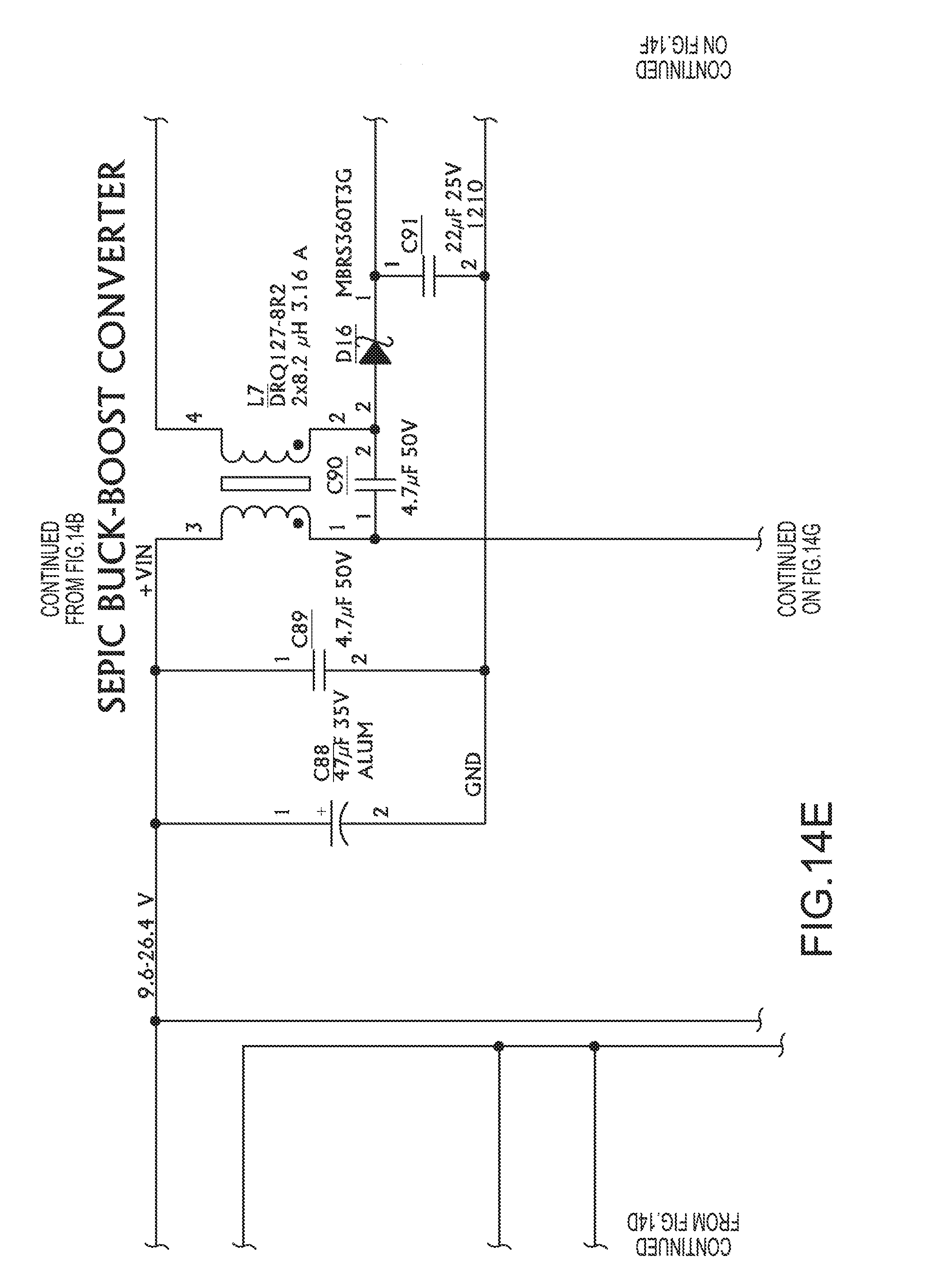

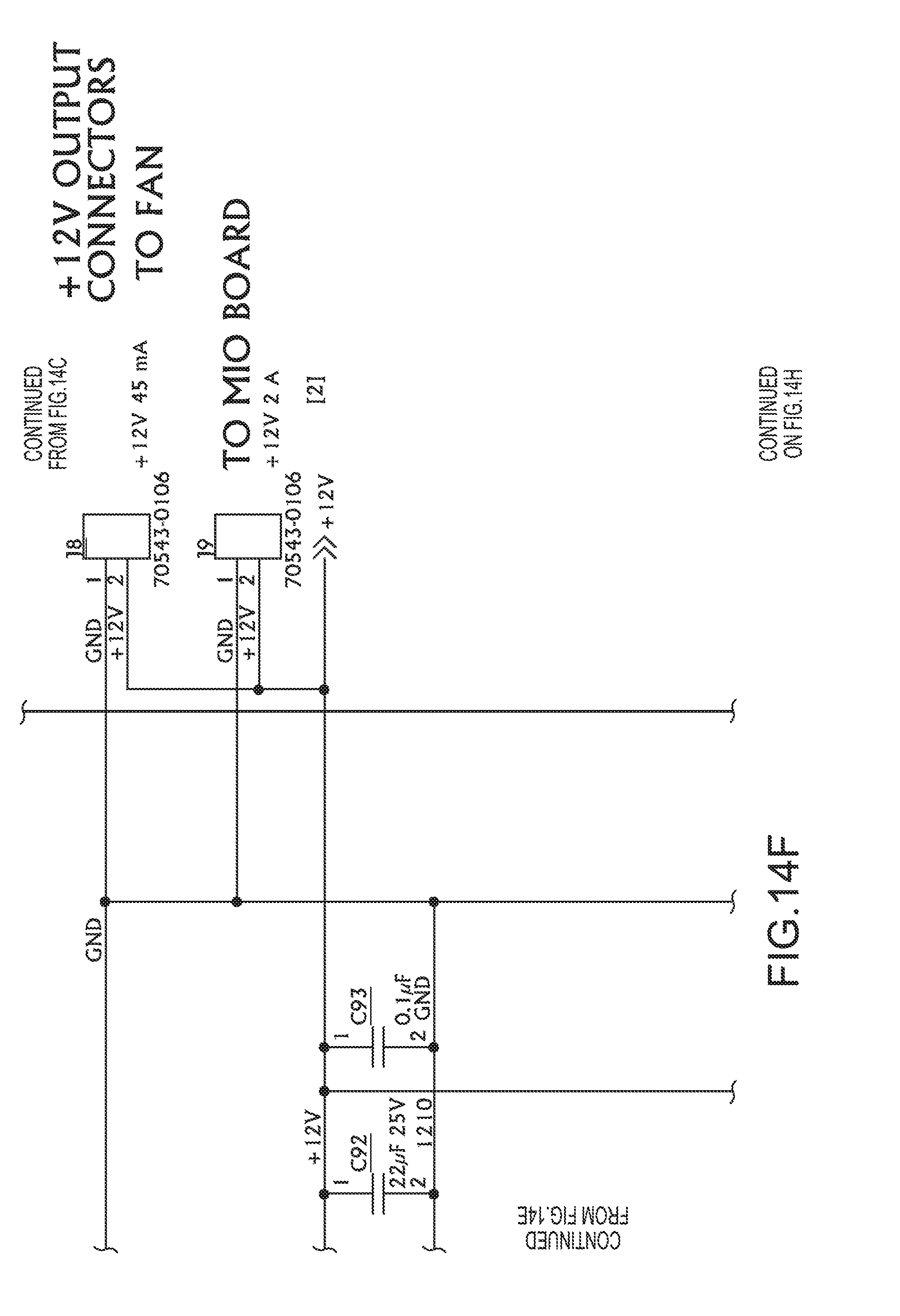

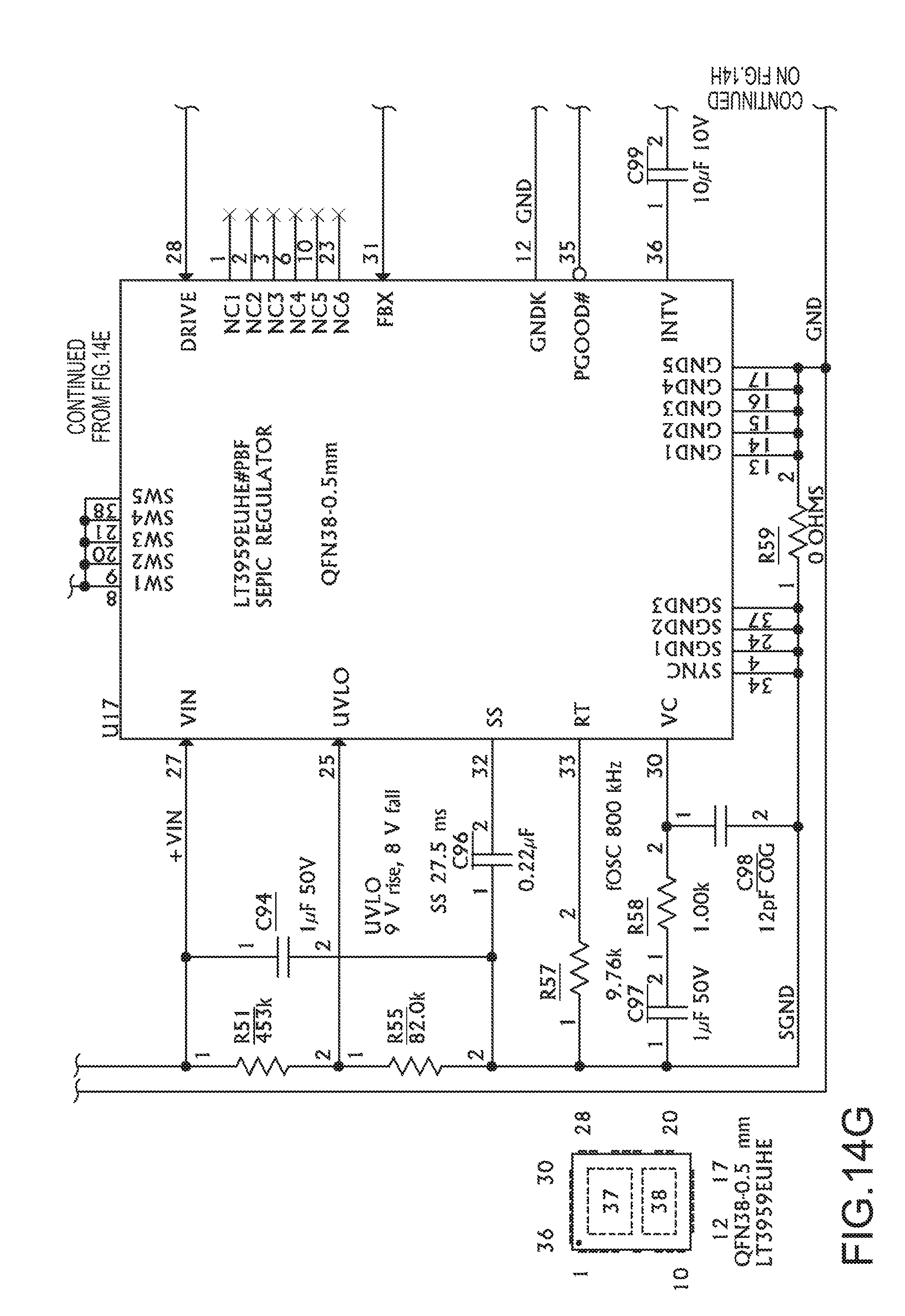

[0044] FIGS. 14-14H depict a schematic diagram of a sensor circuit utilized in the hardware configuration of FIGS. 10A-10C.

[0045] FIGS. 15A-15B depict an example CPLD clock diagram in accordance with one embodiment of the technology.

[0046] FIGS. 16A-16C depict an example addressing scheme in accordance with one embodiment of the technology.

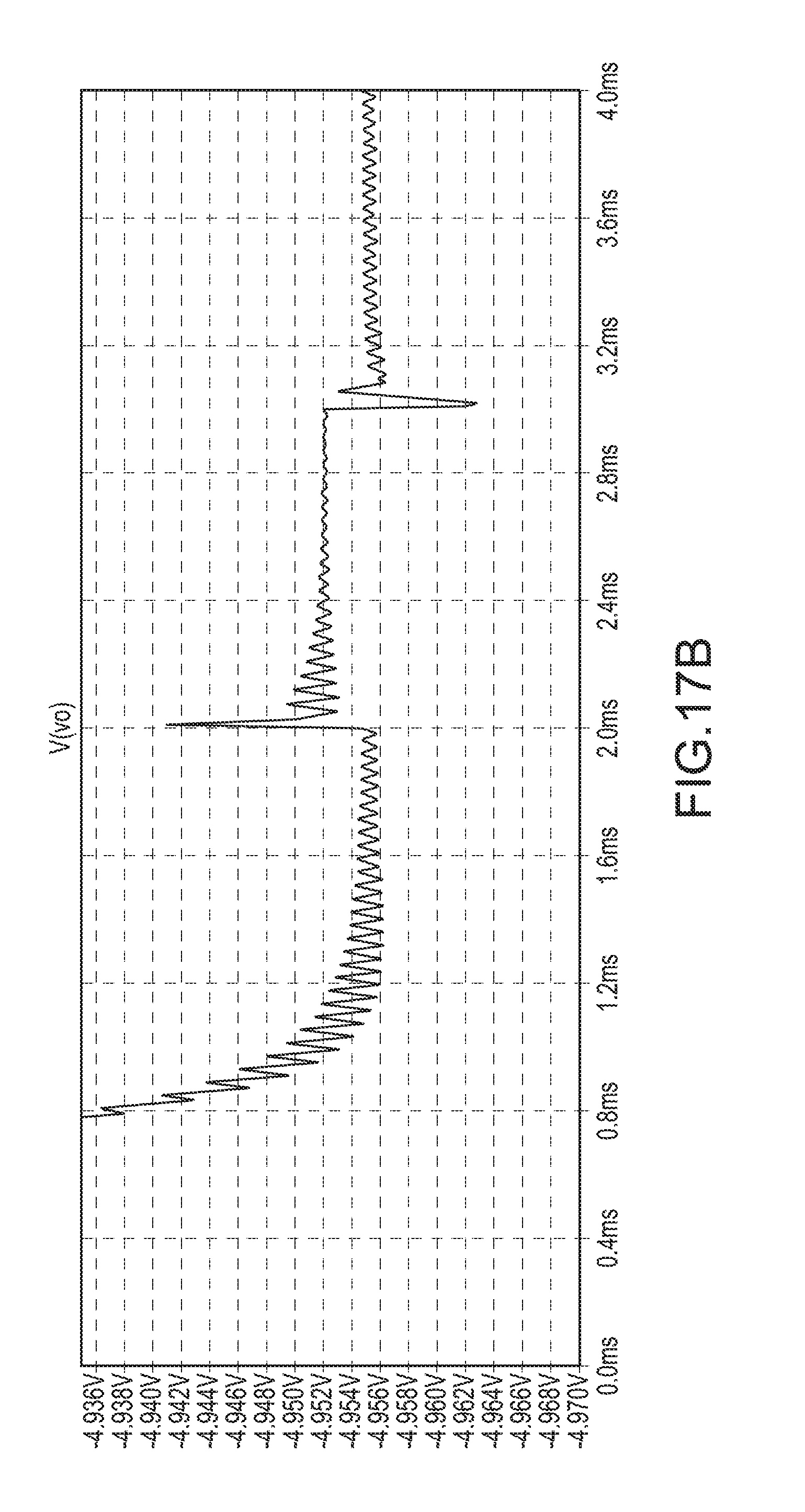

[0047] FIGS. 17A-17B depict output load responses to output load steps.

[0048] FIG. 17C depict a frequency and phase plot of a response of an input circuit.

[0049] FIG. 17D depicts an output load response to an output load step.

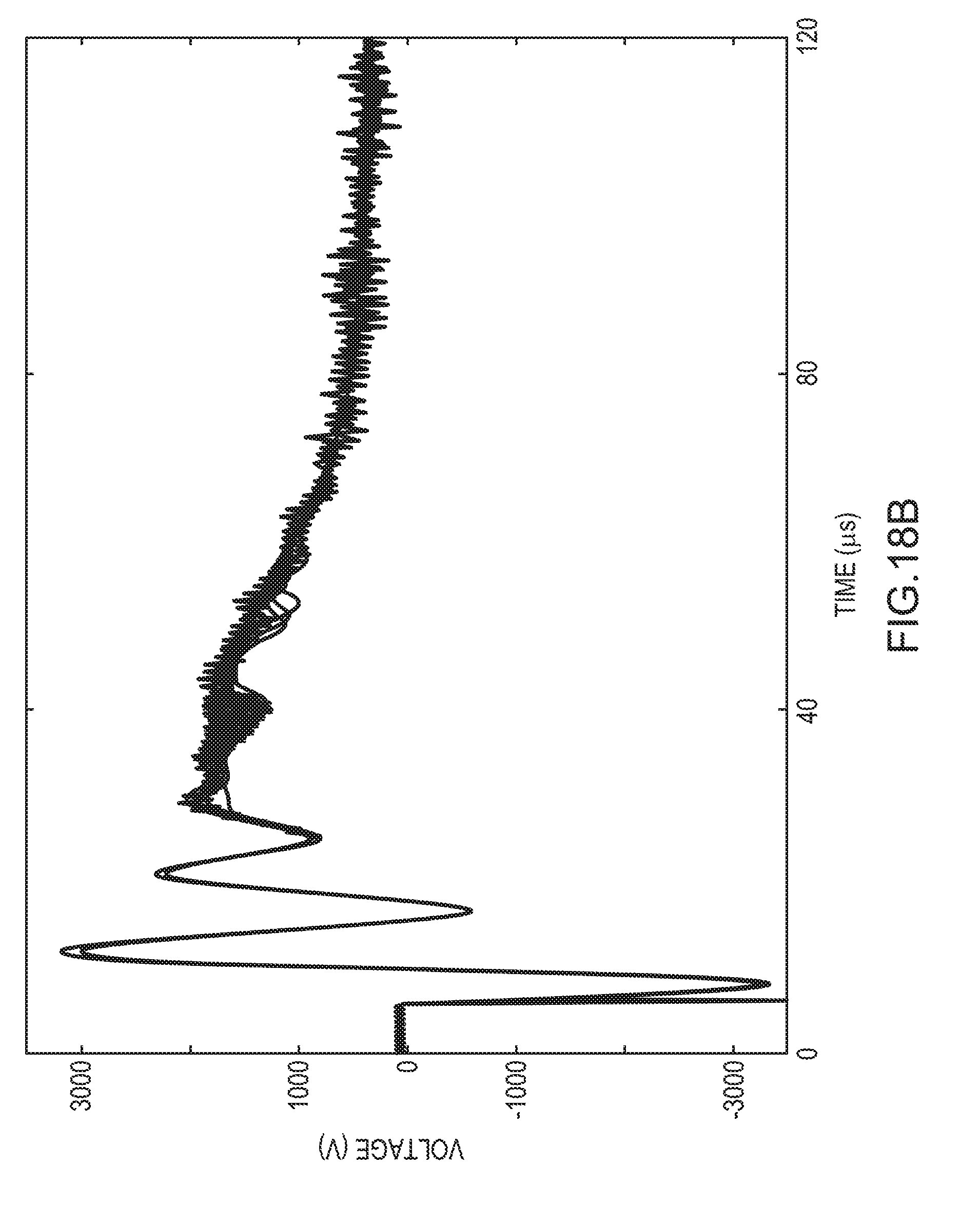

[0050] FIGS. 18A-18C depict waveform details and characteristics of the stun device of FIG. 2.

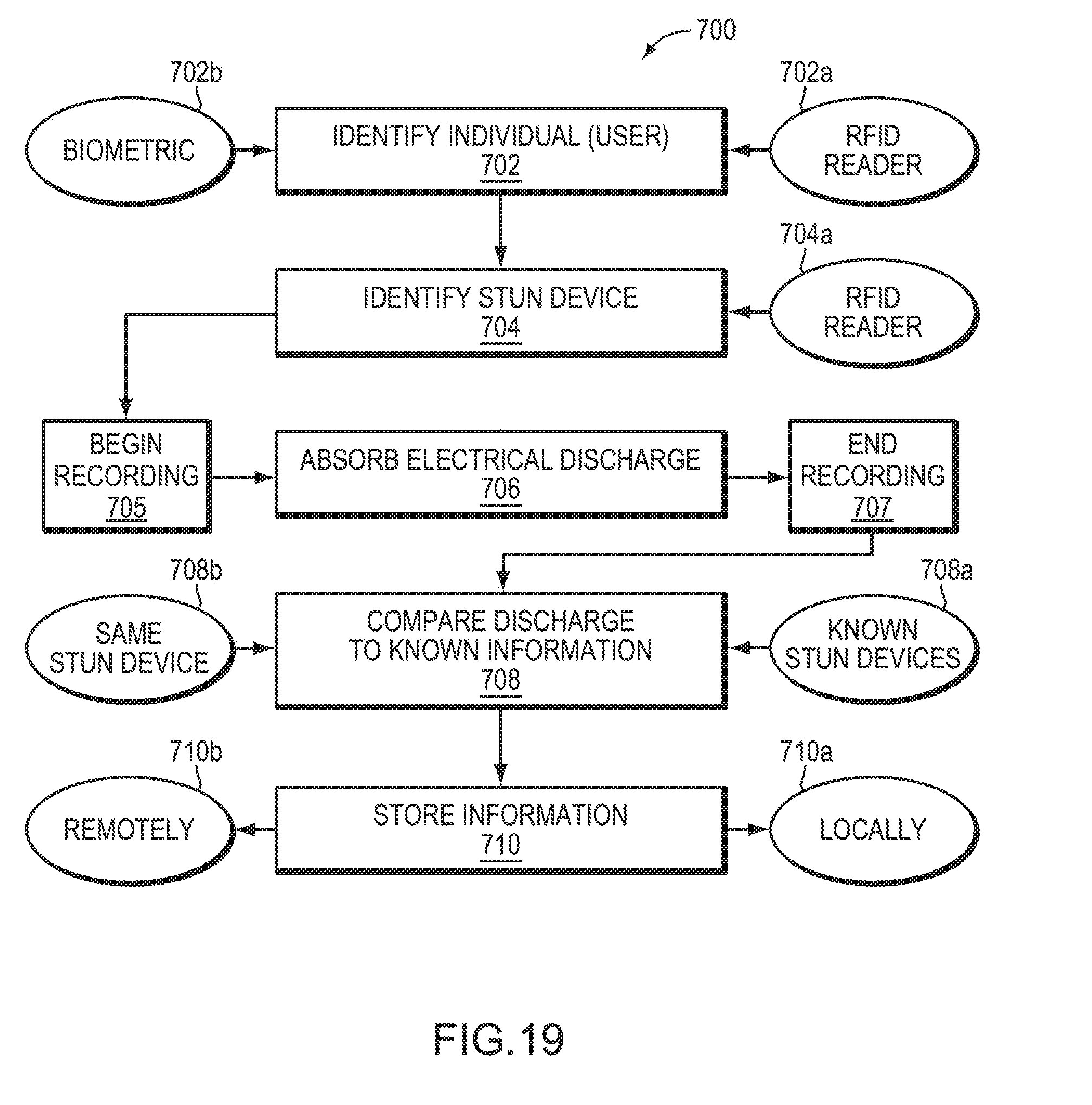

[0051] FIG. 19 depicts a method of testing an electric discharge stun device, in accordance with one embodiment of the technology.

[0052] FIG. 20 depicts a method of ensuring proper operation of an electric discharge stun device, in accordance with one embodiment of the technology.

[0053] FIG. 21 depicts a method of determining a biological response to an electric discharge from a stun device, in accordance with one embodiment of the technology.

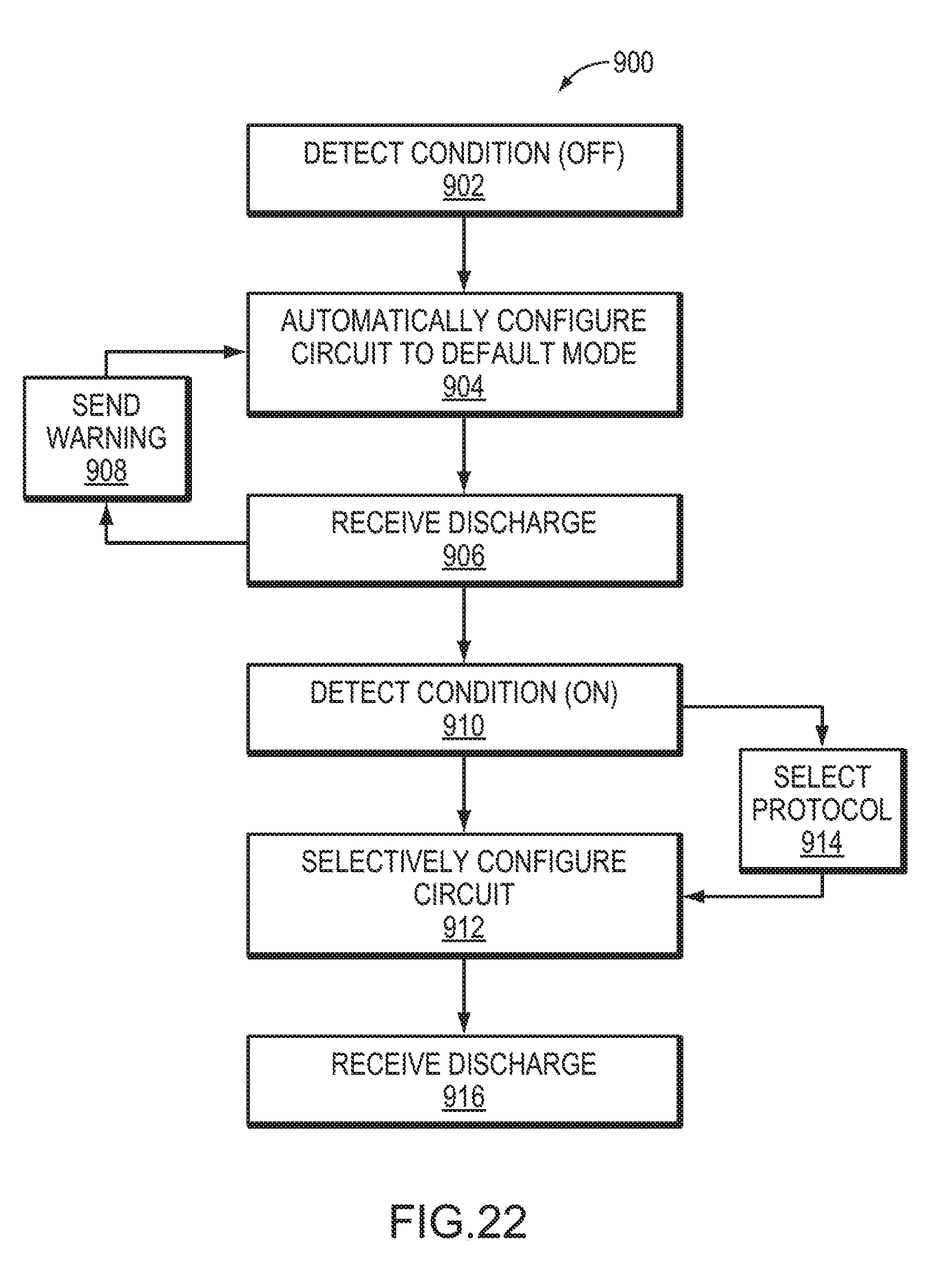

[0054] FIG. 22 depicts a method of configuring a circuit in a stun device testing system in accordance with another embodiment of the present technology.

DETAILED DESCRIPTION

[0055] FIG. 4A depicts a schematic perspective view of a stun device testing and data storage system 100 in accordance with an embodiment of the technology. The system 100 may include a tester 102, a computer 104 of any type (desk top, hand-held, PDA, laptop, etc.), a printer 106, and, optionally, an ethernet or other connection 108 to an external network 110. The various components of the system 100 may be connected via cable connections 112 or a wireless connection (not shown) of any type. The depicted system is able to record and store captured data for analysis of waveforms. Such analysis may be supported by extensive libraries of waveforms and other analytical tools, such as single or multiple software programs for the specific purpose of analysis, as appropriate, to maintain, manage and/or verify outputs of stun devices. Moreover, reporting of data via secure data custody links can be integrated in state and federal databases for the effective tracking of device performance and safety compliance. These libraries may be maintained either within the tester 102, the computer 104, or in an external database, accessed via the network 110. The libraries of information may be accessed or updated on a regular or semi-regular basis by software utilized by the computer 104 or the tester 102. Additionally, the information obtained from the system 100 may be sent via the network 110 to an electronic information repository (e.g., the cloud) that stores, processes, analyzes, etc., information from any number of similar systems, thus quickly building a database of information to be used and accessed by all authorized users of the systems. Authorized researchers could also access the data repository to perform additional research and analysis.

[0056] In one embodiment of the technology, the data from each discharge may be stored in a first storage medium, remote from or local to the device. All other information (e.g., historical data from previously tested devices, known data from known stun devices or manufacturers, etc.) may be stored in a second storage medium. In this way, the information in the second medium may be updated on a regular or semi-regular basis (as described in further detail herein), while the information in the first medium serves as a record for all tests performed with the testing system. In certain embodiments, the first and second mediums may be a single medium for information storage. In certain embodiments, the data may be stored in a compressed format, for example, compressed to a factor of up to about 10:1. Other compression factors may be utilized.

[0057] In the system 100 depicted in FIG. 4A, the tester 102 includes a shallow housing 120 that may be mounted on a wall at shoulder height. Alternative embodiments may be configured for table-top usage, or may be dimensioned to be portable. Such portable devices may be maintained in a carrying case and may include power, communication or other cabling required to use the tester in remote locations. The front of the box presents four testing ports 122 (labeled 1, 2, 3 and 4) and two identification ports 124, 126. The operation and configurations of the testing ports 122 are described below. In some embodiments, described below, a single port may be utilized to perform the measurements described herein, with the stun device tester automatically adjusting the resistance values and/or spark gap configurations during a stun device testing procedure. A single port may be particularly desirable in certain embodiments because it reduces potential shock hazards. In other embodiments, two ports utilizing spark gaps and two ports without spark gaps may be used (adjusting the resistance values as required during a stun device testing procedure). Still other embodiments may utilize two low resistance ports and two high resistance ports (adjusting the spark gap as required during a stun device testing procedure).

[0058] In the tester 102 depicted in FIG. 4A, the four testing ports are utilized to determine a terminal model of the stun device under test. Both the voltage and current developed by a stun device may be used to determine the terminal model. Voltage V is fairly straightforward to measure directly. Current I is usually measured by observing the voltage developed across a known resistance R (or impedance), and derived using the formula I=V/R. Thus, to determine the current, R must be known. To determine the nature of the voltage source, total resistance needs to be known. The total actual resistance is the sum of the resistance of the source and the resistance of the load. The resistance of the load may be estimated by analysis or statistical measurement. In general, it has been determined that, for a stun device tester, a load resistance in the range of about 30 ohms to about 300 ohms is desirable. To predict the current developed by the stun device, the source resistance must also be determined. This can be done by measuring the voltage developed across two different, known load resistances. In one example, a first measurement is conducted with a 50 ohm load, which is associated with a first testing port 122 (port 1, for example) on the tester 102. A second measurement is conducted with a 100 ohm load, which is associated with a second testing port 122 (port 2, for example) on the tester 102. In the first measurement, 5000 volts is developed across 50 ohms; in the second measurement 6667 volts is developed across 100 ohms. The equations governing the two measurements may be simultaneously solved to determine that the source voltage is 10000 and the source resistance is 50 ohms. Thus, the two measurements (i.e., two experiments) yield two values that can be used to determine the source resistance.

[0059] The other two ports 122 (ports 3 and 4, for example) utilize a spark gap in series with the load resistance. Port 3, for example, utilizes a spark gap across 50 ohms; and port 4, for example, utilizes a spark gap across 100 ohms. Spark gaps generally have a very low resistance when conducting, accordingly, there is little appreciable increase in the load resistance. However, spark gaps may introduce transients in the stun device discharge that may affect the stimulus from the device in a potentially injurious way to a target. The behavior of spark gaps is dependent, in part, on the amount of current conducted by the spark gap. Accordingly, two of the ports repeat the measurements with two different load resistances, but also utilize the spark gaps to allow observation of their effect, if any. Spark gaps are present in certain stun devices.

[0060] The first identification port 124 may be utilized to read RFID tags on either or both of a stun device and a badge or other unique identification associated with a user. Alternatively, other readers (for example, bar code readers or other optical or tactile scanners) may be utilized. The second identification port 126 may also or alternatively be utilized to identify a user based on a biometric identifier, such as a user fingerprint. Other biometric systems (for example, voice detectors, retinal scanners, etc.) also may be utilized. A source of illumination may be associated with any or all of the elements and can be used to guide the user through the testing steps. The source of illumination may be a light bulb or light-emitting diode (LED) located within or proximate each port, for example.

[0061] The tester 102 can be used for purposes of registration and device characterization. In one embodiment of a test sequence, a user starts a stun device test by placing a finger in the fingerprint reader 126. The tester 102 responds by illuminating the fingerprint reader light. Additionally, the computer 104 may be activated to provide additional prompts to the user, or to record the testing sequence and results. Regardless, if the user is registered to use the system 100 and/or a stun device, the fingerprint reader light turns off and the light associated with the RFID reader 124 is illuminated. The user then positions the stun device by the reader 124. Successful reading of a registered stun device results in the illumination of testing port 1. The user places the stun device in testing port 1 and discharges the device. Successful reading results in turning off the light in testing port 1 and turning on the light in testing port 2. This process continues until the stun device has been successfully discharged at all four ports. The tester uses the associated computer 104 to archive the discharge data in the central repository (alternatively, the computer 104 may archive the data automatically, either at that time, or later) and, if desired, prints out a summary of the test results on an associated printer 106. The summary may include the measured average energy duration of each stimulus pulse, the number of pulses and total duration of the stimulus, an estimate of the battery condition based on the stun device's previous archived test results, changes observed within the current test, etc. Additionally, it may report the number and nature of observed variations from normal discharge. Advisory information including "Replace Battery" and "DO NOT USE" may also be included in the report. Additionally, the summary may include an image of the waveform, and/or other relevant characteristics thereof. The summary may also include an indication of whether the stun device is approved for subsequent use on a target, based on an analysis of the waveform or other discharge characteristic. The printed summary also may serve an important documentary function, creating a record of the operation of the device prior to use against a human target.

[0062] FIG. 4B depicts a schematic perspective view of a stun device testing system 150 in accordance with another embodiment of the technology. The system 150 includes a tester 152 that may communicate, via a wireless network 154, with a computer 156 and/or a remote storage database 158. Wireless communication helps reduce or eliminate the likelihood of undesirable electrical events being directed to, e.g., the computer 156, should an error occur at the tester 152 when receiving a discharge from a stun device. As described above, the tester 152 also may be a stand-alone device that performs all processes described herein. In the depicted embodiment, the tester 152 includes a single port 160 on a housing 162 for receipt of a discharge end of a stun device. The tester 152 also includes a user interface 164, in this case, a touch screen that displays a graphic user interface. A cord 166 connects the tester 152 to a source of power, such as a building power source, auxiliary vehicle power source, or other source. Alternatively or additionally, the tester 152 may include a switch 168 used to toggle power to the tester 1523. As described below, the tester 152 may be configured such that an unpowered tester 152 may still receive discharges safely, even when unplugged or powered off.

[0063] The computer 156 and/or remote storage database 158 may connect to the wireless network 154 so as to communicate with the tester 152. In other embodiments, the tester 152 may communicate directly with the computer 156 and/or remote storage database 158 via a Bluetooth, RFID, or other wireless or wired connection. In an alternative embodiment, the tester 152 may be controlled by the remote computer 156, which may display on-screen instructions typically displayed on the display 164 of the tester 152. The internal configuration of the tester 152 is described in further detail below. The tester 152 is utilized to test stun devices that have both a high discharge voltage and frequency, thus layout of the internal circuits, as well as automation of the testing processes helps ensure consistent results.

[0064] FIG. 5A is another embodiment of a stun device testing and data storage system 200. The system 200 includes a tester 202 having one or more testing ports or interfaces 222 for receiving a discharge end of a stun device SD. The tester 202 also includes a processor 230 for processing the data received from the stun device SD discharge, as well as for controlling the various elements of the tester 202, described below. The processor 230 receives information from a sensing circuit 232, which receives the discharge from the stun device SD. The processor 230 also communicates with the user interface 234, which may include one or more discrete components. One component may be a first identification port 224, as described above, i.e., a bar code scanner, RFID reader, etc. Other elements of the user interface 234 include a second identification port 226 (e.g., a fingerprint scanner, a voice recognition device, a retinal scanner, etc.). An alphanumeric keypad 236 (similar to those used on telephones) may also be utilized to enter identifying information about the stun device SD or user. In alternative embodiments, the keypad may be a complete keyboard typically utilized on a computer, either built into the tester or remote therefrom and connected by a cable. In other embodiments, a touch screen or voice recognition system having a graphical user interface may also be utilized.

[0065] The tester 202 provides information and feedback to a user via one or more integrated or remote components. For example, a display screen 238 may be utilized to present instructions, images of discharge waveforms, results, or other data to a user. In certain embodiments, the display screen 238 may be incorporated with the touch screen described above. One or more LEDs 240 may be used to provide simple instructions or feedback (e.g., "Proceed," "Fail," "Continue," "In Spec," "Out of Spec," etc.), and a piezoelectric sounder or other sound generating device may also or alternatively be utilized. Additionally, output from the processor 230 may be delivered to a remote oscilloscope 242 or signal analyzer for further research, analysis, or testing purposes. The tester 202 may send certain results to a printer 206, which, in certain embodiments, may be integral with the tester 202. Such an integral printer may be similar to a register printer that prints to a ribbon of paper media. The tester 202 may be a stand-alone device or may be connected directly to a network or internet connection 210, as described above. A stand-alone computer 204 may also be connected to the tester 202 to collect, process, and/or store test data, or to provide diagnostic testing of the tester 202 itself. As described above with regard to FIG. 4A, the computer 204 may be connected to a stand-alone printer 206a, and/or a network 210a.

[0066] FIG. 5B depicts a schematic block diagram of a stun device testing system 250 in accordance with another embodiment of the technology. A stun device SD is inserted into a port 252 of the tester 250. The tester 250 includes a resistor/relay module 254. The resistor/relay module 254 is in communication with a processor 256. A single board computer 258 integrates the function of a wireless transmitter 260, a touch screen 262, as well as a barcode scanner 264. Additionally, the tester 250 may also include one or more environmental modules 266 (as described further below). In certain embodiments, it may be desirable for the environmental module 266 to be downstream of an air intake fan 268 to help ensure accurate readings.

[0067] FIG. 6A depicts a schematic diagram of a stun device testing apparatus 300 in accordance with another embodiment of the technology. The testing apparatus 300 may include a stand-alone tester 302 that includes the circuits to test various stun devices SD. Additionally, the tester 302 may be connected to one or more adapters 350. Each adapter 350 may be manufactured to mate with the discharge end of a particular stun device SD via a coupling 352, and may include a common connector 354 configuration. The adapter 350 may include a voltage divider 356 within the adapter housing 358, as well as the stun device coupler 352. In certain embodiments, the voltage divider 356 may be utilized when the maximum voltage of a stun device is too high for the tester circuitry, and must be reduced to accommodate the measurement and prevent damage to the tester. While a voltage divider may not be required for several known devices on the market today, other devices exist or may be developed with specific characteristics that require modification for measurement on the safety tester. In certain embodiments, the voltage divider may be incorporated directly into the tester 302, as opposed to the adapter housing 358.

[0068] The coupler 352 connects the output leads of the device SD to the adapter 350. A coupler may be manufactured for each known stun device on the market or, alternatively, a universal coupler may be utilized to reduce costs associated with multiple custom couplers. Specifically configured couplers (or adapters, if the coupler is directly integrated into the adapter) may be required, because stun devices vary dramatically in form-factor. Some are large or small handgun formats, some are batons, and others are rectangular shapes. Some stun devices have protruding prongs and some utilize flat contact strips. Projectile-dart based stun devices should be measured with the dart accessory in place, as well as with the accessory disconnected, to verify output of the device when the external device contacts are pressed directly against the skin or penetrating the skin surface. In addition, the adapter 350 provides a high insulation factor to guard against electrical shock to the operator, since stun devices often have a high degree of arcing that can contact a nearby user during device actuation. Thus, an adapter/coupler combination is helpful to both secure a reliable connection to the tester 302 and to provide insulation to prevent electrical shock to users. The adapter or port may be liquid tolerant.

[0069] Specifically configured interfaces, ports, couplers, adapters may also include supports or other physical structure to ensure proper alignment between the stun device and the tester. An exemplary, removable interface 400 is depicted in FIG. 6B. The interface 400 includes a faceplate 402 secured to a receiving port or housing 404. Two compliant members or spring contacts 406 are secured within, and extend from, the receiving housing 404. Compliant members 406 (e.g., springs) help ensure contact between the contact tips 406a and the discharge elements 408 located on the stun device SD. The interface 400 may include a docking station or shelf 410 that provides reliable stun device SD placement and alignment. In certain embodiments, it may also enable the user to release the stun device SD during testing for safety purposes. The interface 400 may be secured to the tester 412 with screws, bolts, magnets, latches, spring clips, or other releasable coupling elements 414. Interfaces may be readily removable from the tester, allowing a number of interfaces adapted to receive specific stun devices to be used with a single tester, thereby reducing manufacturing costs.

[0070] The spring contacts 406 are connected to an interface connector 416 adapted to mate with a tester connector 418 located on the surface of the tester 412. The tester connector 418, in turn, may be wired to a PCB connector 422. The PCB connector 422 connects to a PCB 424 that performs the waveform testing and analysis. Utilizing a removable connection at the PCB enables an operator to remove the PCB 424 from the tester 412 for testing and servicing. Alternatively, a non-removable PCB may be utilized and the tester may be itself tested or updated via a USB port, a network connection, etc. The configuration depicted in FIG. 6B allows different types of stun devices to be tested on the same tester, but the tester of the present technology could also be manufactured with a dedicated built-in interface configured for a single type of stun device. Other types of interfaces are also contemplated to test stun devices and stun guns that deliver electric waveforms utilizing launched projectiles. Since launched projectiles typically utilize barbs to secure to a target, interfaces that utilize compliant or perforated materials that may be penetrated by barbs are contemplated. Such interfaces may utilize screens manufactured of conductive materials, conductive rubbers or plastics, etc.

[0071] Returning to FIG. 6A, the depicted testing apparatus 300 may include a display screen 338, that allows a user to view waveforms WE of the stun device SD discharge or other information. In certain embodiments, discharge periods for analysis can range from 1 to 45 seconds, simulating conditions of contact in the field during actual use. Such a signal capture feature P could be included along with other specific modes of signal capture and analysis for stun devices, and certain data regarding the discharge or the tester itself may be displayed for the operator on a second data display screen 338a. The displayed information may be used to aid an operator of the tester in making a determination regarding the operation of the stun device SD being tested, or regarding the operation of the tester 302 itself In certain embodiments, however, the potentially subjective decision-making process of a human operator is bypassed in favor of a decision made by the tester 302 or an associated computer regarding the suitability of operation of a stun device SD. In such a case, one or both of the data display screens 338, 338a may be omitted from the tester 302 or reconfigured to display a status result (e.g., "OK to Use," "DO NOT USE," etc.).

[0072] Another feature that may be incorporated in the stun device testing apparatus 300 is the capability to measure current leakage and/or electrical breakdown from the stun device SD itself An electrical cable/lead 340 extending from the tester housing 342 may be attached to the stun device SD to measure leakage by the apparatus 300. Information regarding the leakage may be displayed to a user via a leakage display 344 or one of the other display screens 338, 338a on the tester 302. Leakage or breakdown is dependent, in part, on the location and area of the contact providing the leakage or breakdown path, and is important to the operator of the tester 302, to prevent the operator from being incapacitated by the discharge during testing. Also, leakage can indicate a malfunction of the stun device SD. Again, not all information regarding leakage or breakdown need be presented to an operator. In such a case, the leakage display 344 may be omitted from the tester 302, and the tester 302 or the associated computer may make the necessary determinations regarding the safe operation of the stun device SD. In one embodiment, the type of leads utilized for EKG analysis of defibrillators and pacemakers may be employed to measure leakage. The apparatus 300 may also provide waveform analysis for a number of load conditions to simulate contact with differing parts of the body with differing intrinsic resistance and capacitance characteristics. Under such conditions, the internal circuitry of the stun device SD can behave in a consistent fashion to conserve the waveform for the purposes described previously.

[0073] The stun device testing apparatus 300 may also feature output from stun devices as compared against a variety of known and accepted electrical safety standards for electrical devices and for biomedical devices specifically. The apparatus 300 may incorporate one or more comparison outputs 346a, 346b, each offering a visual display or other representation of acceptable comparison and verification by the user. The testing apparatus 300 also may record individual waveforms and detailed time and date information of the tested device, and compare that information with standards based on the manufacturers' specifications, previously recorded discharge characteristics of the specific device, standards of other known devices, etc.

[0074] FIG. 6C depicts a partial perspective view of an interior portion of a housing 452 for a stun device testing apparatus 450 in accordance with one embodiment of the technology. Notably, the housing 452 includes an opening for receiving an airflow from the exterior of the housing 452. The airflow is drawn into the housing 452 by a fan 454. An environmental module 456, which may include at least one of a temperature sensor, a barometric pressure sensor, and a humidity sensor, or combinations thereof, is disposed downstream of the fan 454, such that the airflow is directed over the environmental module 456. In certain embodiments of the various testers described herein, it may be advantageous to detect and record ambient environmental conditions, which can have an effect on the testing protocols and/or test results. By locating the environmental module 456 downstream of the fan 454, the ambient temperature and humidity, for example, may be detected without the reading being detrimentally effected by heat and temperature variations due to components within the housing 452. The environmental module 456 is mounted on a header which spaces the environmental module 456 off the mainboard and into the airstream of the fan 454. This helps ensure that outside temperature, not inside temperature, is read.

[0075] FIG. 7A is a schematic diagram of a hardware configuration of a stun device testing apparatus 500 in accordance with an embodiment of the technology. A device under test (DUT) 502 (i.e., an electric waveform delivery device) is connected to a load 504, which accomplishes at least two goals: 1) a well-known voltage and current waveform can be produced by the use of Ohm's law (Voltage=Current.times.Resistance), and 2) the high voltage signal level from the DUT 502 will be reduced to a level that is not damaging to the analysis circuitry contained within the testing apparatus 500. In one embodiment, a network of resistive devices may be utilized, e.g., the resistive values of an exemplary network may be 100, 250, 500 and 1000 ohm. Each different resistive value may be attached to a computer-controlled relay that may be either mechanical or electrical, depending on the anticipated energy level of the discharge impulse. The resistor and relay network is designed such that they are not mutually exclusive, thereby allowing a wide range of restive values with minimal impact on device size and cost.

[0076] The load 504 is connected to a current monitor 506, which outputs a voltage that is proportional to the current through the load 504. The voltage output of the current monitor 506 is then input to the printed circuit board (PCB) 508. The input signal is first conditioned 510 to match the input requirements of the digitizer (an analog to digital converter, A/D) 512. This conditioning includes several specific functions, including input filtering, digital attenuation, high-gain operational amplification (op-amp), and conversion operational amplification. Input filtering limits the noise bandwidth at the input to the A/D. Digital attenuation combines with the gain from the following stage (high gain operational amplification) to match the input signal level to the full-scale level of the A/D. In one embodiment, this attenuator has a range from about 1.0 dB to about 16 dB, which may be set via commands to a processor 514 or through the use of an on-board switch. The high-gain op-amp circuit is designed for a voltage gain of about ten. Coupled with the input attenuator, the output of this amplifier can be typically in a range of about 0-2V nominally. Finally, a single ended-to-differential conversion op-amp converts the signal into differential format and has an added level shift, since the original signal is DC-coupled.

[0077] In one embodiment, the AID 512 operates at 100 MS/s (million samples per second) with a resolution of 16 bits. This configuration provides the user with the ability to "see" the waveform in 10 nanosecond steps in time, with a total of 65,536 steps in discharge intensity. The output of the A/D 512 is passed directly to the processor 514 (which, in certain embodiments, may be a field programmable gate array (FPGA)), using low-voltage differential signaling (LVDS). FIG. 9A depicts one embodiment of a circuit 630 utilized in the hardware configuration of FIG. 7A for load 504, the current monitor 506, the signal conditioner 510, and the AID 512.

[0078] Returning to the hardware embodiment depicted in FIG. 7A, the FPGA 514 may be manufactured by Xilinx, Inc. FPGAs allow for a wide range of data manipulation techniques while being field re-definable for future product upgrades, features, enhancement, etc. Use of an FPGA 514 provides the option of elimination of external computer control (provided sufficient processing capability is present) of the testing apparatus 500. In that case, the FPGA can perform all of the data analysis internally, handle user display functions, etc. If an external computer is utilized, however, the FPGA may be utilized only for ancillary functions, such as data handling and communications scheduling. VHDL code can be utilized to accept data from the AID 512 continuously while being stored in an internal or external memory array. Additionally, the FPGA 514 can accept commands to stop/start a test, capture data, switch resistive loads, etc. The FPGA 514 also handles all USB 516 communications from the computer running the graphical user interface. In certain embodiments, the communications interface may be defined by the USB 2.0 standard, which is robust, familiar, and readily available in most consumer-based computing electronics.

[0079] FIG. 7B depicts an exemplary embodiment of a FPGA 514 utilized in certain embodiments of the technology. The A/D 512 delivers output to an input memory device 520 that, in the depicted embodiment, is a first in/first out (FIFO) memory to compensate for the differing clock speeds between the A/D clock and the USB clock 526, described below. Output from the input memory device 520 is delivered to both a storage device 522 as well as a peak detection device 524. The storage device 522 is also a FIFO and is described in more detail below, in conjunction with other related elements. The peak detection device 524 determines when the waveform discharged from the DUT 502 reaches a peak signal, initiating storage of the waveform information. This data is in turn output to the USB memory device 526, USB interface 528, and USB clock 530. In certain embodiments, the USB memory device 5256 may be a FIFO. The USB interface 528 changes the clock domain to the USB standard clock frequency, which is necessary to avoid loss of data for data sampled at high rates. For example, certain embodiments of the tester may sample data at 105 MHz, significantly faster than the USB clock.

[0080] Storage device 522 and USB memory device 526 provide memory space for storing data samples received from the A/D 512. In one embodiment, the storage of the incoming data samples is triggered when the peak detection circuit 524 detects a peak in the incoming waveform. Each sample may represent a fixed amount of capture time, for example, 10 nanoseconds (ns). Because the storage device 522 and USD memory device 526 contain a finite amount of storage space, the size of the storage device 522 and USD memory device 526 sets an upper limit on the total time a waveform may be captured. For example, if the storage device 522 and USD memory device 526 store 100 data samples, the total time is 100.times.10 ns=1 microsecond (.mu.s). In one embodiment, the storage device 522 and USD memory device 526 store 64,000 samples, providing 640 .mu.s of total data capture time. Also stored in the FPGA 514 are a number of registers 532 that control operation of the apparatus. These include peak detection registers 532a that control the capture of waveform data associated with the peak, and load control registers 532b that determine the testing load based, at least in part, on the type (i.e., manufacturer, model, etc.) of the DUT 502. Additionally, reset/start registers 532c control when data is taken, when the device is reset, when data capture stops, etc. In one embodiment, the FPGA 514 is able to be re-programmed via the USB interface 528.

[0081] The testing apparatus disclosed herein may be a stand-alone apparatus requiring no connection to a computer. In that case, the processor may run all the necessary analysis and present the required data/info via a screen or other components. In embodiments of the apparatus 500 that include an external computer 518, a LABVIEW.TM.-based graphical user interface (GUI) may be utilized. LABVIEW software is available from National Instruments Corporation, of Austin, Tex. Other types of software that may be utilized include Mathematica and MatLab. The LABVIEW-based programming may be compiled as an .exe executable file, allowing operation on any Windows-based PC (or Intel-based Macs). If desired, the data displayed to the user may be a subset of the total data analyzed, such that the user is not confused by an overload of details or provided unnecessary information to perform his job. The apparatus may provide the option of delivering more information to the user for more advanced purposes.

[0082] During use, when the user selects the stun device to be tested, the program automatically switches to the correct load resistance for that stun device. The user may scan the stun device barcode or enter the stun device serial number, thus initiating a program to look up the appropriate load resistance, which may be stored locally or over a remote network. Raw data may be imported from the memory array into the program for analysis. While any waveform characteristics may be analyzed, capture and analysis of energy delivered, pulse duration, peak current, and frequency, are desirable for most stun devices. The resultant data may then be compared to known values for the particular device, and the testing apparatus may provide a pass/fail indication to the operator. The waveform and any desired data can be displayed on the user interface. LABVIEW supports saving data locally in a specified location and format, but it may also be desirable to upload the data to an internet database.

[0083] In various embodiments of the GUI, a drop down menu may be utilized for the operator to select which stun device is to be tested, or the stun device barcode may be scanned, as described above. The GUI also may utilize areas for data entry, such as serial number, customer name, test operator, etc. A pass or fail indication will illuminate after the data has been analyzed. The waveform may be displayed along with some calculated data such as frequency, peak current, etc., if desired. If available, the stun device manufacturer's expected waveform can be displayed next to the tested device waveform for a visual pass/fail confirmation. A data print out option may be available for printers connected to the computer 518.

[0084] As described above with regard to the embodiment of the tester 102 depicted in FIG. 4A, multiple ports are utilized on certain embodiments of the stun device tester. The multiple ports may be used to determine an electrical terminal model of the stun device. A terminal model is a conceptual embodiment of a mathematical equation that relates the voltage and current at a terminal pair or port of an electrical circuit. In general, a complex electrical network can be divided into a source and a destination connected by a pair of wires (otherwise known as a port). The source, destination, and even the wires themselves are conceptual. Connecting the source and destination ports constrains the voltage across the wires and the current through the wires to be equal. In mathematics, this is equivalent to solving two equations for two unknown quantities. Consider an example where the source is a stun device that can develop 10,000 volts and a target of approximately 50 ohms resistance. The current developed into the target determines the magnitude of the electric field within the target's body. Assuming the stun device has a very low source resistance, then the prediction might be 10,000 volts/50 ohms=200 amp current. If the assumption is that the resistance of the stun device is 1,000,000 ohms then the current is 10,000 volts/1,000,000 ohms=0.01 amps. Both are assumptions. Accordingly, it is desirable to know the current. Based on testing performed, observed currents in the range of 1 to 10 amps suggest source resistances of 1000 to 10,000 ohms. Determination of an electrical terminal model utilizing multiple ports of the exemplary tester depicted in FIG. 4A is described below.

[0085] FIG. 8A is a schematic block diagram of a hardware configuration of a stun device testing apparatus 600 in accordance with another embodiment of the technology. A device under test 602 (e.g., a stun device) is connected to a resistor pack 604 through spring contacts as described herein. The spring contacts help ensure connection by engaging the device under test 602 prior to the device under test 602 being fully seated in a receptacle that receives the device under test 602. The resistor pack 604 presents a minimum load of 1000 ohms regardless of whether the tester 600 is powered or unpowered. Presentation of a minimum (or default) resistance load is a safety feature that prevents inadvertent damage to the tester 600 and/or injury to a user, should the device under test 602 be discharged into an unpowered unit. The load can be changed depending on the protocol being used to test the device under test 602, as controlled by the single board computer 606 (SBC). The output of the resistor pack 604 is a voltage reduction of about 100:1, but other voltage reductions may be utilized. The resistors located within the resistor load pack 604 are calibrated, which allows the tester 600 to calculate voltage and current discharged from the device under test 602 accurately.

[0086] A signal conditioner 608 is used to filter a discharge waveform as well as apply different gains depending on the device under test 602. The discharge-receiving circuit disposed in the signal conditioner may be high-voltage protected as an additional safety feature. A digitizer 610 samples and stores 64 million 12-bit samples. In one embodiment, the sampling rate is 10M/second. Thus, 6.4 seconds worth of data is collected. Other sampling rates may be utilized. In this embodiment, the SBC 606 is not utilized in any real-time data collection, thus reducing or eliminating the possibility of missing data due to software issues. The SBC 606 retrieves the data from the digitizer 610 and applies gain and offset corrections (which are programmed into the digitizer 610) prior to data analysis. The data analysis, as well as the raw data, may be compressed and/or stored on the SBC 606 until a data package is transmitted to a designated remote storage (for example, a computer, remote database, etc.). This data may be transmitted via a wireless module 612 or by a cabled connection. Once stored remotely, the raw data can be deleted from the tester 600 to conserve memory.

[0087] FIG. 8B depicts functions performed by the hardware configuration of FIG. 8A. A stun device testing apparatus 620 utilizes digital processing in the digitizer 610 that includes a complex programmable logic device 622 (CPLD). The CPLD 622 may perform one or more of the following functions. The CPLD 622 may control operation of the A/D converter 624, as well as signal conditioning circuitry gain from the signal conditioner 608. Additionally, the CPLD 622 may control operation of the resistor pack relays in the resistor load pack 604. If a USB chip is utilized, the CPLD 622 may control the interface 626 to the USB chip. Data flow between the AID converter 624 and the SDRAM 628 may also be routed through and otherwise controlled by the CPLD 622. Data flow between the SDRAM 622 and the USB chip, via the USB interface 626, may be similarly routed and controlled. Additionally, the CPLD 622 may determine when data storage to the SDRAM 628 will begin, and the CPLD 622 may deliver a predefined test pattern to the SDRAM 628 to be used as built-in test equipment. In a particular embodiment, when initiated by the SBC 606 over the USB interface 626, the CPLD 622 monitors the incoming data from the A/D converter 624. When the data exceeds an absolute value as defined by the test protocol, the CPLD 622 then directs data to the SDRAM 628 until a full 6.4 seconds worth of data is captured. This data is then sent to the USB chip for use by the SBC 606.

[0088] FIG. 9B is a schematic diagram of a circuit 650 utilized in a stun device testing system in accordance with one embodiment of the technology. The depicted circuit 650 receives and processes waveforms delivered from a multi-port testing apparatus, such as that depicted in FIG. 4A, but components of the circuit 650 may also be used in other circuits and testing apparatus described herein. The testing procedures described below may also be utilized in various embodiments of the testing system described herein. Components include a LABJACK digital I/O, a Cleverscope C328A Digital Oscilloscope, an Avertec laptop computer, an HP Laserjet printer, a Zvetco finger print reader, a PhidgetUSA RFID reader, and a Belkin USB hub. All of these components are commercially available and communicate via a USB connection. Discrete electronics are limited primarily to driving LEDs and resistor-capacitor networks that match the signal received in the ports to the requirements of the digital oscilloscope. This latter requirement is further minimized by the digital oscilloscope's ability to detect and adjust itself to the presented signal. These components require no direct observation or contact by the user, although certain embodiments of the device may include options for such direct, contemporaneous observation. The digital oscilloscope operates as a data acquisition device which is observed and controlled by the connected personal computer. The LABJACK interface can generate control signals for the LEDs that guide the user during operation, as described above. The apparatus can also sense contact closures to allow simple signaling from the user, to sense proper positioning of the stun device in the ports, etc. Two modes of operation may be used, one high-speed sampling mode to capture spikes, transients and normal waveform, and a second to assess temporal patterns upon stimulus triggers of about 10 msec pulse, which is sampled and stored as a waveform. All data from a Liven test is then exported to a computer where detailed comparisons with stored and archival data can be made using appropriate software. Exemplary software can include statistical analysis software programs, such as SYSTAT.TM., manufactured by Systat Software, Inc., of Chicago, Ill. or MATLAB.TM., manufactured by The MathWorks, Inc., of Natick, Mass. Other component manufacturers may provide components utilized in the manufacture of the testing device. The above description does not limit similar configurations using different components.

[0089] Virtually any characteristics of the electric discharge may be measured, recorded, and analyzed by the device. While the most accurate testers may measure, record, and analyze a significant amount data regarding a waveform, more limited analysis of the waveform may be possible based on a smaller number of characteristics. In addition to capturing an image of the waveform, additional data regarding the discharge may also be collected. Certain embodiments of testing devices may test for one or more of an amplitude, a duration, a current, a voltage, an energy, or a temperature associated with the discharge. Additionally, other data may include: 1) joules per pulse, 2) total joules, 3) peak, average current for at least two different loads, 4) open-circuit voltage, 5) features of spark gap variability, etc. Waveform anomalies to be captured may include: 1) fast spikes, amplitude, rise-fall time, 2) differences in waveforms, rms, peak-to-peak, peak difference, 3) rate 5 to 60 pps, 4) variation in rate, 5) burst rate (patterned bursts), 6) duration of stimulus delivery, 7) measured battery voltage and predicted number of discharges based on battery voltage, 8) temperature of measurement log, etc.