Access Device And Phase Change Memory Combination Structure In Backend Of Line (beol)

BRUCE; ROBERT ; et al.

U.S. patent application number 16/227065 was filed with the patent office on 2019-04-25 for access device and phase change memory combination structure in backend of line (beol). This patent application is currently assigned to International Business Machines Corporation. The applicant listed for this patent is International Business Machines Corporation. Invention is credited to ROBERT BRUCE, Fabio Carta, Gloria WingYun Fraczak, Hiroyuki Miyazoe, Kumar R. Virwani.

| Application Number | 20190123100 16/227065 |

| Document ID | / |

| Family ID | 66096641 |

| Filed Date | 2019-04-25 |

View All Diagrams

| United States Patent Application | 20190123100 |

| Kind Code | A1 |

| BRUCE; ROBERT ; et al. | April 25, 2019 |

ACCESS DEVICE AND PHASE CHANGE MEMORY COMBINATION STRUCTURE IN BACKEND OF LINE (BEOL)

Abstract

A combined semiconductor device is fabricated by forming a first access structure from a mixed ionic electronic conduction (MIEC) material. A first side of a first memory structure is electrically coupled with a first side of the first access structure to form the combination device. A subtractive etching process is applied to the combination device such that a surface of the combination device that is substantially orthogonal to a plane of a substrate of the semiconductor device is within a defined tapering tolerance.

| Inventors: | BRUCE; ROBERT; (White Plains, NY) ; Carta; Fabio; (Yorktown Heights, NY) ; Fraczak; Gloria WingYun; (Queens, NY) ; Miyazoe; Hiroyuki; (White Plains, NY) ; Virwani; Kumar R.; (Santa Clara, CA) | ||||||||||

| Applicant: |

|

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Assignee: | International Business Machines

Corporation Armonk NY |

||||||||||

| Family ID: | 66096641 | ||||||||||

| Appl. No.: | 16/227065 | ||||||||||

| Filed: | December 20, 2018 |

Related U.S. Patent Documents

| Application Number | Filing Date | Patent Number | ||

|---|---|---|---|---|

| 15784343 | Oct 16, 2017 | |||

| 16227065 | ||||

| Current U.S. Class: | 1/1 |

| Current CPC Class: | H01L 27/2418 20130101; H01L 45/085 20130101; H01L 45/1233 20130101; H01L 27/2409 20130101; H01L 45/06 20130101; H01L 45/1253 20130101; H01L 45/1683 20130101; H01L 45/1675 20130101; H01L 27/2481 20130101 |

| International Class: | H01L 27/24 20060101 H01L027/24; H01L 45/00 20060101 H01L045/00 |

Claims

1. A method comprising: forming, using a semiconductor fabrication system, a first access structure from a mixed ionic electronic conduction (MIEC) material; electrically coupling a first side of a first memory structure with a first side of the first access structure to form a combination device; and applying a subtractive etching process is applied to the combination device such that a surface of the combination device that is substantially orthogonal to a plane of a substrate of the semiconductor device is within a defined tapering tolerance.

2. The method of claim 1, wherein the subtractive etching process is a single step in the fabrication process.

3. The method of claim 1, further comprising: electrically coupling a first electrode with a second side of the first access structure; and electrically coupling a second electrode with a second side of the first memory structure.

4. The method of claim 1, further comprising: forming a pore in a dielectric material over the first access structure; and filling a Phase-Change memory (PCM) material in the pore to form the first memory structure, wherein the pore is configured to enable an electrical coupling between the first memory structure and the first access structure.

5. The method of claim 1, further comprising: forming a pore in a dielectric material over the first access structure; filling an electrode material in the pore to form an electrode, wherein the pore is configured to enable an electrical coupling between a first end of the electrode and the first access structure, and wherein the first memory structure is formed such that the first surface of the first memory structure is in an electrical coupling with a second end of the electrode.

6. The method of claim 1, further comprising: forming a second access structure from the MIEC material stacked on a second side of the memory structure, wherein the second side of the first memory structure is electrically coupled with a second side of the second access structure; and electrically coupling a first side of a second memory structure with a first side of the second access structure.

7. The method of claim 1, further comprising: electrically coupling a first electrode with a second side of the first access structure; and electrically coupling a second electrode with a second side of the second memory structure.

8. A semiconductor fabrication system comprising a processor, a computer-readable memory, and a computer-readable storage device, and program instructions stored on the storage device for execution by the processors via the memories, the stored program instructions causing the fabrication system to perform operations comprising: forming a first access structure from a mixed ionic electronic conduction (MIEC) material; electrically coupling a first side of a first memory structure with a first side of the first access structure to form a combination device; and applying a subtractive etching process is applied to the combination device such that a surface of the combination device that is substantially orthogonal to a plane of a substrate of the semiconductor device is within a defined tapering tolerance.

9. The semiconductor fabrication system of claim 8, wherein the subtractive etching process is a single step in the fabrication process.

10. The semiconductor fabrication system of claim 8, further comprising: electrically coupling a first electrode with a second side of the first access structure; and electrically coupling a second electrode with a second side of the first memory structure.

11. The semiconductor fabrication system of claim 8, further comprising: forming a pore in a dielectric material over the first access structure; and filling a Phase-Change memory (PCM) material in the pore to form the first memory structure, wherein the pore is configured to enable an electrical coupling between the first memory structure and the first access structure.

12. The semiconductor fabrication system of claim 8, further comprising: forming a pore in a dielectric material over the first access structure; filling an electrode material in the pore to form an electrode, wherein the pore is configured to enable an electrical coupling between a first end of the electrode and the first access structure, and wherein the first memory structure is formed such that the first surface of the first memory structure is in an electrical coupling with a second end of the electrode.

13. The semiconductor fabrication system of claim 8, further comprising: forming a second access structure from the MIEC material stacked on a second side of the memory structure, wherein the second side of the first memory structure is electrically coupled with a second side of the second access structure; and electrically coupling a first side of a second memory structure with a first side of the second access structure.

Description

TECHNICAL FIELD

[0001] The present invention relates generally to a method, system, and computer program product for fabricating compute-in-memory capable semiconductor devices. More particularly, the present invention relates to a method, system, and computer program product for access device and phase-change memory combination structure.

BACKGROUND

[0002] Within the scope of the illustrative embodiments--

[0003] (a) A Memory Element: Refers to an element that is used to store data/information. Many options exist here (including, for example, phase change memory (PCM), MRAM, Resistive RAM, solid electrolyte memory, FeRAM, etc.), with one promising memory node material being PCM.

[0004] (b) A Rectifying Element or Access Device (AD): Since a transistor is not provided at every crosspoint, a device is needed to rectify (exhibit nonlinearity). This ensures that the memory cells that lie on unselected wordlines and bitlines are not inadvertently programmed or shorted to each other and do not leak any significant amount of current.

[0005] A variety of diodes can be used for rectification. The illustrative embodiments recognize that the quality of the diodes that can be fabricated in middle-of-line (MOL) or back end of line (BEOL) lower temperature processes are typically unacceptable because they have to be made in amorphous or polycrystalline silicon that has much lower mobility. These considerations prevent the use of p-n junctions in either single-crystal silicon or other silicon materials as rectifiers for certain memory elements.

[0006] The von Neumann bottleneck is a limitation on throughput caused by the standard personal computer architecture--the stored program computer--which is also known as the von Neumann architecture. In the von Neumann architecture, programs and data are held in memory, the processor and memory are separate and data moves between the two resulting in latency. The improvements in data processing circuits have made data processing faster, whereas the improvements in memory elements have focused on making memories denser rather than faster. In that configuration, latency is a prevalent problem, as is the increasing idle time for data processing circuits awaiting data from the memory elements. These problems are referred to as the limitations of von Neumann architecture.

[0007] New memory and access device combinations are being explored to overcome the limitations of von Neumann architecture. One of the potential candidates proposed by the illustrative embodiments to enable native neuromorphic computing (NNC) that includes a combination of phase change memory and an access device fabricated together as a semiconductor device unit. The illustrative embodiments recognize that such a combination device could enable compute-in-memory operations critical for native neuromorphic computing.

SUMMARY

[0008] The illustrative embodiments provide a method, system, and computer program product. An embodiment provides a semiconductor device that includes a first access structure formed from a mixed ionic electronic conduction (MIEC) material. The device further includes a first side of a first memory structure electrically coupled with a first side of the first access structure to form a combination device, wherein a subtractive etching process is applied to the combination device such that a surface of the combination device that is substantially orthogonal to a plane of a substrate of the semiconductor device is within a defined tapering tolerance.

[0009] An embodiment includes a method of fabricating the semiconductor device.

[0010] An embodiment includes a fabrication system to fabricate the semiconductor device. The system includes one or more processors, one or more computer-readable memories, and one or more computer-readable storage devices, and program instructions stored on at least one of the one or more storage devices for execution by at least one of the one or more processors via at least one of the one or more memories.

BRIEF DESCRIPTION OF THE DRAWINGS

[0011] The novel features believed characteristic of the invention are set forth in the appended claims. The invention itself, however, as well as a preferred mode of use, further objectives and advantages thereof, will best be understood by reference to the following detailed description of the illustrative embodiments when read in conjunction with the accompanying drawings, wherein:

[0012] FIG. 1 depicts an example simple compute-in-memory circuit that is achieved by a combined structure according to an illustrative embodiment;

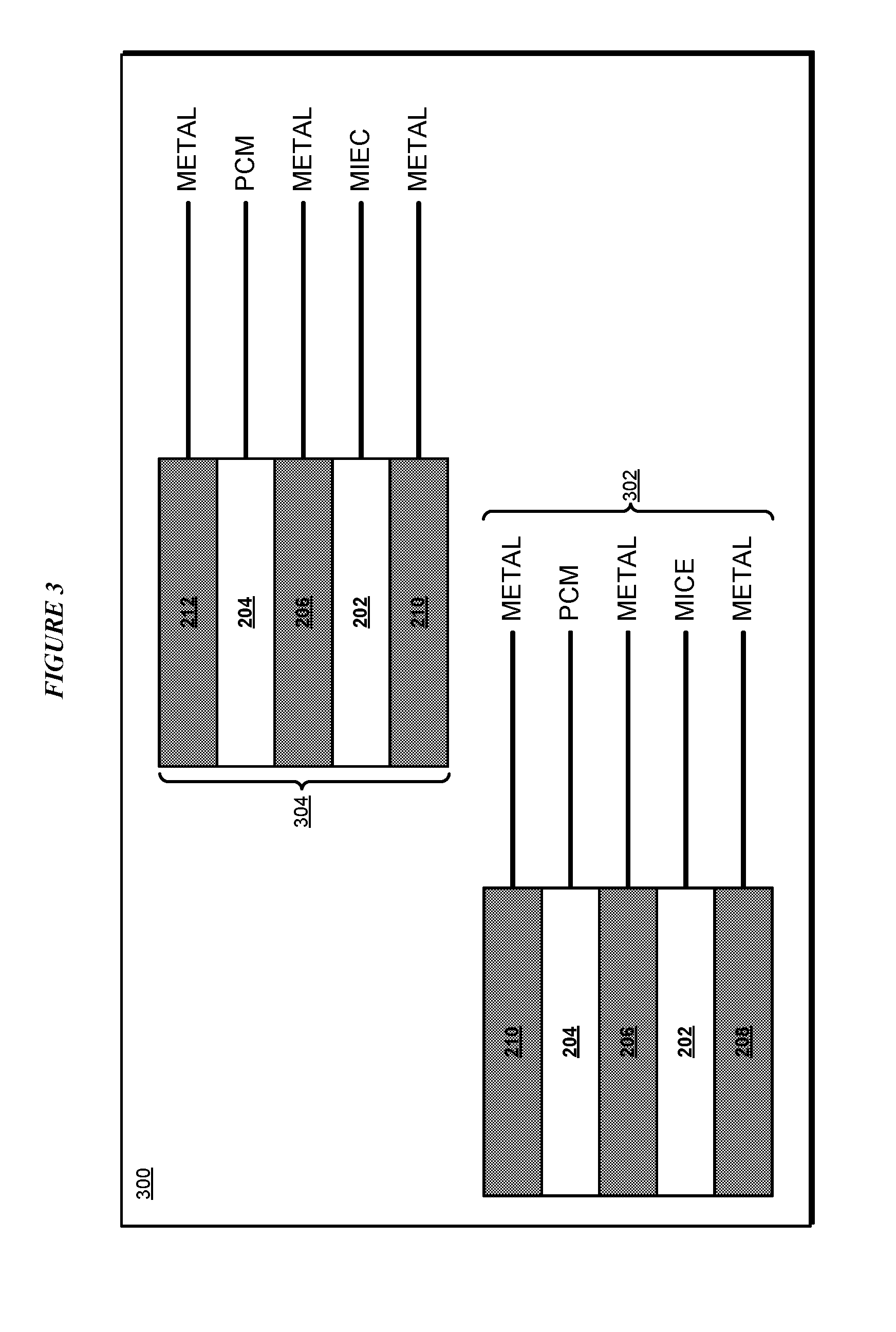

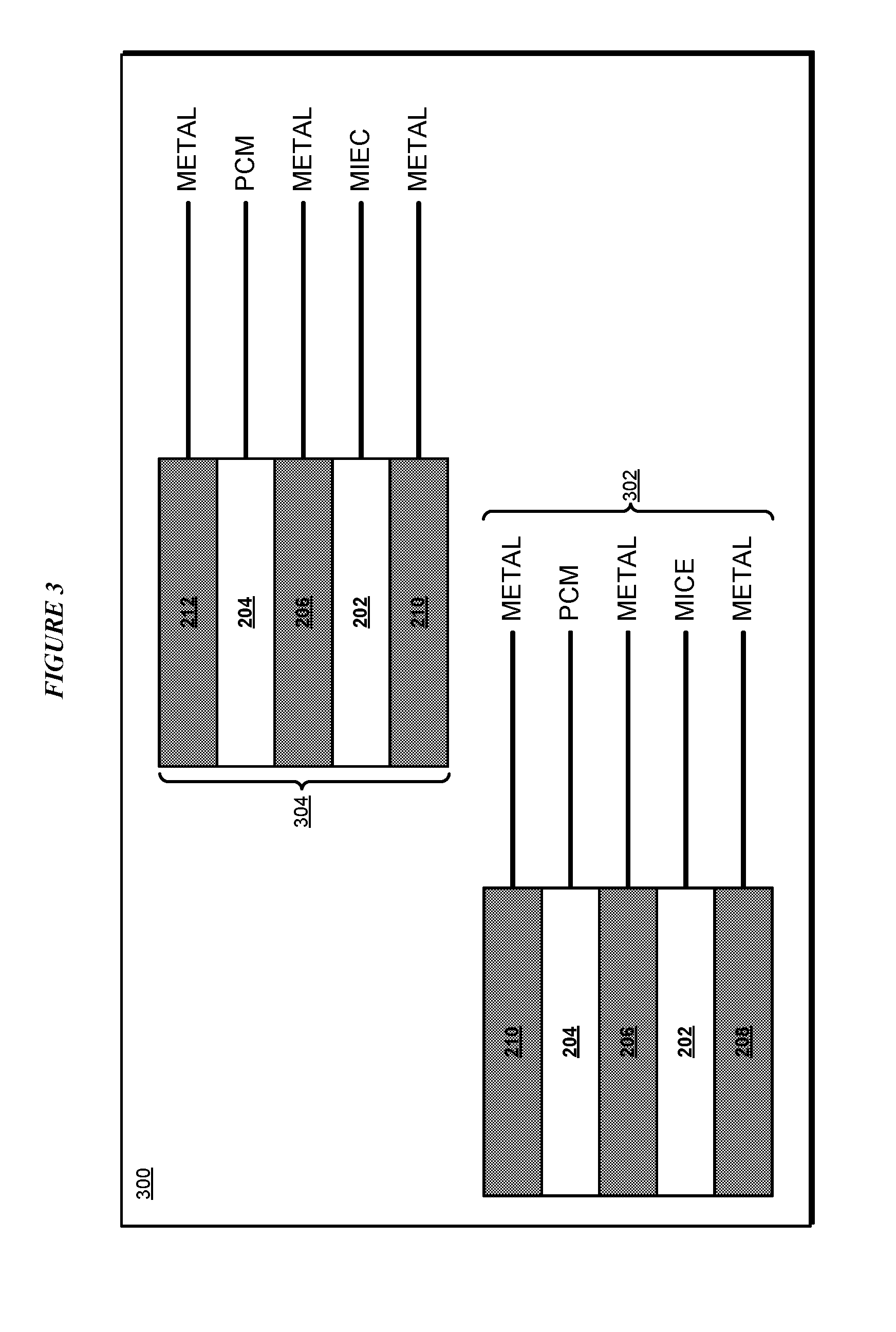

[0013] FIG. 2 depicts one example configuration in which two combined structures are stacked, each combining a memory and an AD structures in accordance with an illustrative embodiment;

[0014] FIG. 3 depicts one example configuration in which two combined structures are fabricated separately in the same process, each combining a memory and an AD structures in accordance with an illustrative embodiment;

[0015] FIG. 4 depicts a view of the combined structure resulting from one variation of a subtractive etching process of fabrication where the etching is performed without spacers in accordance with an illustrative embodiment;

[0016] FIG. 5 depicts a view of the combined structure resulting from another variation of a subtractive etching process of fabrication where the etching uses spacers in accordance with an illustrative embodiment;

[0017] FIG. 6 depicts a view of the combined structure resulting from a pore filling process of fabrication in accordance with an illustrative embodiment;

[0018] FIG. 7 depicts a view of the combined structure resulting from a mushroom process of fabrication in accordance with an illustrative embodiment;

[0019] FIG. 8 depicts an example series of steps in a subtractive etching process according to an illustrative embodiment;

[0020] FIG. 9 depicts another example series of steps in a subtractive etching process according to an illustrative embodiment;

[0021] FIG. 10 depicts an example series of steps in a subtractive etching process according to an illustrative embodiment;

[0022] FIG. 11 depicts another example series of steps in a subtractive etching process according to an illustrative embodiment;

[0023] FIG. 12 depicts an example series of steps in a PCM-pore filling process according to an illustrative embodiment;

[0024] FIG. 13 depicts a continuation of process 1200 in accordance with an illustrative embodiment;

[0025] FIG. 14 depicts a continuation of process 1200 in accordance with an illustrative embodiment;

[0026] FIG. 15 depicts an example series of steps in a PCM mushroom process according to an illustrative embodiment;

[0027] FIG. 16 depicts a continuation of process 1500 in accordance with an illustrative embodiment;

[0028] FIG. 17 depicts a continuation of process 1500 in accordance with an illustrative embodiment; and

[0029] FIG. 18 depicts a continuation of process 1500 in accordance with an illustrative embodiment.

DETAILED DESCRIPTION

[0030] The illustrative embodiments recognize that patterning of a memory element and an AD element in a single patterning process is a difficult problem to solve. Such a patterning process is one of the critical enabling technologies for NNC. Therefore, a need exists for a fabricating process to fabricate a combined memory and AD device.

[0031] The illustrative embodiments further recognize that in the case of PCM, the SET operation is gradual but the RESET operation is abrupt thus each device node for NNC requires not one but two (memory+AD) combination structures. Therefore, an ability to pattern memory (e.g. a PCM device) and AD (e.g., a mixed ionic and electronic conduction (MIEC) device) structure together in a single etch process has distinct advantages. Therefore, a need exists for a fabricating process to fabricate two or more combined memory and AD devices simultaneously in a single fabrication process.

[0032] The illustrative embodiments used to describe the invention generally address and solve the above-described needs and other problems related to fabricating an access device and phase-change memory combination structure. The illustrative embodiments provide a fabrication method for access device and phase-change memory combination structure.

[0033] An embodiment comprises a semiconductor device described herein. Another embodiment comprises a fabrication process for the contemplated semiconductor device and can be implemented as a software application. The software application implementing an embodiment can be configured as a modification of an existing semiconductor fabrication system--such as a photolithography system, as a separate application that operates in conjunction with an existing semiconductor fabrication system, a standalone application, or some combination thereof. For example, the application causes the semiconductor fabrication system to perform the steps described herein, to fabricate an access device and phase-change memory combination structure, as described herein.

[0034] For the clarity of the description, and without implying any limitation thereto, the illustrative embodiments are described using a specific type of memory element (PCM) and a specific type of AD element (MIEC). Within the scope of the illustrative embodiments, an embodiment can be implemented with a variety of similarly purposed elements, where such elements pose similar fabrication problems as are recognized with PCM and MIEC.

[0035] Furthermore, simplified diagrams of the example structures, elements, and device(s) are used in the figures and the illustrative embodiments. In an actual fabrication of a proposed device, additional structures that are not shown or described herein, or structures different from those shown and described herein, may be present without departing the scope of the illustrative embodiments. Similarly, within the scope of the illustrative embodiments, a shown or described structure in the example device may be fabricated differently to yield a similar operation or result as described herein.

[0036] Differently shaded portions in the two-dimensional drawing of the example structures, layers, and formations are intended to represent different structures, layers, and formations in the example fabrication, as described herein. The different structures, layers, and formations may be fabricated using suitable materials that are known to those of ordinary skill in the art as belonging to the same class of materials described herein.

[0037] A specific shape, location, position, or dimension of a shape depicted herein is not intended to be limiting on the illustrative embodiments unless such a characteristic is expressly described as a feature of an embodiment. The shape, location, position, dimension, or some combination thereof, are chosen only for the clarity of the drawings and the description and may have been exaggerated, minimized, or otherwise changed from actual shape, location, position, or dimension that might be used in actual photolithography to achieve an objective according to the illustrative embodiments.

[0038] Furthermore, the illustrative embodiments are described with respect to a specific actual or hypothetical semiconductor device only as an example. The steps described by the various illustrative embodiments can be adapted for fabricating a variety of planar and non-planar devices in a similar manner, and such adaptations are contemplated within the scope of the illustrative embodiments. The specific electrodes placements are also used only as non-limiting examples to describe certain options possible with the illustrative embodiments. Those of ordinary skill in the art will be able to use an embodiment to similarly provide electrical access to a layer or structure in a similar manner, and such usage is also contemplated within the scope of the illustrative embodiments.

[0039] An embodiment when implemented in an application causes a fabrication process to perform certain steps as described herein. The steps of the fabrication process are depicted in the several figures. Not all steps may be necessary in a particular fabrication process. Some fabrication processes may implement the steps in different order, combine certain steps, remove or replace certain steps, or perform some combination of these and other manipulations of steps, without departing the scope of the illustrative embodiments.

[0040] A device of an embodiment described herein, comprises substantial advancement of the compute-in-memory capability that is needed for the advancement of computing technologies, including but not limited to neuro-morphic computing. A manner of patterning a PCM type memory element and an MIEC type AD element as described herein is unavailable in the presently available methods. Thus, a substantial advancement of such devices or data processing systems by executing a method of an embodiment is in an improved fabrication process for fabricating a combined memory and AD device in a single process step.

[0041] The illustrative embodiments are described with respect to certain types of devices, electrical properties, structures, formations, layers, orientations, directions, steps, operations, planes, materials, dimensions, numerosity, data processing systems, environments, components, and applications only as examples. Any specific manifestations of these and other similar artifacts are not intended to be limiting to the invention. Any suitable manifestation of these and other similar artifacts can be selected within the scope of the illustrative embodiments.

[0042] The illustrative embodiments are described using specific code, designs, architectures, protocols, layouts, schematics, and tools only as examples and are not limiting to the illustrative embodiments. Furthermore, the illustrative embodiments are described in some instances using particular software, tools, and data processing environments only as an example for the clarity of the description. The illustrative embodiments may be used in conjunction with other comparable or similarly purposed structures, systems, applications, or architectures.

[0043] The examples in this disclosure are used only for the clarity of the description and are not limiting to the illustrative embodiments. Additional structures, operations, actions, tasks, activities, and manipulations will be conceivable from this disclosure and the same are contemplated within the scope of the illustrative embodiments.

[0044] Any advantages listed herein are only examples and are not intended to be limiting to the illustrative embodiments. Additional or different advantages may be realized by specific illustrative embodiments. Furthermore, a particular illustrative embodiment may have some, all, or none of the advantages listed above.

[0045] With reference to FIG. 1, this figure depicts an example simple compute-in-memory circuit that is achieved by a combined structure according to an illustrative embodiment. A MIEC AD structure described herein operates as a diode depicted in circuit 100. Memory module Mj is a memory element described with respect to a combined structure of the illustrative embodiments. Mj can be formed using PCM or other type of memory element, e.g., CBRAM.

[0046] The simplified circuit depicted in circuit 100 is not intended to be limiting on the types of combined structures that can be formed using an embodiment. Those of ordinary skill in the art will be able to adapt an example device described herein--which achieves the simple circuit 100 of this figure--to form more complex circuits in a similar manner using the described structure. Such adaptations are contemplated within the scope of the illustrative embodiments.

[0047] With reference to FIG. 2, this figure depicts one example configuration in which two combined structures are stacked, each combining a memory and an AD structures in accordance with an illustrative embodiment.

[0048] A combination of one AD structure, e.g., one MIEC layer 202, and one memory element structure, e.g., one PCM layer 204 forms combined structure 200--a building block --according to an embodiment. Any number of such combinations can be stacked in the manner depicted in FIG. 2.

[0049] A distinctive feature of each combined structure 200 according to the illustrative embodiments is that MIEC layer 202 in any instance of combined structure 200 is substantially non-tapering from the bottom to the top of said layer 202. Stated another way, the sides of layer 202 other than the sides of layer 202 shown contacting metal layers are substantially perpendicular relative to the plane of the contact with the metal layers. Patterning MIEC layers with substantially vertical walls is a difficult problem, and is achieved by a process described herein to fabricate combined structure 200.

[0050] The building block combined structure 200 can include one or more suitable layers or structures intervening between structures 202 and 204 to form an electrically conducting path between structures 202 and 204. Layer 206 is such a layer and is formed by depositing a suitable metal during the fabrication process.

[0051] Similarly, suitable conducting structures or layers may be formed on structures 202 and 204 to allow electrical connectivity to combined structure 200 from an external circuit. Layers 208, 210, and 212 depicted in FIG. 2 are examples of such conducting structures and may be formed by depositing the same or different conducting materials.

[0052] For example, layer 208 may be formed as a bottom electrode coupling to MIEC 202 and layer 210 may be formed as a top electrode coupling with PCM 204. Alternatively, layer 210 may be similar to layer 206 and couple PCM 204 with another instance of MIEC 202. Layer 212 may be formed as the top electrode in such a combination.

[0053] An instance of structure 208, 210, or 212 may be formed on any of the sides of structure 202 that are not facing towards, or otherwise connecting to, a side of structure 204 in a non-stacked configuration. An instance of structure 208, 210, or 212 may be formed on any of the sides of structure 204 that are not facing towards, or otherwise connecting to, a side of structure 202 in a non-stacked configuration.

[0054] With reference to FIG. 3, this figure depicts one example configuration in which two combined structures are fabricated separately in the same process, each combining a memory and an AD structures in accordance with an illustrative embodiment. Each of structures 302 and 304 is similar to one instance of combined structure 200 in FIG. 2. In each of combined structures 302 and 304, structures 202, 204, 206, 208, 210, and 212 are fabricated and operate in a manner similar to the fabrication and operations of similarly numbered structures in FIG. 2.

[0055] For example, layer 208 may be formed as a bottom electrode coupling to MIEC 202 in combination device 302 and layer 210 may be formed as a top electrode coupling with PCM 204 in combination device 302. In device 304, layer 210 may be the bottom electrode of MIEC 202 in combination device 304. Layer 212 may be formed as the top electrode in combination device 304.

[0056] Without implying any limitation thereto, structures 302 and 304 may be fabricated in parallel on the same substrate. One reason to form parallel combined structures of FIG. 3 instead of stacked combined structure of FIG. 2 is to reduce capacitance between the layers of the combined structures. Another reason is to reduce aspect ratio of the pillar to be etched.

[0057] With reference to FIG. 4, this figure depicts a view of the combined structure resulting from one variation of a subtractive etching process of fabrication where the etching is performed without spacers in accordance with an illustrative embodiment. Stacked combination device 400 corresponds to stacked combination device 200 instances depicted in FIG. 2. Parallel combination devices 450 corresponds to combination device 302 and 304 instances depicted in FIG. 3.

[0058] Note that the entire stacked combination device 400 and each parallel combination device in 450 has walls or vertical surfaces that are substantially perpendicular to the plane of substrate 401. These vertical surfaces include vertical surfaces of MIEC layers 402, which are also formed in substantially vertical manner using one form of subtractive etching process according to an embodiment. In this form of subtractive etching, no spacer material is needed as the layers are progressively etched from top metal hard mask (HM) layer 412 up to but not including bottom electrode layer 408.

[0059] In function, form, and materials, layer 402 corresponds to layer 202, layer 404 corresponds to layer 204, layer 406 corresponds to layer 206, layer 408 corresponds to layer 208, layer 410 corresponds to layer 210, and layer 412 corresponds to layer 212. Substrate 401 is of any suitable substrate material, commonly but not necessarily Silicon (Si). Dielectric 403 is any suitable dielectric material, such as including but not limited to silicon oxide (SiO2 or "oxide").

[0060] With reference to FIG. 5, this figure depicts a view of the combined structure resulting from another variation of a subtractive etching process of fabrication where the etching uses spacers in accordance with an illustrative embodiment. Stacked combination device 500 corresponds to stacked combination device 200 instances depicted in FIG. 2. Parallel combination devices 550 corresponds to combination device 302 and 304 instances depicted in FIG. 3.

[0061] Note again that the entire stacked combination device 500 and each parallel combination device in 550 has walls or vertical surfaces that are substantially perpendicular to the plane of substrate 401. These vertical surfaces include vertical surfaces of MIEC layers 402, which are also formed in substantially vertical manner using one form of subtractive etching process according to an embodiment.

[0062] In this form of subtractive etching, spacer 505 material is deposited in a stepped manner as the layers are progressively etched from top metal hard mask (HM) layer 412 up to but not including bottom electrode layer 408. Spacer 505 can be formed using any suitable insulator material known to be used for creating an etching resistant barrier. Additional layers may exist above the metal HM layer 412, e.g., a photo-resist (PR) layer, an anti-reflective coating (ARC), and/or an optical planarizing layer (OPL).

[0063] With reference to FIG. 6, this figure depicts a view of the combined structure resulting from a pore filling process of fabrication in accordance with an illustrative embodiment. Any etching of any layer in combination device 600 or 650 can be performed with or without spacers as described in FIGS. 4 and 5.

[0064] Stacked combination device 600 corresponds to stacked combination device 200 instances depicted in FIG. 2. combination device 650 corresponds to any one of parallel combination devices 302 and 304 depicted in FIG. 3.

[0065] Portion 601 can be formed in a manner of a corresponding portion in FIG. 4 or FIG. 5. For example, the layers in portion 601 can be patterned using a combination of lithography, reactive ion etching (RIE), dielectric filling, and chemical-mechanical planarization (CMP) methods of fabrication.

[0066] With reference to stacked combination devices 600, dielectric 602 is deposited over metal 406 layer. Dielectric 602 may be the same as or different from dielectric 403. Pore 604 is formed in dielectric 602 using any suitable pore forming method known to those of ordinary skill in the art. Pore 604 is essentially a tapered hole reaching across the full depth of dielectric 602 and exposing metal 406 below dielectric 602. Pore 604 is filled with PCM material 404.

[0067] Portion 603 is formed over PCM-filled pore 604 in a manner of a corresponding portion in FIG. 4 or FIG. 5. The techniques usable to form portion 603 can be similar to the techniques used in forming portion 601.

[0068] Again, second instance of dielectric 602 is deposited over second instance of metal 406 layer. Second instance of pore 604 is formed in second instance of dielectric 602 using any suitable pore forming method known to those of ordinary skill in the art. Second instance of pore 604 is filled with PCM material 404.

[0069] Any number of combination devices can be stacked in this manner using pore filling method of fabrication of combination devices. Over the last stacked combination device, top electrode layer 612 is formed using any suitable fabrication method, including but not limited to deposition, patterning, or planting.

[0070] Cs 650 is essentially a single combination device where portion 651 corresponds to portion 601 of stacked combination devices 600. The techniques usable to form portion 651 can be similar to the techniques used in forming portion 601.

[0071] Dielectric 602 is deposited over metal 406, pore 604 is formed, and PCM material 404 is filled in pore 604 in a similar manner as in stacked combination devices 600. Top electrode 612 is formed over PCM-filled pore 604.

[0072] With reference to FIG. 7, this figure depicts a view of the combined structure resulting from a mushroom process of fabrication in accordance with an illustrative embodiment. Any etching of any layer in combination device 700 or 750 can be performed with or without spacers as described in FIGS. 4 and 5.

[0073] Stacked combination device 700 corresponds to stacked combination device 200 instances depicted in FIG. 2. combination device 750 corresponds to any one of parallel combination devices 302 and 304 depicted in FIG. 3.

[0074] With reference to stacked combination devices 700, dielectric 602 is deposited over metal 406 layer. Pore 704 is formed in dielectric 602 using any suitable pore forming method known to those of ordinary skill in the art. Pore 604 is filled with a conducting material, such as a metal, to form bottom electrode 704 of PCM 404. PCM 404 formed over bottom electrode 704 in this manner resembles a mushroom, hence the name of the process. Any number of combination devices can be stacked in this manner using mushroom PCM method of fabrication of combination devices.

[0075] The top of PCM 404 in any given combination device can be metalized with layer 410. Metal layer 410 may either couple with another MIEC layer 402, as in combination device 700 when additional combination devices are stacked above as in combination devices 700, or with top electrode 612 at the last stacked combination device in combination devices 700 or the single combination device as in 750.

[0076] With reference to FIG. 8, this figure depicts an example series of steps in a subtractive etching process according to an illustrative embodiment. Assume that the objective is to form structure 400 of FIG. 4--a stacked combination device without spacers. At the beginning of process 800, suppose that layers 801 have been formed using a suitable method of fabrication. Layers 801 include substrate 401, bottom electrode 408, MIEC 402, metal 406, PCM 404, metal 410, MIEC 402, metal 406, PCM 404, and metal HM 412. Above layers 801, oxide layer 803, OPL 805, ARC 807 and PR layer 809 have been deposited.

[0077] The process begins at step 802 by patterning PR layer 809 into a shape. At step 804, the pattern is transferred to ARC 807 and OPL 805 layers, with PR layer 809 being removed (subtracted). The pattern transfer maintains the substantially vertical orientation of the side walls being formed at those layers.

[0078] At step 806, the lithography continues and the pattern is transferred to oxide 803 and metal HM 412, with ARC layer 807 being removed (subtracted). The pattern transfer maintains the substantially vertical orientation of the side walls being formed at those layers.

[0079] At step 808, OPL 805 is stripped (removed or subtracted). Thereafter, the lithography continues, oxide layer 803 is subtracted, and the same pattern is transferred in step 810 to subsequently lower layers until the etching reaches bottom electrode 408. The etched sides of the various layers above layer 408 are encapsulated in a dielectric material, e.g., dielectric 403. One or more of the horizontal surfaces of the encapsulated structure may also be polished.

[0080] With reference to FIG. 9, this figure depicts another example series of steps in a subtractive etching process according to an illustrative embodiment. Assume that the objective is to form structure 500 of FIG. 5--a stacked combination device with spacers.

[0081] Process 900 begins after process 800 has formed layers 801 and performed steps 802, 804, and 806. Process 900 picks up after step 806 of FIG. 8.

[0082] At step 902, PCM 404 Obelow HM 412 is etched in the same pattern as HM 412 and oxide 803 above. A suitable spacer material 911 is deposited to protect the walls of HM 412 and PCM 404 exposed from the etching. Spacer 911 is a part of spacer 505 in FIG. 5. Adding spacer 911 changes the pattern for the layers below PCM 404.

[0083] At step 904, layers 406 and 402 below PCM 404 are etched according to the new pattern while maintaining substantially vertical etched walls at layers 406 and 402. At step 906, a suitable spacer material 913 is deposited to protect the walls of layers 406 and 402 exposed from the etching. Spacer 913 is another part of spacer 505 in FIG. 5. Adding spacer 913 further changes the pattern for the layers below MIEC layer 402.

[0084] At step 908, layers 410 and 404 below MIEC layer 402 are etched according to the new pattern while maintaining substantially vertical etched walls at layers 410 and 404. At step 910, a suitable spacer material 915 is deposited to protect the walls of layers 410 and 404 exposed from the etching. Spacer 915 is another part of spacer 505 in FIG. 5. Adding spacer 915 further changes the pattern for the layers below PCM layer 404.

[0085] At step 912, layers 406 and 402 below PCM layer 404 are etched according to the new pattern while maintaining substantially vertical etched walls at layers 406 and 402. If further stacked combination devices existed below layer 402 etched at step 912, another spacer would be deposited. Because in the depicted example, back electrode layer 408 has been reached by the etching of step 912, no further etching has to occur. Accordingly, no additional spacer is needed to protect the walls of layers 406 and 402 exposed from the etching of step 912. Thereafter, the etched sides of the various layers above layer 408 are encapsulated in a dielectric material, e.g., dielectric 403. One or more of the horizontal surfaces of the encapsulated structure may also be polished.

[0086] With reference to FIG. 10, this figure depicts an example series of steps in a subtractive etching process according to an illustrative embodiment. Assume that the objective is to form structure 450 of FIG. 4--parallel combination devices without spacers. Process 1000 progresses essentially as process 800 in FIG. 8, except that the patterning forms parallel structures with two or more PR layer structures 809 being formed as shown instead of a single PR layer structure 809 in FIG. 8.

[0087] Thereafter, step 1004 corresponds to step 804 albeit patterning multiple parallel vertical structures instead of a single stacked vertical structure. Layers 809, 807, 805, and 803 are subtracted as the pattern progresses downwards through the layers in substantially the manner of process 800. At step 1010, corresponding to step 810 in FIG. 8, dielectric 403 is filled not only around the parallel structures but also between the parallel structures as shown.

[0088] With reference to FIG. 11, this figure depicts another example series of steps in a subtractive etching process according to an illustrative embodiment. Assume that the objective is to form structure 550 of FIG. 5 --parallel combination devices with spacers. Process 1100 progresses essentially as process 900 in FIG. 9, except that the patterning forms parallel structures with two or more oxide layer structures 803 being formed as shown instead of a single oxide layer structure 803 in FIG. 9.

[0089] Thereafter, step 1104 corresponds to step 904 albeit patterning multiple parallel vertical structures instead of a single stacked vertical structure. Step 1104 also deposits spacer 911 not only on the vertical walls but on all etched areas as shown. Step 1106 etches the spacer material from the horizontal areas atop the vertical structures and metal layer 406.

[0090] Step 1110 corresponds to step 910 in FIG. 9, where the bottommost metal layer 406 and MIEC layer 402 are etched before reaching back electrode layer 408 at each of the parallel structures. At step 1112, corresponding to step 912 in FIG. 9, dielectric 403 is filled not only around the parallel structures but also between the parallel structures as shown.

[0091] With reference to FIG. 12, this figure depicts an example series of steps in a PCM-pore filling process according to an illustrative embodiment. The fabrication of any of the combination devices described herein --stacked or parallel, with or without spacer, or some combination thereof--is possible with process 1200, assume that the objective is to form structure 400 of FIG. 4--a stacked combination device without spacers. At the beginning of process 1200, the process forms layers 1201 using a suitable method of fabrication. Layers 1201 include substrate 401, bottom electrode 408, MIEC 402, and metal 406. Above metal layer 406, oxide layer 803, OPL 805, ARC 807 and PR layer 809 have been deposited. The PCM layers are not yet formed, as they will be formed by pore filling in process 1200.

[0092] The process begins at step 1202 by patterning PR layer 809 into a shape, such as by using a suitable photolithography mask. At step 1204, the pattern is transferred to ARC 807 and OPL 805 layers, with PR layer 809 being removed (subtracted). The pattern transfer maintains the substantially vertical orientation of the side walls being formed at those layers.

[0093] At step 1206, the lithography continues and the pattern is transferred to oxide 803 and metal HM 412, with ARC layer 807 being removed (subtracted). The pattern transfer maintains the substantially vertical orientation of the side walls being formed at those layers.

[0094] At step 1208, OPL 805 is stripped (removed or subtracted). Thereafter, the lithography continues, oxide layer 803 is subtracted, and the same pattern is transferred in step 1210 to subsequently lower layers until the etching reaches bottom electrode 408. Process 1200 continues in FIG. 13.

[0095] With reference to FIG. 13, this figure depicts a continuation of process 1200 in accordance with an illustrative embodiment. At step 1212, the etched sides of the various layers above layer 408 are encapsulated in a dielectric material, e.g., dielectric 403. One or more of the horizontal surfaces of the encapsulated structure may also be polished.

[0096] At step 1214, dielectric 602 is deposited above the encapsulated structure resulting from step 1212. In step 1214, pore 604 is formed in dielectric 602. At step 1216, pore 604 is filled with PCM material 404. As can be seen in step 1216, the fill is not exact and some PCM material 404 may remain above the top level of pore 604. Step 1218 performs CMP or otherwise etches back that PCM material 404 which is overflowing pore 604. PCM material 404 makes electrical contact with metal layer 406 below and is available to make electrical contact with a layer that will be deposited above in step 1220.

[0097] At step 1220, a set of layers for the next stacked combination device are deposited above PCM-filled pore 604. The set of layers includes metal layer 410, MIEC layer 402, metal layer 406, and metal HM 412. Process 1200 continues in FIG. 14.

[0098] With reference to FIG. 14, this figure depicts a continuation of process 1200 in accordance with an illustrative embodiment. At step 1222, HM layer 412 is etched. Layers 406, 402, and 410 below HM 412 are subtractively etched as described herein. The etched sides of the various layers above PCM-filled pore 604 are encapsulated in a dielectric material, e.g., dielectric 403. One or more of the vertical surfaces of the encapsulated stacked structure may also be polished.

[0099] At step 1224, dielectric 602 is deposited above the stacked encapsulated structure resulting from step 1222. In step 1224, pore 604 is formed in dielectric 602. Pore 604 is filled with PCM material 404. CMP or other etchback process is performed to remote that PCM material 404 which is overflowing pore 604. PCM material 404 makes electrical contact with metal layer 406 below and is available to make electrical contact with a layer that will be deposited above in step 1226. Assuming that no more combination devices are to be stacked above, PCM-filled pore 604 can now be capped with top electrode 612.

[0100] With reference to FIG. 15, this figure depicts an example series of steps in a PCM mushroom process according to an illustrative embodiment. The fabrication of any of the combination devices described herein --stacked or parallel, with or without spacer, or some combination thereof--is possible with process 1200, assume that the objective is to form structure 400 of FIG. 4--a stacked combination device without spacers. At the beginning of process 1500, the process forms layers 1201, as in FIG. 12, using a suitable method of fabrication. Layers 1201 include substrate 401, bottom electrode 408, MIEC 402, and metal 406. Above metal layer 406, oxide layer 803, OPL 805, ARC 807 and PR layer 809 have been deposited. The PCM layers are not yet formed, as they will be formed by pore filling and mushrooming in process 1500.

[0101] The process begins at step 1502 by patterning PR layer 809 into a shape, such as by using a suitable photolithography mask. At step 1504, the pattern is transferred to ARC 807 and OPL 805 layers, with PR layer 809 being removed (subtracted). The pattern transfer maintains the substantially vertical orientation of the side walls being formed at those layers.

[0102] At step 1506, the lithography continues and the pattern is transferred to oxide 803 and metal HM 412, with ARC layer 807 being removed (subtracted). The pattern transfer maintains the substantially vertical orientation of the side walls being formed at those layers.

[0103] At step 1508, OPL 805 is stripped (removed or subtracted). Thereafter, the lithography continues, oxide layer 803 is subtracted, and the same pattern is transferred in step 1510 to subsequently lower layers until the etching reaches bottom electrode 408. Process 1500 continues in FIG. 13.

[0104] With reference to FIG. 16, this figure depicts a continuation of process 1500 in accordance with an illustrative embodiment. At step 1512, the etched sides of the various layers above layer 408 are encapsulated in a dielectric material, e.g., dielectric 403. One or more of the horizontal surfaces of the encapsulated structure may also be polished.

[0105] At step 1514, dielectric 602 is deposited above the encapsulated structure resulting from step 1512. In step 1514, pore 604 is formed in dielectric 602. At step 1516, pore 604 is filled with bottom electrode material 408. Note that a material different than material 408 may be used to fill pore 604 so long as the other material is suitable for forming an electrode. The fill may not be exact and some bottom electrode material 408 may remain above the top level of pore 604. Step 1518 performs CMP or otherwise etches back that bottom electrode material 408 which is overflowing pore 604. Bottom electrode material 408 makes electrical contact with metal layer 406 below and is available to make electrical contact with a layer that will be deposited above in step 1820.

[0106] At step 1520, PCM layer 404 is deposited over electrode material filled pore 604. Metal layer 410 is deposited above PCM layer 404. Bottom electrode material 408 in pore 604 thus forms the bottom electrode of mushroomed PCM 404. Process 1500 continues in FIG. 17.

[0107] With reference to FIG. 17, this figure depicts a continuation of process 1500 in accordance with an illustrative embodiment. At step 1522, metal layer 410 and PCM 404 are etched. The etched sides of the various layers above filled pore 604 are encapsulated in a dielectric material, e.g., dielectric 403. One or more of the vertical surfaces of the encapsulated stacked structure may also be polished. The top of metal layer 410 may also be subjected to CMP to enable further deposition as shown in FIG. 18. Process 1500 continues in FIG. 18.

[0108] With reference to FIG. 18, this figure depicts a continuation of process 1500 in accordance with an illustrative embodiment. At step 1524, another stack of layers is deposited to form a stacked combination device above the encapsulated structure resulting from step 1522. MIEC layer 402, metal layer 406 are deposited above the encapsulated structure of step 1522, and etched, encapsulated, and polished as described herein. Dielectric 602 is deposited above resulting stacked encapsulated structure. Pore 604 is formed in dielectric 602. Pore 604 is filled with bottom electrode material 408 or another suitable electrode material. CMP or other etchback is performed to remove that electrode material 408 which is overflowing pore 604.

[0109] Electrode material 408 in pore 604 makes electrical contact with metal layer 406 below and is available to make electrical contact with a layer that will be deposited above.

[0110] PCM layer 404 is deposited over the stacked electrode material filled pore 604. Metal layer 410 is deposited above PCM layer 404. Layers 404 and 410 are subtractively etched, encapsulated, and polished as described herein. Bottom electrode material 408 in stacked pore 604 thus forms the bottom electrode of stacked mushroomed PCM 404. Assuming that no more combination devices are to be stacked above, top metal layer 410 can now be capped with top electrode 612.

[0111] While certain steps and processes are described with certain structures, it is to be understood that the steps and/or processes can be adapted to fabricate any of the structure variations described herein within the scope of the illustrative embodiments. While certain materials are used in multiple layers or structures, it is to be understood that substitute materials or different but functionally equivalent materials can be used in place of the described materials at any layers described herein within the scope of the illustrative embodiments. While certain fabrication methods have been used at certain steps, it is to be understood that a fabrication method may be omitted, added, or modified at a described step to achieve functionally similar result from the semiconductor structure within the scope of the illustrative embodiments. While certain operations are described as a "step," several operations can be combined together to form a single fabrication step in a process described herein. While certain orientations have been referred to as "top" and "bottom" with reference to an example vertical orientation of the proposed device, it is to be understood that the device can be reoriented laterally such that the top and bottom become left/right or right/left, or bottom and top, or front/back or back/front, as the reorientation case may be.

[0112] Thus, a semiconductor device, fabrication method therefor, and a fabrication system or apparatus therefor using a software implementation of the method, are provided in the illustrative embodiments for access device and phase-change memory combination structure and other related features, functions, or operations. Where an embodiment or a portion thereof is described with respect to a type of semiconductor device, the fabrication method, system or apparatus, the software implementation, or a portion thereof, are adaptable or configurable for use with a different manifestation of that type of device.

[0113] The present invention may be a semiconductor device, system, a method, and/or a computer program product at any possible technical detail level of integration. The computer program product may include a computer readable storage medium (or media) having computer readable program instructions thereon for causing a processor to carry out aspects of the present invention. A computer readable storage medium, including but not limited to computer-readable storage devices as used herein, is not to be construed as being transitory signals per se, such as radio waves or other freely propagating electromagnetic waves, electromagnetic waves propagating through a waveguide or other transmission media (e.g., light pulses passing through a fiber-optic cable), or electrical signals transmitted through a wire.

[0114] Computer readable program instructions described herein can be downloaded to respective computing/processing devices from a computer readable storage medium or to an external computer or external storage device via a network, for example, the Internet, a local area network, a wide area network and/or a wireless network.

* * * * *

D00000

D00001

D00002

D00003

D00004

D00005

D00006

D00007

D00008

D00009

D00010

D00011

D00012

D00013

D00014

D00015

D00016

D00017

D00018

XML

uspto.report is an independent third-party trademark research tool that is not affiliated, endorsed, or sponsored by the United States Patent and Trademark Office (USPTO) or any other governmental organization. The information provided by uspto.report is based on publicly available data at the time of writing and is intended for informational purposes only.

While we strive to provide accurate and up-to-date information, we do not guarantee the accuracy, completeness, reliability, or suitability of the information displayed on this site. The use of this site is at your own risk. Any reliance you place on such information is therefore strictly at your own risk.

All official trademark data, including owner information, should be verified by visiting the official USPTO website at www.uspto.gov. This site is not intended to replace professional legal advice and should not be used as a substitute for consulting with a legal professional who is knowledgeable about trademark law.